(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6969586号

(P6969586)

(45) 発行日 令和3年11月24日 (2021.11.24)

(24) 登録日 令和3年11月1日 (2021.11.1)

(51) Int.Cl.

F 1

H01L 29/78 (2006.01)

H01L 29/78 653A

H01L 29/739 (2006.01)

H01L 29/78 655A

H01L 29/06 (2006.01)

H01L 29/78 652P

H01L 29/78 652N

請求項の数 4 (全 17 頁)

(21) 出願番号

特願2019-82275 (P2019-82275)

(22) 出願日

平成31年4月23日 (2019.4.23)

(65) 公開番号

特開2020-181854 (P2020-181854A)

(43) 公開日

令和2年11月5日 (2020.11.5)

審査請求日

令和3年3月26日 (2021.3.26)

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74) 代理人 110001128

特許業務法人ゆうあい特許事務所

(72) 発明者 小田 洋平

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

(72) 発明者 澤田 剛一

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

審査官 西出 隆二

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

二層構造のトレンチゲート構造を有する半導体スイッチング素子を備えた半導体装置であって、

前記半導体スイッチング素子は、

第1導電型のドリフト層(2)と、

前記ドリフト層上に形成された第2導電型のボディ領域(3)と、

前記ボディ領域内における該ボディ領域の表層部に形成され、前記ドリフト層より高不純物濃度とされた第1導電型の第1不純物領域(4)と、

一方向を長手方向とすると共に前記第1不純物領域から前記ボディ領域を貫通して前記ドリフト層に達する複数のトレンチ(5)内それぞれに、絶縁膜(6)を介して、シールド電極(7)と中間絶縁膜(9)およびゲート電極層(8)が順に積層されて二層構造とされた複数のトレンチゲート構造と、

前記ドリフト層を挟んで前記ボディ領域と反対側に形成され、前記ドリフト層よりも高不純物濃度とされた第1または第2導電型の高濃度層(1)と、

前記トレンチゲート構造と前記ボディ領域および前記第1不純物領域の上に配置され、前記ボディ領域や前記第1不純物領域に繋がるコンタクトホール(11a)が形成された層間絶縁膜(11)と、

前記コンタクトホールを通じて前記第1不純物領域および前記ボディ領域と電気的に接続される上部電極(10)と、

10

20

前記高濃度層と電気的に接続された下部電極（15）と、を有し、前記シールド電極が前記ゲート電極層の先端部よりも外側まで延設されており、該シールド電極と前記ゲート電極層の底面との間に加えて前記ゲート電極層の先端部との間ににおいても前記中間絶縁膜が形成されており、

前記一方向において、前記ゲート電極層の先端部から前記シールド電極までの間ににおいて絶縁機能を発揮する部分の距離となる実効絶縁距離（L<sub>i</sub>）が、前記中間絶縁膜のうち前記ゲート電極層の底部に位置している部分の厚み（T<sub>b</sub>）よりも大きくなっている、

前記一方向において、前記ゲート電極層の先端部と前記シールド電極との間に、前記中間絶縁膜および該中間絶縁膜と前記ゲート電極層の先端部との間に埋込まれた埋込絶縁膜（11d）のみが配置されており、

前記実効絶縁距離が、前記中間絶縁膜のうち前記ゲート電極層の先端部に位置している部分の厚さ（T<sub>a</sub>）と前記埋込絶縁膜の幅（W）を足した値となっている、半導体装置。

【請求項2】

二層構造のトレンチゲート構造を有する半導体スイッチング素子を備えた半導体装置であって、

前記半導体スイッチング素子は、

第1導電型のドリフト層（2）と、

前記ドリフト層上に形成された第2導電型のボディ領域（3）と、

前記ボディ領域内における該ボディ領域の表層部に形成され、前記ドリフト層より高不純物濃度とされた第1導電型の第1不純物領域（4）と、

一方向を長手方向とすると共に前記第1不純物領域から前記ボディ領域を貫通して前記ドリフト層に達する複数のトレンチ（5）内それぞれに、絶縁膜（6）を介して、シールド電極（7）と中間絶縁膜（9）およびゲート電極層（8）が順に積層されて二層構造とされた複数のトレンチゲート構造と、

前記ドリフト層を挟んで前記ボディ領域と反対側に形成され、前記ドリフト層よりも高不純物濃度とされた第1または第2導電型の高濃度層（1）と、

前記トレンチゲート構造と前記ボディ領域および前記第1不純物領域の上に配置され、前記ボディ領域や前記第1不純物領域に繋がるコンタクトホール（11a）が形成された層間絶縁膜（11）と、

前記コンタクトホールを通じて前記第1不純物領域および前記ボディ領域と電気的に接続される上部電極（10）と、

前記高濃度層と電気的に接続された下部電極（15）と、を有し、

前記シールド電極が前記ゲート電極層の先端部よりも外側まで延設されており、該シールド電極と前記ゲート電極層の底面との間に加えて前記ゲート電極層の先端部との間ににおいても前記中間絶縁膜が形成されており、

前記一方向において、前記ゲート電極層の先端部から前記シールド電極までの間ににおいて絶縁機能を発揮する部分の距離となる実効絶縁距離（L<sub>i</sub>）が、前記中間絶縁膜のうち前記ゲート電極層の底部に位置している部分の厚み（T<sub>b</sub>）よりも大きくなっている、

前記一方向において、前記ゲート電極層の先端部と前記シールド電極との間に、前記中間絶縁膜および該中間絶縁膜と前記ゲート電極層の先端部との間に埋込まれた埋込絶縁膜（11d）に加えて、前記ゲート電極層の一部で構成されかつ前記ゲート電極層から離れた残渣部（8a）が備えられており、

前記実効絶縁距離が、前記中間絶縁膜のうち前記ゲート電極層の先端部に位置している部分の厚さ（T<sub>a</sub>）と前記埋込絶縁膜の幅（W）を足した値となっている、半導体装置。

【請求項3】

トレンチゲート構造を有する半導体スイッチング素子を備えた半導体装置の製造方法であって、

第1導電型または第2導電型の高濃度層（1）と、該高濃度層の一面側に形成され、該高濃度層よりも低不純物濃度とされた第1導電型のドリフト層（2）と、を有する基板（1、2）を用意することと、

10

20

30

40

50

前記ドリフト層に対して、一方向を長手方向とする複数のトレンチ(5)を形成したのち、該複数のトレンチ内それぞれに、絶縁膜(6)を介して、シールド電極(7)と中間絶縁膜(9)およびゲート電極層(8)を順に積層して二層構造の複数のトレンチゲート構造を形成することと、

前記複数のトレンチの間の位置における前記ドリフト層上に、第2導電型のボディ領域(3)を形成することと、

前記ボディ領域内における該ボディ領域の一部の表面部に、前記ドリフト層より高不純物濃度とされた第1導電型の第1不純物領域(4)を形成することと、

前記トレンチゲート構造と前記ボディ領域および前記第1不純物領域の上に層間絶縁膜(11)を形成することと、

前記層間絶縁膜に対して前記ボディ領域や前記第1不純物領域に繋がるコンタクトホール(11a)を形成することと、

前記コンタクトホールを通じて前記第1不純物領域および前記ボディ領域と電気的に接続される上部電極(10)を形成することと、

前記高濃度層と電気的に接続される下部電極(15)を形成することと、を含み、

前記トレンチゲート構造を形成することでは、

前記絶縁膜を介して、前記複数のトレンチの底面および前記一方向における該複数のトレンチの先端部に前記シールド電極を形成することと、

前記シールド電極の上に前記中間絶縁膜を形成することと、

前記中間絶縁膜の上に前記ゲート電極層を形成したのち、前記一方向における先端部において前記ゲート電極層を部分的に除去することと、

前記複数のトレンチ内における前記ゲート電極層が部分的に除去された部分を埋込絶縁膜(11d)で埋込むことと、を行う半導体装置の製造方法。

#### 【請求項4】

前記埋込絶縁膜で埋込むことは、

前記層間絶縁膜を形成することの際に、前記複数のトレンチ内における前記ゲート電極層が部分的に除去された部分に前記層間絶縁膜の一部を前記埋込絶縁膜として埋込むことである、請求項3に記載の半導体装置の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、二層構造のトレンチゲート構造を有する半導体スイッチング素子を備えた半導体装置およびその製造方法に関するものである。

##### 【背景技術】

##### 【0002】

従来、例えば特許文献1に示されるような二層構造のトレンチゲート構造を有するMOSFETを備えた半導体装置が知られている。この半導体装置では、n<sup>+</sup>型基板の上にn<sup>-</sup>型ドリフト層を形成した半導体基板の表層部に、二層構造のトレンチゲートが形成される。トレンチゲート構造は、ゲートトレンチの底部側にシールド絶縁膜を介してソース電位とされるシールド電極が配置されると共に、トレンチ内におけるシールド電極の上側にゲート絶縁膜を介してゲート電極層が配置されることで二層構造とされる。シールド電極とゲート電極層との間には層間絶縁膜(以下、中間絶縁膜という)が形成され、中間絶縁膜によってシールド電極とゲート電極層とが絶縁されている。

##### 【0003】

また、ゲートトレンチは、一方向を長手方向とするライン状で構成され、ゲートトレンチに沿ってシールド電極およびゲート電極層が形成されている。そして、シールド電極とのコンタクトが採れるように、ゲートトレンチの先端部ではシールド電極が半導体基板の表面まで形成されており、ゲート電極層よりもシールド電極の方がトレンチの先端部まで延設されている。

##### 【先行技術文献】

10

20

30

40

50

**【特許文献】****【0004】**

【特許文献1】米国特許第6750508号明細書

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

しかしながら、上記のような構造とする場合、ゲートトレンチの先端部において、シールド電極のうちのゲートトレンチの深さ方向に沿う側壁上への中間絶縁膜の付き周りが製造方法や工程バラツキによって変化する。このため、トレンチゲート構造の長手方向の先端において、該長手方向における内側の位置よりも中間絶縁膜の絶縁耐圧が低くなり、狙った信頼性が得られなくなることがある。10

**【0006】**

また、上記のように二層構造のトレンチゲート構造を有する半導体装置の場合、絶縁膜にバイアスが加わる構造体が多数存在する。このような構造の場合、例えば、スクリーニング用の電圧をそれぞれの絶縁膜、すなわちシールド絶縁膜や中間絶縁膜、ゲート絶縁膜などに対して印加し、所望する絶縁耐圧が得られないものを不良品として除外するという工程が行われる。このことからも、中間絶縁膜の絶縁耐圧が低くなることを抑制することが必要となる。

**【0007】**

本発明は上記点に鑑みて、二層構造のトレンチゲート構造における中間絶縁膜の絶縁耐圧を確保できる構造の半導体スイッチング素子を備えた半導体装置およびその製造方法を提供することを目的とする。20

**【課題を解決するための手段】****【0008】**

上記目的を達成するため、請求項1または2に記載の半導体装置では、半導体スイッチング素子は、第1導電型のドリフト層(2)と、ドリフト層上に形成された第2導電型のボディ領域(3)と、ボディ領域内における該ボディ領域の表層部に形成され、ドリフト層より高不純物濃度とされた第1導電型の第1不純物領域(4)と、一方向を長手方向とすると共に第1不純物領域からボディ領域を貫通してドリフト層に達する複数のトレンチ(5)内それぞれに、絶縁膜(6)を介して、シールド電極(7)と中間絶縁膜(9)およびゲート電極層(8)が順に積層されて二層構造とされた複数のトレンチゲート構造と、ドリフト層を挟んでボディ領域と反対側に形成され、ドリフト層よりも高不純物濃度とされた第1または第2導電型の高濃度層(1)と、トレンチゲート構造とボディ領域および第1不純物領域の上に配置され、ボディ領域や第1不純物領域に繋がるコンタクトホール(11a)が形成された層間絶縁膜(11)と、コンタクトホールを通じて第1不純物領域およびボディ領域と電気的に接続される上部電極(10)と、高濃度層と電気的に接続された下部電極(15)と、を有している。30

**【0009】**

そして、シールド電極がゲート電極層の先端部よりも外側まで延設されており、該シールド電極とゲート電極層の底面との間に加えてゲート電極層の先端部との間においても中間絶縁膜が形成されており、前記一方向において、ゲート電極層の先端部からシールド電極までの間ににおいて絶縁機能を発揮する部分の距離となる実効絶縁距離( $L_i$ )が、中間絶縁膜のうちゲート電極層の底部に位置している部分の厚み( $T_b$ )よりも大きくなっている。40

**【0010】**

このような構成によれば、中間絶縁膜の形成され方が製造方法や工程バラツキによって変化したとしても、ゲート電極層のうちの先端部での中間絶縁膜の絶縁耐圧を確保することが可能となる。したがって、中間絶縁膜の絶縁耐圧が低下することを抑制でき、狙った信頼性を確保することができる。

**【0011】**

10

20

30

40

50

請求項3に記載の半導体装置の製造方法では、第1導電型または第2導電型の高濃度層(1)と、該高濃度層の一面側に形成され、該高濃度層よりも低不純物濃度とされた第1導電型のドリフト層(2)と、を有する基板(1、2)を用意することと、ドリフト層に対して、一方向を長手方向とする複数のトレンチ(5)を形成したのち、該複数のトレンチ内それぞれに、絶縁膜(6)を介して、シールド電極(7)と中間絶縁膜(9)およびゲート電極層(8)を順に積層して二層構造の複数のトレンチゲート構造を形成することと、複数のトレンチの間ににおけるドリフト層上に、第2導電型のボディ領域(3)を形成することと、ボディ領域内における該ボディ領域の一部の表面部に、ドリフト層より高不純物濃度とされた第1導電型の第1不純物領域(4)を形成することと、トレンチゲート構造とボディ領域および第1不純物領域の上に層間絶縁膜(11)を形成することと、層間絶縁膜に対してボディ領域や第1不純物領域に繋がるコンタクトホール(11a)を形成することと、コンタクトホールを通じて第1不純物領域およびボディ領域と電気的に接続される上部電極(10)を形成することと、高濃度層と電気的に接続される下部電極(15)を形成することと、を含んでいる。

#### 【0012】

そして、トレンチゲート構造を形成することでは、絶縁膜を介して、複数のトレンチの底面および前記一方向における該複数のトレンチの先端部にシールド電極を形成することと、シールド電極の上に中間絶縁膜を形成することと、中間絶縁膜の上にゲート電極層を形成したのち、前記一方向における先端部においてゲート電極層を部分的に除去することと、複数のトレンチ内におけるゲート電極層が部分的に除去された部分を埋込絶縁膜(11d)で埋込むことと、を行う。

#### 【0013】

このように、レンチゲート構造の長手方向の両先端のゲート電極層が部分的に除去され、その除去された部分が埋込絶縁膜によって埋込まれている。これにより、前記一方向の両先端において、該一方向に沿うゲート電極層の先端からシールド電極までの実効絶縁距離(Li)が中間絶縁膜のうちのゲート電極層の底部に位置している部分の厚さ(Tb)より大きくなる。

#### 【0014】

これにより、中間絶縁膜の形成され方が製造方法や工程バラツキによって変化したとしても、ゲート電極層のうちの先端部での中間絶縁膜の絶縁耐圧を確保することが可能となる。したがって、中間絶縁膜の絶縁耐圧が低下することを抑制でき、狙った信頼性を確保することができる。

#### 【0015】

なお、各構成要素等に付された括弧付きの参照符号は、その構成要素等と後述する実施形態に記載の具体的な構成要素等との対応関係の一例を示すものである。

#### 【図面の簡単な説明】

#### 【0016】

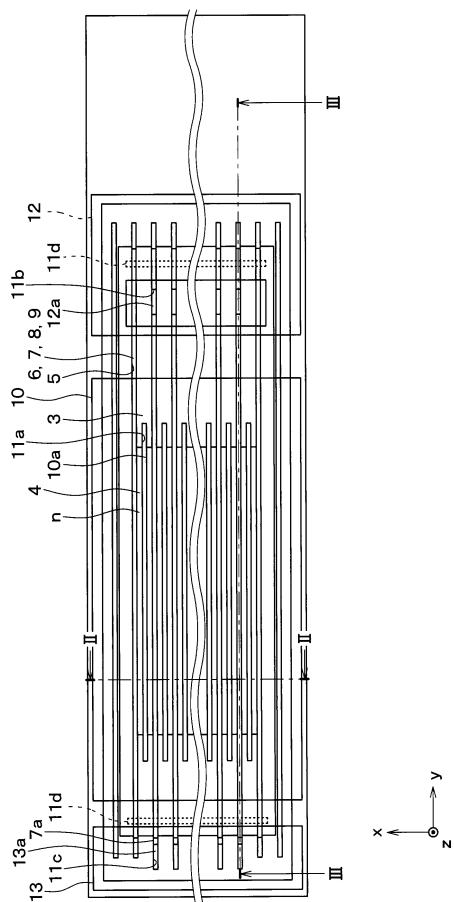

【図1】第1実施形態にかかる半導体装置のセル部の上面レイアウト図である。

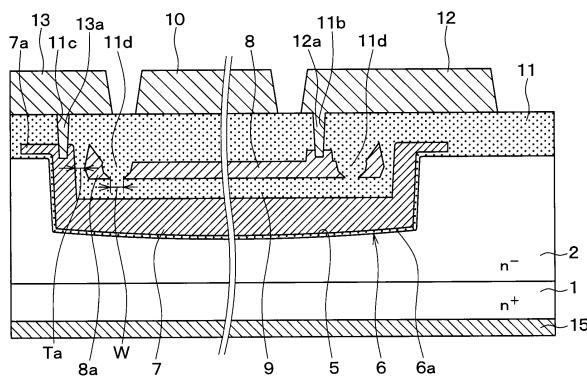

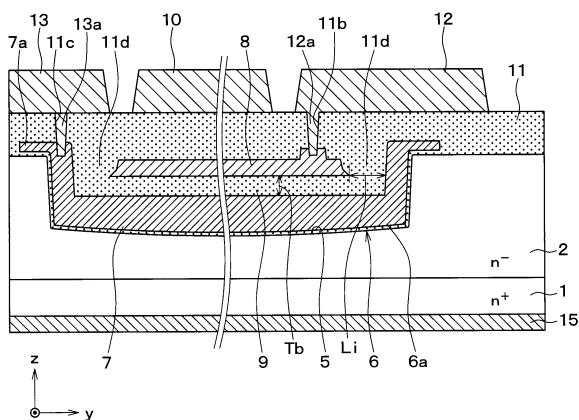

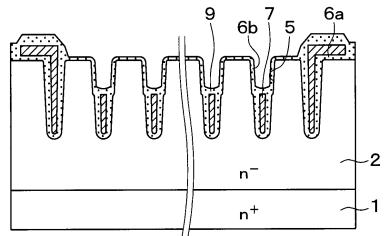

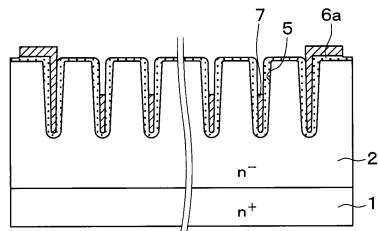

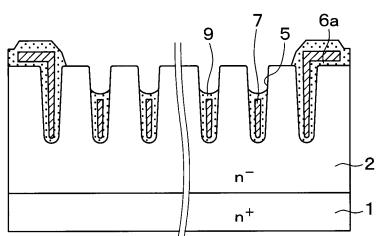

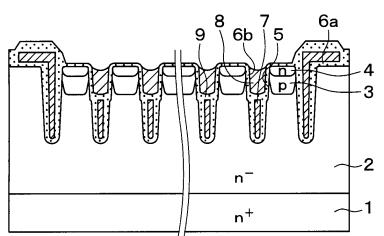

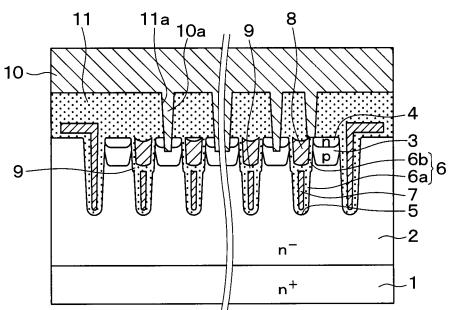

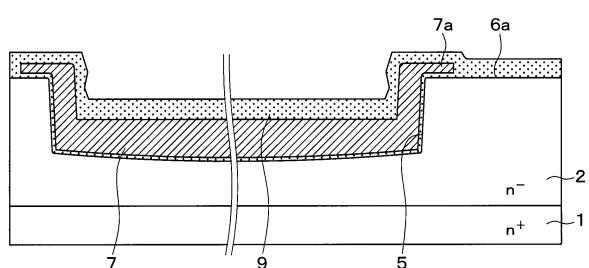

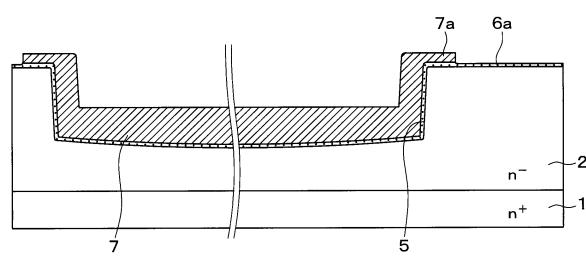

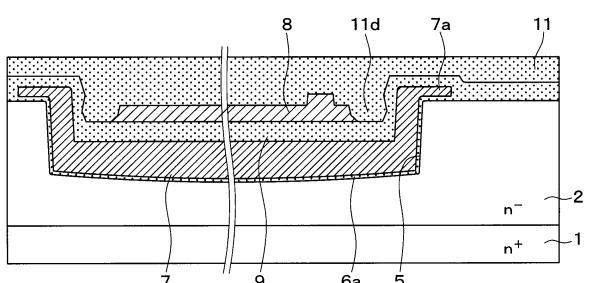

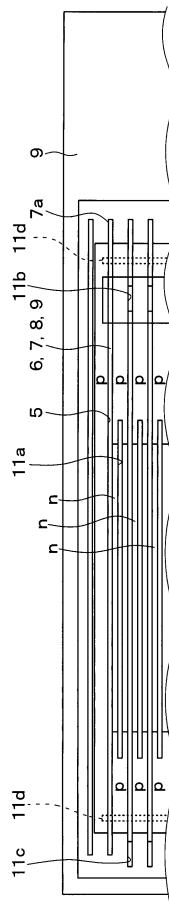

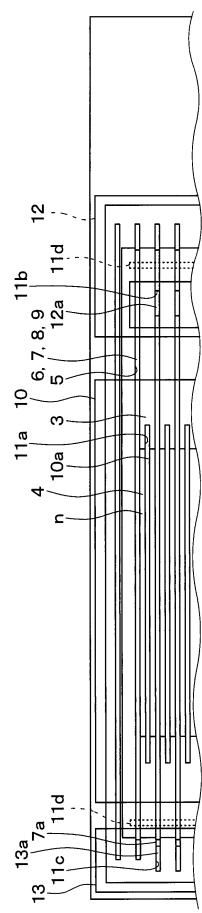

【図2】図1中のII-II断面図である。

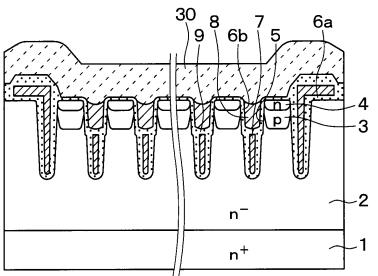

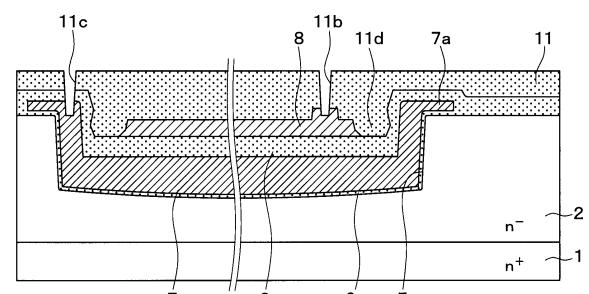

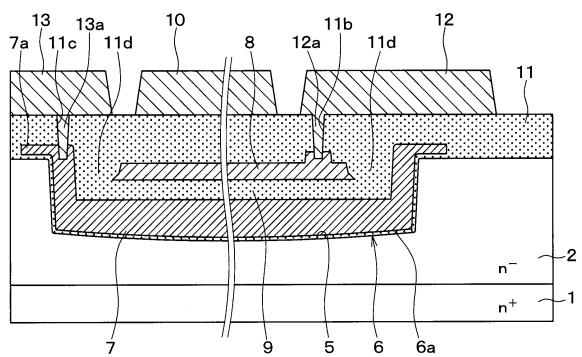

【図3】図1中のIII-III断面図である。

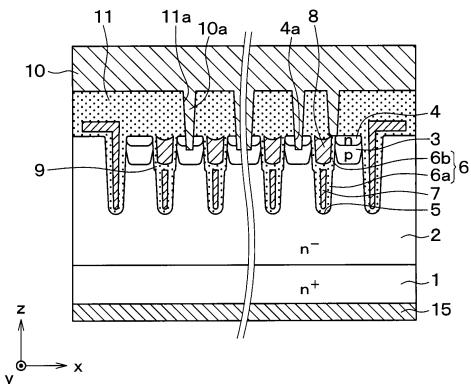

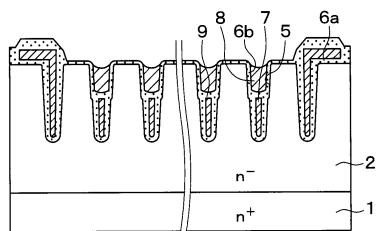

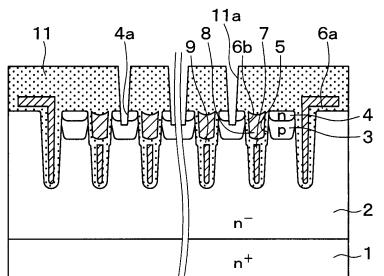

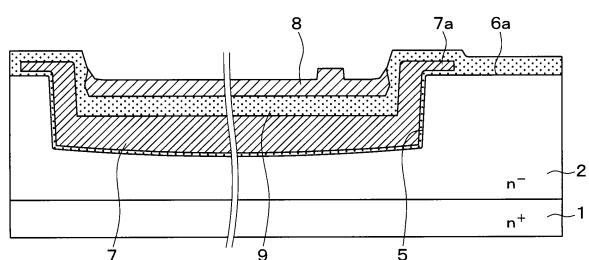

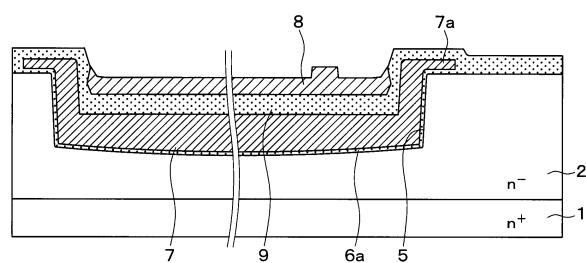

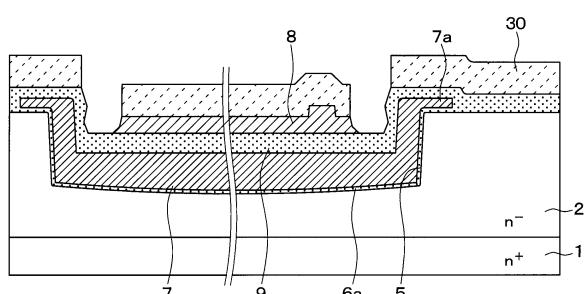

【図4】ゲート電極層の残渣が発生した場合を示した図2に相当する断面図である。

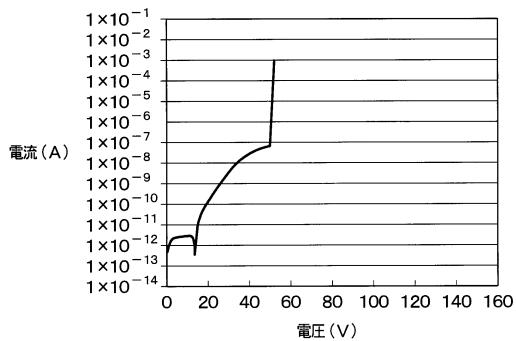

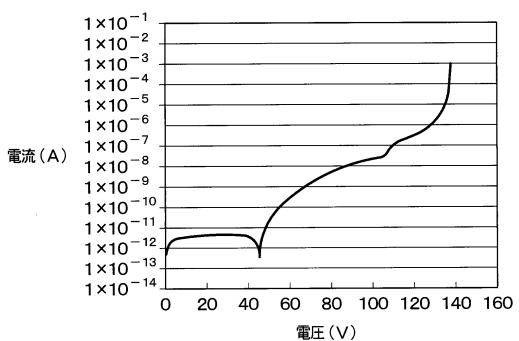

【図5A】従来構造におけるTZDB(Time Zero Dielectric Brake down)波形図である。

【図5B】第1実施形態の構造のTZDB波形図である。

【図6A】第1実施形態にかかる半導体装置の製造工程中の断面図であって、図2に対応する断面での製造工程を示した図である。

【図6B】図6Aに続く半導体装置の製造工程中の断面図である。

【図6C】図6Bに続く半導体装置の製造工程中の断面図である。

【図6D】図6Cに続く半導体装置の製造工程中の断面図である。

【図6E】図6Dに続く半導体装置の製造工程中の断面図である。

10

20

30

40

50

- 【図 6 F】図 6 E に続く半導体装置の製造工程中の断面図である。

- 【図 6 G】図 6 F に続く半導体装置の製造工程中の断面図である。

- 【図 6 H】図 6 G に続く半導体装置の製造工程中の断面図である。

- 【図 6 I】図 6 H に続く半導体装置の製造工程中の断面図である。

- 【図 6 J】図 6 I に続く半導体装置の製造工程中の断面図である。

- 【図 6 K】図 6 J に続く半導体装置の製造工程中の断面図である。

- 【図 7 A】第 1 実施形態にかかる半導体装置の製造工程中の断面図であって、図 3 に対応する断面での製造工程を示した図である。

- 【図 7 B】図 7 A に続く半導体装置の製造工程中の断面図である。

- 【図 7 C】図 7 B に続く半導体装置の製造工程中の断面図である。

- 【図 7 D】図 7 C に続く半導体装置の製造工程中の断面図である。

- 【図 7 E】図 7 D に続く半導体装置の製造工程中の断面図である。

- 【図 7 F】図 7 E に続く半導体装置の製造工程中の断面図である。

- 【図 7 G】図 7 F に続く半導体装置の製造工程中の断面図である。

- 【図 7 H】図 7 G に続く半導体装置の製造工程中の断面図である。

- 【図 7 I】図 7 H に続く半導体装置の製造工程中の断面図である。

- 【図 7 J】図 7 I に続く半導体装置の製造工程中の断面図である。

- 【図 7 K】図 7 J に続く半導体装置の製造工程中の断面図である。

- 【図 8 A】第 1 実施形態にかかる半導体装置の製造工程中のセル部の上面レイアウト図である。

- 【図 8 B】図 8 A に続く半導体装置の製造工程中の断面図である。

- 【図 8 C】図 8 B に続く半導体装置の製造工程中の断面図である。

- 【図 8 D】図 8 C に続く半導体装置の製造工程中の断面図である。

- 【図 8 E】図 8 D に続く半導体装置の製造工程中の断面図である。

- 【図 8 F】図 8 E に続く半導体装置の製造工程中の断面図である。

- 【発明を実施するための形態】

- 【0017】

- 以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、同一符号を付して説明を行う。

- 【0018】

- (第 1 実施形態)

- 第 1 実施形態について説明する。本実施形態では、二層構造のトレンチゲート構造を有する n チャネルタイプの MOSFET が備えられた半導体装置を例に挙げて説明する。以下、図 1 ~ 図 3 に基づいて本実施形態にかかる半導体装置の構造について説明する。

- 【0019】

- なお、これらの図に示す MOSFET は、半導体装置のうちのセル領域に形成されている。実際には、半導体装置は、図 1 に示した部分を囲むように外周領域も設けられるが、ここでは MOSFET のみ図示してある。以下では、図 1 ~ 図 3 に示すように、MOSFET の幅方向を x 方向、x 方向に対して交差する MOSFET の奥行方向を y 方向、MOSFET の厚み方向もしくは深さ方向、つまり x-y 平面に対する法線方向を z 方向として説明する。

- 【0020】

- 図 2 に示すように、本実施形態にかかる半導体装置は、不純物濃度が高濃度とされたシリコン等の半導体材料によって構成された n<sup>+</sup> 型の半導体基板 1 を用いて形成されている。n<sup>+</sup> 型の半導体基板 1 の表面上には、n<sup>+</sup> 型の半導体基板 1 よりも不純物濃度が低濃度とされた n<sup>-</sup> 型ドリフト層 2 が形成されている。

- 【0021】

- また、n<sup>-</sup> 型ドリフト層 2 の表層部の所望位置には、比較的不純物濃度が低く設定された p 型ボディ領域 3 が形成されている。p 型ボディ領域 3 は、例えば n<sup>-</sup> 型ドリフト層 2 に対して p 型不純物をイオン注入することなどによって形成され、チャネル領域を形成す

10

20

30

40

50

るチャネル層としても機能する。p型ボディ領域3は、図1に示すように、後述する複数のトレンチゲート構造の間ににおいて、y方向を長手方向として形成されている。

【0022】

p型ボディ領域3の表層部には、n<sup>-</sup>型ドリフト層2よりも不純物濃度が高濃度とされたソース領域に相当するn型不純物領域4が備えられている。また、n型不純物領域4には、コンタクトトレンチ4aが形成されており、このコンタクトトレンチ4aの底面においてp型ボディ領域3が露出した状態となっている。なお、ここでは図示しないが、p型ボディ領域3のうちの露出した部分に、ボディコンタクトとなるp<sup>+</sup>型コンタクト領域を形成することもできる。さらに、n型不純物領域4のうちのコンタクトトレンチ4aの側面に、ソースコンタクトとなるn<sup>+</sup>型コンタクト領域を形成することもできる。

10

【0023】

また、n<sup>-</sup>型ドリフト層2の表層部のうち各p型ボディ領域3や各n型不純物領域4の間には、一方向を長手方向とする複数本のゲートトレンチ5が形成されている。このゲートトレンチ5はトレンチゲート構造を形成するためのトレンチであり、本実施形態では、各ゲートトレンチ5が等間隔に並行に並べられることでストライプ状のレイアウトとされている。

【0024】

ゲートトレンチ5は、p型ボディ領域3よりも深い位置まで、つまり基板表面側からn型不純物領域4およびp型ボディ領域3を貫通してn<sup>-</sup>型ドリフト層2まで達する深さとされている。また、本実施形態では、ゲートトレンチ5は、底部に向かうほど徐々に幅が狭くなり、底部が丸まった形状とされている。

20

【0025】

ゲートトレンチ5の内壁面は、絶縁膜6によって覆われている。絶縁膜6については、単独の膜で構成されていても良いが、本実施形態の場合は、ゲートトレンチ5のうちの下方部分を覆っているシールド絶縁膜6aと上方部分を覆っているゲート絶縁膜6bとによって構成している。シールド絶縁膜6aは、ゲートトレンチ5の底部から下方部分の側面を覆い、ゲート絶縁膜6bは、ゲートトレンチ5の上方部分の側面を覆っている。本実施形態では、シールド絶縁膜6aをゲート絶縁膜6bよりも厚く形成してある。

【0026】

また、ゲートトレンチ5内には、絶縁膜6を介してドープトPoly-Siによって構成されたシールド電極7およびゲート電極層8が積層されて二層構造となっている。シールド電極7は、ソース電位に固定されることで、ゲート-ドレイン間の容量を小さくし、縦型MOSFETの電気特性の向上を図るために形成されている。ゲート電極層8は、縦型MOSFETのスイッチング動作を行うもので、ゲート電圧印加時にゲートトレンチ5の側面のp型ボディ領域3にチャネル領域を形成する。

30

【0027】

シールド電極7とゲート電極層8との間には中間絶縁膜9が形成されており、中間絶縁膜9によってシールド電極7とゲート電極層8とが絶縁されている。これらゲートトレンチ5、絶縁膜6、シールド電極7、ゲート電極層8および中間絶縁膜9によってトレンチゲート構造が構成されている。このトレンチゲート構造は、例えば図1の紙面左右方向を長手方向として、図1の紙面上下方向、図2で言えば紙面左右方向に複数本が並べられることでストライプ状のレイアウトとされている。

40

【0028】

さらに、図3に示すように、ゲートトレンチ5の長手方向の両端部、すなわち図2の紙面手前側および紙面向こう側の端部において、シールド電極7は、ゲート電極層8よりも外側まで延設されている。そして、それらの部分がシールドライナー7aとしてp型ボディ領域3やn型不純物領域4の表面側から露出させられている。

【0029】

また、ゲート電極層8を覆うように酸化膜などで構成された層間絶縁膜11が形成され、この層間絶縁膜11の上にソース電極に相当する上部電極10やゲート配線12および

50

シールド配線 13 が形成されている。上部電極 10 は、図 2 に示すように、層間絶縁膜 11 に形成されたコンタクトホール 11a 内に埋込まれたタンクステン (W) プラグなどの接続部 10a を通じて p 型ボディ領域 3 や n 型不純物領域 4 と接触させられている。これにより、上部電極 10 が n 型不純物領域 4 および p 型ボディ領域 3 に電気的に接続されている。

【0030】

図 3 に示すように、ゲート配線 12 も、層間絶縁膜 11 に形成されたコンタクトホール 11b 内の W プラグなどの接続部 12a を通じて、ゲート電極層 8 に電気的に接続されている。また、シールド配線 13 も、層間絶縁膜 11 に形成されたコンタクトホール 11c 内の W プラグなどの接続部 13a を通じて、シールド電極 7 に電気的に接続されている。

10

【0031】

また、n<sup>+</sup> 型の半導体基板 1 のうち n<sup>-</sup> 型ドリフト層 2 とは反対側の面にドレイン電極に相当する下部電極 15 が形成されている。このような構成により、縦型 MOSFET の基本構造が構成されている。そして、縦型 MOSFET が複数セル集まって形成されることで、セル領域が構成されている。

【0032】

以上のようにして、縦型 MOSFET を有する半導体装置が構成されている。そして、このように構成される縦型 MOSFET において、y 方向、つまりトレンチゲート構造の長手方向の両先端のゲート電極層 8 が部分的に除去され、その除去された部分が酸化膜などの埋込絶縁膜 11d によって埋込まれている。これにより、y 方向の両先端において、該 y 方向に沿うゲート電極層 8 の先端からシールド電極 7 までの実効絶縁距離 L<sub>i</sub> が中間絶縁膜 9 のうちのゲート電極層 8 の底部に位置している部分の厚さ T<sub>b</sub> より大きくなる。

20

【0033】

これにより、中間絶縁膜 9 の形成され方が製造方法や工程バラツキによって変化したとしても、ゲート電極層 8 のうちの先端部での中間絶縁膜 9 の絶縁耐圧を確保することが可能となる。したがって、中間絶縁膜 9 の絶縁耐圧が低下することを抑制でき、狙った信頼性を確保することができる。

【0034】

ここで、実効絶縁距離 L<sub>i</sub> とは、y 方向に沿うゲート電極層 8 の先端からシールド電極 7 までの間ににおいて絶縁機能を発揮する部分の距離である。

30

【0035】

例えば、図 3 においては、y 方向において、ゲート電極層 8 のうちの先端部が完全に除去されている。この場合、ゲート電極層 8 の先端からシールド電極 7 までの間の距離、つまり絶縁機能を発揮する埋込絶縁膜 11d および中間絶縁膜 9 の y 方向寸法が実効絶縁距離 L<sub>i</sub> となる。これに対して、図 4 に示すように、ゲート電極層 8 の先端部が残渣部 8a として残る場合もある。残渣部 8a が残っていても、埋込絶縁膜 11d および中間絶縁膜 9 が絶縁機能を発揮することから、y 方向におけるゲート電極層 8 とシールド電極 7 との間の絶縁耐圧を確保することはできる。ただし、残渣部 8a についてはほぼ導電体として機能することから、この部分については絶縁機能を発揮しない。したがって、残渣部 8a が存在する場合には、y 方向におけるゲート電極層 8 の先端からシールド電極 7 までの距離より残渣部 8a の寸法分を差し引いた値が実効絶縁距離 L<sub>i</sub> となる。

40

【0036】

実効絶縁距離 L<sub>i</sub> については、少なくとも中間絶縁膜 9 のうちゲート電極層 8 の底部に位置する部分の厚さ T<sub>b</sub> よりも大きくなれば良いが、ほぼ厚さ T<sub>b</sub> に対して埋込絶縁膜 11d の幅 W を足した値になっている。すなわち、製造バラツキなどに起因して中間絶縁膜 9 のうちゲート電極層 8 の先端に位置している部分の厚み T<sub>a</sub> は、部分的に厚み T<sub>b</sub> よりも小さくなり得るが、厚み T<sub>b</sub> と同程度になる。このため、実効絶縁距離 L<sub>i</sub> は、厚み T<sub>b</sub> と同程度の厚み T<sub>a</sub> に対して幅 W を足した値になる。

【0037】

例えば、厚み T<sub>a</sub>、厚み T<sub>b</sub> は、200 nm 程度に設定される。また、幅 W については

50

、 $1 \mu m$ 以上、例えば $3 \sim 4 \mu m$ に設定される。この幅 $W$ は、後述するようにエッティングによりゲート電極層8の先端部を除去したときの幅として設定され、エッティング時のマスク開口幅と横方向エッティング量とによって設定される。このように、ゲート電極層8の先端からシールド電極7までの実効絶縁距離 $L_i$ を中間絶縁膜9のうちのゲート電極層8の底部に位置している部分の厚さ $T_b$ より大きくしているため、中間絶縁膜9の絶縁耐圧が低下することを抑制できる。

#### 【0038】

参考として、T Z D B 波形を調べた。具体的には、ゲート電極層8に対してゲート電圧 $G$ を印加すると共にシールド電極7をソース電圧に相当する接地電位とし、ゲート電圧 $G$ を変化させたときのゲート電極層8とシールド電極7との間に流れる電流の変化を調べた。図5 Aは、従来構造、つまりゲート電極層8のうちの先端部を除去していない構造のT Z D B 波形、図5 Bは、本実施形態の構造のT Z D B 波形を示している。これらの図より、従来構造と比較して、本実施形態の構造の方が、絶縁破壊されるゲート電圧値が大きくなっている。同じゲート電圧 $G$ のときの電流 $I$ を小さい値に抑えられていた。このため、中間絶縁膜9の絶縁耐圧の低下を抑制できていることが判る。

#### 【0039】

次に、本実施形態にかかる半導体装置の製造方法について図6 A～図6 J、図7 A～図7 Jおよび図8 A～図8 Fを参照して説明する。図6 A～図6 Jおよび図7 A～図7 Jは、半導体装置の製造方法における各工程と対応する断面図である。図8 A～図8 Fは、各工程と対応するセル部の上面レイアウト図であるが、一部の工程のみについてのみ示してある。

#### 【0040】

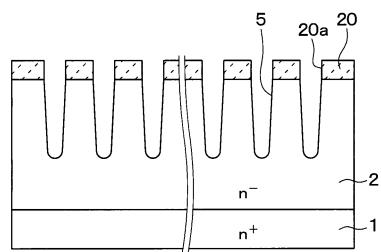

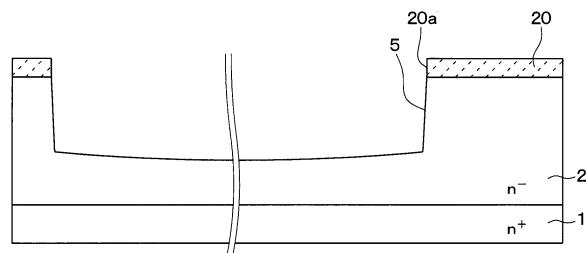

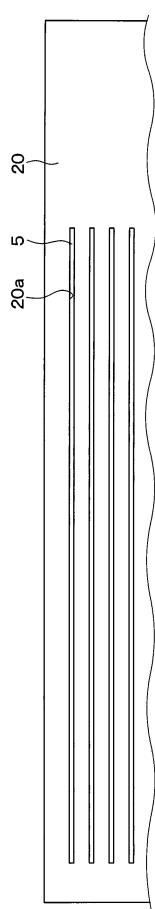

##### 〔図6 A、図7 Aに示す工程〕

まず、半導体基板1を用意し、半導体基板1の表面上にn<sup>-</sup>型ドリフト層2をエピタキシャル成長させることで、高濃度層に相当する半導体基板1の一面側にn<sup>-</sup>型ドリフト層2が形成された基板を用意する。次に、ゲートトレンチ5の形成予定領域が開口するハードマスク20を配置する。このときのハードマスク20の上面レイアウトは図8 Aのようになる。その後、ハードマスク20をマスクとして用いたエッティングによりゲートトレンチ5を形成する。

#### 【0041】

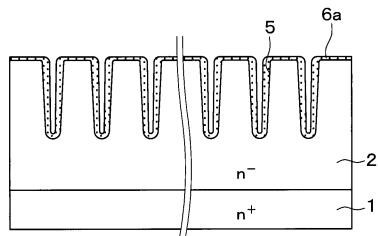

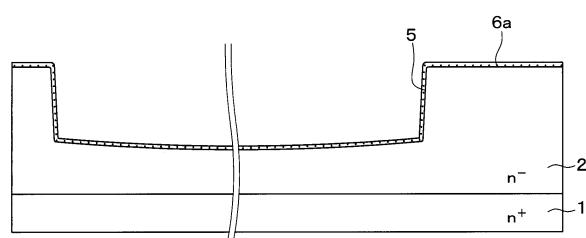

##### 〔図6 B、図7 Bに示す工程〕

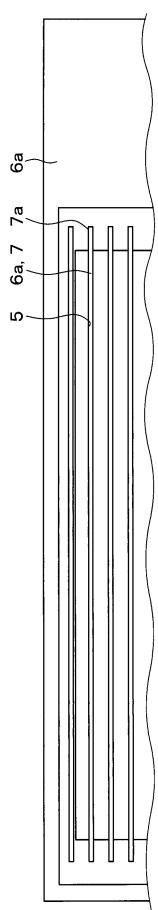

続いて、ハードマスク20を除去した後、熱酸化などによってゲートトレンチ5の内壁面を含めてn<sup>-</sup>型ドリフト層2の表面にシールド絶縁膜6aを形成する。

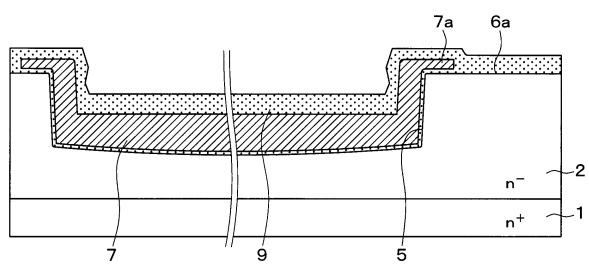

#### 【0042】

##### 〔図6 C、図7 Cに示す工程〕

シールド絶縁膜6aの上にドープトポリシリコンを積んでからエッチバックし、ゲートトレンチ5の底部やゲートトレンチ5の端部などにドープトポリシリコンを残すことでシールド電極7やシールドライナー7aを形成する。また、最も外側に位置するゲートトレンチ5については、ドープトポリシリコンで埋込まれたままとし、シールドライナー7aとして使用する。なお、このときの上面レイアウトは図8 Bのようになる。

#### 【0043】

##### 〔図6 D、図7 Dに示す工程〕

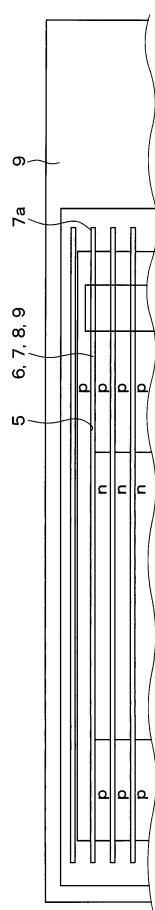

シールド絶縁膜6aのうちゲートトレンチ5の上部の側面上やn<sup>-</sup>型ドリフト層2の表面上に形成された部分をエッティングして除去する。そして、プラズマCVD (chemical vapor deposition) などで絶縁膜をデポジションすることでシールド電極7の上やゲートトレンチ5の上部の側面を覆ったのち、マスクを用いてシールド電極7やシールドライナー7aの上に形成された部分のみが残るようにエッティングする。これにより、中間絶縁膜9が形成される。

#### 【0044】

##### 〔図6 E、図7 Eに示す工程〕

10

20

30

40

50

熱酸化などによってゲートトレンチ 5 の上部の側面上などに絶縁膜を形成することで、ゲート絶縁膜 6 b が形成される。

【0045】

〔図 6 F、図 7 F に示す工程〕

再びドープトポリシリコンを積んでから、エッチバックすることでゲートトレンチ 5 内にゲート電極層 8 を形成する。これにより、トレンチゲート構造が形成される。ゲート電極層 8 のうちの一部については、ゲート配線 1 2 に接続されるため、部分的に上方に突出した状態で残される。なお、このときの上面レイアウトは図 8 C のようになる。

【0046】

〔図 6 G、図 7 G に示す工程〕

10

p 型不純物をイオン注入することにより、p 型ボディ領域 3 を形成する。そして、n 型不純物領域 4 の形成予定領域が開口する図示しないマスクを配置したのち、n 型不純物をイオン注入することで n 型不純物領域 4 を形成する。

【0047】

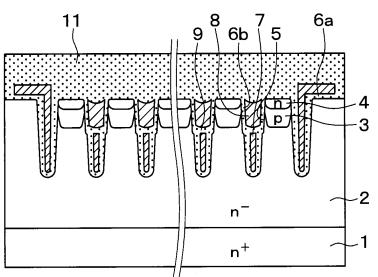

〔図 6 H、図 7 H に示す工程〕

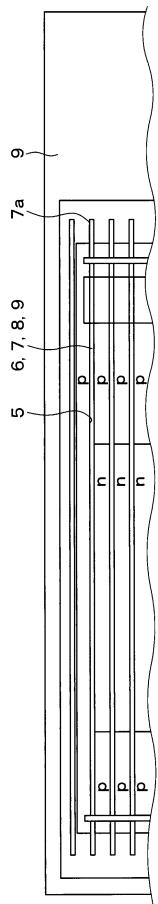

ゲート電極層 8 やゲート絶縁膜 6 b などの表面を覆うようにマスク 3 0 を形成したのち、マスク 3 0 のうちの埋込絶縁膜 1 1 d の形成予定領域を開口させる。そして、マスク 3 0 で覆った状態でドープトポリシリコンをエッチングすることで、ゲート電極層 8 のうちの先端部を除去する。このときの上面レイアウトは図 8 D のようになる。

【0048】

20

このとき、ドープトポリシリコンが確実に除去されるように、オーバエッチング量を 50 % 増加している。例えば、ドープトポリシリコンの厚みを 1  $\mu\text{m}$  としていた場合には、1.5  $\mu\text{m}$  分の厚みを除去できるエッチング量としている。また、このようにした場合、例えばマスク 3 0 の開口幅を 0.4  $\mu\text{m}$  としたとき、横方向エッチング量が 1.5  $\mu\text{m}$  となり、ゲート電極層 8 のうちの先端部を 3.4  $\mu\text{m}$  除去することができる。

【0049】

なお、マスク 3 0 の開口位置によっては、図 4 に示したようにゲート電極層 8 のうちの先端部が全て除去されずに残渣部 8 a として残り得るが、残渣部 8 a が残っていたとしても、実効絶縁距離 L i を設定できるため問題ない。

【0050】

30

〔図 6 I、図 7 I に示す工程〕

続いて、CVD 等によって酸化膜などで構成される層間絶縁膜 1 1 を形成したのち、平坦化研磨を行って層間絶縁膜 1 1 の表面の平坦化を行う。これにより、ゲート電極層 8 のうちの先端部が除去されることで開口した部分にも、層間絶縁膜 1 1 が埋込まれ、この部分が埋込絶縁膜 1 1 d となる。なお、このときの上面レイアウトは図 8 D のようになる。

【0051】

〔図 6 J、図 7 J に示す工程〕

図示しないハードマスクを配置したのち、ハードマスクで覆った状態で層間絶縁膜 1 1 をエッチングすることで、層間絶縁膜 1 1 に対してコンタクトホール 1 1 a ~ 1 1 c を形成する。これにより、n 型不純物領域 4 の表面の一部が露出させられる。

40

【0052】

さらに、ハードマスクを除去したのち、層間絶縁膜 1 1 をマスクとしてシリコンエッチングを行い、コンタクトホール 1 1 a と対応する位置にコンタクトトレンチ 4 a を形成する。これにより、コンタクトトレンチ 4 a の底面において p 型ボディ領域 3 が露出させられる。

【0053】

〔図 6 K、図 7 K に示す工程〕

配線加工工程として、コンタクトホール 1 1 a ~ 1 1 c 内に接続部 1 0 a、1 2 a、1 3 a を形成する工程と行う。そして、さらに層間絶縁膜 1 1 の表面に A 1 等の配線材料を成膜し、それをパターニングすることで上部電極 1 0 やゲート配線 1 2 およびシールド配

50

線 1 3 を形成する。

【 0 0 5 4 】

最後に、下部電極 1 5 の形成工程を行う。このようにして、本実施形態にかかる縦型MOSFETを有する半導体装置が完成する。

【 0 0 5 5 】

以上説明したように、本実施形態の半導体装置では、ゲート電極層 8 の先端からシールド電極 7 までの実効絶縁距離  $L_i$  を中間絶縁膜 9 のうちのゲート電極層 8 の底部に位置している部分の厚さ  $T_b$  より大きくしている。したがって、中間絶縁膜 9 の絶縁耐圧が低下することを抑制でき、狙った信頼性を確保することができる。

【 0 0 5 6 】

10

( 他の実施形態 )

本開示は、上記した実施形態に準拠して記述されたが、当該実施形態に限定されるものではなく、様々な変形例や均等範囲内の変形をも包含する。加えて、様々な組み合わせや形態、さらには、それらに一要素のみ、それ以上、あるいはそれ以下、を含む他の組み合わせや形態をも、本開示の範疇や思想範囲に入るものである。

【 0 0 5 7 】

( 1 ) 例えば、上記実施形態では、半導体基板 1 によって高濃度の不純物領域を形成し、その上に  $n^-$  型ドリフト層 2 をエピタキシャル成長させることで、高濃度層と  $n^-$  型ドリフト層 2 とが形成された基板を構成している。これは、ドリフト層を挟んで  $p$  型ボディ領域 3 と反対側に高濃度層を構成する場合の一例を示したに過ぎず、ドリフト層を半導体基板によって構成し、その一面側にイオン注入等を行うことで高濃度層を形成するようにしても良い。

20

【 0 0 5 8 】

( 2 ) また、上記実施形態では、トレンチゲート構造を形成してから、 $p$  型ボディ領域 3 や  $n$  型不純物領域 4 を形成したが、これらの形成順を逆にしても良い。すなわち、 $p$  型ボディ領域 3 や  $n$  型不純物領域 4 が最終的にトレンチゲート構造の間に位置する部分に形成されれば良い。

【 0 0 5 9 】

( 3 ) また、上記実施形態では、第 1 導電型を  $n$  型、第 2 導電型を  $p$  型とした  $n$  チャネルタイプのトレンチゲート構造のMOSFETを半導体スイッチング素子の一例として説明した。しかしながら、これは一例を示したに過ぎず、他の構造の半導体スイッチング素子、例えば  $n$  チャネルタイプに対して各構成要素の導電型を反転させた  $p$  チャネルタイプのトレンチゲート構造のMOSFETとしても良い。さらに、MOSFET以外に、同様の構造のIGBTに対しても本発明を適用することができる。IGBTの場合、半導体基板 1 の導電型を  $n$  型から  $p$  型に変更する以外は、上記実施形態で説明した縦型MOSFETと同様である。

30

【 符号の説明 】

【 0 0 6 0 】

- 3  $p$  型ボディ領域

- 4  $n$  型不純物領域

- 6 絶縁膜

- 7 シールド電極

- 8 ゲート電極層

- 9 中間絶縁膜

- 10 上部電極

- 11 層間絶縁膜

- 11 a 埋込絶縁膜

- 12 下部電極

40

【 図 1 】

【 図 4 】

【図5A】

【 図 2 】

【図3】

【図5B】

【図 6 A】

【図 6 B】

【図 6 E】

【図 6 C】

【図 6 F】

【図 6 D】

【図 6 G】

【図 6 H】

【図 6 J】

【図 6 I】

【図 6 K】

【図 7 A】

【図 7 D】

【図 7 B】

【図 7 E】

【図 7 C】

【図 7 F】

【図 7 G】

【図 7 I】

【図 7 H】

【図 7 J】

【図 7 K】

【図 8 A】

【図 8 B】

【図 8 C】

【図 8 D】

【図 8 E】

【図 8 F】

---

フロントページの続き

(56)参考文献 特開2016-062981(JP, A)

特開2013-143522(JP, A)

特開2017-045827(JP, A)

特開2012-059943(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/78

H01L 29/739

H01L 29/06