UFFICIO ITALIANO BREVETTI E MARCHI

| DOMANDA NUMERO     | 101999900811892 |  |

|--------------------|-----------------|--|

| Data Deposito      | 31/12/1999      |  |

| Data Pubblicazione | 01/07/2001      |  |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| Н       | 04     | L           |        |             |

### Titolo

METODO DI RECUPERO DEL SEGNALE D'OROLOGIO IN UN SISTEMA DI TELECOMUNICAZIONI E RELATIVO CIRCUITO.

# "METODO DI RECUPERO DEL SEGNALE D'OROLOGIO IN UN SISTEMA DI TELECOMUNICAZIONI E RELATIVO CIRCUITO"

di ALCATEL, di nazionalità francese, con sede in 54 Rue La Boétie, 75008 Parigi, ed elettivamente domiciliata presso il Mandatario Ing. Giorgio Crovini, presso Metroconsult S.r.l, piazza Cavour 3, 10060 None (TO).

Inventore designato: Santo MAGGIO, via Mattei, 56 Gorgonzola (MI)

Paolo TAINA, via Moriano, 9 Vimercate (MI)

Massimiliano RUTAR, via Buonarroti, 2 Carnate (MI)

Depositata il 3 1 DiC. 1999 No.

T099A 001185

## **DESCRIZIONE**

La presente invenzione si riferisce ad un metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni.

Nella realizzazione di sistemi di comunicazione digitale ci si trova spesso nella condizione in cui un oscillatore locale genera la frequenza con cui vengono inviati i dati a un terminale ricevente remoto, il quale, estraendo l'informazione di orologio dai dati stessi, mediante ad esempio un circuito ad aggancio di fase PLL (Phase Locked Loop), utilizza tale frequenza sia per leggere i dati ricevuti sia per temporizzare la propria trasmissione.

In figura 1a è rappresentato a esemplificazione di quanto detto uno schema di principio di una rete di telecomunicazioni di tipo sincrono, ad esempio di tipo SDH (Synchronous Data Hierarchy), nel quale vi è un primo nodo N1, dotato di un primo orologio locale OL1. Detto orologio locale OL1 fornisce la temporizzazione a un trasmettitore TX1. Il primo nodo N1 comunica, inviando un segnale dati DIN, con un secondo nodo N2, il quale in ingresso presenta un circuito ad aggancio di fase PL. Il

Ing. Giorgio CROVINI

circuito ad aggancio di fase PL riceve a un suo ingresso un segnale di orologio di riferimento CKREF generato da un secondo orologio locale OL2. L'orologio locale OL1 e l'orologio locale OL2 sono sincroni per ipotesi, per cui, in linea di principio, il segnale di orologio di riferimento CKREF dovrebbe essere sincrono con il segnale dati in ingresso DIN, mentre la fase di detti segnali può essere differente. Inoltre possono verificarsi anche delle dissintonie fra detti segnali. Il circuito ad aggancio di fase PLL provvede quindi a produrre un segnale d'orologio recuperato RCK sincrono e in fase con il segnale dati in ingresso DIN per scandire correttamente le operazioni di un ricevitore RX2, in modo che sia in grado di decodificare con il campionamento, cioè la scansione corretta, il segnale dati DIN trasmesso secondo il primo orologio locale OL1.

L'uso del circuito PLL per il recupero del segnale di orologio è la soluzione comunemente usata.

Detta soluzione presenta però degli inconvenienti dovuti alla difficoltà di ottenere prestazioni molto elevate per mezzo dei circuiti PLL, specialmente ad alte frequenze, a causa del rumore e dell'accoppiamento elettrico con altri circuiti. In particolare, queste difficoltà si evidenziano in connessione alla trasmissione di dati in reti SDH. Inoltre i circuiti PLL mostrano una forte dipendenza in frequenza, sicchè un impiego del medesimo circuito PLL a una diversa frequenza non è possibile senza riprogettare l'intero anello.

Inoltre l'uso di circuiti PLL notoriamente introduce un 'jitter' cioè una distorsione in frequenza, che si riflette in variazioni di fase.

In alternativa agli anelli ad aggancio di fase, è noto impiegare degli anelli ad aggancio di ritardo noti anche come DLL (Delay Locked Loop).

Gli anelli DLL sono anch'essi basati su anelli di retroazione e comprendono una

linea di ritardo, che riceve in ingresso un segnale di orologio e produce in uscita uno più segnali ritardati rispetto al segnale d'orologio. Un comparatore di fase si occupa quindi di controllare la differenza di fase rispetto al segnale da inseguire e comandare di conseguenza una logica di controllo che governa il ritardo introdotto dalla linea di ritardo.

Uno dei problemi associati a questo tipo di circuiti è che gli elementi di ritardo delle linee di ritardo pur avendo associato un ritardo nominale, presentano all'atto pratico dei notevoli scarti da detto valore nominale di ritardo o sfasamento. Ciò si riflette sul fatto che si devono usare dei valori di ritardo piuttosto elevati, in modo che l'incidenza degli scarti sia poco rilevante. Ne deriva che la partizione che si riesce a operare sul periodo di bit del segnale dati in ingresso non può essere molto fine. Inoltre con circuiti DLL di questo tipo è estremamente difficoltoso inseguire un jitter pronunciato dei dati in ingresso.

La presente invenzione si propone di risolvere gli inconvenienti sopra citati e di indicare un metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni che sia di realizzazione migliorata, e più efficiente rispetto alle soluzioni note.

In tale ambito, scopo principale della presente invenzione è quello di indicare un metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni adatto all'impiego ad alte frequenze.

Un ulteriore scopo della presente invenzione è quello di indicare un metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni che mostri una bassa dipendenza in frequenza dei parametri di progetto.

Un ulteriore scopo della presente invenzione è quello di indicare un metodo di

recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni che permetta di impiegare linee di ritardo, le quali introducano uno sfasamento molto piccolo, e quindi permettano di avere un'elevata risoluzione in fase

Un ulteriore scopo della presente invenzione è quello di indicare un metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni che funzioni anche in presenza di un jitter d'ingresso molto pronunciato.

Per raggiungere tali scopi, formano oggetto della presente invenzione un metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni e/o un circuito di recupero del segnale d'orologio incorporanti le caratteristiche delle rivendicazioni allegate, che formano parte integrante della presente descrizione.

Ulteriori scopi, caratteristiche e vantaggi della presente invenzione risulteranno chiari dalla descrizione particolareggiata che segue e dai disegni annessi, forniti a puro titolo di esempio esplicativo e non limitativo, in cui:

- in figura la è riportato uno schema a blocchi illustrante un sistema di trasmissione e ricezione implementante un metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni secondo l'arte nota;

- in figura 1b è riportato uno schema a blocchi illustrante un sistema di trasmissione e ricezione implementante un metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni secondo l'invenzione

- in figura 2 è riportato uno schema di principio di un circuito realizzante il metodo

di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni secondo l'invenzione;

- in figura 3 è riportato uno schema di principio di un dettaglio del circuito realizzante il metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni di figura 2;

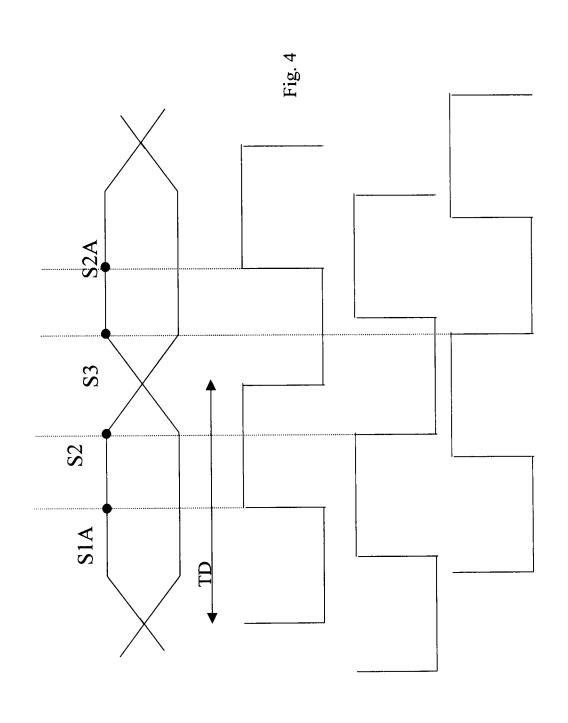

- in figura 4 è riportato un diagramma temporale di segnali impiegati nel circuito di figura 2.

In figura 1b è rappresentato uno schema di principio di un sistema di trasmissione e ricezione analogo a quello di figura 1a, ma recante un circuito di recupero del segnale d'orologio DCR secondo l'invenzione. Come si può notare detto circuito di recupero DCR secondo l'invenzione si sostituisce all'anello ad aggancio di fase PL di figura 1a, operando egualmente sul segnale dati in ingresso DIN e fornendo il segnale d'orologio recuperato RCK al ricevitore RX2.

Il circuito di recupero del segnale d'orologio DCR, come sarà illustrato più chiaramente nel seguito della descrizione, è pero un circuito digitale basato sull'impiego di una linea di ritardo che genera una molteplicità di fasi fra cui selezionare il segnale d'orologio recuperato RCK più conveniente.

In figura 2 è rappresentato uno schema di un circuito di recupero del segnale d'orologio DCR secondo l'invenzione.

Detto circuito comprende un blocco di ritardo LD, che riceve in ingresso il segnale d'orologio di riferimento CKREF e fornisce in uscita m segnali di orologio equiritardati CK1..CKm. Detti segnali d'orologio equiritardati CKREF sono sfasati fra loro di un ritardo o sfasamento T.

Il blocco di ritardo LD è realizzato sostanzialmente attraverso una linea di ritardo, la quale comprende una molteplicità di elementi di ritardo D, ciascuno delle quali

introduce un ritardo nominalmente pari al ritardo T, e di prese P dalle quali si possono prelevare segnali d'orologio crescentemente ritardati. Nel caso di un segnale d'orologio di riferimento CKREF alla frequenza di 622 MHz, cioè con un periodo di bit di 1600 ps, si può impiegare un ritardo T di 100 ps, che determina la necessità di 16 prese P per coprire il periodo di bit.

Il blocco di ritardo LD fornisce in uscita, come già accennato, un numero fisso m di segnali d'orologio equiritardati CK1, ...CKm. Detti segnali equiritardati CK1 ... CKm vengono forniti a un blocco selettore di fase PS, il quale opera solo sui primi n degli m segnali equiritardati CK1...CKm, cioè su dei segnali equiritardati di copertura CK1...CKn, che sono quelli necessari a coprire un periodo di bit TD del segnale dati in ingresso DIN. Nel caso di esempio, n varrà 16, mentre m è un numero intero più grande, dimensionato secondo l'entità delle derive della frequenza che si intende inseguire.

I segnali equiritardati di copertura CK1..CKn vengono inviati in parallelo ad un primo multiplexer MUXA e ad un secondo multiplexer MUXB, che emettono un rispettivo primo segnale di recupero CKA e un secondo segnale di recupero CKB. Detti primo segnale di recupero CKA e secondo segnale di recupero CKB vengono inviati a un blocco commutatore sincrono SPS, il quale è atto a scegliere quale fra il primo segnale di recupero CKA e il secondo segnale di recupero CKB impiegare in qualità di segnale d'orologio recuperato RCK.

Il segnale d'orologio recuperato RCK è inviato a un comparatore di fase PC insieme al segnale dati in ingresso DIN. Detto comparatore di fase PC emette un segnale di fase SF che viene inviato ad un ingresso di un blocco di controllo logico LC.

Detto blocco di controllo logico LC sovrintende al funzionamento del circuito di recupero del segnale d'orologio DCR. Detto blocco di controllo logico LC riceve

infatti dalla linea di ritardo LD l'informazione sul numero n di prese P di detta linea di ritardo LD, che vengono impiegate per coprire il periodo di bit TD del segnale dati in ingresso DIN. Il numero n è fornito al blocco di controllo logico LC attraverso un circuito sensore NS, il cui funzionamento è illustrato in dettaglio in figura 3.

Detto blocco di controllo logico LC riceve inoltre dal comparatore di fase PC un segnale di fase SF, che contiene l'informazione sulla differenza in fase fra il segnale d'orologio recuperato RCK e il segnale dati in ingresso DIN.

Il blocco di controllo logico LC, sulla base di dette informazioni ricevute, emette un segnale di selezione A del primo segnale di recupero CKA e un segnale di selezione B del secondo segnale di recupero CKB, che vengono inviati ai rispettivi primo multiplexer MUXA e secondo multiplexer MUXB del blocco selettore di fase PS. Inoltre detto blocco di controllo logico LC emette un primo segnale di abilitazione ENA e un secondo segnale di abilitazione ENB, che vengono inviati al blocco commutatore sincrono SPS. Detto blocco commutatore sincrono SPS in figura 2 è schematizzato per semplicità tramite due porte logiche LSP1 e LSP2 che ricevono a uno dei loro ingressi rispettivamente il primo segnale di recupero CKA e il secondo segnale di recupero CKB, mentre al loro altro ingresso ricevono rispettivamente il primo segnale di abilitazione ENA e secondo segnale di abilitazione ENB. L'uscita di dette porte logiche LSP1 e LSP2 è inviata a una terza porta logica LSP3, che fornisce in uscita il segnale d'orologio recuperato RCK, selezionato tramite l'azione sul primo segnale di abilitazione ENA e sul secondo segnale di abilitazione ENB, come sarà meglio illustrato più avanti.

Il blocco di controllo logico LC comprende un filtro F e una macchina logica ML, cioè una macchina a stati finiti. Il filtro F riceve il segnale di fase SF e fornisce dei comandi di selezione SC alla macchina logica ML.

Il filtro F consiste sostanzialmente di un contatore up/down.

Viene ora illustrato il funzionamento del circuito di recupero del segnale d'orologio DCR.

Come detto, il segnale d'orologio recuperato RCK e il segnale dati in ingresso vengono comparati nel comparatore di fase PC. Il segnale di fase SF così ottenuto provvede, attraverso al filtro F e ai comandi di selezione SC l'informazione sull'entità della differenza di fase alla macchina logica ML a stati finiti del blocco logico di controllo LC. Detta blocco logico di controllo LC, sulla base che dell'informazione sul numero n di segnali equiritardati di copertura CK1..CKn, secondo le sue regole interne codificate nella macchina logica ML a stati finiti, emette un primo segnale di selezione A, che seleziona tramite primo il multiplexer CKA, quello fra i segnali equiritardati di copertura CK1..CKn più adatto a ridurre la differenza di fase fra il segnale d'orologio recuperato RCK e il segnale dati in ingresso DIN. Viene selezionato in questo modo il primo segnale di recupero CKA. Allo stesso modo il blocco logico di controllo LC seleziona anche il secondo segnale di recupero CKB, tramite il secondo multiplexer MUXB e il secondo segnale di selezione B. Il secondo segnale di recupero CKB è un segnale d'orologio spostato di uno più periodi avanti o indietro rispetto al primo segnale di recupero CKA e corrisponde alla correzione successiva che viene apportata dal blocco logico di controllo LC.

Dopo l'invio del primo segnale di selezione A o del secondo segnale di selezione B il blocco logico di controllo LC invia il primo segnale di abilitazione ENA e il secondo segnale di abilitazione ENB per pilotare il blocco commutatore sincrono SPS a commutare fra il primo segnale di recupero CKA e il secondo segnale di recupero CKB secondo la necessità. Ciò determina nel segnale d'orologio recuperato CKR

all'uscita di detto blocco commutatore sincrono SPS, uno spostamento di fase in anticipo o in ritardo.

Dopo che il blocco commutatore sincrono SPS ha effettuato la commutazione, il contatore del filtro F viene riassettato portando il suo valore a mezzo del suo campo di variazione, e il filtro F ricomincia ad accumulare le informazioni provenienti tramite il segnale di fase SF sulla comparazione fra il segnale dati in ingresso DIN e il segnale d'orologio recuperato RCK, che ora ha subito uno spostamento di fase, come descrittp.

In figura 3 è rappresentato il circuito sensore NS, il quale comprende un multiplexer MUXc, il quale riceve in ingresso gli m segnali equiritardati CK1...CKn, ed è pilotato da un segnale di contatore C, generato da una base tempi, qui non mostrata. Il segnale di contatore C pilota il multiplexer MUXc in modo che alla sua uscita, un segnale scandito CKc, siano successivamente presenti, nell'arco di un periodo di bit TD, tutti i segnali equiritardati CK1..CKm. Il segnale scandito CKc è inviato quindi a un campionatore SMP che impiega come riferimento il segnale d'orologio CK1, cioè il segnale coincidente con il segnale di riferimento CKREF. Il campionatore SMP rileva quando la comparazione con il segnale d'orologio CK1 produce uno zero logico, in quanto il segnale scandito CKc ha la medesima fase del segnale d'orologio CK1, e il valore del segnale di contatore C corrisponde al numero n di segnale equiritardati spaziati di copertura CK1...CKn del periodo di bit TD.

In figura 4 è rappresentato un diagramma temporale dei segnali impiegati dal comparatore di fase PC, che verrà impiegato per illustrare più in dettaglio sia il funzionamento del comparatore di fase PC, sia il funzionamento del blocco logico di controllo LC e del blocco commutatore sincrono SPS.

Sono illustrati il segnale dati in ingresso DIN, il segnale d'orologio recuperato RCK,

nonché un segnale anticipato ACK e un segnale ritardato DCK, che corrispondono rispettivamente a segnali d'orologio in anticipo e in ritardo rispetto alla transizione del segnale dati in ingresso DIN di un ritardo T.

Dunque le transizioni del segnale d'orologio recuperato, del segnale anticipato ACK e del segnale ritardato DCK, utilizzati come segnali di campionamento dal comparatore di fase PC, identificano quattro campioni S1A, S2, S3 e S1B. Ad ogni periodo del segnale d'orologio dunque il comparatore di fase PC raccoglie quattro campioni e si può dare una delle seguenti condizioni:

- tutti i campioni S1A, S2, S3, S1B sono eguali (ad esempio ci sono due bit consecutivi eguali): il comparatore di fase PC invia come segnale di fase SF un segnale di mantenimento M;

- S1A e S2 sono eguali, S3 e S1B sono eguali, ma le due coppie differiscono fra loro: il comparatore di fase PC invia come segnale di fase SF un segnale di mantenimento MT;

- S1A, S2, S3 sono eguali, ma differiscono da S1B; ciò significa che il segnale di campionamento, cioè il segnale d'orologio recuperato RCK deve venire ritardato: il comparatore di fase PC invia come segnale di fase SF un segnale di ritardo DY;

- S2, S3, S1B sono eguali, ma differiscono da S1A; ciò significa che il segnale di campionamento, cioè il segnale d'orologio recuperato RCK deve venire anticipato: il comparatore di fase PC invia come segnale di fase SF un segnale di anticipo AD;

- Viene rilevata una condizione anomala (ad esempio S1A e S1B sono eguali, S2 e S3 sono eguali, ma le coppie differiscono. Ciò può avvenire se il segnale d'orlogio recuperato CKR è vicino alla transizione del segnale dati in ingresso DIN e i segnali ACK e DCK sono vicini al centro del bit); viene inviato un

segnale di deriva DR, atto a spostare la fase del segnale d'orologio di un ottavo di periodo per uscire dalla condizione anomala;

Il segnale di mantenimento MT, il segnale di anticipo AD, il segnale di ritardo DY e il segnale di deriva DR costituiscono il contenuto del segnale di fase SF, che viene inviato al contatore che costituisce il filtro F. Detto contatore up/down:

- incrementa di 1 se riceve il segnale di ritardo DY;

- decrementa di 1 se riceve il segnale di anticipo AD;

- rimane inalterato se riceve il segnale di mantenimento MT.

Quando il contatore del filtro F raggiunge il suo massimo emette un comando di ritardo del'orologio MDC, che viene inviato alla macchina a stati ML. Quando il contatore del filtro F raggiunge invece il suo minimo emette un comando di anticipo dell'orologio MAC verso la macchina a stati ML. Il comando di ritardo del'orologio MDC e il comando di anticipo dell'orologio MAC corrispondono ai comandi di selezione SC sopra citati.

La macchina a stati ML riceve i comandi di selezione SC e genera il primo segnale di selezione A (o il secondo segnale di selezione B) secondo le seguentire regole:

- quando riceve un comando di ritardo dell'orologio MDC, seleziona uno fra i segnali equiritardati di copertura CK1...CKn all'ingresso del primo multiplexer MUXA (o del secondo multiplexer MUXB) che sia ritardato di un ritardo T rispetto a quello ultimo selezionato; se il segnale ultimo selezionato era quello con il massimo ritardo ottenibile dal blocco di ritardo DL, cioè il segnale CKn, il nuovo segnale selezionato tramite il primo segnale di selezione A (o il secondo segnale di selezione B) sarà il segnale CK1;

- quando riceve un comando di anticipo dell'orologio MAC, seleziona uno fra i segnali equiritardati di copertura CK1...CKn all'ingresso del primo multiplexer

MUXA (o del secondo multiplexer MUXB) che sia anticipato di un ritardo T rispetto a quello ultimo selezionato; se il segnale ultimo selezionato era quello con il minimo ritardo ottenibile dal blocco di ritardo DL, cioè il segnale CK1, il nuovo segnale selezionato tramite il primo segnale di selezione A (o il secondo segnale di selezione B) sarà il segnale CKn.

Il blocco commutatore sincrono SPS, come detto, agisce successivamente e il segnale di recupero CKA e il segnale di recupero CKB sono presenti all'uscita del blocco commutatore sincrono SPS contemporaneamente per una durata di circa mezzo periodo d'orologio dopo la commutazione, in modo da permettere la transizione nonostante la frequenza di funzionamento molto elevata (622 MHz). Il primo e secondo segnale di abilitazione ENA e il secondo segnale di abilitazione ENB servono a inibire il funzionamento del blocco commutatore sincrono SPS negli intervalli in cui, alla sua uscita a causa della logica impiegata e dei livelli dei segnali, potrebbero prodursi i cosiddetti 'glitch' cioè transizioni spurie.

Il comparatore di fase PC descritto è di realizzazione particolarmente semplificata a scopo di chiarezza, ma le sue capacità possono facilmente essere aumentate facendolo operare su un maggior numero di segnali come i segnali ACK e DCK. Ad esempio, provvedendo due ulteriori segnali d'orologio sfalsati in anticipo o in ritardo di due ritardi T si possono avere sei campioni per ogni periodo del segnale dati in ingresso DIN, sicché è possibile nel segnale di fase SF fornire ad esempio un segnale di anticipo AD ed un segnale di forte anticipo ADF. Il filtro F, ricevendo il segnale di anticipo AD incrementa di 1 il contatore, ricevendo il segnale di forte anticipo ADF incrementa di 2 detto contatore, in modo da favorire una più rapida convergenza del circuito di recupero del segnale d'orologio DCR. Analogamente ci si comporta per i segnali in ritardo.

Il numero n di prese P del blocco di ritardo LD per coprire il periodo di bit del segnale dati in ingresso DIN, come è evidente dalla precedente descrizione, è variabile nel tempo, in modo da inseguire le eventuali derive del segnale dati in ingresso DIN.

E' inoltre chiaro che la realizzazione pratica del comparatore di fase PC sarà alquanto differente dalla sua descrizione qui fornita a livello di principi di funzionamento. Ad esempio, sarà opportuno usare il solo segnale d'orologio recuperato RCK e ricavare il segnale ACK e il segnale DCK, come anche gli ulteriori segnali sfalsati che si volessero impiegare, attraverso prese di una linea di ritardo contenuta all'interno dello stesso comparatore di fase PC.

Inoltre nella realizzazione pratica, al fine di minimizzare le connessioni, per attuare il campionamento come descritto in figura 3, sarà in realtà il segnale dati in ingresso DIN a passare attraverso le linee di ritardo del comparatore di fase PC, venendo ora anticipato, ora sfalsato, e si effettuerà la comparazione delle diverse fasi del segnale dati in ingresso DIN così ottenute con l'unico segnale d'orologio recuperato RCK.

In questo modo si evita inoltre di dover provvedere una molteplicità di blocchi SPS (tre nel caso di esempio).

Dalla descrizione effettuata risultano pertanto chiare le caratteristiche della presente invenzione, così come chiari risultano i suoi vantaggi.

Il metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni secondo l'invenzione permette vantaggiosamente di realizzare un circuito digitale con un elevata immunità al rumore, sia in quanto circuito digitale sia in quanto il dato viene campionato solo una volta. Inoltre è possibile provvedere molti circuiti su uno stesso chip, in quanto, essendo il circuito secondo l'invenzione digitale, non dà luogo ad accoppiamenti fra parti diverse del

circuito.

Inoltre, vantaggiosamente, è possibile realizzare linee di ritardo, le quali introducono un ritardo molto piccolo, e quindi avere un'elevata risoluzione in fase, in quanto si impiega un ritardo nominalmente fisso fra le prese della linea di ritardo e si varia dinamicamente il numero n di prese che vengono utilizzate dal circuito sulla base di una comparazione fra la somma dei ritardi e il periodo di bit. In questo modo, le tolleranze e le derive della linea di ritardo non incidono gravemente, in quanto il circuito di recupero del segnale d'orologio secondo l'invenzione si basa sul ritardo reale introdotto dalla linea di ritardo, che viene misurato di volta in volta attraverso il numero di prese attive.

Ciò permette vantaggiosamente di impiegare elementi di ritardo che introducono valori piccoli di ritardo.

Inoltre vantaggiosamente il metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni e il relativo circuito mostrano una dipendenza molto bassa dalla frequenza di funzionamento, in quanto è possibile facilmente scalare il ritardo imposto dalla linea di ritardo e coprire con detto ritardo variato un nuovo periodo di bit.

Inoltre vantaggiosamente il metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni e il relativo circuito secondo l'invenzione funzionano anche in presenza di un jitter d'ingresso illimitato, grazie alla capacità di garantire una rapida convergenza.

Questa caratteristica rende ad esempio il metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni e il relativo circuito secondo l'invenzione adatti a eseguire una funzione di 'dejittering' qualora venga usato un orologio di sistema a bassa frequenza, moltiplicato in frequenza da un PLL

analogico.

E' chiaro che numerose varianti sono possibili per l'uomo del ramo al metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni e/o circuito di recupero del segnale d'orologio descritto come esempio, senza per questo uscire dai principi di novità insiti nell'idea inventiva, così come è chiaro che nella sua pratica attuazione le forme dei dettagli illustrati potranno essere diverse, e gli stessi potranno essere sostituiti con degli elementi tecnicamente equivalenti.

\* \* \* \* \* \* \* \*

Ing. Giorgio CROVINI

# Ing. Giorgio CROVIN Graps Carti

#### RIVENDICAZIONI

- 1. Metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni nel quale è previsto di comparare il segnale dati in ingresso (DIN) con un segnale di orologio recuperato (RCK) per controllare la generazione di detto segnale d'orologio recuperato (RCK) e prevede di generare una pluralità di segnali d'orologio ritardati (CK1...CKn) ricavata ritardando in maniera molteplice almeno un segnale di riferimento (CKREF), detti segnali d'orologio ritardati (CK1... CKn) essendo sfasati fra loro caratterizzato dal fatto chedetti segnali d'orologio ritardati (CK1... CKn) presentano uno sfasamento (T) fra loro che è nominalmente costante nel tempo e inoltre si prevede di selezionare il segnale d'orologio recuperato (RCK) fra detti segnali d'orologio ritardati (CK1...CKn).

- 2. Metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni secondo la rivendicazione 1 caratterizzato dal fatto di impiegare un numero (n) di segnali ritardati (CK1... CKn) tale che la somma degli sfasamenti (T) associati a tali segnali ritardati (CK1...CKn) copra il periodo di bit (TD) del segnale dati in ingresso (DIN).

- 3. Metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni secondo la rivendicazione 2 caratterizzato dal fatto che detto numero (n) di segnali ritardati (CK1... CKn) tale che la somma dei tempi di ritardo (T) associati a tali segnali ritardati (CK1...CKn) copra il periodo di bit (TD) del segnale dati in ingresso (DIN), viene variato dinamicamente, tramite un'operazione di paragone del periodo di bit (TD) con la somma degli sfasamenti (T),.

- 4. Metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un

sistema di telecomunicazioni secondo la rivendicazione 3 caratterizzato dal fatto che lo sfasamento (T) tra ogni coppia adiacente di segnali ritardati (CK1...CKn) è nominalmente eguale.

- 5. Metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni secondo la rivendicazione 3, caratterizzato dal fatto che detta pluralità di segnali d'orologio ritardati (CK1...CKn) è ricavata ritardando in maniera molteplice un unico segnale di riferimento (CKREF).

- 6. Metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni secondo la rivendicazione 4, caratterizzato dal fatto di selezionare un primo segnale di recupero (CKA) e un secondo segnale di recupero (CKB) prima di selezionare il segnale d'orologio di recupero (RCK)

- 7. Metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni secondo la rivendicazione 5, caratterizzato dal fatto di commutare fra detti primo segnale di recupero (CKA) e secondo segnale di recupero (CKB) per la selezione del segnale d'orologio di recupero (RCK).

- 8. Metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni secondo le rivendicazioni 5 o 6 caratterizzato dal fatto che il primo segnale di recupero (CKA) e il secondo segnale di recupero (CKB) sono sfasati di un intervallo di tempo (T).

- 9. Metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni secondo la rivendicazione 5 caratterizzato dal fatto che sono previsti segnali di abilitazione (ENA, ENB) per abilitare la commutazione fra il primo segnale di recupero (CKA) e il secondo segnale di

- recupero (CKB).

- 10. Metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni secondo la rivendicazione 1 e seguenti caratterizzato dal fatto di comparare il segnale dati in ingresso (DIN) con il segnale di orologio recuperato (RCK), impiegando la comparazione di più fasi del segnale dati in ingresso (DIN) e/o del segnale d'orologio recuperato (RCK, ACK, DCK) al fine di ottenere una pluralità di campioni (S1A, S2, S3, S1B) per ciclo di campionamento.

- 11. Metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni secondo la rivendicazione 9 caratterizzato dal fatto di filtrare l'uscita (SF) dell'operazione di comparazione.

- 12. Circuito di recupero del segnale d'orologio da un segnale dati in ingresso (DIN) in una rete di telecomunicazioni, del tipo che comprende un comparatore di fase (PC) che paragona la fase del segnale dati in ingresso (DIN) e la fase di un segnale d'orologio di recupero (RCK) per fornire un'informazione di fase (SF) che controlla mezzi di generazione (LD, PS, SPS, LC) di detto segnale d'orologio di recupero caratterizzato dal fatto che detti mezzi di generazione (LD, PS, SPS, LC) comprendono una linea di ritardo (LD) dotata di una pluralità di prese (P) per generare una pluralità di segnali ritardati (CK1...CKn)

- 13. Circuito di recupero del segnale d'orologio secondo la rivendicazione 10 caratterizzato dal fatto che i mezzi di generazione (LD, PS, SPS, LC) comprendono mezzi di selezione (PS, SPS, LC) del segnale d'orologio recuperato (CKR).

- 14. Circuito di recupero del segnale d'orologio secondo la rivendicazione 12 caratterizzato dal fatto che i mezzi di selezione (PS, SPS, LC) comprendono un

primo blocco di selezione (PS) per selezionare un primo segnale di recupero (CKA) e un secondo segnale di recupero (CKB) dalla pluralità di segnali ritardati (CK1...CKn) e comprendono inoltre un secondo blocco di commutazione (SPS) per commutare fra detti primo segnale di recupero (CKA) e secondo segnale di recupero (CKB).

- 15. Circuito di recupero del segnale d'orologio secondo la rivendicazione 13 caratterizzato dal fatto che i mezzi di selezione (PS, SPS, LC) comprendono inoltre una logica di controllo (LC) che pilota il primo blocco di selezione (PS) e il secondo blocco di commutazione (SPS) in base all'informazione di fase (SF) fornita dal comparatore di fase (PC)

- 16. Circuito di recupero del segnale d'orologio secondo la rivendicazione 14 caratterizzato dal fatto che la logica di controllo (LC) comprende un filtro (F) per filtrare l'informazione di fase (SF).

- 17. Circuito di recupero del segnale d'orologio secondo la rivendicazione 14 caratterizzato dal fatto che la logica di controllo comprende una macchina logica (ML) che emette dei segnali di selezione (A;B) e di abilitazione (ENA, ENB) in base all'informazione di fase (SF).

- 18. Metodo di recupero del segnale d'orologio da un segnale dati in ingresso in un sistema di telecomunicazioni e/o circuito di recupero del segnale d'orologio che secondo gli insegnamenti della presente descrizione e dei disegni annessi.

\* \* \* \* \* \*

p.i. Ing. Giorgio Crovini

(No. Iscr. Albo 857B)

Fig. 3

Ing. Giorgio CROVINI

Ş

Ing. Giorgio CROVINI

Ö

gion him

RCK

ACK

DIN

Ing. Giorgio CROVINI

in the