(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4605952号

(P4605952)

(45) 発行日 平成23年1月5日(2011.1.5)

(24) 登録日 平成22年10月15日(2010.10.15)

|              |           |

|--------------|-----------|

| (51) Int.Cl. | F 1       |

| HO2J 7/02    | (2006.01) |

| HO2J 7/00    | (2006.01) |

| B60L 11/18   | (2006.01) |

| HO1M 10/44   | (2006.01) |

| HO2J         | 7/02      |

| HO2J         | 7/00      |

| B60L         | 11/18     |

| HO1M         | 10/44     |

請求項の数 45 (全 30 頁)

(21) 出願番号 特願2001-258859 (P2001-258859)

(22) 出願日 平成13年8月29日 (2001.8.29)

(65) 公開番号 特開2003-70179 (P2003-70179A)

(43) 公開日 平成15年3月7日 (2003.3.7)

審査請求日 平成20年8月28日 (2008.8.28)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(73) 特許権者 000001203

新神戸電機株式会社

東京都中央区明石町8番1号

(74) 代理人 100077816

弁理士 春日 謙

(72) 発明者 宮崎 英樹

茨城県日立市大みか町七丁目1番1号

株式会社 日立製作所 日立

研究所内

最終頁に続く

(54) 【発明の名称】蓄電装置及びその制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

電気的に直列に接続され、それぞれ、電気的に直列に接続された複数のバッテリセルを有する複数のバッテリモジュールと、

前記複数のバッテリモジュールのそれぞれに対応して設けられて、対応するバッテリモジュールが有する複数のバッテリセルのそれぞれの状態を検出すると共に、第1信号伝送路によって電気的に非絶縁状態で直列に接続された複数の第1制御装置と、を有し、

前記複数の第1制御装置のそれぞれは、前記第1信号伝送路に信号を出力するための信号出回路、前記第1信号伝送路から信号を入力するための信号入回路、及びロジック回路を備えており、

前記複数の第1制御装置の直列接続は、電気的な接続が絶縁手段によって絶縁された第2信号伝送路を介して第2制御装置に接続されており、

さらに、前記複数の第1制御装置の直列接続は、直列に接続される一方の第1制御装置のロジック回路から他方の第1制御装置のロジック回路に出力される信号によって前記一方の第1制御装置の信号出回路が動作して、前記一方の第1制御装置の信号出回路から前記第1信号伝送路を介して前記他方の第1制御装置の信号入回路に電流が供給され、その電流によって前記他方の第1制御装置の信号入回路が動作して、前記一方の第1制御装置のロジック回路から出力された信号が前記他方の第1制御装置のロジック回路に伝送されることにより、前記第2制御装置から前記第2信号伝送路を介して入力された指令信号を、電気的に非絶縁状態で直列に伝送する、

ことを特徴とする蓄電装置。

【請求項 2】

電気的に直列に接続され、それぞれ、電気的に直列に接続された複数のバッテリセルを有する複数のバッテリモジュールと、

前記複数のバッテリモジュールのそれぞれに対応して設けられて、対応するバッテリモジュールが有する複数のバッテリセルのそれぞれの状態を検出すると共に、第1信号伝送路によって電気的に非絶縁状態で直列に接続された複数の第1制御装置と、を有し、

前記複数の第1制御装置のそれぞれは、前記第1信号伝送路に信号を出力するための信号出力回路、前記第1信号伝送路から信号を入力するための信号入力回路、及びロジック回路を備えており、

前記信号出力回路は定電流出力回路によって構成されており、

前記信号入力回路は電位変換回路によって構成されており、

前記複数の第1制御装置の直列接続は、電気的な接続が絶縁手段によって絶縁された第2信号伝送路を介して第2制御装置に接続されており、

さらに、前記複数の第1制御装置の直列接続は、直列に接続される一方の第1制御装置のロジック回路から他方の第1制御装置のロジック回路に出力される信号によって前記一方の第1制御装置の定電流出力回路が動作して、前記一方の第1制御装置の定電流出力回路から前記第1信号伝送路を介して前記他方の第1制御装置の電位変換回路に定電流が供給され、その定電流によって前記他方の第1制御装置の電位変換回路が動作して、前記一方の第1制御装置のロジック回路から出力された信号が前記他方の第1制御装置のロジック回路に電位変換されて伝送されることにより、前記第2制御装置から前記第2信号伝送路を介して入力された指令信号を、電気的に非絶縁状態で直列に伝送する、

ことを特徴とする蓄電装置。

【請求項 3】

請求項1又は2に記載の蓄電装置において、

前記絶縁手段は、前記絶縁によって分けられた信号伝送路の異なる基準電位を維持する

、

ことを特徴とする蓄電装置。

【請求項 4】

電気的に直列に接続され、それぞれ、電気的に直列に接続された複数のバッテリセルを有する複数のバッテリモジュールと、

第1信号伝送路と、

前記複数のバッテリモジュールのそれぞれに対応して設けられて、対応するバッテリモジュールが有する複数のバッテリセルのそれぞれの状態を検出すると共に、前記第1信号伝送路によって電気的に非絶縁状態で直列に接続された複数の第1制御装置と、

電気的な接続が絶縁手段によって絶縁され、前記複数の第1制御装置の直列接続と、前記複数の第1制御装置の直列接続に対して指令信号を出力する第2制御装置とを接続する第2信号伝送路と、を有し、

前記絶縁手段は、前記第1制御装置が第1電圧に維持され、前記第2制御装置が、前記第1電圧よりも低い第2電圧に維持されるように、前記第2信号伝送路に配置されており、

前記複数の第1制御装置は、それぞれ、信号入出力回路及びロジック回路を有する集積回路から構成されており、

前記複数の第1制御装置の直列接続は、直列に接続される一方の集積回路のロジック回路から他方の集積回路のロジック回路に出力される信号によって前記一方の集積回路の信号出力回路が動作して、前記一方の集積回路の信号出力回路から前記第1信号伝送路を介して前記他方の集積回路の信号入力回路に電流が供給され、その電流によって前記他方の集積回路の信号入力回路が動作して、前記一方の集積回路のロジック回路から出力された信号が前記他方の集積回路のロジック回路に伝送されることにより、前記第2制御装置から前記第2信号伝送路を介して入力された指令信号を、電気的に非絶縁状態で直列に伝送

10

20

30

40

50

しており、

前記直列に接続される一方の集積回路の信号入力回路と他方の集積回路の信号出力回路は異なる基準電位を有する、

ことを特徴とする蓄電装置。

【請求項 5】

請求項 4 に記載の蓄電装置において、

前記絶縁手段は、前記第 2 信号伝送路の前記第 2 制御装置側の低電圧信号伝送路から、前記第 2 信号伝送路の前記第 1 制御装置側の高電圧信号伝送路に前記指令信号を伝送する、

ことを特徴とする蓄電装置。

10

【請求項 6】

電気的に直列に接続され、それぞれ、電気的に直列に接続された複数のバッテリセルを有する複数のバッテリモジュールと、前記複数のバッテリモジュールのそれぞれに対応して設けられて、対応するバッテリモジュールが有する複数のバッテリセルのそれぞれの状態を検出すると共に、第 1 信号伝送路によって電気的に非絶縁状態で直列に接続された複数の第 1 制御装置と、を有する第 1 回路領域と、

前記複数の第 1 制御装置の直列接続に対して指令信号を出力する第 2 制御装置を有し、前記第 1 回路領域とは基準電位が異なる第 2 回路領域と、

前記第 1 及び第 2 回路領域の異なる基準電位を維持し、前記第 1 及び第 2 回路領域を接続するための装置と、を有し、

20

前記複数の第 1 制御装置のそれぞれは、前記第 1 信号伝送路に信号を出力するための信号出力回路、前記第 1 信号伝送路から信号を入力するための信号入力回路、及びロジック回路を備えており、

前記複数の第 1 制御装置の直列接続は、直列に接続される一方の第 1 制御装置のロジック回路から他方の第 1 制御装置のロジック回路に出力される信号によって前記一方の第 1 制御装置の信号出力回路が動作して、前記一方の第 1 制御装置の信号出力回路から前記第 1 信号伝送路を介して前記他方の第 1 制御装置の信号入力回路に電流が供給され、その電流によって前記他方の第 1 制御装置の信号入力回路が動作して、前記一方の第 1 制御装置のロジック回路から出力された信号が前記他方の第 1 制御装置のロジック回路に伝送されることにより、前記第 2 制御装置から前記第 1 及び第 2 回路領域を接続するための装置を介して入力された指令信号を、電気的に非絶縁状態で直列に伝送する、

ことを特徴とする蓄電装置。

30

【請求項 7】

請求項 6 に記載の蓄電装置において、

前記第 1 及び第 2 回路領域は、前記第 1 及び第 2 回路領域を接続する装置によって電気的に分けられる、

ことを特徴とする蓄電装置。

【請求項 8】

電気的に直列に接続され、それぞれ、電気的に直列に接続された複数のバッテリセルを有する複数のバッテリモジュールと、

40

前記複数のバッテリモジュールのそれぞれに対応して設けられ、絶縁手段を介して第 2 制御装置から伝送された指令信号を受信して、対応するバッテリモジュールが有する複数のバッテリセルの状態を検出すると共に、信号伝送路によって電気的に非絶縁状態で直列に接続された複数の第 1 制御装置と、を有し、

前記複数の第 1 制御装置は、それぞれ、集積回路から構成されており、

前記複数の集積回路は、それぞれ、信号入力端子、信号出力端子、電圧検出端子、前記信号入力端子を介して信号を受信する信号入力回路、前記信号出力端子を介して信号を送信する信号出力回路、ロジック回路、及び前記電圧検出端子を介して、対応するバッテリモジュールが有する複数のバッテリセルのそれぞれの電圧を検出する電圧検出回路を有しており、

50

さらに、前記複数の集積回路は、異なる基準電位を有し、直列に接続される一方の集積回路の信号出力端子と他方の集積回路の信号入力端子とが前記信号伝送路によって電気的に非絶縁状態で接続されていると共に、直列に接続される一方の集積回路のロジック回路から他方の集積回路のロジック回路に出力される信号によって前記一方の集積回路の信号出力回路が動作して、前記一方の集積回路の信号出力回路から前記信号伝送路を介して前記他方の集積回路の信号入力回路に電流が供給され、その電流によって前記他方の集積回路の信号入力回路が動作して、前記一方の集積回路のロジック回路から出力された信号が前記他方の集積回路のロジック回路に伝送されることにより、前記第2制御装置から前記絶縁手段を介して入力された指令信号を、電気的に非絶縁状態で直列に伝送する、ことを特徴とする蓄電装置。

10

## 【請求項9】

電気的に直列に接続され、それぞれ、電気的に直列に接続された複数のバッテリセルを有する複数のバッテリモジュールと、

前記複数のバッテリモジュールのそれぞれに対応して設けられ、絶縁手段を介して第2制御装置から伝送された指令信号を受信して、対応するバッテリモジュールが有する複数のバッテリセルの状態を検出すると共に、信号伝送路によって電気的に非絶縁状態で直列に接続された複数の第1制御装置と、を有し、

前記複数の第1制御装置は、それぞれ、集積回路から構成されており、

前記複数の集積回路は、それぞれ、信号入力端子、信号出力端子、電圧検出端子、前記信号入力端子を介して信号を受信する信号入力回路、前記信号出力端子を介して信号を送信する信号出力回路、ロジック回路、及び前記電圧検出端子を介して、対応するバッテリモジュールが有する複数のバッテリセルのそれぞれの電圧を検出する電圧検出回路を有しており、

20

前記信号出力回路は定電流出力回路によって構成されており、

前記信号入力回路は電位変換回路によって構成されており、

さらに、前記複数の集積回路は、異なる基準電位を有し、直列に接続される一方の集積回路の信号出力端子と他方の集積回路の信号入力端子とが前記信号伝送路によって電気的に非絶縁状態で接続されていると共に、直列に接続される一方の集積回路のロジック回路から他方の集積回路のロジック回路に出力される信号によって前記一方の集積回路の定電流出力回路が動作して、前記一方の集積回路の定電流出力回路から前記信号伝送路を介して前記他方の集積回路の電位変換回路に定電流が供給され、その定電流によって前記他方の集積回路の電位変換回路が動作して、前記一方の集積回路のロジック回路から出力された信号が前記他方の集積回路のロジック回路に電位変換されて伝送されることにより、前記第2制御装置から前記絶縁手段を介して入力された指令信号を、電気的に非絶縁状態で直列に伝送する、

30

ことを特徴とする蓄電装置。

## 【請求項10】

車両に搭載される蓄電装置であって、

電気的に直列に接続され、それぞれ、電気的に直列に接続された複数のバッテリセルを有する複数のバッテリモジュールと、

40

前記複数のバッテリモジュールのそれぞれに対応して設けられ、絶縁手段を介して第2制御装置から伝送された指令信号を受信して、対応するバッテリモジュールが有する複数のバッテリセルの状態を検出する複数の第1制御装置と、を有し、

前記複数の第1制御装置は、それぞれ、信号入力端子を介して信号を受信する信号入力回路、信号出力端子を介して信号を送信する信号出力回路、及びロジック回路を備え、前記複数の第1制御装置のそれぞれの信号出力端子が、直列に接続される他の第1制御装置の信号入力端子に信号伝送路を介して接続されることにより、電気的に非絶縁状態で直列に接続されており、

前記直列に接続された複数の第1制御装置は、前記絶縁手段を介して前記第2制御装置から前記指令信号を受信し、

50

さらに、前記直列に接続された複数の第1制御装置は、直列に接続される一方の第1制御装置のロジック回路から他方の第1制御装置のロジック回路に出力される信号によって前記一方の第1制御装置の信号出力回路が動作して、前記一方の第1制御装置の信号出力回路から前記信号伝送路を介して前記他方の第1制御装置の信号入力回路に電流が供給され、その電流によって前記他方の第1制御装置の信号入力回路が動作して、前記一方の第1制御装置のロジック回路から出力された信号が前記他方の第1制御装置のロジック回路に伝送されることにより、前記第2制御装置から前記絶縁手段を介して受信した指令信号を、電気的に非絶縁状態で直列に伝送する、

ことを特徴とする蓄電装置。

## 【請求項11】

10

車両に搭載される蓄電装置であって、

電気的に直列に接続され、それぞれ、電気的に直列に接続された複数のバッテリセルを有する複数のバッテリモジュールと、

前記複数のバッテリモジュールのそれぞれに対応して設けられ、絶縁手段を介して第2制御装置から伝送された指令信号を受信して、対応するバッテリモジュールが有する複数のバッテリセルの状態を検出する複数の第1制御装置と、を有し、

前記複数の第1制御装置は、それぞれ、信号入力端子を介して信号を受信する信号入力回路、信号出力端子を介して信号を送信する信号出力回路、及びロジック回路を備え、前記複数の第1制御装置のそれぞれの信号出力端子が、直列に接続される他の第1制御装置の信号入力端子に信号伝送路を介して接続されることにより、電気的に非絶縁状態で直列に接続されており、

前記信号出力回路は定電流出力回路によって構成されており、

20

前記信号入力回路は電位変換回路によって構成されており、

前記直列に接続された複数の第1制御装置は、前記絶縁手段を介して前記第2制御装置から前記指令信号を受信し、

さらに、前記直列に接続された複数の第1制御装置は、直列に接続される一方の第1制御装置のロジック回路から他方の第1制御装置のロジック回路に出力される信号によって前記一方の第1制御装置の定電流出力回路が動作して、前記一方の第1制御装置の定電流出力回路から前記信号伝送路を介して前記他方の第1制御装置の電位変換回路に定電流が供給され、その定電流によって前記他方の第1制御装置の電位変換回路が動作して、前記一方の第1制御装置のロジック回路から出力された信号が前記他方の第1制御装置のロジック回路に電位変換されて伝送されることにより、前記第2制御装置から前記絶縁手段を介して受信した指令信号を、電気的に非絶縁状態で直列に伝送する、

ことを特徴とする蓄電装置。

30

## 【請求項12】

請求項9乃至11のいずれかに記載の蓄電装置において、

前記第1制御装置のそれぞれに対する指令信号は、最高電位バッテリモジュールに対応する前記第1制御装置から、最低電位バッテリモジュールに対応する前記第1制御装置に向かって順に伝送される、

ことを特徴とする蓄電装置。

40

## 【請求項13】

請求項12に記載の蓄電装置において

前記絶縁手段は、前記最高電位バッテリモジュールに対応する第1制御装置の信号入力回路に接続されており、

前記絶縁手段を介して伝送された指令信号は、前記最高電池バッテリモジュールに対応する第1制御装置の信号入力回路に入力される、

ことを特徴とする蓄電装置。

## 【請求項14】

請求項9に記載の蓄電装置において、

前記各集積回路は複数の端子を有し、

50

前記複数の端子は、前記対応するバッテリモジュールの複数のバッテリセルに対してそれぞれ対をなした端子と、他の端子とを含んでおり、

前記バッテリセルに対をなした端子と前記他の端子は交互に配置されている、ことを特徴とする蓄電装置。

【請求項 15】

請求項 10 又は 11 に記載の蓄電装置において、

前記複数の第 1 制御装置は、複数の端子を有する集積回路であり、

前記複数の端子は、前記対応するバッテリモジュールの複数のバッテリセルに対してそれぞれ対をなした端子と、他の端子とを含んでおり、

前記バッテリセルに対をなした端子と前記他の端子は交互に配置されている、ことを特徴とする蓄電装置。

10

【請求項 16】

請求項 14 に記載の蓄電装置において、

前記複数の第 1 制御装置は前記第 2 制御装置との間で信号を送受信しており、

前記信号伝送は、前記第 2 制御装置と前記最高電位の第 1 制御装置との間、及び前記第 2 制御装置と前記最低電位の第 1 制御装置との間で行われ、さらに、前記複数の第 1 制御装置の間の電気的な接続によって行われる、

ことを特徴とする蓄電装置。

【請求項 17】

請求項 9 乃至 11 のいずれかに記載の蓄電装置において、

20

前記絶縁手段は、最高電位バッテリモジュールに対応する第 1 制御装置と前記第 2 制御装置との間の信号伝送路に設けられている、

ことを特徴とする蓄電装置。

【請求項 18】

請求項 17 に記載の蓄電装置において、

前記絶縁手段は、最低電位バッテリモジュールに対応する第 1 制御装置と前記第 2 制御装置との間の信号伝送路に設けられている、

ことを特徴とする蓄電装置。

【請求項 19】

請求項 9 乃至 11 のいずれかに記載の蓄電装置において、

30

放電回路を有し、

前記放電回路は、スイッチと抵抗とを有すると共に、前記バッテリセルの少なくとも一つの正負極間に並列に接続されている、

ことを特徴とする蓄電装置。

【請求項 20】

請求項 19 に記載の蓄電装置において、

前記複数の第 1 制御装置は前記第 2 制御装置との間で信号を送受信し、

前記複数の第 1 制御装置は、前記対応するバッテリモジュールにおけるバッテリセルの電圧情報を前記第 2 制御装置に伝送して、前記第 2 制御装置から伝送された放電指令信号を受信し、前記放電指令信号に基づいて前記放電回路の前記スイッチを制御して、前記対応するバッテリモジュールにおけるバッテリセルの放電を制御する、

40

ことを特徴とする蓄電装置。

【請求項 21】

請求項 19 に記載の蓄電装置において、

前記複数の第 1 制御装置は前記第 2 制御装置との間で信号を送受信し、

前記複数の第 1 制御装置は、前記対応するバッテリモジュールにおけるバッテリセルの放電レベルを発生し、前記対応するバッテリモジュールのバッテリセルに設けられた前記放電回路のスイッチを制御して、前記対応するバッテリモジュールにおけるバッテリセルの放電を制御する、

ことを特徴とする蓄電装置。

50

**【請求項 2 2】**

請求項 8 乃至 11 のいずれかに記載の蓄電装置において、

前記絶縁手段はフォトカプラである、

ことを特徴とする蓄電装置。

**【請求項 2 3】**

請求項 8 乃至 11 のいずれかに記載の蓄電装置において、

前記バッテリセルはリチウム電池セルである、

ことを特徴とする蓄電装置。

**【請求項 2 4】**

請求項 8 乃至 11 のいずれかに記載の蓄電装置において、

前記指令信号又は電圧検出信号は第 1 及び第 2 信号線を介して前記第 1 制御装置と前記

第 2 制御装置との間で伝送されており、

前記第 1 信号線は前記絶縁手段と前記複数の第 1 制御装置との間を接続しており、

前記第 2 信号線は前記第 2 制御装置と前記絶縁手段との間を接続しており、

前記第 1 信号線における前記指令信号又は前記電圧検出信号のグランドレベルは、前記

第 2 信号線における前記指令信号又は前記電圧検出信号のグラントレベルとは異なる、

ことを特徴とする蓄電装置。

**【請求項 2 5】**

請求項 8 乃至 11 のいずれかに記載の蓄電装置において、

前記複数の第 1 制御装置に対する電力は第 1 電源によって供給されており、

前記第 2 制御装置に対する電力は第 2 電源によって供給されており、

前記第 2 電源は前記第 1 電源とは異なる、

ことを特徴とする蓄電装置。

**【請求項 2 6】**

請求項 2 5 に記載の蓄電装置において、

前記指令信号又は電圧検出信号は第 1 及び第 2 信号線を介して前記第 1 制御装置と前記

第 2 制御装置との間で伝送されており、

前記第 1 信号線は前記絶縁手段と前記複数の第 1 制御装置との間を接続しており、

前記第 2 信号線は前記第 2 制御装置と前記絶縁手段との間を接続しており、

前記第 1 信号線における前記指令信号又は前記電圧検出信号のグランドレベルは、前記

第 2 信号線における前記指令信号又は前記電圧検出信号のグラントレベルとは異なる、

ことを特徴とする蓄電装置。

**【請求項 2 7】**

請求項 8 乃至 11 のいずれかに記載の蓄電装置において、

前記絶縁手段は、異なる電流の流れを分ける、

ことを特徴とする蓄電装置。

**【請求項 2 8】**

正極及び負極を有する多数のリチウム単電池が直列に接続され、前記多数のリチウム単

電池が、直列に接続された複数のリチウム単電池で構成される複数のリチウム単電池グル

ープに分けられたリチウムバッテリと、

前記複数のリチウム単電池グループに対応して設けられ、電気的に直列に接続された複

数の集積回路と、を有し、

前記複数の集積回路は、それぞれ、

対応するリチウム単電池グループの電位が加えられる基準電位端子と、

信号入力端子と、

信号出力端子と、

前記対応するリチウム単電池グループに含まれる複数のリチウム単電池のそれぞれの端

子電圧を取り込むための電圧取込端子と、

前記電圧取込端子に供給された端子電圧を選択的に取り込むためのマルチプレクサと、

前記マルチプレクサにより取り込まれた端子電圧をデジタル変換するための A / D 変

10

20

30

40

50

換回路と、

前記信号入力端子を介して信号を受信する信号入回路と、

前記信号出力端子を介して信号を送信する信号出回路と、

ロジック回路、を有しており、

前記複数の集積回路の電気的な直列接続は、直列に接続される一方の集積回路の信号出力端子と他方の集積回路の信号入力端子とを信号伝送路によって電気的に非絶縁状態で接続することにより構成されると共に、直列に接続される一方の集積回路のロジック回路から他方の集積回路のロジック回路に出力される信号によって前記一方の集積回路の信号出回路が動作して、前記一方の集積回路の信号出回路から前記信号伝送路を介して前記他方の集積回路の信号入回路に電流が供給され、その電流によって前記他方の集積回路の信号入回路が動作して、前記一方の集積回路のロジック回路から出力された信号が前記他方の集積回路のロジック回路に伝送されることにより、絶縁手段を介してバッテリコントローラから受けた信号を電気的に非絶縁状態で直列に伝送する、

ことを特徴とする蓄電装置。

【請求項 29】

請求項 28 に記載の蓄電装置において、

前記複数の集積回路は、前記基準電位端子に加えられる電位の順にしたがって電気的に非絶縁状態で直列に接続されている、

ことを特徴とする蓄電装置。

【請求項 30】

請求項 28 又は 29 に記載の蓄電装置において、

前記基準電位端子に加えられる電位は、対応する前記リチウム単電池グループ内の最低電位である、

ことを特徴とする蓄電装置。

【請求項 31】

請求項 28 乃至 30 のいずれかに記載の蓄電装置において、

前記絶縁手段は、前記直列に接続された集積回路と前記バッテリコントローラとの間の電気的な接続を絶縁して、前記直列に接続された集積回路の電圧領域と前記バッテリコントローラの電圧領域とを切り離している、

ことを特徴とする蓄電装置。

【請求項 32】

請求項 31 に記載の蓄電装置において、

前記絶縁手段は、最高電位のリチウム単電池グループに対応する集積回路と前記バッテリコントローラとの間の信号伝送路に設けられ、両者間の電気的な接続を絶縁している、

ことを特徴とする蓄電装置。

【請求項 33】

請求項 32 に記載の蓄電装置において、

前記絶縁手段は、さらに、最低電位のリチウム単電池グループに対応する集積回路と前記バッテリコントローラとの間の信号伝送路に設けられ、両者間の電気的な接続を絶縁している、

ことを特徴とする蓄電装置。

【請求項 34】

請求項 28 乃至 33 のいずれかに記載の蓄電装置において、

前記信号出回路は、対応する集積回路に加わる電位を基準とした信号を前記信号出回路を介して出力し、

前記信号入回路は、前記信号出回路から出力され、対応する集積回路に加わる電位とは異なる電位を基準とする信号を前記信号入回路を介して受信し、この受信した信号を、対応する集積回路に加わる電位を基準とした信号に電位変換する、

ことを特徴とする蓄電装置。

【請求項 35】

10

20

30

40

50

請求項 2 8 乃至 3 4 のいずれかに記載の蓄電装置において、

前記複数の集積回路は、それぞれ、対応するリチウム単電池グループから供給された電圧を受けて、集積回路の内部回路を動作させるための一定電圧を出力する内部電源を有する、

ことを特徴とする蓄電装置。

【請求項 3 6】

請求項 2 8 乃至 3 5 のいずれかに記載の蓄電装置において、

前記複数の集積回路のそれぞれは、少なくとも第 1 端子グループに属する前記信号入出力端子と、第 2 端子グループに属する前記信号入出力端子とを有し、

前記複数の集積回路の電気的な直列接続は、前記端子グループ毎に、連続的に接続される前記集積回路の間での前記信号出力端子と前記信号入力端子との電気的非絶縁状態での接続によって構成されると共に、前記端子グループ毎に、前記絶縁を介して前記バッテリコントローラから信号を受ける、

ことを特徴とする蓄電装置。

【請求項 3 7】

電気的に直列に接続され、それぞれ、電気的に直列に接続された複数のリチウム単電池を有する複数の蓄電モジュールと、

前記複数の蓄電モジュールに対応して設けられ、それぞれ、対応する蓄電モジュールが有する複数のリチウム単電池のそれぞれの端子電圧を取り込むための複数の電圧入力端子、信号入力端子、信号出力端子、前記信号入力端子を介して信号を受信する信号入回路、前記信号出力端子を介して信号を送信する信号出回路、前記電圧入力端子から取り込まれたリチウム単電池の端子電圧を選択的に取り込むためのマルチプレクサ、前記マルチ

プレクサで選択された端子電圧をデジタル変換する A/D コンバータ、及びロジック回路を有する複数の集積回路と、

前記複数の集積回路の信号入出力端子を電気的に非絶縁状態で接続し、前記複数の集積回路を直列に接続する信号伝送路と、

前記複数の集積回路の電圧入力端子を、対応する蓄電モジュールが有する複数のリチウム単電池の端子に電気的に接続する接続回路と、を有し、

前記信号伝送路には、絶縁手段を介してバッテリコントローラが接続されており、

前記複数の集積回路に対する前記バッテリコントローラからの信号は、直列に接続される一方の集積回路のロジック回路から他方の集積回路のロジック回路に出力される信号によって前記一方の集積回路の信号出回路が動作して、前記一方の集積回路の信号出回路から前記信号伝送路を介して前記他方の集積回路の信号入回路に電流が供給され、その電流によって前記他方の集積回路の信号入回路が動作して、前記一方の集積回路のロジック回路から出力された信号が前記他方の集積回路のロジック回路に伝送されることにより、前記集積回路のそれぞれに伝送される、

ことを特徴とする蓄電装置。

【請求項 3 8】

請求項 3 7 に記載の蓄電装置において、

前記複数の集積回路は、対応する蓄電モジュールの電位の順にしたがって電気的非絶縁状態で直列に接続されている、

ことを特徴とする蓄電装置。

【請求項 3 9】

請求項 3 7 又は 3 8 に記載の蓄電装置において、

前記複数の集積回路に対する前記バッテリコントローラからの信号は、前記信号伝送路によって最高電位の前記蓄電モジュールに対応する前記集積回路から最低電位の前記蓄電モジュールに対応する集積回路に向かって順に伝送される、

ことを特徴とする蓄電装置。

【請求項 4 0】

請求項 3 7 乃至 3 9 のいずれかに記載の蓄電装置において、

10

20

30

40

50

前記絶縁手段は、前記直列に接続された集積回路と前記バッテリコントローラとの間の電気的な接続を絶縁して、前記直列に接続された集積回路の電圧領域と前記バッテリコントローラの電圧領域とを切り離している、

ことを特徴とする蓄電装置。

【請求項 4 1】

請求項 4 0 に記載の蓄電装置において、

前記絶縁手段は、最高電位の蓄電モジュールに対応する集積回路と前記バッテリコントローラとの間の信号伝送路に設けられ、両者間の電気的な接続を絶縁している、

ことを特徴とする蓄電装置。

【請求項 4 2】

10

請求項 4 1 に記載の蓄電装置において、

前記絶縁手段は、さらに、最低電位の蓄電モジュールに対応する集積回路と前記バッテリコントローラとの間の信号伝送路に設けられ、両者間の電気的な接続を絶縁している、

ことを特徴とする蓄電装置。

【請求項 4 3】

請求項 3 7 乃至 4 2 のいずれかに記載の蓄電装置において、

前記信号出力回路は、対応する集積回路に加わる電位を基準とした信号を前記信号出力端子を介して出力し、

前記信号入力回路は、前記信号出力回路から出力され、対応する集積回路に加わる電位とは異なる電位を基準とする信号を前記信号入力端子を介して受信し、この受信した信号を、対応する集積回路に加わる電位を基準とした信号に電位変換する、

ことを特徴とする蓄電装置。

20

【請求項 4 4】

請求項 3 7 乃至 4 3 のいずれかに記載の蓄電装置において、

前記複数の集積回路は、それぞれ、対応する蓄電モジュールから供給された電圧を受けて、集積回路の内部回路を動作させるための一定電圧を出力する内部電源を有する、

ことを特徴とする蓄電装置。

【請求項 4 5】

請求項 3 7 乃至 4 4 のいずれかに記載の蓄電装置において、

前記複数の集積回路のそれぞれは、少なくとも第 1 端子グループに属する前記信号入出力端子と、第 2 端子グループに属する前記信号入出力端子とを有し、

30

前記信号伝送路は、前記端子グループ毎に、前記信号出力端子と前記信号入力端子との電気的非絶縁状態での接続によって複数構成され、

前記複数の信号伝送路のそれぞれには、前記絶縁手段を介して前記バッテリコントローラが接続されている、

ことを特徴とする蓄電装置。

【発明の詳細な説明】

【0 0 0 1】

【発明の属する技術分野】

本発明は、高エネルギーの蓄電器を複数個直列に接続したものを制御する蓄電装置及びその制御方法に係り、特に、複数個の蓄電器を直列に接続した蓄電モジュールを制御する下位の制御装置と、複数の下位制御装置に指令を出す上位制御装置を用いたものに好適な蓄電装置及びその制御方法に関する。

40

【0 0 0 2】

【従来の技術】

従来の蓄電装置では、例えば、特開平 10 - 322925 号公報に記載されているように、直列に接続した複数の単電池を組電池として、複数の組電池を更に直列に接続すると共に、各組電池毎に下位の制御装置を備え、上位の制御装置から下位の制御装置に指令を送る構成としている。ここで、下位制御装置は、対応する組電池が備える単電池の状態を監視する。組電池数と同数設けられた下位制御装置は、組電池を介して電気的に直列に接続

50

されており、上位の制御装置と下位制御装置間の信号伝達及び下位制御装置同士の信号伝達には、フォトカプラ等の絶縁手段を用いて、制御装置間の電位差に影響されない構成としている。

【0003】

また、下位制御装置は、例えば、特開2000-92732号公報に記載されているように、単電池の容量調整を行うものである。容量調整とは、単電池にスイッチを介して抵抗を並列に接続し、電圧検出回路で計測した単電池の電圧が高い場合に上記スイッチを駆動して蓄えられた電気量の一部を放電し、単電池間の電圧差を小さくすることである。特に、開路電圧と残存容量の相関性が高い非晶質系炭素を負極活物質に用いたリチウムイオン電池では、単電池間の電圧差を小さくすることで各単電池の容量を均等化することが有効である。

10

【0004】

また、近年、二次電池と同等な電気量を蓄積でき、かつ二次電池に比べて寿命劣化の少ないウルトラキャパシタが用いられるようになっている。ウルトラキャパシタにおいても、例えば、特開2001-37077号公報に記載されているように、キャパシタセル間の電圧均等化法が採用されている。この方法は、キャパシタセルに並列にスイッチを接続し、キャパシタの電圧を検出して電流の一部をスイッチにバイパスさせる回路を設けるものであり、先の特開2000-92732号公報と類似している。

【0005】

下位制御装置は、単電池或いはキャパシタセルの電圧を検出し、電圧が高い場合に、前述のスイッチを駆動して容量調整している。一方、上位制御装置は、下位制御装置に容量調整を実施させるための指令信号を送る。特開2000-92732号公報に記載されているものでは、下位制御装置が起動時に組電池の各単電池の開放電圧を測定し、その値を上位制御装置に伝える。上位制御装置は全ての下位制御装置から得た開放電圧の値から容量調整時の電圧基準値を計算して、再び、下位制御装置に指令する。

20

【0006】

【発明が解決しようとする課題】

本発明が解決しようとする課題としては、以下の3つがある。第1は、コストの問題である。二次電池やウルトラキャパシタは電気自動車、或いはハイブリッド電気自動車用の蓄電装置として期待されているが、量産化に向けて低コスト化を達成することが求められている。蓄電装置の低コスト化には単電池或いはキャパシタセル自体の低コスト化と共に、複数個を備える下位制御装置複数の低コスト化が必要である。この方法としては、下位制御装置をI C (集積回路)化することが有効である。

30

【0007】

しかしながら、下位制御装置をI C化した場合においても、上位の制御装置と下位制御装置間の信号伝達及び下位制御装置同士の信号伝達に用いるフォトカプラ等の絶縁手段は残る。リチウムイオン電池の場合を例とすれば、この電位差は単電池の電圧を3.6Vと仮定し、全部で40ヶの電池を直列に接続した場合、最低電位の電池と最高電位の電池の電位差は144Vになる。この例で、仮に単電池4ヶづつを組電池とした場合、10ヶの下位制御装置を備えることになり、それぞれの下位制御装置が入出力用に2ヶ程度の絶縁手段を備えるとすれば、合計20ヶの絶縁手段が必要になり、制御装置のコストが高くなると言う問題があった。

40

【0008】

第2は、信頼性の問題である。蓄電装置の負荷として接続されるインバータ装置等が発生するノイズによって指令信号に外乱が入る可能性があり、こうした外乱に対して、上位制御装置から下位制御装置に指令を与える場合、信号伝達の信頼性が低下するという問題があった。

【0009】

第3は、電圧検出の精度の問題である。複数の下位制御装置は、それぞれ電圧検出回路を備え、対応する蓄電モジュールに具備された蓄電器の電圧を検出するが、電池の電圧検出

50

精度は許容される誤差が数十mVと高精度な性能が必要とされる。非晶質系炭素を負極活動物質に用いたリチウムイオン電池は、開放電圧と残存容量の相関性がニッケル水素電池等他の電池に比べて明確であるが、リチウムイオン電池の場合でも容量調整における電圧均等化の許容誤差は±50mV以下と言われている。尚、50mVの電圧はリチウムイオン電池の残存容量に換算すると約5%に相当する。リチウムイオン電池の最高電圧は約4.2Vであるが、上記50mVは4.2Vに対して1.2%にあたり、電圧検出の精度が厳しいことが分かる。

【0010】

高精度な電圧検出を達成するためには、十数ビットのA/Dコンバータを用いることが一般的であるが、A/Dコンバータの精度は基準電圧源の精度に依存するため、下位制御装置は誤差が極めて小さい（例えば±25mV程度）の高精度基準電圧源が必要になる。ここで、各下位制御装置はそれぞれ、電位の異なる組電池に接続されるため、高精度基準電圧源を複数の下位制御装置で共通化することは難しく、それぞれの下位制御装置が独立した高精度基準電圧源を備えていた。すなわち、電圧検出の高精度化を図るには、複数の下位制御装置がそれぞれ備える基準電圧源のコストが高くなると言う問題があった。

10

【0011】

本発明の第1の目的は、絶縁手段の個数を低減して、低コストな制御装置を備えた蓄電装置を提供することにある。

【0012】

本発明の第2の目的は、ノイズ等の外乱による影響を低減して、信頼性の向上した信号伝達が可能な蓄電装置の制御方法を提供することにある。

20

【0013】

本発明の第3の目的は、電圧検出の高精度化を図れるとともに、低コストな蓄電装置を提供することにある。

【0014】

本発明の主たる特徴は、電気的に直列に接続され、それぞれ、電気的に直列に接続された複数のバッテリセルを有する複数のバッテリモジュールと、前記複数のバッテリモジュールのそれぞれに対応して設けられて、対応するバッテリモジュールが有する複数のバッテリセルのそれぞれの状態を検出すると共に、第1信号伝送路によって電気的に非絶縁状態で直列に接続された複数の第1制御装置と、を有し、前記複数の第1制御装置のそれぞれは、前記第1信号伝送路に信号を出力するための信号出力回路、前記第1信号伝送路から信号を入力するための信号入力回路、及びロジック回路を備えており、前記複数の第1制御装置の直列接続は、電気的な接続が絶縁手段によって絶縁された第2信号伝送路を介して第2制御装置に接続されており、さらに、前記複数の第1制御装置の直列接続は、直列に接続される一方の第1制御装置のロジック回路から他方の第1制御装置のロジック回路に出力される信号によって前記一方の第1制御装置の信号出力回路が動作して、前記一方の第1制御装置の信号出力回路から前記第1信号伝送路を介して前記他方の第1制御装置の信号入力回路に電流が供給され、その電流によって前記他方の第1制御装置の信号入力回路が動作して、前記一方の第1制御装置のロジック回路から出力された信号が前記他方の第1制御装置のロジック回路に伝送されることにより、前記第2制御装置から前記第2信号伝送路を介して入力された指令信号を、電気的に非絶縁状態で直列に伝送するものである。

30

【0024】

【発明の実施の形態】

以下、図1～図10を用いて、本発明の一実施形態による蓄電装置及びその制御方法について説明する。

40

最初に、図1を用いて、本実施形態による蓄電装置の全体構成について説明する。

図1は、本発明の一実施形態による蓄電装置の全体構成を示す回路図である。

【0025】

二次電池の単電池VB1, VB2, …, VB12は、4ヶの単電池を直列に接続した形を

50

蓄電モジュールとしている。電気自動車或いはハイブリッド電気自動車に用いられる二次電池装置は十数ヶから二十数ヶの蓄電モジュールを備える場合があるが、本実施形態では数多くのモジュールを直列に接続する場合でも同様な構成であることから、図1に示した例では、3ヶの蓄電モジュールを直列に接続した構成を例として示している。

【0026】

図示する例では、最高電位にある第一の蓄電モジュールは、単電池VB1, ..., VB4から構成されている。各単電池VB1, ..., VB4の正極及び負極は、第一の下位制御装置IC-1が備える端子T1, T3, T5, T7, T9とそれぞれ接続される。また、単電池VB1の正極と負極間に、抵抗R1とスイッチ素子S1からなる容量調整回路を備えている。スイッチ素子S1のゲート端子には、下位制御装置IC-1の端子T2から制御信号が入力する。同様に、単電池VB2、単電池VB3、及び単電池VB4の正極と負極間に、それぞれ、抵抗R2とスイッチ素子S2、抵抗R3とスイッチ素子S3、及び抵抗R4とスイッチ素子S4の容量調整回路を備える。スイッチ素子S2, S3, S4のゲート端子はそれぞれ下位制御装置IC-1の端子T4, T6, T8から制御信号が入力する。

【0027】

中間電位にある第二の蓄電モジュールは、単電池VB5, ..., VB8を備えている。第一の蓄電モジュールと同様に、各単電池VB1, ..., VB4の正極及び負極は、第二の下位制御装置IC-2が備える端子T1, T3, T5, T7, T9とそれぞれ接続される。また、単電池VB5, ..., VB8も、それぞれ正極と負極間に、抵抗R5とスイッチ素子S5、抵抗R6とスイッチ素子S6、抵抗R7とスイッチ素子S7、及び抵抗R8とスイッチ素子S8を直列に接続した容量調整回路を備える。

【0028】

同様に、最低電位にある第三の蓄電モジュールは、単電池VB9, ..., VB12の単電池を備えている。各単電池VB9, ..., VB12の正極及び負極は、第三の下位制御装置IC-3が備える端子T1, T3, T5, T7, T9とそれぞれ接続される。単電池VB9, ..., VB12も、正極と負極間にそれぞれ抵抗R9とスイッチ素子S9、抵抗R10とスイッチ素子S10、抵抗R11とスイッチ素子S11、及び抵抗R12とスイッチ素子S12を直列に接続した容量調整回路を備えており、各スイッチ素子は第三の下位制御装置IC-3で駆動される。

【0029】

なお、各下位制御装置IC-1, IC-2, IC-3の内部構成、機能と周辺部品の構成については、図2以降を用いて後述する。

【0030】

次に、各下位制御装置IC-1, IC-2, IC-3の接続関係について説明する。

単電池VB4と単電池VB5が直列に接続されることから、第一の下位制御装置IC-1と第二の下位制御装置IC-2は直列に接続されており、同様に第二の下位制御装置IC-2は第三の下位制御装置IC-3と直列に接続される。

【0031】

次に、上位制御装置MPUは、第一の下位制御装置IC-1から第三の下位制御装置IC-3に指令を与える。上位制御装置MPUが出力する制御指令は、フォトカプラF1, F2, F3で絶縁され、第一の下位制御装置IC-1の入力端子In-1, In-2, In-3に伝達される。フォトカプラF1, F2, F3の受光側トランジスタは、それぞれ、抵抗RF1, RF2, RF3に接続されている。抵抗RF1, RF2, RF3は、いずれも単電池VB1の正極から電源を供給される。第一の下位制御装置IC-1は、入力端子In-1, In-2, In-3に伝達された信号を、出力端子Out-1, Out-2, Out-3から出力するが、出力端子Out-1, Out-2, 及び出力端子Out-3は、第二の下位制御装置IC-2が備える入力端子In-1, In-2, In-3と、それぞれ、電気的に非絶縁で接続される。

【0032】

10

20

30

40

50

同様に、第二の下位制御装置 I C - 2 は、入力端子 I n - 1 , I n - 2 , I n - 3 に伝達された信号を出力端子 O u t - 1 , O u t - 2 , O u t - 3 から出力する。第二の下位制御装置 I C - 2 の出力端子 O u t - 1 , … , O u t - 3 は、第三の下位制御装置 I C - 3 が備える入力端子 I n - 1 , I n - 2 , I n - 3 とそれぞれ、電気的に非絶縁で接続される。

#### 【 0 0 3 3 】

最低電位の下位制御装置 I C - 3 は、出力端子 O u t - 1 , O u t - 2 , O u t - 3 から出力する信号で対応するトランジスタ T r 1 , T r 2 , T R 3 を駆動し、それぞれのトランジスタ第二の下位制御装置が接続されたフォトカプラ F 4 , F 5 , F 6 を介して、信号を上位制御装置 M P U に伝達させる。ここで、フォトカプラ F 4 , F 5 , F 6 の発光側は、いずれも下位制御装置 I C - 3 の基準電圧出力端子 V D D に接続し、基準電圧出力端子 V D D から電流の供給を得る。フォトカプラ F 4 , F 5 , F 6 の発光側とトランジスタ T r 1 , T r 2 , T R 3 の間に設けた抵抗 R F 4 , R F 5 , R F 6 は、それぞれ、フォトカプラ F 4 , F 5 , F 6 の発光側に流れる電流を調整するために使用する。

10

#### 【 0 0 3 4 】

下位制御装置 I C - 1 の内部回路は、単電池 V B 4 の負極を基準電位とし、この基準電位を G N D - 1 で表す。また、下位制御装置 I C - 2 と下位制御装置 I C - 3 の内部回路は、それぞれ、単電池 V B 8 , 単電池 V B 1 2 の負極を基準電位とし、この基準電位を G N D - 2 , G N D - 3 で表す。各基準電位 G N D - 1 , … , G N D - 3 は、いずれも対応する下位制御装置 I C - 1 , … , I C - 3 で使用する個別なグランド端子である。一方、図 1 の全体の構成におけるグランドは、上位制御装置 M P U に対する電源 V c c の負極とする。上位制御装置 M P U と下位制御装置 I C - 1 , … , I C - 3 は、フォトカプラ F 1 , … , F 6 で絶縁されていることから、V c c の負極と各基準電位 G N D - 1 , … , G N D - 3 の間も絶縁されている。

20

#### 【 0 0 3 5 】

下位制御装置 I C - 1 , … , I C - 3 に備える各端子と周辺部品に関しては図 2 で説明するが、各制御装置 I C - 1 , … , I C - 3 での違いは、各自に設けた端子 A 1 , … , A 3 , 及び端子 B 1 , B 2 の電位である。これらの端子は、図 7 で述べる電圧検出の誤差を補正するための端子であり、下位制御装置 I C - 1 から下位制御装置 I C - 3 が個別に持つ電圧検出誤差に応じて、端子 A 1 , … , A 3 , 及び端子 B 1 , B 2 に、「1」又は「0」のデジタル値を与える。ここで、「1」は下位制御装置の基準電圧 V D D 、「0」は下位制御装置毎の個別グランド G N D - 1 , … , G N D - 3 の電位である。上記電圧検出誤差は、下位制御装置 I C - 1 から下位制御装置 I C - 3 で異なるため、図 1 の例においても、各下位制御装置 I C - 1 , … , I C - 3 で、端子 A 1 , … , A 3 , 及び端子 B 1 , B 2 の「1」又は「0」の値は異なることを記載している。

30

#### 【 0 0 3 6 】

上位制御装置 M P U は、蓄電モジュールに流れる充電及び放電の電流を絶縁型の電流検出器 C T で検出する。また、直列に接続された蓄電モジュールの電圧合計値を抵抗 R V 1 , R V 2 で分圧して検出する。ここで、上位制御装置 M P U と各蓄電モジュールは絶縁されることから、抵抗 R V 1 , R V 2 で分圧した電圧は一旦、電圧 - 周波数変換器 V F によりパルス信号に変換され、V F の出力をフォトカプラ F 7 を介して上位制御装置 M P U に伝達する。上位制御装置 M P U は、フォトカプラ F 7 より得た電圧 - 周波数変換器 V F の出力から蓄電モジュールの総電圧を読み取り、この値と電流検出器 C T から得た電流を元に 3ヶの蓄電モジュールに対する平均的な残存容量を演算する。

40

#### 【 0 0 3 7 】

電気自動車或いはハイブリッド電気自動車において十数ヶから二十数ヶの蓄電モジュールを備える場合、最上位の下位制御装置 I C - 1 と最下位の下位制御装置 I C - 3 が上位制御装置 M P U とフォトカプラを介して接続する構成は図 1 と同じである。蓄電モジュールと同数設けられる下位制御装置の残り十数ヶから二十数ヶは、図 1 の下位制御装置 I C - 2 と同様に入力端子 I n - 1 , I n - 2 , I n - 3 が 1 つ高電位の蓄電モジュール用に設

50

けられた下位制御装置の出力端子と、またと出力端 Out - 1, Out - 2, Out - 3 がそれぞれ、1つ低電位の蓄電モジュール用に設けられた下位制御装置の入力端子とそれぞれ、非絶縁で接続される。

【0038】

図示する例では、絶縁手段としては、7個のフォトカプラ F1, …, F6, F7 を用いている。図示の例では、3個の下位制御装置 IC - 1, …, IC - 3 から構成される場合を示しているが、下位制御装置が例えば、10個になった場合でも、絶縁手段であるフォトカプラの個数は、7個でよいものである。一方、従来の構成では、単電池4ヶづつを組電池とし、10ヶの下位制御装置を備えた場合、それぞれの下位制御装置が入出力用に2ヶ程度の絶縁手段を備えるため、合計20個の絶縁手段が必要になる。それに対して、本実施形態では、常に7個で良いため、絶縁手段の個数を低減して、制御装置のコストを低減することができる。

【0039】

次に、図2を用いて、本実施形態による蓄電装置に用いる下位制御装置内部の構成について説明する。

図2は、本発明の一実施形態による蓄電装置に用いる下位制御装置内部の構成を示す回路図である。なお、図2においては、下位制御装置 IC - 1 の構成について示しているが、他の下位制御装置 IC - 2, IC - 3 も同様である。また、図1と同一符号は、同一部分を示している。

【0040】

スイッチ素子の駆動手段 Dr 1, Dr 2, Dr 3, Dr 4 は、それぞれ、容量調整用のスイッチ素子 S1, S2, S3, S4 の制御端子に接続されており、それぞれのスイッチ素子 S1, S2, S3, S4 を駆動する。駆動手段 Dr 1, Dr 2, Dr 3, Dr 4 は、それぞれ、下位制御装置 IC - 1 内部のロジック回路3から信号を得て、スイッチ素子 S1, …, S4 を個別に駆動する。

【0041】

アナログスイッチ AS1, AS2, AS3, AS4 は、一端が単電池の正極にそれぞれ接続され、他端がキャパシタ C1 の + 端子 C1P に共通接続されている。同様に、アナログスイッチ BS1, BS2, BS3, BS4 も、一端が単電池の負極にそれぞれ接続され、他端がキャパシタ C1 の - 端子 C1N に共通接続されている。また、キャパシタ C1 の + 端子 C1P には、アナログスイッチ CS1 を接続し、アナログスイッチ CS1 の他端は、第二のキャパシタ C2 の + 端子 C2P に接続される。更に、キャパシタ C2 の - 端子 C1N には、アナログスイッチ CS2 を接続し、アナログスイッチ CS2 の他端は第二のキャパシタ C2 の - 端子 C2N に接続する。

【0042】

アナログスイッチ AS1 とアナログスイッチ BS1, AS2 と BS2, AS3 と BS3, AS4 と BS4 はそれぞれペアであり、同時にオン、オフする。また、(a) アナログスイッチ AS1, アナログスイッチ BS1 と、(b) アナログスイッチ AS2, アナログスイッチ BS2 と、(c) アナログスイッチ AS3, アナログスイッチ BS3 と、(d) アナログスイッチ AS4, アナログスイッチ BS4 の各ペアは、4つのマルチブレクサ用スイッチとして働く。即ち、(a), …, (d) のマルチブレクサ用スイッチで単電池 VB1, …, VB4 のいずれか1つを選択し、選択した単電池と第一のキャパシタ CS1 を接続する。一方、アナログスイッチ CS1 とアナログスイッチ CS2 も同時にオン、オフし、これらがオンすると第一のキャパシタ CS1 と第二のキャパシタ CS2 を接続する。

【0043】

アナログスイッチ CS1 とアナログスイッチ CS2 がオンする動作モードを (e) とすると、例えば、単電池 VB1 の電圧を計測する場合、ロジック回路3は、(a) アナログスイッチ AS1, アナログスイッチ BS1 のペアをオンさせる第一のモードと (e) アナログスイッチ CS1 とアナログスイッチ CS2 をオンさせる第二のモードを交互に繰り返す。この間、(b), …, (d) のマルチブレクサ用スイッチはオフを維持させる。この第

10

20

30

40

50

一のモード( a )と、第二のモード( e )を数百回、パルス的に繰り返すことにより、単電池 V B 1 とアナログスイッチ C S 1 、及びアナログスイッチ C S 2 は最終的に同じ電圧になる。これは( a )と( e )を1回実施することにより、単電池 V B 1 とアナログスイッチ C S 1 、及びアナログスイッチ C S 1 とアナログスイッチ C S 2 の電位差に応じた電流が流れ、それぞれの電位差を軽減するためである。

【 0 0 4 4 】

また、( b )アナログスイッチ A S 2 、アナログスイッチ B S 2 のペアをオンさせる第一のモードと( e )アナログスイッチ C S 1 とアナログスイッチ C S 2 をオンさせる第二のモードを交互に繰り返し、この間、( a )、( c )、( d )のマルチブレクサ用スイッチはオフを維持させ、第一のモード( b )と、第二のモード( e )を数百回、パルス的に繰り返すことにより、単電池 V B 2 とアナログスイッチ C S 1 、及びアナログスイッチ C S 2 は最終的に同じ電圧になる。

10

【 0 0 4 5 】

同様にして、( c )アナログスイッチ A S 3 、アナログスイッチ B S 3 のペアをオンさせる第一のモードと( e )アナログスイッチ C S 1 とアナログスイッチ C S 2 をオンさせる第二のモードを交互に繰り返して、単電池 V B 3 とアナログスイッチ C S 1 、及びアナログスイッチ C S 2 は最終的に同じ電圧にできる。

【 0 0 4 6 】

また、( d )アナログスイッチ A S 4 、アナログスイッチ B S 4 のペアをオンさせる第一のモードと( e )アナログスイッチ C S 1 とアナログスイッチ C S 2 をオンさせる第二のモードを交互に繰り返して、単電池 V B 4 とアナログスイッチ C S 1 、及びアナログスイッチ C S 2 は最終的に同じ電圧にできる。

20

【 0 0 4 7 】

図中、破線で示した電圧検出回路 1 は、上述したマルチブレクサ用スイッチ、アナログスイッチ、第一と第二のキャパシタを含む構成を有している。電圧検出回路 1 の出力は、アナログスイッチ C S 2 の正極電圧( C 2 P )である。正極電圧 C 2 P は、比較器 C M P 1 、 C M P 2 、 C M P 3 を用いて、それぞれ過充電電圧、過放電電圧、容量調整レベル等に対応する基準電圧と比較する。基準電圧は、基準電源回路 2 から供給される。また、電圧検出回路 1 の出力( C 2 P )は、検出セル電圧 V x として、 A / D コンバータ 7 の入力へ伝えられ、 A / D コンバータ 7 で正極電圧( C 2 P )のアナログ値をデジタル値に変える。 A / D コンバータ 7 は、上述した端子 A 1 , … , A 3 , 及び端子 B 1 , B 2 に与えられる信号によって、電圧検出誤差を補正することができる。

30

【 0 0 4 8 】

基準電源回路 2 は、単電池 V B 1 - V B 4 の総電圧から一定電圧( 例えば 5 V )を作ると共に、下位制御装置 I C - 1 の外部に設けた基準電圧用素子 V R に電流を供給し、先の一定電圧より高精度な電圧を発生させ、この電圧を端子 V r e f - 1 から下位制御装置 I C - 1 に取り込む。端子 V r e f - 1 から入力された電圧は数種類に分圧され、比較器 C M P 1 、 C M P 2 、 C M P 3 に応じた基準電圧として使用する。また、クロック発生器 5 は、下位制御装置 I C - 1 の外部に設けた振動子 C Z を用いてクロックを作り、ロジック回路 3 等で用いる。なお、入力回路 4 と出力回路 6 の詳細構成については、図 3 , 図 4 を用いて後述する。

40

【 0 0 4 9 】

次に、図 3 を用いて、本実施形態による蓄電装置の中の下位制御装置に用いる出力回路 6 及び入力回路 4 の第 1 の構成について説明する。

図 3 は、本発明の一実施形態による蓄電装置の中の下位制御装置に用いる出力回路 6 及び入力回路 4 の第 1 の構成を示す回路図である。なお、図 3 では、下位制御装置 I C - 1 の出力回路 6 と、下位制御装置 I C - 2 の入力回路 4 の詳細について示している。また、図 1 , 図 2 と同一符号は、同一部分を示している。

【 0 0 5 0 】

電源回路 2 のトランジスタ Q は、電源制御回路 8 によって、ベース電流を制御され、端子

50

VDDに一定電圧を出力しており、この一定電圧を出力回路6に供給する。

【0051】

出力回路6は、端子VDDと下位制御装置IC-1のグランドGND-1間に設けられ、P-MOSFET(MP1)と、N-MOSFET(MN1)からなる相補型スイッチを備えている。P-MOSFET(MP1)と、N-MOSFET(MN1)の間には、抵抗R14が接続されている。また、P-MOSFET(MP1)には、並列に、抵抗R13が接続されている。相補型スイッチの出力は、P-MOSFET(MP3)のゲート端子に印加する。

【0052】

ここで、ロジック回路3から出力された信号で、P-MOSFET(MP1)がオンすると、P-MOSFET(MP3)のゲート-ソース間をショートして、P-MOSFET(MP3)をオフさせる。また、N-MOSFET(MN1)がオンすると、端子VDDの電圧を、抵抗R13と抵抗R14で分圧した電圧が発生し、抵抗R13の両端の電圧が、P-MOSFET(MP3)のゲート-ソース間に印加される。抵抗R13の両端の電圧は、P-MOSFET(MP3)のゲートしきい値電圧より大きく、P-MOSFET(MP3)をオンさせるが、P-MOSFET(MP3)の出力電流を抑制するために、ゲートしきい値電圧よりわずかに大きい値に設定する(しきい値電圧より1V或いは2V程度高くする)。

【0053】

この結果、P-MOSFET(MP3)は定電流スイッチとして働き、出力の定電流を下位制御装置IC-2の入力回路4に流し込む。P-MOSFET(MP3)の出力端子と、端子VDDの間には、ダイオードD1と抵抗RE1を直列にした静電破壊防止回路を備え、出力端子Out-1に外部からサージ電圧が入ると、このサージ電圧を抵抗RE1、ダイオードD1を介し、端子VDD及び端子VDDに接続されたキャパシタCV1にバイパスして、P-MOSFET(MP3)のゲートソース間がサージ電圧で静電破壊することを防止できる。また、P-MOSFET(MP3)の出力端子とGND-1にも、抵抗RE2と、ダイオードD2を静電破壊対策として備えるが、さらに、これらに加えて、ツエナーダイオードZD1を直列に接続している。

【0054】

図示するように、2ヶの下位制御装置IC-1, IC-2の入出力端子を非絶縁で接続すると、P-MOSFET(MP3)がオフの期間中に、出力端子Out-1から入力端子In-1を通り、更に下位制御装置IC-2に接続された単電池を通ってGND-1へ戻る電流経路が作られ、単電池の放電を招くことになる。これを放置すると、単電池は過放電状態になるため、上記電流経路に単電池電圧より高い降伏電圧を有するツエナーダイオードZD1を放電電流遮断用として設けている。

【0055】

次に、入力回路4の構成について説明する。下位制御装置IC-2の入力端子In-1は、抵抗RE4と抵抗RE6の直列接続を介して、単電池VB5の負極に接続している。したがって、入力端子In-1の基準電位は、GND-2より高い単電池VB5の負極電位になっている。入力端子In-1には、抵抗RE3を介して、N-MOSFET(MN2)のゲート端子を接続し、N-MOSFET(MN2)のソース端子も、抵抗RE6を介して、単電池VB5の負極に接続する。N-MOSFET(MN2)のゲート端子と単電池VB5の正極の間には、ダイオードD3を、同様に、N-MOSFET(MN2)のゲート端子とソース端子の間には、ダイオードD4をそれぞれ静電破壊防止用に備える。これらの構成から、N-MOSFET(MN2)も基準電位がGND-2より高い単電池VB5の負極電位になっている。

【0056】

N-MOSFET(MN2)のドレイン端子と単電池VB5の正極間には、抵抗RE5を備え、抵抗RE5両端の電圧をP-MOSFET(MP4)のゲートソース間に印加する。P-MOSFET(MP4)のドレイン端子は、抵抗RE7, RE8の直列接続を介して、G

10

20

30

40

50

N D - 2 に接続する。また、抵抗 R E 8 には、並列にツエナーダイオード Z D 2 を設け、抵抗 R E 8 の両端の電圧をロジック回路 3 に伝える。

【 0 0 5 7 】

以上の構成を持つ入力回路 4 は、多段階で電位変換を行う回路が特徴である。即ち、下位制御装置 I C - 1 の P - M O S F E T ( M P 3 ) が output した定電流を、単電池 V B 5 の負極を電位基準とする N - M O S F E T ( M N 2 ) で一旦受け、N - M O S F E T ( M N 2 ) がオンすると、抵抗 R E 5 に生じた電圧で P - M O S F E T ( M P 4 ) をオンさせ、P - M O S F E T ( M P 4 ) を流れる電流で、抵抗 R E 8 両端に信号電圧を作り、ロジックに伝える。

【 0 0 5 8 】

一般的な回路、特に集積回路はグランドを基準電位とする入力端子、及び出力端子を有する。これに対して、本実施形態の下位制御装置は、出力が定電流、入力は回路のグランドより高い基準電位に接続され、出力回路で多段階に電位変換する。こうした構成は制御装置間を非絶縁で接続するために必要である。先に、ツエナーダイオード Z D 1 による単電池の放電防止について説明したが、もし、入力端子 I n - 1 の電位基準をグランド G N D - 2 に選ぶと、単電池 V B 5 , … , V B 8 の単電池が、P - M O S F E T ( M P 3 ) がオフの期間中に、下位制御装置 I C - 1 の出力端子 O u t - 1 から下位制御装置 I C - 2 の入力端子 I n - 1 を通り、放電する経路を作る。放電電流を遮断するためには、ツエナーダイオードの降伏電圧を高くせねばならない。また、P - M O S F E T ( M P 3 ) のソースドレイン間電圧として単電池 V B 5 , … , V B 8 の電圧合計が印加されるため、P - M O S F E T ( M P 3 ) は常時電圧ストレスがかかることになる。こうした点を考慮すれば、入力端子 I n - 1 の基準電位を高く選び、ツエナーダイオード Z D 1 の降伏電圧を低くし、合わせて P - M O S F E T ( M P 3 ) の電圧ストレスを軽減することが望ましいものである。

【 0 0 5 9 】

以上説明したように、放電電流経路は、下位制御装置の出力端子と低電位側の蓄電モジュール内の蓄電池との間に、形成される。具体的には、下位制御装置 I C - 1 の出力端子 O u t - 1 と、この下位制御装置 I C - 1 よりも低電位側の蓄電池モジュール（蓄電池 V B 5 , V B 6 , V B 7 , V B 8 で構成される）の中の蓄電池 V B 6 との間には、下位制御装置 I C - 1 の出力端子 O u t - 1 , 下位制御装置 I C - 2 の入力端子 I n - 1 , 抵抗 R E 3 , ダイオード D 4 , 蓄電池 V B 6 の正極 , 蓄電池 V B 5 の負極 , 蓄電池 V B 5 の正極 , 下位制御装置 I C - 1 のグランド G N D - 1 , ツエナーダイオード Z D 1 , ダイオード D 2 , 抵抗 R E 2 , 下位制御装置 I C - 1 の出力端子 O u t - 1 と接続される放電電流経路が形成される。そこで、本実施形態では、この放電電流経路に、ツエナーダイオード Z D 1 , ダイオード D 2 , D 4 等の蓄電池の放電を阻止する遮断素子を設けている。

【 0 0 6 0 】

次に、図 4 を用いて、本実施形態による蓄電装置の中の下位制御装置に用いる出力回路 6 及び入力回路 4 の第 2 の構成例について説明する。

図 4 は、本発明の一実施形態による蓄電装置の中の下位制御装置に用いる出力回路 6 及び入力回路 4 の第 2 の構成例を示す回路図である。なお、図 3 では、下位制御装置 I C - 1 の出力回路 6 と、下位制御装置 I C - 2 の入力回路 4 の詳細について示している。また、図 1 , 図 2 , 図 3 と同一符号は、同一部分を示している。

【 0 0 6 1 】

下位制御装置 I C - 1 の出力回路 6 は、図 3 に示した出力回路 6 と同じ構成を有している。

【 0 0 6 2 】

下位制御装置 I C - 2 の入力回路 4 は、図 3 に示した入力回路とは、次の点で異なっている。すなわち、入力端子 I n - 1 に、P - M O S F E T ( M P 5 ) のソース端子を接続し、P - M O S F E T ( M P 5 ) のゲート端子は単電池 V B 5 の正極に接続することで、入力端子 I n - 1 の基準電位を、下位制御装置 I C - 1 のグランド G N D - 1 と電位が等しい単電池 V B 5 の正極電圧に選んでいる。

【 0 0 6 3 】

10

20

30

40

50

P - M O S F E T ( M P 5 ) には、ソースゲート間に、ツエナーダイオード Z D 3 と抵抗 R E 9 を並列に備え、P - M O S F E T ( M P 3 ) が output する定電流で、P - M O S F E T ( M P 5 ) にゲート電圧を印加し、P - M O S F E T ( M P 5 ) をオンさせる。P - M O S F E T ( M P 5 ) のドレイン端子は、抵抗 R 4 とツエナーダイオード Z D 4 を経て、単電池 V B 6 の負極に接続する。抵抗 R E 4 の両端電圧は、N - M O S F E T ( M N 2 ) のゲートソース間電圧として印加される。N - M O S F E T ( M N 2 ) のソース端子も、ツエナーダイオード Z D 4 を介して、単電池 V B 6 の負極に接続する。N - M O S F E T ( M N 2 ) のドレイン端子と単電池 V B 5 の正極間に抵抗 R E 5 を備え、抵抗 R E 5 の両端の電圧を P - M O S F E T ( M P 4 ) のゲートソース間に印加する。P - M O S F E T ( M P 4 ) のドレイン端子は、抵抗 R E 7 , R E 8 の直列接続を介して、グランド G N D - 2 に接続する。抵抗 R E 8 には、並列にツエナーダイオード Z D 2 を設け、抵抗 R E 8 の両端の電圧をロジック回路 3 に伝える。

#### 【 0 0 6 4 】

この構成によれば、下位制御装置 I C - 1 の出力端子 O u t - 1 から下位制御装置 I C - 2 の入力端子 I n - 1 を通り、ツエナーダイオード Z D 3 からグランド G N D - 1 へ戻る経路には単電池が存在せず、電池の放電電流を心配する必要は無いものである。また、下位制御装置 I C - 2 の入力端子 I n - 1 から P - M O S F E T ( M P 5 ) をドレインソース間、ツエナーダイオード Z D 4 をそれぞれ経て単電池 V B 6 の負極に至り、単電池 V B 6 と単電池 V B 5 からグランド G N D - 1 へ戻る経路が作られるが、P - M O S F E T ( M P 3 ) のオフ時には、P - M O S F E T ( M P 5 ) もまたオフであり、この経路で単電池 V B 5 , V B 6 が放電することは無いものである。放電電流を遮断する第一の素子は、P - M O S F E T ( M P 5 ) であり、ツエナーダイオード Z D 4 は、P - M O S F E T ( M P 5 ) が不良等で放電電流を流す状態になっても、これを遮断するために冗長的に用いている。

#### 【 0 0 6 5 】

以上のように、図 3 若しくは図 4 に示した構成とすることにより、下位制御装置の入出力端子間を非絶縁で接続しても、単電池の放電電流を遮断することができ、これにより非絶縁接続が可能になる。尚、図 3 及び図 4 の例では、下位制御装置 I C - 1 の出回路と下位制御装置 I C - 2 の入回路をそれぞれ 1 チャンネルずつ示したが、これらは図 1 に記載したように 1 つの下位制御装置に同じ構成が複数、備えられている。

#### 【 0 0 6 6 】

次に、図 5 を用いて、本実施形態による蓄電装置の制御方法について説明する。ここでは、図 1 ~ 図 4 に示した例において、上位制御装置 M P U からの指令で下位制御装置 I C - 1 , ... , I C 3 を動作させる場合の制御内容について説明する。

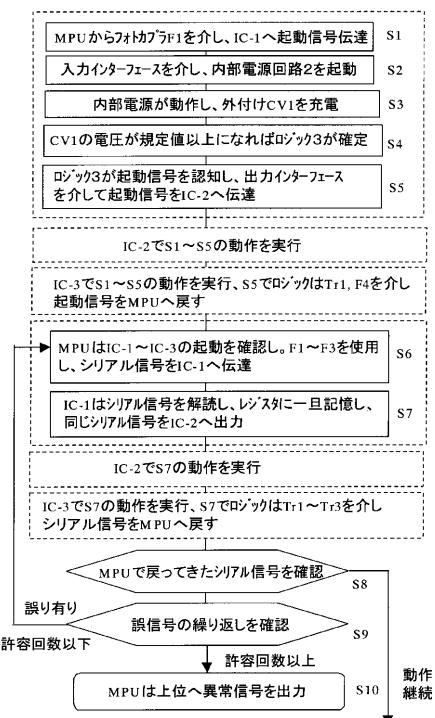

図 5 は、本発明の一実施形態による蓄電装置の制御内容を示すフローチャートである。

#### 【 0 0 6 7 】

ここでは、スリープ状態にあった下位制御装置 I C - 1 , ... , I C - 3 が上位制御装置 M P U からの信号で起動し、その後の正常な動作を実施する際のフローについて説明する。

#### 【 0 0 6 8 】

ステップ s 1 において、上位制御装置 M P U は、フォトカプラ F 1 を介して、下位制御装置 I C - 1 の入力端子 I n - 1 に起動信号を伝達する。

#### 【 0 0 6 9 】

次に、ステップ s 2 において、下位制御装置 I C - 1 の入回路 4 は、入力端子 I n - 1 に伝達された信号の電位を変換し、この信号を内部電源回路 2 に伝達する。

#### 【 0 0 7 0 】

次に、ステップ s 3 において、内部電源回路 2 が起動し、トランジスタ Q を制御する。但し、下位制御装置 I C - 1 に外付けしたキャパシタ C V 1 が、トランジスタ Q の出力電流で充電され、一定な電圧 V D D に達するまでの間、時間を要する。

#### 【 0 0 7 1 】

次に、ステップ s 4 において、キャパシタ C V 1 の電圧が、電圧 V D D よりわずかに小さい規定値以上になれば、ロジック 3 を始め、図 2 に示した各回路の動作が確立する。その

10

20

30

40

50

後、C V 1 の電圧は一定値 V D D に制御される。

【 0 0 7 2 】

次に、ステップ s 5 において、ロジック 3 は、上位制御装置 M P U から伝達された起動信号を認知し、これを出力回路 6 を介して 1 つ低電位の下位制御装置 I C - 2 に伝達する。

【 0 0 7 3 】

同様にして、以下、ステップ s 1 , … , ステップ s 5 と同様なフローで、下位制御装置 I C - 2 と下位制御装置 I C - 3 が起動する。さらに、下位制御装置 I C - 3 は、フォトカプラ F 4 を介して上位制御装置 M P U へ起動信号を戻す。

【 0 0 7 4 】

次に、ステップ s 6 において、上位制御装置 M P U は、全ての下位制御装置 I C - 1 , I C - 2 , I C - 3 がスリープ状態から起動したことを認知し、次の指令に移る。即ち、上位制御装置 M P U は、フォトカプラ F 1 , … , F 3 を用いて、シリアル形式の制御指令を、下位制御装置 I C - 1 , … , I C - 3 へ送る。 10

【 0 0 7 5 】

次に、ステップ s 7 において、下位制御装置 I C - 1 は、入力端子 I n - 1 , … , I n - 3 より得たシリアル信号を入力回路 4 で電位変換し、これをロジック 3 で解読する。そして、この信号をレジスタに一旦記憶し、同じシリアル信号を次の下位制御装置 I C - 2 へ送る。

【 0 0 7 6 】

引き続き、下位制御装置 I C - 2 , I C - 3 もステップ s 7 と同様な動作を実施する。そして、下位制御装置 I C - 3 は、フォトカプラ F 4 , … , F 6 を用いてシリアル信号を上位制御装置 M P U へ戻す。 20

【 0 0 7 7 】

ステップ s 8 において、上位制御装置 M P U は、戻ってきたシリアル信号を確認し、正常な場合は次の制御指令を送る。一方、上位制御装置 M P U に戻ったシリアル信号に誤りがある場合は、ステップ s 9 において、信号伝達に関する誤り回数を積算し、回数が許容回数以下の場合は、やり直しのために同じ指令信号を下位制御装置 I C - 1 へ送る。一方、誤り回数が許容回数以上に達した場合は、異常と判断して、ステップ s 10 において、上位制御装置 M P U は上位のシステムへ異常信号を出力する。 30

【 0 0 7 8 】

この制御フローでは、下位制御装置 I C - 1 から I C - 3 まで指令が届くまでに時間遅延がある。しかしながら、電池の電圧変化はマイコン等制御回路の動作に比べてゆっくりしており、下位制御装置 I C - 1 から I C - 3 で実施する単電池の状態監視は約数十 m s 毎に実施する程度で良い。このため、下位制御装置 I C - 1 から I C - 3 までの信号伝達で生じる時間遅延も状態監視の周期に比べて小さければ問題は無いものである。一方、上位制御装置 M P U は下位制御装置 I C - 1 へ発した指令と下位制御装置 I C - 3 から戻った指令を比べることで、いずれかの 1 つの下位制御装置が誤った場合もこれを発見できる。特に、非絶縁で信号を送る場合には、二次電池装置に接続されたインバータ等が発生するノイズの影響が心配されるが、上述した制御方法によれば、上位制御装置 M P U は 1 つづつの指令が全ての下位制御装置で正確に認識されたことを確認でき、装置の信頼性を向上することができる。 40

【 0 0 7 9 】

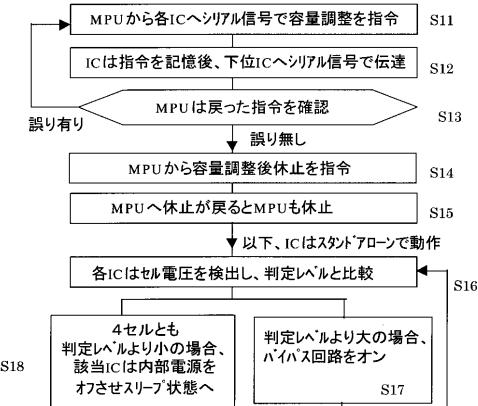

次に、図 6 を用いて、本実施形態による蓄電装置における容量調整時の制御方法について説明する。

図 6 は、本発明の一実施形態による蓄電装置における容量調整時の制御内容を示すフローチャートである。

【 0 0 8 0 】

ステップ s 11 において、上位制御装置 M P U は、各下位制御装置 I C - 1 , I C - 2 , I C - 3 に容量調整を指令する。

【 0 0 8 1 】

次に、ステップ s 1 2 において、各下位制御装置 I C - 1 , I C - 2 , I C - 3 は、指令をレジスタに格納（記憶）し、1つ低電位の下位制御装置へ同じ指令を送る。この方法は、図 5 に示したものと同様である。

【 0 0 8 2 】

次に、ステップ s 1 3 において、上位制御装置 M P U は、下位制御装置 I C - 3 から戻った指令を確認し、正常ならばステップ s 1 4 に移り、誤りがある場合はステップ s 1 1 に戻り再度、同じ指令を与える。

【 0 0 8 3 】

正常な場合には、ステップ s 1 4 において、上位制御装置 M P U は、下位制御装置 I C - 1 , ... , I C - 3 に容量調整後、休止する指令を送る。

10

【 0 0 8 4 】

次に、ステップ s 1 5 において、上位制御装置 M P U は、この指令の戻りを確認すると、上位制御装置 M P U 自身も休止状態に入る。以後は上位制御装置 M P U から指令が来ることはなく、下位制御装置 I C - 1 , ... , I C - 3 はそれぞれスタンドアローンの状態で動作する。

【 0 0 8 5 】

即ち、ステップ s 1 6 において、下位制御装置 I C - 1 , ... , I C - 3 は、それぞれ、対応する蓄電モジュールに具備された単電池の電圧を、図 2 の電圧検出回路 1 で順次検出し、検出された値と判定レベル（容量調整用基準電圧：図 2 の基準電圧回路 2 が比較器 C M P 3 に出力する電圧）と比較する。

20

【 0 0 8 6 】

単電池の電圧が判定レベルより高い場合は、ステップ s 1 7 において、各単電池に対応するスイッチ素子 S 1 , ... , S 1 2 をオンさせ、再び、ステップ s 1 6 の処理を実行する。

【 0 0 8 7 】

単電池の電圧が判定レベルより低くなると、ステップ s 1 8 において、下位制御装置 I C - 1 , ... , I C - 3 は、それぞれ、対応する蓄電モジュールに具備された単電池の電圧が判定値より小さくなつたことを確認すると、各装置に備えた内部電源 2 をオフし、スリープ状態に入る。尚、スタンドアローンの状態では直列に接続された下位制御装置 I C - 1 , ... , I C - 3 はどういう順でスリープに入るかは決まっていない。そこで、図 3 、図 4 に示したように上下装置間での入出力の非絶縁接続では定電流スイッチ M P 3 に過大な電圧が印加されたり、単電池が局部的に放電したりする不具合を防止するようにしている。

30

【 0 0 8 8 】

なお、以上の例では、容量調整指令は、図 2 の比較器 C M P 3 に予め備えられた容量調整用基準電圧を用いている。しかしながら、図 7 に示す A / D コンバータを用い、上位制御装置 M P U が指示する任意の電圧を容量指令値として用いることができる。この場合、ステップ s 1 6 における判定レベルは、上位制御装置 M P U が指示する任意の電圧となる。なお、この点については、図 7 を用いて後述する。

【 0 0 8 9 】

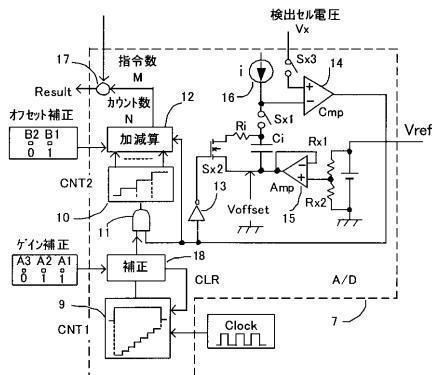

次に、図 7 ~ 図 1 0 を用いて、本実施形態による蓄電装置に用いる A / D コンバータ 7 の構成及び動作について説明する。本実施形態における A / D コンバータは、電圧検出手段の誤差を校正する機能を備えている。

40

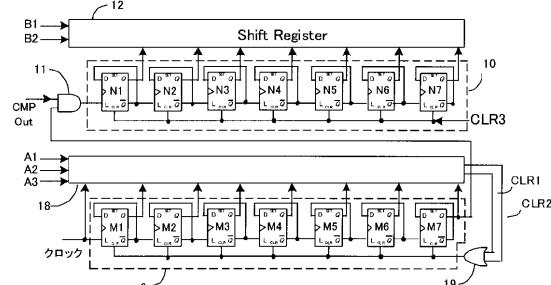

最初に、図 7 及び図 8 を用いて、本実施形態による蓄電装置に用いる A / D コンバータの全体構成について説明する。

図 7 は、本発明の一実施形態による蓄電装置に用いる A / D コンバータの構成を示す回路図である。図 8 は、本発明の一実施形態による蓄電装置に用いる A / D コンバータにおけるタイミングチャートである。なお、図 1 と同一符号は、同一部分を示している。

【 0 0 9 0 】

A / D コンバータ 7 は、図 1 に示したように、電圧検出誤差の補正用端子 A 1 , ... , A 3 , 及び補正用端子 B 1 , B 2 を備えている。図 2 に示した電圧検出手段 1 で検出された電圧 ( C 2 P の電圧 ) V x は、スイッチ手段 S x 3 を介して、比較器 1 4 の + 端子に伝えら

50

れる。一方、定電流手段  $S \times 6$  の電流  $i$  は、スイッチ手段  $S \times 3$  と同期して駆動されるスイッチ手段  $S \times 1$  を介して、キャパシタ  $C_i$  に蓄積される。キャパシタ  $C_i$  の電圧とアンプ 15 が出力する調整電圧 ( $V_{offset}$ ) とを加算した電圧が、比較器 14 の - 端子に印加され、検出電圧  $V_x$  と比較される。キャパシタ  $C_i$  は、単電池の電圧を一回、計測し終わると、論理インバータ 13 で駆動されたスイッチ手段  $S \times 2$  と抵抗  $R_i$  による放電回路で放電される。即ち、スイッチ手段  $S \times 3$  がオンして、検出電圧  $V_x$  が比較器 14 の + 端子に伝えられた瞬間には、キャパシタ  $C_i$  の電圧はゼロであり、比較器 14 の - 端子電圧は調整電圧 ( $V_{offset}$ ) に等しい。スイッチ手段  $S \times 2$  は、スイッチ手段  $S \times 1$  とスイッチ手段  $S \times 3$  がオンした時刻以降、オフ状態を継続する。このため、スイッチ手段  $S \times 1$  とスイッチ手段  $S \times 3$  がオンした時刻以降は時間と共に、キャパシタ  $C_i$  の電圧が電流  $i$  を積分して増加して行く。10

#### 【0091】

比較器 14 の出力は、キャパシタ  $C_i$  の電圧と調整電圧 ( $V_{offset}$ ) を加算した電圧が検出すべき単電池の電圧  $V_x$  より大きくなると、「1」から「0」に変わる。A/D コンバータ 7 は、スイッチ手段  $S \times 1$  とスイッチ手段  $S \times 3$  がオンした時刻から、比較器 14 の出力が「0」に変わるまでの時間を計測する積分型の検出を行う。

#### 【0092】

調整電圧 ( $V_{offset}$ ) を用いるのは、電池の残存容量と電圧の関係による。例えば、非晶質系炭素を用いたリチウムイオン電池の場合、残存容量が 0 % の状態で単電池電圧（開放電圧）は約 2.9 V であり、容量が 100 % の状態の開放電圧は約 4.1 V である。20 A/D コンバータ 7 は、例えば、2.9 V から 4.1 V までの電圧を精度良く検出することを求められており、残存容量が 0 % 以下の電圧は計測の対象ではない。そこで、残存容量が 0 % 以下の電圧（例えば 2 V）を調整電圧 ( $V_{offset}$ ) として選定し、調整電圧以上の電圧に対して高精度な検出が行えるよう工夫したものである。ここで、調整電圧は、図 2 に示した基準電圧  $V_{ref}$  の値を抵抗  $R \times 1$ ,  $R \times 2$  で分圧し、この値にアンプ 15 のゲインを掛けたものを用いている。

#### 【0093】

スイッチ手段  $S \times 1$  とスイッチ手段  $S \times 3$  がオンした時刻から比較器 14 の出力が 0 になるまでの時間は、次のようにして計測する。始めにクロックパルスを第一カウンタ 9 で分周する。図 8 (D) に示すクロックパルスの周波数を 10 MHz として、このパルスを例えば 128 発カウントして、図 8 (A) に示す半周期の信号を作る。補正用端子  $A_1, \dots, A_3$  が「1」か「0」かの状態に応じてカウント数は異なり、図 8 では基準の 128 発に対し ± 3 発の補正が可能な場合を例示している。なお、補正の詳細については、図 9 を用いて後述する。30

#### 【0094】

図 7において、比較器 14 の出力が 1 であれば、AND 回路 11 は、第一カウンタ 9 で分周されたパルスを次の第二カウンタ 10 に伝える。第二カウンタ 10 は、図 8 (C) に示すように、比較器 14 の出力が 0 になるまで、第一カウンタ 9 の出力をカウントする。調整電圧を含まない  $C_i$  の電圧が 0 V, ..., 3 V の範囲をフルスケールとして、3 V までのカウント数を 128 発と想定している。第二カウンタ 10 の特徴はシフトレジスタ 12 において、図 8 (B) に示すように、補正用端子  $B_1, B_2$  が「1」か「0」かの状態に応じて、第二カウンタ 10 の結果に ± 1 カウント（或いは 2 カウント）することである。シフトレジスタ 12 の出力は、上位制御装置 MPU から伝達された容量調整レベルとディジタル的に比較する、或いはシフトレジスタ 12 の出力を上位制御装置 MPU に伝える等の役割で使用する。40

#### 【0095】

ここで、補正用端子  $A_1, \dots, A_3$  に応じた第一カウンタ 9 の補正は、定電流  $i$ , キャパシタ  $C_i$  の値で決まるキャパシタ  $C_i$  の電圧値を補正することであり、ゲイン補正に相当する。また、補正用端子  $B_1, B_2$  による第二カウンタ 10 の補正は、アンプ 15 の出力である調整電圧を補正することであり、オフセット補正に相当する。50

## 【0096】

前述のようにクロック周波数を 10 MHz, 第一カウンタ 9 でのカウント数を 128, 第二カウンタでのカウント数をフルスケールで 128 とすれば、単電池電圧が 4 V の場合、約 1.1 ms の時間を要する。そこで、第一及び第二カウンタでのカウント数は、所望する電圧検出の精度と計測時間に応じて変更しても良いものである。

## 【0097】

A/D コンバータ 7 の補正端子 A1, A2, A3, B1, B2 は、直列に接続された下位制御装置 IC-1, ..., IC-3 が個別に備える基準電圧源の精度を校正するために備えられている。そのために、予め下位制御装置 IC-1, ..., IC-3 毎に、定電流  $i$ 、キャパシタ  $Ci$ 、及び調整電圧 ( $V_{offset}$ ) の誤差を検出し、これらの誤差を補正するよう、端子 A1, ..., A3 と端子 B1, B2 に「1」又は「0」の情報を与える。この「1」又は「0」は、前述のように、各端子を VDD 又は GND-1 に接続することによって設定でき、抵抗のレーザートリミングなどの特別な装置は必要としないものである。

10

## 【0098】

次に、図 9 及び図 10 を用いて、本実施形態による蓄電装置に用いる A/D コンバータの中の第一カウンタ 9 と第二カウンタ 10 の構成及び動作について説明する。

図 9 は、本発明の一実施形態による蓄電装置に用いる A/D コンバータの中の第一カウンタ 9 と第二カウンタ 10 の構成を示す回路図である。図 10 は、本発明の一実施形態による蓄電装置に用いる A/D コンバータにおける真理値表である。なお、図 7 と同一符号は、同一部分を示している。

20

## 【0099】

カウンタ 9, 10 は、128 カウントに応じた構成を示している。第一カウンタ 9 は、フリップフロップ M1, ..., M7 を備えており、各フリップフロップの出力を補正用ロジック 18 に入力する。補正用ロジック 18 は、補正用端子 A1, ..., A3 の状態に応じて、 $\pm 3$  パルス分だけ分周の周期を変更可能とする。補正用ロジック 18 は、図 10 に示すような真理値表を論理回路或いはソフトウェア的に作ったものである。補正用ロジック 18 の出力によってフリップフロップ M1, ..., M7 がクリアされる周期は異なり、このクリアまでの周期を半周期とするパルスが、フリップフロップ N1, ..., N7 で構成される第二カウンタ 10 に届けられる。シフトレジスタ 12 は、フリップフロップ N1, ..., N7 の各出力を補正用端子 B1, B2 の状態に応じて  $\pm 1$  カウント (或いは 2 カウント) 補正し、出力する。

30

## 【0100】

比較器 14 で判定されるキャパシタ  $Ci$  の電圧範囲を 0, ..., 3 V (Vx で表せば 0, ..., 5 V) をフルスケールとすると、シフトレジスタ 12 で補正される  $\pm 1$  カウントは  $\pm 2.3.4 \text{ mV}$  に相当する。また、補正用ロジック 18 で補正されるパルス幅 (第二カウンタの入力パルス幅) は 128 発に対して  $\pm 3$  発であれば  $\pm 2\%$  の補正が可能になる。

## 【0101】

図 1 に示した下位制御装置 IC-1, IC-2, IC-3 は、それぞれ製品出荷前に電圧検出手段の精度を検査し、各々が持つ基準電圧誤差に係わる電圧検出精度を評価する。そして、下位制御装置毎に補正用端子 A1, ..., A3 及び B1, B2 を用いて電圧検出精度が許容範囲以内になるように校正する。このようにすれば、基準電圧用に高価な高精度部品を備える必要が無く、装置の高精度化と低コストが両立できる。

40

## 【0102】

以上説明したように、本実施形態によれば、絶縁手段の個数を低減して、低コストな制御装置とすることができる。

また、ノイズ等の外乱による影響を低減して、信頼性の向上した信号伝達が可能となる。さらに、電圧検出の高精度化を図れるとともに、低コスト化することができる。

## 【0103】

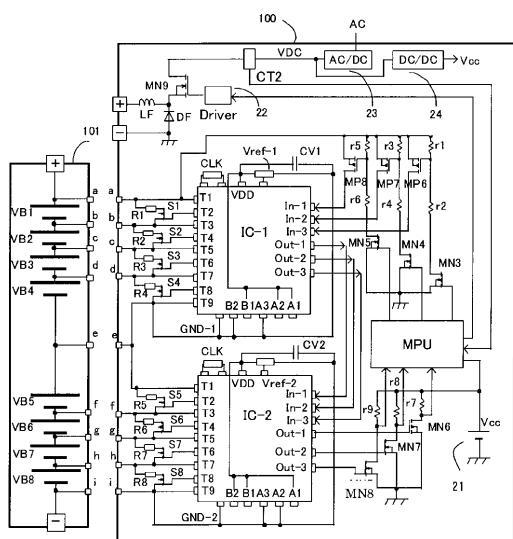

次に、図 11 を用いて、本発明の他の実施形態による蓄電装置について説明する。

図 11 は、本発明の他の実施形態による蓄電装置の全体構成を示す回路図である。

50

## 【0104】

本実施形態における蓄電装置では、充電器パッケージ100には、下位制御装置IC-1, IC-2と上位制御装置が収納されている。なお、蓄電モジュールを構成する単電池VB1-VB4と単電池VB5-VB8は、充電器パッケージ100とは別の電池パック101に収納している。

## 【0105】

従来、モバイル用機器では、電池の異常を検出する制御装置（下位制御装置IC-1, IC-2に相当する）を電池パック内部に搭載していた。一方、ハイブリッド電気自動車に使用されるニッケル水素或いはリチウム電池は、短時間に定格電流の数、…、十倍の電流を充放電可能な高出力型である。こうした高出力型電池は今後、自動車以外の民生用途（例えば電動工具やコードレスクリーナ等）に適用されるものと予想される。電動工具を例とすれば、電池定格の十倍近い電流を放電すると共に、定格の数倍の電流で急速充電を行う機能が求められる。電池定格の十倍近い電流を放電させると、制御装置の電圧検出手段は、電池の残存容量と相関性がある開放電圧（電池に負荷が繋がっていない状態の電圧）と電池の内部抵抗と大電流の積で決まる電圧降下分を合成した電圧を検出することになる。合成電圧が過放電レベル以下に減少すると、検出回路が過放電と判定してしまい装置は停止する。しかしながら、高出力型電池は短時間であれば合成電圧が過放電レベル以下に減少しても電池の安全性上、支障は無いものである。また、電動工具のような場合、電池の軽量化と低コスト化が求められるため、安全上支障が無ければ電池の保護に係わる制御装置（ICなど）を電池パックとは別の充電器に搭載し、工具を使用中はサーミスタ等の簡易な温度検知手段だけで電池の異常をモニタし、電池周辺の温度が許容値を超えた場合は、モータ等の電池負荷側で電流を遮断すれば良いものである。本実施形態では、このような電池の使い方を考慮している。

10

## 【0106】

図11に示す例では、電池パック101に、単電池を8ヶ直列に接続したものを収納している。充電器100内部には、図2に示した下位制御装置IC-1, IC-2が2ヶ直列に備えられている。下位制御装置IC-1, IC-2の周辺、即ち、容量調整用スイッチ、及び抵抗、クロック用振動子、基準電圧用部品は図1と同じ構成である。また、電圧検出補正用端子A1, A2, A3, B1, B2も、図1と同じである。

20

## 【0107】

図1と相違する点は、上位制御装置MPUと下位制御装置IC-1, IC-2の接続法であり、本実施形態では、絶縁用のフォトカプラは使用せず、スイッチ素子を用いた電位変換手段を備えている。即ち、上位制御装置MPUから高電位側の下位制御装置IC-1に信号を伝達する電位変換手段は、上位制御装置MPUからゲート信号を入力されるN-MOSFET(MN3), (MN4), (MN5)を備え、これらのスイッチ手段は、それぞれ、抵抗r1と抵抗r2、抵抗r3と抵抗r4、及び抵抗r5と抵抗r6からなる直列抵抗に接続される。ここで、抵抗r1, r2, r3は、一端が最高電位の単電池VB1の正極に接続される。抵抗r1, r2, r3の電圧は、それぞれ、P-MOSFET(MP6), (MP7), (MP8)のゲートに接続され、上位制御装置MPUによってN-MOSFET(MN3), (MN4), (MN5)がオン・オフすると、これに応じてP-MOSFET(MP6), (MP7), (MP8)もオン・オフする。P-MOSFET(MP6), (MP7), (MP8)のドレイン端子は、下位制御装置IC-1の入力端子In-1, In-2及びIn-3に伝達される。

30

## 【0108】

同様に低電位側の下位制御装置IC-2から上位制御装置MPUへ戻る信号を電位変換する手段は、下位制御装置IC-3の出力端子Out-1, Out-2, Out-3にそれぞれゲートが接続されたN-MOSFET(MN6), (MN7), (MN8)を備え、N-MOSFET(MN6), (MN7), (MN8)のドレイン端子と制御電源21(Vcc)の正極の間に抵抗r7, r8, r9を接続する。そして、抵抗r7, r8, r9の電圧が上位制御装置MPUに戻る。上位制御装置MPUは、充電制御用の回路にも信号を送る。即ち

40

50

、高電圧電源VDCに接続されたパワーMOSFET(MN9)とそのドライバ回路22、パワーMOSFET(MN9)に接続された還流用ダイオードDF、パワーMOSFET(MN9)に一端が接続されたチョークコイルLFが充電用回路であり、高電圧電源VDCからパワーMOSFET(MN9)を経て電池パック101に流れる電流は、電流検出器CT2でモニタする。また、高電圧電源VDCは、商用交流電源に接続されるAC/DCコンバータ23で作られ、VDCの出力をDC/DCコンバータ24を用いて上位制御装置MPU用の制御電源21を作る。

#### 【0109】

電池パック101に搭載された単電池の各電極と充電器100内部の対応する下位制御装置IC-1, IC-2は、それぞれ、端子a, …, iで接続する。また、電池パック101と充電器100の正極、負極をそれぞれ接続して充電電流を流す。充電器100は、上位制御装置MPUが出力する信号でパワーMOSFET(MN9)を流れる充電電流を制御する。下位制御装置IC-1, IC-2は、電池パック101の充電中或いは充電終了後に、図6にて説明した容量調整を実施する。充電中に容量調整を実施する際には、電池パック101と充電器100が接続された際に、下位制御装置IC-1, IC-2に搭載されたA/Dコンバータで各単電池の電圧を計測し、上位制御装置MPUにその数値を順次送る。上位制御装置MPUでは、各単電池の電圧から容量調整レベルを算出し、下位制御装置IC-1, IC-2に伝達する。以後、充電電流が流れる中、下位制御装置IC-1, IC-2は容量調整と過充電の検出を実施する。尚、図6のステップs18で述べた調整後にスリープする動作はないものである。

10

20

#### 【0110】

以上説明したように、本実施形態によれば、絶縁手段の個数を低減して、低コストな制御装置とすることができる。

また、ノイズ等の外乱による影響を低減して、信頼性の向上した信号伝達が可能となる。さらに、電圧検出の高精度化を図れるとともに、低コスト化することができる。

#### 【0111】

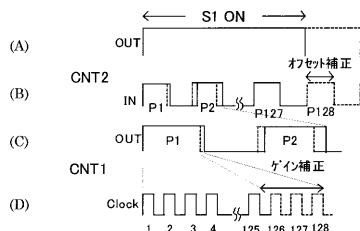

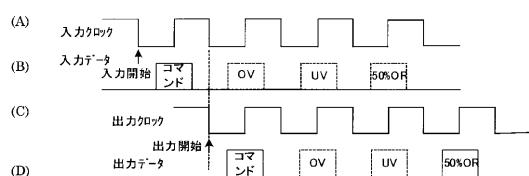

次に、図12を用いて、本発明のその他の実施形態による蓄電装置の制御方法について説明する。

図12は、本発明のその他の実施形態による蓄電装置における制御内容を示すタイミングチャートである。なお、本実施形態に用いる蓄電装置の構成は、図1に示すもの、図11に示すもののいずれをも用いることができる。

30

#### 【0112】

図12は、上位制御装置MPUから下位制御装置IC-1へ、或いは下位制御装置IC-1, IC-2, CI-3間で伝達される入出力データ伝送方法を示している。

#### 【0113】

上位制御装置MPUは、図12(A)に示したクロック信号と、このクロック信号に同期した入力データ(図12(B))を、最高電位にある下位制御装置IC-1に伝達する。そして、下位制御装置IC-1, …, IC-3間では、高電位側から低電位側へ入力されたデータをシリアルで伝送する。即ち、入力クロックと入力データを受け取った下位制御装置は、図12(C), (D)に示すように、1クロック分ずらして同じ信号を出力する。

40

#### 【0114】

このようにすれば、信号が入力してから出力するまでの信号遅延時間を短縮することができる。図12(B), (D)に、破線で示したOV, UV, 及び50%ORはそれぞれ、過充電、過放電、及び容量調整判定のビットを意味している。図12で1つ高電位側から受け取った入力データにOV, UV, 及び50%ORの情報がある場合は実線で、無い場合は波線で示している。出力データでは50%ORを実線で示したが、これは入力データを受け取った下位制御装置が対応する単電圧(例えば単電池VB1, …, VB4)の電圧を検出した結果、容量調整レベルを越える単電池があったことを意味する。このように、下位制御装置は、過充電、過放電、及び容量調整判定等に関して入力されたデータと、対

50

応する単電池の検出結果の論理和 ( O R ) をとり、その結果を下位制御装置に伝達する。

【 0 1 1 5 】

上位制御装置 M P U は、戻ってきたデータで O V , U V , 5 0 % O R のいずれかのフラグが立っていれば、全体の単電池のうち、少なくとも 1 つは判定レベルを超えた電池があったことを認識することができる。

【 0 1 1 6 】

以上のようなシリアル信号にすれば、複数の下位制御装置が非絶縁で接続された場合において、信号伝達の遅延も短く、 O R 形式によりフェールセーフ型になるため、信頼性も向上する。なお、論理和の代わりに、論理積をとることにより、充放電時の信号解析から電池電圧のバラツキを推定することができ、この検出により容量調整機能を動作させることもできる。

10

【 0 1 1 7 】

なお、図 1 ~ 図 1 2 に示した実施形態において、単電池 V B 1 , … , V B 1 2 を二次電池としているが、これに限定するものではなく、ウルトラキャパシタでもよいものである。

【 0 1 1 8 】

【発明の効果】

本発明によれば、絶縁手段の個数を低減して、制御装置を低コスト化することができる。また、ノイズ等の外乱による影響を低減して、信頼性の向上した信号伝達が可能となる。さらに、電圧検出の高精度化を図れるとともに、低コスト化することができる。

【図面の簡単な説明】

20

【図 1 】本発明の一実施形態による蓄電装置の全体構成を示す回路図である。

【図 2 】本発明の一実施形態による蓄電装置に用いる下位制御装置内部の構成を示す回路図である。

【図 3 】本発明の一実施形態による蓄電装置の中の下位制御装置に用いる出力回路 6 及び入力回路 4 の第 1 の構成を示す回路図である。

【図 4 】本発明の一実施形態による蓄電装置の中の下位制御装置に用いる出力回路 6 及び入力回路 4 の第 2 の構成例を示す回路図である。

【図 5 】本発明の一実施形態による蓄電装置の制御内容を示すフローチャートである。

【図 6 】本発明の一実施形態による蓄電装置における容量調整時の制御内容を示すフローチャートである。

30

【図 7 】本発明の一実施形態による蓄電装置に用いる A / D コンバータの構成を示す回路図である。

【図 8 】本発明の一実施形態による蓄電装置に用いる A / D コンバータにおけるタイミングチャートである。

【図 9 】本発明の一実施形態による蓄電装置に用いる A / D コンバータの中の第一カウンタ 9 と第二カウンタ 1 0 の構成を示す回路図である。

【図 1 0 】本発明の一実施形態による蓄電装置に用いる A / D コンバータにおける真理値表である。

【図 1 1 】本発明の他の実施形態による蓄電装置の全体構成を示す回路図である。

【図 1 2 】本発明のその他の実施形態による蓄電装置における制御内容を示すタイミングチャートである。

40

【符号の説明】

1 … 電圧検出手段

2 … 電源回路

3 … ロジック回路

4 … 入力回路

5 … クロック発生回路

6 … 出力回路

7 … A / D コンバータ

8 … 電源制御回路

50

- 9 ... 第一カウンタ

10 ... 第二カウンタ

11 ... AND回路

12 ... シフトレジスタ

13 ... 論理インバータ

14 ... 比較器

15 ... アンプ

16 ... 定電流回路手段

17 ... ディジタルな比較手段

18 ... 補正用ロジック

19 ... OR回路

20 ... AND回路

21 ... 制御電源

22 ... ドライバ回路

23 ... AC / DCコンバータ

24 ... DC / DCコンバータ

100 ... 充電器

101 ... 電池パック

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 図 8 】

〔 四 9 〕

【 义 1 0 】

| No | A1 | A2 | A3 | CLK | M1<br>Q | M2<br>Q | M3<br>Q | M4<br>Q | M5<br>Q | M6<br>Q | M7<br>Q | CLR<br>1 | CLR<br>2 |

|----|----|----|----|-----|---------|---------|---------|---------|---------|---------|---------|----------|----------|

| 1  | -  | 0  | 0  | 0   | -       | -       | -       | -       | -       | 1       | -       | -        | -        |

| 2  | 1  | 1  | 0  | 0   | 1       | -       | -       | -       | -       | -       | 1       | 0        | 1        |

| 3  | 1  | 0  | 1  | 0   | 0       | 1       | -       | -       | -       | -       | 1       | 0        | 1        |

| 4  | 1  | 1  | 1  | 0   | 1       | 1       | -       | -       | -       | -       | 1       | 0        | 1        |

| 5  | 0  | 1  | 0  | 0   | 1       | 1       | 1       | 1       | 1       | 1       | 0       | 0        | 1        |

| 6  | 0  | 0  | 1  | 0   | 0       | 1       | 1       | 1       | 1       | 1       | 0       | 0        | 1        |

| 7  | 0  | 1  | 1  | 0   | 1       | 0       | 1       | 1       | 1       | 1       | 0       | 0        | 1        |

【 1 1 】

【図12】

---

フロントページの続き

(72)発明者 江守 昭彦

茨城県日立市大みか町七丁目1番1号 株式会社 日立製作所 日立研究所内

(72)発明者 工藤 彰彦

東京都中央区日本橋本町二丁目8番7号 新神戸電機株式会社内

(72)発明者 甲斐 剛

東京都中央区日本橋本町二丁目8番7号 新神戸電機株式会社内

審査官 石川 晃

(56)参考文献 特開2001-224138 (JP, A)

特開2000-173674 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H02J 7/02

H02J 7/00

B60L 11/18

H01M 10/44