(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 11 2006 001 663 T5 2008.05.08

(12)

## Veröffentlichung

der internationalen Anmeldung mit der

(87) Veröffentlichungs-Nr.: **WO 2007/005263**

in deutscher Übersetzung (Art. III § 8 Abs. 2 IntPatÜG)

(21) Deutsches Aktenzeichen: **11 2006 001 663.6**

(86) PCT-Aktenzeichen: **PCT/US2006/023851**

(86) PCT-Anmeldetag: **19.06.2006**

(87) PCT-Veröffentlichungstag: **11.01.2007**

(43) Veröffentlichungstag der PCT Anmeldung

in deutscher Übersetzung: **08.05.2008**

(51) Int Cl.<sup>8</sup>: **H01L 21/00 (2006.01)**

(30) Unionspriorität:

**60/696,320** 30.06.2005 US

**60/696,027** 30.06.2005 US

**60/696,350** 30.06.2005 US

**60/696,305** 30.06.2005 US

**60/701,781** 22.07.2005 US

**60/702,076** 22.07.2005 US

**60/753,040** 21.12.2005 US

(71) Anmelder:

**FAIRCHILD SEMICONDUCTOR CORP.**, South

Portland, Me., US

(74) Vertreter:

**Eisenführ, Speiser & Partner, 20457 Hamburg**

(72) Erfinder:

**Jeon, Oseob, Seoul, KR; Choi, Yoonhwa, Inchun, KR; Gooi, Boon Huan, Penang, MY; Estacio, Maria Cristina B., Talamban, Cebu, PH; Chong, David, Penang, MY; Keng, Tan Teik, Penang, MY; Nam, Shibaek, Puchon, Kyonggido, KR; Joshi, Rajeev, Cupertino, Calif., US; Wu, Chung-Lin, San Jose, Calif., US; Iyer, Venkat, Cupertino, Calif., US; Lim, Lay Yeap, Lebuh Nipah, Penang, MY; Lee, Buyong-Ok, Puchon, Kyonggido, KR**

(54) Bezeichnung: **Halbleiterchip-Gehäuse und Verfahren zur Herstellung desselben**

(57) Hauptanspruch: Verfahren umfassend:

Bereitstellen eines vorgeformten Substrats mit einer Leiterrahmenstruktur und einem Formmaterial, wobei die Leiterrahmenstruktur einen ersten leitenden Teilbereich, einen zweiten leitenden Teilbereich und einen Zwischen-Teilbereich zwischen dem ersten leitenden Teilbereich und dem zweiten leitenden Teilbereich beinhaltet;

Trennen des Zwischen-Teilbereichs, um den ersten leitenden Teilbereich von dem zweiten leitenden Teilbereich elektrisch zu isolieren;

Befestigen eines Halbleiterchips an dem Substrat; und

elektrisches Koppeln der ersten und zweiten leitenden Teilbereiche zu dem Halbleiterchip.

**Beschreibung****VERWEISE AUF VERWANDTE ANMELDUNGEN**

**[0001]** Diese Patentanmeldung ist eine Nachanmeldung zu und beansprucht die Priorität der folgenden vorläufigen US-Anmeldungen: 60/701,781, angemeldet am 22. Juli 2005; 60/696,320, angemeldet am 30. Juni 2005; 60/696,027, angemeldet am 30. Juni 2005; 60/696,350, angemeldet am 30. Juni 2005; 60/702,076, angemeldet am 22. Juli 2005; 60/696,305, angemeldet am 30. Juni 2005, und 60/753,040, angemeldet am 21. Dezember 2005. Diese vorläufigen US-Anmeldungen werden hiermit durch Bezugnahme in ihrer Gesamtheit für alle Zwecke eingeschlossen.

**HINTERGRUND DER ERFINDUNG**

**[0002]** Verschiedene Halbleiterchip-Gehäuse oder -packungen sind bekannt.

**[0003]** Während solche Gehäuse nützlich sind, können sie verbessert werden. Beispielsweise sind viele der oben beschriebenen Gehäuse schwer und/oder teuer herzustellen.

**[0004]** Folglich wäre es wünschenswert, verbesserte Halbleiterchip-Gehäuse, Verfahren zur Herstellung von Halbleiterchip-Gehäusen, Komponenten für solche Chipgehäuse und elektrische Baugruppen, die solche Halbleiterchip-Gehäuse verwenden, bereitzustellen. Solche verbesserten Halbleiterchip-Gehäuse würden vorzugsweise weniger teuer herzustellen sein und/oder würden eine bessere Funktionalität aufweisen.

**ZUSAMMENFASSUNG DER ERFINDUNG**

**[0005]** Ausführungsformen der Erfindung sind auf Halbleiterchip-Gehäuse, Verfahren zur Herstellung von Halbleiterchip-Gehäusen und elektrischen Baugruppen, die die Halbleiterchip-Gehäuse beinhalten, gerichtet.

**[0006]** Eine Ausführungsform der Erfindung ist auf ein Verfahren gerichtet, umfassend Bereitstellen eines vorgeformten Substrats mit einer Leiterrahmenstruktur und einem Formmaterial, wobei die Leiterrahmenstruktur einen ersten leitenden Teilbereich, einen zweiten leitenden Teilbereich und einen Zwischen-Teilbereich zwischen dem ersten leitenden Teilbereich und dem zweiten leitenden Teilbereich beinhaltet; Trennen des Zwischen-Teilbereichs, um den ersten leitenden Teilbereich von dem zweiten leitenden Teilbereich elektrisch zu isolieren; Befestigen eines Halbleiterchips an dem Substrat; und elektrisches Koppeln der ersten und zweiten leitenden Teilbereiche zu dem Halbleiterchip.

**[0007]** Eine weitere Ausführungsform der Erfindung ist auf ein Halbleiterchip-Gehäuse gerichtet, umfassend: ein vorgeformtes Substrat mit einer Leiterrahmenstruktur und einem Formmaterial, wobei die Leiterrahmenstruktur einen ersten leitenden Teilbereich, einen zweiten leitenden Teilbereich und eine Aussparung zwischen dem ersten leitenden Teilbereich und dem zweiten leitenden Teilbereich beinhaltet; einen Halbleiterchip auf dem vorgeformten Substrat; und ein Einkapsel-Material, das den Halbleiterchip abdeckt und die Aussparung zwischen dem ersten leitenden Teilbereich und dem zweiten leitenden Teilbereich füllt.

**[0008]** Eine weitere Ausführungsform der Erfindung ist auf ein Verfahren gerichtet, umfassend: Bereitstellen eines vorgeformten Substrats mit einer ersten Oberfläche und einer zweiten Oberfläche, wobei das vorgeformte Substrat eine Leiterrahmenstruktur und ein Formmaterial beinhaltet, wobei die Leiterrahmenstruktur ein Feld-Gebiet bzw. Feld-Region umfasst, wobei eine äußere Oberfläche des Feld-Gebiets und eine äußere Oberfläche des Formmaterials im Wesentlichen planparallel bzw. planar sind und mit der zweiten Oberfläche des vorgeformten Substrats zusammenfallen; und Befestigen von zumindest zwei Halbleiterchips an der ersten Oberfläche des vorgeformten Substrats.

**[0009]** Eine weitere Ausführungsform der Erfindung ist auf ein Halbleiterchip-Gehäuse gerichtet, umfassend: ein vorgeformtes Substrat mit einer ersten Oberfläche und einer zweiten Oberfläche, wobei das vorgeformte Substrat eine Leiterrahmenstruktur und ein Formmaterial beinhaltet, wobei die Leiterrahmenstruktur ein Feld-Gebiet umfasst, wobei eine äußere Oberfläche des Feld-Gebiets und eine äußere Oberfläche des Formmaterials im Wesentlichen planparallel sind und mit der zweiten Oberfläche des vorgeformten Substrats zusammenfallen; und zumindest zwei Halbleiterchips zu der ersten Oberfläche des vorgeformten Substrats gekoppelt sind.

**[0010]** Eine weitere Ausführungsform der Erfindung ist auf ein Verfahren zum Formen eines Halbleiter-

chip-Gehäuses gerichtet, das Verfahren umfassend: Formen eines Substrats, wobei Formen eines Substrats umfasst (i) Platzieren einer Leiterrahmenstruktur zwischen einer ersten Ausformform und einer zweiten Ausformform, (ii) Kontaktieren der Leiterrahmenstruktur mit den ersten und zweiten Ausformformen, und (iii) Formen eines Formmaterials um die Leiterrahmenstruktur; Befestigen eines Halbleiterchips an dem Substrat; und Einkapseln des Halbleiterchips in einem Einkapsel-Material.

**[0011]** Eine weitere Ausführungsform der Erfindung ist auf ein Halbleiterchip-Gehäuse gerichtet, umfassend: ein Substrat, wobei Formen eines Substrats eine Leiterrahmenstruktur und ein Formmaterial umfasst, wobei das Substrat zumindest eine konkave Struktur formt; und einen Halbleiterchip auf dem Substrat.

**[0012]** Eine weitere Ausführungsform der Erfindung ist auf ein Verfahren gerichtet, umfassend: Bereitstellen eines Substrats beinhaltend eine Leiterrahmenstruktur und ein Formmaterial, wobei eine Oberfläche des Formmaterials und die Leiterrahmenstruktur im Wesentlichen planparallel sind, und wobei das Substrat ein erstes Chip-Befestigungs-Gebiet und ein zweites Chip-Befestigungs-Gebiet beinhaltet; Befestigen eines ersten Halbleiterchips an dem ersten Chip-Befestigungs-Gebiet; und Befestigen eines zweiten Halbleiterchips an dem zweiten Chip-Befestigungs-Gebiet.

**[0013]** Eine weitere Ausführungsform der Erfindung ist auf ein Halbleiterchip-Gehäuse gerichtet, umfassend: ein Substrat beinhaltend eine Leiterrahmenstruktur und ein Formmaterial, wobei eine Oberfläche des Formmaterials und die Leiterrahmenstruktur im Wesentlichen planparallel sind, und wobei das Substrat ein erstes Chip-Befestigungs-Gebiet und ein zweites Chip-Befestigungs-Gebiet umfasst; einen ersten Halbleiterchip auf dem ersten Chip-Befestigungs-Gebiet; und einen zweiten Halbleiterchip auf dem zweiten Chip-Befestigungs-Gebiet.

**[0014]** Eine weitere Ausführungsform der Erfindung ist auf ein Verfahren zur Herstellung eines Substrats für ein Halbleiterchip-Gehäuse gerichtet, das Verfahren umfassend: Bereitstellen einer ersten Leiterrahmenstruktur und einer zweiten Leiterrahmenstruktur; Befestigen der ersten und zweiten Leiterrahmenstruktur aneinander mittels einer Klebeschicht; und Aufbringen des Formmaterials auf die erste Leiterrahmenstruktur, die zweite Leiterrahmenstruktur, oder die Klebeschicht.

**[0015]** Eine weitere Ausführungsform der Erfindung ist auf ein Halbleiterchip-Gehäuse gerichtet, umfassend: ein vorgeformtes Substrat umfassend eine Leiterrahmenstruktur und ein Formmaterial, wobei eine äußere Oberfläche der Leiterrahmenstruktur und eine äußere Oberfläche des Formmaterials im Wesentlichen planparallel sind; und einen Halbleiterchip auf dem vorgeformten Substrat; an dem vorgeformten Substrat befestigte Leiter, wobei die Leiter einzeln aus dem vorgeformten Substrat geformt wurden

**[0016]** Eine weitere Ausführungsform der Erfindung ist auf ein Verfahren gerichtet, umfassend: Bereitstellen eines Substrats umfassend eine leitende Chip-Befestigungs-Oberfläche; Befestigen eines hochseitigen Transistors beinhaltend einen hochseitigen Transistor-Eingang an dem Substrat, wobei der hochseitige Transistor-Eingang zu der leitenden Chip-Befestigungs-Oberfläche gekoppelt ist; und Befestigen eines niedrigseitigen Transistors beinhaltend einen niedrigseitigen Transistor-Ausgang an dem Substrat, wobei der niedrigseitige Transistor-Eingang zu der leitenden Chip-Befestigungs-Oberfläche gekoppelt ist.

**[0017]** Eine weitere Ausführungsform der Erfindung ist auf ein Halbleiterchip-Gehäuse gerichtet, umfassend: ein Substrat umfassend eine leitende Chip-Befestigungs-Oberfläche; einen hochseitigen Transistor umfassend einen hochseitigen Transistor-Eingang, wobei der hochseitige Transistor-Eingang zu der leitenden Chip-Befestigungs-Oberfläche gekoppelt ist; und einen niedrigseitigen Transistor beinhaltend einen niedrigseitigen Transistor-Ausgang, wobei der niedrigseitige Transistor-Eingang zu der leitenden Chip-Befestigungs-Oberfläche gekoppelt ist.

**[0018]** Diese und andere Ausführungsformen der Erfindung sind nachfolgend in weiteren Details beschrieben.

#### KURZE BESCHREIBUNG DER ZEICHNUNGEN

**[0019]** [Fig. 1A-Fig. 1H](#) zeigen Querschnitte von Komponenten während des Formens eines Halbleiterchip-Gehäuses gemäß einer Ausführungsform der Erfindung.

**[0020]** [Fig. 1I](#) zeigt eine Unteransicht eines Halbleiterchip-Gehäuses gemäß einer Ausführungsform der Erfindung.

- [0021] [Fig. 1J](#) ist eine Draufsicht auf eine Anordnung von Substraten während der Herstellung.

- [0022] [Fig. 1K](#) ist eine quergeschnittene Seitenansicht einer Leiste beinhaltend eine Referenzkerbe.

- [0023] [Fig. 1L](#) zeigt eine Draufsicht auf ein Substrat mit Trennlinien.

- [0024] [Fig. 2A](#) zeigt eine Unteransicht auf ein anderes Halbleiterchip-Gehäuse gemäß einer Ausführungsform der Erfindung.

- [0025] [Fig. 2B](#) zeigt eine quergeschnittene Seitenansicht des in [Fig. 2A](#) gezeigten Halbleiterchip-Gehäuses.

- [0026] [Fig. 2C](#) zeigt eine Unteransicht auf eine Leiterrahmen-Struktur gemäß einer Ausführungsform der Erfindung.

- [0027] [Fig. 2D](#) zeigt eine Unteransicht auf ein Halbleiterchip-Gehäuse gemäß einer anderen Ausführungsform der Erfindung.

- [0028] [Fig. 2E](#) zeigt eine quergeschnittene Seitenansicht eines anderen Halbleiterchip-Gehäuses gemäß einer anderen Ausführungsform der Erfindung.

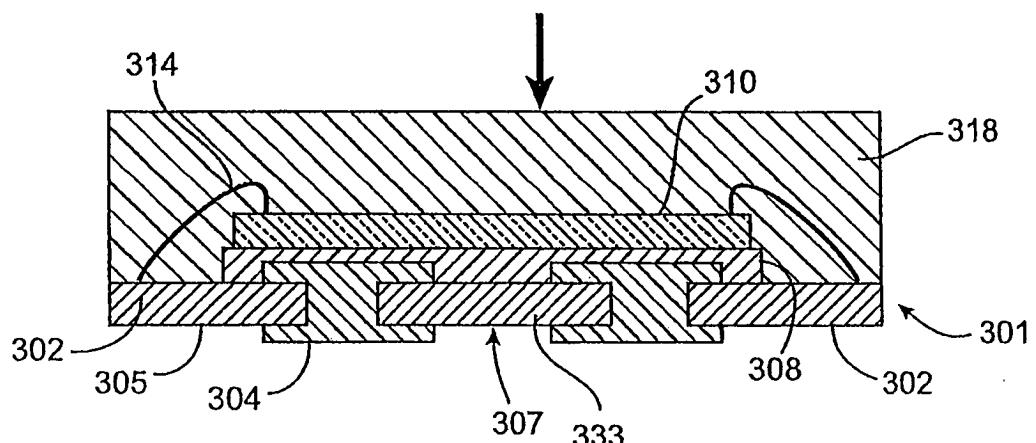

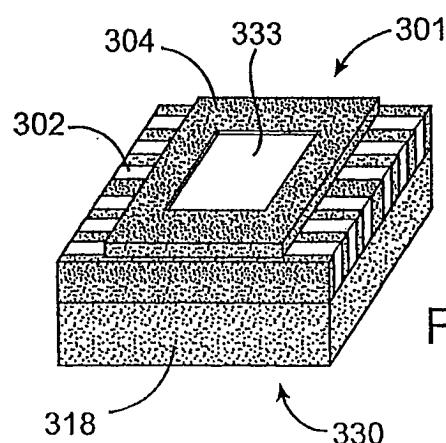

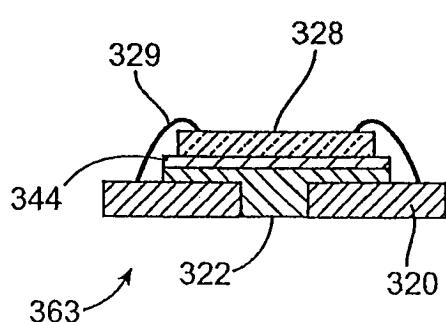

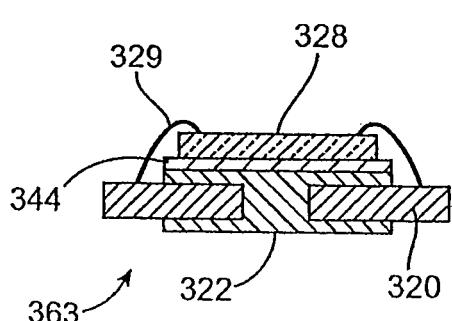

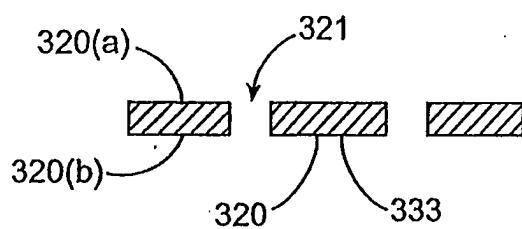

- [0029] [Fig. 3A](#)-[Fig. 3C](#) zeigen eine Draufsicht auf ein Halbleiterchip-Gehäuse während es aufgebaut wird.

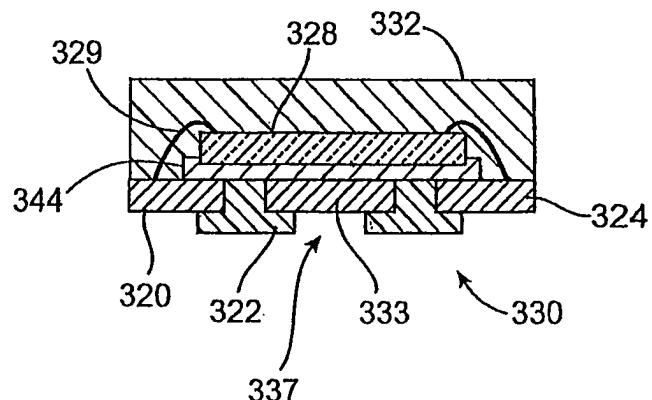

- [0030] [Fig. 3D](#) zeigt eine Unteransicht auf ein Halbleiterchip-Gehäuse.

- [0031] [Fig. 3E](#) zeigt eine quergeschnittene Seitenansicht eines Substrats gemäß einer Ausführungsform der Erfindung.

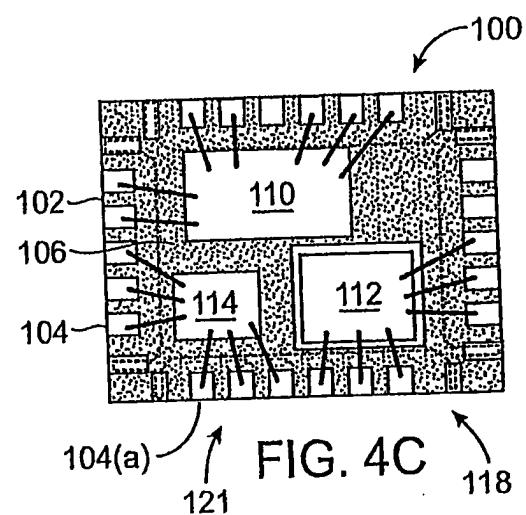

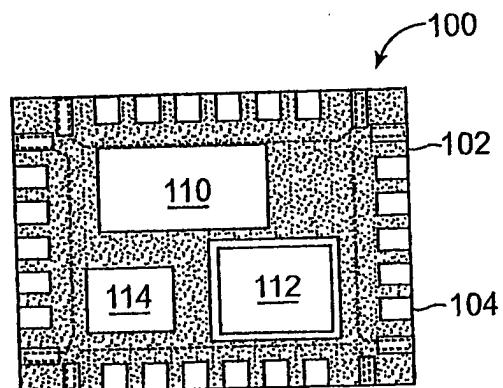

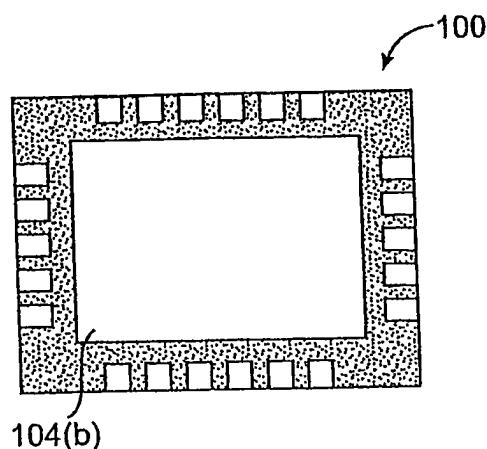

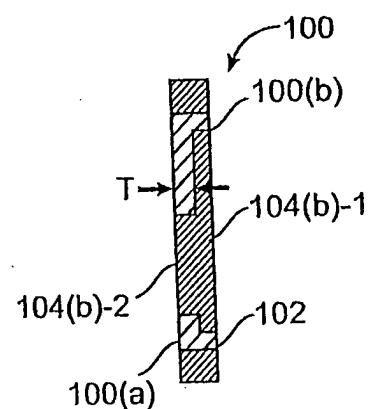

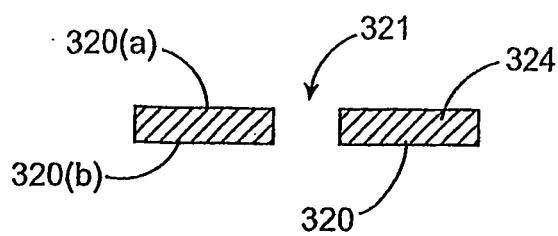

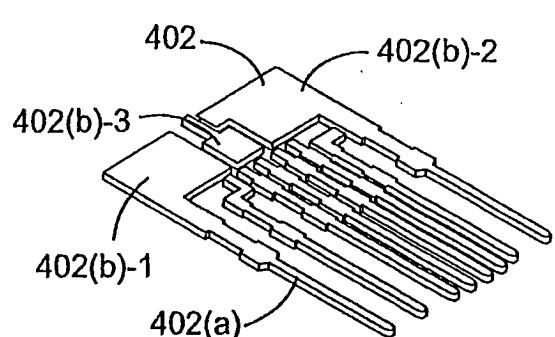

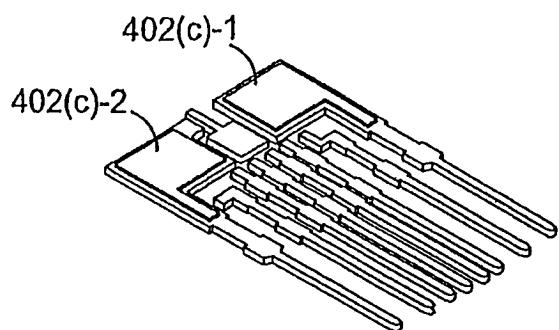

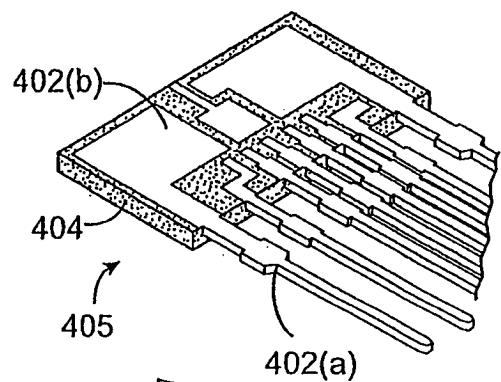

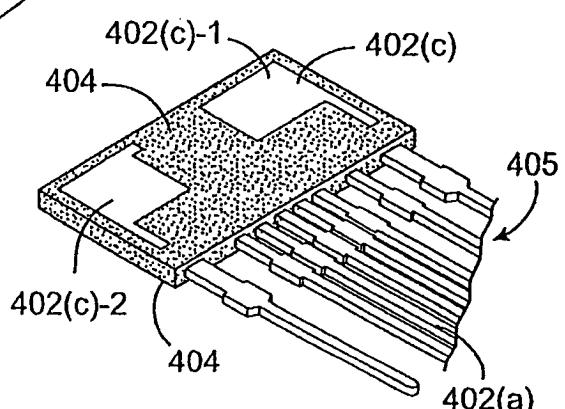

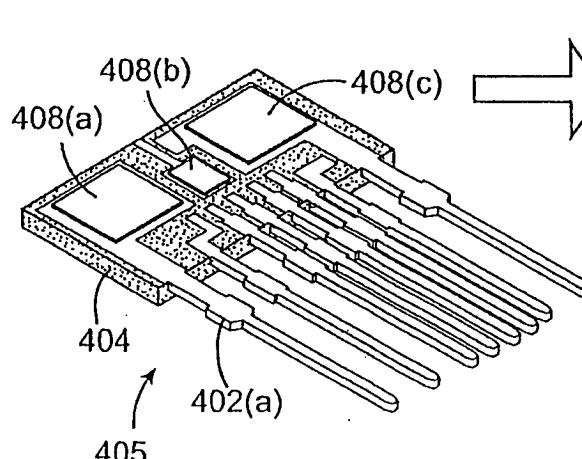

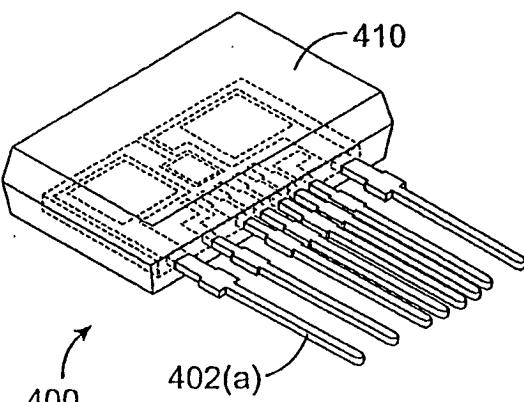

- [0032] [Fig. 4A](#)-[Fig. 4C](#) zeigen Draufsichten eines anderen Halbleiterchip-Gehäuses gemäß einer Ausführungsform der Erfindung.

- [0033] [Fig. 4D](#) zeigt eine Unteransicht auf ein Substrat gemäß einer Ausführungsform der Erfindung.

- [0034] [Fig. 4E](#) zeigt eine quergeschnittene Seitenansicht eines Substrats gemäß einer Ausführungsform der Erfindung.

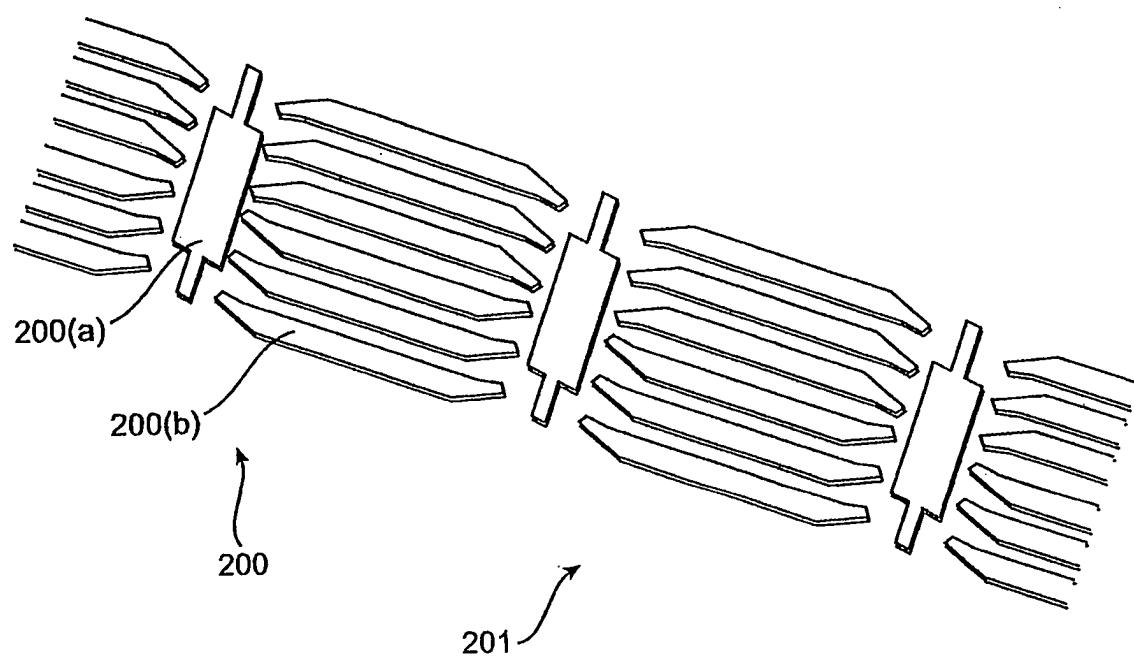

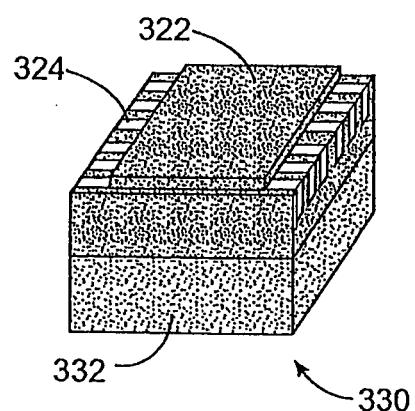

- [0035] [Fig. 5](#) zeigt eine perspektivische Ansicht einer Leiterrahmen-Struktur-Anordnung.

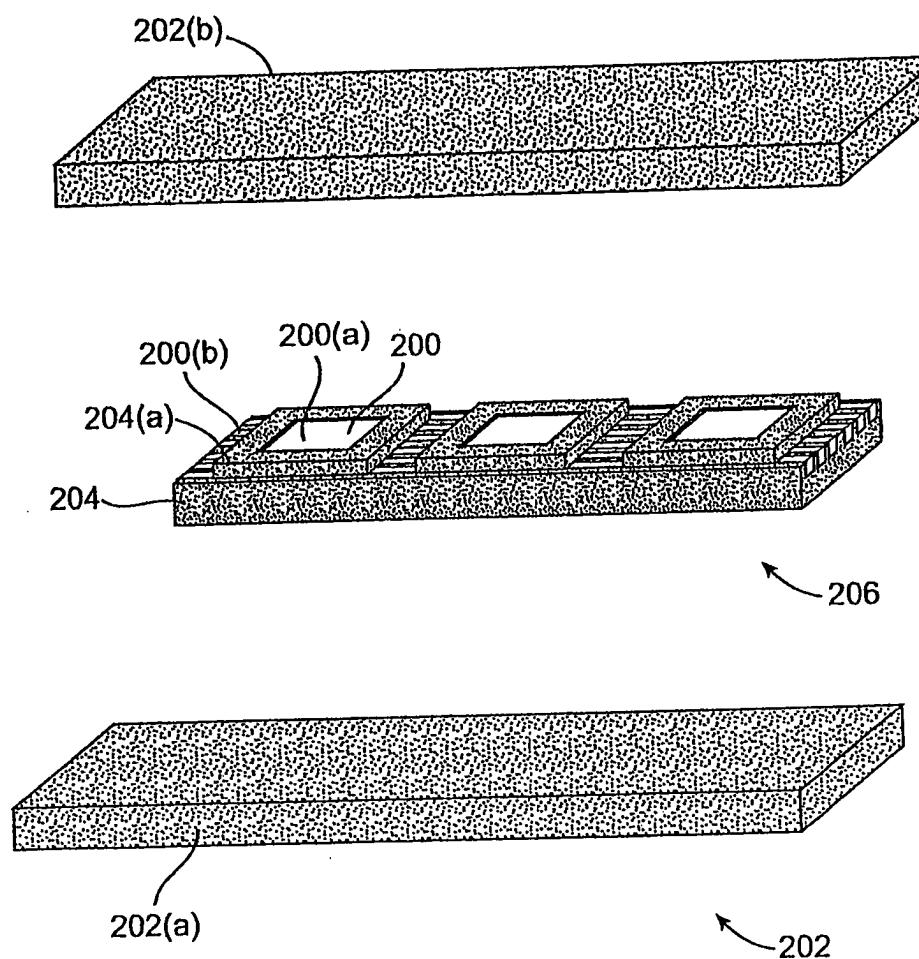

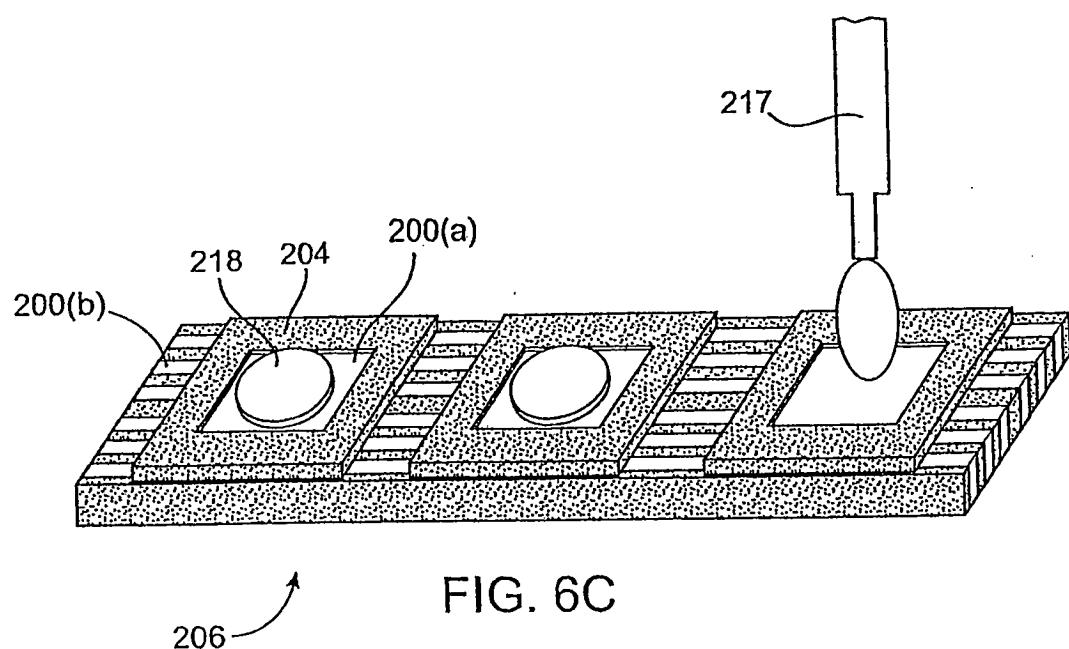

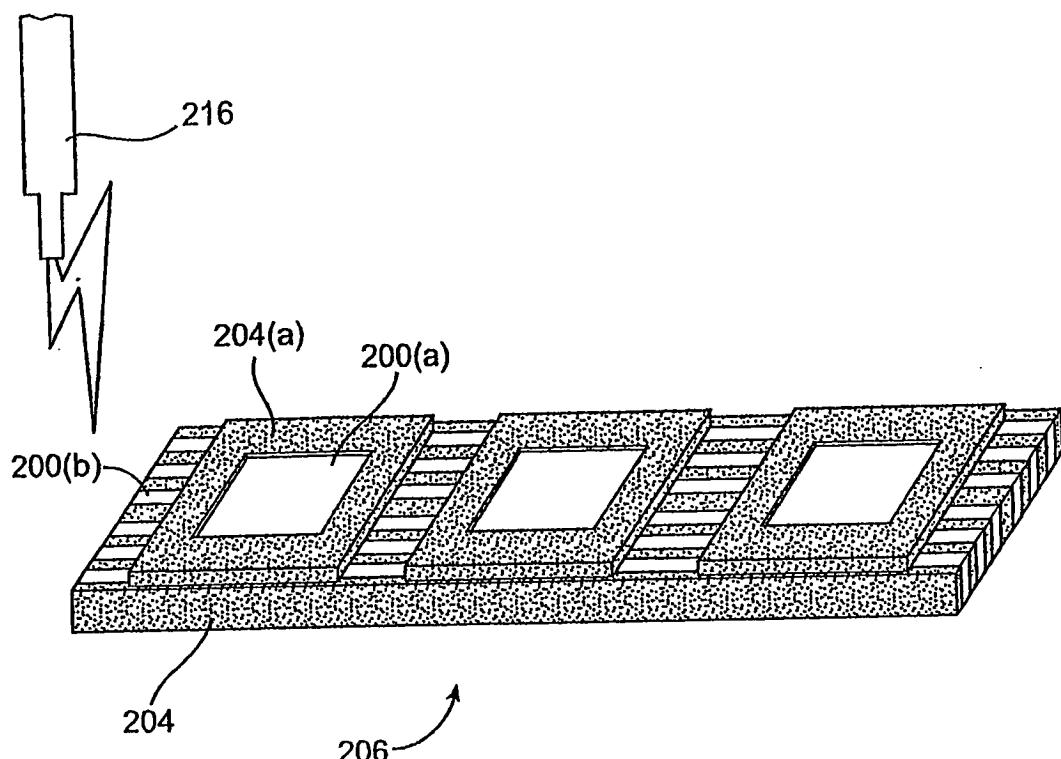

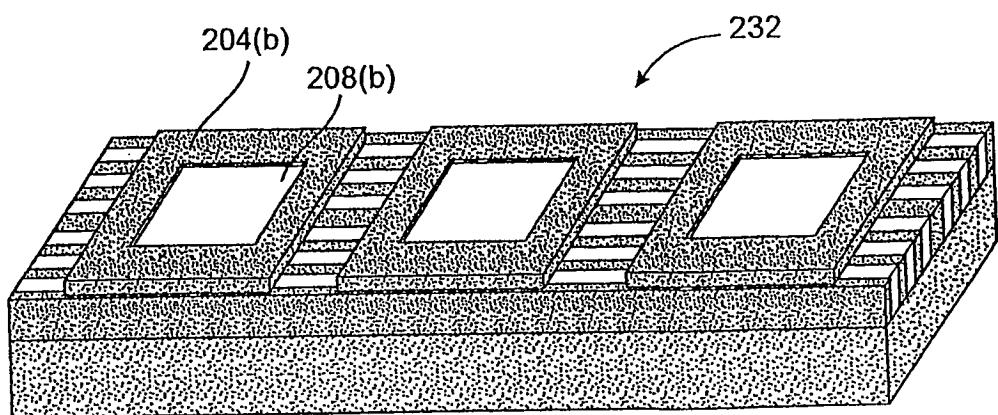

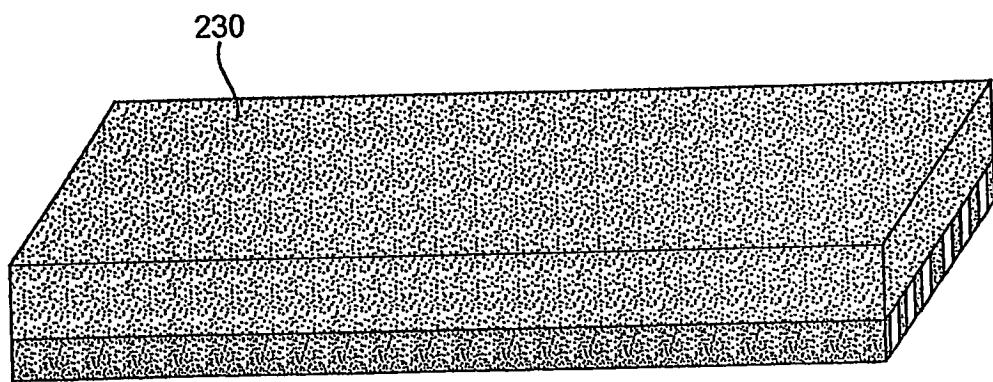

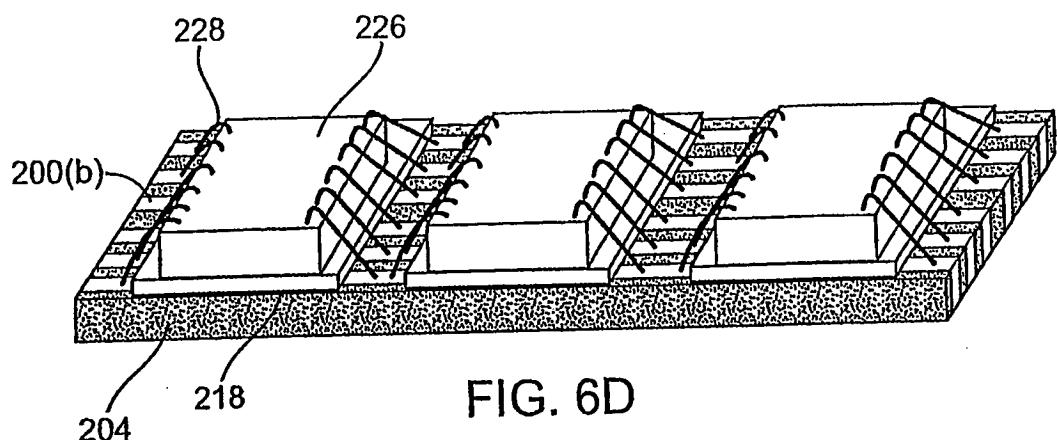

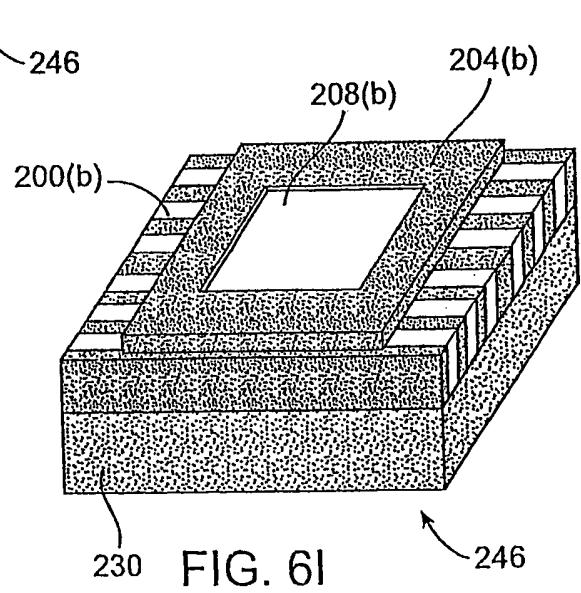

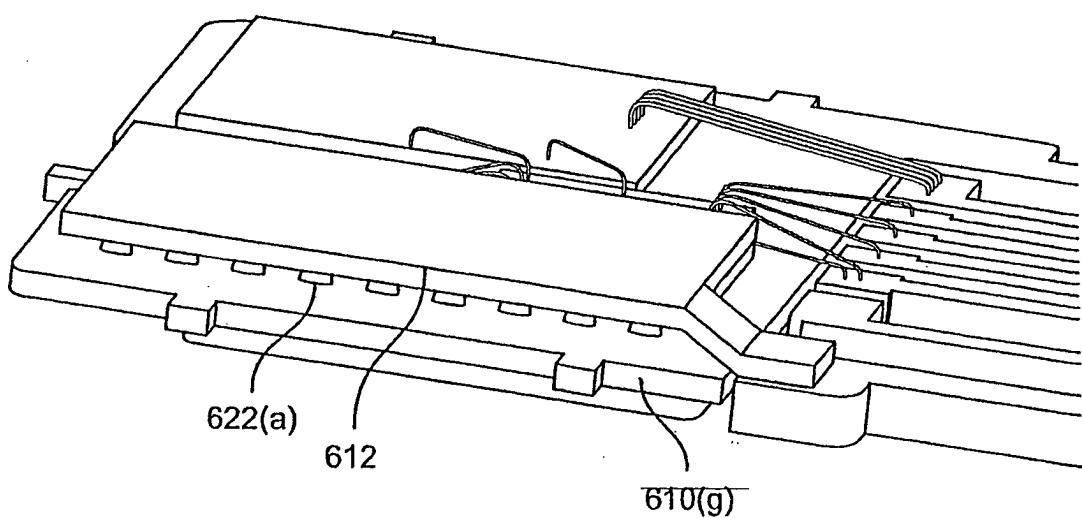

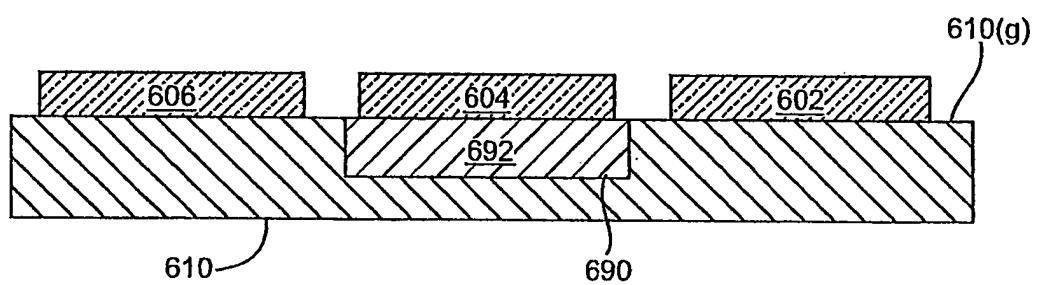

- [0036] [Fig. 6A](#)-[Fig. 6I](#) zeigen perspektivische Ansichten von Chipgehäusen während sie geformt werden.

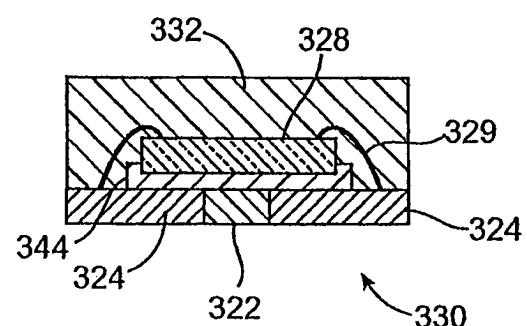

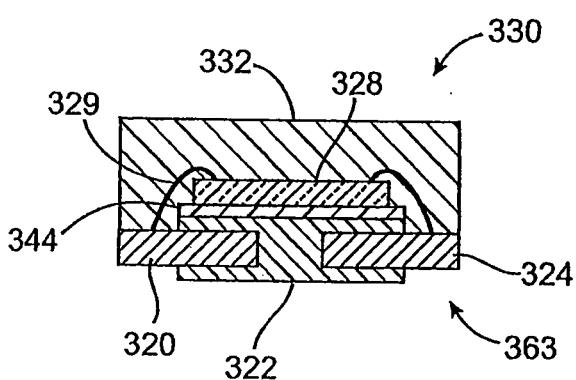

- [0037] [Fig. 7A](#)-[Fig. 7C](#) zeigen Seiten-Querschnitte eines anderen Halbleiterchip-Gehäuses während es geformt wird.

- [0038] [Fig. 7D](#) zeigt eine perspektivische Ansicht eines Halbleiterchip-Gehäuses, geformt mittels des in [Fig. 7A](#)-[Fig. 7C](#) gezeigten Prozesses.

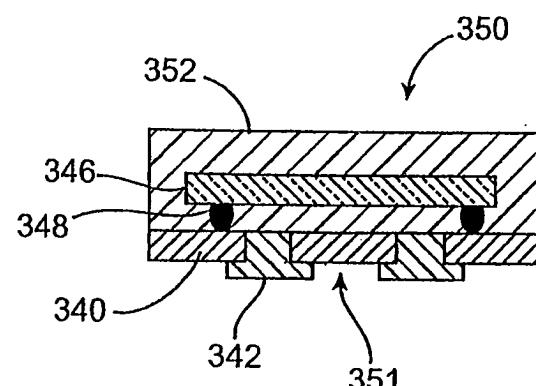

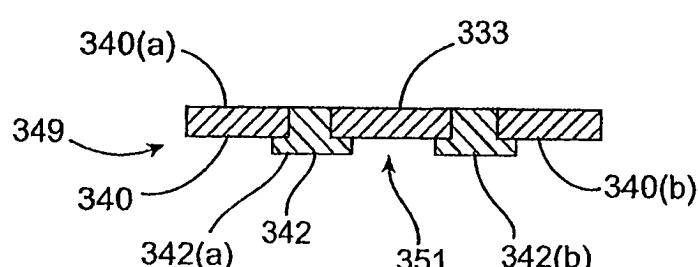

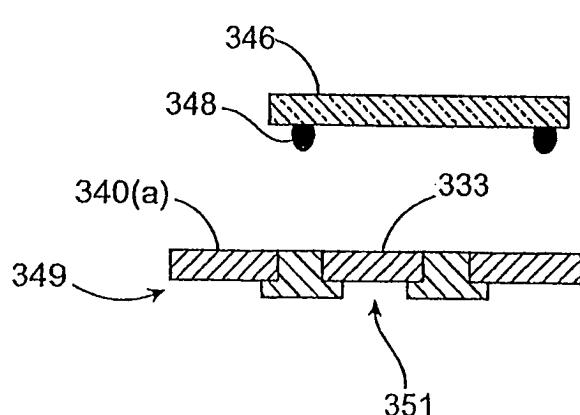

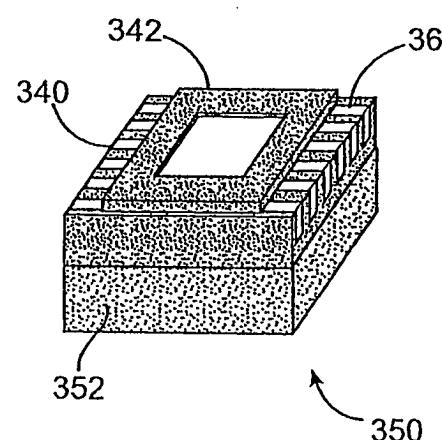

- [0039] [Fig. 8A](#)-[Fig. 8D](#) zeigen Seiten-Querschnitte eines anderen Halbleiterchip-Gehäuses während es geformt wird.

- [0040] [Fig. 8E](#) zeigt eine perspektivische Ansicht des Halbleiterchip-Gehäuses, geformt mittels des in [Fig. 8A](#)-[Fig. 8D](#) gezeigten Prozesses.

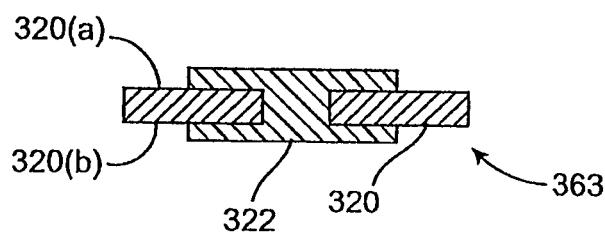

- [0041] [Fig. 9A](#)-[Fig. 9D](#) zeigen Querschnitte eines anderen Halbleiterchip-Gehäuses während es geformt wird.

- [0042] [Fig. 9E](#) zeigt eine perspektivische Ansicht eines anderen Halbleiterchip-Gehäuses gemäß einer Ausführungsform der Erfindung.

- [0043] [Fig. 10A](#)-[Fig. 10D](#) zeigen Querschnitte eines anderen Halbleiterchip-Gehäuses während es geformt wird.

[0044] [Fig. 10E](#) zeigt eine perspektivische Ansicht eines anderen Halbleiterchip-Gehäuses gemäß einer Ausführungsform der Erfindung.

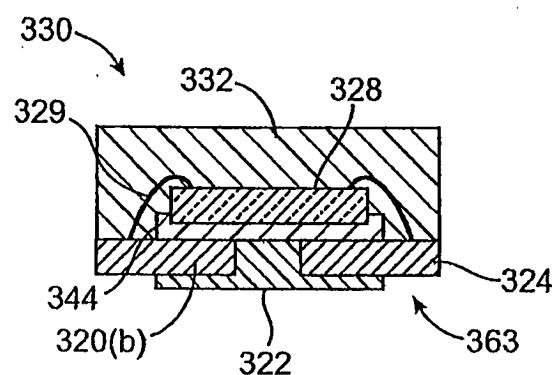

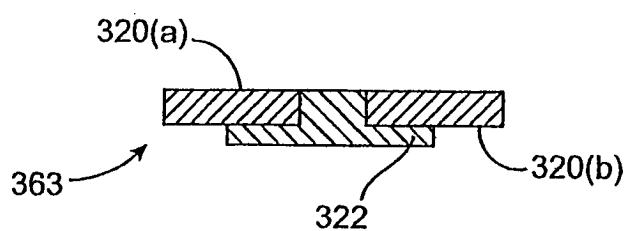

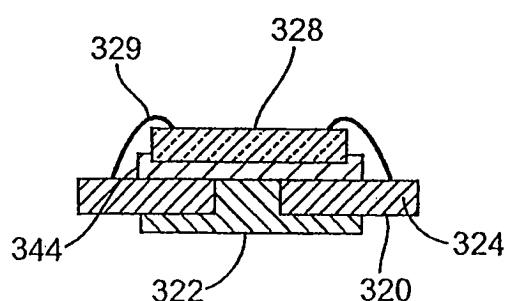

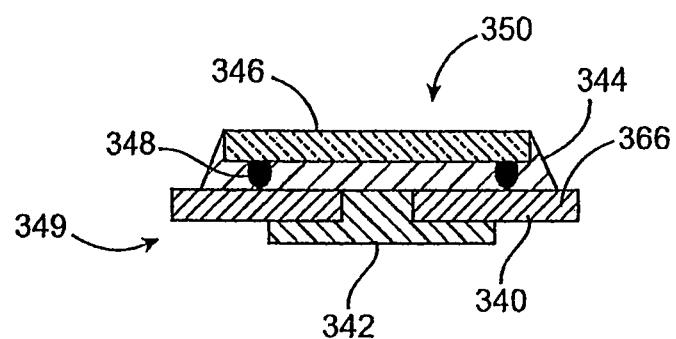

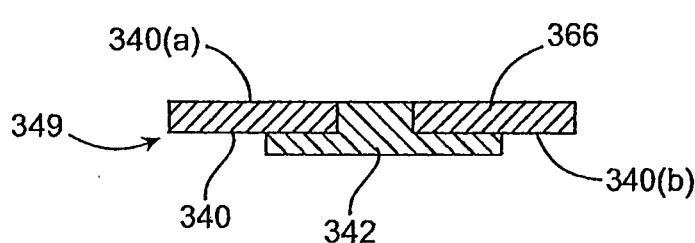

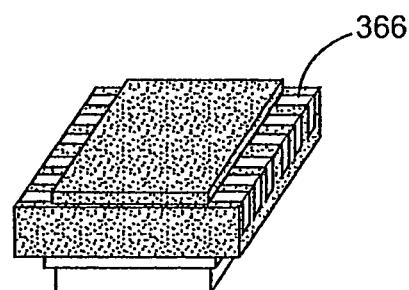

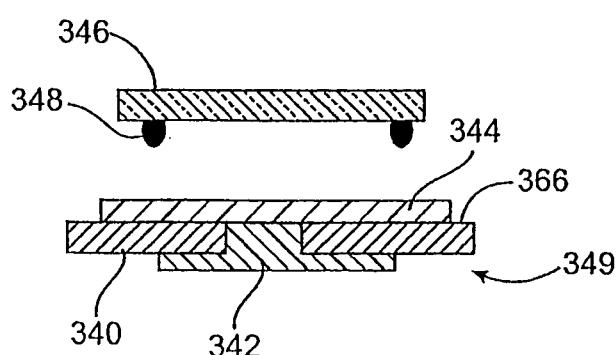

[0045] [Fig. 11A](#)-[Fig. 11D](#) zeigen Querschnitte eines anderen Halbleiterchip-Gehäuses während es geformt wird.

[0046] [Fig. 11E](#) zeigt eine perspektivische Unteransicht auf das Halbleiterchip-Gehäuse.

[0047] [Fig. 12A](#)-[Fig. 12D](#) zeigen Querschnitte eines anderen Halbleiterchip-Gehäuses während es geformt wird.

[0048] [Fig. 12E](#) zeigt eine perspektivische Unteransicht auf das in [Fig. 12D](#) gezeigte Halbleiterchip-Gehäuse.

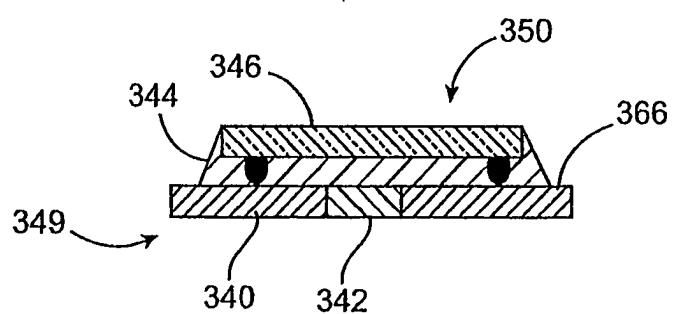

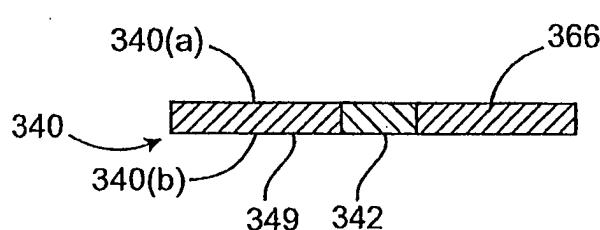

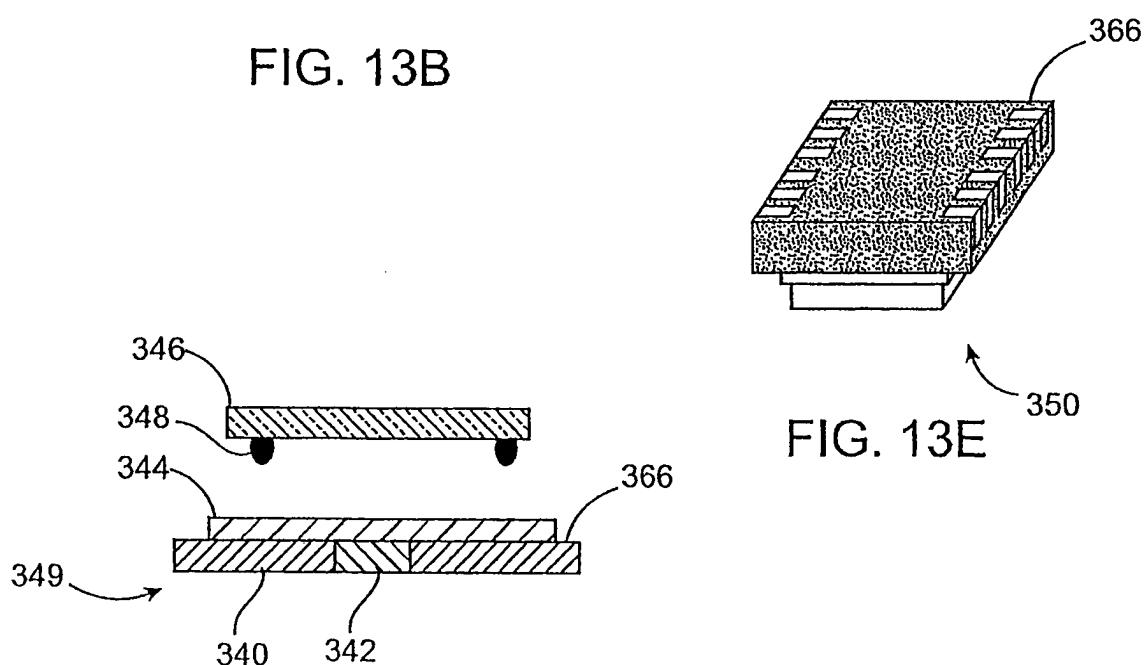

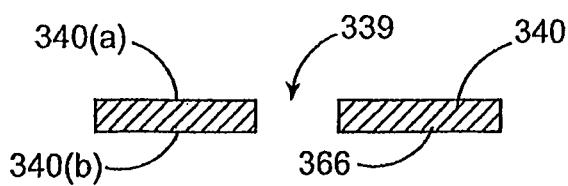

[0049] [Fig. 13A](#)-[Fig. 13D](#) zeigen Querschnitte eines anderen Halbleiterchip-Gehäuses während es geformt wird.

[0050] [Fig. 13E](#) zeigt eine perspektivische Unteransicht des in [Fig. 13D](#) gezeigten Halbleiterchip-Gehäuses.

[0051] [Fig. 14A](#)-[Fig. 14D](#) zeigen Querschnitte eines anderen Halbleiterchip-Gehäuses, während es geformt wird.

[0052] [Fig. 14E](#) zeigt eine perspektivische Ansicht des in [Fig. 14D](#) gezeigten Halbleiterchip-Gehäuses.

[0053] [Fig. 15A](#)-[Fig. 15D](#) zeigen Querschnitte eines anderen Halbleiterchip-Gehäuses, während es geformt wird.

[0054] [Fig. 15E](#) zeigt eine perspektivische Unteransicht des in [Fig. 15D](#) gezeigten Halbleiterchip-Gehäuses.

[0055] [Fig. 16A](#)-[Fig. 16D](#) zeigen Querschnitte eines anderen Halbleiterchip-Gehäuses, während es geformt wird.

[0056] [Fig. 16E](#) zeigt eine perspektivische Unteransicht des in [Fig. 16D](#) gezeigten Halbleiterchip-Gehäuses.

[0057] [Fig. 17A](#)-[Fig. 17D](#) zeigen Querschnitte eines anderen Halbleiterchip-Gehäuses, während es geformt wird.

[0058] [Fig. 17E](#) zeigt eine perspektivische Unteransicht des in [Fig. 17D](#) gezeigten Halbleiterchip-Gehäuses.

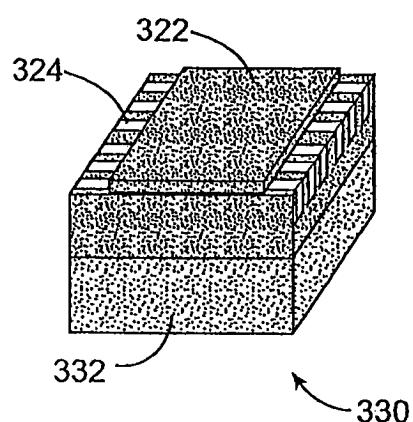

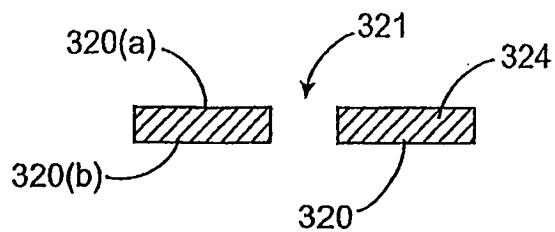

[0059] [Fig. 18A-1](#) ist eine perspektivische Unteransicht einer Leiterrahmen-Struktur.

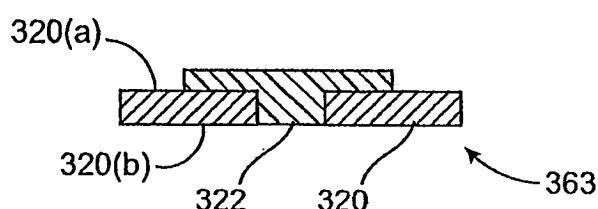

[0060] [Fig. 18A-2](#) ist eine perspektivische Draufsicht einer Leiterrahmen-Struktur, die teilweise geätzt wurde.

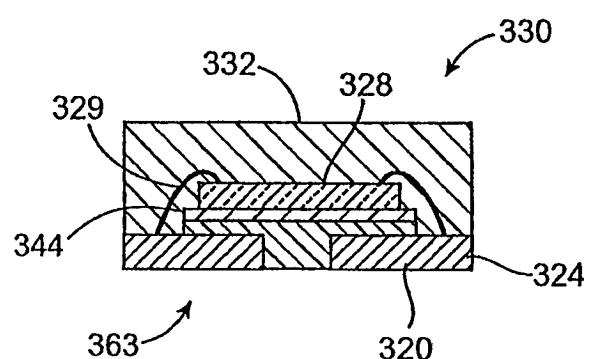

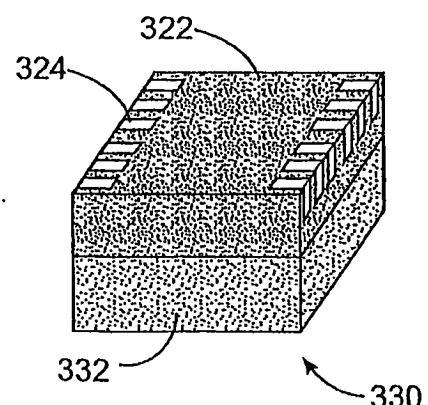

[0061] [Fig. 18B-1](#) ist eine perspektivische Unteransicht eines vorgeformten Substrats.

[0062] [Fig. 18B-2](#) ist eine perspektivische Draufsicht eines vorgeformten Substrats.

[0063] [Fig. 18C](#) ist eine perspektivische Draufsicht eines vorgeformten Substrats mit einem darauf montierten Halbleiterchip.

[0064] [Fig. 18D](#) ist eine perspektivische Draufsicht eines Halbleiterchip-Gehäuses beinhaltend ein vorgeformtes Substrat.

[0065] [Fig. 19A](#) ist eine perspektivische Draufsicht auf ein vorgeformtes Leiterrahmen-Substrat beinhaltend einen darauf montierten Halbleiterchip.

[0066] [Fig. 19B](#) zeigt eine perspektivische Unteransicht des in [Fig. 18A](#) gezeigten vorgeformten Leiterrahmen-Substrats.

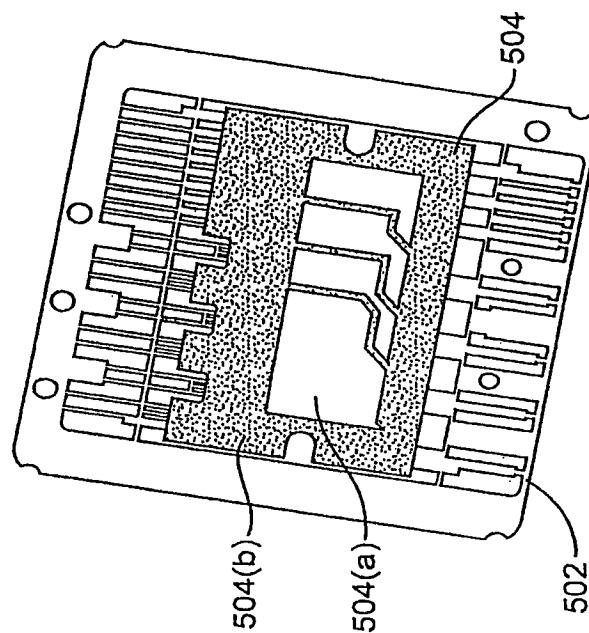

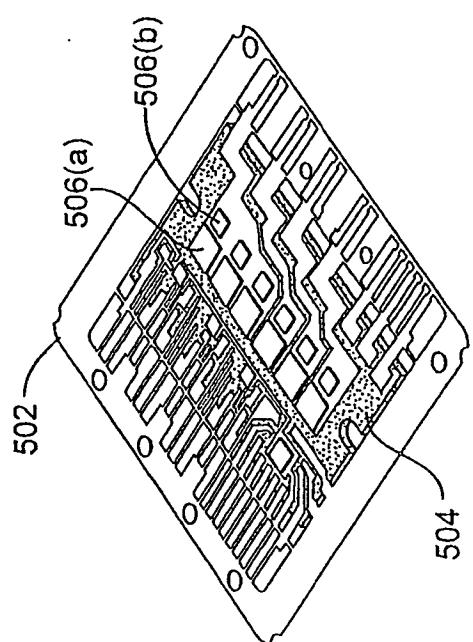

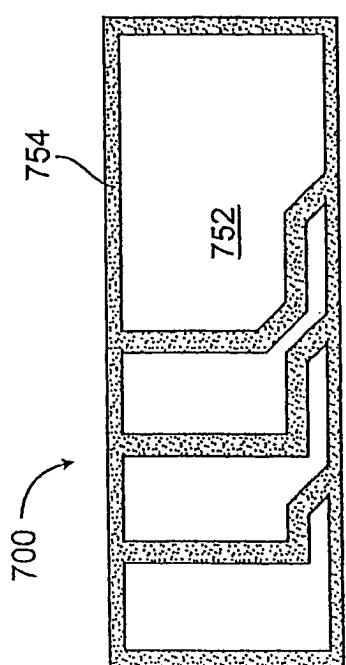

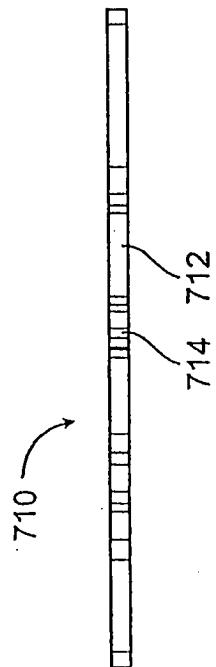

[0067] [Fig. 20A](#) ist eine Draufsicht auf ein vorgeformtes Substrat gemäß einer Ausführungsform der Erfindung.

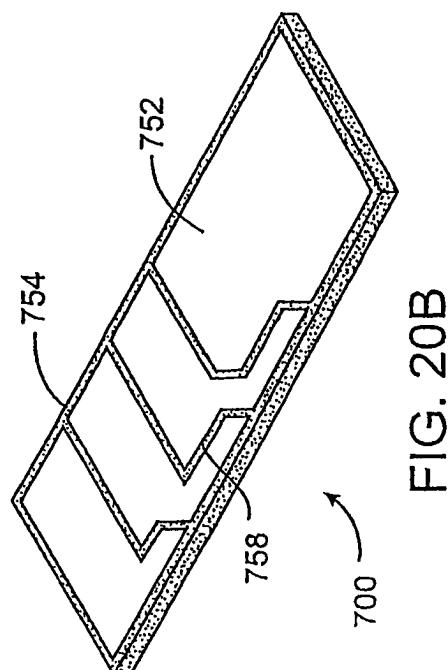

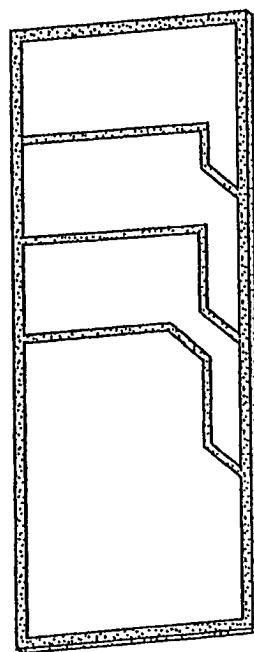

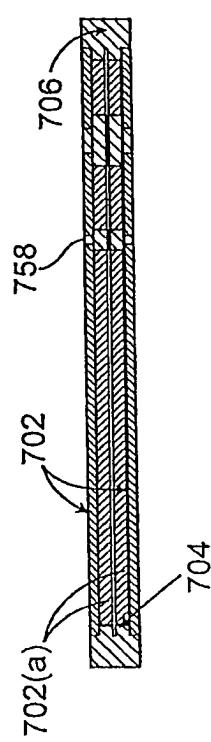

[0068] [Fig. 20B](#) zeigt eine perspektivische Draufsicht auf ein vorgeformtes Substrat gemäß einer Ausführungsform der Erfindung.

[0069] [Fig. 20C](#) zeigt eine quergeschnittene Seitenansicht eines vorgeformten Substrats gemäß einer Ausführungsform der Erfindung.

[0070] [Fig. 20D](#) zeigt eine perspektivische Unteransicht eines vorgeformten Substrats gemäß einer Ausführungsform der Erfindung.

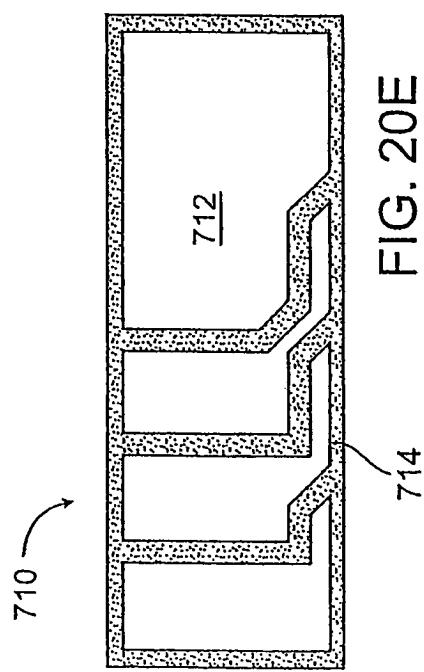

[0071] [Fig. 20E](#) zeigt eine Draufsicht auf ein vorgeformtes Substrat gemäß einer Ausführungsform der Erfindung.

[0072] [Fig. 20F](#) zeigt eine quergeschnittene Seitenansicht eines vorgeformten Substrats gemäß einer Ausführungsform der Erfindung.

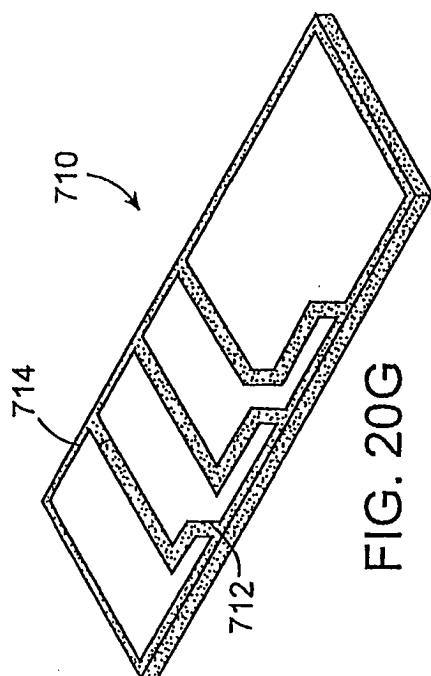

[0073] [Fig. 20G](#) ist eine perspektivische Draufsicht auf ein vorgeformtes Substrat gemäß einer Ausführungsform der Erfindung.

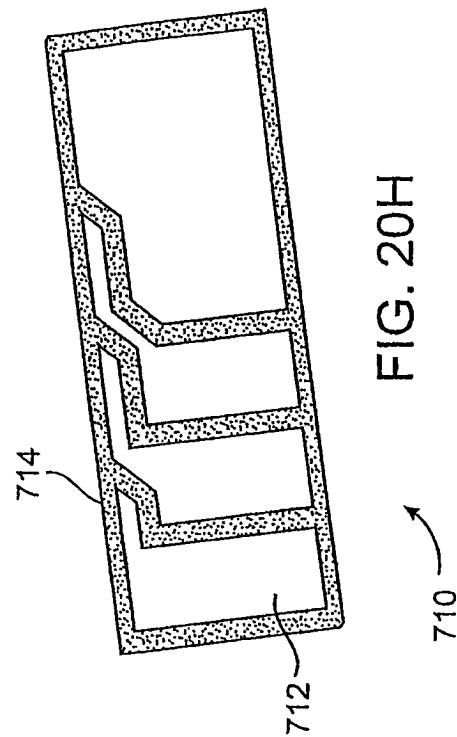

[0074] [Fig. 20H](#) ist eine perspektivische Unteransicht auf ein vorgeformtes Substrat gemäß einer Ausführungsform der Erfindung.

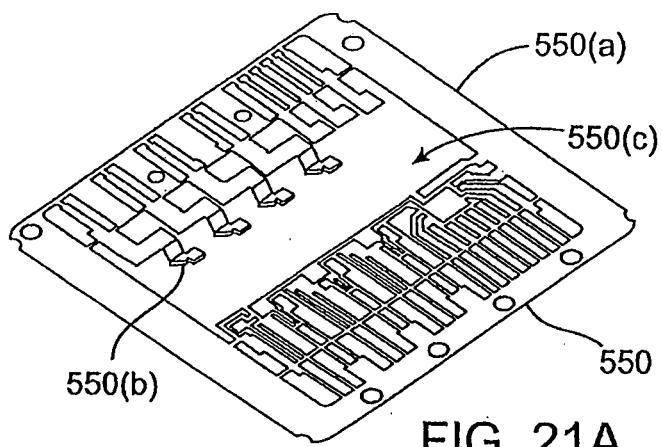

[0075] [Fig. 21A](#) ist eine perspektivische Draufsicht auf eine Rahmenstruktur.

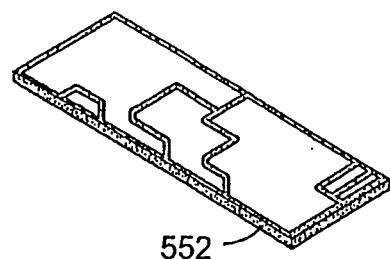

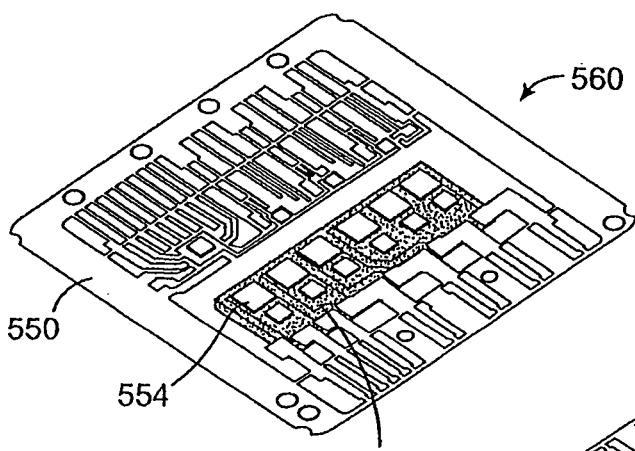

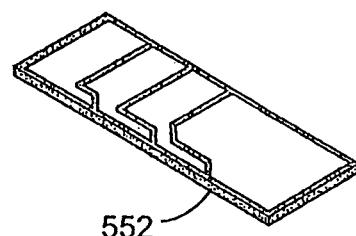

[0076] [Fig. 21B](#)-[Fig. 21C](#) sind perspektivische Ansichten von vorgeformten Substraten gemäß Ausführungsformen der Erfindung.

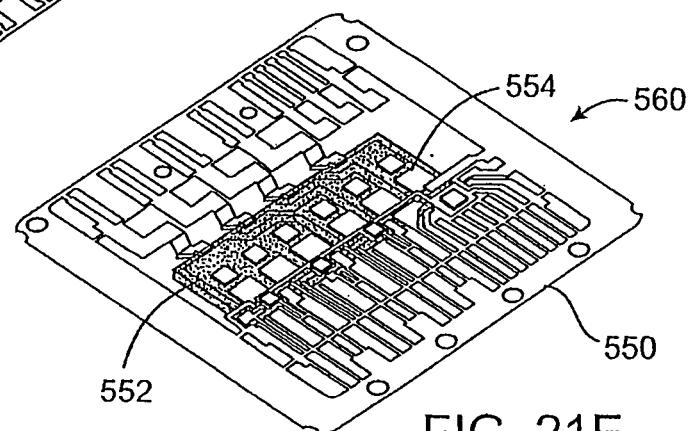

[0077] [Fig. 21D](#) und [Fig. 21E](#) zeigen perspektivische Draufsichten auf in Rahmen montierte vorgeformte Substraten. Halbleiterchips sind auf den vorgeformten Substraten montiert.

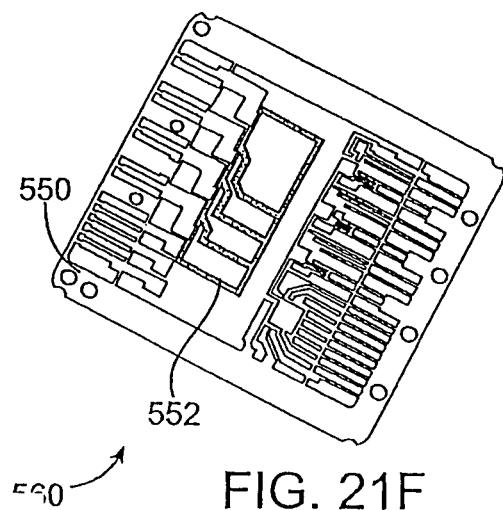

[0078] [Fig. 21F](#) zeigt eine perspektivische Unteransicht eines vorgeformten, in einem Rahmen montierten Substrats.

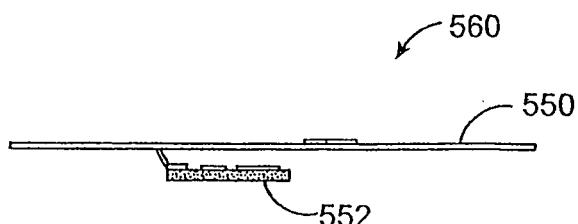

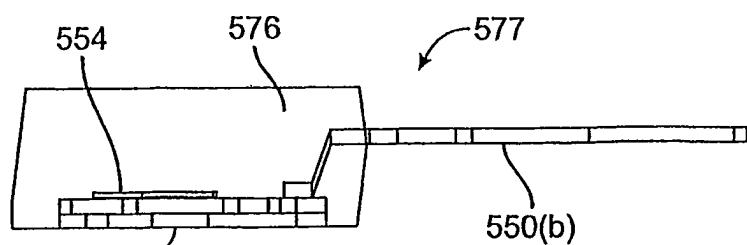

[0079] [Fig. 21G](#) zeigt eine Seitenansicht eines vorgeformten, an einem Rahmen montierten Substrats.

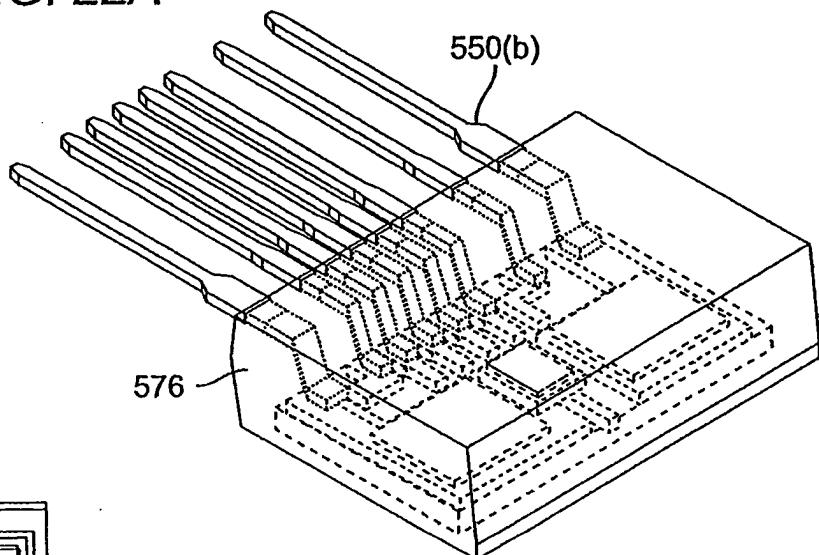

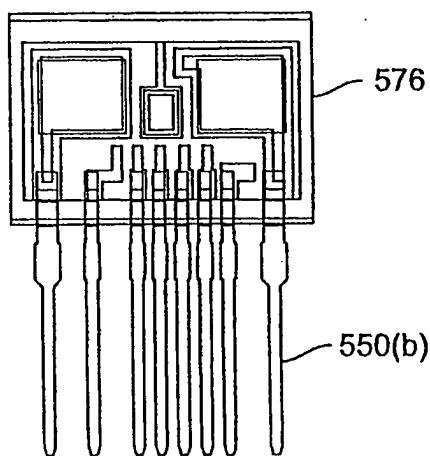

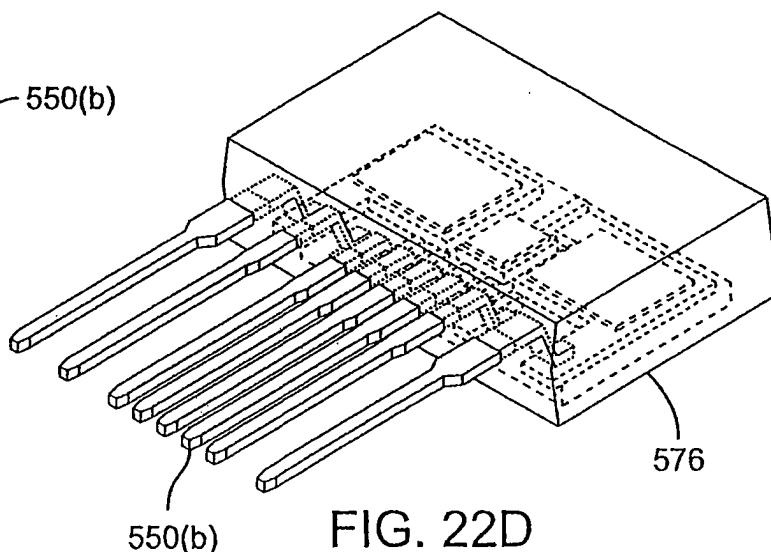

[0080] [Fig. 22A](#)-[Fig. 22D](#) zeigen jeweils Seiten-Querschnitte, perspektivische Rückansichten, Draufsichten und perspektivische Vorderansichten eines geformten Chipgehäuses gemäß einer Ausführungsform der Erfindung.

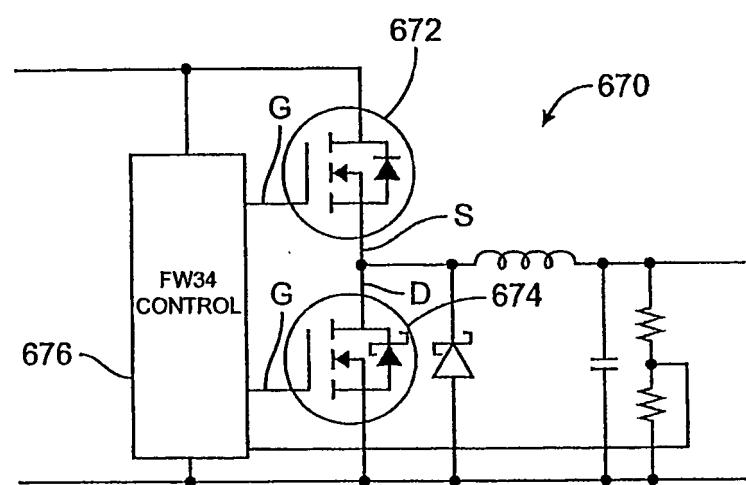

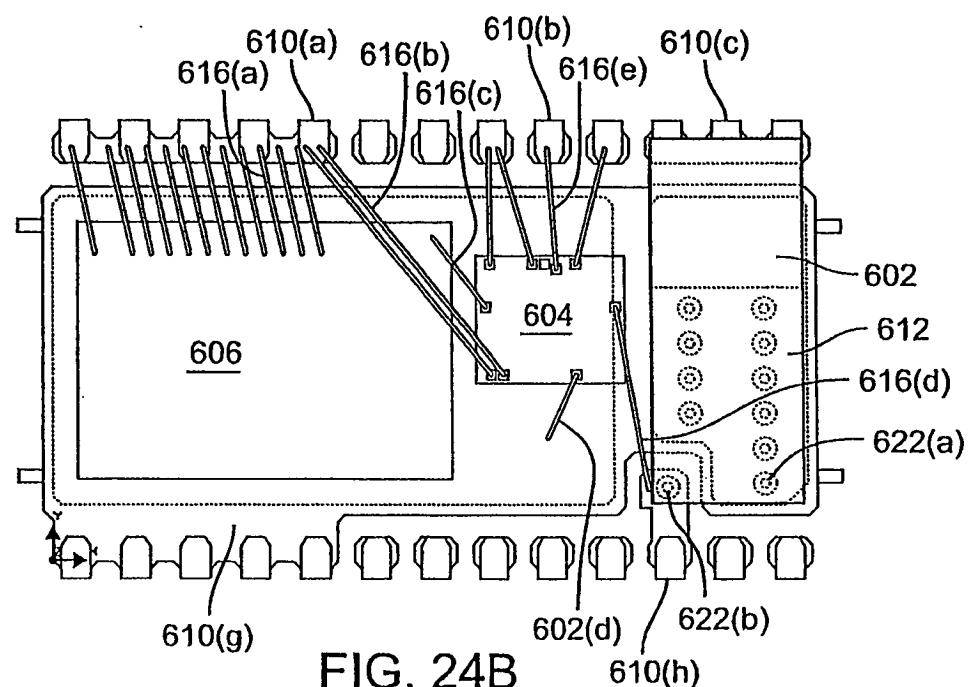

[0081] [Fig. 23](#) ist ein Schaltdiagramm für einen synchronen Abwärtswandler (buck-converter), der dem in [Fig. 24C](#) gezeigten Gehäuse entspricht.

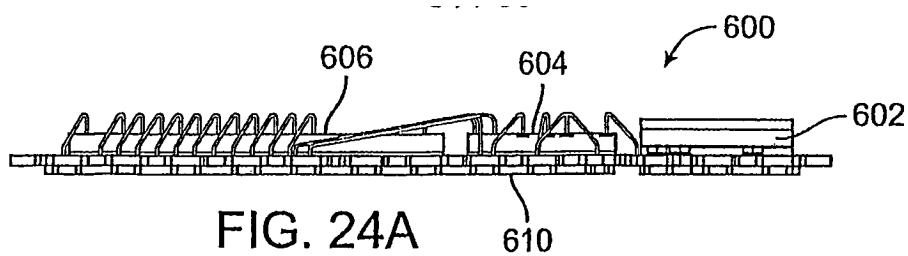

[0082] [Fig. 24A](#) zeigt eine Seitenansicht eines Halbleiterchip-Gehäuses entsprechend einer Ausführungsform der Erfindung.

[0083] [Fig. 24B](#) zeigt eine Draufsicht auf ein Halbleiterchip-Gehäuse gemäß einer Ausführungsform der Erfindung.

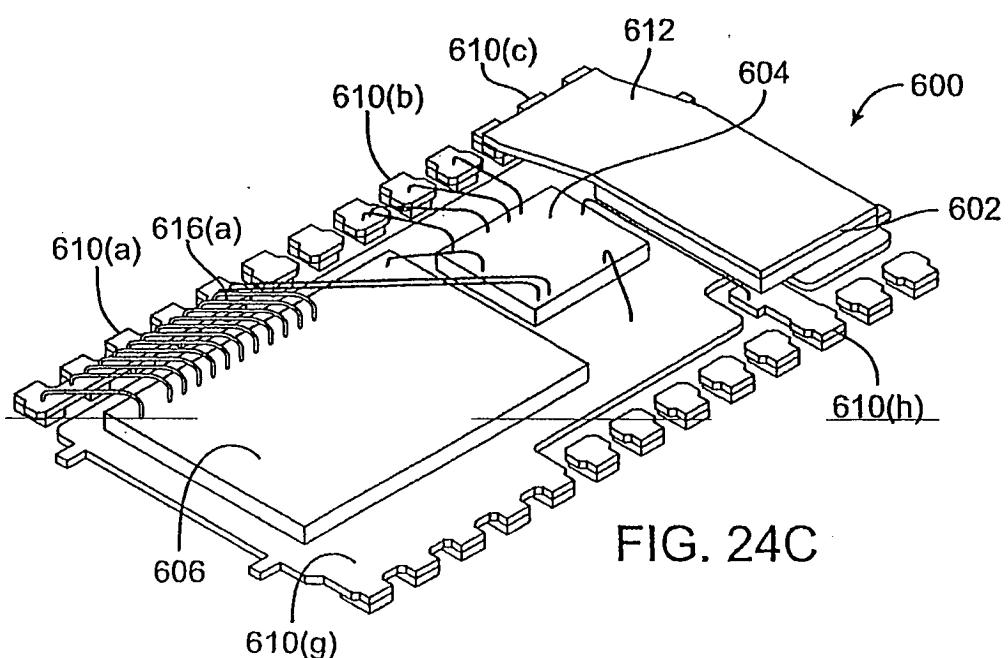

[0084] [Fig. 24C](#) zeigt eine perspektivische Ansicht eines Halbleiterchip-Gehäuses gemäß einer Ausführungsform der Erfindung.

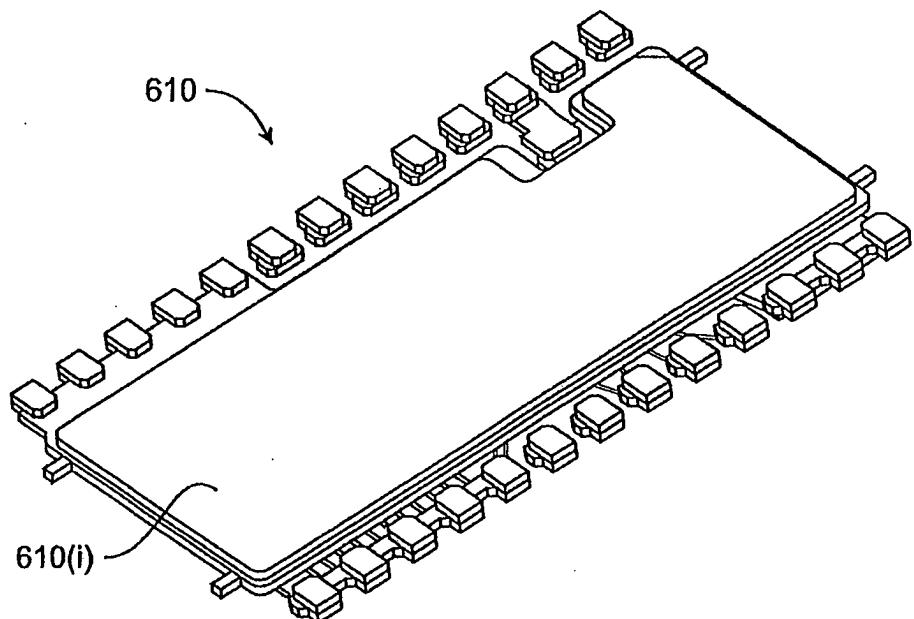

[0085] [Fig. 24D](#) zeigt eine perspektivische Unteransicht einer Leiterrahmen-Struktur.

[0086] [Fig. 24E](#) ist eine perspektivische Seitenansicht eines Halbleiterchip-Gehäuses gemäß einer Ausführungsform der Erfindung.

[0087] [Fig. 25](#) zeigt eine Seitenansicht einer anderen Ausführungsform der Erfindung. In dieser Ausführungsform ist ein Formmaterial in einem Leiterrahmen abgelegt und isoliert einen Chip von leitenden Gebieten auf der Leiterrahmen-Struktur.

## DETAILLIERTE BESCHREIBUNG

**[0088]** Ausführungsformen der Erfindung sind auf Halbleiterchip-Gehäuse und Verfahren zur Herstellung von Halbleiterchip-Gehäusen gerichtet.

**[0089]** Ein Halbleiterchip-Gehäuse gemäß einer Ausführungsform der Erfindung beinhaltet ein Substrat und einen auf dem Substrat montierten Halbleiterchip. Der Halbleiterchip kann an dem Substrat mittels eines Klebstoffs oder beliebigen anderen geeigneten Verbindungsmedium befestigt sein. In dem Halbleiterchip-Gehäuse kann die untere Oberfläche und/oder die obere Oberfläche des Halbleiterchips elektrisch zu leitenden Gebieten des Substrats gekoppelt sein. Ein Einkapsel-Material kann den Halbleiterchip einkapseln. Wie im Folgenden detaillierter beschrieben wird, kann das Substrat gemäß Ausführungsformen der Erfindung verschiedene Konfigurationen in verschiedenen Ausführungsformen haben.

**[0090]** Das Substrat kann jegliche geeignete Konfiguration haben. In bevorzugten Ausführungsformen der Erfindung jedoch beinhaltet das Substrat eine Leiterrahmen-Struktur und ein Formmaterial. Üblicherweise ist zumindest eine Oberfläche der Leiterrahmen-Struktur im Wesentlichen planparallel mit einer äußeren Oberfläche des Formmaterials. In einigen Ausführungsformen sind beide gegenüberliegenden Hauptoberflächen der Leiterrahmen-Struktur im Wesentlichen planparallel mit gegenüberliegenden äußeren Oberflächen des Formmaterials in dem Substrat. In anderen Ausführungsformen ist nur eine Hauptoberfläche der Leiterrahmen-Struktur im Wesentlichen planparallel mit einer äußeren Oberfläche des Formmaterials.

**[0091]** Der Begriff "Leiterrahmen-Struktur" kann sich auf eine Struktur beziehen, die von einem Leiterrahmen abgeleitet ist. Leiterrahmen-Strukturen können beispielsweise durch bekannte Stanzprozesse geformt werden. Eine beispielhafte Leiterrahmen-Struktur kann auch durch Ätzen eines kontinuierlich leitenden Blechs, um ein vorbestimmtes Muster zu formen, geformt werden. Daher kann in Ausführungsformen der Erfindung die Leiterrahmen-Struktur in einem Halbleiterchip-Gehäuse eine kontinuierliche metallische Struktur oder eine diskontinuierliche metallische Struktur sein.

**[0092]** Eine Leiterrahmen-Struktur gemäß einer Ausführungsform der Erfindung kann ursprünglich eine von vielen Leiterrahmen-Strukturen in einer Anordnung von Leiterrahmen-Strukturen, die miteinander durch Stege verbunden sind, sein. Während des Herstellungsprozesses eines Halbleiterchip-Gehäuses, kann die Leiterrahmen-Struktur-Anordnung getrennt werden, um einzelne Leiterrahmen-Strukturen voneinander zu trennen. Als ein Ergebnis dieser Trennung, können Teilbereiche einer Leiterrahmen-Struktur (solche wie ein Source-Leiter und ein Gate-Leiter) in einem endgültigen Halbleiterchip-Gehäuse elektrisch und mechanisch voneinander entkoppelt sein. In anderen Ausführungsformen wird eine Anordnung von Leiterrahmen-Strukturen nicht verwendet, wenn Halbleiterchip-Gehäuse gemäß Ausführungsformen der Erfindung hergestellt werden.

**[0093]** Eine Leiterrahmen-Struktur gemäß einer Ausführungsform der Erfindung kann jegliches geeignete Material umfassen, kann jegliche geeignete Form haben und kann jegliche geeignete Dicke haben. Exemplarische Leiterrahmen-Struktur-Materialien beinhalten Metalle wie Kupfer, Aluminium, Gold etc. und Legierungen daraus. Die Leiterrahmen-Strukturen können auch beschichtete Schichten wie beschichtete Gold-, Chrom-, Silber-, Palladium-, Nickel-Schichten etc. beinhalten.

**[0094]** Eine Leiterrahmenstruktur gemäß einer Ausführungsform der Erfindung kann auch jegliche geeignete Konfiguration haben. Beispielsweise kann die Leiterrahmen-Struktur auch jegliche geeignete Dicke aufweisen, beinhaltend eine Dicke von weniger als etwa 1 mm (z.B. weniger als etwa 0,5 mm). Zusätzlich kann die Leiterrahmen-Struktur ein Chip-Befestigungsgebiet haben, das ein Chip-Anschluss-Feld (Die Attach Pad DAP) ausbildet kann. Leiter können sich seitlich weg von dem Chip-Befestigungs-Gebiet erstrecken. Sie können auch Oberflächen haben, die planparallel und/oder nicht planparallel sind mit der Oberfläche, die das Chip-Befestigungs-Gebiet formt. Beispielsweise können die Leiter in einigen Beispielen abwärts gebogen sein in Bezug auf das Chip-Befestigungs-Gebiet.

**[0095]** Wenn sich die Leiter der Leiterrahmen-Struktur nicht seitlich über das Formmaterial hinaus erstrecken, kann das Substrat als ein "leiterloses" Substrat angesehen werden und ein Gehäuse beinhaltend das Substrat könnte als ein "leiterloses" Gehäuse angesehen werden. Wenn die Leiter der Leiterrahmen-Strukturen sich über das Formmaterial hinaus erstrecken, dann kann das Substrat ein "Leiter-Substrat" und das Gehäuse ein "Leiter-Gehäuse" sein.

**[0096]** Das Formmaterial, das in dem Substrat verwendet wird, kann jegliches geeignete Material umfassen. Geeignete Formmaterialien beinhalten biphenylbasierte Materialien und multifunktionale vernetzte Epoxid-

harzverbundmaterialien. Geeignete Formmaterialien werden in flüssiger oder halbfester Form auf einer Leiterrahmen-Struktur aufgeschichtet und werden anschließend ausgehärtet, um sie zu verfestigen.

**[0097]** Der Halbleiterchip, der auf dem Substrat montiert ist, kann jegliches geeignete Halbleiterbauelement beinhalten. Geeignete Bauelemente können vertikale oder horizontale Bauelemente beinhalten. Vertikale Bauelemente haben zumindest einen Eingang auf einer Seite des Chips und einen Ausgang auf der anderen Seite des Chips, so dass Strom vertikal durch den Chip fließen kann. Horizontale Bauelemente beinhalten zumindest einen Eingang auf einer Seite des Chips und einen Ausgang auf derselben Seite des Chips, so dass Strom horizontal durch den Chip fließt. Exemplarische Halbleiterbauelemente werden auch in der US-Patentanmeldung Nr. 11/026,276, angemeldet am 29. Dezember 2004, beschrieben, die hierin in ihrer Gesamtheit für alle Zwecke durch Bezugnahme eingeschlossen wird.

**[0098]** Vertikale Leistungs-Transistoren beinhalten VDMOS-Transistoren und vertikale bipolare Transistoren. Ein VDMOS-Transistor ist ein MOSFET, der zwei oder mehr Halbleitergebiete hat, die durch Diffusion geformt sind. Er hat ein Source-Gebiet, ein Drain-Gebiet und ein Gate. Das Bauelement ist vertikal, indem sich das Source-Gebiet und das Drain-Gebiet auf gegenüberliegenden Oberflächen des Halbleiterchips befinden. Das Gate kann eine vergrabene Gate-Struktur oder eine ebene Gate-Struktur sein und ist auf derselben Oberfläche wie das Source-Gebiet ausgebildet. Vergrabene Gate-Strukturen sind bevorzugt, da gegrabene Gate-Strukturen schmäler sind und weniger Raum beanspruchen als ebene Gate-Strukturen. Im Betrieb ist der Stromfluss von dem Source-Gebiet zu dem Drain-Gebiet in einem VDMOS-Bauelement im Wesentlichen rechtwinklig zu den Chipoberflächen.

**[0099]** Ein Einkapsel-Material kann verwendet werden, um den Halbleiterchip einzukapseln. Das Einkapsel-Material kann denselben oder einen anderen Typ von Material wie das vorher beschriebene Formmaterial umfassen. In einigen Ausführungsformen bedeckt oder zumindest teilweise bedeckt das Einkapsel-Material das Substrat und ein oder mehrere Halbleiterchips auf dem Substrat. Das Einkapsel-Material kann verwendet werden, um den einen oder mehrere Halbleiterchips vor möglichen Beschädigungen aufgrund der Aussetzung der umliegenden Umgebung zu schützen.

**[0100]** Jeglicher geeignete Prozess kann verwendet werden, um den/die Halbleiterchip(s) und/oder das Substrat, das den/die Halbleiterchip(s) stützt, einzukapseln. Beispielsweise können ein Halbleiterchip und ein Substrat in einer Ausformform platziert werden und ein Einkapsel-Material kann um zumindest einen Teil des Halbleiterchips und/oder des Substrats geformt werden. Spezifische Formbedingungen sind dem Durchschnittsfachmann bekannt.

#### I. Chip-Gehäuse beinhaltend Substrate mit getrennten Isolations-Gebieten

**[0101]** Während die charakteristischen Größen von Mikroleiter-Gehäuse-(Microlead Package MLP)-Komponenten kleiner und kleiner werden, sind die Designs durch Metall-zu-Metall-Abstände und der Leistungsfähigkeit von Maßtolleranzen geätzter und halb-geätzter Rahmentechnologie begrenzt. Ausführungsformen der Erfindung offenbaren ein vorgeformtes Rahmen-Layout, das in der Lage ist, Doppelreihen für bloßgelegte Felder aufzunehmen. Ein Doppelreihen-MLP hat eine kleinere Gehäusegröße im Vergleich zu einem Einreihen-MLP für dieselbe Anzahl von Leitern. In Ausführungsformen der Erfindung wird eine Leiterrahmen-Struktur vorgeformt und dann gesägt, um zwei leitende Felder zu isolieren.

**[0102]** Eine Ausführungsform der Erfindung ist auf ein Verfahren gerichtet, das Bereitstellen eines vorgeformten Substrats beinhaltend eine Leiterrahmen-Struktur und ein Formmaterial beinhaltet, wobei die Leiterrahmen-Struktur einen ersten leitenden Teilbereich, einen zweiten leitenden Teilbereich und einen Zwischen-Teilbereich zwischen dem ersten leitenden Teilbereich und dem zweiten leitenden Teilbereich beinhaltet. Das Formmaterial in dem Substrat kann eine Dicke haben, die im Wesentlichen gleich einer Dicke der Leiterrahmen-Struktur ist. Beispielsweise kann die Dicke des Formmaterials im Wesentlichen gleich der Dicke des ersten leitenden Teilbereichs und/oder des zweiten leitenden Teilbereichs sein.

**[0103]** Der Zwischen-Teilbereich wird dann getrennt, um den ersten leitenden Teilbereich von dem zweiten leitenden Teilbereich elektrisch zu isolieren. Die ersten und zweiten leitenden Teilbereiche können unterschiedliche Anschlüsse in einem Chip-Gehäuse darstellen. Beispielsweise können die ersten und zweiten leitenden Teilbereiche aus der Gruppe bestehend aus einem Gate-Leiter, einem Source-Leiter und einem Drain-Leiter, ausgewählt sein, wobei die ersten und zweiten leitenden Teilbereiche unterschiedlich sind. Eine Vielzahl von ersten und zweiten leitenden Teilbereichen kann Reihen von leitenden Teilbereichen formen.

[0104] Nach dem Trennen der Leiterrahmen-Struktur wird zumindest ein Halbleiterchip an dem Substrat befestigt. Ein geeigneter Klebstoff oder Lot kann verwendet werden, um den Halbleiterchip an dem Substrat zu befestigen. Der Halbleiterchip kann von dem oben beschriebenen Typ sein. Beispielsweise kann die Leiterrahmen-Struktur ein Halbleiterchip umfassend einen Leistungs-MOSFET sein.

[0105] Nachdem der Halbleiterchip an dem Substrat befestigt ist, kann der Halbleiterchip elektrisch zu den ersten und den zweiten leitenden Teilbereichen gekoppelt werden. Beispielsweise können der Halbleiterchip und die ersten und zweiten leitenden Teilbereiche über Drähte miteinander verbunden sein. Alternativ können leitende Klemmen verwendet werden, um den Halbleiterchip zu den ersten und zweiten leitenden Teilbereichen zu koppeln.

[0106] Nachdem der Halbleiterchip elektrisch zu den ersten und zweiten leitenden Teilbereichen in dem vorgeformten Substrat gekoppelt ist, kann ein Einkapsel-Material über dem Halbleiterchip aufgeschichtet werden, um ihn einzukapseln. Das Einkapsel-Material kann vom gleichen oder einem unterschiedlichen Materialtyp sein wie das oben beschriebene Formmaterial.

[0107] Das geformte Halbleiterchip-Gehäuse kann Leiter aufweisen, die sich nicht über eine äußere Oberfläche des Formmaterials hinaus erstrecken. In einigen Ausführungsformen kann das Halbleiterchip-Gehäuse als "Mikroleiter-Gehäuse" oder MLP-Gehäuse bezeichnet werden.

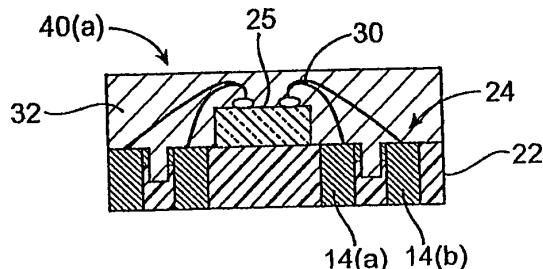

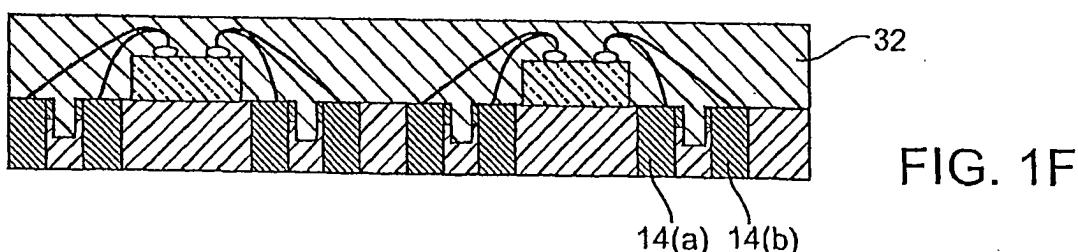

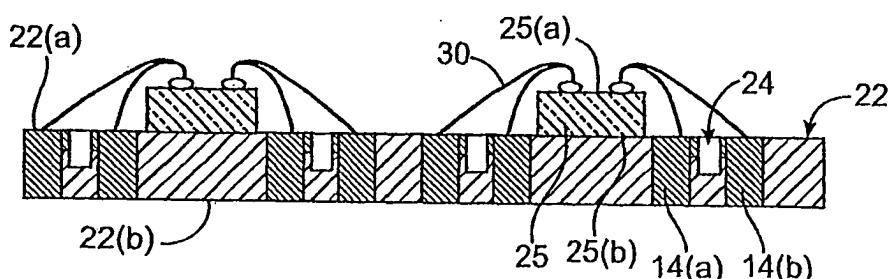

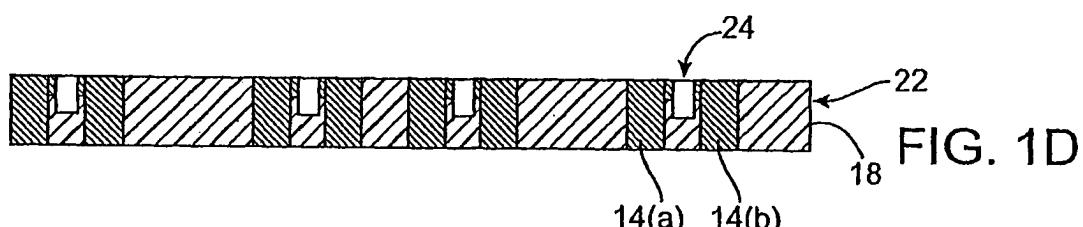

[0108] Beispielhafte Verfahren und Chipgehäuse können mit Bezug auf die [Fig. 1A](#)-[Fig. 1L](#) beschrieben werden.

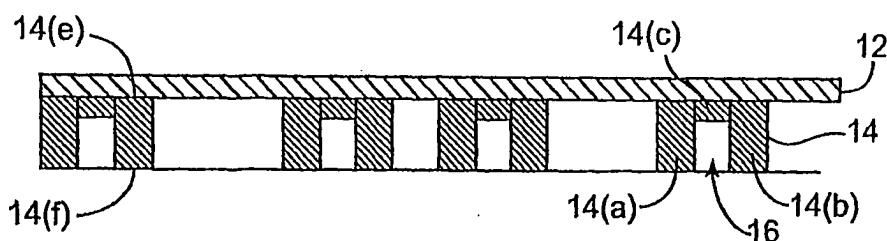

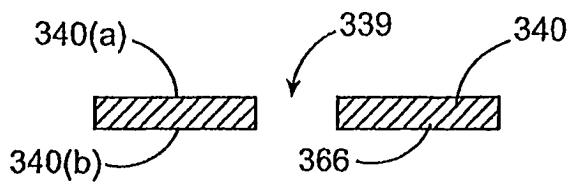

[0109] [Fig. 1A](#) zeigt eine Leiterrahmen-Struktur **14** gemäß einer Ausführungsform der Erfindung. Die Leiterrahmen-Struktur **14** in diesem Beispiel weist kein Chip-Anschluss-Feld (Die Attach Pad DAP) auf. Wie weiter unten beschrieben wird, wird das Substrat, das die Leiterrahmen-Struktur **14** beinhaltet, ein Chip-Befestigungs-Gebiet haben, das aus dem Formmaterial geformt ist. Die Leiterrahmen-Struktur **14** hat eine erste Oberfläche **14(e)** die einer zweiten Oberfläche **14(f)** der Leiterrahmen-Struktur **14** gegenüberliegt.

[0110] Die Leiterrahmen-Struktur **14** beinhaltet einen ersten leitenden Teilbereich **14(a)**, einen zweiten leitenden Teilbereich **14(b)**, und einen Zwischen-Teilbereich **14(c)** zwischen dem ersten leitenden Teilbereich **14(a)** und dem zweiten leitenden Teilbereich **14(b)**. Wie dargestellt sind die Dicken der ersten und zweiten leitenden Teilbereiche **14(a)**, **14(b)** im Wesentlichen gleich, doch die Dicke des Zwischen-Teilbereichs **14(c)** ist geringer als die Dicken der ersten und zweiten leitenden Teilbereiche **14(a)**, **14(b)**. Als eine Folge dieser unterschiedlichen Dicken, ist eine Aussparung **16** definiert durch den ersten leitenden Teilbereich **14(a)**, den zweiten leitenden Teilbereich **14(b)** und den Zwischen-Teilbereich **14(c)**.

[0111] Die Leiterrahmen-Struktur **14** kann mittels jeglichen geeigneten Prozesses geformt werden. Beispielsweise kann die Leiterrahmen-Struktur **14** mittels Fotolack- und Ätzverfahren oder Prägeverfahren geformt werden. Diese Verfahren und andere Verfahren sind dem Durchschnittsfachmann bekannt. Beispielsweise kann die in [Fig. 1A](#) gezeigte Aussparung **16** unter Verwendung bekannter Fotolithografie- und Ätzverfahren geformt werden. In einem beispielhaften Fotolithografie- und Ätzprozess kann eine Rohmetall-Struktur (nicht gezeigt) mit einer Schicht Fotolack überzogen werden. Diese Fotolackschicht kann belichtet und entwickelt werden. Belichtete Gebiete der Metallstruktur können mittels eines nassen oder trockenen Ätzprozesses geätzt werden. Die Aussparung **16** kann mittels eines nassen oder trockenen Ätzprozesses geformt werden.

[0112] Wie in [Fig. 1A](#) gezeigt, kann, nachdem die Leiterrahmen-Struktur **14** geformt ist, ein Stück Band **12** an der ersten Oberfläche **14(e)** der Leiterrahmen-Struktur **14** befestigt werden. Das Stück Band **12** bedeckt die erste Oberfläche **14(e)** der Leiterrahmen-Struktur **14**, so dass das Formmaterial, das verwendet wird, um das Substrat zu formen, nicht die erste Oberfläche **14(e)** bedeckt.

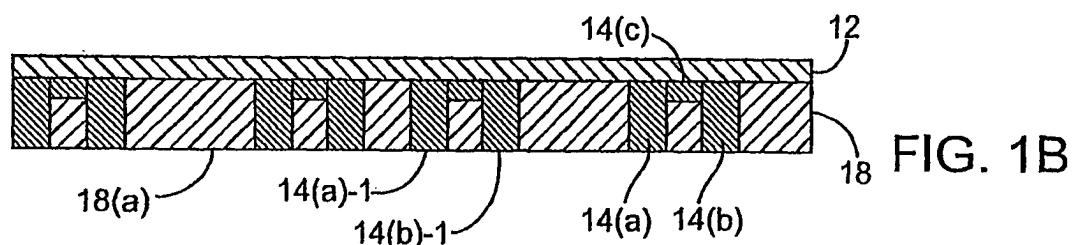

[0113] Wie in [Fig. 1B](#) gezeigt, kann, nachdem das Band **12** an der ersten Oberfläche **14(e)** der Leiterrahmen-Struktur **14** befestigt ist, ein Formmaterial **18**, wie ein Epoxid-Formmaterial, auf der Leiterrahmen-Struktur **14** aufgeschichtet und verfestigt werden. Das Formmaterial **18** füllt die Aussparung **16** der Leiterrahmen-Struktur **14** und die Fugen zwischen den verschiedenen ersten und zweiten leitenden Teilbereichen **14(a)**, **14(b)**. Überschüssiges Formmaterial kann entfernt werden, so dass die zweite Oberfläche **14(f)** nicht mit dem Formmaterial bedeckt ist. Das Gebiet zwischen den ersten und zweiten Oberflächen **14(e)**, **14(f)** der Leiterrahmen-Struktur **14** jedoch ist in diesem Beispiel mit dem Formmaterial **18** gefüllt.

[0114] Wie in [Fig. 1B](#) gezeigt, kann eine äußere Oberfläche **18(a)** des Formmaterials **18** im Wesentlichen

planparallel mit äußereren Oberflächen **14(a)-1**, **14(b)-1** der ersten und zweiten leitenden Teilbereiche **14(a)**, **14(b)** sein. Wie gezeigt ist die Dicke des Formmaterials **18** an bestimmten Stellen im Wesentlichen gleich der Dicke der ersten und zweiten leitenden Teilbereiche **14(a)**, **14(b)**.

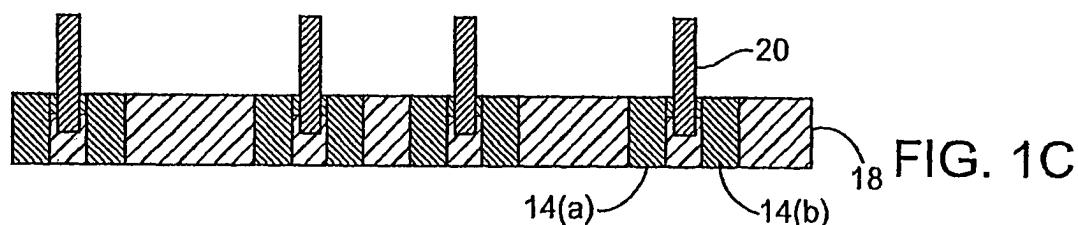

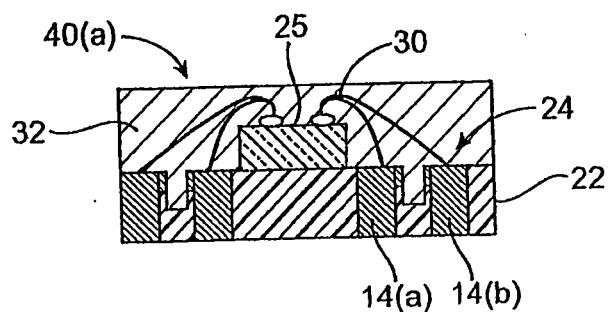

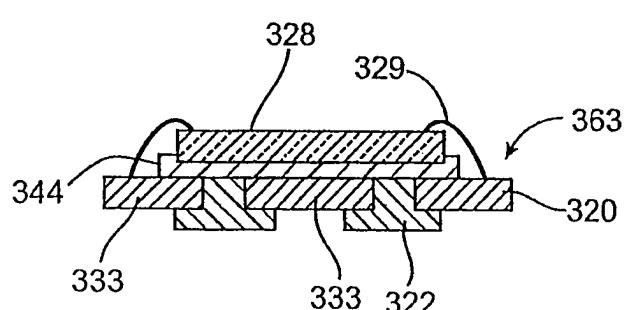

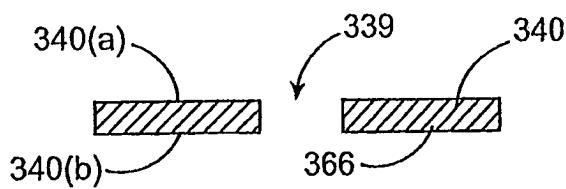

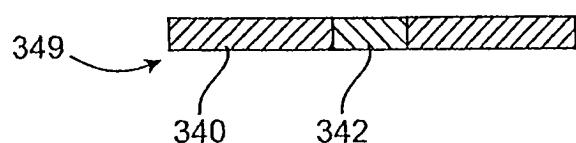

**[0115]** Wie in [Fig. 1C](#) gezeigt, trennt ein erstes Trennelement **20** den Zwischen-Teilbereich **14(c)** der Leiterrahmen-Struktur **14** nach dem Formen, um dadurch eine oder mehrere Aussparungen **24** in dem Substrat **22** zu formen. Die eine oder mehrere Aussparungen **24** kann sich gänzlich durch den Zwischen-Teilbereich **14(c)** erstrecken und kann sich teilweise in das Formmaterial **18** erstrecken. Die Aussparungen **24** können über die Hälfte der Dicke (oder weniger) der Dicke des Substrats **22** geformt sein. Durch das Trennen der Zwischen-Teilbereiche **14(c)** können die ersten und zweiten leitenden Teilbereiche **14(a)**, **14(b)** elektrisch und mechanisch voneinander isoliert werden. Wie im Folgenden detaillierter erklärt wird, können die isolierten ersten und zweiten leitenden Teilbereiche **14(a)**, **14(b)** danach als separate elektrische Anschlüsse (z.B. elektrische Verbindungsfelder) in dem resultierenden Halbleiterchip-Gehäuse dienen.

**[0116]** Jegliches geeignete erste Trennelement **20** kann verwendet werden, um den Zwischen-Teilbereich **14(c)** zu trennen. Beispielsweise kann das erste Trennelement **20** ein Wasserstrahl, eine Säge, ätzendes Material oder ein Laser sein.

**[0117]** Wie in [Fig. 1D](#) gezeigt, wird nach dem Trennen ein vorgeformtes Substrat **22** geformt. Das Substrat **22** hat Aussparungen **24**, wo die Trennung durchgeführt wurde. Die Aussparungen **24** entkoppeln die ersten und zweiten leitenden Teilbereiche **14(a)**, **14(b)**, so dass sie mechanisch und elektrisch voneinander isoliert sind.

**[0118]** Das geformte vorgeformte Substrat **22** kann Leiter, die sich über die seitlichen Kanten des Formmaterials **18** hinaus erstrecken, haben oder nicht. In dem spezifischen Substrat **22** korrespondieren die Leiter der Leiterrahmen-Struktur **14** mit den ersten und zweiten leitenden Teilbereichen **14(a)**, **14(b)**. In anderen Ausführungsformen kann das Substrat **22** Leiter haben, welche sich seitlich über die seitlichen Kanten der Leiterrahmen-Struktur **14** hinaus erstrecken und die nach unten gebogen sein können, um Anschlussverbindungen zu formen, oder nicht.

**[0119]** Wie in [Fig. 1E](#) gezeigt, können ein oder mehrere Halbleiterchips **25** dann auf dem Substrat **22** montiert werden. Das Substrat **22** kann eine erste Oberfläche **22(a)** und eine der ersten Oberfläche **22(a)** gegenüberliegende zweite Oberfläche **22(b)** beinhalten. In diesem Beispiel sind zumindest zwei Halbleiterchips **25** direkt auf dem Formmaterial **18** montiert. Eine Vielzahl von Halbleiterchips **25** kann auf dem Substrat **22** montiert sein, wenn eine Vielzahl von Halbleiterchip-Gehäusen zu formen sind. Wie weiter unten erläutert wird, können verbundene Gehäuse geformt werden und diese können schließlich in einem Vereinzelungsprozess voneinander getrennt werden.

**[0120]** Jegliches geeignete Material kann verwendet werden, um den einen oder mehrere Halbleiterchips **25** auf dem Substrat **22** zu montieren. Beispielsweise kann Lot oder ein leitender oder nicht leitender Klebstoff verwendet werden, um den einen oder mehrere Halbleiterchips **25** auf dem Substrat **22** zu montieren. Geeignete Klebstoffe beinhalten gefüllte oder ungefüllte Epoxid-Klebstoffe.

**[0121]** Der eine oder mehrere Halbleiterchips **25** können an jeglicher geeigneten Stelle auf dem Substrat **22** montiert sein. Wie in [Fig. 1E](#) gezeigt, sind der eine oder mehrere Halbleiterchips **25** auf einem isolierenden Material wie dem Formmaterial **18** montiert. In anderen Ausführungsformen kann die Leiterrahmen-Struktur **14** ein oder mehrere leitende Chip-Befestigungs-Felder (nicht gezeigt) beinhalten und der eine oder mehrere Halbleiterchips **25** können auf dem einen oder den mehreren Chip-Befestigungs-Feldern montiert sein.

**[0122]** Die Halbleiterchips **25** können jegliche der oben beschriebenen Halbleiterchips sein. Beispielsweise kann jeder Chip **25** eine erste Oberfläche **25(a)** und eine zweite Oberfläche **25(b)** haben, wobei die zweite Oberfläche **25(b)** näher an dem Substrat **22** ist als die erste Oberfläche **25(a)**. In einigen Ausführungsformen kann die erste Oberfläche **25(a)** einen Source-Anschluss, einen Gate-Anschluss und einen Drain-Anschluss haben, während die zweite Oberfläche **25(b)** keine Anschlüsse hat. In anderen Ausführungsformen kann die erste Oberfläche **25(a)** einen Source- und/oder Gate-Anschluss haben, während die zweite Oberfläche **25(b)** einen Drain-Anschluss hat (oder umgekehrt). In diesem Fall können der eine oder mehrere Halbleiterchips **25** auf leitenden Chip-Anschluss-Feldern (nicht gezeigt) anstelle auf dem Formmaterial **18** montiert sein.

**[0123]** Nach dem Montieren des einen oder mehreren Halbleiterchips **25** können Drähte **30** an den elektrischen Anschlüssen an der ersten Oberfläche **25(a)** der Halbleiterchips **25** und den ersten und zweiten leitenden

den Teilbereichen **14(a)**, **14(b)** befestigt (und damit elektrisch gekoppelt) werden. Die Drähte **30** können alternativ als "Drahtverbindungen" bezeichnet werden. Die Drähte können aus einem Edelmetall, wie Gold, Silber, Platin etc. ausgebildet sein, oder können ein Übergangsmaterial, wie Kupfer, Aluminium etc. beinhalten. In einigen Ausführungsformen können die Drähte die Form beschichteter Drähte (z.B. ein mit einem Edelmetall wie Gold oder Platin überzogener Kupferdraht) haben. Alternativ oder zusätzlich können leitende Klemmen verwendet werden, um die elektrischen Anschlüsse an der ersten Oberfläche **25(a)** des Halbleiterchips **25** zu den ersten und zweiten leitenden Teilbereichen **14(a)**, **14(b)** zu koppeln.

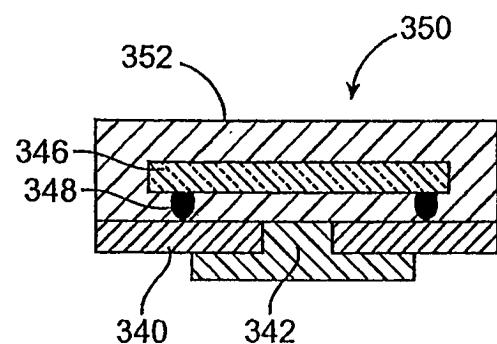

**[0124]** Mit Bezug auf [Fig. 1F](#) kann dann ein Einkapsel-Material **32** auf die erste Oberfläche **22(a)** des Substrats **22** und auf die auf der ersten Oberfläche **22(a)** des Substrats **22** montierten Halbleiterchips **25** aufgeschichtet werden. Das Einkapsel-Material **32** füllt die zuvor geformten Aussparungen **24** in dem Substrat **22**. Das Füllen der Aussparungen **24** in dem Substrat **22** durch das Einkapsel-Material **32** "verriegelt" vorzugsweise das Einkapsel-Material **32** mit dem Substrat **22**. Das Einkapsel-Material **32** kann auch geformt werden, so dass es sich nicht über die seitlichen Kanten des Substrats **22** hinaus erstreckt.

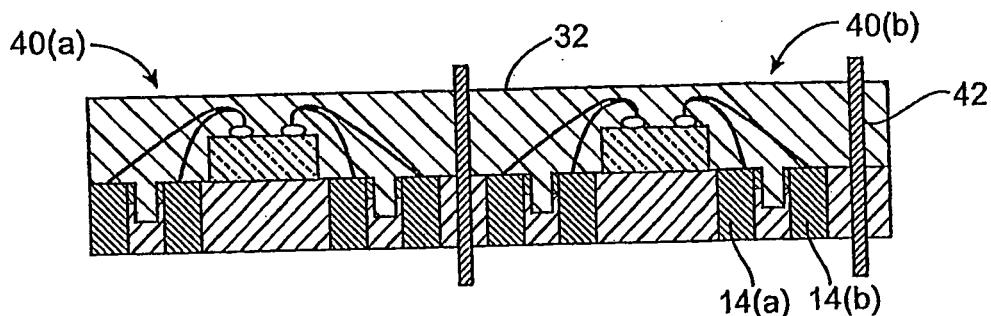

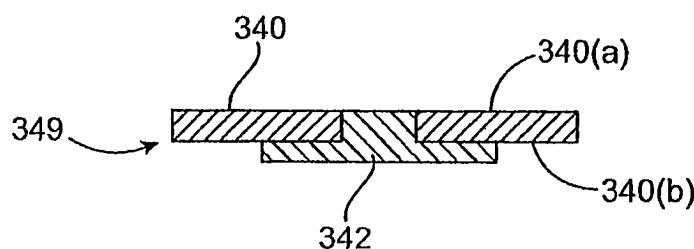

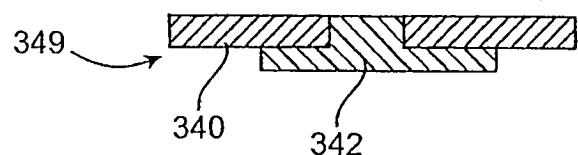

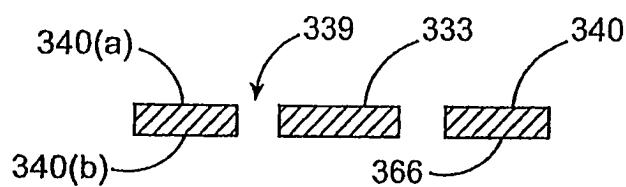

**[0125]** Bezug nehmend auf [Fig. 1G](#) kann, nach dem Aufschichten des Einkapsel-Materials **32**, ein zweites Trennelement **42** (welches das gleiche oder ein anderes als das erste oben beschriebene Trennelement **20** sein kann) verwendet werden, um die geformten Gehäuse **40(a)**, **40(b)** voneinander zu trennen. Das zweite Trennelement **42** kann das Einkapsel-Material **32** und das Substrat **22** durchtrennen. Dieser Prozess kann als "Vereinzelung" bezeichnet werden.

**[0126]** [Fig. 1H](#) zeigt eine quergeschnittene Seitenansicht eines Halbleiterchip-Gehäuses **40(a)** gemäß einer Ausführungsform der Erfindung nach Vereinzelung. Wie in [Fig. 1H](#) gezeigt, sind die Seiten des Einkapsel-Materials **32** flächengleich mit den Seiten des Substrats **22**. Das Einkapsel-Material **32** überdeckt sowohl den Halbleiterchip **25** als auch die Drähte **30**. Die ersten und zweiten leitenden Teilbereiche **14(a)**, **14(b)** sind elektrisch voneinander isoliert und formen elektrische Anschlüsse auf der Unterseite des Gehäuses **40(a)**.

**[0127]** Wie in [Fig. 1I](#) gezeigt, können die ersten und zweiten leitenden Teilbereiche **14(a)**, **14(b)** elektrische Anschlüsse auf der Unterseite des Gehäuses **40(a)** formen. Die Anschlüsse entsprechend der ersten und zweiten leitenden Teilbereiche **14(a)**, **14(b)** können leitenden Kontaktflecken auf einer gedruckten Schaltkreisplatte (nicht gezeigt) entsprechen.

**[0128]** Das in [Fig. 1I](#) gezeigte Halbleiterchip-Gehäuse **40(a)** kann leicht auf der Schaltkreisplatte (nicht gezeigt) montiert werden, um eine elektrische Baugruppe zu formen. Lot kann auf die bloßliegenden Oberflächen der ersten und zweiten leitenden Teilbereiche **14(a)**, **14(b)** und/oder auf die entsprechenden leitenden Kontaktflecken auf der Schaltkreisplatte aufgeschichtet werden. Das Halbleiterchip-Gehäuse **40(a)** kann dann auf der Schaltkreisplatte wie ein Flip-Chip montiert werden.

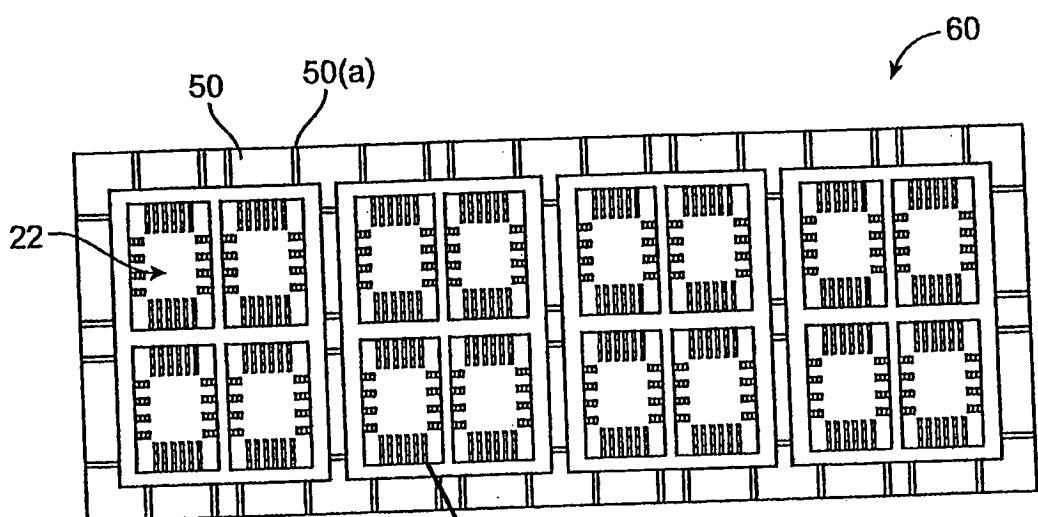

**[0129]** [Fig. 1J](#) zeigt eine Leistenstruktur **50**, die mehrere Substrate **22** während des Gehäuse-Form-Prozesses aufnehmen kann. Die Leistenstruktur **50** beinhaltet mehrere Referenz-Trenn-Kerben **50(a)**. Die Kerben **50(a)** können verwendet werden, um das Führen des vorbeschriebenen ersten Trennelements zu unterstützen, so dass die optimale Trenntiefe bestimmt werden kann, bevor der Zwischen-Teilbereich zwischen den ersten und zweiten leitenden Teilbereichen getrennt wird. Die Kerben **50(a)** können in einigen Fällen als "Sägestraßen-Referenzen" bezeichnet werden.

**[0130]** [Fig. 1K](#) zeigt eine Seitenansicht einer Referenz-Kerbe **50(a)** in einer Leistenstruktur **50**. Wie gezeigt erstreckt sich die Kerbe **50(a)** durch einen Teil der Dicke der Rahmenstruktur **50**.

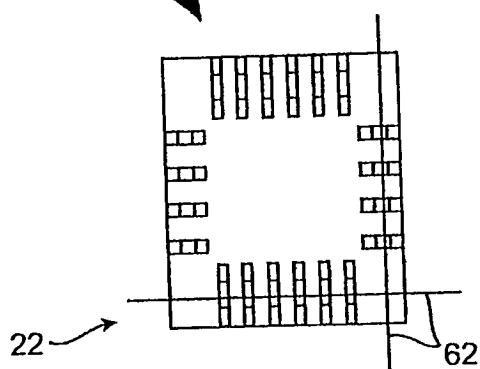

**[0131]** [Fig. 1L](#) zeigt horizontale und vertikale Trennlinien. Diese Linien **62** definieren Trennpfade für das erste Trennelement, während es den Zwischen-Teilbereich, der die ersten und zweiten leitenden Teilbereiche der Leiterrahmen-Struktur in dem Substrat **22** isoliert, trennt.

**[0132]** Wenn das Trennen durch die Trennlinien durchgeführt wird, kann ein Sägeblatt beispielsweise nur durch einen Teil der Leistenstrukturen **50** trennen, so dass sie intakt bleiben können und die verschiedenen Substrate **22** weiter verarbeitet werden können. Als Alternative zum Verwenden einer Säge und Referenz-Kerben **50(a)** kann man einen Laser verwenden, um die zuvor beschriebenen Zwischen-Teilbereiche zu trennen, die sich zwischen den ersten und zweiten leitenden Teilbereichen befinden. Ein Laserstrahl kann verwendet werden, um speziell die Zwischen-Teilbereiche zu trennen, ohne Referenz-Kerben zu verwenden.

**[0133]** Die oben beschriebenen Ausführungsformen haben eine Reihe von Vorteilen. Wie oben erwähnt, kann

durch das Bereitstellen einer Aussparung zwischen ersten und zweiten leitenden Teilbereichen einer Leiterrahmen-Struktur und anschließendes Füllen der Aussparung mit einem Einkapsel-Material, das Einkapsel-Material mit dem vorgeformten Substrat "verriegelt" werden. Dies hilft sicherzustellen, dass das geformte Chip-Gehäuse stabil und robust ist. Auch können Chip-Gehäuse mit einer Vielzahl elektrischer Anschlüsse schnell und effizient mittels der Ausführungsformen der Erfindung geformt werden. Zusätzlich können Ausführungsformen der Erfindung zumindest zwei Reihen von MLP-Gehäusen mit minimierten Gehäusedimensionen formen und ohne bloßliegende Chip-Anschluss-Felder (DAPs).

**[0134]** In den mit Bezug auf [Fig. 1A-Fig. 1L](#) beschriebenen Ausführungsformen befindet sich der Halbleiterchip innerhalb eines von den inneren Teilbereichen der Leiter definierten Gebiets. In anderen Ausführungsformen der Erfindung ist es möglich, ein Halbleiterchip-Gehäuse bereitzustellen, das eine Konfiguration aufweist, in der der Halbleiterchip Teilbereiche der Leiter überlappt. Dieser Typ von Halbleiterchip-Gehäuse kann auch ein Zweireihen-MLP-Gehäuse sein. Das verbesserte Zweireihen-MLP-Gehäuse ermöglicht eine höhere Stiftzahl bei gleicher Gehäusegröße, ohne thermische Leistungsfähigkeit zu opfern. Das verbesserte Zweireihen-MLP-Gehäuse ist auch kleiner als vergleichbare Gehäuse mit derselben Anzahl von Pins bzw. Stiften, ohne thermische Leistungsfähigkeit zu opfern. Diese zusätzlichen Ausführungsformen sind mit Bezug zu den [Fig. 2A-Fig. 2E](#) beschrieben.

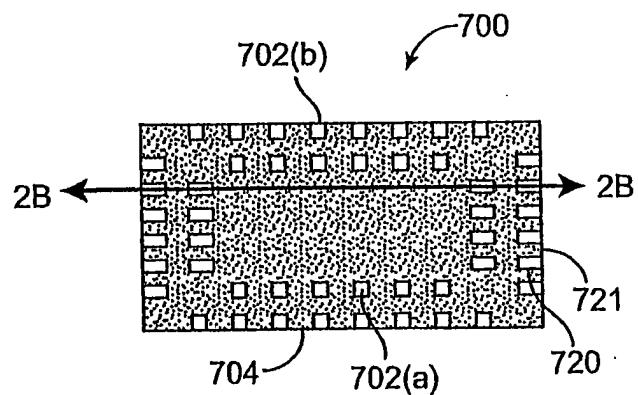

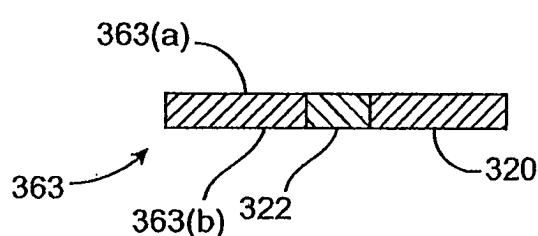

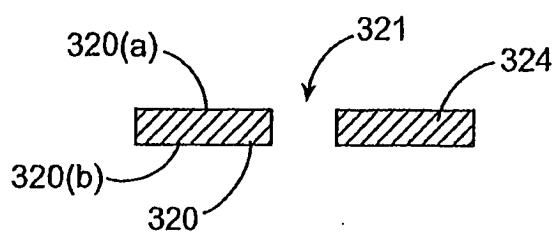

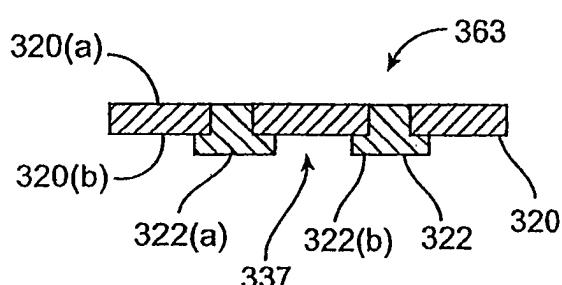

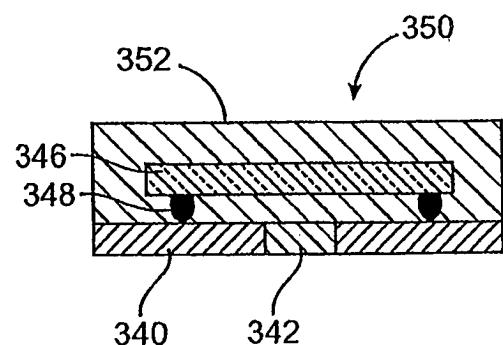

**[0135]** [Fig. 2A](#) zeigt eine Unteransicht eines Halbleiterchip-Gehäuses **700** gemäß einer Ausführungsform der Erfindung. Das Halbleiterchip-Gehäuse **700** beinhaltet eine Leiterrahmen-Struktur **720** beinhaltend eine Vielzahl von inneren ersten leitenden Teilbereichen **702(a)** und einer Vielzahl von äußeren zweiten leitenden Teilbereichen **702(b)**. Wie gezeigt, umgeben die zweiten leitenden Teilbereiche **702(b)** die ersten leitenden Teilbereiche **702(a)**. Wie in den vorhergehenden Ausführungsformen, formt ein Formmaterial **704** ein Substrat **721** mit einer Leiterrahmen-Struktur **720**. Äußere Oberflächen des Formmaterials **704** sind im Wesentlichen planparallel mit äußeren Oberflächen der ersten und zweiten leitenden Teilbereiche **702(a), 702(b)** der Leiterrahmen-Struktur **720**.

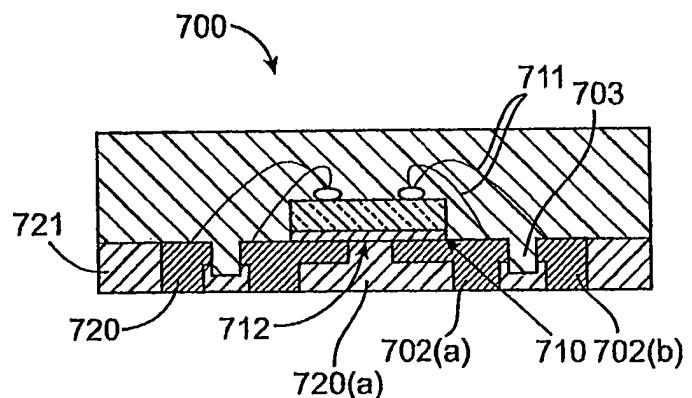

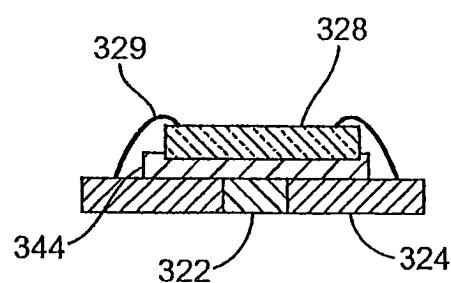

**[0136]** Eine quergeschnittene Seitenansicht des Halbleiterchip-Gehäuses **700** ist in [Fig. 2B](#) gezeigt. [Fig. 2B](#) ist ein Querschnitt entlang der Linie 2B-2B in [Fig. 2A](#). Das Halbleiterchip-Gehäuse **700** beinhaltet einen Halbleiterchip **710**, der auf einem Substrat **721** mittels eines Chip-Befestigungs-Materials **712** wie Lot oder einem nicht leitendem Klebstoff, montiert ist. In diesem Beispiel ist die Unterseite des Halbleiterchips **710** nicht elektrisch zu dem ersten leitenden inneren Teilbereich **702(a)** gekoppelt. Wie in den vorgenannten Ausführungsformen beinhaltet das Substrat **721** das Formmaterial **704** und die Leiterrahmen-Struktur **720** und es existieren Aussparungen **703**, die in dem Substrat **721** geformt sind. Die Aussparungen **703** befinden sich zwischen entsprechenden ersten und zweiten leitenden Teilbereichen **702(a), 702(b)** und sind durch Trennen der Zwischen-Teilbereiche der Leiterrahmen-Struktur **720**, die sich zwischen den ersten und zweiten leitenden Teilbereichen **702(a), 702(b)** befinden, geformt. Trennprozesse sind weiter oben in [Fig. 1C](#) und [Fig. 1D](#) beschrieben und alle der oben beschriebenen Trennprozesse können hier verwendet werden.

**[0137]** Anschließend können Verfahrensschritte beinhaltend Chip-Befestigung, Verbinden über Drähte, Einkapselung und Vereinzelung durchgeführt werden. Solche Verfahrensschritte sind oben mit Bezug zu [Fig. 1E-Fig. 1H](#) beschrieben. Diese Beschreibungen werden hier eingeschlossen.

**[0138]** Anders als im vorbeschriebenen Gehäuse, das in [Fig. 1G](#) gezeigt ist, ist der Halbleiterchip **710** in dieser Ausführungsform auf dem Substrat **721** montiert, so dass er sich über den inneren ersten leitenden Teilbereichen **702(a)** und einer geätzten Region **720(a)** der Leiterrahmen-Struktur **720** befindet und diese überlappt. Drähte **711** koppeln den Halbleiterchip **710** elektrisch zu den oberen Oberflächen der ersten und zweiten leitenden Teilbereiche **702(a), 702(b)**.

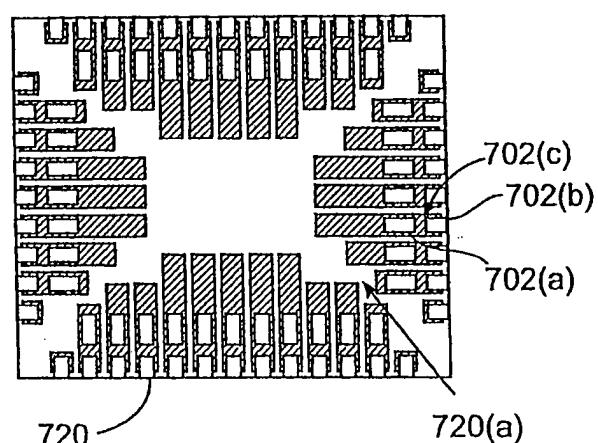

**[0139]** [Fig. 2C](#) ist eine Unteransicht auf die Leiterrahmen-Struktur **720**, die in dem Substrat **721** verwendet ist. Wie gezeigt, sind die ersten und zweiten leitenden Teilbereiche **702(a), 702(b)** nach Ätzen geformt. Zwischen-Teilbereiche **702(c)** befinden sich zwischen ersten und zweiten leitenden Teilbereichen **702(a), 702(b)**. Zusammen können ein erster und zweiter leitender Teilbereich **702(a), 702(b)** und ein Zwischen-Teilbereich **702(c)** zwischen den ersten und zweiten Teilbereichen **702(a), 702(b)** eine Aussparung formen. Wie oben angedeutet, wird der Zwischen-Teilbereich **702(c)** schließlich getrennt und wird mit einem Einkapsel-Material gefüllt. Die Leiterrahmen-Struktur **720** beinhaltet auch geätzte Gebiete **720(a)**, wo Material von der Leiterrahmen-Struktur **720** entfernt ist.

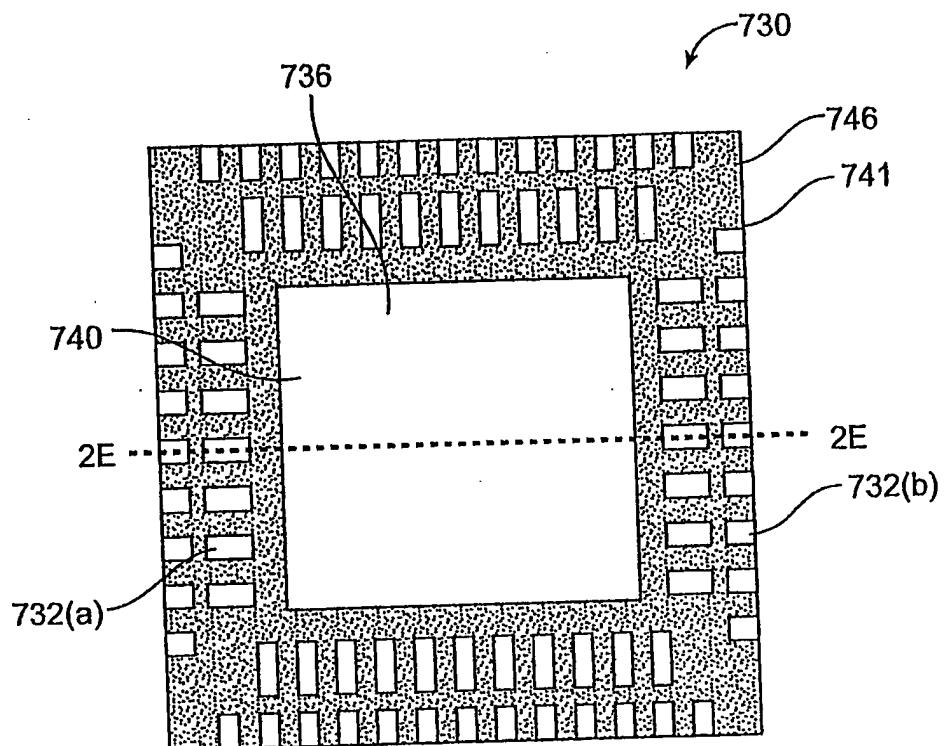

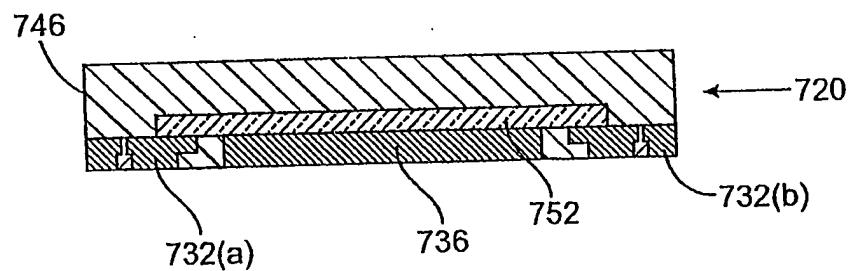

**[0140]** [Fig. 2D](#) zeigt eine Unteransicht auf ein Halbleiterchip-Gehäuse **730** gemäß einer anderen Ausführungsform der Erfindung. Wie in den vorhergehenden Ausführungsformen beinhaltet das Halbleiterchip-Ge-

häuser **730** eine Leiterrahmen-Struktur **740** und ein Formmaterial **746**. Zusammen können diese Komponenten eine Substrat **741** formen. Die Leiterrahmen-Struktur **740** beinhaltet einen zentralen Teilbereich **736**, der sowohl ein Chip-Befestigungs-Gebiet beinhaltet ein Chip-Anschluss-Feld (DAP) als auch innere erste leitende Teilbereiche **732(a)** und äußere zweite leitende Teilbereiche **732(b)** beinhalten kann. Die zweiten leitenden Teilbereiche **732(b)** können die inneren ersten leitenden Teilbereiche **732(a)** umgeben, und die ersten und zweiten leitenden Teilbereiche **732(a), 732(b)** können wie oben beschrieben elektrisch voneinander isoliert sein.

**[0141]** Wie in [Fig. 2E](#) gezeigt, ist ein Halbleiterchip **752** an dem Chip-Befestigungs-Gebiet des zentralen Teilbereichs **736** mittels eines Chip-Befestigungs-Materials oder Ähnlichem montiert. Der Halbleiterchip **752** überlappt sowohl viele der ersten leitenden Teilbereiche **732(a)** als auch den zentralen Teilbereich **736**. Jeder der zweiten leitenden Teilbereiche in der Vielzahl von zweiten leitenden Teilbereiche **732(b)** ist elektrisch von einem entsprechenden ersten leitenden Teilbereich in der Vielzahl von ersten leitenden Teilbereichen **732(b)** isoliert. [Fig. 2E](#) ist ein Querschnitt entlang der Linie 2E-2E in [Fig. 2D](#). Die zuvor beschriebenen Drähte sind aus [Fig. 2E](#) zur Klarheit weggelassen.

**[0142]** Die mit Bezug auf [Fig. 2A](#)-[Fig. 2E](#) beschriebenen Ausführungsformen haben eine Reihe von Vorteilen. Ausführungsformen der Erfindung ermöglichen eine höhere Stiftzahl, ohne thermische Leistungsfähigkeit zu opfern. Ausführungsformen der Erfindung können alternativ kleiner sein als vergleichbare Gehäuse mit der gleichen Anzahl von Pins, ohne thermische Leistungsfähigkeit zu opfern. Beispielsweise kann ein kleines Gehäuse mittels solcher Ausführungsformen geformt werden, obwohl der in dem Gehäuse verwendete Chip relativ groß ist. Andere Designs sind nicht in der Lage, einen großen Halbleiterchip in ein Gehäuse einzuschließen, ohne die Größe des Gehäuses zu vergrößern. Das liegt daran, dass in anderen Designs der Halbleiterchip auf einem DAP (Chip-Anschluss-Feld) von vergleichbarer Größe platziert wird. In den oben beschriebenen Ausführungsformen kann der Halbleiterchip jedoch laterale Dimensionen aufweisen, die größer als ein DAP sind oder gar kein DAP haben, während der Halbleiterchip zumindest einige der leitenden Teilbereiche (Leiter) der Leiterrahmen-Struktur überlappt. Thermische Leistungsfähigkeit wird nicht geopfert und kann verbessert werden, da Wärme nicht nur durch ein DAP abgeführt wird, sondern auch durch die Leiter (leitenden Teilbereiche) der Leiterrahmen-Struktur.

**[0143]** Tabelle 1 stellt die von den spezifischen, mit Bezug zu [Fig. 2A](#)-[Fig. 2E](#) beschriebenen Ausführungsformen bereitgestellten Vorteile im Vergleich zu den spezifischen oben in den [Fig. 1A](#)-[Fig. 1L](#) (Ausführungsform 1) beschriebenen Ausführungsformen dar. Wie in Tabelle 1 gezeigt, können die Ausführungsformen, die mit Bezug auf die [Fig. 2A](#)-[Fig. 2E](#) spezifisch beschrieben sind (Ausführungsform 2) kleiner sein, höhere Stiftzahlen haben und bessere thermische Eigenschaften aufweisen als die Ausführungsformen, die spezifisch in den [Fig. 1A](#)-[Fig. 1L](#) beschrieben sind.

| Tabelle 1                                          |                                      |                                                                           |

|----------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------|

| Eigenschaft                                        | Ausführungsform 1                    | Ausführungsform 2                                                         |

| Größe (Teilung)                                    | 7 mm × 6 mm (0,65 mm Teilung)        | 6 mm × 5 mm (0,4 mm-0,5 mm Teilung)                                       |

| Stiftzahl                                          | 56 Pin                               | 80 Pin                                                                    |

| Teilungs-Grenze                                    | Min 0,5 mm                           | Min 0,4 mm                                                                |

| Thermischer Widerstand-Einzelplatte (Grade C/W)    | DAP nicht gelötet mit 56 Pins – 82,6 | DAP nicht gelötet mit 80 Pins – 78,7 DAP nicht gelötet mit 64 Pins – 72,1 |

| Thermischer Widerstand-Mehr-fachplatte (Grade C/W) | DAP nicht gelötet mit 56 Pins – 45,1 | DAP nicht gelötet mit 80 Pins – 35,3 DAP nicht gelötet mit 64 Pins – 32,8 |

## II. Chip-Gehäuse beinhaltend mehrere Halbleiterchips

**[0144]** Während die charakteristischen Größen von Mikroleiter-Gehäuse (Microlead Package MLP)-Komponenten kleiner und kleiner werden, sind die Designs durch Metall-zu-Metall-Abstände und der Leistungsfähigkeit von Maßtoleranzen geätzter und halb-geätzter Rahmentechnologie begrenzt. Dies veranlasste die Einführung der Bump-Chip-Träger-(bump chip carrier BCC)-Technologie, die derzeit keine Layout-Beschränkungen bietet, aber üblicherweise nasse Ätzprozesse verwenden würde. Die Verwendung von nassen Ätzprozessen ist nicht bevorzugt.

**[0145]** Ausführungsformen der Erfindung verwenden vorgeformte Substrate, die Leiterrahmen-Strukturen einschließen. Die Substrate können mehrere Halbleiterchips aufnehmen. Üblicherweise erfordert ein Multichip-Gehäuse die Verwendung eines bestimmten Substrat-Layouts. Ein bestimmtes Substrat-Layout ist üblicherweise für das bestimmte Multichip-Gehäuse spezifisch. Ausführungsformen der Erfindung sind in der Lage, diese Beschränkung aufzuheben durch das Ermöglichen des Wiederverwendens desselben Designs eines vorgeformten Substrats, um mehrere Halbleiterchip-Layouts aufzunehmen. Ein dargelegtes Feld-Layout kann auch dafür verwendet werden, die thermische Leistungsfähigkeit des Halbleiterchip-Gehäuses in Ausführungsformen der Erfindung zu verbessern. Andere Layout-Konzepte beinhalten die Fähigkeit des Halbleiterchip-Gehäuses, Zugang zu bieten zu einem Drain-Kontakt eines Halbleiterchips (z.B. wenn der Halbleiterchip einen vertikalen Leistungs-MOSFET umfasst).

**[0146]** In einer Ausführungsform der Erfindung wird ein vorgeformtes Substrat beinhaltend eine erste Oberfläche und eine zweite Oberfläche bereitgestellt. Das vorgeformte Substrat beinhaltet eine Leiterrahmen-Struktur und ein Formmaterial. Die Leiterrahmen-Struktur umfasst ein Feld-Gebiet. Eine äußere Oberfläche des Feld-Gebiets und eine äußere Oberfläche des Formmaterials sind im Wesentlichen planparallel und fallen mit der zweiten Oberfläche des vorgeformten Substrats zusammen. Zumindest zwei Halbleiterchips sind an dem Substrat befestigt. Vorzugsweise sind die zumindest zwei Halbleiterchips an dem Formmaterial des Substrats befestigt und an Leitern an den seitlichen Kanten des Substrats mittels Verbindungsdrähte und/oder leitenden Klemmen verbunden.

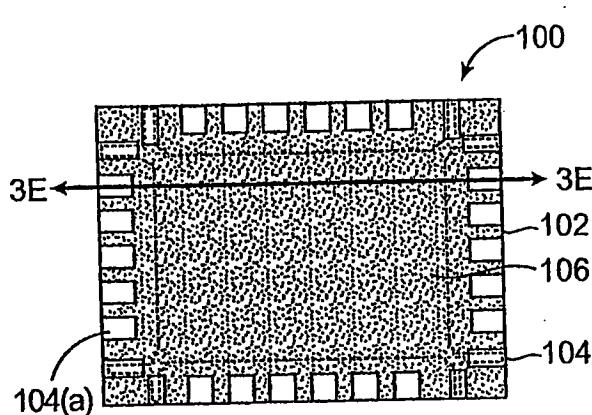

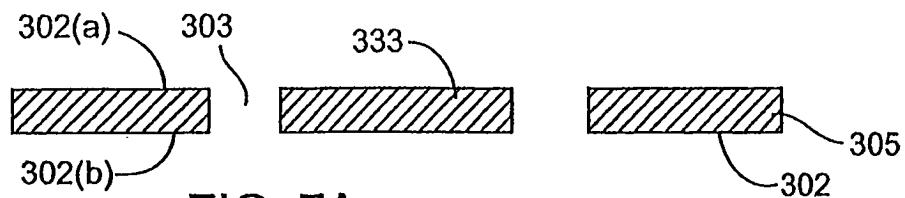

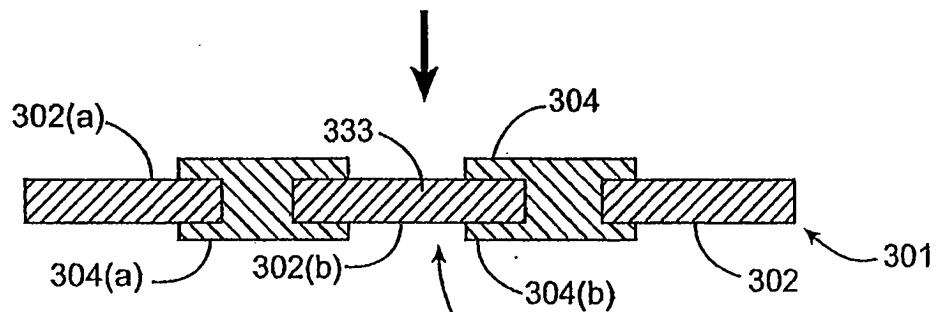

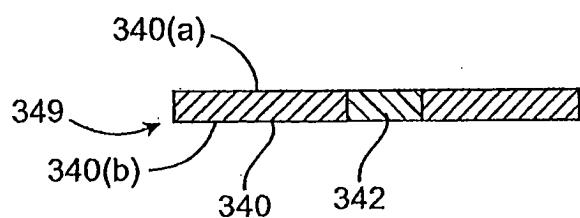

**[0147]** [Fig. 3A](#)-[Fig. 3E](#) zeigen Schritte in der Ausbildung eines Halbleiterchip-Gehäuses beinhaltend ein vorgeformtes Substrat und mehrere Halbleiterchips.

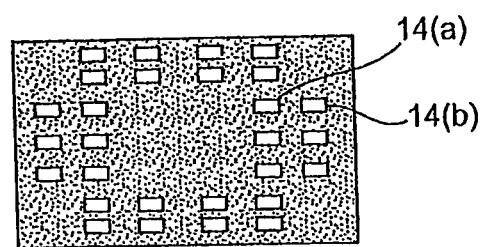

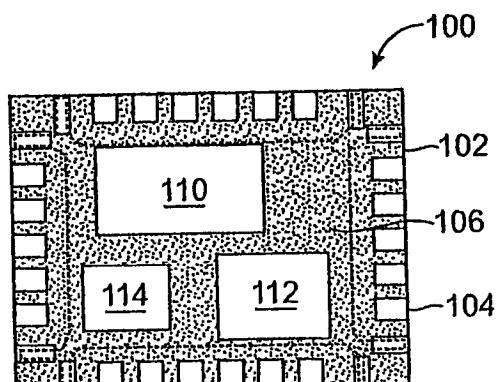

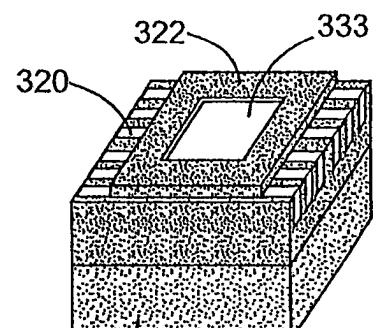

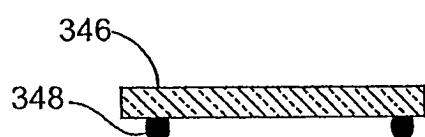

**[0148]** [Fig. 3A](#) zeigt eine Draufsicht auf ein vorgeformtes Substrat **100** gemäß einer Ausführungsform der Erfindung. Das vorgeformte Substrat **100** umfasst ein Formmaterial **102** und eine Leiterrahmen-Struktur **104**. Zumindest eine äußere Oberfläche des Formmaterials **102** und eine äußere Oberfläche der Leiterrahmen-Struktur **104** sind im Wesentlichen planparallel. Die Leiterrahmen-Struktur **104** beinhaltet eine Anzahl von Leitern **104(a)**, die sich an äußeren Seitenkantengebieten des Substrats **100** befinden und dort enden. Die Leiter **104(a)** in diesem Beispiel befinden sich an jeder der vier Seitenkantengebiete des Substrats **100** und sind freigelegt durch ein Formmaterial **102** und erstrecken sich nicht über dieses hinaus. Äußere Oberflächen der Leiter **104a** können im Wesentlichen planparallel mit der äußeren Oberfläche des Formmaterials **102** sein.

**[0149]** Wie in [Fig. 3A](#) durch die gepunkteten Linien dargestellt, beinhaltet die Leiterrahmen-Struktur ein abgesenktes zentrales Gebiet, das sich innerhalb der Leiter **104(a)** befindet. Das heruntergesetzte zentrale Gebiet kann durch einen Teil-Ätzprozess geformt sein. Die obere Oberfläche des heruntergesetzten zentralen Gebiets ist mit dem Formmaterial **102** bedeckt.

**[0150]** Die obere Oberfläche des Formmaterials **102** kann ein Chip-Befestigungs-Gebiet **100(a)** ausbilden, auf dem zwei oder mehr Halbleiterchips (nicht gezeigt) montiert werden können. Da die obere Oberfläche des Formmaterials **102** als Chip-Befestigungs-Gebiet **106** verwendet wird und keine leitenden Chip-Anschluss-Felder als Anbringungs-Oberflächen der dargestellten Ausführungsform verwendet werden, kann das vorgeformte Substrat **100** eine Vielzahl von Halbleiterchips stützen ohne zu erfordern, dass diese Chips in einem bestimmten Layout angeordnet sind. Mehrere Multichip-Konfigurationen können verwendet werden, ohne das externe Leiter-Layout zu verändern.

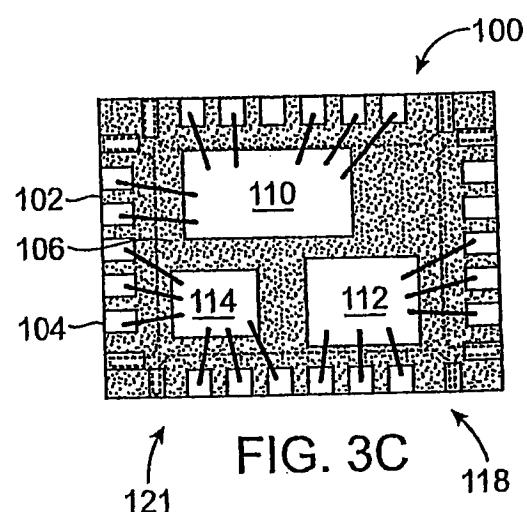

**[0151]** Bezug nehmend auf [Fig. 3B](#) werden, nachdem das Substrat geformt ist, Halbleiterchips **110**, **112**, **114** auf dem Chip-Befestigungs-Gebiet **106** auf dem Substrat **100** montiert. Ein nichtleitender (oder leitender) Klebstoff kann verwendet werden, um die Halbleiterchips **110**, **112**, **114** an dem Chip-Befestigungs-Gebiet **106** zu befestigen. Die Halbleiterchips können jegliche der oben beschriebenen Halbleiterchips sein. Vorzugsweise können die Chips **110**, **112**, **114** auf dem Formmaterial **102** des Substrats in jeglicher geeigneten Anordnung platziert sein.

**[0152]** Bezug nehmend auf [Fig. 3C](#), können, nachdem die Halbleiterchips **110**, **112**, **114** auf dem Substrat **100** montiert sind, die oberen Oberflächen der Halbleiterchips **110**, **112**, **114** elektrisch zu den Leitern **104(a)** gekoppelt werden, um ein Halbleiterchip-Gehäuse **121** zu formen. Wenn gewünscht, kann ein optionales Einkapsel-Material über sowohl die Halbleiterchips **110**, **112**, **114** als auch die leitenden Strukturen (z.B. Drähte, Klemmen etc.), die verwendet werden, um die Leiter **104(a)** zu den oberen Oberflächen der Halbleiterchips **110**, **112**, **114** zu koppeln, aufgeschichtet und ausgehärtet werden.

**[0153]** [Fig. 3C](#) zeigt spezifisch eine Anzahl von Drahtverbindungen **118**, die die elektrischen Anschlüsse

(nicht gezeigt) an den oberen Oberflächen der Halbleiterchips **110, 112, 114** zu den seitlichen Leitern **104(a)** der Leiterrahmen-Struktur **104** elektrisch koppeln. Die Drahtverbindungen **118** können über Drahtverbindungs-Verfahren geformt werden, die auf dem Gebiet der Technik bekannt sind. Alternativ können leitende Klemmen und Lot verwendet werden, um die elektrischen Anschlüsse auf der oberen Oberfläche der Halbleiterchips **110, 112, 114** zu den Leitern **104(a)** zu koppeln.

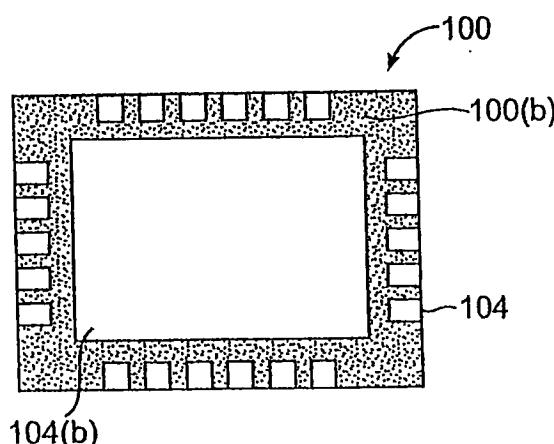

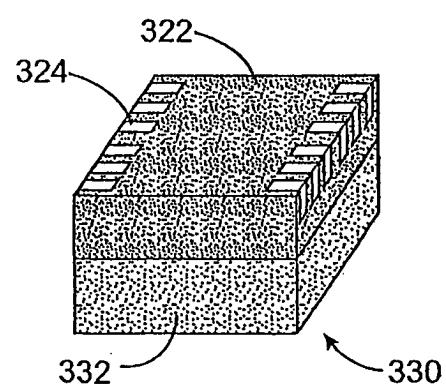

**[0154]** [Fig. 3D](#) zeigt eine Unteransicht auf das Substrat **100**. Die Unterseite des Substrats **100** und der Leiterrahmen-Struktur **104** beinhaltet ein Feld-Gebiet **104(b)**, das sich gegenüber dem Chip-Befestigungs-Gebiet **106** befindet. Das Feld-Gebiet **104(b)** ist groß und nimmt einen bedeutenden Teilbereich der zweiten Oberfläche **100(b)** des Substrats **100** ein und ist heruntergesetzt mit Bezug auf die Leiter **104(a)** an den Kanten des Substrats **100**. In diesem Beispiel kann das bloßliegende Feld-Gebiet **104(b)** zumindest ca. 50% der lateralen Fläche des Substrats **100** in Anspruch nehmen. Das große Feld-Gebiet **104(b)** versieht das geformte Gehäuse mit guten Wärme-Transfer-Eigenschaften, da das große Feld-Gebiet **104(b)** der Leiterrahmen-Struktur als eine Wärmesenke fungiert.

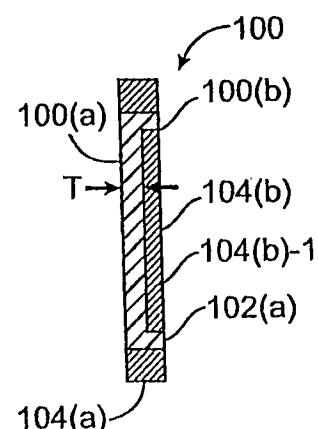

**[0155]** [Fig. 3E](#) zeigt eine quergeschnittene Seitenansicht des Substrats **100** entlang der Linie 3E-3E in [Fig. 3A](#). Das Feld-Gebiet **104(b)** hat eine äußere Oberfläche **104(b)-1**, die einen umfangreichen Teilbereich der unteren Oberfläche des Substrats **100** einnimmt. Die äußere Oberfläche **104(b)-1** des Feld-Gebiets **104(b)** ist freigelegt von und im Wesentlichen planparallel mit einer äußeren Oberfläche **102(a)** des Formmaterials in dem Substrat **100**. In diesem Beispiel isoliert das Formmaterial **102** die Halbleiterchips **110, 112, 114** elektrisch von dem Feld-Gebiet **104(b)**. Das freigelegte Feld-Gebiet **104(b)** kann auf eine Schaltkreisplatte (nicht gezeigt) gelötet werden, wenn es gewünscht ist, einen thermischen Pfad von den Halbleiterchips **110, 112, 114** zu der Schaltkreisplatte bereitzustellen.

**[0156]** Wie in [Fig. 3E](#) gezeigt, haben die Leiter **104(a)** Dicken, die im Wesentlichen gleich der maximalen Dicke des Formmaterials **102** sind. Zusätzlich ist in dem Substrat **100** eine innere Oberfläche des Feld-Gebiets **104(b)** der Leiterrahmen-Struktur **104** durch das Formmaterial bedeckt. Das Formmaterial **102** hat eine Dicke "T" und in diesem Beispiel entspricht die kombinierte Dicke T und die Dicke des Feld-Gebiets **104(b)** der Dicke des Substrats **100**.

**[0157]** Die mit Bezug auf [Fig. 3A-Fig. 3E](#) beschriebenen Ausführungsformen haben eine Reihe von Vorteilen. Erstens verbessert das große freigelegte Feld-Gebiet **104(b)** die thermische Leistungsfähigkeit des geformten Halbleiterchip-Gehäuses durch Bereitstellen eines großen Wärme-Leitungs-Pfads von den Halbleiterchips **110, 112, 114**. Zusätzlich hat das große Chip-Befestigungs-Gebiet **106** des Substrats **100** keine leitenden Felder, so dass verschiedene Multi-Chip-Layouts in einem Gehäuse bereitgestellt werden können, obwohl nur ein Substrat-Design verwendet wird.

**[0158]** [Fig. 4A-4F](#) stellen ein Verfahren zum Formen einer anderen Ausführungsform der Erfindung dar.

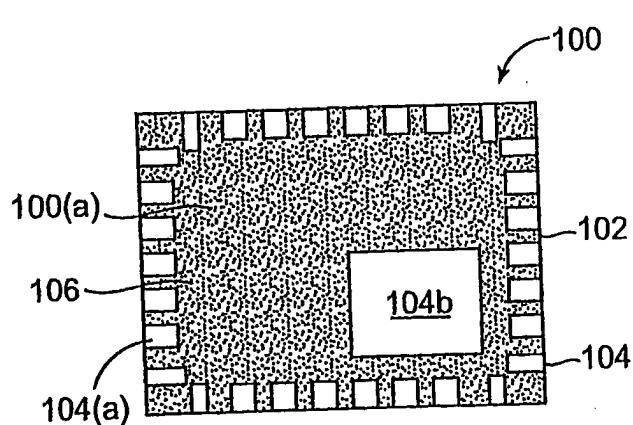

**[0159]** [Fig. 4A](#) zeigt ein anderes vorgeformtes Substrat **100** gemäß einer Ausführungsform der Erfindung. Das Substrat **100** beinhaltet eine Leiterrahmen-Struktur **104** beinhaltend ein Feld-Gebiet **104(b)** und Leiter **104(a)** und ein Formmaterial **102**. Ein Chip-Befestigungs-Gebiet **106** an einer oberen Oberfläche **100(a)** des vorgeformten Substrats **100** kann eine Oberfläche des Feld-Gebiets **104(b)** beinhalten und kann eine Anzahl von Halbleiterchips (nicht gezeigt) stützen. Die gepunkteten Linien in [Fig. 4B](#) zeigen die Kontur der Leiterrahmen-Struktur **104**, und die Leiterrahmen-Struktur **104** kann durch einen Teil-Ätzprozess geformt sein.

**[0160]** Anders als das oben mit Bezug zu [Fig. 3A](#) beschriebene Substrat **100**, hat das Feld-Gebiet **104(b)** in diesem Beispiel gegenüberliegende Oberflächen, die mit den gegenüberliegenden Oberflächen des Substrats **100** zusammenfallen. In dieser Ausführungsform beinhaltet das Chip-Befestigungs-Gebiet **106** sowohl eine äußere Oberfläche des Feld-Gebiets **104(b)** und eine äußere Oberfläche des Formmaterials **102**.

**[0161]** In diesem Beispiel erstreckt sich das Feld-Gebiet **104(b)** durch die gesamte Dicke des Substrats **100** und kann einen leitenden und/oder thermischen Pfad für einen Halbleiterchip (nicht gezeigt) auf dem Feld-Gebiet **104(b)** durch das Substrat **100** und zu einer darunter liegenden Schaltkreisplatte (nicht gezeigt) darstellen. In einigen Ausführungsformen kann das Feld-Gebiet **104(b)** elektrisch zu einem Eingangs- oder Ausgangs-Anschluss eines elektrischen Bauelements in einem Halbleiterchip (in [Fig. 4A](#) nicht gezeigt) gekoppelt sein. Beispielsweise kann das Feld-Gebiet **104(b)** elektrisch zu dem Drain-Gebiet eines MOSFETs in einem Halbleiterchip gekoppelt sein.

**[0162]** Wie in [Fig. 4B](#) gezeigt, kann eine Anzahl von Halbleiterchips **110, 112, 114** auf dem Chip-Befesti-

gungs-Gebiet **106** platziert sein. Einer der Halbleiterchips, Halbleiterchip **112**, kann an dem Feld-Gebiet **104(b)** befestigt sein, während die anderen Halbleiterchips **110, 114** an dem Formmaterial befestigt sein können. Der Halbleiterchip **112** kann ein vertikales Bauelement wie ein vertikaler MOSFET sein. Wie oben beschrieben, haben solche vertikalen Bauelemente einen Eingang an einer Oberfläche des Chips und einen Ausgang an einer anderen gegenüberliegenden Oberfläche des Chips. Die anderen Halbleiterchips **110, 114** können horizontale Bauelemente beinhalten. Wie oben beschrieben, hat ein horizontales Bauelement einen Eingang und einen Ausgang auf der selben Oberfläche des Chips.

**[0163]** Bezug nehmend auf [Fig. 4C](#) werden, nachdem die Halbleiterchips **110, 112, 114** auf dem Substrat montiert sind, eine Zahl von Drahtverbindungen **118** geformt, um die Leiter **104(a)** mit den oberen Oberflächen der Halbleiterchips **110, 114, 112** zu verbinden. Ein Halbleiterchip-Gehäuse **121** ist dann geformt.

**[0164]** [Fig. 4D](#) zeigt eine Unteransicht auf das Substrat **100**. Wie in [Fig. 4D](#) gezeigt, ist freigelegte Oberfläche des Feld-Gebiets **104** größer an der unteren Oberfläche **100(b)** des Substrats **100** als an der freigelegten Oberfläche des Feld-Gebiets **104(b)** an der oberen Oberfläche **100(a)** des Substrats **100**. In anderen Ausführungsformen kann die freigelegte Oberfläche des Feld-Gebiets **104(b)** an der oberen Oberfläche **100(a)** des Substrats **100** größer sein oder die gleiche Größe haben wie die freigelegte Oberfläche des Feld-Gebiets **104(b)** an der unteren Oberfläche des Substrats **100**.

**[0165]** [Fig. 4E](#) zeigt eine Seitenansicht des in [Fig. 4A](#) gezeigten Substrats **100**. Wie in [Fig. 4E](#) gezeigt, sind die ersten und zweiten gegenüberliegenden Oberflächen **104(b)-1, 104(b)-2** des Feld-Gebiets **104(b)** im Wesentlichen planparallel mit äußeren Oberflächen des Formmaterials **102**. Das Formmaterial **102** kann eine Dicke "T" an einem geätzten Teilbereich des Feld-Gebiets **104(b)** haben. Daher kann das Formmaterial **102** eine Dicke haben, die gleich der Dicke des Substrats **100** an manchen Stellen ist und es kann eine Dicke "T" an anderen Stellen haben.

**[0166]** Die mit Bezug auf [Fig. 4A](#)-[Fig. 4E](#) beschriebenen Ausführungsformen haben eine Reihe von Vorteilen. Erstens verbessert das große freigelegte Feld-Gebiet **104(b)** die thermische Leistungsfähigkeit des geformten Halbleiterchip-Gehäuses durch Bereitstellen eines großen Wärme-Leit-Pfads von den Halbleiterchips **110, 112, 114**. Zusätzlich kann das große Chip-Befestigungs-Gebiet **106** des Substrats **100** als leitender und thermischer Pfad für einen oder mehrere Halbleiterchips, die auf dem Substrat **100** montiert sind, dienen.

**[0167]** Die in [Fig. 3A](#)-[Fig. 3E](#) und [Fig. 4A](#)-[Fig. 4E](#) gezeigten Ausführungsformen haben weiterhin andere Vorteile in Ergänzung zu den bereits genannten. Erstens, da kein DAP erforderlich ist, können viele verschiedene Halbleiterchip-Konfigurationen verwendet werden, ohne die externen Leiter-Konfigurationen zu verändern. Der Abstand zwischen Chips auf dem Substrat kann minimiert werden, da ein DAP nicht erforderlich ist, wodurch ein kompakteres Gehäuse bereitgestellt wird. Zweitens, da ein DAP nicht erforderlich ist, ist ein Riegel, der verwendet wird, um den DAP während der Verarbeitung zu verbinden, nicht erforderlich. Dies kann die Verarbeitung vereinfachen. Drittens kann ein von einem mit einem freigelegten Feld verbundenen Gebiet in Anspruch genommenes Gebiet in einem Substrat gemäß einer Ausführungsform der Erfindung maximiert werden. Wie oben gezeigt, kann das freigelegte Feld fast die gesamte Rückseite des Substrats, das die Halbleiterchips stützt, in Anspruch nehmen. Viertens kann, wie oben gezeigt, die Leiterrahmen-Struktur eine freigelegte Oberfläche in dem Substrat haben, um den Drain- oder anderen Anschluss in einem elektrischen Bauelement in einem Halbleiterchip, der auf dem Substrat montiert ist, zu verbinden. Dies kann erreicht werden, während die freigelegte Feld-Fläche auf der gegenüberliegenden Seite des Substrats, welche schließlich an eine geeignete Schaltkreisplatte gelötet wird, maximiert wird.

### III. Verfahren zum Herstellen eines Halbleiterchip-Gehäuses unter Verwendung einer gedruckten Leiterrahmenstruktur

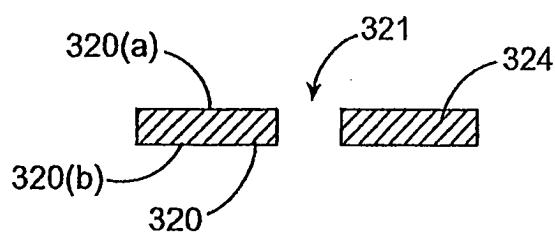

**[0168]** Einige der vorgeformten Substratausführungsformen, welche zuvor beschrieben wurden, verwenden eine geätzte Leiterrahmenstruktur (z.B. die in Bezug auf die [Fig. 1A](#)-[Fig. 1H](#) beschriebenen Ausführungsformen) und werden unter Verwendung von teurem Abdeckband ausgebildet. Das Verwenden von geätzten Leiterrahmen und Abdeckband ist teuer. Band ist ein verhältnismäßig teures Bauteil in dem Herstellungsverfahren und das Abdecken und Ätz-Verfahren erhöhen die Herstellungszeit, Komplexität und die Kosten eines vorgeformten Substrats. Es wäre wünschenswert, ein Verfahren zum Herstellen eines vorgeformten Substrats bereitzustellen, welches nicht auf die Verwendung von Abdeckband oder geätzten Leiterrahmenstrukturen zurückgreift.

**[0169]** Um dieses Problem anzugehen, können Ausführungsformen der Erfindung einen gedruckten Leiter-

rahmenapparat verwenden, um ein vorgeformtes Substrat auszubilden. Abdeckband und geätzte Leiterrahmen werden nicht benötigt, um das vorgeformte Substrat auszubilden, so dass das letztendliche Gehäuse, welche hergestellt wird, weniger teuer ist als ein Gehäuse, welche ausgebildet wird unter Verwendung eines geätzten Leiterrahmens und Abdeckbandes. Aufgrund der Verfahrenseffizienz, welche unter Verwendung von Ausführungsformen der Erfindung erreicht wird, können die resultierenden Halbleiterchip-Gehäuse, welche gemäß Ausführungsformen der Erfindung hergestellt werden, etwa 42% weniger kosten als vergleichbare Halbleiterchip-Gehäuse, welche vorgeformte Substrate mit geätzten Leiterrahmenstrukturen verwenden.

**[0170]** Zusätzlich zur Adressierung der zuvor erläuterten Probleme wäre es auch wünschenswert, die thermischen Eigenschaften von Halbleiterchip-Gehäusen beinhaltend vorgeformte Substrate zu verbessern. In Ausführungsformen der Erfindung ist die thermische Eigenschaft gut, weil Hitze von einem Halbleiterchip zu den Leitern einer Leiterrahmenstruktur übertragen werden kann.

**[0171]** Es wäre auch wünschenswert, in einigen Fällen, den Bereich eines Lötpunktes, der verwendet wird, um ein Halbleiterchip-Gehäuse mit einer Schaltkreisplatte zu verbinden, zu vergrößern. Unter Verwendung von Ausführungsformen der Erfindung kann eine konkave Struktur in dem Substrat ausgebildet werden. Mit einer konkaven Struktur ist es möglich, die Größe eines Lötpunktes zu vergrößern und ein ausgesetztes Feld kann vor möglichem elektrischen Kurzschluss geschützt werden. Dies wird in weiterem Detail unten erläutert.

**[0172]** Ausführungsformen der Erfindung können auch Flip-Chip-Befestigungsmethoden einsetzen, welche einen nicht leitenden Klebstoff oder einen Lötbuckel und einen Verflüssigungsprozess verwenden. Die Leiterrahmenstrukturgestaltung ist verhältnismäßig einfach und es ist auch möglich, die Stiftanzahl für eine vorgegebene Gehäusegröße zu erhöhen. Es ist auch möglich, einen größeren Chip in dem Halbleiterchip-Gehäuse zu verwenden, weil ein DAP (Die Attach Pad, Chipanschlussfeld) nicht erforderlich ist in den Ausführungsformen der Erfindung.

**[0173]** In einer Ausführungsform umfasst das Verfahren das Ausbilden eines vorgeformten Substrats. Der Schritt des Ausbildens des vorgeformten Substrates umfasst (i) das Platzieren einer Leiterrahmenstruktur zwischen wenigstens einer ersten Ausformform und einer zweiten Ausformform, (ii) Kontaktieren der Leiterrahmenstruktur mit der ersten und zweiten Ausformform, und (iii) Ausbilden eines Ausformmaterials um die Leiterrahmenstruktur. Die Leiterrahmenstruktur kann eine nicht geätzte Leiterrahmenstruktur sein und die ersten und zweiten Ausformformen können Teil eines Ausformapparats oder Werkzeugs sein. Nachdem das vorgeformte Substrat ausgebildet ist, wird ein Halbleiterchip an dem vorgeformten Substrat befestigt. Drahtanschlüsse, leitende Clips, Lotstrukturen (beispielsweise Lotbälle) oder Ähnliches können verwendet werden, um den Halbleiterchip mit Leitern in dem vorgeformten Substrat zu koppeln. Nachdem der Halbleiterchip elektrisch und mechanisch mit dem vorgeformten Substrat gekoppelt ist, wird der Halbleiterchip dann in ein Kapselmaterial eingekapselt, um ein Halbleiterchip-Gehäuse auszubilden. Das Kapselmaterial kann das gleiche oder ein unterschiedliches sein zu dem zuvor beschriebenen Ausformmaterial. Z.B. kann das Kapselmaterial unterschiedlich sein als das zuvor beschriebene Ausformmaterial, um die thermischen Eigenschaften des ausgeformten Chipgehäuses zu verbessern und um die Herstellungskosten zu verringern.

**[0174]** In einer spezifischen Ausführungsform kann das Verfahren zum Herstellen eines Halbleiterchip-Gehäuses den folgenden Prozess verwenden: a) einen ersten Ausformprozess, um ein vorgeformtes Substrat zu bilden, b) einen Substratreinigungsprozess, welcher ein Plasma, einen Laser, oder chemisches Ätzen und/oder einen Deflash-Prozess verwenden kann, c) einen Chipbefestigungsprozess, d) einen Plasmareinigungsprozess, e) einen Drahtverbindungsprozess, e) einen zweiten Ausform- oder Kapselprozess, und f) einen Vereinzelungsprozess. Jeder dieser spezifischen Prozesse wird in weiterem Detail weiter unten beschrieben.

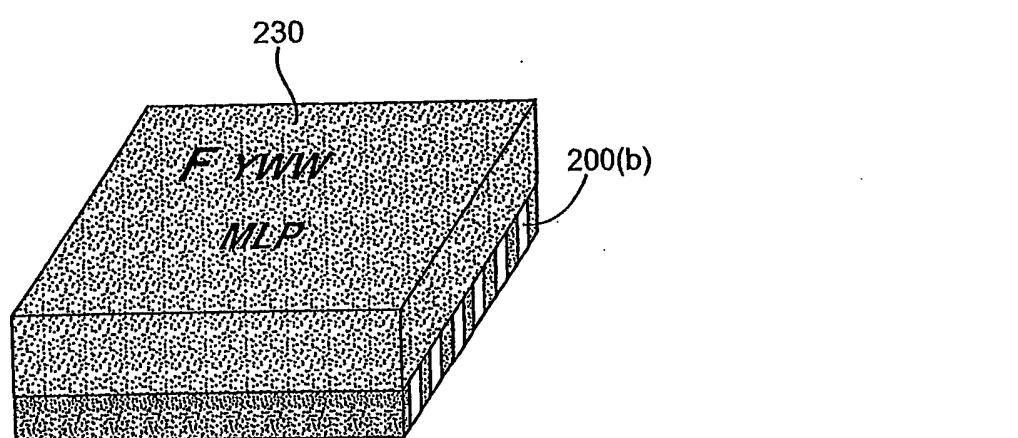

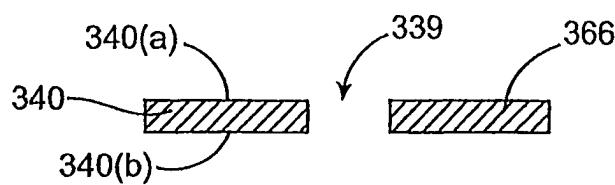

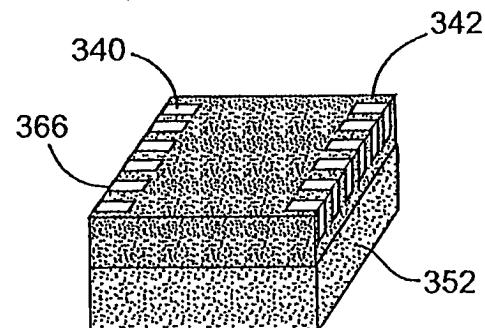

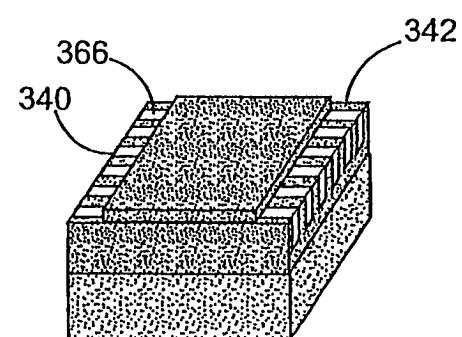

**[0175]** [Fig. 5](#) zeigt eine Leiterrahmenstrukturanordnung **201**, welche eine Anzahl von verbundenen Leiterrahmenstrukturen **200** beinhaltet. Jede Leiterrahmenstruktur **200** in der Leiterrahmenstrukturanordnung **201** beinhaltet ungeschnittene Leitungen **200(b)** und eine größeren Hauptbereich **200(a)**. Die ungeschnittenen Leitungen **200(b)** erstrecken sich auf gegenüberliegenden Seiten des Hauptbereichs **200(a)**. Die Leiterrahmenstrukturen **200** in der Leiterrahmenstrukturanordnung **201** werden gegebenenfalls in individuellen Halbleiterchip-Gehäusen verwendet und werden gegebenenfalls voneinander getrennt. Die Leiterrahmenstrukturen **200** und die Leiterrahmenstrukturanordnung **201** können jegliche Charakteristika oder Eigenschaften von jeglichen der zuvor beschriebenen Leiterrahmenstrukturen aufweisen.

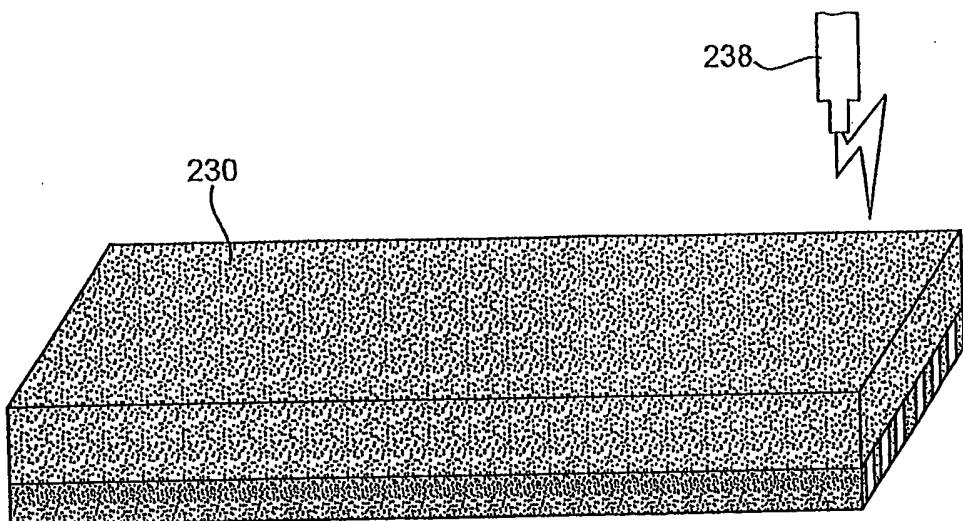

**[0176]** [Fig. 6A](#) zeigt eine perspektivische Ansicht einer ausgeformten Leiterrahmenstrukturanordnung **206**,

nachdem sie in einem Ausformwerkzeug **202** ausgebildet worden ist. Das Ausformwerkzeug **202** beinhaltet eine erste Ausformform **202(a)** und eine zweite Ausformform **202(b)**. Ein Einlass zum Einführen eines unausgehärteten Ausformmaterials und ein Fluidauslass für überschüssiges Ausformmaterial können in dem Ausformwerkzeug **202** bereitgestellt sein. In einigen Fällen können auch Heizelemente (nicht gezeigt) bereitgestellt werden, um das Ausformmaterial zu heizen, so dass es fließen kann. Im Allgemeinen sind Ausformwerkzeuge im Stand der Technik bekannt.

**[0177]** Um die ausgeformte Leiterrahmenstruktur anordnung **206** auszubilden, kann die zuvor beschriebene Leiterrahmenstruktur anordnung **201** zwischen die ersten und zweiten Ausformformen **202(a), 202(b)** eingesetzt werden. Ein Ausformmaterial **204** wird um die Leiterrahmenstruktur anordnung **200** ausgeformt und härtet aus, um eine geformte Leiterrahmenstruktur anordnung **206** auszubilden. Das Ausformmaterial **204** exponiert äußere Oberflächen der Leitungen **200(b)** und des Hauptbereichs **200(a)**. Eine leicht erhöhte Randstruktur **204(a)** kann um jeden Hauptbereich **200(a)** vorhanden sein. Einige äußere Oberflächen des Ausformmaterials **204** und die Leiterrahmenstrukturen in der Leiterrahmenstruktur anordnung **200** sind im Wesentlichen koplanar miteinander.