(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5819350号

(P5819350)

(45) 発行日 平成27年11月24日(2015.11.24)

(24) 登録日 平成27年10月9日(2015.10.9)

(51) Int.Cl.

G06F 9/445 (2006.01)

F 1

G06F 9/06

610J

請求項の数 8 (全 24 頁)

(21) 出願番号 特願2013-124391 (P2013-124391)

(22) 出願日 平成25年6月13日 (2013.6.13)

(65) 公開番号 特開2015-1757 (P2015-1757A)

(43) 公開日 平成27年1月5日 (2015.1.5)

審査請求日 平成27年5月7日 (2015.5.7)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 110001678

特許業務法人藤央特許事務所

(72) 発明者 早川 典充

神奈川県秦野市堀山下1番地 株式会社日立製作所 1Tプラットフォーム事業本部

内

(72) 発明者 吉田 圭佑

神奈川県横浜市西区みなとみらい二丁目3

番3号 株式会社日立情報通信エンジニア

リング内

最終頁に続く

(54) 【発明の名称】 計算機システム及び起動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のオペレーティングシステムが稼働する計算機を複数備える計算機システムであつて、

前記複数の計算機の各々は、プロセッサ、前記プロセッサに接続される第1のメモリ、前記プロセッサに接続される第2のメモリ、前記プロセッサに接続されるI/Oデバイス、及び前記プロセッサに接続される記憶装置を有し、

前記複数のオペレーティングシステムは、第1のオペレーティングシステム及び第2のオペレーティングシステムを含み、

前記第2のメモリは、前記第1のオペレーティングシステムの起動時に、前記計算機が備えるハードウェアを制御し、前記第1のオペレーティングシステムの起動処理を実行する第1のハードウェア制御部を格納し、 10

前記記憶装置は、

前記第1のオペレーティングシステムの実行イメージである第1のオペレーティングシステムイメージと、

前記第1のオペレーティングシステムを起動する第1のオペレーティングシステムブートローダと、

前記第2のオペレーティングシステムの実行イメージである第2のオペレーティングシステムイメージと、

前記第2のオペレーティングシステムを起動する第2のオペレーティングシステムブー

10

20

トローダと、

前記第2のオペレーティングシステムの起動時に、前記計算機が備えるハードウェアを制御し、前記第2のオペレーティングシステムの起動処理を実行する第2のハードウェア制御部と、

前記第2のハードウェア制御部が参照する情報が格納される前記第1のメモリにおける記憶領域の絶対アドレスであるアドレスデータを書き換えるアドレス書換部と、を格納し、

前記第2のハードウェア制御部は、当該第2のハードウェア制御部を起動するための起動部を含み、

前記プロセッサは、電源が投入された場合、前記第2のメモリに格納される前記第1のハードウェア制御部を前記第1のメモリに書き込み、前記第1のハードウェア制御部を実行し、

前記第1のハードウェア制御部は、

前記記憶装置から前記第2のハードウェア制御部、及び前記アドレス書換部を読み出して、前記第1のメモリの所定の記憶領域に書き込み、

前記第2のハードウェア制御部に含まれる前記起動部が格納される記憶領域の先頭アドレスを取得して、ベースアドレスデータとして前記第1のメモリに書き込み、

前記記憶装置から前記第1のオペレーティングシステムブートローダを読み出して、前記第1のメモリに書き込み、

前記第1のメモリに書き込まれた第1のオペレーティングシステムブートローダを起動し、

前記第1のオペレーティングシステムブートローダは、

前記記憶装置から前記第1のオペレーティングシステムイメージを読み出して、前記第1のメモリに書き込み、

前記第1のメモリに書き込まれた第1のオペレーティングシステムイメージを実行することによって前記第1のオペレーティングシステムを起動し、

前記第1のオペレーティングシステムは、前記アドレス書換部を起動し、

前記アドレス書換部は、

前記第1のメモリに書き込まれたベースアドレスデータを取得し、

書換対象のアドレスデータが格納される記憶領域のアドレスである対象アドレスを取得し、

前記取得されたベースアドレスデータに基づいて、前記取得された対象アドレスに対応する記憶領域に格納される前記アドレスデータを書き換え、

前記起動部を起動し、

前記起動部は、前記書き換えられたアドレスデータを用いて、前記第2のハードウェア制御部を起動し、

前記第2のハードウェア制御部は、

前記記憶装置から前記第2のオペレーティングシステムブートローダを読み出して、前記第1のメモリに書き込み、

前記第1のメモリに書き込まれた第2のオペレーティングシステムブートローダを起動し、

前記第2のオペレーティングシステムブートローダは、

前記記憶装置から前記第2のオペレーティングシステムイメージを読み出して、前記第1のメモリに書き込み、

前記第1のメモリに書き込まれた第2のオペレーティングシステムイメージを実行することによって前記第2のオペレーティングシステムを起動することを特徴する計算機システム。

### 【請求項2】

請求項1に記載の計算機システムであって、

前記アドレス書換部は、

10

20

30

40

50

前記第2のハードウェア制御部から前記対象アドレスに関する情報を取得し、前記取得された対象アドレスに対応する記憶領域に格納されるアドレスデータに前記ベースアドレスデータを加算することによって、当該アドレスデータを書き換えることを特徴とする計算機システム。

【請求項3】

請求項2に記載の計算機システムであって、前記アドレス書換部は、前記第2のハードウェア制御部の実行形式のファイルを参照することによって前記対象アドレスに関する情報を取得することを特徴とする計算機システム。

【請求項4】

請求項3に記載の計算機システムであって、前記記憶装置は、第1の記憶装置及び第2の記憶装置を含み、前記第1の記憶装置は、前記第1のオペレーティングシステムイメージ、前記第1のオペレーティングシステムブートローダ、前記第2のハードウェア制御部、及び前記アドレス書換部を格納し、前記第2の記憶装置は、前記第2のオペレーティングシステムイメージ、及び前記第2のオペレーティングシステムブートローダを格納することを特徴とする計算機システム。

【請求項5】

複数のオペレーティングシステムが稼働する計算機における起動方法であって、前記計算機は、プロセッサ、前記プロセッサに接続される第1のメモリ、前記プロセッサに接続される第2のメモリ、前記プロセッサに接続されるI/Oデバイス、及び前記プロセッサに接続される記憶装置を備え、前記複数のオペレーティングシステムは、第1のオペレーティングシステム及び第2のオペレーティングシステムを含み、前記第2のメモリは、前記第1のオペレーティングシステムの起動時に、前記計算機が備えるハードウェアを制御し、前記第1のオペレーティングシステムの起動処理を実行する第1のハードウェア制御部を格納し、前記記憶装置は、前記第1のオペレーティングシステムの実行イメージである第1のオペレーティングシステムイメージと、前記第1のオペレーティングシステムを起動する第1のオペレーティングシステムブートローダと、前記第2のオペレーティングシステムの実行イメージである第2のオペレーティングシステムイメージと、前記第2のオペレーティングシステムを起動する第2のオペレーティングシステムブートローダと、前記第2のオペレーティングシステムの起動時に、前記計算機が備えるハードウェアを制御し、前記第2のオペレーティングシステムの起動処理を実行する第2のハードウェア制御部と、

前記第2のハードウェア制御部が参照する情報が格納される前記第1のメモリにおける記憶領域の絶対アドレスであるアドレスデータを書き換えるアドレス書換部と、を格納し、前記第2のハードウェア制御部は、当該第2のハードウェア制御部を起動するための起動部を含み、

前記方法は、前記プロセッサが、電源が投入された場合、前記第2のメモリに格納される前記第1のハードウェア制御部を前記第1のメモリに書き込み、前記第1のハードウェア制御部を実行する第1のステップと、前記プロセッサによって実行される前記第1のハードウェア制御部が、前記記憶装置から前記第2のハードウェア制御部、及び前記アドレス書換部を読み出して、前記第1のメ

10

20

30

40

50

モリの所定の記憶領域に書き込む第2のステップと、

前記プロセッサによって実行される第1のハードウェア制御部が、前記第2のハードウェア制御部に含まれる前記起動部が格納される記憶領域の先頭アドレスを取得して、ベースアドレスデータとして前記第1のメモリに書き込む第3のステップと、

前記プロセッサによって実行される前記第1のハードウェア制御部が、前記記憶装置から前記第1のオペレーティングシステムブートローダを読み出して、前記第1のメモリに書き込む第4のステップと、

前記プロセッサによって実行される前記第1のハードウェア制御部が、前記第1のメモリに書き込まれた第1のオペレーティングシステムブートローダを起動する第5のステップと、

10

前記プロセッサによって実行される前記第1のオペレーティングシステムブートローダが、前記記憶装置から前記第1のオペレーティングシステムイメージを読み出して、前記第1のメモリに書き込む第6のステップと、

前記プロセッサによって実行される前記第1のオペレーティングシステムブートローダが、前記第1のメモリに書き込まれた第1のオペレーティングシステムイメージを実行することによって前記第1のオペレーティングシステムを起動する第7のステップと、

前記プロセッサによって実行される前記第1のオペレーティングシステムが、前記アドレス書換部を起動する第8のステップと、

前記プロセッサによって実行される前記アドレス書換部が、前記第1のメモリに書き込まれたベースアドレスデータを取得する第9のステップと、

20

前記プロセッサによって実行されるアドレス書換部が、書換対象のアドレスデータが格納される記憶領域のアドレスである対象アドレスを取得する第10のステップと、

前記プロセッサによって実行されるアドレス書換部が、前記取得されたベースアドレスデータに基づいて、前記取得された対象アドレスに対応する記憶領域に格納される前記アドレスデータを書き換える第11のステップと、

前記プロセッサによって実行されるアドレス書換部が、前記起動部を起動する第12のステップと、

前記プロセッサによって実行される前記起動部は、前記書き換えられたアドレスデータを用いて、前記第2のハードウェア制御部を起動する第13のステップと、

前記プロセッサによって実行される前記第2のハードウェア制御部が、前記記憶装置から前記第2のオペレーティングシステムブートローダを読み出して、前記第1のメモリに書き込む第14のステップと、

30

前記プロセッサによって実行される前記第2のハードウェア制御部が、前記第1のメモリに書き込まれた第2のオペレーティングシステムブートローダを起動する第15のステップと、

前記プロセッサによって実行される前記第2のオペレーティングシステムブートローダが、前記記憶装置から前記第2のオペレーティングシステムイメージを読み出して、前記第1のメモリに書き込む第16のステップと、

前記プロセッサによって実行される前記第2のオペレーティングシステムブートローダが、前記第1のメモリに書き込まれた第2のオペレーティングシステムイメージを実行することによって前記第2のオペレーティングシステムを起動する第17のステップと、を含むことを特徴する起動方法。

40

#### 【請求項6】

請求項5に記載の起動方法であって、

前記第10のステップでは、前記第2のハードウェア制御部から前記対象アドレスに関する情報を取得し、

前記第11のステップでは、前記取得された対象アドレスに対応する記憶領域に格納されるアドレスデータに前記ベースアドレスデータを加算することによって、当該アドレスデータを書き換えることを特徴とする起動方法。

#### 【請求項7】

50

請求項 6 に記載の起動方法であって、

前記第 1 のステップでは、前記第 2 のハードウェア制御部の実行形式のファイルを参考することによって前記対象アドレスに関する情報を取得することを特徴とする起動方法。

。

**【請求項 8】**

請求項 7 に記載の起動方法であって、

前記記憶装置は、第 1 の記憶装置及び第 2 の記憶装置を含み、

前記第 1 の記憶装置は、前記第 1 のオペレーティングシステムイメージ、前記第 1 のオペレーティングシステムブートローダ、前記第 2 のハードウェア制御部、及び前記アドレス書換部を格納し、

。

前記第 2 の記憶装置は、前記第 2 のオペレーティングシステムイメージ、及び前記第 2 のオペレーティングシステムブートローダを格納することを特徴とする起動方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、一つの計算機上に複数の OS が稼働する計算機システム、及び計算機の起動方法に関する。

**【背景技術】**

**【0002】**

近年、物理計算機上のハードウェアリソースを有効に活用するために、一台の物理計算機上で二つ以上の OS (オペレーティングシステム) を起動する技術が注目されている (例えば、特許文献 1 及び特許文献 2 参照)。 20

**【0003】**

特許文献 1 には、「マルチオペレーティングシステム計算機は、優先度が設定された複数のタスクを優先度順に実行する第 1 の OS (オペレーティングシステム) と、前記第 1 の OS と異なる第 2 の OS とを動作 OS として交互に動作させるマルチオペレーティングシステム計算機であって、前記第 1 の OS が動作 OS として動作しているときに前記複数のタスクのうち所定の優先度が設定された所定のタスクであって動作 OS の切替え契機を特定するための切替え契機タスクとして用いられるタスクが実行された場合に、動作 OS を前記第 1 の OS から前記第 2 の OS に切り替える OS 切替え部」を備えることが記載されている。 30

**【0004】**

また、特許文献 2 には、「第 1 の OS と第 2 の OS との少なくとも 2 つの OS を起動するマルチ OS 起動装置において、(1) メモリ領域を有し、前記メモリ領域に対してメモリ空間が定義される 1 次記憶部と、(2) セカンドブートローダと、前記第 2 の OS とを記憶する 2 次記憶部と、(3) CPU に対する制御情報を示すコンテキストであって前記第 1 の OS 用のコンテキストである第 1 のコンテキストで動作する前記第 1 の OS のもとで動作するファーストブートローダを前記第 1 のコンテキストで動作中の前記第 1 の OS のもとで動作させることにより、前記第 1 の OS が管理する第 1 のメモリ空間として前記第 1 のコンテキストにより前記 1 次記憶装置に対して定義された前記 1 次記憶部のメモリ領域に前記 2 次記憶部から前記セカンドブートローダと前記第 2 の OS とを前記ファーストブートローダにロードさせる OS 実行部と、(4) 前記第 1 のメモリ空間として定義されたメモリ領域にロードされた前記セカンドブートローダを前記第 1 のコンテキストで動作中の前記第 1 の OS のもとで実行することにより前記第 2 の OS が管理する第 2 のメモリ空間として定義されるメモリ領域と前記セカンドブートローダ及び前記第 2 の OS がロードされたメモリ領域とを含む第 3 のメモリ空間を前記 1 次記憶部に対して定義する前記セカンドブートローダ用のコンテキストを前記セカンドブートローダに生成させると共に生成された前記セカンドブートローダ用のコンテキストへ前記第 1 のコンテキストから切り替えさせ、前記セカンドブートローダ用のコンテキストのもとで前記セカンドブートローダを実行することにより前記第 3 のメモリ空間に含まれる前記第 2 のメモリ空間として 40

10

20

30

40

50

定義された前記 1 次記憶部のメモリ領域に前記ファーストブートローダによって前記 1 次記憶部のメモリ領域にロードされた前記第 2 の OS を前記セカンドブートローダにロードさせると共に前記第 2 の OS 用のコンテキストを生成させ、生成された前記第 2 の OS 用のコンテキストへ前記セカンドブートローダ用のコンテキストから切り替えさせ、前記第 2 の OS 用のコンテキストのもとで前記セカンドブートローダに前記第 2 の OS の起動を実行させるローダ実行部と」を備えることが記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献 1】特開平 11 - 149385 号公報

10

【特許文献 2】国際公開第 2009 / 113394 号

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献 1 及び特許文献 2 では、OS 1 のデバイスドライバが、外部記憶装置から OS 2 のブートローダ及びイメージファイルを読み出し、OS 2 用のメモリ領域に書き込むことによって、OS 2 を起動させることを特徴とする。

【0007】

しかし、セキュリティ上の理由で、OS 1 が、OS 2 のブートローダ及びイメージファイルが格納される記憶領域に対するアクセスが許可されていない場合がある。また、OS 1 のイメージファイル及び OS 2 のイメージファイルが異なる外部記憶装置に格納されている場合、OS 1 のカーネルが古い等の理由によって、OS 1 が、OS 2 のイメージファイルが格納される外部記憶装置のデバイスドライバを使用できない場合がある。前述のように、セキュリティ及びハードウェア構成の制限によって、OS 2 を起動することができない場合が存在する。

20

【0008】

本発明は、OS 1 が直接関与することなく、通常の起動処理と同様の手順に従って OS 2 を起動するためのシステム及び起動方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

30

本願において開示される発明の代表的な一例を示せば以下の通りである。すなわち、複数のオペレーティングシステムが稼働する計算機を複数備える計算機システムであって、前記複数の計算機の各々は、プロセッサ、前記プロセッサに接続される第 1 のメモリ、前記プロセッサに接続される第 2 のメモリ、前記プロセッサに接続される I/O デバイス、及び前記プロセッサに接続される記憶装置を有し、前記複数のオペレーティングシステムは、第 1 のオペレーティングシステム及び第 2 のオペレーティングシステムを含み、前記第 2 のメモリは、前記第 1 のオペレーティングシステムの起動時に、前記計算機が備えるハードウェアを制御し、前記第 1 のオペレーティングシステムの起動処理を実行する第 1 のハードウェア制御部を格納し、前記記憶装置は、前記第 1 のオペレーティングシステムの実行イメージである第 1 のオペレーティングシステムイメージと、前記第 1 のオペレーティングシステムを起動する第 1 のオペレーティングシステムブートローダと、前記第 2 のオペレーティングシステムの実行イメージである第 2 のオペレーティングシステムイメージと、前記第 2 のオペレーティングシステムを起動する第 2 のオペレーティングシステムブートローダと、前記第 2 のオペレーティングシステムの起動時に、前記計算機が備えるハードウェアを制御し、前記第 2 のオペレーティングシステムの起動処理を実行する第 2 のハードウェア制御部と、前記第 2 のハードウェア制御部が参照する情報が格納される前記第 1 のメモリにおける記憶領域の絶対アドレスであるアドレスデータを書き換えるアドレス書換部と、を格納し、前記第 2 のハードウェア制御部は、当該第 2 のハードウェア制御部を起動するための起動部を含み、前記プロセッサは、電源が投入された場合、前記第 2 のメモリに格納される前記第 1 のハードウェア制御部を前記第 1 のメモリに書き込み

40

50

、前記第1のハードウェア制御部を実行し、前記第1のハードウェア制御部は、前記記憶装置から前記第2のハードウェア制御部、及び前記アドレス書換部を読み出して、前記第1のメモリの所定の記憶領域に書き込み、前記第2のハードウェア制御部に含まれる前記起動部が格納される記憶領域の先頭アドレスを取得して、ベースアドレスデータとして前記第1のメモリに書き込み、前記記憶装置から前記第1のオペレーティングシステムブートローダを読み出して、前記第1のメモリに書き込み、前記第1のメモリに書き込まれた第1のオペレーティングシステムブートローダを起動し、前記第1のオペレーティングシステムブートローダは、前記記憶装置から前記第1のオペレーティングシステムイメージを読み出して、前記第1のメモリに書き込み、前記第1のメモリに書き込まれた第1のオペレーティングシステムイメージを実行することによって前記第1のオペレーティングシステムを起動し、前記第1のオペレーティングシステムは、前記アドレス書換部を起動し、前記アドレス書換部は、前記第1のメモリに書き込まれたベースアドレスデータを取得し、書換対象のアドレスデータが格納される記憶領域のアドレスである対象アドレスを取得し、前記取得されたベースアドレスデータに基づいて、前記取得された対象アドレスに対応する記憶領域に格納される前記アドレスデータを書き換え、前記起動部を起動し、前記起動部は、前記書き換えられたアドレスデータを用いて、前記第2のハードウェア制御部を起動し、前記第2のハードウェア制御部は、前記記憶装置から前記第2のオペレーティングシステムブートローダを読み出して、前記第1のメモリに書き込み、前記第1のメモリに書き込まれた第2のオペレーティングシステムブートローダを起動し、前記第2のオペレーティングシステムブートローダは、前記記憶装置から前記第2のオペレーティングシステムイメージを読み出して、前記第1のメモリに書き込み、前記第1のメモリに書き込まれた第2のオペレーティングシステムイメージを実行することによって前記第2のオペレーティングシステムを起動することを特徴する。

10

【発明の効果】

【0010】

本発明によれば、第1のOSが直接関与することなく第2のOSを起動することができる。また、アドレス書換部がアドレスデータを書き換えることによって、第2のハードウェア制御部がどの記憶領域に書き込まれても正常に動作することができる。

【0011】

前述した以外の課題、構成及び効果は、以下の実施形態の説明によって明らかにされる。

30

。

【図面の簡単な説明】

【0012】

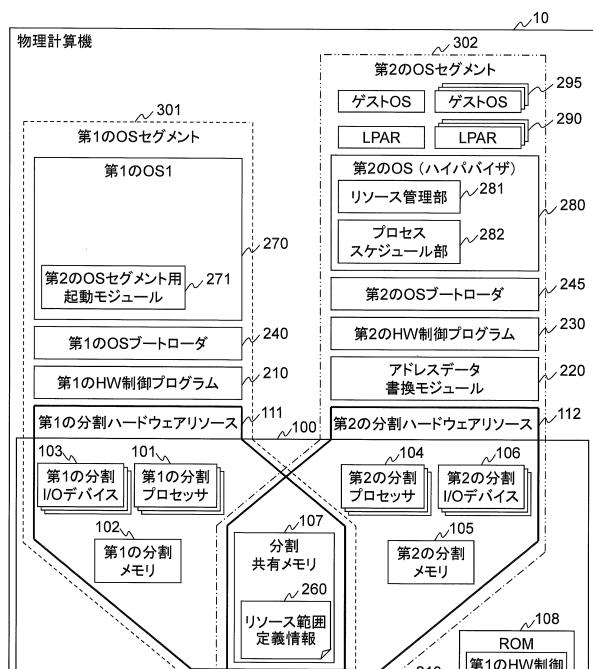

【図1】本発明の実施例1における計算機システムの構成の一例を示す説明図である。

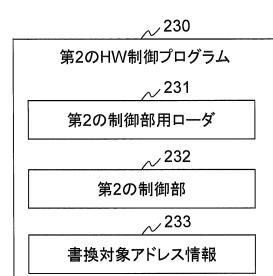

【図2】本発明の実施例1における第2のHW制御プログラムの構成例を示す説明図である。

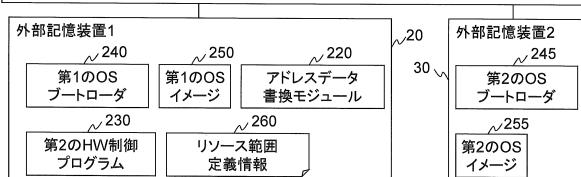

【図3】本発明の実施例1における第1のHW制御プログラムの構成例を示す説明図である。

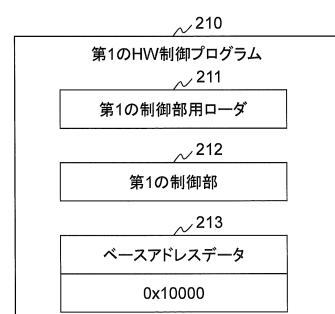

【図4】本発明の実施例1におけるアドレスデータ書換モジュールの構成例を示す説明図である。

40

【図5】本発明の実施例1におけるリソース範囲定義情報の一例を示す説明図である。

【図6】本発明の実施例1の書換対象アドレス情報の一例を示す説明図である。

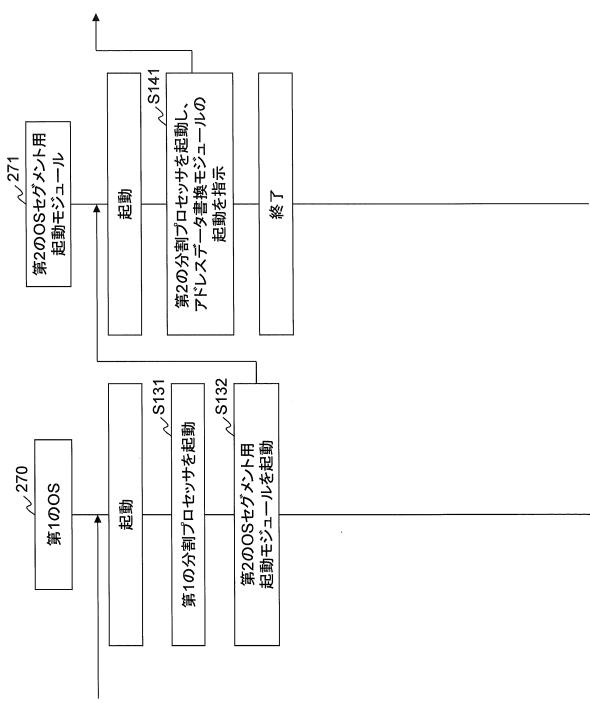

【図7A】本発明の実施例1における計算機システムの起動処理を説明するシーケンス図である。

【図7B】本発明の実施例1における計算機システムの起動処理を説明するシーケンス図である。

【図7C】本発明の実施例1における計算機システムの起動処理を説明するシーケンス図である。

【図7D】本発明の実施例1における計算機システムの起動処理を説明するシーケンス図である。

50

【図8】本発明の実施例1における第2の制御部用ローダのアドレスデータの変化の状態を示す説明図である。

【発明を実施するための形態】

【0013】

以下、図面を用いて実施例について説明する。

【実施例1】

【0014】

図1は、本発明の実施例1における計算機システムの構成の一例を示す説明図である。

【0015】

本実施例の計算機システムは、物理計算機10、第1の外部記憶装置20、及び第2の外部記憶装置30から構成される。物理計算機10は、第1の外部記憶装置20及び第2の外部記憶装置30と直接、又は、ネットワークを介して接続される。ネットワークとしては、WAN、及びLAN等が考えられる。なお、物理計算機10は、装置内部に記憶装置を備えていてもよい。

10

【0016】

物理計算機10は、所定の処理を実行するOSが稼働する計算機である。本実施例では、第1のOS270及び第2のOS280の二つのOSが稼働するものとする。なお、第1のOS270及び第2のOS280は、一般的なOS及び仮想化機能を提供するハイパバイザのいずれを適用してもよい。以下の説明では、第1のOS270を一般的なOS、第2のOS280をハイパバイザであるものとする。

20

【0017】

また、本実施例では、第1のOS270及び第2のOS280を並列に稼働させる。具体的には、第1のOS270の起動後、第2のOS280を起動させる起動方式を採用する。また、第2のOS280は、一般的な起動手順に沿って起動するようとする。

【0018】

これによって、第1のOS270によって第2のOS280のOSイメージが扱われないため、セキュリティ面の課題を解決することができる。また、第1のOS270のデバイスドライバに依存することなく第2のOS280を起動することができる。

【0019】

物理計算機10は、ハードウェアリソース100として複数のプロセッサ、複数のメモリ、複数のI/Oデバイス、及びROM108を備える。

30

【0020】

プロセッサは、メモリに格納されるプログラムを実行する。プロセッサがプログラムを実行することによって、OS等の機能が実現される。以下、プログラムを主体に処理を説明する場合、当該プログラムがプロセッサによって実行されていることを示す。

【0021】

メモリは、プロセッサによって実行されるプログラム及び当該プログラムの実行に必要な情報を格納する。また、メモリは、各プログラムのワークエリアを含む。

【0022】

I/Oデバイスは、外部装置と接続し、外部から情報を入力し、外部に情報を出力するためのデバイスである。例えば、I/Oデバイスとしては、ネットワークインターフェース、及びディスクインターフェース等が考えられる。

40

【0023】

ROM108は、OSの起動時に用いられる第1のHW(ハードウェア)制御プログラム210を格納するための専用の記憶媒体である。第1のHW制御プログラム210は、第1の外部記憶装置20等に格納されてもよい。なお、第1のHW制御プログラム210としては、BIOS(Basic Input/Output System)が考えられる。

【0024】

第1のHW制御プログラム210は、OSの起動処理時に、物理計算機10のハードウ

50

エアリソース 100 を制御し、OS ブートローダ 及び OS イメージ等、OS の起動に必要なプログラムを外部記憶装置から読み出し、読み出されたプログラムをメモリに書き込む。

#### 【0025】

第 1 の外部記憶装置 20 及び第 2 の外部記憶装置 30 は、物理計算機 10 が OS を起動するために必要なプログラム及び情報を格納する装置である。

#### 【0026】

第 1 の外部記憶装置 20 及び第 2 の外部記憶装置 30 は、例えば、HDD (Hard Disk Drive) 及び SSD (Solid State Drive) 等の記憶媒体が考えられる。また、第 1 の外部記憶装置 20 及び第 2 の外部記憶装置 30 は、コントローラ及び複数の記憶媒体を備えるストレージシステムであってもよい。10

#### 【0027】

物理計算機 10 は、第 1 の外部記憶装置 20 及び第 2 の外部記憶装置 30 からプログラム及び情報を読み出し、複数の OS を起動させる。ここで、第 1 の外部記憶装置 20 及び第 2 の外部記憶装置 30 に格納されるプログラム及び情報について説明する。

#### 【0028】

第 1 の外部記憶装置 20 は、プログラムとして、第 1 の OS ブートローダ 240、第 1 の OS イメージ 250、アドレスデータ書換モジュール 220、及び第 2 の HW 制御プログラム 230 を格納し、また、情報としてリソース範囲定義情報 260 を格納する。

#### 【0029】

第 1 の OS イメージ 250 は、第 1 の OS 270 の OS イメージである。20

#### 【0030】

第 1 の OS ブートローダ 240 は、第 1 の OS イメージ 250 を用いて第 1 の OS 270 を起動する。本実施例では、第 1 の OS ブートローダ 240 は、第 1 の外部記憶装置 20 から第 1 の OS イメージ 250 を読み出し、第 1 の OS イメージ 250 を第 1 の分割メモリ 102 に書き込み、第 1 の OS 270 を起動する。

#### 【0031】

第 2 の HW 制御プログラム 230 は、OS の起動処理時に、物理計算機 10 のハードウェアリソース 100 を制御し、OS ブートローダ 及び OS イメージ等、OS の起動に必要なプログラムを外部記憶装置から読み出し、読み出されたプログラムをメモリに書き込む。30

#### 【0032】

アドレスデータ書換モジュール 220 は、第 2 の HW 制御プログラム 230 の起動時にアドレスデータを書き換え、その後、第 2 の HW 制御プログラム 230 を起動する。ここで、アドレスデータは、第 2 の HW 制御プログラム 230 の起動時に参照される関数等が格納される記憶領域の先頭アドレス（ポインタ）である。

#### 【0033】

リソース範囲定義情報 260 は、ハードウェアリソース 100 の割り当てに関する情報を格納する。なお、リソース範囲定義情報 260 の詳細については、図 5 を用いて後述する。40

#### 【0034】

第 2 の外部記憶装置 30 は、プログラムとして、第 2 の OS ブートローダ 245 及び第 2 の OS イメージ 255 を格納する。

#### 【0035】

第 2 の OS イメージ 255 は、第 2 の OS 280 の OS イメージである。

#### 【0036】

第 2 の OS ブートローダ 245 は、第 2 の OS イメージ 255 を用いて第 2 の OS 280 を起動する。本実施例では、第 2 の OS ブートローダ 245 は、第 2 の外部記憶装置 30 から第 2 の OS イメージ 255 を読み出し、第 2 の OS イメージ 255 を第 2 の分割メモリ 105 に書き込み、第 2 の OS 280 を起動する。50

**【0037】**

なお、第2のOSブートローダ245及び第2のOSイメージ255は、第1の外部記憶装置20に格納されてもよい。

**【0038】**

ハードウェアリソース100は、リソース範囲定義情報260に基づいて割り当てられる。本実施例では、OS等の各プログラムが排他的に使用するハードウェアリソースと、各プログラムが共有して使用するハードウェアリソースとに分けられる。

**【0039】**

ここで、排他的に使用するハードウェアリソースは、当該ハードウェアリソースが割り当てられたプログラムが占有的に使用し、他のプログラムが使用できないハードウェアリソースを示す。10

**【0040】**

以下の説明では、リソース範囲定義情報260に基づいて分割されたハードウェアリソース100を分割ハードウェアリソース100と記載する。本実施例では、分割ハードウェアリソース100には、分割プロセッサ、分割メモリ、分割共有メモリ、及び分割I/Oデバイスが含まれる。

**【0041】**

また、以下の説明では、分割ハードウェアリソース、及び分割ハードウェアリソース上の稼働するプログラムをまとめてOSセグメントと記載する。本実施例では、一つのOSセグメントに一つのOSが稼働するものとする。20

**【0042】**

本実施例では、物理計算機10には、第1のOSセグメント301及び第2のOSセグメント302の二つのOSセグメントが存在する。

**【0043】**

第1のOSセグメント301には、第1の分割ハードウェアリソース111が割り当てられる。第1の分割ハードウェアリソース111は、第1の分割プロセッサ101、第1の分割メモリ102、第1の分割I/Oデバイス103、及び分割共有メモリ107を含む。また、第1の分割ハードウェアリソース111上では、第1のHW制御プログラム210、第1のOSブートローダ240、及び第1のOS270が稼働する。

**【0044】**

第2のOSセグメント302には、第2の分割ハードウェアリソース112が割り当てられる。第2の分割ハードウェアリソース112は、第2の分割プロセッサ104、第2の分割メモリ105、第2の分割I/Oデバイス106、及び分割共有メモリ107を含む。また、アドレスデータ書換モジュール220、第2のHW制御プログラム230、第2のOSブートローダ245、及び第2のOS280が稼働する。

**【0045】**

前述したように、各OSセグメントに含まれるプログラムは、当該OSセグメントに割り当てられた分割ハードウェアリソースのみを使用し、他のOSセグメントに割り当てられた分割ハードウェアリソースは使用しない。

**【0046】**

ただし、後述するように、第2のOSセグメント用起動モジュール271を実行する第1の分割プロセッサ101は、第2のOS280の起動時に、第2の分割プロセッサ104に起動命令を発行することによって、当該第2の分割プロセッサ104を起動させる。ただし、当該処理は、第2のOSセグメント302の初期起動時にのみ許可される処理である。また、当該処理は、単に、分割プロセッサを起動させる処理であり、第1のOSセグメント301が、占有的に使用するわけではないため、セキュリティ及びハードウェアリソースの割当ポリシ等の問題は発生しない。

**【0047】**

ここで、OSセグメント上で稼働するプログラムについて説明する。なお、第1の外部記憶装置20と同一のプログラムについては説明を省略する。50

**【0048】**

第1のOSセグメント301上では、第1のHW制御プログラム210、第1のOSブートローダ240、及び第1のOS270が稼働する。

**【0049】**

第1のOS270は、第1の分割ハードウェアリソース111上で稼働するOSである。第1のOS270は、第2のOSセグメント用起動モジュール271を含む。

**【0050】**

第2のOSセグメント用起動モジュール271は、第2のOS280を起動させるための命令を発効する。具体的には、第2のOSセグメント用起動モジュール271は、第2の分割プロセッサ104の起動を指示する。

10

**【0051】**

なお、第2のOSセグメント用起動モジュール271を実行する第1の分割プロセッサ101が、第2の分割プロセッサ104を操作（起動）することになる。しかし、第2のOSセグメント302に割り当てられた第2の分割ハードウェアリソース112の初期起動時に限り許可される処理であり、セキュリティ面の問題も発生しない。

**【0052】**

第2のOSセグメント302上では、アドレスデータ書換モジュール220、第2のHW制御プログラム230、第2のOSブートローダ245、及び第2のOS280が稼働する。

20

**【0053】**

本実施例の第2のOS280は、ハイパバイザに対応する。ハイパバイザは、第2の分割ハードウェアリソース112を用いて複数のLPAR290を生成し、生成されたLPAR290上で複数のゲストOS295を稼働させる。本実施例のハイパバイザは、リソース管理部281及びプロセススケジュール部282を有する。

**【0054】**

リソース管理部281は、リソース範囲定義情報260に基づいて、第2の分割ハードウェアリソース112を管理する。プロセススケジュール部282は、第2の分割ハードウェアリソース112を用いて生成されたLPAR290上にゲストOS295を稼働させる。

**【0055】**

30

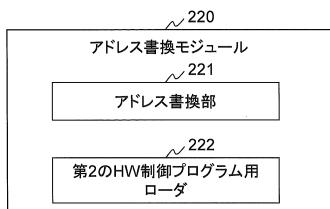

図2は、本発明の実施例1における第2のHW制御プログラム230の構成例を示す説明図である。

**【0056】**

第2のHW制御プログラム230は、第2のOS280の起動時に実行されるプログラムである。第2のHW制御プログラム230は、第2の制御部用ローダ231、第2の制御部232及び書換対象アドレス情報233を含む。

**【0057】**

第2の制御部用ローダ231は、第2の制御部232を起動する。具体的には、第2の制御部用ローダ231は、第2の分割メモリ105の空き領域に第2の制御部232を書き込み、当該第2の制御部232を起動する。

40

**【0058】**

本実施例では、後述するアドレスデータ書換モジュール220によって、第2の制御部用ローダ231が保持するアドレスデータに関する情報が変換される。

**【0059】**

第2の制御部232は、第2の制御部用ローダ231によって起動された後、第2の分割ハードウェアリソース112を制御する。また、第2の制御部232は、第2の外部記憶装置30から第2のOSブートローダ245を読み出し、第2の分割メモリ105に読み出された第2のOSブートローダ245を書き込む。その後、第2の制御部232は、第2の分割メモリ105に書き込まれた第2のOSブートローダ245を起動する。

**【0060】**

50

書換対象アドレス情報 233 は、書換対象のアドレスデータが格納される記憶領域に関する情報を格納する。書換対象アドレス情報 233 の詳細については、図 6 を用いて後述する。

#### 【0061】

一般的な計算機には、計算機のハードウェアリソースを制御する HW 制御プログラムが存在する。HW 制御プログラムは、OS の起動時に、OS イメージより先にメモリに書き込まれ、実行される。

#### 【0062】

図 2 に示すように、一般的な HW 制御プログラムは、制御部用ローダを含む。制御部用ローダは、計算機の起動時に最初に実行されるプログラムである。そのため、制御部用ローダは、関数等の一部のデータの読み出しについては、絶対アドレスで表記されたアドレスデータを参照するように設定されている。10

#### 【0063】

二つの OS を独立に起動させるために、一つの計算機上に二つの異なる HW 制御プログラムを実行する場合、アドレスデータが重複することによって、制御部用ローダが正常に動作しない可能性がある。また、HW 制御プログラムをそれぞれ異なる記憶領域に書き込んだ場合であっても、同様の問題が発生する。

#### 【0064】

すなわち、HW 制御プログラムは、分割メモリに書き込まれた場合、格納される記憶領域が通常の記憶領域と異なる。そのため、アドレスデータが示す参照先のアドレスが不適切なアドレスとなり、制御部用ローダが正常に動作しない可能性がある。20

#### 【0065】

本発明では、第 2 の HW 制御プログラム 230 が書き込まれる記憶領域に依存することなく、第 2 の制御部用ローダ 231 が正常に動作するための機能を提供する。

#### 【0066】

具体的には、アドレスデータ書換モジュール 220 が、第 2 の HW 制御プログラム 230 が書き込まれた記憶領域に対応させて、第 2 の制御部用ローダ 231 に設定されるアドレスデータを書き換える。これによって、参照先のアドレスが適切なアドレスに変更されるため、第 2 の制御部用ローダ 231 は、正常に関数等を呼び出し、処理を実行することができる。30

#### 【0067】

なお、第 2 の制御部 232 は、第 2 の制御部用ローダ 231 によって第 2 の分割メモリ 105 の空き領域に書き込まれ、起動される。したがって、第 2 の制御部用ローダ 231 が正常に稼働することによって、第 2 の制御部 232 が第 1 の分割メモリ 102 上で稼働するという問題は発生しない。

#### 【0068】

図 3 は、本発明の実施例 1 における第 1 の HW 制御プログラム 210 の構成例を示す説明図である。

#### 【0069】

第 1 の HW 制御プログラム 210 は、第 1 の OS 270 の起動時、すなわち、システム起動時に実行されるプログラムである。第 1 の HW 制御プログラム 210 は、第 1 の制御部用ローダ 211、第 1 の制御部 212、及びベースアドレスデータ 213 を含む。40

#### 【0070】

第 1 の制御部用ローダ 211 は、第 1 の制御部 212 を起動する。具体的には、第 1 の制御部用ローダ 211 は、第 1 の分割メモリ 102 の空き領域に第 1 の制御部 212 を書き込み、当該第 1 の制御部 212 を起動する。

#### 【0071】

第 1 の制御部 212 は、第 1 の制御部用ローダ 211 によって起動された後、第 1 の分割ハードウェアリソース 111 を制御する。本実施例の第 1 の制御部 212 は、第 1 の OS 270 を起動する前に、以下のような処理を実行する。50

**【0072】**

第1の制御部212は、アドレスデータ書換モジュール220、及び第2のHW制御プログラム230を第1の外部記憶装置20から読み出し、第2の分割メモリ105に読み出されたアドレスデータ書換モジュール220、及び第2のHW制御プログラム230を書き込む。

**【0073】**

第1の制御部212は、HW制御プログラム2に含まれる第2の制御部用ローダ231が格納される記憶領域の先頭アドレスを取得し、取得されたアドレスをベースアドレスデータ213として保持する。さらに、第1の制御部212は、ベースアドレスデータ213を、第2の分割メモリ105の特定の記憶領域に書き込む。

10

**【0074】**

なお、当該記憶領域は、予め、定義された記憶領域であるものとする。また、アドレスデータ書換モジュール220は、当該記憶領域を参照するように予め設定されているものとする。

**【0075】**

前述した処理が完了した後、第1の制御部212は、第1の外部記憶装置20から第1のOSブートローダ240を読み出し、第1の分割メモリ102に読み出された第1のOSブートローダ240を書き込む。その後、第1の制御部212は、第1の分割メモリ102に書き込まれた第1のOSブートローダ240を起動する。

**【0076】**

20

ベースアドレスデータ213は、第2の制御部用ローダ231が格納される記憶領域の先頭アドレスである。

**【0077】**

図4は、本発明の実施例1におけるアドレスデータ書換モジュール220の構成例を示す説明図である。

**【0078】**

アドレスデータ書換モジュール220は、第2の制御部用ローダ231が保持するアドレスデータを変換する。アドレスデータ書換モジュール220は、第1のOS270起動前に、第1のHW制御プログラム210によって、第1の外部記憶装置20から読み出され、第2の分割メモリ105に書き込まれる。また、アドレスデータ書換モジュール220は、第2のOSセグメント用起動モジュール271によって起動される。

30

**【0079】**

アドレスデータ書換モジュール220は、アドレスデータ書換部221、及び第2のHW制御プログラム用ローダ222を含む。

**【0080】**

アドレスデータ書換部221は、第2の制御部用ローダ231におけるアドレスデータを変換する。具体的には、以下のような処理が実行される。

**【0081】**

アドレスデータ書換部221は、第2のHW制御プログラム230のリロケーションセクションを参照することによって、アドレスデータが格納される記憶領域のアドレスを取得する。

40

**【0082】**

アドレスデータ書換部221は、取得されたアドレスに対応する記憶領域に格納されるアドレスデータに、ベースアドレスデータ213を加算することによって、当該アドレスデータを書き換える。

**【0083】**

なお、予め、第2のHW制御プログラム230にアドレスデータが格納される記憶領域のアドレスの情報が含まれる場合、アドレスデータ書換モジュール220は、第2のHW制御プログラム230に含まれる情報を参照することによって、当該アドレスデータが含まれる記憶領域のアドレスを取得してもよい。

50

**【0084】**

第2のHW制御プログラム用ローダ222は、第2のHW制御プログラム230に含まれる第2の制御部用ローダ231のアドレスデータが書き換えられた後、当該第2の制御部用ローダ231を起動する。

**【0085】**

書き換えられたアドレスデータは、第2の分割メモリ105の所定の記憶領域に対応するアドレスデータに変換されているため、第2の制御部用ローダ231は、書き換えられたアドレスデータに基づいて、関数等を正しく参照することができる。したがって、第2の制御部用ローダ231は、正常に動作することができる。

**【0086】**

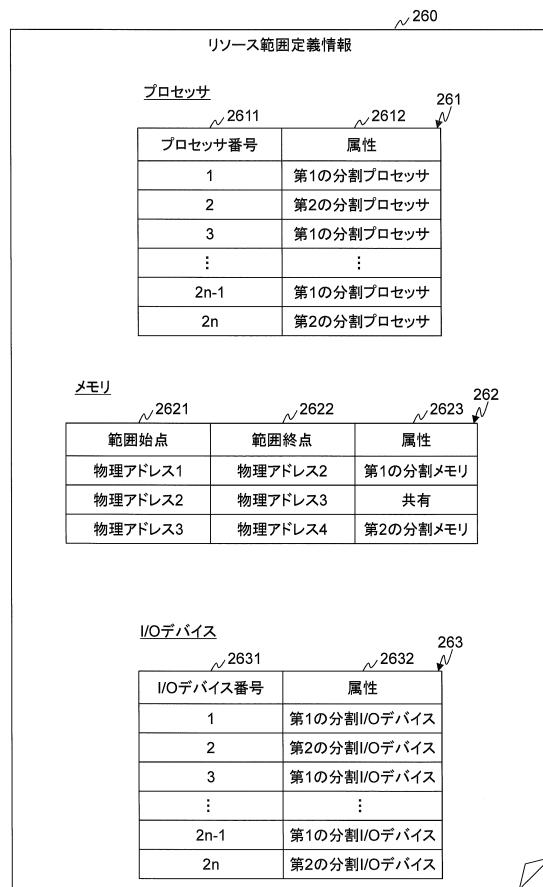

図5は、本発明の実施例1におけるリソース範囲定義情報260の一例を示す説明図である。

10

**【0087】**

リソース範囲定義情報260は、分割ハードウェアリソースとして割り当てるハードウェアリソース100の範囲(割当量、割当数等)に関する情報を格納する。本実施例では、リソース範囲定義情報260は、プロセッサの定義情報261、メモリの定義情報262、及びI/Oデバイスの定義情報263を含む。

**【0088】**

プロセッサの定義情報261は、プロセッサ番号2611及び属性2612を含む。プロセッサ番号2611は、物理計算機10が備えるプロセッサを一意に識別するための識別番号である。属性2612は、プロセッサの割り当て属性を示す情報である。

20

**【0089】**

各OSセグメントが共有して使用するプロセッサの場合、属性2612には共有して使用する旨の情報が格納される。例えば、属性2612には「共有」が格納される。

**【0090】**

また、OSセグメントが占有的に使用するプロセッサの場合、属性2612にはOSセグメントを特定するための情報が格納される。例えば、第1のOSセグメント301に割り当たられるプロセッサの場合、属性2612には「第1の分割プロセッサ」が格納される。これによって、各OSセグメントが占有的に使用するプロセッサを定義することができる。

30

**【0091】**

図5に示す例では、プロセッサ番号2611が奇数の識別番号であるプロセッサは、第1のOSセグメント301に割り当たられる第1の分割プロセッサ101として定義され、プロセッサ番号2611が偶数の識別番号であるプロセッサは、第2のOSセグメント302に割り当たられる第2の分割プロセッサ104として定義される。

**【0092】**

メモリの定義情報262は、範囲始点2621、範囲終点2622、及び属性2623を含む。

**【0093】**

範囲始点2621及び範囲終点2622は、分割メモリとして割り当てる記憶領域の始点及び終点のアドレスである。属性2623は、記憶領域の割り当て属性を示す情報である。なお、範囲始点2621及び範囲終点2622の代わりに、記憶領域の先頭アドレス及び記憶領域の長さを、記憶領域を特定する情報として用いてもよい。

40

**【0094】**

各OSセグメントが共有して使用する記憶領域、すなわち、分割共有メモリの場合、属性2623には「共有」が格納される。

**【0095】**

また、OSセグメントが占有的に使用する記憶領域の場合、属性2623にはOSセグメントを特定するための情報が格納される。例えば、第1のOSセグメント301に割り当たられる記憶領域の場合、属性2623には「第1の分割メモリ」が格納される。これ

50

によって、各OSセグメントが占有的に使用する記憶領域、すなわち、分割メモリを定義することができる。

#### 【0096】

図5に示す例では、物理アドレス1から物理アドレス2の範囲の記憶領域は、第1のOSセグメント301に割り当てられる第1の分割メモリ102として定義され、物理アドレス3から物理アドレス4の範囲の記憶領域は、第2のOSセグメント302に割り当てられる第2の分割メモリ105として定義される。また、物理アドレス2から物理アドレス3の範囲の記憶領域は、第1のOSセグメント301及び第2のOSセグメント302に割り当てられる分割共有メモリ107として定義される。

#### 【0097】

I/Oデバイスの定義情報263は、I/Oデバイス番号2631及び属性2632を含む。I/Oデバイス番号2631は、物理計算機10が備えるI/Oを一意に識別するための識別番号である。属性2632は、I/Oデバイスの割り当て属性を示す情報である。

#### 【0098】

各OSセグメントが共有して使用するI/Oデバイスの場合、属性2632には共有して使用する旨の情報が格納される。例えば、属性2632には「共有」が格納される。

#### 【0099】

また、OSセグメントが占有的に使用するI/Oデバイスの場合、属性2632にはOSセグメントを特定するための情報が格納される。例えば、第1のOSセグメント301に割り当てられるI/Oデバイスの場合、属性2632には「第1の分割I/Oデバイス」が格納される。これによって、各OSセグメントが占有的に使用するI/Oデバイスを定義することができる。

#### 【0100】

図5に示す例では、I/Oデバイス番号2631が奇数の識別番号であるI/Oデバイスは、第1のOSセグメント301に割り当てられる第1の分割I/Oデバイス103として定義され、I/Oデバイス番号2631が偶数の識別番号のI/Oデバイスは、第2のOSセグメント302に割り当てられる第2の分割I/Oデバイス106として定義される。

#### 【0101】

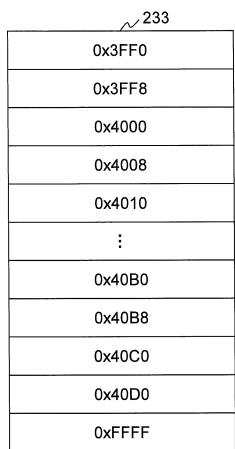

図6は、本発明の実施例1の書換対象アドレス情報233の一例を示す説明図である。

#### 【0102】

書換対象アドレス情報233は、第2の制御部用ローダ231が格納される記憶領域の先頭アドレスからのオフセットを格納する。

#### 【0103】

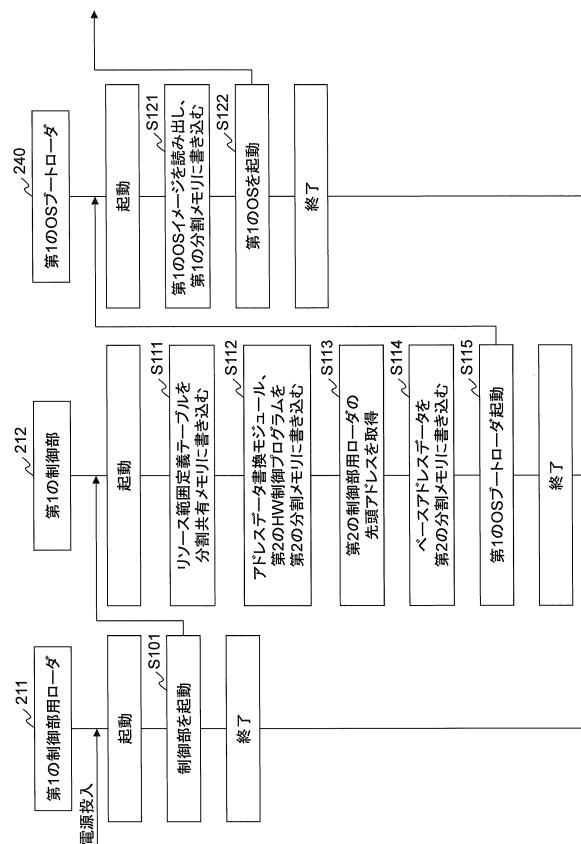

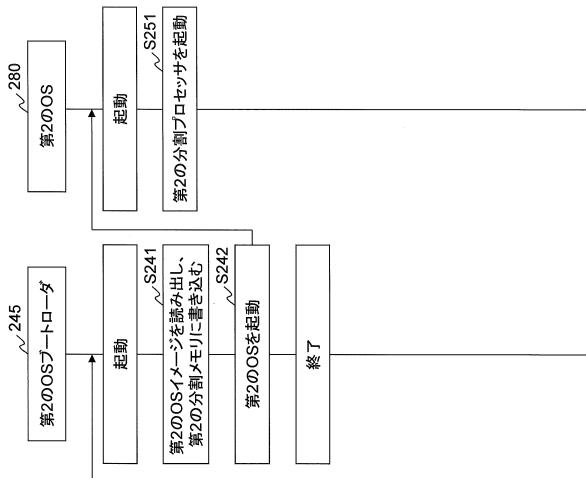

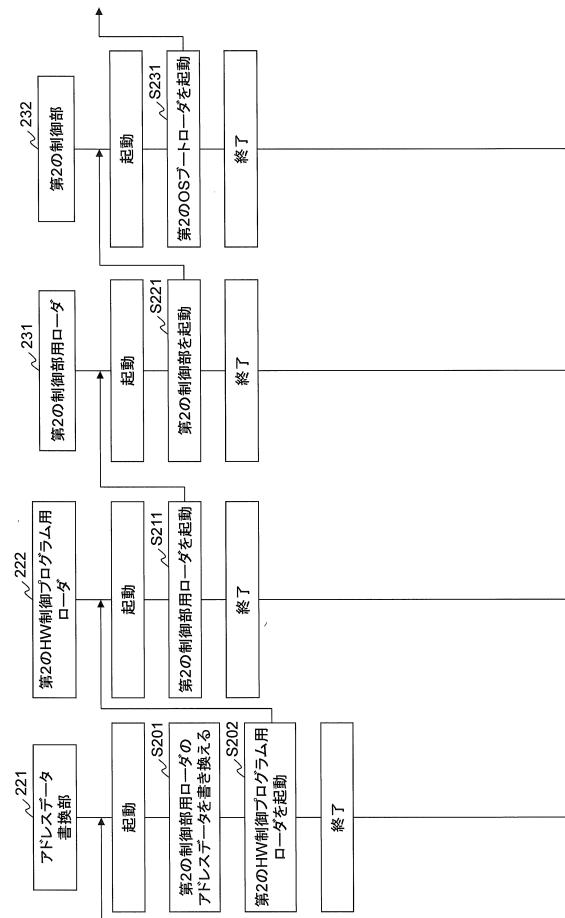

図7A、図7B、図7C、及び図7Dは、本発明の実施例1における計算機システムの起動処理を説明するシーケンス図である。

#### 【0104】

物理計算機10に電源が投入されると、まず、ROM108に格納される第1のHW制御プログラム210の第1の制御部用ローダ211が起動する。第1の制御部用ローダ211は、第1のHW制御プログラム210をメモリに書き込み、第1の制御部212を起動する(ステップS101)。その後、第1の制御部用ローダ211は、処理を終了する(ステップS102)。

#### 【0105】

本実施例では、第1の分割プロセッサ101に含まれる一つのプロセッサが、第1の制御部用ローダ211を実行し、また、第1の制御部用ローダ211によって起動された第1の制御部212を実行する。また、第1の制御部212は、第1の分割メモリ102の記憶領域に書き込まれる。

#### 【0106】

なお、第1の制御部用ローダ211及び第1の制御部212を実行するプロセッサ、及

10

20

30

40

50

び第1のHW制御プログラム210が書き込まれる記憶領域は、前述したものに限定されず、システム構成に合わせて適宜変更できる。

#### 【0107】

以下の説明では、第2の制御部用ローダ231を実行する一つの第1の分割プロセッサ101を第1の起動用プロセッサとも記載する。

#### 【0108】

第1の制御部212は、起動後、第1の外部記憶装置20から、リソース範囲定義情報260を読み出し、読み出されたリソース範囲定義情報260を分割共有メモリ107に書き込む（ステップS111）。

#### 【0109】

第1の制御部212は、第1の外部記憶装置20からアドレスデータ書換モジュール220及び第2のHW制御プログラム230を読み出し、リソース範囲定義情報260に基づいて、読み出されたアドレスデータ書換モジュール220及び第2のHW制御プログラム230を第2の分割メモリ105に書き込む（ステップS112）。

#### 【0110】

第1の制御部212は、第2の分割メモリ105に書き込まれた第2のHW制御プログラム230に含まれる第2の制御部用ローダ231が格納される記憶領域の先頭アドレスを取得する（ステップS113）。第1の制御部212は、取得された先頭アドレスをベースアドレスデータ213として保持する。

#### 【0111】

第1の制御部212は、リソース範囲定義情報260に基づいて、第2の分割メモリ105にベースアドレスデータ213を書き込む（ステップS114）。本実施例では、第1の制御部212は、第2の分割メモリ105の記憶領域のうち、予め、定義された記憶領域にベースアドレスデータ213を書き込む。

#### 【0112】

第1の制御部212は、第1のOSブートローダ240を第1の外部記憶装置20から読み出し、第1の分割メモリ102に読み出された第1のOSブートローダ240を書き込み、第1のOSブートローダ240を起動する（ステップS115）。その後、第1の制御部212は、処理を終了する。第1のOSブートローダ240は、第1の起動用プロセッサによって実行される。

#### 【0113】

なお、第1の制御部212は、第2の分割メモリ105へのアクセスを行っているが、第1のOS270起動前の処理であり、第1のOS270によって第2のOS280のデータを直接扱われることはない。したがって、セキュリティ上の問題は発生しない。

#### 【0114】

第1のOSブートローダ240は、起動後、第1の外部記憶装置20から第1のOSイメージ250を読み出し、リソース範囲定義情報260に基づいて、読み出された第1のOSイメージ250を第1の分割メモリ102に書き込む（ステップS121）。

#### 【0115】

第1のOSブートローダ240は、第1のOSイメージ250を用いて、第1のOS270を起動する（ステップS122）。その後、第1のOSブートローダ240は、処理を終了する。第1の起動用プロセッサが、第1のOSイメージ250を用いて、第1のOS270を起動する。

#### 【0116】

第1のOS270は、起動後、リソース範囲定義情報260に基づいて、第1のOS270が使用する第1の分割プロセッサ101を起動する（ステップS131）。これ以後、第1のOS270は、第1の分割プロセッサ101を用いて稼働する。

#### 【0117】

第1のOS270は、第2のOSセグメント用起動モジュール271を起動する（ステップS132）。その後、第1のOS270は、通常の処理を実行する。なお、本発明は

10

20

30

40

50

、第1のOS270が実行する処理の種類に限定されない。

#### 【0118】

第2のOSセグメント用起動モジュール271は、起動後、第2の分割プロセッサ104を起動させ、アドレスデータ書換モジュール220の起動を指示する(ステップS141)。その後、第2のOSセグメント用起動モジュール271は、処理を終了する。

#### 【0119】

具体的には、第2のOSセグメント用起動モジュール271は、第2の分割プロセッサ104のうちの少なくとも一つのプロセッサの起動命令を発行する。以下、第2のOSセグメント用起動モジュール271によって起動される第2の分割プロセッサ104を第2の起動用プロセッサとも記載する。

10

#### 【0120】

なお、ステップS141の処理は、第2のOSセグメント302の初期起動時にのみ許可される処理である。また、当該処理は、単に、分割プロセッサを起動させる処理であり、第1のOSセグメント301が、占有的に使用するわけではないため、セキュリティ及びハードウェアリソースの割当ポリシ等の問題は発生しない。

#### 【0121】

第2のOSセグメント用起動モジュール271によって起動された第2の起動用プロセッサは、リソース範囲定義情報260に基づいて、第2の分割メモリ105に書き込まれるアドレスデータ書換モジュール220を実行する。これによって、最初に、アドレスデータ書換部221が起動される。

20

#### 【0122】

アドレスデータ書換部221は、起動後、第2の制御部用ローダ231に設定されるアドレスデータを書き換える(ステップS201)。具体的には、以下のようないし処理が実行される。

#### 【0123】

まず、アドレスデータ書換部221は、第2の分割メモリ105に書き込まれた第2のHW制御プログラム230から書換対象アドレス情報233を取得する。これによって、書換対象のアドレスデータが特定される。

#### 【0124】

アドレスデータ書換部221は、第2の分割メモリ105に書き込まれるベースアドレスデータ213を取得する。

30

#### 【0125】

アドレスデータ書換部221は、書換対象アドレス情報233に基づいて、書換対象のアドレスデータが格納される記憶領域のアドレスデータに、ベースアドレスデータ213の値を加算することによって、アドレスデータを書き換える。例えば、第2の制御部用ローダ231のバイナリコードが書き換えられる。

#### 【0126】

以上がステップS201の処理の説明である。

#### 【0127】

次に、アドレスデータ書換部221は、第2のHW制御プログラム用ローダ222を起動する(ステップS202)。その後、アドレスデータ書換部221は、処理を終了する。第2のHW制御プログラム用ローダ222は、第2の起動用プロセッサによって実行される。

40

#### 【0128】

第2のHW制御プログラム用ローダ222は、起動後、第2の制御部用ローダ231を起動する(ステップS211)。その後、第2のHW制御プログラム用ローダ222は、処理を終了する。第2の制御部用ローダ231は、第2の起動用プロセッサによって実行される。

#### 【0129】

第2の制御部用ローダ231は、起動後、第2の制御部232を起動する(ステップS

50

221)。その後、第2の制御部用ローダ231は、処理を終了する。第2の制御部232は、第2の起動用プロセッサによって実行される。

#### 【0130】

本実施例では、第2の制御部用ローダ231は、書き換えられたアドレスデータを用いて処理を実行するため、不正なアドレスに基づくエラーは発生しない。なお、第2の制御部用ローダ231が実行する処理は、公知のものであるため詳細な説明は省略する。

#### 【0131】

第2の制御部232は、第2のOSブートローダ245を第2の外部記憶装置30から読み出し、第2の分割メモリ105に読み出された第2のOSブートローダ245を書き込み、第2のOSブートローダ245を起動する(ステップS231)。その後、第2の制御部232は、処理を終了する。第2のOSブートローダ245は、第2の起動用プロセッサによって実行される。

#### 【0132】

第2のOSブートローダ245は、起動後、第2の外部記憶装置30から第2のOSイメージ255を読み出し、リソース範囲定義情報260に基づいて、読み出された第2のOSイメージ255を第2の分割メモリ105に書き込む(ステップS241)。

#### 【0133】

第2のOSブートローダ245は、第2のOSイメージ255を用いて、第2のOS280を起動する(ステップS242)。その後、第2のOSブートローダ245は、処理を終了する。第2のプロセッサが、第2のOSイメージ255を用いて、第2のOS280を起動する。第2のOS280は、第2の起動用プロセッサによって実行される。

#### 【0134】

第2のOS280は、起動後、リソース範囲定義情報260に基づいて、第2のOS280が使用する第2の分割プロセッサ104を起動する(ステップS251)。これ以後、第2のOS280は、第2の分割プロセッサ104を用いて稼働する。

#### 【0135】

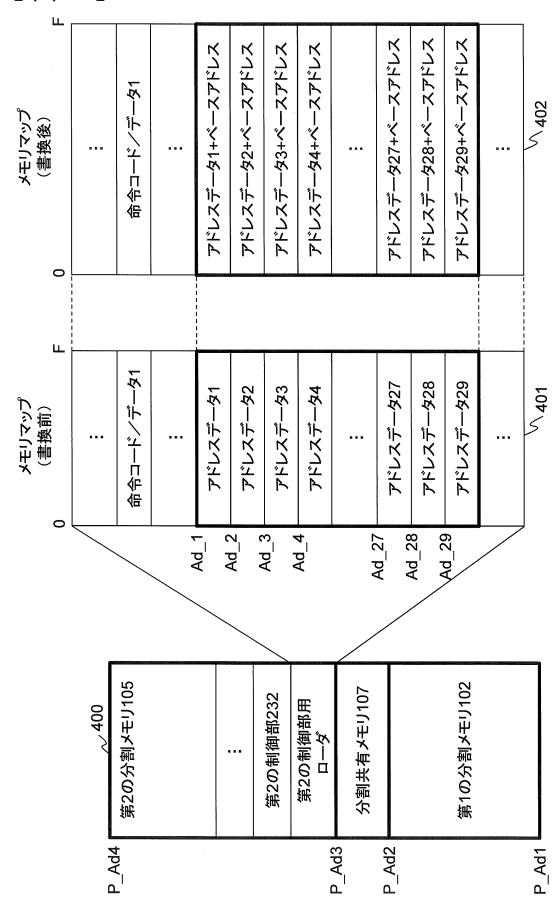

図8は、本発明の実施例1における第2の制御部用ローダ231のアドレスデータの変化の状態を示す説明図である。

#### 【0136】

記憶領域400は、物理計算機10が備えるメモリによって提供されるメモリの記憶領域を示す。本実施例では、P\_Ad1(物理アドレス1)からP\_Ad2(物理アドレス2)までの記憶領域が第1の分割メモリ102に対応し、P\_Ad2(物理アドレス2)からP\_Ad3(物理アドレス3)までの記憶領域が分割共有メモリ107に対応し、P\_Ad3(物理アドレス3)からP\_Ad4(物理アドレス4)までの記憶領域が第2の分割メモリ105に対応する。

#### 【0137】

また、メモリマップ401は、アドレスデータが書き換えられる前の第2の制御部用ローダ231のメモリマップを示し、メモリマップ402は、アドレスデータが書き換えられた後の第2の制御部用ローダ231のメモリマップを示す。

#### 【0138】

図8に示す例では、メモリマップ401、402の太枠の範囲、すなわち、Ad\_1からAd\_2までの範囲に含まれる記憶領域が書換対象のアドレスデータが格納される記憶領域である。

#### 【0139】

図8に示すように、アドレスデータ書換部221によって、各記憶領域に格納されるアドレスデータは、元のアドレスデータにベースアドレスデータ213の値が加算された値に書き換えられる。

#### 【0140】

これによって、第2の制御部用ローダ231は、第2の分割メモリ105内の所定のアドレスを参照することによって、正常に動作することができる。すなわち、第2のHW制

10

20

30

40

50

御プログラム 230 がどの記憶領域に書き込まれても、当該第 2 の HW 制御プログラム 230 を正常に動作させることが可能となる。

【0141】

以上で説明したように、本発明によれば、第 2 の HW 制御プログラム 230 が第 2 の OS280 の起動処理を行うため、第 1 の OS270 が直接関与することなく、第 2 の OS280 を起動することができる。

【0142】

また、第 2 の HW 制御プログラム 230 に含まれる第 2 の制御部用ローダ 231 のアドレスデータを予め書き換えることによって、第 2 の HW 制御プログラム 230 がどの記憶領域に書き込まれても起動させることができる。 10

【0143】

したがって、第 1 の OS270 が第 2 の OS280 のデータを扱うことができないシステム構成の場合、第 1 の HW 制御プログラム 210 のデバイスドライバが、第 2 の外部記憶装置 30 に対応していない場合であっても、第 2 の OS280 を起動することができる。

【0144】

(変形例 1)

実施例 1 では、第 2 の HW 制御プログラム 230 が書換対象アドレス情報 233 を保持していたが、本発明はこれに限定されない。この場合、ステップ S201 の処理は以下のようになる。 20

【0145】

アドレスデータ書換部 221 は、第 2 の制御部用ローダ 231 の実行形式のファイルを参照し、当該実行形式のファイルに含まれるリロケーションセクション（リロケーション情報）に基づいて、書換対象のアドレスデータが含まれる記憶領域を特定する。

【0146】

なお、第 2 の制御部用ローダ 231 の実行形式のファイルは、予め、第 1 の外部記憶装置 20 等に格納し、第 1 の制御部 212 が第 2 の分割メモリ 105 に書き込む方法が考えられる。

【0147】

その他の処理は、実施例 1 と同一であるため説明を省略する。 30

【0148】

(変形例 2)

実施例 1 では、第 1 の制御部 212 が、アドレスデータ書換モジュール 220 及び第 2 の HW 制御プログラム 230 を第 2 の分割メモリ 105 に書き込んでいたが、本発明はこれに限定されない。

【0149】

一つの方法としては、第 1 の OS セグメント 301 上で稼働する任意のプログラムが、アドレスデータ書換モジュール 220 及び第 2 の HW 制御プログラム 230 を第 2 の分割メモリ 105 に書き込む。この場合、第 2 の分割メモリ 105 への一時的なアクセスを可能とするために、以下のような処理が必要となる。 40

【0150】

任意のプログラムは、第 2 の分割メモリ 105 の一部の記憶領域に対して、書き込み可能なページテーブルを生成し、当該ページテーブルを参照することによって、第 1 の OS270 用の仮想メモリ空間に第 2 の分割メモリ 105 の一部の記憶領域をマッピングする。

【0151】

また、アドレスデータ書換モジュール 220 及び第 2 の HW 制御プログラム 230 が第 2 の分割メモリ 105 に書き込まれた後、任意のプログラムは、第 1 の OS270 用の仮想メモリ空間にマップされた第 2 の分割メモリ 105 の一部の記憶領域のマッピングを解除する。これによって、第 2 の分割メモリ 105 へのアクセスが禁止される。 50

## 【0152】

他の方法としては、第1の制御部212が、第2の分割メモリ105ではなく、分割共有メモリ107に、アドレスデータ書換モジュール220及び第2のHW制御プログラム230を書き込む。この場合、第2の分割プロセッサ104が、分割共有メモリ107にアクセスするように設定すればよい。

## 【0153】

各実施例では、ソフトウェアによる制御を用いた例について説明したが、その一部をハードウェアによって実現することも可能である。

## 【0154】

以上、本発明を添付の図面を参照して詳細に説明したが、本発明はこのような具体的構成に限定されるものではなく、添付した請求の範囲の趣旨内における様々な変更及び同等の構成を含むものである。10

## 【符号の説明】

## 【0155】

|     |                    |    |

|-----|--------------------|----|

| 10  | 物理計算機              |    |

| 20  | 第1の外部記憶装置          |    |

| 30  | 第2の外部記憶装置          |    |

| 100 | ハードウェアリソース         |    |

| 101 | 第1の分割プロセッサ         |    |

| 102 | 第1の分割メモリ           | 20 |

| 103 | 第1の分割I/Oデバイス       |    |

| 104 | 第2の分割プロセッサ         |    |

| 105 | 第2の分割メモリ           |    |

| 106 | 第2の分割I/Oデバイス       |    |

| 107 | 分割共有メモリ            |    |

| 108 | ROM                |    |

| 111 | 第1の分割ハードウェアリソース    |    |

| 112 | 第2の分割ハードウェアリソース    |    |

| 210 | 第1のHW制御プログラム       |    |

| 211 | 第1の制御部用ローダ         | 30 |

| 212 | 第1の制御部             |    |

| 213 | ベースアドレスデータ         |    |

| 220 | アドレスデータ書換モジュール     |    |

| 221 | アドレスデータ書換部         |    |

| 222 | 第2のHW制御プログラム用ローダ   |    |

| 230 | 第2のHW制御プログラム       |    |

| 231 | 第2の制御部用ローダ         |    |

| 232 | 第2の制御部             |    |

| 233 | 書換対象アドレス情報         |    |

| 240 | 第1のOSブートローダ        | 40 |

| 245 | 第2のOSブートローダ        |    |

| 250 | 第1のOSイメージ          |    |

| 255 | 第2のOSイメージ          |    |

| 260 | リソース範囲定義情報         |    |

| 261 | プロセッサの定義情報         |    |

| 262 | メモリの定義情報           |    |

| 263 | I/Oデバイスの定義情報       |    |

| 270 | 第1のOS              |    |

| 271 | 第2のOSセグメント用起動モジュール |    |

| 280 | 第2のOS              | 50 |

- 2 8 1 リソース管理部

2 8 2 プロセススケジュール部

2 9 0 L P A R

2 9 5 ゲストOS

3 0 1 第1のOSセグメント

3 0 2 第2のOSセグメント

4 0 0 記憶領域

4 0 1 メモリマップ

4 0 2 メモリマップ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7 A】

【図7B】

【 7 D 】

【図7c】

( 8 )

---

フロントページの続き

(72)発明者 下城 孝

神奈川県横浜市西区みなとみらい二丁目3番3号 株式会社日立情報通信エンジニアリング内

(72)発明者 小長谷 昌利

神奈川県横浜市西区みなとみらい二丁目3番3号 株式会社日立情報通信エンジニアリング内

(72)発明者 中川 義仁

神奈川県小田原市中里322番2号 株式会社日立製作所 ITプラットフォーム事業本部内

(72)発明者 森木 俊臣

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所 中央研究所内

審査官 石川 亮

(56)参考文献 特開2001-290665(JP,A)

特許第4916576(JP,B2)

(58)調査した分野(Int.Cl., DB名)

G 06 F 9 / 445