(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5640081号

(P5640081)

(45) 発行日 平成26年12月10日(2014.12.10)

(24) 登録日 平成26年10月31日(2014.10.31)

(51) Int.Cl.

G06F 7/499 (2006.01)

F 1

G06F 7/499

請求項の数 20 (全 13 頁)

(21) 出願番号 特願2012-513148 (P2012-513148)

(86) (22) 出願日 平成22年5月24日 (2010.5.24)

(65) 公表番号 特表2012-528391 (P2012-528391A)

(43) 公表日 平成24年11月12日 (2012.11.12)

(86) 國際出願番号 PCT/US2010/035900

(87) 國際公開番号 WO2010/138432

(87) 國際公開日 平成22年12月2日 (2010.12.2)

審査請求日 平成25年5月14日 (2013.5.14)

(31) 優先権主張番号 12/472,715

(32) 優先日 平成21年5月27日 (2009.5.27)

(33) 優先権主張国 米国(US)

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVICES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンディベール、ビイ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・ブレイス、メイル・ストップ

・68 (番地なし)

(74) 代理人 100108833

弁理士 早川 裕司

(74) 代理人 100111615

弁理士 佐野 良太

最終頁に続く

(54) 【発明の名称】飽和を伴う整数乗算および乗算加算演算

## (57) 【特許請求の範囲】

## 【請求項1】

第1および第2演算数を受け取るための第1および第2入力、和シグナルを提供するための第1出力、ならびにキャリー・シグナルを提供するための第2出力を有する乗算器(420)と、

前記第1および第2演算数の符号ビットを受け取るための第1および第2入力、第3演算数を受け取るための第3入力、バイアス加数シグナルを提供するための第1出力、ならびに前記第1および第2演算数の積の符号を表すシグナルを提供するための第2出力を有するバイアス加数発生器(440)と、

前記乗算器の前記第1および第2出力に結合される第1および第2入力、前記バイアス加数シグナルを受け取るための第3入力、ならびに前記第1、第2および第3入力の和を表すシグナルを提供するための出力を有する加算器(430)と、

前記加算器の前記出力に結合される第1入力、飽和最小値を受け取るための第2入力、飽和最大値を受け取るための第3入力、制御入力、および飽和シグナルを伴う乗算加算結果を提供するための出力を有するマルチブレクサ(466)と、

前記バイアス加数発生器の前記第2出力に結合される第1入力、前記和の符号を表すシグナルを受け取るための第2入力、および前記マルチブレクサの前記制御入力に結合される出力を有する選択ロジック(468)とを備えた乗算加算器(400)。

## 【請求項2】

前記乗算器はブースの再コーディング(422)を使用することで特徴付けられるキャ

10

20

リー・セーブ乗算器配列（424）である請求項1の乗算加算器（400）。

**【請求項3】**

前記バイアス加数シグナルは前記和およびキャリー・シグナルと同じビット数を含む請求項1の乗算加算器（400）。

**【請求項4】**

前記第1、第2および第3演算数の各々は符号付き整数からなる請求項1，2，3のいずれかの乗算加算器（400）。

**【請求項5】**

前記バイアス加数発生器（440）は、

前記第1演算数の符号ビットを受け取るための第1入力、前記第2演算数の符号ビットを受け取るための第2入力、ならびに前記第1および第2演算数の前記積の前記符号を表す符号シグナルを提供するための出力を有するロジックゲート（550）と、

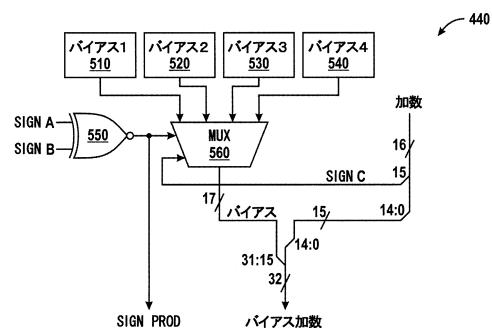

第1バイアスを受け取るための第1入力、第2バイアスを受け取るための第2入力、第3バイアスを受け取るための第3入力、第4バイアスを受け取るための第4入力、前記ロジックゲートの前記出力に結合される第1制御入力、前記第3演算数の前記符号を受け取るための第2制御入力、ならびに前記加算器の前記第3入力に結合されて前記バイアス加数シグナルを供給するための出力を有するマルチプレクサ（560）と、を備える請求項3の乗算加算器（400）。

**【請求項6】**

前記第1および第2演算数はパックされた演算数からなり、前記乗算加算器は飽和を伴う類似する複数の乗算加算結果を生成するための複数のセクションを備える請求項1，2，3，5のいずれかの乗算加算器（400）。

**【請求項7】**

第1および第2演算数の積を表す和シグナルおよび第1および第2演算数の積を表すキャリー・シグナルを提供するための乗算器（220）と、

前記和シグナル、前記キャリー・シグナルおよびバイアス・シグナルの和を表す中間結果シグナルを提供するための加算器（230）と、

前記第1および第2演算数の積の符号によって決定される値を有する前記バイアス・シグナルを提供するためのバイアス発生器（240）と、

前記積の前記符号および前記中間結果の符号に応じて、前記加算器の前記中間結果シグナルの部分、飽和最小値および飽和最大値の1つを選択するための出力選択回路（260）と、を備えた演算処理部（200）。

**【請求項8】**

前記加算器は符号拡張加数に基づいて前記中間結果シグナルをさらに提供する請求項7の演算処理部（200）。

**【請求項9】**

第3演算数を符号拡張して前記符号拡張加数を提供するための符号拡張ロジック（250）をさらに備えた請求項8の演算処理部（200）。

**【請求項10】**

前記第1、第2および第3演算数の各々は符号付き整数からなる請求項7，8，9のいずれかの演算処理部（200）。

**【請求項11】**

前記バイアス発生器（240）は前記第1および第2演算数の前記積の前記符号に応じて負のバイアスおよび正のバイアスの一方を前記バイアス・シグナルとして提供する請求項9の演算処理部（200）。

**【請求項12】**

前記第1（612）および第2（614）演算数はパックされた演算数からなり、前記演算処理部は飽和を伴う類似する複数の結果（618）を生成するための複数のセクションを備える請求項7，8，9，11のいずれかの演算処理部（200）。

**【請求項13】**

10

20

30

40

50

前記出力選択回路（260，460）は前記中間結果シグナルの前記部分の最上位ビットをさらに反転する（450）請求項7の演算処理部（200）。

#### 【請求項14】

第1（212）および第2（214）演算数の積を表す和シグナルおよび第1（212）および第2（214）演算数の積を表すキャリー・シグナルを形成することと、

前記第1および第2演算数の積の符号によって決定される値を有するバイアス・シグナル（240）を形成することと、

前記和シグナル、前記キャリー・シグナル、符号拡張加数および前記バイアス・シグナルの加算（230）に応じて第1出力シグナルを提供することと、

前記積の前記符号および前記第1出力シグナルの符号に応じて、前記第1出力シグナルの部分、飽和最小値（462）および飽和最大値（464）の1つを最終結果として選択することと、を備えた方法。10

#### 【請求項15】

前記和およびキャリー・シグナルを形成することは、キャリー・セーブ乗算器配列（424）およびブースの再コーディング（422）を使用して前記和およびキャリー・シグナルを形成することをさらに備える請求項14の方法。

#### 【請求項16】

前記和およびキャリー・シグナルの各々のビットサイズと一致するように第3演算数（216）を符号拡張すること（250）をさらに備えた請求項14の方法。20

#### 【請求項17】

前記バイアス・シグナルを形成することは、

前記第1演算数（212）の符号ビット、

前記第2演算数（214）の符号ビット、

前記第1および第2演算数に基づいて前記積の前記符号を決定すること、ならびに

前記積の前記符号に基づいて負のバイアス（242）または正のバイアス（244）の間で選択すること（248）、に応じて前記バイアス・シグナルを形成することをさらに備える請求項16の方法。

#### 【請求項18】

前記最終結果は前記第3演算数と同じバイナリビット数からなる請求項16又は17の方法。30

#### 【請求項19】

前記和およびキャリー・シグナルを形成することは、当該第1および第2のパックされた演算数の積を表すパックされた和およびキャリー・シグナルを形成することを備える請求項14の方法。

#### 【請求項20】

前記第1出力シグナルを提供することは、前記和シグナル、前記キャリー・シグナル、前記符号拡張加数および前記バイアス・シグナルの和として前記第1出力シグナルを提供することを備え、前記最終結果は前記和より少ないバイナリビット数からなる請求項14, 15, 16, 17のいずれかの方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本開示は概してデータ処理装置に係り、具体的には演算処理装置に係る。

##### 【背景技術】

##### 【0002】

データ処理装置には、整数または浮動小数点の処理装置などの特殊な演算処理部が含まれる場合がある。演算処理部はグラフィックス処理、デジタルシグナル処理、そして科学アプリケーションに関連するタスクを実行する上で特に有効である。演算処理部は一般的に、命令が特定の数学的計算に関連付けられている事を特徴として、命令を実行する。例えば、演算処理部は乗算、加算、乗加算、行列計算などの算術演算を実行する命令が含ま50

れる場合がある。演算処理部は一般的に、バイナリ浮動小数点形式、バイナリ整数形式のいずれか、または両方を使用して数値を表す。浮動小数点数と整数の数値は、各関連付けられた精度を持ち、特定の値の範囲を表す事が出来、それは数値を表すために使用されるバイナリビット数によって決まる。演算処理部は、サポートされている範囲を超えた数学的演算の結果を表すために、飽和演算を使える。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0003】

飽和演算は、算術演算の結果が最小値と最大値の間の一定の範囲に限定されている算術の一種である。また、演算の結果が最大値より大きい場合（オーバーフロー状態と呼ぶ）、演算処理部は表現可能な最大値に対応する結果を出す。また、演算の結果が最小値より小さい場合（アンダーフロー状態と呼ぶ）、演算処理部は表現可能な最小値に対応する結果を出す。飽和演算を使用する事で、計算がオーバーフローまたはアンダーフロー状態のいずれかをもたらす場合に、発生し得るエラーの重大度を軽減出来る。例えば、飽和を使用せずに、計算がサポートされている範囲をオーバーフローした場合、演算処理部は負の値の結果を出す可能性がある。残念な事に、演算処理部が正しい飽和結果を出すために飽和が生じたことを検出する事は、装置の計算性能に悪影響を与える可能性がある。これは、特に結果のサイズ（数を表すために使用されるバイナリビット数）が、被乗数、乗数または加数と同サイズに制限される乗算加算操作で当てはまる。

10

#### 【課題を解決するための手段】

20

#### 【0004】

第1の態様においては、乗算加算器は、第1および第2演算数を受け取るための第1および第2入力、和シグナルを提供するための第1出力、ならびにキャリー・シグナルを提供するための第2出力を有する乗算器と、第1および第2演算数の符号ビットを受け取るための第1および第2入力、第3演算数を受け取るための第3入力、バイアス加数シグナルを提供するための第1出力、ならびに第1および第2演算数の積の符号を表すシグナルを提供するための第2出力を有するバイアス加数発生器と、乗算器の第1および第2出力に結合される第1および第2入力、バイアス加数シグナルを受け取るための第3入力、ならびに第1、第2および第3入力の和を表すシグナルを提供するための出力を有する加算器と、加算器の第1出力に結合される第1入力、飽和最小値を受け取るための第2入力、飽和最大値を受け取るための第3入力、制御入力、および飽和シグナルを伴う乗算加算結果を提供するための出力を有するマルチプレクサ（466）と、バイアス発生器の第2出力に結合される第1入力、和の符号を表すシグナルを受け取るための第2入力、およびマルチプレクサの制御入力に結合される出力を有する選択ロジックと、を含む。

30

#### 【0005】

第1の態様の1つの実施形態においては、乗算器は、キャリー・セーブ乗算器配列であり、そしてブースの再コーディングを使用することで特徴付けられる。第1の態様の別の実施形態においては、バイアス加数シグナルは和およびキャリー・シグナルと同じビット数を含む。第1の態様のさらなる実施形態においては、第1、第2および第3演算数の各々は符号付き整数を含む。第1の態様のさらに別の実施形態においては、バイアス加数発生器は、第1演算数の符号ビットを受け取るための第1入力、第2演算数の符号ビットを受け取るための第2入力、ならびに第1および第2演算数の積の符号を表す符号シグナルを提供するための出力を有するロジックゲートと、第1バイアスを受け取るための第1入力、第2バイアスを受け取るための第2入力、第3バイアスを受け取るための第3入力、第4バイアスを受け取るための第4入力、ロジックゲートの出力に結合される第1制御入力、第3演算数の符号を受け取るための第2制御入力、ならびに加算器の第3入力に結合されてバイアス加数シグナルを供給するための出力を有するマルチプレクサと、を含む。第1の態様の別の実施形態においては、第1および第2演算数はパックされた演算数を含み、乗算加算器は飽和を伴う類似する複数の乗算加算結果を生成するための複数のセクションを含む。

40

50

**【0006】**

第2の態様においては、演算処理部は、第1および第2演算数の積を表す和およびキャリー・シグナルを提供するための乗算器と、和シグナル、キャリー・シグナルおよびバイアス・シグナルの和を表す中間結果シグナルを提供するための加算器と、第1および第2演算数の積の符号によって決定される値を有するバイアス・シグナルを提供するためのバイアス発生器と、積の符号および中間結果の符号に応じて、加算器の第1出力シグナルの部分、飽和最小値および飽和最大値の1つを選択するための出力選択回路とを含む。第2の態様の1つの実施形態においては、加算器は、符号拡張加数に基づいて中間結果シグナルをさらに提供する。第2の態様の別の実施形態においては、演算処理部は、第3演算数を符号拡張して符号拡張加数を提供するための符号拡張ロジックをさらに含む。第2の態様のさらなる実施形態においては、第1、第2および第3演算数の各々は符号付き整数を含む。第2の態様のさらに別の実施形態においては、バイアス発生器は、第1および第2演算数の積の符号に応じて負のバイアスおよび正のバイアスの一方をバイアス・シグナルとして提供する。第2の態様のさらなる別の実施形態においては、第1および第2演算数はパックされた演算数を含み、演算処理部は飽和を伴う類似する複数の結果を生成するための複数のセクションを含む。第2の態様の別の実施形態においては、出力選択回路は、第1出力シグナルの部分の最上位ビットをさらに反転する。

10

**【0007】**

第3の態様においては、方法は、第1および第2演算数の積を表す和およびキャリー・シグナルを形成することと、第1および第2演算数の積の符号によって決定される値を有するバイアス・シグナルを形成することと、和シグナル、キャリー・シグナル、符号拡張加数およびバイアス・シグナルの加算に応じて第1出力シグナルを提供することと、積の符号および第1出力シグナルの符合に応じて、第1出力シグナルの部分、飽和最小値および飽和最大値の1つを最終結果として選択することと、を含む。第3の態様の1つの実施形態においては、和およびキャリー・シグナルを形成することは、キャリー・セーブ乗算器配列およびブースの再コーディングを使用して和およびキャリー・シグナルを形成することをさらに含む。第3の態様のさらなる実施形態においては、方法は、和およびキャリー・シグナルの各々のビットサイズと一致するよう第3演算数を符号拡張することをさらに含む。第3の態様のさらに別の実施形態においては、バイアス・シグナルを形成することは、第1演算数の符号ビット、第2演算数の符号ビット、第1および第2演算数に基づいて乗算の積の符号を決定すること、ならびに積の符号に基づいて負のバイアスまたは正のバイアスの間で選択すること、に応じてバイアス・シグナルを形成することをさらに含む。第3の態様の更に別の実施形態においては、最終結果は第3演算数と同じバイナリビット数を含む。第3の態様の別の実施形態においては、和およびキャリー・シグナルを形成することは、第1および第2のパックされた演算数の積を表すパックされた和およびキャリー・シグナルを形成することを含む。第3の態様のさらなる実施形態においては、第1出力シグナルを提供することは、和シグナル、キャリー・シグナル、符号拡張加数およびバイアス・シグナルの和として第1出力シグナルを提供することを含み、最終結果は和より少ないバイナリビット数を含む。

20

**【図面の簡単な説明】**

30

**【0008】**

本開示は、添付の図面を参照する事により、当業者はより良く理解出来、そしてその多くの特徴および利点は明らかになる：

40

**【0009】**

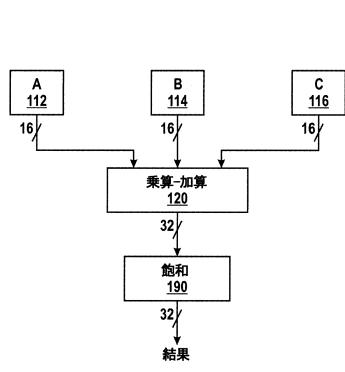

【図1】図1は、以前から知られている形で飽和演算を実行する操作が可能な、従来の演算処理部を示すブロック図である。

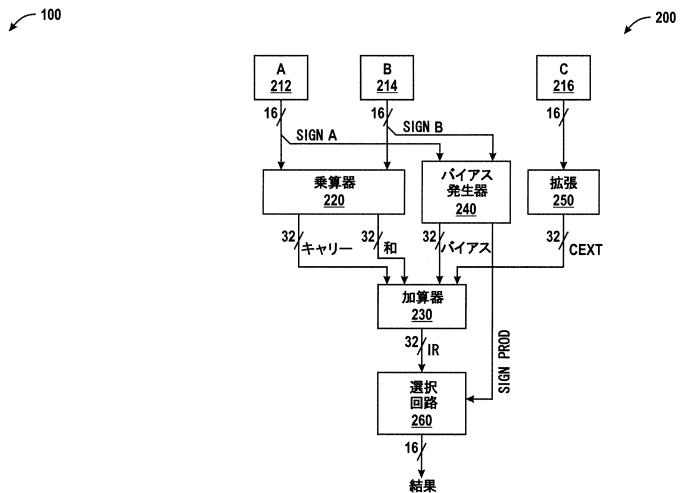

【図2】図2は、本発明の一実施形態に従って、飽和演算を実行する操作が可能な、演算処理部を示すブロック図である。

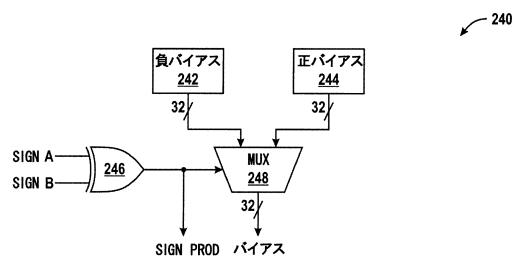

【図3】図3は、図2のバイアス発生器を示す部分回路図であって部分ブロック図である。

50

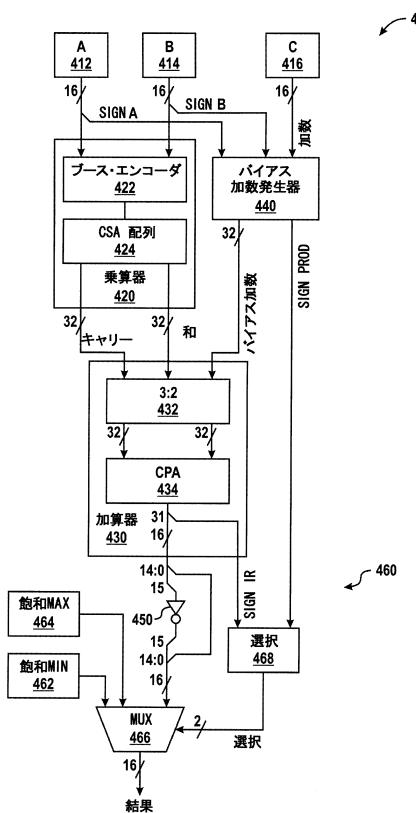

【図4】図4は、本発明の別の実施形態に従って、飽和演算を実行する操作が可能な、演算処理部を示すブロック図である。

【図5】図5は、図4のバイアス加数発生器を示す部分回路図であって部分ブロック図である。

【図6】図6は、本発明のさらに別の実施形態による、パックされた演算数の飽和演算を実行する操作が可能な、演算処理部を示すブロック図である。

#### 【0010】

別の図面での同じ参照符号の使用は、類似または同一の項目を示す。明確にすると、同一名はシグナル、シグナルを通すノード、シグナルで表される情報を示す。

#### 【発明を実施するための形態】

10

#### 【0011】

図1は以前から知られている形で、飽和演算を実行する操作が可能な、従来の演算処理部100を示すブロック図である。演算処理部100は、2つの演算数を乗算して積を得ると共に、中間結果を出すために3つ目の演算数に積を加算することによって、乗算加算演算を行う。飽和検出回路は、中間結果を受け取り、計算の最終結果を出す。演算処理部100は、「A」とラベルされた被乗数演算数112、「B」とラベルされた乗数演算数114、「C」とラベルされた加数演算数116、中間結果を出すための乗算加算モジュール120、「結果(RESULT)」とラベルされた最終結果を出す飽和モジュール190を含む。

#### 【0012】

20

乗算加算モジュール120は、演算数112を受け取るための第1入力、演算数114を受け取るための第2入力、演算数116を受け取るための第3入力、そして出力を持つ。飽和モジュール190は、乗算加算モジュール120の出力に接続された入力、シグナルRESULTを出す出力、を持つ。演算処理部100は、後続の乗算加算演算の加数として、以前に計算された乗算加算結果を用いて乗算加算演算を実行することも出来る。

#### 【0013】

演算処理部100は、それぞれが16ビット符号付き整数である演算数A、BとCを受け取る。乗算加算モジュール120によって提供された中間結果は、正確に乗算加算演算の結果を表すための追加ビットを含む。図1で示した本例では、飽和モジュール190によって提供された最終結果は、32ビットの符号付き整数である。飽和モジュール190は、乗算加算モジュール120によって提供された中間結果の値が、32ビットの符号付き整数で表す事が出来るものを超えているかを検出する(オーバーフローまたはアンダーフローと呼ばれる状態)。オーバーフローが発生した場合、飽和モジュール190は、最大の正の32ビット符号付き整数、バイナリ01111...1111を表すシグナルRESULTを生成する。アンダーフローが発生した場合、飽和モジュール190は、最大の負の32ビットの符号付き整数、バイナリ100...0000を表すシグナルRESULTを生成する。乗算加算モジュール120によって提供された中間結果が、サポートされている範囲内であれば、飽和検出モジュール190は、変更されていない中間結果をその出力に出す。

30

#### 【0014】

40

飽和モジュール190は、各演算数のそれぞれの符号と中間結果の符号に基づいて、オーバーフローまたはアンダーフロー状態が発生したかを判定する。しかしながら、最終結果の表現が符号付き16ビット整数に制限される場合、飽和モジュール190の操作はより複雑でかなりの時間がかかる。したがって、演算処理部100の計算性能が低下する。

#### 【0015】

乗算加算演算のオーバーフローおよびアンダーフローは、演算の最終結果に基づいて決定される。したがって、飽和した乗算加算を実行する事は、飽和した乗算操作に続いて飽和した加算の操作を実行する事とは数学的に等価ではない。例えば、乗算操作は自らサポートしている範囲を超えた積を生成する可能性があるが、加数の加算は最終的な乗算加算結果をサポートしているバイナリビット数で表現可能な値に返す事が出来る。乗算加

50

算演算を特徴付ける4つの可能な例がある：1)乗算の積は結果を表すために割り当てられたビット数を超え、加数の加算は最終結果をサポートされている範囲に戻さない。2)乗算の積は、結果を表すために割り当てられるビット数を超えて加数の加算は、サポートされている範囲に最終結果を戻す。3)乗算の積は、結果を表すために割り当てられるビット数を超えないが、加算の加算はサポートされている範囲を超える値が結果となる。4)乗算の積は、結果を表すために割り当てられるビット数を超えず、加算の加算はサポートされている範囲を超えない値が結果となる。

#### 【0016】

図2は、本発明の一実施形態に従って、飽和演算を実行する操作が可能な演算処理部200を示すブロック図である。演算処理部200は、乗算加算演算を実行し、バイアス値を提供するためのバイアス発生器を備えている。バイアス値、中間積、加数演算数は共に加算され、図1の飽和モジュール190によって実行される、複雑で時間のかかる操作は、図1の演算処理部100のように結果を大幅に遅延させる事なく、迅速に実行出来る単純な多重化操作に置き換えられる。

10

#### 【0017】

演算処理部200は、「A」とラベルされた被乗数演算数212、「B」とラベルされた乗数演算数214、「C」とラベルされた加数演算数216、乗算器220、バイアス発生器240、拡張ロジック250、加算器230、出力選択回路260を含む。

#### 【0018】

乗算器220は、演算数212を受け取るための第1入力、演算数214を受け取るための第2入力、「キャリー(CARRY)」とラベルされたシグナルを提供するための第1出力、「和(SUM)」とラベルされたシグナルを提供するための第2出力を持つ。バイアス発生器240は、演算数212の符号に対応する「SIGNA」とラベルされたシグナルを受け取るための第1入力、演算数214の符号に対応する「SIGNB」とラベルされたシグナルを受け取るための第2入力、「バイアス(BIAS)」とラベルされたシグナルを提供するための出力、「SIGNPROD」とラベルされた演算数212と演算数214の積の符号を表すシグナルを提供するための出力を持つ。拡張ロジック250は、演算数216を受け取るための第1入力、「CEXT」とラベルされたシグナルを受け取るための出力を持つ。加算器230は、シグナルCARRYを受け取るための第1入力、シグナルSUMを受け取るための第2入力、シグナルBIASを受け取るための第3入力、シグナルCEXTを受け取るための第4入力、「IR」とラベルされた中間結果を出すための出力、を持つ。選択回路260は、中間結果シグナルIRを受け取るための第1入力、シグナルSIGNPRODを受け取るための第2入力、「結果(RESULT)」とラベルされた最終結果を出すための出力を持つ。

20

#### 【0019】

各演算数212、214および216は、16ビット符号付き整数である。乗算器220は演算数212と演算数214を受け取り、シグナルCARRYで表される32ビットのCARRY値の形にある積と、シグナルSUMで表される32ビットの和を出す。

30

#### 【0020】

バイアス発生器240は、被乗数演算数212と乗数演算数214の積の符号に基づいた、シグナルBIASによって表されるバイアス値を提供する。積の符号は、シグナルSIGNAとSIGNBで表される、それぞれの演算数の符号に基づいて決定される。シグナルBIASは、高位17ビットが重要で下位15ビットが各ゼロである事を特徴とする32ビットの情報を含む。拡張ロジック250は、32ビットシグナルCEXTを提供するために加数演算数216を符号拡張し、シグナルSUM、CARRY、BIASのそれぞれに関連付けられたビット数に対応するようとする。

40

#### 【0021】

加算器230は、32ビットのバイアス値(シグナルBIAS)、32ビットの符号拡張加数(シグナルCEXT)、2つの32ビット乗算結果(シグナルCARRYとシグナルSUM)を加算し、シグナルIRで表される32ビットの中間結果を出す。一実施形態

50

で加算器 230 は、1つ以上のキャリー (CARRY) セーブ加算器 (CSA) ステージと最後のキャリー (CARRY) 伝播加算器 (CPA) を含む。別の実施形態では、加算器 230 に含まれている CSA ステージは、乗算器 220 に含まれている CSA ステージと共有出来る。従って、32ビットのバイアス値と符号拡張加数は、乗算器 220 内に含まれる1つ以上の CSA ステージ内で加算 (圧縮) 出来る。バイアス値は、16ビット符号付き整数に関連付けられた範囲を超えたはずだが 32ビットの符号付き整数の範囲内にある全ての結果が、シグナル IR で表される 32ビットの中間結果のオーバーフロー やアンダーフローの表示を提供するように強制する。つまり、16ビット符号付き整数のオーバーフロー やアンダーフローは、32ビットの中間結果の符号と演算数 212 と 214 の積の符号に基づいて、簡単に決定出来る。

10

#### 【0022】

出力選択回路 260 は、シグナル SIGNPROD で表される演算数 212 と演算数 214 の積の符号、そしてシグナル IR の最上位ビットで表される中間結果の符号を使用して、乗加算演算がオーバーフローまたはアンダーフロー状態をもたらしたかを判断する。中間結果はバイアス値の加算を含むので、出力選択回路 260 は、32ビットの中間結果に基づいて、必要な 16ビットの結果に対応するオーバーフローおよびアンダーフロー状態を容易に検出出来る。演算数 212 と演算数 214 の積の符号が 1 (負) であり、且つ中間結果の符号がゼロ (正) である場合、アンダーフローが発生したものとして、出力選択回路 260 は、16ビット符号付き整数、バイナリ 1000 0000 0000 0000 0000 を使用して表現可能な最も負の値にシグナル RESULT を設定する。演算数 212 と演算数 214 の積の符号がゼロ (正) であり、且つ中間結果の符号が 1 (負) である場合、オーバーフローが発生したものとして、出力選択回路 260 は、16ビット符号付き整数、バイナリ 0111 1111 1111 1111 を使用して表現可能な最大の正の値にシグナル RESULT を設定する。オーバーフロー、アンダーフローのどちらも発生しなかった場合、出力選択回路 260 は中間結果の一部に基づいて出力を提供する。具体的には、飽和が発生しなかった場合、最終結果は、ビット 15 を反転後のシグナル IR で表される中間結果の下位 16ビットに等しい。

20

#### 【0023】

図 3 は、図 2 のバイアス発生器 240 を示す部分回路図であって部分ブロック図である。バイアス発生器 240 は、負のバイアス値 242、正のバイアス値 244、排他的 NOR ゲート 246、マルチプレクサ 248 を含む。排他的 NOR ゲート 246 は、シグナル SIGNA を受け取るための第 1 入力、シグナル SIGNB を受け取るための第 2 入力、シグナル SIGNPROD を提供するための出力を持つ。マルチプレクサ 248 は、負のバイアス値 242 を受け取るための第 1 データ入力、正のバイアス値 244 を受け取るための第 2 入力、シグナル SIGNPROD を受け取るための制御入力、シグナル BIAS を供給するための出力を持つ。

30

#### 【0024】

シグナル SIGNPROD がロジック高位 (負) の場合、マルチプレクサ 248 は負のバイアス値 242 を選択し、以下のバイナリの値を持つシグナル BIAS を生成する。

#### 【0025】

1000 0000 0000 0000 1000 0000 0000 0000

40

#### 【0026】

シグナル SIGNPROD がロジック低位 (正) の場合、マルチプレクサ 248 は正のバイアス値 244 を選択し、以下のバイナリの値を持つシグナル BIAS を生成する。

#### 【0027】

0111 1111 1111 1111 1000 0000 0000 0000

#### 【0028】

図 4 は、本発明の一実施形態に係る、飽和演算を実行する操作が可能な、演算処理部 400 を示すブロック図である。演算処理部 400 は、乗算加算演算を実行出来る。図 2 の演算処理部 200 とは異なり、演算処理部 400 は、バイアス発生器 240 の機能と拡張

50

ロジック 250 の機能を、「(バイアス加数 (B I A S E D A D D E N D)」とラベルされたバイアス加数を形成する單一モジュールに結合する。演算処理部 400 は、「A」とラベルされた被乗数演算数 412 と、「B」とラベルされた乗数演算数 414 と、「C」とラベルされた加数演算数 416 と、ブース・エンコーダ 422 および CSA 配列 424 を含む乗数モジュール 420 と、バイアス加数発生器 440 と、3:2 コンプレッサー 432 およびキャリー (CARRY) 伝播加算器 434 を含む加算器 430 と、飽和最小値 462、飽和最大値 464、マルチプレクサ 466、インバータ 450、および選択ロジック 468 を含む出力選択回路 460 と、を含む。

#### 【0029】

乗算器 420 は、演算数 412 を受け取るための第1入力、演算数 414 を受け取るための第2入力、「キャリー (CARRY)」とラベルされたシグナルを提供するための第1出力、「和 (SUM)」とラベルされたシグナルを提供するための第2出力を持つ。バイアス加数発生器 440 は、演算数 412 の符号に対応する「SIGNA」とラベルされたシグナルを受け取るための第1入力、演算数 414 の符号に対応する「SIGNB」とラベルされたシグナルを受け取るための第2入力、「加数 (ADDEND)」とラベルされたシグナルによって表される加数演算数 416 を受け取るための入力、「バイアス加数 (B I A S E D A D D E N D)」とラベルされたシグナルを提供するための第1出力、演算数 412 と演算数 414 の積の符号に対応する「SIGNPROD」とラベルされたシグナルを提供するための第2出力を持つ。加算器 430 は、シグナル CARRY を受け取るための第1入力と、シグナル SUM を受け取るための第2入力と、シグナル BIAS ADDEND を受け取るための第3入力と、CPA 434 によって提供された 32 ビットの中間結果の最下位 16 ビットに対応する「IR」とラベルされた中間結果を出すための第1出力と、CPA 434 によって提供された 32 ビットの中間結果の符号に対応する「SIGNIR」とラベルされたシグナルを提供するための第2出力と、を有する。インバータ 450 は、シグナル IR のビット 15 を受け取るための入力と、出力を持つ。マルチプレクサ 466 は、飽和最小値 462 を受け取るための第1入力、飽和最大値 464 を受け取るための第2入力、16 ビットの非飽和の結果を受け取るための第3入力、「選択 (SELECT)」とラベルされたシグナルを受け取るための制御入力、「結果 (RESULT)」とラベルされたシグナルを出力するための出力を持つ。16 ビットの非飽和結果の最上位ビットは、インバータ 450 によって提供され、16 ビットの非飽和結果の 14~0 のビットは、シグナル IR (14:0) によって提供される。選択ロジック 468 は、シグナル SIGNIR を受け取るための第1入力、シグナル SIGNPROD を受け取るための第2入力、マルチプレクサ 466 の制御入力にシグナル SELECT を提供する出力を持つ。

#### 【0030】

各演算数 412、414、416 は 16 ビット符号付き整数である。乗算器 420 は、演算数 412 および演算数 414 を受け取り、シグナル CARRY で表される 32 ビットの CARRY 値の形にある積と、シグナル SUM で表される 32 ビットの和を出す。乗算器 420 は、ブース・エンコーダ 422 を使用して、ブースの再コーディング (Booth's recoding) として知られるプロセスで部分積を出す。CSA 配列 424 は、シグナル CARRY と SUM を提供するために、これらの部分積を、連続する CSA ステージで二つの部分積に縮退する。

#### 【0031】

バイアス加数発生器 440 はバイアス値を生成し、32 ビットシグナル BIAS ADDEND を提供するために、そのバイアス値を加数演算数 416 と組み合わせる。バイアス加数発生器 440 の操作は、下記図 5 を参照しながらさらに説明する。

#### 【0032】

コンプレッサー 432 は、シグナル CARRY、SUM と BIAS ADDEND を受け取り、CPA 434 に 32 ビットキャリーと 32 ビット和シグナルで表されるそれぞれの値の和を提供する。CPA 434 は、コンプレッサー 432 により生成されたキャリー

10

20

30

40

50

/ 和表現を、単一の32ビットのバイナリ整数で表される結果に変換し、シグナルIRを介してマルチブレクサ466に、この値の最下位16ビットを提供する。選択モジュール468がオーバーフローかアンダーフロー状態のどちらも発生しなかったと判断した場合、シグナルIRによって表される値が乗加算演算の最終結果と等しくなる。

【 0 0 3 3 】

マルチプレクサ466と選択モジュール468の操作は、図2の出力選択回路260を参照して説明したものと同じであり、ここに追加の詳細を示す。選択モジュール468がオーバーフロー状態を検出した場合、選択モジュール468は、マルチプレクサ466がシグナルRESULTを介して飽和最大値464を最終結果として提供するように、シグナルSELECTを介してマルチプレクサ466を設定する。選択モジュール468がアンダーフロー状態を検出した場合、選択モジュール468は、マルチプレクサ466がシグナルRESULTを介して飽和最小値462を最終結果として提供するように、マルチプレクサ466を設定する。選択モジュール468がオーバーフローとアンダーフロー状態のいずれも検出しない場合、選択モジュール468は最終結果として非飽和の結果を出すようマルチプレクサ466を設定する。

10

【 0 0 3 4 】

図5は、図4のバイアス加数発生器440を示す部分回路図であって部分ブロック図である。バイアス加数発生器440は、図2のバイアス発生器240と拡張ロジック250によって実行される操作を組み合わせ、バイアス値およびそれとは別の符号拡張加数よりはむしろ単一のバイアス加数を提供する。この機能によって、加算器430は3つの値のみの和を計算するのに対し、図2の加算器230は4つの値の和を計算する必要がある。

20

( 0 0 3 5 )

バイアス加数発生器 440 は、第 1 バイアス値 510 、第 2 バイアス値 520 、第 3 バイアス値 530 、第 4 バイアス値 540 、排他的 NOR ゲート 550 、マルチプレクサ 560 を含む。排他的 NOR ゲート 550 は、シグナル SIGNA を受け取るための第 1 入力、シグナル SIGNB を受け取るための第 2 入力、シグナル SIGNPROD を提供するための出力を持つ。マルチプレクサ 560 は、バイアス値 510 を受け取るための第 1 データ入力、バイアス値 520 を受け取るための第 2 データ入力、バイアス値 530 を受け取るための第 3 データ入力、バイアス値 540 を受け取るための第 4 データ入力、シグナル SIGNPROD を受け取るための第 1 制御入力、加数オペランド 416 の符号を表す「SIGNC」とラベルされたシグナルを受け取るための第 2 制御入力、「バイアス(BIAS)」とラベルされたシグナルを提供するための出力を持つ。シグナル BIAS は 17 ビットのバイナリ値であり、32 ビットシグナルバイアス加数(BIASEDADDEND) の 17 ビット上位部分を提供する。シグナル BIASEDADDEND の最下位 15 ビットは、シグナル加数(ADDEND) の最下位 15 ビットに基づいて決定される。バイアス加数発生器の操作は、次の表に示される：

30

[ 0 0 3 6 ]

【表1】

40

【 0 0 3 7 】

このように、シグナル B I A S E D A D D E N D は、バイアス値と加数の符号が無い部

50

分を連結したものである。なお、シグナルB I A S E D A D D E N Dのビット15は加数演算数416の符号の逆元である。

#### 【0038】

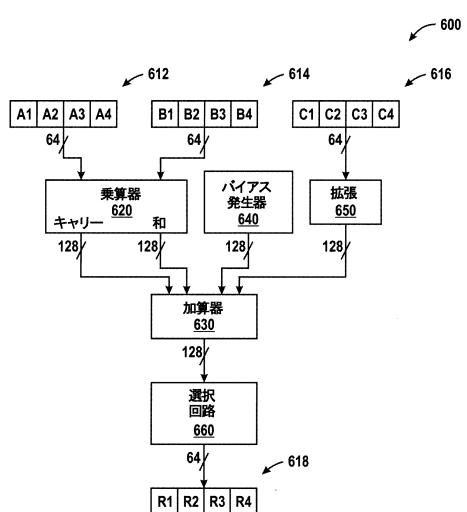

図6は、本発明のさらに別の実施形態による、パックされた演算数の飽和演算を実行する操作が可能な、演算処理部600を示すブロック図である。演算処理部600は、「A1、A2、A3、A4」とラベルされた被乗数演算数612、「B1、B2、B3、B4」とラベルされた乗数演算数614、「C1、C2、C3、C4」とラベルされた加数演算数616、乗算器620、バイアス発生器640、拡張ロジック650、加算器630、出力選択回路660、「R1、R2、R3、R4」とラベルされた結果618を含む。

#### 【0039】

演算処理部600の接続と操作は、図2の演算処理部200に似ているが、例外として演算数612、614、及び616、そして結果618の各々は、それぞれが4つの別個の16ビット符号付き整数を含むパックされた演算数である。パックされた演算数を、複数多重精度演算数と呼ぶ事も出来る。演算処理部600は、4つの乗算加算演算を並行して実行する。例えば、演算処理部600は、 $R1 = (A1 \times B1) + C1$ 、 $R2 = (A2 \times B2) + C2$ 、 $R3 = (A3 \times B3) + C3$ 、及び $R4 = (A4 \times B4) + C4$ の結果を計算する。演算処理部600は、図2の演算処理部200を参照して説明したのと同様の方法で、これらの各計算を個々に実行する。乗算器620は、それぞれが複数の積を表す、128ビットのキャリー・シグナルと128ビットの和シグナルを提供する。バイアス発生器640は、それぞれの計算に対応する一意のバイアス値を提供する。出力選択回路660は、それぞれの計算がオーバフローまたはアンダフローになるかを決定し、必要に応じて表現可能な最大値または表現可能な最小値を置換する。

#### 【0040】

上記の一般説明で記載されている全ての活動や要素が必須ではない事、特定の活動または装置の一部が不要になる可能性がある事、1つ以上のさらなる活動が行われる可能性がある事、または記載されているものに加えて、要素が含まれる可能性がある事に留意されたい。さらにまた、活動がリストされている順序は、それらが実行される順序とは限らない。

#### 【0041】

さらに、各概念は特定の実施形態を参照して説明されている。しかしながら、当業者は様々な修正および変更が以下の特許請求の範囲に記載された本開示の範囲から逸脱する事なく行う事が出来る事を理解出来る。それに応じて、仕様および図面は限定的な意味ではなく、例示としてみなされるべきであり、全てのそのような修正は本開示の範囲内に含まれる事が意図されている。

#### 【0042】

例えば、本明細書中で使用される技法は、乗算演算を行う事が出来るが乗算加算操作ができない乗算器でも使える。この場合においては、加数の入力が省略される。しかしながら、乗算加算演算を行う事が出来る演算処理部は、実行制御部によって、単純な乗算操作を実行するために入力された加数を無効にするよう設定出来る。開示された技術は、乗算または乗算加算演算の結果が、対応する中間積を表すために使用されるビット数よりも少ないビット数の情報を含む場合、いつでも適用出来る。例えば、最終結果を表すために使用されるビット数が、各演算数を表すために使用されるビット数と等しい場合、または最終結果を表すために使用されるビット数が、加数演算数を表すために使用されるビット数と等しい場合に、飽和が必要であるかもしれない。

#### 【0043】

利点、他の長所、及び問題の解決策は特定の実施形態に関連して上記で説明されている。しかしながら、利点、長所、問題の解決策、および任意の利点、長所、または解決策を生じさせまたはより明白なものにしえるいかなる特徴も、臨界的であるとして、必須であるとして、または任意のもしくは全ての請求項の本質的な特徴として解釈されるべきではない。

10

20

30

40

50

【図1】

(先行技術)

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(74)代理人 100162156

弁理士 村雨 圭介

(72)発明者 ケビン エイ. ハード

アメリカ合衆国、コロラド州 80528、フォート コリンズ、ソウヒル ドライブ 5007

(72)発明者 スコット エイ. ヒルカー

アメリカ合衆国、カリフォルニア州 95008、キャンベル、ロングフェロー アベニュー 1

040

審査官 緑川 隆

(56)参考文献 特開平09-245019(JP,A)

特開2006-227939(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 7 / 00

G 06 F 7 / 38 - 7 / 78