(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-54188

(P2004-54188A)

(43) 公開日 平成16年2月19日(2004.2.19)

(51) Int.CI.<sup>7</sup>**G09G** 3/30**G09F** 9/30**G09G** 3/20**H01L** 29/786**H03K** 17/695

F 1

G09G 3/30

G09F 9/30

G09G 3/20

H01L 29/786

H03K 17/695

審査請求 未請求 請求項の数 45 O L (全 30 頁) 最終頁に続く

テーマコード (参考)

3K007

5C080

5C094

5F110

5J055

- (21) 出願番号 特願2002-223165 (P2002-223165)

(22) 出願日 平成14年7月31日 (2002.7.31)

(31) 優先権主張番号 特願2001-274140 (P2001-274140)

(32) 優先日 平成13年9月10日 (2001.9.10)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2002-160245 (P2002-160245)

(32) 優先日 平成14年5月31日 (2002.5.31)

(33) 優先権主張国 日本国 (JP)

- (71) 出願人 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107076

弁理士 藤綱 英吉

(74) 代理人 100107261

弁理士 須澤 修

(72) 発明者 宮澤 貴士

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

F ターム (参考) 3K007 AB02 AB04 AB17 AB18 BA06

BB07 DB03 GA02 GA04

最終頁に続く

(54) 【発明の名称】 単位回路、電子回路、電子装置、電気光学装置、駆動方法および電子機器

## (57) 【要約】

【課題】 駆動トランジスタ Tr 1 のバラツキを補償する。

【解決手段】 電流型の被駆動素子 L と、これに供給する電流量を制御する駆動トランジスタ Tr 1 と、そのゲートに接続された容量素子 C と、駆動トランジスタ Tr 1 のゲートに接続されたスイッチングトランジスタ Tr 3 と、スイッチングトランジスタ Tr 3 のゲートに接続された走査線 S と、スイッチングトランジスタ Tr 3 のソースもしくはドレインと接続されたデータ線 D と、スイッチングトランジスタ Tr 3 を介して信号線と接続される電源線 V とを備える画素回路において、電源線 V とスイッチングトランジスタ Tr 3 との間にダイオード接続された補償トランジスタ Tr 4 を介在させる。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

被駆動素子と、

前記被駆動素子への電流量を制御する駆動トランジスタと、

前記駆動トランジスタのゲートに接続された容量素子と、

前記ゲートに直接接続され、ダイオード接続された補償トランジスタとを含み、

前記補償トランジスタを通過する、データ信号として供給されるデータ電流に応じて前記駆動トランジスタの導通状態が設定される

ことを特徴とする単位回路。

**【請求項 2】**

請求項 1 に記載の単位回路において、

さらに、前記補償トランジスタと、ソースまたはドレインのいずれか一方を介して直列に接続された第 1 のスイッチングトランジスタとを含み、

前記第 1 のスイッチングトランジスタのソースまたはドレインの他方は、信号線に接続され、前記第 1 のスイッチングトランジスタを介して前記信号線と前記補償トランジスタとが電気的に接続された時に前記データ電流が前記補償トランジスタを通過することを特徴とする単位回路。

**【請求項 3】**

被駆動素子と、

前記被駆動素子への電流量を制御する駆動トランジスタと、

前記駆動トランジスタのゲートに接続された容量素子と、

前記駆動トランジスタのゲートに接続された第 1 のスイッチングトランジスタと、

前記第 1 のスイッチングトランジスタのゲートに接続された第 1 の信号線と、前記第 1 のスイッチングトランジスタのソースまたはドレインのいずれか一方に接続された第 2 の信号線と、

電源電圧が印加された電源線とを備えた単位回路であって、

前記電源線と前記第 1 のスイッチングトランジスタのソースまたはドレインのいずれか他方との間に直列に接続された補償トランジスタ及び第 2 のスイッチングトランジスタを有し、

前記補償トランジスタはダイオード接続され、

前記第 2 のスイッチングトランジスタのゲートは前記第 1 の信号線とは異なる第 3 の信号線に接続されている

ことを特徴とする単位回路。

**【請求項 4】**

請求項 3 に記載の単位回路において、

前記第 1 のスイッチングトランジスタ及び前記第 2 のスイッチングトランジスタが共にオン状態となる期間が設けられている

ことを特徴とする単位回路。

**【請求項 5】**

被駆動素子と、

前記被駆動素子への電流量を制御する駆動トランジスタと、

前記駆動トランジスタのゲートに接続された容量素子と、

前記駆動トランジスタのゲートに接続された第 1 のスイッチングトランジスタと、

前記第 1 のスイッチングトランジスタのゲートに接続された第 1 の信号線と、前記第 1 のスイッチングトランジスタのソースまたはドレインのいずれか一方に接続された第 2 の信号線と、

電源電圧が印加された電源線とを備えた単位回路であって、

前記電源線と前記第 1 のスイッチングトランジスタのソースまたはドレインのいずれか他方との間に直列に接続された補償トランジスタ及び第 2 のスイッチングトランジスタを有し、

10

20

30

40

50

前記補償トランジスタはダイオード接続され、

前記第2のスイッチングトランジスタのゲートは前記第1の信号線に接続されている

ことを特徴とする単位回路。

【請求項6】

請求項3または5に記載の単位回路において、

前記第2の信号線はデータ信号として電流を供給することを特徴とする単位回路。

【請求項7】

請求項6に記載の単位回路において、

前記補償トランジスタに流れる電流量に応じた電荷が前記容量素子に蓄電されることを特

徴とする単位回路。 10

【請求項8】

前記駆動トランジスタと前記補償トランジスタとにおいてゲート電圧に対するソース・ド

レイン間の電流特性が略同一であることを特徴とする請求項1乃至7のいずれかに記載の

単位回路。

【請求項9】

前記補償トランジスタに流れる電流量は、前記駆動トランジスタによって制御された電流量

よりも大きいことを特徴とする請求項1乃至7のいずれかに記載の単位回路。

【請求項10】

請求項1乃至9のいずれかに記載の単位回路において、前記被駆動素子が有機エレクトロ

ルミネッセンス素子であることを特徴とする単位回路。 20

【請求項11】

請求項3乃至10のいずれかに記載の単位回路において、前記駆動トランジスタ、前記第

1及び第2のスイッチングトランジスタ、前記補償トランジスタは、それぞれ薄膜トラン

ジスタであることを特徴とする単位回路。

【請求項12】

請求項1乃至11のいずれかに記載の単位回路において、前記駆動トランジスタはpチャ

ネル型であることを特徴とする単位回路。

【請求項13】

第1の走査線に供給される走査信号に応じてオンまたはオフするとともに、ソースまたは

ドレインのいずれか一方がデータ線に接続された第1のスイッチングトランジスタと、

電源電圧が印加される電源線と前記第1のスイッチングトランジスタのソースまたはドレ

インのいずれか他方との間に直列に接続された補償トランジスタ及び第2のスイッチ

ングトランジスタであって、 30

ダイオードとして機能する補償トランジスタと、

前記第1の走査線とは異なる第2の走査線に供給される走査信号に応じてオンまたはオフ

する第2のスイッチングトランジスタと、

ゲートが前記第1のスイッチングトランジスタのソースまたはドレインのいずれか他方に

接続されて、被駆動素子を駆動する駆動トランジスタと、

前記駆動トランジスタのゲート電圧を保持する容量素子と

を具備することを特徴とする単位回路。 40

【請求項14】

第1の走査線に供給される走査信号に応じてオンまたはオフするとともに、ソースまたは

ドレインのいずれか一方がデータ線に接続された第1のスイッチングトランジスタと、

電源電圧が印加される電源線と前記第1のスイッチングトランジスタのソースまたはドレ

インのいずれか他方との間に直列に接続された補償トランジスタ及び第2のスイッチ

ングトランジスタであって、

ダイオードとして機能する補償トランジスタと、

前記第1の走査線に供給される走査信号に応じてオンまたはオフする第2のスイッチング

トランジスタと、

ゲートが前記第1のスイッチングトランジスタのソースまたはドレインのいずれか他方に 50

接続されて、被駆動素子を駆動する駆動トランジスタと、前記駆動トランジスタのゲート電圧を保持する容量素子とを具備することを特徴とする単位回路。

**【請求項 15】**

走査線に供給される走査信号に応じてオンまたはオフするとともに、ソースまたはドレインのいずれか一方がデータ線に接続されたスイッチングトランジスタと、前記スイッチングトランジスタがオンする期間の少なくとも一部または全部の期間にて第1の電源電圧が印加される第1の電源線と前記スイッチングトランジスタのソースまたはドレインのいずれか一方がデータ線に接続されたスイッチングトランジスタと、前記スイッチングトランジスタのソースまたはドレインのいずれか一方が第2の電源電圧が印加された第2の電源線に接続されて、被駆動素子を駆動する駆動トランジスタと、前記駆動トランジスタのゲート電圧を保持する容量素子とを具備することを特徴とする単位回路。10

**【請求項 16】**

走査信号が供給される走査線にゲートが接続されるとともに、ソースまたはドレインのいずれか一方がデータ線に接続されたスイッチングトランジスタと、ソースまたはドレインにゲートが接続された補償トランジスタであって、前記走査信号に応じて前記スイッチングトランジスタがオンする期間の少なくとも一部または全部の期間にて第1の電源電圧が印加される第1の電源線にソースまたはドレインのいずれか一方が接続され、前記スイッチングトランジスタのソースまたはドレインのいずれか一方がデータ線に接続されるとともに、自己のソースまたはドレインの一方が第2の電源電圧が印加された第2の電源線に接続されて、被駆動素子を駆動する駆動トランジスタと、前記駆動トランジスタのゲートに一端が接続された容量素子とを具備することを特徴とする単位回路。20

**【請求項 17】**

前記第1の電源電圧と前記第2の電源電圧とは略等しいことを特徴とする請求項15または16に記載の単位回路。30

**【請求項 18】**

請求項1乃至17のいずれかに記載の単位回路を少なくとも一つ備えたことを特徴とする電子装置。

**【請求項 19】**

請求項1乃至17のいずれかに記載の単位回路を画素回路として備えた電気光学装置を実装したことを特徴とする電子機器。

**【請求項 20】**

複数の単位回路を含む電子回路であって、

前記複数の単位回路の各々は、

第1の端子及び第2の端子を含む駆動トランジスタと、40

第3の端子及び第4の端子を含み、前記駆動トランジスタのゲートに前記第3の端子が接続された補償トランジスタと、

第5の端子及び第6の端子を含み、前記駆動トランジスタのゲート及び前記第3の端子に前記第5の端子が接続されたスイッチングトランジスタと、

前記補償トランジスタ及び前記スイッチングトランジスタを経由して流れる電流に応じた電荷量を保持するとともに、前記駆動トランジスタのゲートに一端が接続された容量素子と

を含み、

前記第4の端子は前記複数の単位回路のうち他の単位回路の前記第4の端子と共に第1の50

電源線に接続され、

前記第2の端子は第2の電源線に接続され、

前記第1の電源線を複数の電位に設定する、または、前記第1の電源線と電源電位との切断・接続を制御する制御回路を備える

ことを特徴とする電子回路。

【請求項21】

請求項20に記載の電子回路において、

前記単位回路の各々には、前記駆動トランジスタ、前記補償トランジスタ及び前記スイッチングトランジスタ以外のトランジスタは存在しないことを特徴とする電子回路。

【請求項22】

請求項20または21に記載の電子回路において、

前記補償トランジスタは、そのゲートが前記第3の端子に接続されていることを特徴とする電子回路。

【請求項23】

請求項20乃至22のいずれかに記載の電子回路において、

前記駆動トランジスタと前記補償トランジスタの導電型は同じであることを特徴とする電子回路。

【請求項24】

請求項20乃至23のいずれかに記載の電子回路において、前記第1の端子には電子素子が接続されていることを特徴とする電子回路。

【請求項25】

請求項24に記載の電子回路において、

前記電子素子は、電流駆動される被駆動素子であることを特徴とする電子回路。

【請求項26】

請求項20乃至24のいずれかに記載の電子回路において、

前記制御回路は、第7の端子及び第8の端子を含むトランジスタであり、前記第7の端子は電源に接続され、前記第8の端子は前記第1の電源線に接続されていることを特徴とする電子回路。

【請求項27】

請求項20乃至24のいずれかに記載の電子回路において、

前記補償トランジスタ及び前記スイッチングトランジスタを経由して電流が流れている期間、少なくとも前記第1の電源線及び前記第2の電源線の電位は実質的に同電位となるように設定されていることを特徴とする電子回路。

【請求項28】

請求項27に記載の電子回路において、

前記第1の電源線と前記第2の電源線とが同電位を有する電源に電気的に接続可能であることを特徴とする電子回路。

【請求項29】

請求項20乃至27のいずれかに記載の電子回路において、

前記駆動トランジスタの閾値電圧は前記補償トランジスタの閾値電圧より高くならないよう40に設定されていることを特徴とする電子回路。

【請求項30】

請求項20乃至27のいずれかに記載の電子回路において、

前記補償トランジスタに流れる電流量は、前記駆動トランジスタによって制御された電流量よりも大きいことを特徴とする電子回路。

【請求項31】

複数の単位回路を備えた電気光学装置であって、

前記複数の単位回路の各々は、

第1の端子及び第2の端子を含む駆動トランジスタと、

第3の端子及び第4の端子を含み、前記駆動トランジスタのゲートに前記第3の端子が接50

続された補償トランジスタと、

第5の端子及び第6の端子を含み、前記駆動トランジスタのゲート及び前記第3の端子に前記第5の端子が接続されたスイッチングトランジスタと、

前記第1の端子に接続された電気光学素子と、

前記補償トランジスタ及び前記スイッチングトランジスタを経由して流れる電流に応じた電荷量を保持し、前記駆動トランジスタのゲートに一端が接続された容量素子とを含み、

前記第4の端子に接続された第1の電源線は、前記複数の単位回路のうち少なくとも1つの他の単位回路の前記第4の端子にも共通接続され、

前記第2の端子は第2の電源線に接続され、

前記第1の電源線を複数の電位に設定する、または、前記第1の電源線と電源電位との切断・接続を制御する制御回路を備える

ことを特徴とする電気光学装置。

#### 【請求項32】

請求項31に記載の電気光学装置において、

前記電気光学素子は有機EL素子であることを特徴とする電気光学装置。

#### 【請求項33】

請求項31または32に記載の電気光学装置において、

前記制御回路は、第7の端子及び第8の端子を含むトランジスタであり、前記第7の端子は電源に接続され、前記第8の端子は前記第1の電源線に接続されている

ことを特徴とする電気光学装置。

#### 【請求項34】

請求項31乃至33のいずれかに記載の電気光学装置において、

前記補償トランジスタ及び前記スイッチングトランジスタを経由して電流が流れている期間は少なくとも前記第1の電源線及び前記第2の電源線の電位は実質的に同電位となるよう設定されていることを特徴とする電気光学装置。

#### 【請求項35】

請求項34に記載の電気光学装置において、

前記第1の電源線と前記第2の電源線とが同電位を有する電源に電気的に接続可能であることを特徴とする電気光学装置。

#### 【請求項36】

請求項31乃至34のいずれかに記載の電気光学装置において、

前記駆動トランジスタの閾値電圧は前記補償トランジスタの閾値電圧より高くならないように設定されていることを特徴とする電気光学装置。

#### 【請求項37】

複数の走査線と、複数のデータ線と、前記複数の走査線と前記複数のデータ線との各交差部に対応してそれぞれ配置された単位回路と、複数の第1の電源線とを含む電気光学装置であって、

前記単位回路の各々は、

第1の端子及び第2の端子を含む駆動トランジスタと、

第3の端子及び第4の端子を含み、前記駆動トランジスタのゲートに前記第3の端子が接続された補償トランジスタと、

第5の端子及び第6の端子を含み、前記駆動トランジスタのゲート及び前記第3の端子に前記第5の端子が接続されたスイッチングトランジスタと、

前記第1の端子に接続された電気光学素子と、

前記補償トランジスタ及び前記スイッチングトランジスタを経由して流れる電流値に応じた電荷量を保持し、前記駆動トランジスタのゲートに一端が接続された容量素子とを含み、

一連の単位回路に含まれるスイッチングトランジスタのゲートは一つの走査線に共通接続され、前記一連の単位回路における第4の端子は一つの第1の電源線に共通接続され、

10

20

30

40

50

前記第1の電源線の各々を複数の電位に設定する、または、一つの第1の電源線と電源電位との切断・接続を制御する制御回路を備えることを特徴とする電気光学装置。

【請求項38】

請求項37に記載の電気光学装置において、

前記一連の単位回路における第2の端子は、一つの第2の電源線に共通接続されていることを特徴とする電気光学装置。

【請求項39】

請求項37または38に記載の電気光学装置において、

前記補償トランジスタのゲートは、自己の第3の端子に接続されていることを特徴とする電気光学装置。 10

【請求項40】

請求項37乃至39のいずれかに記載の電気光学装置において、

前記電気光学素子は有機EL素子であることを特徴する電気光学装置。

【請求項41】

請求項37乃至39のいずれかに記載の電気光学装置において、

前記走査線に沿って、同色の電気光学素子が配置されるようにしたことを特徴とする電気光学装置。

【請求項42】

第1の端子及び第2の端子を含む駆動トランジスタと、

第3の端子及び第4の端子を含み、前記駆動トランジスタのゲートに前記第3の端子が接続された補償トランジスタと、

第5の端子及び第6の端子を含み、前記駆動トランジスタのゲート及び前記第3の端子に前記第5の端子が接続されたスイッチングトランジスタと、

前記駆動トランジスタのゲートに一端が接続された容量素子と

を含む単位回路を複数備え、

一連の単位回路における第4の端子は第1の電源線に共通接続された電子回路の駆動方法であって、

前記一連の単位回路の第4の端子の各々を所定電位に電気的接続し、かつ、前記一連の単位回路に含まれるスイッチングトランジスタの各々をオン状態とすることにより、前記補償トランジスタを経由して流れる電流に応じた電荷量を容量素子に保持し、前記電荷量に応じた電圧を前記駆動トランジスタに印加して、前記第1の端子と前記第2の端子との間の導通状態を設定するステップと、

前記一連の単位回路の第4の端子の各々を前記所定電位から電気的に切り離すステップとを含むことを特徴とする電子回路の駆動方法。 30

【請求項43】

第1の端子及び第2の端子を含む駆動トランジスタと、

第3の端子及び第4の端子を含み、前記駆動トランジスタのゲートに前記第3の端子が接続された補償トランジスタと、

第5の端子及び第6の端子を含み、前記駆動トランジスタのゲート及び前記第3の端子に前記第5の端子が接続されたスイッチングトランジスタと、 40

前記第1の端子に接続された電気光学素子と、

前記駆動トランジスタのゲートに一端が接続された容量素子と

を含む単位回路が、複数の走査線と複数のデータ線の各交差部に対応してそれぞれ配置され、

一連の単位回路に含まれるスイッチングトランジスタのゲートが一つの走査線に共通接続され、前記一連の単位回路における第4の端子が一つの第1の電源線に共通接続された電気光学装置の駆動方法であって、

前記一連の単位回路の第4の端子の各々を所定電位に電気的接続し、かつ、前記一連の単位回路に含まれるスイッチングトランジスタのゲートにそれぞれ走査信号を供給しオン状 50

態として、前記複数のデータ線の対応するデータ線と電気的に接続する期間に、前記補償トランジスタを経由して流れる電流の電流レベルに応じた電荷量を容量素子に保持し、前記電荷量に応じた電圧を前記第1のゲートに印加して、前記第1の端子と前記第2の端子との間の導通状態を設定するステップと、

前記一連の単位回路の第4の端子の各々を前記所定電位から電気的に切り離すステップとを含むことを特徴とする電気光学装置の駆動方法。

#### 【請求項 4 4】

請求項 20 乃至 30 のいずれかに記載の電子回路を実装したことを特徴とする電子機器。

#### 【請求項 4 5】

請求項 31 乃至 41 のいずれかに記載の電気光学装置を実装したことを特徴とする電子機器。 10

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

この発明は、有機エレクトロルミネッセンス素子などのような電流型の被駆動素子を駆動するトランジスタの特性バラツキを補償する単位回路、電子回路、電気光学装置、駆動方法、電子機器に関する。 20

##### 【0002】

##### 【従来の技術】

近年、従来のLCD (Liquid Crystal Display) 素子に代わる次世代の発光デバイスとして、有機EL (Electronic Luminescence) 素子が注目されている。有機EL素子は、自発光型であるために視野角依存性が少なく、また、バックライトや反射光が不要であるために低消費電力であるなど、表示パネルとして優れた特性を有している。 20

##### 【0003】

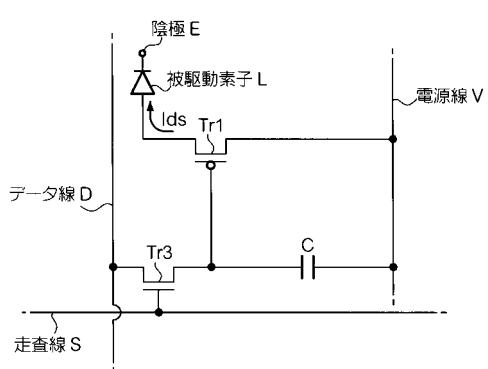

このような有機EL素子を駆動するための従来の回路としては、例えば、図14に示す構成が挙げられる。この回路において、駆動トランジスタTr1のドレインは、正孔注入用電極を介して、電流型の被駆動素子L(有機EL素子)に接続されている。スイッチングトランジスタTr3のゲートは走査線Sに、ソースはデータ線Dに、ドレインは駆動トランジスタTr1のゲートと容量素子Cの一端とにそれぞれ接続されている。容量素子Cの他端は電源線Vに接続されている。スイッチングトランジスタTr3は、走査線Sからゲートに供給される選択電位によりオン・オフ制御され、このオンの期間中にデータ線Dから供給される信号電圧により容量素子Cに電荷が蓄電される。 30

##### 【0004】

そして、この電荷により生じる容量素子Cの端子間電圧により駆動トランジスタTr1のゲートに電圧が印加され、この電圧に応じた量の電流IdSが電源線Vから被駆動素子Lに供給される。なお、駆動トランジスタTr1のゲートに印加される電圧に応じて駆動トランジスタTr1のソース・ドレイン間のコンダクタンスが制御され、これにより被駆動素子Lたる有機EL素子の輝度が定められる。 40

##### 【0005】

##### 【発明が解決しようとする課題】

しかしながら、上記回路を適用した表示パネルの製造プロセスにおいて、画素を構成する被駆動素子Lの特性については、表示パネルの各画素にわたって比較的均一に構成することができるのに対し、駆動トランジスタTr1の特性については、半導体膜の膜質や、膜厚、不純物濃度や拡散領域、ゲート絶縁膜等の材質、膜厚、動作温度などの各種条件により、表示パネルの各画素にわたって均質化することは難しい。

##### 【0006】

ここで、上記回路における各トランジスタを、薄膜トランジスタにより構成する場合、各トランジスタの特性にバラツキが生じやすく、とくに上記回路を用いて表示パネルを構成したときには、駆動トランジスタTr1のゲート電圧に対するドレイン・ソース間電流の 50

特性のバラツキが問題となる。すなわち、各画素の駆動トランジスタTr1のゲートに共通の電圧を印加しても、有機EL素子を流れる電流量は、上記バラツキの存在により画素毎に異なるため、各画素の発光輝度にむらが生じて表示パネルの画像品質が著しく損なわれてしまうことになる。

#### 【0007】

このような事情から、電流型の被駆動素子を駆動する駆動トランジスタのバラツキを補償するための回路が必要とされている。

本発明は、このような事情に鑑みてなされたもので、その目的とするところは、駆動トランジスタの特性バラツキの影響を受けにくくして、有機EL素子などの電流型の被駆動素子に、目的とする電流を供給することが可能な単位回路、電子回路、電気光学装置、駆動方法、電子機器を提供することにある。

#### 【0008】

##### 【課題を解決するための手段】

上記目的を達成するため、本発明は、被駆動素子と、前記被駆動素子への電流量を制御する駆動トランジスタと、前記駆動トランジスタのゲートに接続された容量素子と、前記ゲートに直接接続され、ダイオード接続された補償トランジスタとを含み、前記補償トランジスタを通過する、データ信号として供給されるデータ電流に応じて前記駆動トランジスタの導通状態が設定されることを特徴とする。この構成によれば、例えば、補償トランジスタが駆動トランジスタのゲートに直接接続されているので、これら2つのトランジスタは互いに近接して設けられる結果、その2つのトランジスタの特性を揃えること、または特性比を調整することが容易となる。また、補償トランジスタを通過するデータ電流が、駆動トランジスタによって制御される電流量に直接反映される。ここで、前記補償トランジスタと、ソースまたはドレインのいずれか一方を介して直列に接続された第1のスイッチングトランジスタとを含み、前記第1のスイッチングトランジスタのソースまたはドレインの他方は、信号線に接続され、前記第1のスイッチングトランジスタを介して前記信号線と前記補償トランジスタとが電気的に接続された時に前記データ電流が前記補償トランジスタを通過する構成が好ましい。

#### 【0009】

また、上記目的を達成するための、本発明は、被駆動素子と、前記被駆動素子への電流量を制御する駆動トランジスタと、前記駆動トランジスタのゲートに接続された容量素子と、前記駆動トランジスタのゲートに接続された第1のスイッチングトランジスタと、前記第1のスイッチングトランジスタのゲートに接続された第1の信号線と、前記第1のスイッチングトランジスタのソースまたはドレインのいずれか一方に接続された第2の信号線と、電源電圧が印加された電源線とを備えた単位回路であって、前記電源線と前記第1のスイッチングトランジスタのソースまたはドレインのいずれか一方を介して直列に接続された補償トランジスタ及び第2のスイッチングトランジスタを有し、前記補償トランジスタはダイオード接続され、前記第2のスイッチングトランジスタのゲートは前記第1の信号線とは異なる第3の信号線に接続されている構成を特徴とする。また、本発明は、電流駆動される被駆動素子と、前記被駆動素子への電流量を制御する駆動トランジスタと、前記駆動トランジスタのゲートに接続された容量素子と、前記駆動トランジスタのゲートに接続された第1のスイッチングトランジスタと、前記第1のスイッチングトランジスタのゲートに接続された第1の信号線と、前記第1のスイッチングトランジスタのソースまたはドレインのいずれか一方に接続された第2の信号線と、電源電圧が印加された電源線とを備えた単位回路であって、前記電源線と前記第1のスイッチングトランジスタのソースまたはドレインのいずれか一方との間に直列に接続された補償トランジスタ及び第2のスイッチングトランジスタを有し、前記補償トランジスタはダイオード接続され、前記第2のスイッチングトランジスタのゲートは前記第1の信号線に接続されている構成を特徴とする。いずれの構成においても、駆動トランジスタのバラツキを補償することが可能となる。ここで、前者と後者とを比較すると、後者に係る構成の方では、第1及び第2のスイッチングトランジスタのゲートが同一の第1の信号線に接続されるので、第3の信号

10

20

30

40

50

線が不要となり、配線数を削減することが可能となる。なお、ダイオード接続されたトランジスタとは、そのソースまたはドレインのいずれか一方が、ゲートに接続された状態にあるトランジスタをいう。また、前者に係る構成において、前記第1のスイッチングトランジスタ及び前記第2のスイッチングトランジスタが共にオン状態となる期間が設けられている構成が好ましい。

ここで、前者および後者に係る構成において、前記第2の信号線は、データ信号として電流を供給するデータ線である構成が好ましい。

また、前記補償トランジスタに流れる電流量に応じた電荷が前記容量素子に蓄電される構成でも良い。

前記駆動トランジスタと前記補償トランジスタとにおいてゲート電圧に対するソース・ドレイン間の電流特性が略同一であることも好ましいが、前記補償トランジスタに流れる電流量は、前記駆動トランジスタによって制御された電流量よりも大きい構成であっても良い。

さらに、前記被駆動素子が有機エレクトロルミネッセンス素子であることが望ましい。

また、前記駆動トランジスタ、前記第1及び第2のスイッチングトランジスタ、前記補償トランジスタは、それぞれ薄膜トランジスタであることが好ましいが、前記駆動トランジスタについては、経年変化の少ないpチャネル型であることが望ましい。

#### 【0010】

上記目的を達成するために、本発明は、第1の走査線に供給される走査信号に応じてオンまたはオフするとともに、ソースまたはドレインのいずれか一方がデータ線に接続された第1のスイッチングトランジスタと、電源電圧が印加される電源線と前記第1のスイッチングトランジスタのソースまたはドレインのいずれか他方との間に直列に接続された補償トランジスタ及び第2のスイッチングトランジスタであって、ダイオードとして機能する補償トランジスタと、前記第1の走査線とは異なる第2の走査線に供給される走査信号に応じてオンまたはオフする第2のスイッチングトランジスタと、ゲートが前記第1のスイッチングトランジスタのソースまたはドレインのいずれか他方に接続されて、被駆動素子を駆動する駆動トランジスタと、前記駆動トランジスタのゲート電圧を保持する容量素子とを具備する構成を特徴とする。

また、本発明は、第1の走査線に供給される走査信号に応じてオンまたはオフするとともに、ソースまたはドレインのいずれか一方がデータ線に接続された第1のスイッチングトランジスタと、電源電圧が印加される電源線と前記第1のスイッチングトランジスタのソースまたはドレインのいずれか他方との間に直列に接続された補償トランジスタ及び第2のスイッチングトランジスタであって、ダイオードとして機能する補償トランジスタと、前記第1の走査線に供給される走査信号に応じてオンまたはオフする第2のスイッチングトランジスタと、ゲートが前記第1のスイッチングトランジスタのソースまたはドレインのいずれか他方に接続されて、被駆動素子を駆動する駆動トランジスタと、前記駆動トランジスタのゲート電圧を保持する容量素子とを具備する構成を特徴とする。いずれの構成においても、駆動トランジスタのバラツキを補償することが可能となる。ここで、前者と後者とを比較すると、後者に係る構成の方では、第1及び第2のスイッチングトランジスタのゲートが同一の走査線に接続されるので、第2の走査線が不要となり、配線数を削減することが可能となる。

#### 【0011】

上記目的を達成するために、本発明は、走査線に供給される走査信号に応じてオンまたはオフするとともに、ソースまたはドレインのいずれか一方がデータ線に接続されたスイッチングトランジスタと、前記スイッチングトランジスタがオンする期間の少なくとも一部または全部の期間にて第1の電源電圧が印加される第1の電源線と前記スイッチングトランジスタのソースまたはドレインのいずれか他方との間にダイオードとして機能する補償トランジスタと、ゲートが前記スイッチングトランジスタのソースまたはドレインの他方に接続されるとともに、自己のソースまたはドレインの一方が第2の電源電圧が印加された第2の電源線に接続されて、被駆動素子を駆動する駆動トランジスタと、前記駆動ト

10

20

30

40

50

ランジスタのゲート電圧を保持する容量素子とを具備する構成を特徴とする。

また、本発明は、走査信号が供給される走査線にゲートが接続されるとともに、ソースまたはドレインのいずれか一方がデータ線に接続されたスイッチングトランジスタと、ソースまたはドレインにゲートが接続された補償トランジスタであって、前記走査信号に応じて前記スイッチングトランジスタがオンする期間の少なくとも一部または全部の期間にて第1の電源電圧が印加される第1の電源線にソースまたはドレインのいずれか一方が接続され、前記スイッチングトランジスタのソースまたはドレインのいずれか他方に、自己のソースまたはドレインのいずれか他方が接続された補償トランジスタと、ゲートが前記スイッチングトランジスタのソースまたはドレインの他方に接続されるとともに、自己のソースまたはドレインの一方が第2の電源電圧が印加された第2の電源線に接続されて、被駆動素子を駆動する駆動トランジスタと、前記駆動トランジスタのゲートに一端が接続された容量素子とを具備する構成を特徴とする。いずれの構成においても、駆動トランジスタのパラツキを補償するとともに、トランジスタを1個減らすことが可能となる。10

ここで、前記第1の電源電圧と前記第2の電源電圧とは略等しいことが望ましい。

また、上記単位回路を少なくとも1つ用いて、電気光学装置、記憶装置、センサー装置等の種々の電子装置を構成しても良い。例えば、上記単位回路を画素回路として用いれば電気光学装置を構成することが可能である。このような電気光学装置を電子機器に実装しても良い。

#### 【0012】

上記目的を達成するために、本発明は、複数の単位回路を含む電子回路であって、前記複数の単位回路の各々は、第1の端子及び第2の端子を含む駆動トランジスタと、第3の端子及び第4の端子を含み、前記駆動トランジスタのゲートに前記第3の端子が接続された補償トランジスタと、第5の端子及び第6の端子を含み、前記駆動トランジスタのゲート及び前記第3の端子に前記第5の端子が接続されたスイッチングトランジスタと、前記補償トランジスタ及び前記スイッチングトランジスタを経由して流れる電流に応じた電荷量を保持するとともに、前記駆動トランジスタのゲートに一端が接続された容量素子とを含み、前記第4の端子は前記複数の単位回路のうち他の単位回路の前記第4の端子と共に第1の電源線に接続され、前記第2の端子は第2の電源線に接続され、前記第1の電源線を複数の電位に設定する、または、前記第1の電源線と電源電位との切断・接続を制御する制御回路を備える構成を特徴とする。この構成によれば、簡素な構成で駆動トランジスタの閾値電圧を補償することができる。20

この電子回路において、前記単位回路の各々には、前記駆動トランジスタ、前記補償トランジスタ及び前記スイッチングトランジスタ以外のトランジスタは存在しない。したがって、駆動トランジスタの閾値電圧を補償しつつ、使用するトランジスタの個数を従来のものに較べて1個低減させることできる。

この電子回路において、前記補償トランジスタは、そのゲートが前記第3の端子に接続されている。したがって、駆動トランジスタを流れる電流は、容量素子に充電される電圧で制御することができる。

この電子回路において、前記駆動トランジスタと前記補償トランジスタの導電型は同じである。これによれば、駆動トランジスタを容易に補償することができる。40

この電子回路において、前記第1の端子には電子素子が接続されている。駆動トランジスタの閾値電圧は補償されているので、電子素子に流れる電流値を精度良く制御することができる。なお、電子素子としては、電流駆動される被駆動素子である。

この電子回路において、前記制御回路は、第7の端子及び第8の端子を含むトランジスタであり、前記第7の端子は電源に接続され、前記第8の端子は前記第1の電源線に接続されている。これによれば、制御回路を容易に構成することができる。

この電子回路において、前記補償トランジスタ及び前記スイッチングトランジスタを経由して電流が流れている期間、少なくとも前記第1の電源線及び前記第2の電源線の電位は実質的に同電位となるように設定されている。これによれば、補償トランジスタで生成された駆動トランジスタの閾値電圧とほぼ等しい電圧を該駆動トランジスタのゲートに確実50

に供給することができる。

この電子回路において、前記第1の電源線と前記第2の電源線とが同電位を有する電源に電気的に接続可能である。これによれば、第1の電源線と第2の電源線とに供給される電圧を容易にほぼ等しくさせることができる。

この電子回路において、前記駆動トランジスタの閾値電圧は前記補償トランジスタの閾値電圧より高くなないように設定されている。これによれば、駆動トランジスタの閾値電圧を確実に補償することができる。

この電子回路において、前記補償トランジスタに流れる電流量は、前記駆動トランジスタによって制御された電流量よりも大きい構成が好ましい。この構成によれば、スイッチングトランジスタがオンしたときに、当該スイッチングトランジスタ及び補償トランジスタに流れる電流量に応じた電荷を迅速に容量素子に蓄積することが可能となる。10

上記の電子回路を少なくとも1つ用いて、例えば、電気光学装置、記憶装置、センサー装置等の種々の電子装置を構成しても良い。

#### 【0013】

また、本発明は、複数の単位回路を備えた電気光学装置であって、前記複数の単位回路の各々は、第1の端子及び第2の端子を含む駆動トランジスタと、第3の端子及び第4の端子を含み、前記駆動トランジスタのゲートに前記第3の端子が接続された補償トランジスタと、第5の端子及び第6の端子を含み、前記駆動トランジスタのゲート及び前記第3の端子に前記第5の端子が接続されたスイッチングトランジスタと、前記第1の端子に接続された電気光学素子と、前記補償トランジスタ及び前記スイッチングトランジスタを経由して流れる電流に応じた電荷量を保持し、前記駆動トランジスタのゲートに一端が接続された容量素子とを含み、前記第4の端子に接続された第1の電源線は、前記複数の単位回路のうち少なくとも1つの他の単位回路の前記第4の端子にも共通接続され、前記第2の端子は第2の電源線に接続され、前記第1の電源線を複数の電位に設定する、または、前記第1の電源線と電源電位との切断・接続を制御する制御回路を備える。これによれば、駆動トランジスタの閾値電圧を補償しつつ、従来のものと較べて使用するトランジスタが1個低減されるので、開口率を向上させて、表示品質の高くすることが可能となる。また、単位回路を構成するトランジスタの数を従来のものと較べて1個低減させることができるために、歩留まりを向上させることができる。20

この電気光学装置において、前記電気光学素子は有機EL素子である。これによれば、従来のものと較べて使用するトランジスタを1個低減させることで開光率が高く、かつ、有機EL素子の輝度階調を精度良く制御することができる。30

この電気光学装置において、前記制御回路は、第7の端子及び第8の端子を含むトランジスタであり、前記第7の端子は電源に接続され、前記第8の端子は前記第1の電源線に接続されている。駆動トランジスタの閾値電圧を補償しつつ、従来のものと較べて使用するトランジスタを1個低減した単位を容易に構成することができる。

この電気光学装置において、前記補償トランジスタ及び前記スイッチングトランジスタを経由して電流が流れている期間は少なくとも前記第1の電源線及び前記第2の電源線の電位は実質的に同電位となるように設定されている。これによれば、補償トランジスタで生成された駆動トランジスタの閾値電圧とほぼ等しい電圧を同駆動トランジスタのゲートに確実に供給することができる。この電気光学装置において、前記第1の電源線と前記第2の電源線とが同電位を有する電源に電気的に接続可能である。これによれば、単位回路に接続される第1の電源線と第2の電源線とに供給される電圧を容易にほぼ等しくさせることができる。40

この電気光学装置において、前記駆動トランジスタの閾値電圧は前記補償トランジスタの閾値電圧より高くなないように設定されている。これによれば、駆動トランジスタの閾値電圧を確実に補償することができる。したがって、電気光学素子の輝度階調を精度良く制御することができる。

#### 【0014】

本発明は、複数の走査線と、複数のデータ線と、前記複数の走査線と前記複数のデータ線

50

20

30

40

50

との各交差部に対応してそれぞれ配置された単位回路と、複数の第1の電源線とを含む電気光学装置であって、前記単位回路の各々は、第1の端子及び第2の端子を含む駆動トランジスタと、第3の端子及び第4の端子を含み、前記駆動トランジスタのゲートに前記第3の端子が接続された補償トランジスタと、第5の端子及び第6の端子を含み、前記駆動トランジスタのゲート及び前記第3の端子に前記第5の端子が接続されたスイッチングトランジスタと、前記第1の端子に接続された電気光学素子と、前記補償トランジスタ及び前記スイッチングトランジスタを経由して流れる電流値に応じた電荷量を保持し、前記駆動トランジスタのゲートに一端が接続された容量素子とを含み、一連の単位回路に含まれるスイッチングトランジスタのゲートは一つの走査線に共通接続され、前記一連の単位回路における第4の端子は一つの第1の電源線に共通接続され、前記第1の電源線の各々を複数の電位に設定する、または、一つの第1の電源線と電源電位との切断・接続を制御する制御回路を備える。これによれば、単位回路内に設けられたすべての駆動トランジスタの閾値電圧を補償しつつ、従来のものと較べて使用するトランジスタが1個低減されるので、開口率を向上させて、表示品質の高くすることが可能となる。また、単位回路を構成するトランジスタの数を従来のものと較べて1個低減させることができため、歩留まりを向上させることができる。10

この電気光学装置において、前記一連の単位回路における第2の端子は、一つの第2の電源線に共通接続されている。これによれば、表示品質の高くすることが可能となる。

この電気光学装置において、前記補償トランジスタのゲートは、自己の第3の端子に接続されている。これによれば、補償トランジスタで生成された駆動トランジスタの閾値電圧とほぼ等しい電圧を同駆動トランジスタのゲートに確実に供給することができる。20

この電気光学装置において、前記電気光学素子は有機EL素子である。これによれば、有機EL素子の輝度階調を精度良く制御することができる。この電気光学装置において、前記走査線に沿って、同色の電気光学素子が配置されるようにした。これによれば、開口率を更に向上させることができる。

#### 【0015】

本発明は、第1の端子及び第2の端子を含む駆動トランジスタと、第3の端子及び第4の端子を含み、前記駆動トランジスタのゲートに前記第3の端子が接続された補償トランジスタと、第5の端子及び第6の端子を含み、前記駆動トランジスタのゲート及び前記第3の端子に前記第5の端子が接続されたスイッチングトランジスタと、前記駆動トランジスタのゲートに一端が接続された容量素子とを含む単位回路を複数備え、一連の単位回路における第4の端子は第1の電源線に共通接続された電子回路の駆動方法であって、前記一連の単位回路の第4の端子の各々を所定電位に電気的接続し、かつ、前記一連の単位回路に含まれるスイッチングトランジスタの各々をオン状態とすることにより、前記補償トランジスタを経由して流れる電流に応じた電荷量を容量素子に保持し、前記電荷量に応じた電圧を前記駆動トランジスタに印加して、前記第1の端子と前記第2の端子との間の導通状態を設定するステップと、前記一連の単位回路の第4の端子の各々を前記所定電位から電気的に切り離すステップとを含む。これによれば、駆動トランジスタの閾値電圧を補償して電子回路を駆動させることができる。30

#### 【0016】

本発明は、第1の端子及び第2の端子を含む駆動トランジスタと、第3の端子及び第4の端子を含み、前記駆動トランジスタのゲートに前記第3の端子が接続された補償トランジスタと、第5の端子及び第6の端子を含み、前記駆動トランジスタのゲート及び前記第3の端子に前記第5の端子が接続されたスイッチングトランジスタと、前記第1の端子に接続された電気光学素子と、前記駆動トランジスタのゲートに一端が接続された容量素子とを含む単位回路が、複数の走査線と複数のデータ線の各交差部に対応してそれぞれ配置され、一連の単位回路に含まれるスイッチングトランジスタのゲートが一つの走査線に共通接続され、前記一連の単位回路における第4の端子が一つの第1の電源線に共通接続された電気光学装置の駆動方法であって、前記一連の単位回路の第4の端子の各々を所定電位に電気的接続し、かつ、前記一連の単位回路に含まれるスイッチングトランジスタのゲー40

50

トにそれぞれ走査信号を供給しオン状態として、前記複数のデータ線の対応するデータ線と電気的に接続する期間に、前記補償トランジスタを経由して流れる電流の電流レベルに応じた電荷量を容量素子に保持し、前記電荷量に応じた電圧を前記第1のゲートに印加して、前記第1の端子と前記第2の端子との間の導通状態を設定するステップと、前記一連の単位回路の第4の端子の各々を前記所定電位から電気的に切り離すステップとを含む。これによれば、駆動トランジスタの閾値電圧を補償して電気光学装置を駆動させることができる。

#### 【0017】

本発明の電子機器は、上記電子回路または上記電気光学装置を実装しているので、回路内における駆動トランジスタの閾値電圧を補償することができる上、従来のものと較べて使用するトランジスタを1個低減することができるので、電子機器の歩留まりを向上させることができる。10

#### 【0018】

##### 【発明の実施の形態】

以下、本発明の実施形態について図面を参照して説明する。

#### 【0019】

##### <第1実施形態>

まず、本発明の第1実施形態について説明する。図1は、第1実施形態に係る単位回路が適用される電気光学装置の構成を示す図である。この図に示されるように、この電気光学装置においては、複数の走査線(S1、S2、S3、……)および複数のデータ線(D1、D2、D3、……)が互いに交差するように配設されるとともに、その交差の各々に、本実施形態に係る単位回路の一例である画素回路20がそれぞれマトリクス状に設けられている。20

走査線駆動回路130は、走査線S1、S2、S3、……に対し、所定のタイミングで選択電位Vselをそれぞれ印加する。データ線駆動回路140は、データ線D1、D2、D3、……に対し、データ電流Idataを、それぞれデータ信号として供給する。なお、図1においては、後述する電源線Vが省略されている。また、この説明においては、画素回路20がマトリクス状に配列している部分を表示パネルと呼ぶこともある。本実施形態においては、表示すべき画素の1つが、1つの画素回路20に対応しているが、1つの画素を複数のサブ画素によって表示する構成としても良い。30

#### 【0020】

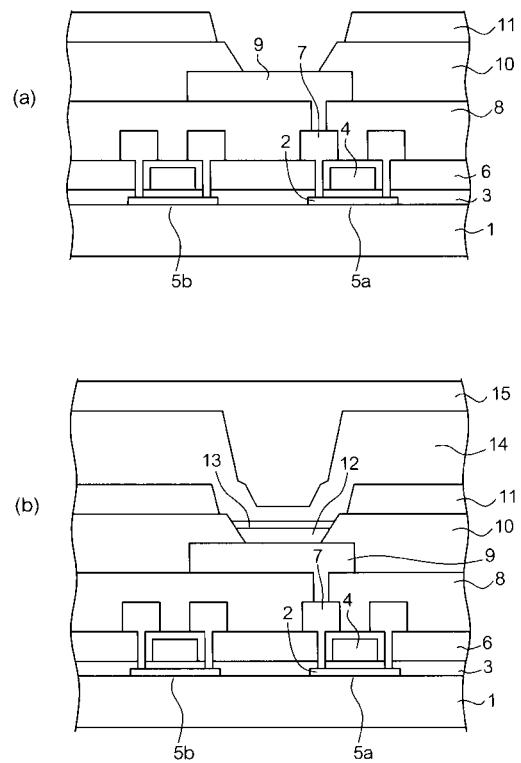

図2(a)は、本実施形態に係る単位回路としての画素回路20の詳細な構成を示す回路図である。なお、この図における画素回路は、一般的な走査線Sとデータ線Dとの交差に対応するものの1つである。

この図において、被駆動素子Lは、例えば、電流駆動される有機EL素子であり、この図ではダイオードとして表記している。この単位回路は、被駆動素子Lのほかに、駆動トランジスタTr1、スイッチングトランジスタTr2(第2のスイッチングトランジスタ)、スイッチングトランジスタTr3(第1のスイッチングトランジスタ)、補償トランジスタTr4、電荷を蓄積する容量素子Cを含んでいる。このうち、駆動トランジスタTr1、補償トランジスタTr4は、いずれも経時劣化の少ないpチャネル型の薄膜トランジスタ(Thin Film Transistor:TFT)であり、スイッチングトランジスタTr2、Tr3はnチャネル型のTFTである。40

#### 【0021】

なお、各トランジスタにpチャネル型もしくはnチャネル型のいずれの導電型を用いるかの選択は、ここで示したものに限られる訳ではない。また、スイッチングトランジスタTr2、Tr3導電型(nチャネル型であるか、pチャネル型であるか)については互いに異なっていてよい。ただし、スイッチングトランジスタTr2、Tr3との導電型を互いに異なる場合には、走査線Sにくわえて、これとは排他的な論理レベルをとる走査線を別途設けて、pチャネル型をとるスイッチングトランジスタのゲートを接続する必要がある。50

## 【0022】

被駆動素子Lの一端は、図示しない正孔注入用電極を介して駆動トランジスタTr1のドレインに接続される一方、被駆動素子Lの他端は陰極Eに接続されている。

また、駆動トランジスタTr1のソースは電源線Vに接続される一方、そのゲートは、容量素子Cの一端と、スイッチングトランジスタTr3のドレインと、トランジスタTr4のドレインとにそれぞれ接続されている。容量素子Cの他端は電源線Vに接続されている。

補償トランジスタTr4のドレインは自己のゲートに接続されている。したがって、補償トランジスタTr4はダイオード接続となっている。

## 【0023】

なお、補償トランジスタTr4のドレインとゲートとは、容量素子Cの一端（駆動トランジスタTr1のゲート、スイッチングトランジスタTr3のドレイン）に接続され、また、補償トランジスタTr4のソースは、スイッチングトランジスタTr2のソースに接続されている。スイッチングトランジスタTr2のドレインは電源線Vに接続されている。スイッチングトランジスタTr3のソースはデータ線Dに接続され、スイッチングトランジスタTr2、Tr3のゲートは、それぞれ走査線Sに接続されている。

## 【0024】

つぎに、図2(a)の単位回路の動作について説明する。スイッチングトランジスタTr2、Tr3は、走査線Sを介して各ゲートに印加される選択電位Vselによりオン・オフ制御される。ここで本実施形態において、スイッチングトランジスタTr2、Tr3はともにnチャネル型であるため、選択電位Vselがハイレベルのときにそれぞれオンとなる。スイッチングトランジスタTr2、Tr3がオンの状態のときにデータ線Dを介してデータ電流Idataが供給されると、補償トランジスタTr4のゲートとソースの電位が等しくなるので、補償トランジスタTr4では、

$$Vgs (\text{ゲートとソースの電位差}) = Vds (\text{ドレインとソースの電位差})$$

となり、この状態に対応した電荷が容量素子Cに蓄電され、これにより容量素子Cの端子間電圧が駆動トランジスタTr1のゲートに印加される。すなわち、データ線Dから供給されるデータ電流Idataの量により駆動トランジスタTr1のゲート電圧が制御され、これにより駆動トランジスタTr1のドレイン・ソース間ににおける電流量が制御され、被駆動素子Lを流れる電流Idsの値が制御されることになる。

## 【0025】

上記回路において、駆動トランジスタTr1と補償トランジスタTr4とは、いわゆるカレント・ミラー回路を構成しており、駆動トランジスタTr1のドレイン・ソース間ににおける電流Idsの値、すなわち、被駆動素子Lに供給される電流の値は、補償トランジスタTr4のドレイン・ソース間ににおける電流量に比例する。

また、駆動トランジスタTr1のドレイン・ソース間ににおける電流Idsと、補償トランジスタTr4のドレイン・ソース間に流れるデータ電流Idataとの比は、駆動トランジスタTr1と補償トランジスタTr4との特性により定まる。したがって、駆動トランジスタTr1と補償トランジスタTr4との特性の一つである利得係数（トランジスタのゲートおよびソースに一定の電圧を印加したときにそのトランジスタに流れる電流量）を一致させておくことで、駆動トランジスタTr1に流れる電流Idsと、補償トランジスタTr4を流れるデータ電流Idataとを一致させることができる。特に、本実施形態では、補償トランジスタTr4のドレインは駆動トランジスタTr1のゲートに直接接続されているので、補償トランジスタTr4を通過するデータ電流Idataが、駆動トランジスタによって制御される電流Idsに直接反映されて、両者の一致性を高めることができる。

## 【0026】

このため、駆動トランジスタTr1と補償トランジスタTr4との利得係数を一致するように表示パネルを構成すれば、たとえ表示パネルの画素ごとに形成されている駆動トランジスタTr1にバラツキが発生しても、表示パネルの各画素に含まれる被駆動素子Lに同

じ大きさの電流  $I_{ds}$  を供給することができる。よって、駆動トランジスタ  $T_{r1}$  の特性バラツキに起因する輝度むらを抑えることができる。

#### 【0027】

よく知られているように、被駆動素子  $L$  を含む表示パネルの製造プロセスにおいて、近接するトランジスタの特性を互いに一致させることは容易である。上述したように本実施形態では、補償トランジスタ  $T_{r4}$  のドレインは駆動トランジスタ  $T_{r1}$  のゲートに直接接続されてほどに近接している。このため、同一の画素回路において、駆動トランジスタ  $T_{r1}$  と補償トランジスタ  $T_{r4}$  との利得係数を一致するように構成することは、困難なことではなく、したがって、輝度むらの少ない表示パネルを製造することは、比較的容易である。

10

#### 【0028】

また、本実施形態では、データ線駆動回路 140 により供給されるデータ電流  $I_{data}$  に応じて駆動トランジスタ  $T_{r1}$  のゲート電圧が設定されるが、駆動トランジスタ  $T_{r1}$  と補償トランジスタ  $T_{r4}$  とがいわゆるカレント・ミラー回路を構成しているので、温度変化などによる駆動トランジスタ  $T_{r1}$  のドレイン・ソース間における電流  $I_{ds}$  の変動が抑制されて、安定化が図られることになる。

#### 【0029】

図 2 (a) の回路では、補償トランジスタ  $T_{r4}$  を、スイッチングトランジスタ  $T_{r2}$  と、スイッチングトランジスタ  $T_{r3}$  との間に介在させているが、図 2 (b) に示すように、スイッチングトランジスタ  $T_{r2}$  と電源線  $V$  との間に介在させるようにしてもよい。なお、この回路においても駆動トランジスタ  $T_{r1}$  のドレイン・ソース間電流  $I_{ds}$  が、補償トランジスタ  $T_{r4}$  を流れるデータ電流  $I_{data}$  により定まることは、図 2 (a) に示される回路と同様である。

20

#### 【0030】

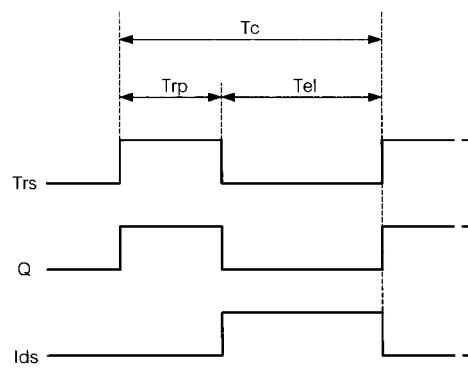

図 3 は、図 2 (a) に示した単位回路の動作を説明するためのタイミングチャートである。

まず、走査線駆動回路 130 が走査線  $S$  に供給する選択電位  $V_{sel}$  をハイレベルにする一方、データ線駆動回路 140 がデータ線  $D$  にデータ電流  $I_{data}$  を供給する。

選択電位  $V_{sel}$  がハイレベルになると、スイッチングトランジスタ  $T_{r2}$ 、 $T_{r3}$  がともにオン状態になるので、データ電流  $I_{data}$  は、電源線  $V$ 、スイッチングトランジスタ  $T_{r2}$ 、補償トランジスタ  $T_{r4}$ 、スイッチングトランジスタ  $T_{r3}$ 、およびデータ線  $D$  という経路にて流れれる。

30

このデータ電流  $I_{data}$  に応じて、駆動トランジスタ  $T_{r1}$  のゲート電圧が定められて、該ゲート電圧に応じた電流  $I_{ds}$  が電源線  $V$  より供給されて被駆動素子  $L$  が発光とともに、該ゲート電圧は、容量素子  $C$  によって保持される。したがって、選択電位  $V_{sel}$  がローレベルになって、スイッチングトランジスタ  $T_{r2}$ 、 $T_{r3}$  がともにオフ状態になっても、保持されたゲート電圧に応じた電流  $I_{ds}$  が被駆動素子  $L$  に流れ続けるので、被駆動素子  $L$  の発光状態は、次回選択電位  $V_{sel}$  が再びハイレベルになるまで、維持されることとなる。

40

#### 【0031】

ところで、カレント・ミラー回路を構成している駆動トランジスタ  $T_{r1}$  と補償トランジスタ  $T_{r4}$  との利得係数は、上述したようにこれを一致させる場合に限られず、この単位回路が適用される表示パネルのサイズや走査周波数等の種々の要求に応じて適宜設定することができる。

例えば、補償トランジスタ  $T_{r4}$  の利得係数を、駆動トランジスタ  $T_{r1}$  の利得係数よりも大きくした構成としても良い。このような構成によれば、補償トランジスタ  $T_{r4}$  に流れる電流  $I_{data}$  が、駆動トランジスタ  $T_{r1}$  に流れる電流  $I_{ds}$  よりも大きくなるので、容量素子  $C$  において電荷蓄積に要する時間を短縮化することができる。このため、表示パネルの画素数の増大や大サイズ化に伴って要求される走査周波数の高周波数化に対処することが可能となる。

50

これとは逆に、補償トランジスタTr4の利得係数を、駆動トランジスタTr1の利得係数よりも小さくした構成としても良い。この構成によれば、補償トランジスタTr4によるデータ電流Idataが、駆動トランジスタTr1による電流Idsよりも小さくなるので、容量素子Cにおける電荷蓄積の際に消費される電力を抑えることができる。

### 【0032】

また、図2(a)または図2(b)において、同一行の画素回路20におけるスイッチングトランジスタTr2、Tr3のゲートは、互いに同一の走査線Sに接続された構成となっていた。この構成に限らず、走査線Sとは異なる走査線を設けて、すなわち、1行につき2本の走査線を設けて、スイッチングトランジスタTr2、Tr3のゲートが互いに異なる走査線Sに接続された構成としても良い。ここで、両構成を比較すると、前者に係る構成(1行の画素回路20につき1本の走査線を有する構成)の方が、後者に係る構成(1行の画素回路20につき2本の走査線を有する構成)と比較して、配線に要する領域が少なくて済むので、有効光学面積を確保することによる開口率の向上が容易となる。

### 【0033】

次に、上記画素回路20における製造プロセスについて、TFTおよび画素の製造プロセスについて説明する。

まず、ガラス基板1上に、SiH<sub>4</sub>を用いたPECVDや、Si<sub>2</sub>H<sub>6</sub>を用いたLPCVDにより、アモルファスシリコンを形成するとともに、該アモルファスシリコンを、エキシマレーザー等のレーザー照射や、固相成長によって多結晶化させて、多結晶シリコン層2を形成する(図4(a)参照)。

多結晶シリコン層2をパターニングして、ゲート絶縁膜3を形成した後、さらにゲート4を形成する(図4(b)参照)。

続いて、リンやボロンなどの不純物を、ゲート4をマスクとして用いて自己整合的に多結晶シリコン層2に打ち込み、トランジスタ5a、5bを形成する。なお、ここではトランジスタ5a、5bの導電型は、それぞれp型、n型である。第1層間絶縁膜6を形成した後、コンタクトホールを開孔し、さらに、ソースおよびドレイン7を形成する(図4(c)参照)。

そして、第2層間絶縁膜8を形成した後、コンタクトホールを開孔し、さらにITO(indium Tin Oxide)からなる画素電極9を形成する(図4(d)参照)。

### 【0034】

このように形成された第2層間絶縁膜8および画素電極9を覆うように、密着層10を形成し、発光領域に対応して開口部を形成する。さらに、層間層11を形成して、同じく発光領域に対応して開口部を形成する(図5(a)参照)。

つぎに、酸素プラズマやCF<sub>4</sub>プラズマなどのプラズマ処理によって、基板表面の濡れ性を制御する。その後、正孔注入層12および発光層13を、それぞれ液相プロセスや真空プロセスにより形成する。なお、液相プロセスには、スピンドルコートや、スキージ塗り、インクジェットプロセスなどが挙げられ、また、真空プロセスには、スパッタリングや、蒸着などが挙げられる。さらに、アルミニウムなどの金属を含んだ陰極14を形成する。最後に、封止層15を形成し、有機EL素子を完成させる(図5(b)参照)。

ここで、密着層10の役割は、基板と層間層11との密着性を向上し、また、正確な発光面積を得ることにある。また、層間層11の役割は、ゲート4やソース、ドレイン7から陰極14を遠ざけて寄生容量を低減すること、液相プロセスで正孔注入層12や発光層13を形成する際に、表面の濡れ性を制御して正確なパターニングができるようにすることにある。なお、発光層13の上に電子輸送層(図示しない)を設けてもよい。

### 【0035】

#### <第2実施形態>

上述した第1実施形態では、例えば、駆動トランジスタTr1と補償トランジスタTr4との利得係数が同じとなるように形成することによって、駆動トランジスタTr1のドレイン・ソース間ににおける電流Idsを、補償トランジスタTr4のドレイン・ソース間に流れるデータ電流Idataに一致させることができた。このため、駆動トランジスタTr4

10

20

30

40

50

$r_1$  に特性バラツキが発生しても、各画素にわたって被駆動素子 L に同じ大きさの電流  $I_{ds}$  を供給することができ、駆動トランジスタの特性バラツキに起因する輝度むらを抑えることが可能となった。

しかしながら、第 1 実施形態では、図 2 (a) または図 2 (b) から明らかなように、1 つの画素において計 4 個のトランジスタが必要である。このため、表示パネルとしてみた場合、トランジスタの数の分だけ、歩留まりの低下や、開口率の低下を招きやすい。

そこで、駆動トランジスタ  $T_{r1}$  の特性バラツキに起因する輝度むらを抑えた上で、1 つの画素において必要となるトランジスタの個数を減少させた第 2 実施形態について説明することにする。

#### 【0036】

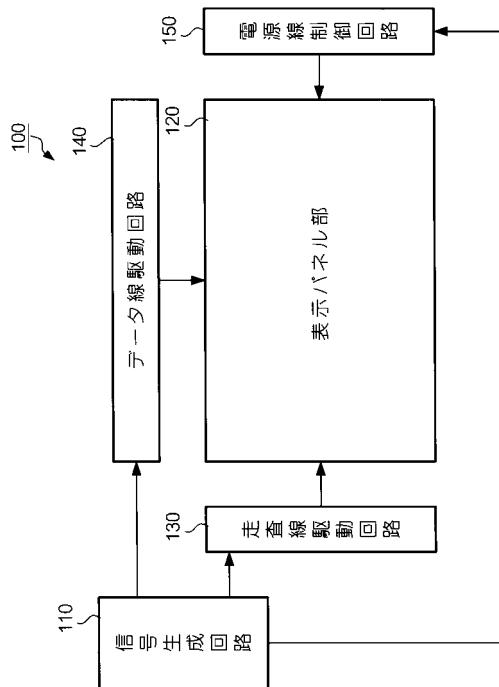

図 6 は、第 2 実施形態に係る単位回路が適用される有機 EL ディスプレイの構成を示すブロック図である。

この図に示されるように、有機 EL ディスプレイ 100 は、信号生成回路 110、表示パネル部 120、走査線駆動回路 130、データ線駆動回路 140 および電源線制御回路 150 を備えている。

有機 EL ディスプレイ 100 における信号生成回路 110、走査線駆動回路 130、データ線駆動回路 140 および電源線制御回路 150 は、それぞれが独立した電子部品によって構成されていてもよい。例えば、信号生成回路 110、走査線駆動回路 130、データ線駆動回路 140 および電源線制御回路 150 が、各々 1 チップの半導体集積回路装置によって構成されていてもよい。また、信号生成回路 110、走査線駆動回路 130、データ線駆動回路 140 および電源線制御回路 150 の全部若しくは一部がプログラマブルな I C チップで構成され、その機能が当該 I C チップに書き込まれたプログラムによってソフトウェア的に実現されてもよい。

#### 【0037】

信号生成回路 110 は、図示しない外部装置からの画像データに基づいて、表示パネル部 120 に画像を表示させるための走査制御信号およびデータ制御信号を作成する。そして、信号生成回路 110 は、前記走査制御信号を走査線駆動回路 130 に出力するとともに、前記データ制御信号をデータ線駆動回路 140 に出力する。さらに、信号生成回路 110 は、電源線制御回路 150 に対してタイミング制御信号を出力する。

#### 【0038】

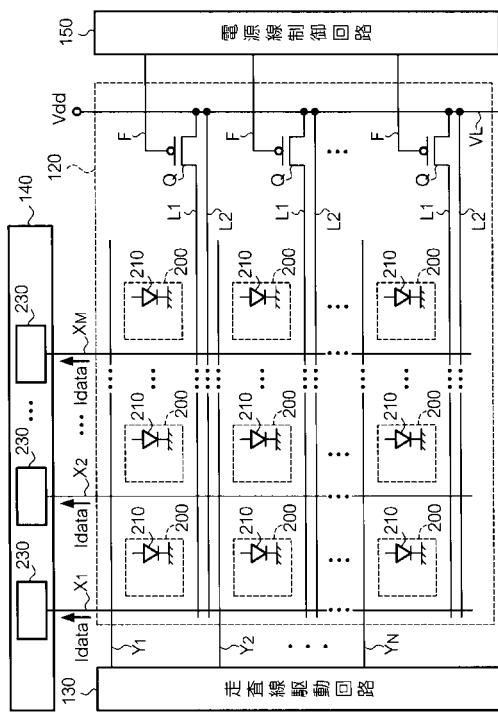

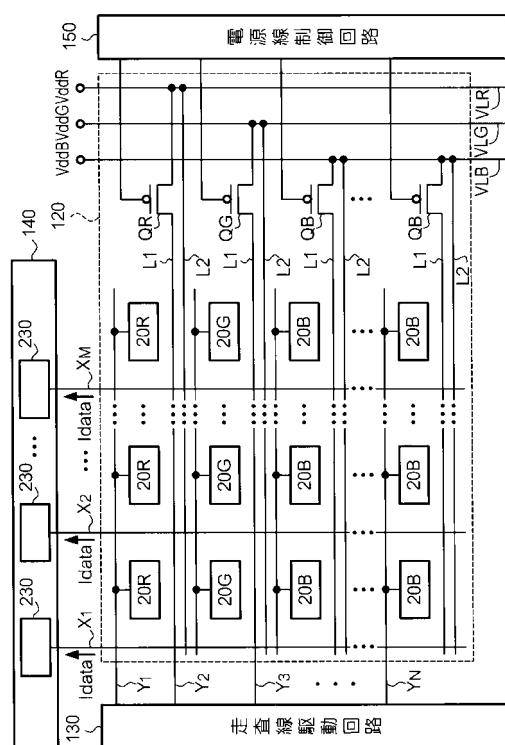

図 7 は、表示パネル部 120 およびデータ線駆動回路 140 の内部構成を示す図である。この図に示されるように、表示パネル部 120 は、列方向に沿って延びる M 本のデータ線  $X_m$  ( $m = 1 \sim M$ ;  $m$  は整数) と、行方向に沿って延びる N 本の走査線  $Y_n$  ( $n = 1 \sim N$ ;  $n$  は整数) との交差部に対応する位置に単位回路としての画素回路 200 をそれぞれ有している。つまり、各画素回路 200 は、列方向に沿って延びるデータ線  $X_m$  と、行方向に沿って延びる走査線  $Y_n$  とにそれぞれ接続されることによってマトリクス状に配列して、電子回路を構成している。

また、行毎に、それぞれ行方向（走査線の延設方向）に沿って第 1 の電源線  $L_1$  と第 2 の電源線  $L_2$  とが設けられている。

#### 【0039】

画素回路 200 は、第 1 実施形態の被駆動素子 L と同様な有機 EL 素子 210 を含む。1 行分の画素回路 200 は、当該行に対応する第 1 の電源線  $L_1$  および第 2 の電源線  $L_2$  に接続されている。すなわち、1 行分の画素回路 200 は、第 1 の電源線  $L_1$  および第 2 の電源線  $L_2$  を互いに共用している。

ここで、各行における第 1 の電源線  $L_1$  は、それぞれトランジスタ Q を介して間接的に電圧供給線  $V_L$  に接続されているが、各行における第 2 の電源線  $L_2$  は、それぞれ直接的に電圧供給線  $V_L$  に接続されて、画素回路 200 に、駆動電圧  $V_{dd}$  を供給する構成となっている。

走査線駆動回路 130 は、信号生成回路 110 から出力される走査制御信号に応じて、複数の走査線  $Y_n$  のうち順番に 1 本ずつ走査線を選択するとともに、選択した走査線に対し

10

20

30

40

50

、その選択を示す走査信号を供給する。

データ線駆動回路 140 は、データ線の 1 本毎にラインドライバ 230 を備え、1 つのラインドライバ 230 は、それに対応するデータ線の一端に接続されている。ここで、ラインドライバ 230 は、信号生成回路 110 から出力されたデータ制御信号に基づいて、データ電流 I data を生成し、対応するデータ線に供給する。

一般的に言えば、m 列目のラインドライバ 230 は、n 行目の走査線 Yn が選択されたときに、n 行 m 列に位置する画素回路 200 に含まれる有機 EL 素子 210 の輝度を指示するデータ電流 I data を m 列目のデータ線 Xm に供給する。

なお、画素回路 200 では、後述するように、対応するデータ線に供給されるデータ電流 I data に応じて内部状態が設定されると、該内部状態に応じて有機 EL 素子 210 に供給される駆動電流 Ids が制御される構成となっている。10

#### 【0040】

電源線制御回路 150 は、行毎に設けられる電源線制御線 F に電源線制御信号をそれぞれ供給して、各行のトランジスタ Q のオン・オフを制御する。詳細には、電源線制御回路 150 は、信号生成回路 110 から出力される走査制御信号に基づき、ある行の電源線制御信号について、当該行の走査線の選択を示す走査信号と完全に一致するように生成して、または、その選択状態が時間的に一部重複するように生成して、当該行に対応する電源線制御線 F に供給する。15

#### 【0041】

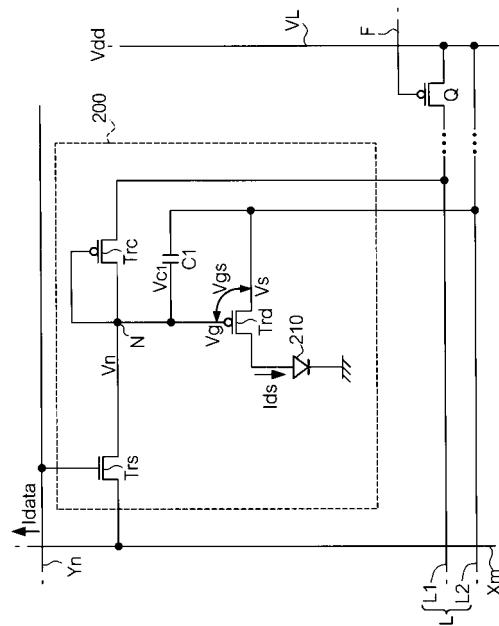

図 8 は、第 2 実施形態に係る単位回路としての画素回路 200 の詳細な構成を示す回路図である。この図においては、各画素回路 200 のうち、n 行目の走査線 Yn と m 列目のデータ線 Xm との交差に対応するものが例示されている。20

図 8 に示されるように、画素回路 200 は、3 つのトランジスタと 1 つの容量素子とを含んでいる。詳細には、画素回路 200 は、駆動トランジスタ Trd、補償トランジスタ Trc、スイッチングトランジスタ Trs および容量素子としての保持用キャパシタ C1 を含んでいる。

なお、本実施形態では、駆動トランジスタ Trd および補償トランジスタ Trc の導電型は、それぞれ、p 型 (p チャネル) であり、スイッチングトランジスタ Trs の導電型は、n 型 (n チャネル) であるが、これらの導電型の選択については、ここで示したものに限られない。また、画素回路 200 に含まれるトランジスタは、通常、TFT (薄膜トランジスタ) で形成される。30

#### 【0042】

駆動トランジスタ Trd のドレイン (第 1 の端子) は、有機 EL 素子 210 の陽極に接続されている。有機 EL 素子 210 の陰極は接地されている。駆動トランジスタ Trd のソース (第 2 の端子) は、第 2 の電源線 L2 に接続されている。第 2 の電源線 L2 は、表示パネル部 120 の右端側に設けられた電圧供給線 VL に接続されている。駆動トランジスタ Trd のゲート (第 1 のゲート) は、ノード N に接続されている。なお、ノード N とは、駆動トランジスタ Trd のゲートと、保持用キャパシタ C1 の一端と、スイッチングトランジスタ Trs のドレインと、補償トランジスタ Trc のドレインとの接続点である。保持用キャパシタ C1 の他端は、駆動トランジスタ Trd のソース、すなわち、第 2 の電源線 L2 に接続されている。40

#### 【0043】

スイッチングトランジスタ Trs のドレイン (第 6 の端子) は、データ線 Xm と接続され、そのドレイン (第 5 の端子) は、ノード N に接続されている。また、スイッチングトランジスタ Trs のゲートは、走査線 Yn に接続されている。したがって、走査線 Yn に、当該走査線 Yn が選択されたことを示す走査信号が供給されると (ハイレベルになると)、スイッチングトランジスタ Trs は導通状態となる。

#### 【0044】

ノード N には、補償トランジスタ Trc のドレイン (第 3 の端子) のみならず、そのゲートも接続されている。また、補償トランジスタ Trc のソース (第 4 の端子) は、第 1 の50

電源線 L 1 に接続されている。したがって、補償トランジスタ T r c は、第 1 の電源線 L 1 からノード N までを順方向とするダイオードとして機能する。

なお、各画素回路 200 内に配置形成されるトランジスタは、通常、 TFT ( 薄膜トランジスタ ) で構成されている。

#### 【 0 0 4 5 】

第 1 の電源線 L 1 は、制御回路としてのトランジスタ Q を介して電圧供給線 V L に接続されている。なお、第 1 の電源線 L 1 と第 2 の電源線 L 2 とで電源線 L が構成されている。トランジスタ Q のゲートは、電源線制御線 F に接続されている。トランジスタ Q は、電源線制御回路 150 から電源線制御線 F を介して供給される電源線制御信号に応じて、電気的切断の状態 ( オフ状態 ) または電気的接続の状態 ( オン状態 ) のいずれかとなる。トランジスタ Q の導電型は p 型 ( p チャネル ) であるので、電源線制御信号がローレベルとなったときに、トランジスタ Q がオン状態となる。

#### 【 0 0 4 6 】

次に、有機 EL ディスプレイ 100 における画素回路 200 の駆動方法について図 9 を参照して説明する。図 9 は、この駆動方法を説明するためのタイミングチャートである。

まず、データ書き込み期間 T r p において、走査線 Y n の選択を示す走査信号が走査線駆動回路 130 によって供給されると ( 走査線 Y n がハイレベルになると ) 、スイッチングトランジスタ T r s がオン状態となる。このような走査信号の供給に合わせて、トランジスタ Q をオン状態にするローレベルの電源線制御信号が電源線制御線 F に供給されるので、データ書き込み期間 T r p では、トランジスタ Q もオン状態となる。

したがって、電流が、電圧供給線 V L 、トランジスタ Q 、第 1 の電源線 L 1 、補償トランジスタ T r c 、スイッチングトランジスタ T r s およびデータ線 X m という経路で流れる。このときに流れる電流は、ラインドライバ 230 によって生成されるデータ電流 I d a t a 、すなわち、n 行 m 列の画素回路 200 に含まれる有機 EL 素子 210 の輝度を指示するデータ電流 I d a t a である。

そして、このときに流れるデータ電流 I d a t a に応じた電圧 V C 1 がノード N に発生して、保持用キャパシタ C 1 に保持されるとともに、駆動トランジスタ T r d のゲートに印加される。このため、駆動用トランジスタ T r d に駆動電流 I d s が流れ、有機 EL 素子 210 が発光し始める。

#### 【 0 0 4 7 】

次に、データ書き込み期間 T r p が終了して、発光期間 T e 1 に至ると、走査線 Y n がローレベルになる。このため、スイッチングトランジスタ T r s がオフ状態となる。このような走査信号が状態遷移に合わせて、電源線制御信号がハイレベルに変化するので、トランジスタ Q もオフ状態となる。スイッチングトランジスタ T r s およびトランジスタ Q とともにオフ状態となっても、駆動トランジスタ T r d のゲートには、保持用キャパシタ C 1 によって保持された電圧 V C 1 が印加されるので、有機 EL 素子 210 の発光状態は、次回、走査線 Y n が再び選択されるまで ( トランジスタ Q が再びオンになるまで ) 、維持されることになる。

#### 【 0 0 4 8 】

なお、このような動作は、走査線 Y n に対応する 1 行分の画素回路 200 の各々においても、それぞれ同時に実行される。また、画素回路 200 の全体についてみると、1、2、3、...、N 行目の走査線について順番に実行される。

また、データ書き込み期間 T r p と発光期間 T e 1 とで、駆動周期 T c が構成される。この駆動周期 T c とは、有機 EL 素子 210 の輝度が 1 回ずつ更新される周期を意味しており、いわゆるフレーム期間 ( 垂直走査期間 ) と同義である。

#### 【 0 0 4 9 】

上記の画素回路の動作機構を簡単に説明するために、補償用トランジスタ T r c の閾値電圧 V t h 2 を考慮して表すとすれば、前記ノード N での電位 V n は、保持用キャパシタ C 1 に生じた電圧 V C 1 と、駆動電圧 V d d から補償用トランジスタ T r c の閾値電圧 V t h 2 を差し引いた値 ( V n = V d d - V t h 2 ) とを加算した値で表現される。すなわち

10

20

30

40

50

、次式(1)で表される。

$$V_g = V_{C1} + V_{dd} - V_{th2} \dots (1)$$

【0050】

駆動トランジスタTrdのゲート・ソース間電圧Vgsは、そのゲート電位Vgと駆動用トランジスタTrdのソース電位Vs(=Vdd)との差(Vg-Vs)であるので、駆動トランジスタのゲート・ソース間電圧Vgsは、次式(2)のように変形できる。

$$V_{gs} = V_g - V_s \dots (2)$$

【0051】

この式(2)に、式(1)で示されるVgおよびVs(=Vdd)を代入すると、次式(3)が得られる。

$$\begin{aligned} V_{gs} &= V_{C1} + V_{dd} - V_{th2} - V_{dd} \\ &= V_{C1} - V_{th2} \dots (3) \end{aligned}$$

【0052】

ここで、上述したように補償トランジスタTrcの閾値電圧Vth2を駆動トランジスタTrdの閾値電圧Vth1とほぼ等しいとすれば、式(3)で示されるゲート・ソース間電圧Vgsは、次式(4)のように表すことができる。

$$V_{gs} = V_{C1} - V_{th1} \dots (4)$$

【0053】

一方、駆動トランジスタTrdのソース・ドレイン間に流れる電流Idsは、次式(5)で表される。

$$I_{ds} = (1/2) (-V_{gs} - V_{th1})^2 \dots (5)$$

【0054】

この式における $\beta$ は、利得係数であり、

$$= (\mu A W / L)$$

で示される。ここで、 $\mu$ はキャリアの移動度、Aはゲート容量、Wはチャネル幅、Lはチャネル長を、それぞれ示している。

式(5)に、式(4)で示されるVgsを代入すると、

$$\begin{aligned} I_{ds} &= (1/2) \beta (-V_{C1} + V_{th1} - V_{th1})^2 \\ &= (1/2) \beta (-V_{C1})^2 \dots (6) \end{aligned}$$

【0055】

この式(6)を見ても判るように、駆動トランジスタTrdのソース・ドレイン間に流れる電流Idsは、保持用キャパシタC1に生じた電圧Vc1のみで決定される。

【0056】

一般に、互いに近接するトランジスタの閾値特性等を揃えることは容易である。このため、同一画素回路のような、極めて近接する補償トランジスタTrcと駆動トランジスタTrdの閾値電圧特性を揃えることも容易であるので、有機EL素子210に流れる駆動電流Idsを、駆動トランジスタTrdの閾値電圧特性に依存することなく、データ電流Idataで決定することができる。

すなわち、第2実施形態においても、補償トランジスタTrcのドレインは駆動トランジスタTrdのゲートに直接接続されているので、近接する結果、両トランジスタの特性を揃えることが容易であるとともに、補償トランジスタTrcを通過するデータ電流Idataが、駆動トランジスタTrdによって制御される電流Idsに直接反映されて、両者の一致性を高めることができる。

【0057】

したがって、表示パネル部120において画素回路200毎に、駆動トランジスタTrdの閾値電圧がバラツキによって相違しても、有機EL素子210に流れる電流Idsに影響を与えないで、駆動トランジスタの特性バラツキに起因する輝度むらを抑えることが、上記第1実施形態と同様に可能となる。

## 【0058】

さらに、第2実施形態では、1つの画素回路200に形成されるトランジスタは3個であり、第1実施形態の画素回路20の4個と比較して、1個少なくすることができる。このため、第2実施形態によれば、駆動トランジスタの特性バラツキに起因する輝度むらを抑えることができる点にくわえて、トランジスタの不良による歩留まり低下を抑えることができるとともに、1画素当たりの開口面積を確保して開口率を向上させることができるとなる。

## 【0059】

なお、第2実施形態においても、第1実施形態と同様に適宜設定して良い。例えば、補償トランジスタTrcの利得係数を、駆動トランジスタTrdの利得係数よりも大きくした構成としても良い。このような構成によれば、補償トランジスタTrcに流れる電流Idataが、駆動トランジスタTrdに流れる電流Idsよりも大きくなるので、容量素子Cにおいて電荷蓄積に要する時間を短縮化することができる。このため、表示パネルの画素数の増大や大サイズ化に伴って要求される走査周波数の高周波数化に対処することができる。

これとは逆に、補償トランジスタTrcの利得係数を、駆動トランジスタTrdの利得係数よりも小さくした構成としても良い。この構成によれば、補償トランジスタTrcによるデータ電流Idataが、駆動トランジスタTrdによる電流Idsよりも小さくなるので、容量素子Cにおける電荷蓄積の際に消費される電力を抑えることができる。

## 【0060】

第2実施形態では、スイッチング用トランジスタTrsおよびトランジスタQは、データ書き込み期間Trpにおいてともにオン状態となり、発光期間Te1においてともにオフ状態となるように設定されていることが好ましいが、特にこれには限定されない。また、駆動電流Idsは、有機EL素子210にデータ書き込み期間Trpに流れず、発光期間Te1に流れるように設定されていることが好ましいが、特にこれには限定されない。

駆動トランジスタTrdに対して補償トランジスタTrcのチャネル幅等を大きくすることにより、駆動トランジスタTrdと補償トランジスタTrcのサイズが同一である場合に比べて、低階調のデータを供給する際もデータ電流Idataとして相対的に高い電流を利用できるので、寄生容量等による動作遅延を抑制することができる。

また、画素回路200において、駆動トランジスタTrdの閾値電圧Vth1が補償トランジスタTrcの閾値電圧Vth2以上となるように設定されることが好ましいが、特にこれには限定されない。例えば、有機EL素子210をデータ書き込み期間Trpにおいても発光させるときは、駆動トランジスタTrdの閾値電圧Vth1を補償用トランジスタTrcの閾値電圧Vth2より低くなるように設定してもよい。

くわえて、電源線制御信号が供給される期間と走査信号が供給される期間とは完全、あるいは、一部時間的に重なるように設定される。つまり、トランジスタQはデータ書き込み期間Trpとほぼ同じ期間でオン状態となるように設定されている。しかし、トランジスタQをオンさせる電源線制御信号を、走査線の選択を示す走査信号よりも先に供給することにより、データ電流Idataによって設定された駆動用トランジスタTrdのゲートの電圧が駆動電圧Vddにより変化するのを抑制することができるので、望ましい場合がある。

## 【0061】

また、図7において、電圧供給線VLを表示パネル部120の右端側に設けたが、これに限定されることではなく、例えば、表示パネル部120の左端側に設けてもよいし、また、トランジスタQおよび電圧供給線VLを、電源線制御回路150とは別体として構成したが、電源線制御回路150の内部に設けるようにしてもよい。

さらに、制御回路としてトランジスタQを用いたが、トランジスタQに替えて、低電位と高電位との間で切換える可能なスイッチを設けてもよい。駆動用トランジスタTrdの駆動能力を向上させるためにバッファ回路やソースフォロワ回路を含むボルテージフォロワ回路などを用いて、第2の電源線L2や電圧供給線VLのインピーダンスを十分に低くして

10

20

30

40

50

も良い。

**【0062】**

<第2実施形態の応用>

図7に示した表示パネルでは、説明を簡略化のために単色で階調表示する例を挙げて説明したが、実際の表示パネルとしての機能を考えた場合には、カラー表示することが要求される場合がある。そこで、カラー表示のための電気光学装置を、第2実施形態の応用例として説明する。

**【0063】**

図10は、この応用例に係る電気光学装置の構成を示すブロック図である。なお、図10における電気光学装置は、電気光学素子として有機EL素子を用いた有機ELディスプレイであり、図7と同じ構成部材については同一の符号を付与して、その詳細な説明を省略する。

図10において、表示パネル部120は、赤色の光を放射する有機EL素子210を有した赤用画素回路200Rと、緑色の光を放射する有機EL素子210を有した緑用画素回路200Gと、青色の光を放射する有機EL素子210を有した青用画素回路200Bとで構成される。

**【0064】**

ここで、表示パネル部120において、1行目には赤用画素回路200Rが配列し、2行目には緑用画素回路200Gが配列し、3行目には青用画素回路200Bが配列し、4行目には赤用画素回路200Rが配列し、以降、この配列が繰り返されている。すなわち、同色の画素回路は、走査線の延設方向に沿って1行分配列するとともに、1行分の同色画素回路が、走査線、第1の電源線L1および第2の電源線L2を兼用している。

なお、各色の画素回路200R、200G、200Bの回路構成は、それぞれ、図8に示した画素回路200の回路構成と等しい。

**【0065】**

この応用例において電圧供給線は、色毎に専用の駆動電圧を供給するために3本設けられている。すなわち、電圧供給線VLRは、赤用画素回路200Rの駆動電圧VddRを供給し、電圧供給線VLGは、緑用画素回路200Gの駆動電圧VddGを供給し、電圧供給線VLBは、青用画素回路200Bの駆動電圧VddBを供給する。

また、第1の電源線L1および第2の電源線L2が、それぞれ行方向に沿って、行毎に設けられている。ここで、同一行に位置する赤用画素回路200Rに対応する第1の電源線L1は、トランジスタQRを介して電圧供給線VLRとは間接的に接続されて、当該トランジスタQRがオンしたときに駆動電圧VddRを供給する一方、第2の電源線L2は、電圧供給線VLRとは直接的に接続されて、駆動電圧VddRを常時供給する。

同一行に位置する緑用画素回路200G、青用画素回路200Bについてもそれぞれ同様である。すなわち、同一行に位置する緑用画素回路200Gについての第1の電源線L1は、トランジスタQGがオンしたときに駆動電圧VddGを供給する一方、第2の電源線L2は、駆動電圧VddGを常時供給し、また、同一行に位置する青用画素回路200Gについての第1の電源線L1は、トランジスタQBがオンしたときに駆動電圧VddBを供給する一方、第2の電源線L2は、駆動電圧VddBを常時供給する。

**【0066】**

次に、応用例に係る電気光学装置において、画素回路200R、200G、200Bの駆動方法について説明する。

まず、1行目の走査線Y1が選択されて、その旨を示す走査信号が供給されると（走査線Y1がハイレベルになると）、1行目に位置する赤用画素回路200Rの各々においてスイッチングトランジスタTrsがオン状態となる。このような走査信号が供給に合わせて、1行目の電源線制御信号がローレベルになるので、1行目のトランジスタQRもオン状態となる。

さらに、該走査信号の供給に合わせて、1行目の画素回路200Rに含まれる有機EL素子210の輝度を指示するデータ電流Idataが、各列のデータ線にそれぞれ供給され

10

20

30

40

50

る。

このため、1行目の画素回路200Rの各々においては、データ電流I<sub>data</sub>に応じた電荷が保持用キャパシタC1に蓄積されることによって駆動トランジスタTrdのゲート電圧が保持される。したがって、駆動トランジスタTrdは、当該ゲート電圧に応じた駆動電流I<sub>ds</sub>を赤用の有機EL素子210に供給し始め、これにより、赤用の有機EL素子210の発光が開始する。

#### 【0067】

続いて、2行目の走査線Y2が選択されて、その旨を示す走査信号が供給されると（走査線Y2がハイレベルになると）、2行目に位置する緑用画素回路200Gの各々においてスイッチングトランジスタTrsがオン状態となる。このような走査信号が供給に合わせて、2行目の電源線制御信号がローレベルになるので、2行目のトランジスタQGもオン状態となる。

該走査信号の供給に合わせて、2行目の画素回路200Gに含まれる有機EL素子210の輝度を指示するデータ電流I<sub>data</sub>が、各列のデータ線にそれぞれ供給される。

このため、2行目の画素回路200Gの各々においては、データ電流I<sub>data</sub>に応じた電荷が保持用キャパシタC1に蓄積されることによって駆動トランジスタTrdのゲート電圧が保持される。したがって、駆動トランジスタTrdは、当該ゲート電圧に応じた駆動電流I<sub>ds</sub>を緑用の有機EL素子210に供給し始め、これにより、緑用の有機EL素子210の発光が開始する。

なお、2行目の走査線Y2が選択されると、1行目の画素回路200Rの各々において、スイッチングトランジスタTrsおよびトランジスタQRがともにオフ状態となるが、その駆動トランジスタTrdは、保持用キャパシタC1によって保持されたゲート電圧に応じた駆動電流I<sub>ds</sub>を赤用の有機EL素子210に供給するので、赤用の有機EL素子210の発光状態は維持される。

#### 【0068】

次に、3行目の走査線Y3が選択されて、その旨を示す走査信号が供給されると（走査線Y3がハイレベルになると）、3行目に位置する青用画素回路200Bの各々においてスイッチングトランジスタTrsがオン状態となる。このような走査信号が供給に合わせて、3行目の電源線制御信号がローレベルになるので、3行目のトランジスタQBもオン状態となる。

該走査信号の供給に合わせて、3行目の画素回路200Bに含まれる有機EL素子210の輝度を指示するデータ電流I<sub>data</sub>が、各列のデータ線にそれぞれ供給される。

このため、3行目の画素回路200Gの各々においては、データ電流I<sub>data</sub>に応じた電荷が保持用キャパシタC1に蓄積されることによって駆動トランジスタTrdのゲート電圧が保持される。したがって、駆動トランジスタTrdは、当該ゲート電圧に応じた駆動電流I<sub>ds</sub>を青用の有機EL素子210に供給し始め、これにより、青用の有機EL素子210の発光が開始する。

なお、3行目の走査線Y3が選択されると、2行目の画素回路200Rの各々において、スイッチングトランジスタTrsおよびトランジスタQRがともにオフ状態となるが、その駆動トランジスタTrdは、保持用キャパシタC1によって保持されたゲート電圧に応じた駆動電流I<sub>ds</sub>を緑用の有機EL素子210に供給するので、緑用の有機EL素子210の発光状態は維持される。

以降同様な動作が、4、5、6、…、N行目まで順番に繰り返されると、再び1行目の走査線Y1が選択されて、データ（保持用キャパシタC1に蓄積されたデータ電流I<sub>data</sub>に応じた電荷）が書き換えられることになる。

#### 【0069】

このように応用例に係る有機ELディスプレイ100においても、第2実施形態と同様な効果を得ることができる。

一般に、赤、緑、青の有機EL素子210の発光効率は、互いに異なるので、駆動電圧についても、色毎に最適な値を設定する必要となる場合がある。応用例では、同一行に同一

10

20

30

40

50

色の画素回路を配列させるとともに、第1の電源線L1および第2の電源線L2を共用させて、色毎に駆動電圧を供給する構成となっているので、色毎に最適な駆動電圧を設定することが容易である。また、有機EL素子210が長期間の発光により経時劣化等して、色毎に、駆動電圧を再設定する必要が生じる場合もあるが、応用例では、そのような色毎に駆動電圧の再設定も容易となる。

#### 【0070】

なお、上述した第1、第2実施形態や、その応用例では、単位回路（電子回路）として画素回路を例示したが、RAM等（特にMRAM）の記憶装置に適用しても良い。また、被駆動素子として有機EL素子を例に挙げたが、無機EL素子でも良いしLEDやFEDでも良い。更には光検出素子等のセンサー素子であっても良い。

10

#### 【0071】

##### <電子機器>

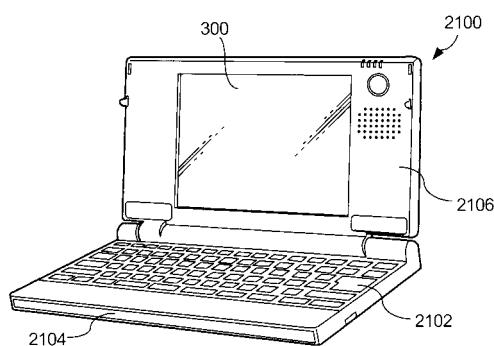

つぎに、第1、第2実施形態やその応用例に係る単位回路を含む電気光学装置を適用した電子機器のいくつかの事例について説明する。

図11は、この電気光学装置を適用したモバイル型のパーソナルコンピュータの構成を示す斜視図である。この図に示されるように、実施形態に係る単位回路を含む電気光学装置300は、パーソナルコンピュータ2100の表示ユニットとしても用いられている。なお、パーソナルコンピュータ2100の本体2104には、キーボード2102が備えられる。

#### 【0072】

図12は、上記電気光学装置300を適用した携帯電話機の構成を示す斜視図である。この図において、携帯電話機2200は、複数の操作ボタン2202のほか、受話口2204、送話口2206とともに、前述の電気光学装置300を備えている。

20

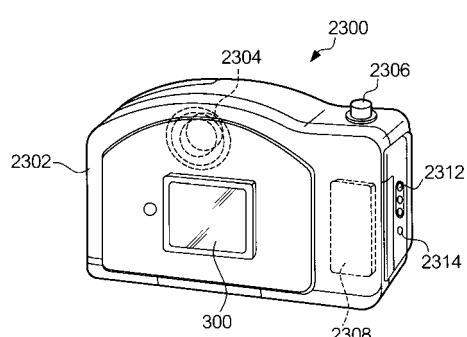

#### 【0073】

図13は、前述の電気光学装置300をファインダに適用したデジタルスチルカメラの構成を示す斜視図である。銀塩カメラは、被写体の光像によってフィルムを感光させるのに対し、デジタルスチルカメラ2300は、被写体の光像をCCD（Charge Coupled Device）などの撮像素子により光電変換して撮像信号を生成・記憶するものである。ここで、デジタルスチルカメラ2300における本体2302の背面には、上述した電気光学装置300が設けられている。この電気光学装置300は、撮像信号に基づいて表示を行うので、被写体を表示するファインダとして機能することになる。また、本体2302の前面側（図13においては裏面側）には、光学レンズやCCDなどを含んだ受光ユニット2304が設けられている。

30

#### 【0074】

撮影者が電気光学装置300に表示された被写体像を確認して、シャッタボタン2306を押下すると、その時点におけるCCDの撮像信号が、回路基板2308のメモリに転送・記憶される。

40

また、このデジタルスチルカメラ2300にあって、ケース2302の側面には、外部表示を行うためのビデオ信号出力端子2312と、データ通信用の入出力端子2314とが設けられている。

#### 【0075】

なお、上記電気光学装置が適用される電子機器としては、図11に示されるパーソナルコンピュータや、図12に示される携帯電話機、図13に示されるデジタルスチルカメラの他にも、液晶テレビや、ビューファインダ型、モニタ直視型のビデオテープレコーダ、カーナビゲーション装置、ページャ、電子手帳、電卓、ワードプロセッサ、ワークステーション、テレビ電話、POS端末、タッチパネルを備えた機器等などが挙げられる。そして、これらの各種電子機器の表示部として、実施形態に係る電気光学装置が適用可能であることは言うまでもない。

#### 【0076】

##### 【発明の効果】

50

以上説明したように本発明によれば、駆動トランジスタのバラツキの影響を受けにくくして、有機EL素子などのような電流型の被駆動素子に、目的とする電流を供給することが可能となる。

【図面の簡単な説明】

【図1】本発明の第1実施例に係る単位回路を適用した電気光学装置の構成を示すプロック図である。

【図2】(a)、(b)は、それぞれ単位回路としての画素回路の構成を示す図である。

【図3】同画素回路の駆動方法を説明するためのタイミングチャートである。

【図4】(a)～(c)は、それぞれ同電気光学装置の製造プロセスの一部を示す図である。

10

【図5】(a)および(b)は、それぞれ同電気光学装置の製造プロセスの一部を示す図である。

【図6】本発明の第2実施例に係る単位回路を適用した電気光学装置の構成を示すプロック図である。

【図7】同電気光学装置における表示パネル等の構成を示す図である。

【図8】同単位回路としての画素回路の構成を示す図である。

【図9】同画素回路の駆動方法を説明するためのタイミングチャートである。

【図10】第2実施形態の応用例に係る電気光学装置のうち、表示パネル等の構成を示す図である。

【図11】実施形態に係る単位回路を含む電気光学装置を適用したモバイル型のパソコン

20 ルコンピュータの構成を示す斜視図である。

【図12】同電気光学装置を適用した携帯電話機の構成を示す斜視図である。

【図13】同電気光学装置を適用したデジタルスチルカメラの構成を示す斜視図である。

。 【図14】電流型の被駆動素子を駆動する従来の単位回路の一例を示す図である。

【符号の説明】

C … キャパシタ

L … 被駆動素子

Tr 1 … 駆動トランジスタ

Tr 2 … スイッチングトランジスタ(第2のスイッチングトランジスタ)

30

Tr 3 … スイッチングトランジスタ(第1のスイッチングトランジスタ)

Tr 4 … 補償トランジスタ

V … 電源線

D … データ線

S … 走査線

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 13】

【図 12】

【図 14】

## フロントページの続き

(51) Int.Cl.<sup>7</sup> F I テーマコード(参考)

H 05 B 33/14 G 09 G 3/20 641D

G 09 G 3/20 642A

H 05 B 33/14 A

H 01 L 29/78 614

H 03 K 17/687 B

F ターム(参考) 5C080 AA06 BB05 DD05 DD28 EE28 FF11 JJ02 JJ03 JJ04 JJ06

5C094 AA04 AA07 AA08 AA10 AA43 AA44 BA03 BA12 BA27 CA19

CA24 CA25 DA13 DB01 DB04 EA04 FB01 FB12 FB14 FB15

FB20

5F110 AA07 AA30 BB02 BB05 CC02 DD02 GG02 GG13 GG45 GG47

NN03 NN71 NN72 PP01 PP03 QQ11

5J055 AX48 BX09 BX16 CX29 DX13 EY12 EY21 EZ04 GX01 GX04

GX07 GX08 GX09