(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2016-525301

(P2016-525301A)

(43) 公表日 平成28年8月22日(2016.8.22)

(51) Int.Cl.

H03K 23/40 (2006.01)

H03K 5/12 (2006.01)

F 1

H03K 23/40

H03K 5/12

テーマコード (参考)

審査請求 未請求 予備審査請求 未請求 (全 25 頁)

(21) 出願番号 特願2016-521539 (P2016-521539)

(86) (22) 出願日 平成26年6月18日 (2014.6.18)

(85) 翻訳文提出日 平成28年2月22日 (2016.2.22)

(86) 國際出願番号 PCT/US2014/042920

(87) 國際公開番号 WO2014/209715

(87) 國際公開日 平成26年12月31日 (2014.12.31)

(31) 優先権主張番号 13/926,631

(32) 優先日 平成25年6月25日 (2013.6.25)

(33) 優先権主張国 米国(US)

(71) 出願人 595020643

クアアルコム・インコーポレイテッド

Q U A L C O M M I N C O R P O R A T

E D

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】フィードバックループ内にデューティサイクル調整を有する分周器

## (57) 【要約】

フィードバックループ内にデューティサイクル調整を有する分周器(300)が開示される。例示的な設計では、装置は、フィードバックループ中で結合された少なくとも1つの分周回路(310a、310b)及び少なくとも1つのデューティサイクル調整回路(320a、320b)を含む。分周回路(1つ又は複数)は、第1の周波数のクロック信号(入力クロック)を受け、第1の周波数のフラクションである第2の周波数の少なくとも1つの分周信号(Idivp、Idivn)を供給する。デューティサイクル調整回路(1つ又は複数)は、少なくとも1つの分周信号のデューティサイクルを調整し、少なくとも1つのデューティサイクル調整信号(Iadip、Iadin)を分周回路(1つ又は複数)に供給する。分周回路(1つ又は複数)は、第1及び第2のラッチ(310a、310b)を含み得、デューティサイクル調整回路(1つ又は複数)は、第1及び第2のデューティサイクル調整回路(320a、320b)を含み得る。第1及び第2のラッチ並びに第1及び第2のデューティサイクル調整回路は、フィードバックループ中

FIG. 3

**【特許請求の範囲】****【請求項 1】**

装置であつて、

フィードバックループ中で結合されており、第1の周波数のクロック信号を受け、第2の周波数の少なくとも1つの分周信号を供給するように構成された少なくとも1つの分周回路(610a、610k)、ここで、前記第2の周波数は、前記第1の周波数の分数である、と、

前記フィードバックループ内で前記少なくとも1つの分周回路に結合されており、前記少なくとも1つの分周信号のデューティサイクルを調整し、少なくとも1つのデューティサイクル調整信号を前記少なくとも1つの分周回路に供給するように構成された少なくとも1つのデューティサイクル調整回路(620a、620k)と

を備える装置。

**【請求項 2】**

前記少なくとも1つの分周回路は、

前記クロック信号を受け、第1の分周信号を供給するように構成された第1のラッチ(310a)と、

前記クロック信号を受け、第2の分周信号を供給するように構成された第2のラッチ(310b)と

を備える、請求項1に記載の装置。

**【請求項 3】**

前記少なくとも1つのデューティサイクル調整回路は、

前記第1のラッチから前記第1の分周信号を受け、第1のデューティサイクル調整信号を前記第2のラッチに供給するように構成された第1のデューティサイクル調整回路(320a)と、

前記第2のラッチから前記第2の分周信号を受け、第2のデューティサイクル調整信号を前記第1のラッチに供給するように構成された第2のデューティサイクル調整回路(320b)と

を備える、請求項2に記載の装置。

**【請求項 4】**

前記第1のデューティサイクル調整回路は、

調整可能なバイアス電流を受け、前記調整可能なバイアス電流に基づいて決定された調整可能なデューティサイクルを有する前記第1のデューティサイクル調整信号を供給するように構成されたインバータ(434)

を備える、請求項3に記載の装置。

**【請求項 5】**

前記第1のデューティサイクル調整回路は、

デューティサイクル制御信号を受け、前記インバータに前記調整可能なバイアス電流を供給するように構成されたデューティサイクルコントローラ(436)

を更に備える、請求項4に記載の装置。

**【請求項 6】**

前記デューティサイクルコントローラは、

前記デューティサイクル制御信号を受け、少なくとも1つの制御信号を供給するように構成されたルックアップテーブル(532)と、

前記少なくとも1つの制御信号を受け、前記インバータに前記調整可能なバイアス電流を供給するように構成されたバイアス電流生成器(534)と

を備える、請求項5に記載の装置。

**【請求項 7】**

前記第1のラッチは、更に、前記第2のデューティサイクル調整信号を受け、前記第1の分周信号を供給するように構成される、請求項3に記載の装置。

**【請求項 8】**

10

20

30

40

50

前記第1のラッチは、更に、前記第2のラッチから前記第2の分周信号を受け、前記第1の分周信号を供給するように構成される、請求項7に記載の装置。

【請求項9】

前記第1のラッチ及び前記第2のラッチ並びに前記第1のデューティサイクル調整回路及び前記第2のデューティサイクル調整回路は、2分周を行うように構成され、前記第2の周波数は、前記第1の周波数の2分の1である、請求項3に記載の装置。

【請求項10】

前記第1の分周信号は、同相の分周信号を備え、前記第2の分周信号は、直交の分周信号を備える、請求項3に記載の装置。

【請求項11】

分周信号を生成する方法であって、

フィードバックループ中で結合された少なくとも1つの分周回路で少なくとも1つの分周信号を生成すること(712)、ここで、前記少なくとも1つの分周回路は、第1の周波数のクロック信号を受け、第2の周波数の前記少なくとも1つの分周信号を供給し、前記第2の周波数は、前記第1の周波数の分数である、と、

前記フィードバックループ内で前記少なくとも1つの分周回路に結合された少なくとも1つのデューティサイクル調整回路で前記少なくとも1つの分周信号のデューティサイクルを調整することによって、少なくとも1つのデューティサイクル調整信号を生成すること(714)と

を備える方法。

10

【請求項12】

前記少なくとも1つの分周回路は、第1のラッチ及び第2のラッチを備え、前記少なくとも1つの分周信号を前記生成することは、

前記第1のラッチで第1の分周信号を生成することと、

前記第2のラッチで第2の分周信号を生成することと

を備える、請求項11に記載の方法。

20

【請求項13】

前記少なくとも1つのデューティサイクル調整回路は、第1のデューティサイクル調整回路及び第2のデューティサイクル調整回路を備え、前記少なくとも1つのデューティサイクル調整信号を前記生成することは、

前記第1のデューティサイクル調整回路で第1のデューティサイクル調整信号を生成することと、

前記第2のデューティサイクル調整回路で第2のデューティサイクル調整信号を生成することと

を備える、請求項12に記載の方法。

30

【請求項14】

前記第1のデューティサイクル調整回路は、インバータを備え、前記第1のデューティサイクル調整信号を前記生成することは、

前記インバータの調整可能なバイアス電流に基づいて決定された調整可能なデューティサイクルを有する前記第1のデューティサイクル調整信号を生成すること

を備える、請求項13に記載の方法。

40

【請求項15】

デューティサイクル制御信号に基づいて前記インバータのための前記調整可能なバイアス電流を生成すること

を更に備える、請求項14に記載の方法。

【請求項16】

デューティサイクル制御信号に基づいて少なくとも1つの制御信号を生成することと、

前記少なくとも1つの制御信号に基づいて前記インバータのための前記調整可能なバイアス電流を生成すること

を更に備える、請求項14に記載の方法。

50

## 【請求項 17】

装置であつて、

第1の周波数のクロック信号を受け、前記クロック信号に基づいて第2の周波数の少なくとも1つの分周信号を生成するための手段、ここで、前記第2の周波数は、前記第1の周波数のフラクションである、と、

前記少なくとも1つの分周信号のデューティサイクルを調整することによって少なくとも1つのデューティサイクル調整信号を生成するための手段、ここで、前記少なくとも1つの分周信号を生成するための前記手段及び前記少なくとも1つのデューティサイクル調整信号を生成するための前記手段は、フィードバックループ中で結合される、と

を備える装置。

10

## 【請求項 18】

前記少なくとも1つの分周信号を生成するための前記手段は、

第1の分周信号を生成するように構成された第1のラッチする手段と、

第2の分周信号を生成するように構成された第2のラッチする手段と

を備える、請求項17に記載の装置。

## 【請求項 19】

前記少なくとも1つのデューティサイクル調整信号を生成するための前記手段は、

第1のデューティサイクル調整信号を生成するように構成された第1のデューティサイクル調整手段と、

第2のデューティサイクル調整信号を生成するように構成された第2のデューティサイクル調整手段と

を備える、請求項18に記載の装置。

20

## 【請求項 20】

前記第1のデューティサイクル調整手段は、調整可能なバイアス電流に基づいて決定される調整可能なデューティサイクルを有する前記第1のデューティサイクル調整信号を生成するように構成される、請求項19に記載の装置。

## 【請求項 21】

デューティサイクル制御信号に基づいて前記調整可能なバイアス電流を生成するための手段

を更に備える、請求項20に記載の装置。

30

## 【請求項 22】

非一時的コンピュータ可読媒体を備えたコンピュータプログラム製品であつて、前記非一時的コンピュータ可読媒体は、

フィードバックループ中で結合された少なくとも1つの分周回路で少なくとも1つの分周信号の生成を指揮することを少なくとも1つのプロセッサに行わせるコード、ここで、前記少なくとも1つの分周回路は、第1の周波数のクロック信号を受け、第2の周波数の前記少なくとも1つの分周信号を供給し、前記第2の周波数は、前記第1の周波数のフラクションである、と、

前記フィードバックループ内で前記少なくとも1つの分周回路に結合された少なくとも1つのデューティサイクル調整回路で前記少なくとも1つの分周信号のデューティサイクルを調整することによって、少なくとも1つのデューティサイクル調整信号の生成を指揮することを前記少なくとも1つのプロセッサに行わせるコード、と

を備える、コンピュータプログラム製品。

40

## 【発明の詳細な説明】

## 【優先権の主張】

## 【0001】

[0001] 本願は、本願の譲受人に譲渡され、参照により本明細書に明確に組み込まれる、2013年6月25日に出願された「FREQUENCY DIVIDER WITH DUTY CYCLE ADJUSTMENT WITHIN FEEDBACK LOOP」と題する米国特許非仮出願第13/926,631号の優先権を主張する。

50

## 【技術分野】

## 【0002】

[0002] 本開示は一般にエレクトロニクスに関し、より具体的には分周器に関する。

## 【背景技術】

## 【0003】

[0003] 分周器は、第1の周波数のクロック信号を受け、第1の周波数よりも低い第2の周波数の分周信号を供給する回路である。例えば、分周器は、2の係数でクロック信号を分周し、クロック信号の半分の周波数の分周信号を供給し得る。

## 【0004】

[0004] 分周器は、局部発振器（LO）生成器のような様々な回路において一般に使用される。例えば、LO生成器は、（i）第1の周波数の発振器／クロック信号を生成するための発振器と、（ii）発振器／クロック信号を分周し、第2の周波数の分周信号を供給するための分周器とを含み得る。分周信号は、同相（I）及び直交（Q）LO信号を生成するために使用され得、これは、周波数ダウンコンバージョンのために受信機によって、及び／又は、周波数アップコンバージョンのために送信機によって使用され得る。

10

## 【0005】

[0005] 調整可能なデューティサイクルを有するLO信号を生成することが望まれ得る。受信機のためのLO信号のデューティサイクルは、受信機内のミキサがいつオンにされるかを決定し得る。このように、LO信号のデューティサイクルは、受信機の線形性に対して大きなインパクトを与える、二次入力インターポリートポイント（IIP2）のような様々な性能メトリックに影響を及ぼし得る。良い線形性を得るためにLO信号のデューティサイクルを調整することが望まれ得る。

20

## 【発明の概要】

## 【0006】

[0006] フィードバックループ内にデューティサイクル調整を有する分周器が本明細書で開示される。例示的な設計では、装置は、少なくとも1つの分周回路及び少なくとも1つのデューティサイクル調整回路を含み得る。少なくとも1つの分周回路は、フィードバックループ内で結合され得、第1の周波数のクロック信号を受け、第2の周波数の少なくとも1つの分周信号を供給し得る。第2の周波数は、第1の周波数のフラクションであり得る。少なくとも1つのデューティサイクル調整回路は、フィードバックループ内の少なくとも1つの分周回路に結合され得、少なくとも1つの分周信号のデューティサイクルを調整し得、少なくとも1つのデューティサイクル調整信号を少なくとも1つの分周回路に供給し得る。

30

## 【0007】

[0007] 例示的な設計では、少なくとも1つの分周回路は、第1及び第2のラッチを含み得る。第1のラッチは、クロック信号を受け、第1の分周信号を供給し得る。第2のラッチは、クロック信号を受け、第2の分周信号を供給し得る。少なくとも1つのデューティサイクル調整回路は、第1及び第2のデューティサイクル調整回路を含み得る。第1のデューティサイクル調整回路は、第1のラッチから第1の分周信号を受け、第2のラッチに第1のデューティサイクル調整信号を供給し得る。第2のデューティサイクル調整回路は、第2のラッチから第2の分周信号を受け、第1のラッチに第2のデューティサイクル調整信号を供給し得る。第1及び第2のラッチ並びに第1及び第2のデューティサイクル調整回路は、2分周（divide-by-2）を行い得る。

40

## 【0008】

[0008] 本開示の様々な態様及び特徴が、以下で更に詳細に説明される。

## 【図面の簡単な説明】

## 【0009】

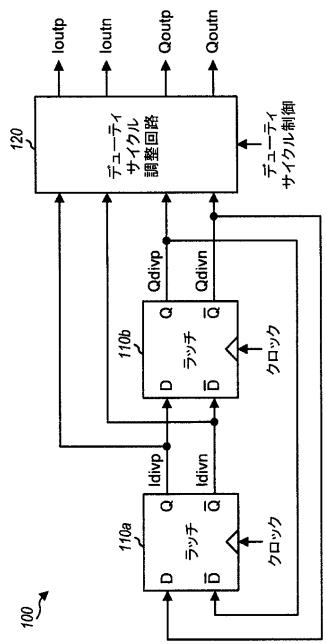

【図1】図1は、フィードバックループの外側にデューティサイクル調整を有する分周器を示す。

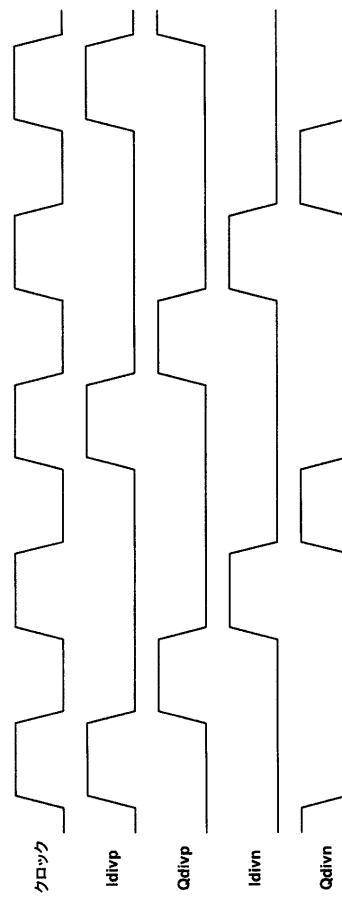

【図2A】図2Aは、図1の分周器のためのクロック信号及び分周信号を示す。

50

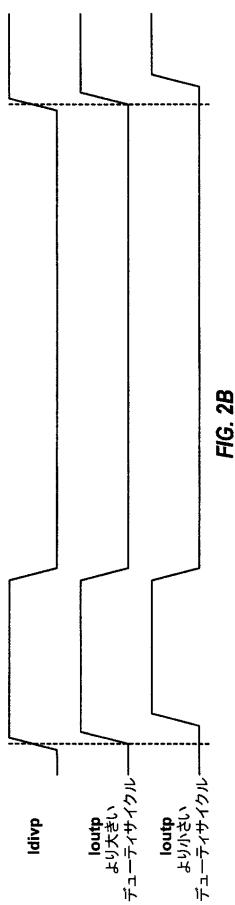

【図2B】図2Bは、分周信号のデューティサイクルの調整を示す。

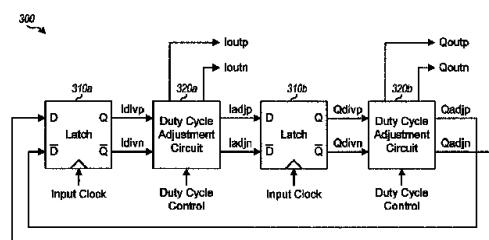

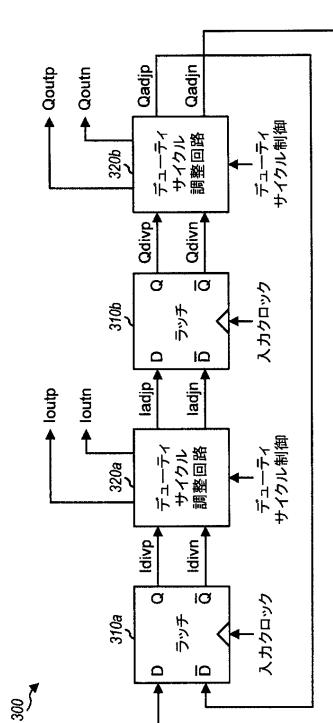

【図3】図3は、フィードバックループ内にデューティサイクル調整を有する分周器の例示的な設計を示す。

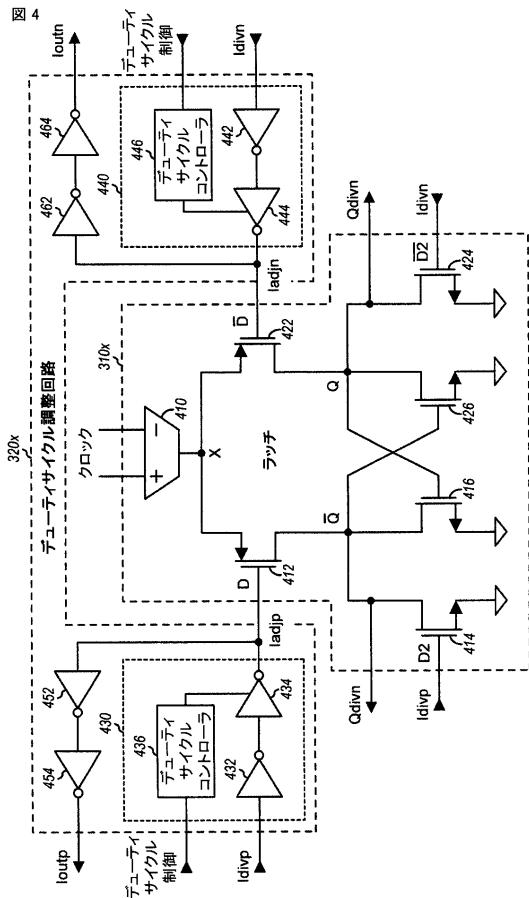

【図4】図4は、ラッチ及びデューティサイクル調整回路の例示的な設計を示す。

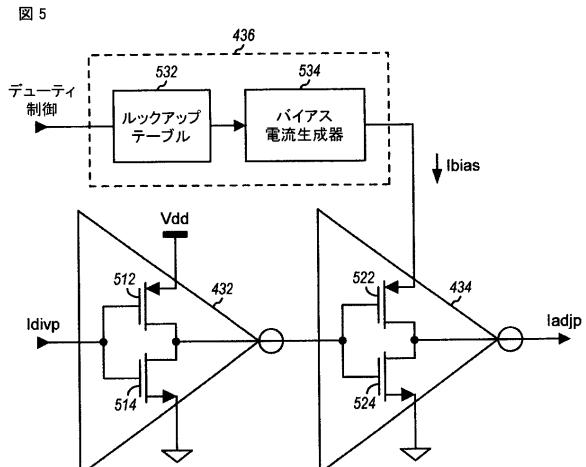

【図5】図5は、図4のデューティサイクル調整回路内のインバータ及びデューティサイクルコントローラの例示的な設計を示す。

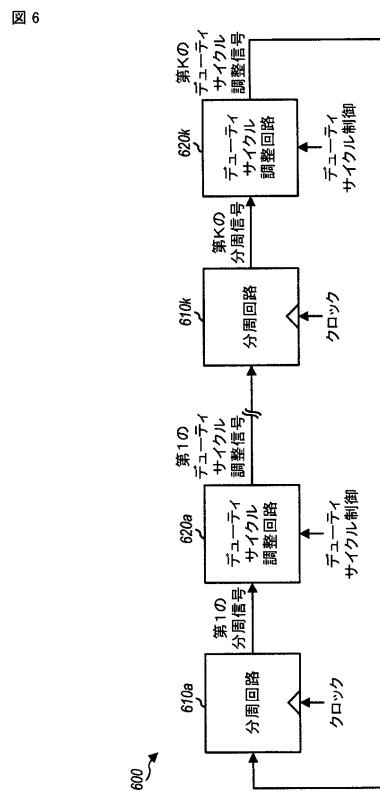

【図6】図6は、フィードバックループ内にデューティサイクル調整を有する分周器の別の例示的な設計を示す。

【図7】

【図8】図8は、分周信号を生成するためのプロセスを示す。

10

【発明を実施するための形態】

【0010】

[0017] 以下に示される詳細な説明は、本開示の例示的な設計の説明であることが意図され、本開示が実施され得る唯一の設計を表すことは意図されない。「例示的(exemplary)」という用語は、本明細書では、「実例、事例、又は例示として機能する」という意味で用いられる。本明細書において「例示的」として説明される任意の設計は、必ずしも、他の設計よりも好ましい又は有利であると解釈されるべきでない。詳細な説明は、本開示の例示的な設計の完全な理解を提供することを目的として特定の詳細を含む。本明細書で説明される例示的な設計がこれらの特定の詳細なしに実施され得ることは、当業者には明らかであろう。いくつかの事例では、周知の構造及びデバイスが、本明細書で示される例示的な設計の新規性を曖昧にしないために、ブロック図形式で示される。

20

【0011】

[0018] 図1は、フィードバックループの外側にデューティサイクル調整を有する分周器100のブロック図を示す。分周器100は、2つのラッチ110a及び110bと、1つのデューティサイクル調整回路120とを含む。ラッチ110a及び110bは、フィードバックループ中で結合され、2分周分周器(divide-by-2 divider)を実装する。

【数1】

30

第1のラッチ110aのQ及び $\bar{Q}$ 出力は、それぞれ、第2のラッチ110bのD及び $\bar{D}$ 入力に結合される。第2のラッチ110bのQ及び $\bar{Q}$ 出力はスワップされ、それぞれ、第1のラッチ110aの $\bar{D}$ 及びD入力に結合される。ラッチ110a及び110bはまた、クロック信号を受ける。

【0012】

[0019] 第1のラッチ110aは、

【数2】

40

そのQ及び $\bar{Q}$ 出力において

【0013】

それぞれ補完 $I_{divp}$ 及び $I_{divn}$ 分周信号をデューティサイクル調整回路120に供給する。第2のラッチ110bは、

## 【数3】

そのQ及び $\bar{Q}$ 出力において

## 【0014】

それぞれ補完Q

d i v p

及びQ

d i v n

分周信号をデューティサイクル調整回路120に供給する。I

d i v p

、I

d i v n

、Q

d i v p

、及びQ

d i v n

信号は、クロック信号の2分の1の周波数である。デューティサイクル調整回路120は、それぞれ4つの分周信号I

d i v p

、I

d i v n

、Q

d i v p

、及びQ

d i v n

に基づいて所望のデューティサイクルを有する4つの出力信号I

o u t p

、I

o u t n

、Q

o u t p

、及びQ

o u t n

を生成する。デューティサイクル調整回路120は、I

o u t p

、I

o u t n

、Q

o u t p

、及びQ

o u t n

信号のデューティサイクルを調整し得る。

10

## 【0015】

[0020] 図1では、ラッチ110a及び110bは、フィードバックループ中で結合され、2分周分周器を形成する。デューティサイクル調整回路120は、2分周分周器の後、かつ、フィードバックループの外側に位置する。I

d i v p

、I

d i v n

、Q

d i v p

、及びQ

d i v n

信号のスルーレートは、ラッチ110a及び110bによって増幅及び鮮鋭化(sharpen)され得る。故に、ラッチ110a及び110bからのI

d i v p

、I

d i v n

、Q

d i v p

、及びQ

d i v n

信号のデューティサイクルを変えることは非常に困難になり得る。その上、ラッチ110a及び110bからのI

d i v p

、I

d i v n

、Q

d i v p

、及びQ

d i v n

信号のデューティサイクルを調整するために余分なバッテリ電力が消費され得る。

20

## 【0016】

[0021] 図2Aは、クロック信号と、図1のラッチ110a及び110bからのI

d i v p

、I

d i v n

、Q

d i v p

、及びQ

d i v n

信号とのタイミング図を示す。クロック信号は、図2Aの一番上に示される。I

d i v p

及びI

d i v n

信号は、互いに対し1クロックサイクルだけ遅れている。Q

d i v p

及びQ

d i v n

信号もまた、互いに対し1クロックサイクルだけ遅れている。Q

d i v p

信号は、I

d i v p

信号に対し2分の1クロックサイクルだけ遅れている。

30

## 【0017】

[0022] 図2Bは、I

o u t p

信号のデューティサイクルの調整を示す。I

d i v p

信号は、図2Bの一番上に示される。I

d i v p

信号は、固定のデューティサイクルを有し、これは、ラッチ110a及び110bの回路設計によって決定され得る。より大きいデューティを有するI

o u t p

信号及びより小さいデューティを有するI

o u t p

信号が、I

d i v p

信号の下に示される。I

o u t p

信号のデューティサイクルは、I

d i v p

信号の立上り/立下り遷移に対して、少量だけ、I

o u t p

信号の立上り/立下り遷移を遅らせることによって増やされ得る。I

o u t p

信号のデューティサイクルは、I

d i v p

信号の立上り/立下り遷移に対して、より多くの量だけ、I

o u t p

信号の立上り/立下り遷移を遅らせることによって減らされ得る。

40

## 【0018】

[0023] 図3は、フィードバックループ内にデューティサイクル調整を有する分周器300の例示的な設計のブロック図を示す。分周器300は、2つのラッチ310a及び310bと、2つのデューティサイクル調整回路320a及び320bとを含み、これらは、フィードバックループ中で結合されており、2分周分周器を実装する。

## 【数4】

第1のラッチ310aは、(i) デューティサイクル調整回路320bの出力に結合されたそのD及び $\bar{D}$ 入力と、(ii) デューティサイクル調整回路320aの入力に結合されたそのQ及び $\bar{Q}$ 出力とを有する。第2のラッチ310bは、(i) デューティサイクル調整回路320aの出力に結合されたそのD及び $\bar{D}$ 入力と、(ii) デューティサイクル調整回路320bの入力に結合されたそのQ及び $\bar{Q}$ 出力とを有する。

10

## 【0019】

[0024] 第1のラッチ310aは、

## 【数5】

そのQ及び $\bar{Q}$ 出力において、

20

## 【0020】

それぞれ $I_{d i v p}$ 及び $I_{d i v n}$ 分周信号をデューティサイクル調整回路320aに供給する。デューティサイクル調整回路320aは、それぞれ $I_{d i v p}$ 及び $I_{d i v n}$ 信号に基づいて $I_{adj p}$ 及び $I_{adj n}$ 信号を生成する。 $I_{adj p}$ 及び $I_{adj n}$ 信号は、所望のデューティサイクルを有するデューティサイクル調整信号である。デューティサイクル調整回路320aはまた、所望のデューティサイクルを有する $I_{out p}$ 及び $I_{out n}$ 出力信号を供給する。 $I_{out p}$ 及び $I_{out n}$ 信号は、それぞれ $I_{adj p}$ 及び $I_{adj n}$ 信号のバッファされたバージョンであり得る。デューティサイクル調整回路320aは、 $I_{adj p}$ 、 $I_{adj n}$ 、 $I_{out p}$ 、及び $I_{out n}$ 信号のデューティサイクルを調整し得る。同様に、第2のラッチ310bは、

30

## 【数6】

そのQ及び $\bar{Q}$ 出力において、

## 【0021】

それぞれ $Q_{d i v p}$ 及び $Q_{d i v n}$ 分周信号をデューティサイクル調整回路320bに供給する。デューティサイクル調整回路320bは、所望のデューティサイクルを有する $Q_{adj p}$ 及び $Q_{adj n}$ デューティサイクル調整信号を、それぞれ $Q_{d i v p}$ 及び $Q_{d i v n}$ 信号に基づいて生成する。デューティサイクル調整回路320bはまた、所望のデューティサイクルを有する $Q_{out p}$ 及び $Q_{out n}$ 信号を供給する。 $Q_{out p}$ 及び $Q_{out n}$ 信号は、それぞれ、 $Q_{adj p}$ 及び $Q_{adj n}$ 信号のバッファされたバージョンであり得る。デューティサイクル調整回路320bは、 $Q_{adj p}$ 、 $Q_{adj n}$ 、 $Q_{out p}$ 、及び $Q_{out n}$ 信号のデューティサイクルを調整し得る。

40

## 【0022】

[0025] 図3に示されるように、デューティサイクル調整回路320a及び320bは、フィードバックループ内に位置する。デューティサイクル調整回路320aは、第1のラッチ310aからの $I_{d i v p}$ 及び $I_{d i v n}$ 信号に基づいて生成される $I_{adj p}$ 及び $I_{adj n}$ 信号のデューティサイクルを調整することができる。デューティサイクル調

50

整回路 3 2 0 b は、ラッチ 3 1 0 b からの  $Q_{d i v p}$  及び  $Q_{d i v n}$  信号に基づいて生成される  $Q_{a d j p}$  及び  $Q_{a d j n}$  信号のデューティサイクルを調整することができる。

【0 0 2 3】

[0026] 図 3 のラッチ 3 1 0 a 及び 3 1 0 b 並びにデューティサイクル調整回路 3 2 0 a 及び 3 2 0 b は、様々な手法で実装され得る。ラッチ 3 1 0 a 及び 3 1 0 b 並びにデューティサイクル調整回路 3 2 0 a 及び 3 2 0 b の幾つかの例示的な設計が以下で説明される。

【0 0 2 4】

[0027] 図 4 は、ラッチ 3 1 0 x 及びデューティサイクル調整回路 3 2 0 x の例示的な設計の略図を示す。ラッチ 3 1 0 x は、図 3 のラッチ 3 1 0 a 及び 3 1 0 b の各々に使用され得る。デューティサイクル調整回路 3 2 0 x は、図 3 のデューティサイクル調整回路 3 2 0 a 及び 3 2 0 b の各々に使用され得る。簡潔さのため、図 4 は、ラッチ 3 1 0 b に使用され、 $I_{a d j p}$  及び  $I_{a d j n}$  信号を受け、 $Q_{d i v p}$  及び  $Q_{d i v n}$  信号を供給するラッチ 3 1 0 x を示す。図 4 はまた、デューティサイクル調整回路 3 2 0 a に使用され、 $I_{d i v p}$  及び  $I_{d i v n}$  信号を受け、 $I_{a d j p}$  及び  $I_{a d j n}$  信号を供給するデューティサイクル調整回路 3 2 0 x を示す。

10

【0 0 2 5】

[0028] 図 4 に示される設計では、ラッチ 3 1 0 x は、g m セル 4 1 0、P 型金属酸化膜半導体 (PMOS) トランジスタ 4 1 2 及び 4 2 2、並びにN 型金属酸化膜半導体 (NMOS) トランジスタ 4 1 4、4 1 6、4 2 4、及び 4 2 6 を含む。G m セル 4 1 0 は、差動クロック信号を受けるその非反転 (+) 入力及び反転 (-) 入力と、ノード X に結合されたその出力とを有する。PMOS トランジスタ 4 1 2 は、ノード X に結合されたそのソースと、ラッチ 3 1 0 x の D 入力に結合されたそのゲートと、

20

【数 7】

ラッチ 3 1 0 x の  $\bar{Q}$  出力に結合されたそのドレインとを有する。

30

【0 0 2 6】

PMOS トランジスタ 4 2 2 は、ノード X に結合されたそのソースと、

【数 8】

ラッチ 3 1 0 x の  $\bar{D}$  入力に結合されたそのゲートと、

40

【0 0 2 7】

ラッチ 3 1 0 x の Q 出力に結合されたそのドレインとを有する。NMOS トランジスタ 4 1 4 は、回路接地に結合されたそのソースと、ラッチ 3 1 0 x の D 2 入力に結合されたそのゲートと、

【数 9】

ラッチ 3 1 0 x の  $\bar{Q}$  出力に結合されたそのドレインとを有する。

50

【0 0 2 8】

NMOS トランジスタ 4 1 6 は、回路接地に結合されたそのソースと、ラッチ 3 1 0 x の Q 出力に結合されたそのゲートと、

【数10】

ラッチ310xの $\bar{Q}$ 出力に結合されたそのドレインとを有する。

【0029】

NMOSトランジスタ424は、回路接地に結合されたそのソースと、

【数11】

ラッチ310xの $\bar{D}_2$ 入力に結合されたそのゲートと、

10

【0030】

ラッチ310xのQ出力に結合されたそのドレインとを有する。NMOSトランジスタ426は、回路接地に結合されたそのソースと、

【数12】

ラッチ310xの $\bar{Q}$ 出力に結合されたそのゲートと、

20

【0031】

ラッチ310xのQ出力に結合されたそのドレインとを有する。

【0032】

[0029] 図4に示される設計では、デューティサイクル調整回路320xは、 $I_{d_i v_p}$ 信号のためのデューティサイクル調整回路430と、 $I_{d_i v_n}$ 信号のためのデューティサイクル調整回路440とを含む。デューティサイクル調整回路430は、インバータ432及び434と、デューティサイクルコントローラ436とを含む。インバータ432は、 $I_{d_i v_p}$ 信号を受けるその入力と、インバータ434の入力に結合されたその出力とを有する。インバータ434は、ラッチ310xのD入力に結合され、PMOSトランジスタ412のゲートに $I_{adjp}$ 信号を供給するその出力を有する。デューティサイクルコントローラ436は、デューティサイクル制御信号を受けるその入力と、インバータ434に調整可能なバイアス電流を供給するその出力とを有する。同様に、デューティサイクル調整回路440は、インバータ442及び444と、デューティサイクルコントローラ446とを含む。インバータ442は、 $I_{d_i v_n}$ 信号を受けるその入力と、インバータ444の入力に結合されたその出力とを有する。インバータ444は、

30

【数13】

ラッチ310xの $\bar{D}$ 入力に結合されており、

40

【0033】

PMOSトランジスタ422のゲートに $I_{adjn}$ 信号を供給するその出力を有する。デューティサイクルコントローラ446は、デューティサイクル制御信号を受けるその入力と、インバータ444に調整可能なバイアス電流を供給するその出力とを有する。

【0034】

[0030] ラッチ310xは、以下のように動作する。PMOSトランジスタ412及びNMOSトランジスタ414は、 $I_{adjp}$ 及び $I_{d_i v_p}$ 信号を受け、

【数14】

ラッチ310xの $\bar{Q}$ 出力において

【0035】

$Q_{d i v n}$ 信号を供給する第1のインバータを形成する。PMOSトランジスタ422及びNMOSトランジスタ424は、 $I_{adjn}$ 及び $I_{divn}$ 信号を受け、ラッチ310xのQ出力において $Q_{divp}$ 信号を供給する第2のインバータを形成する。NMOSトランジスタ416及び426は、

10

【数15】

ラッチ310xのQ及び $\bar{Q}$ 出力において論理値を維持する。

【0036】

[0031] デューティサイクル調整回路430は、以下のように動作する。インバータ432は、 $I_{divp}$ 信号をバッファし、バッファされた $I_{divp}$ 信号を供給する。インバータ434は更に、バッファされた $I_{divp}$ 信号をバッファし、 $I_{adjp}$ 信号を供給する。 $I_{adjp}$ 信号の立上り/立下り遷移は、インバータ434のバイアス電流を変えることによって調整され得る。具体的には、 $I_{adjp}$ 信号の立上り/立下り遷移は、(i)インバータ434に対するバイアス電流がより大きい場合には進められ得、又は(ii)インバータ434に対するバイアス電流がより小さい場合には遅らせられ得る。デューティサイクル調整回路440は、デューティサイクル調整回路430と同様の手法で動作し、調整可能なデューティサイクルを有する $I_{adjn}$ 信号を供給する。 $Q_{adjp}$ 及び $Q_{adjn}$ 信号のデューティサイクルは、 $I_{adjp}$ 及び $I_{adjn}$ 信号のデューティサイクルと同様の手法で(及び、それから独立して)調整され得る。

20

【0037】

[0032] ラッチ310xは、図4に示されるように、ラッチ310aに使用され得る。このケースでは、ラッチ310xは、図4に示されるように、

30

【数16】

そのD及び $\bar{D}$ 入力において $I_{adjp}$ 及び $I_{adjn}$ 信号を受け、そのD2及び $\bar{D}2$ 入力において $I_{divp}$ 及び $I_{divn}$ 信号を受け、そのQ及び $\bar{Q}$ 出力において $Q_{divp}$ 及び $Q_{divn}$ 信号を供給する。

【0038】

ラッチ310xは、ラッチ310bにも使用され得る(図4には示されない)。このケースでは、ラッチ310xは、

40

## 【数17】

そのD及び $\bar{D}$ 入力においてQadjp及びQadjn信号を受け、そのD2及び $\bar{D}2$ 入力においてQdivp及びQdivn信号を受け、そのQ及び $\bar{Q}$ 出力においてIdivp及びIdivn信号を供給する。ラッチ310bは、ラッチ310aと同様の手法で実装され得る。

10

## 【0039】

[0033] デューティサイクル調整回路320xは、図4に示されるように、デューティサイクル調整回路320bに使用され得る。このケースでは、デューティサイクル調整回路430は、Idivp信号を受け、Iadjp信号を供給し、デューティサイクル調整回路440は、Idivn信号を受け、Iadjn信号を供給し得る。デューティサイクル調整回路320xは、デューティサイクル調整回路320aにも使用され得る(図4には示されない)。このケースでは、デューティサイクル調整回路430は、Qdivp信号を受け、Qadjp信号を供給し、デューティサイクル調整回路440は、Qdivn信号を受け、Qadjn信号を供給し得る。デューティサイクル調整回路320bは、デューティサイクル調整回路320aと同様の手法で実装され得る。

20

## 【0040】

[0034] 図4は、ラッチ310xの例示的な設計を示す。ラッチはまた、他の手法でも実装され得る。例えば、gmセル410は、電源電圧に結合されたソースと、クロック信号を受けるゲートと、ノードXに結合されたドレインとを有するPMOSトランジスタと置き換えられ得る。NMOSトランジスタ414及び424は、取り除かれ得るか、又は

## 【数18】

Q及び $\bar{Q}$ 出力と回路接地との間に結合された抵抗器と置き換えら得る。

30

## 【0041】

[0035] 図4は、デューティサイクル調整回路430が2つのインバータ432及び434を含む例示的な設計を示し、ここで、インバータ432は、固定のバイアス電流を有し、インバータ434は、調整可能なバイアス電流を有する。調整可能なバイアス電流は、他の手法でも供給され得る。別の設計では、両方のインバータ432及び434が、調整可能なバイアス電流を有し得る。更に別の設計では、インバータ432が、調整可能なバイアス電流を有し得、インバータ434が、固定のバイアス電流を有し得る。このケースでは、インバータ432に供給される調整可能なバイアス電流は、インバータ434に供給される調整可能なバイアス電流と比べて逆の手法で設定され得る。例えば、より小さいデューティサイクルは、より大きいバイアス電流がインバータ434に供給されるか、又はより小さいバイアス電流がインバータ432に供給されることで得られ得る。

40

## 【0042】

[0036] デューティサイクル調整回路は、任意の数のインバータを含み得る。一設計では、デューティサイクル調整回路は、分周信号(例えば、Idivp信号)に基づいてデューティサイクル調整信号(例えば、Iadjp信号)を生成するために偶数の数のインバータ(例えば、2つのインバータ)を含み得る。この設計では、デューティサイクル調整信号は、分周信号と同じ極性を有するだろう。別の設計では、デューティサイクル調整回路は、分周信号に基づいてデューティサイクル調整信号を生成するために奇数の数のインバータ(例えば、1つのインバータ)を含み得る。この設計では、デューティサイクル

50

調整信号は、分周信号と反対の極性を有するだろう。例えば、インバータ 432 が省略され得、インバータ 434 が、その入力において  $I_{d i v n}$  信号を受け、その出力において  $I_{a d j p}$  信号を供給し得る。代替的又は追加的に、インバータ 454 が省略され得、インバータ 452 が、その入力において  $I_{a d j p}$  信号を受け、その出力において  $I_{o u t n}$  信号を供給し得る。より少ない数のバッファは、電力消費を減らし得るが、より多くの数のバッファは、スルーレートを改善し得る。バッファの数は、電力消費とスルーレートとの間のトレードオフに基づいて選択され得る。

#### 【0043】

[0037] 図 5 は、図 4 のデューティサイクル調整回路内のインバータ 432 及び 434 並びにデューティサイクルコントローラ 436 の例示的な設計の略図を示す。この設計では、インバータ 432 は、ゲートが互いに結合され、ドレインが互いに結合された PMOS トランジスタ 512 と NMOS トランジスタ 514 とを含む。PMOS トランジスタ 512 のソースは、電源 ( $V_{d d}$ ) に結合され、NMOS トランジスタ 514 のソースは、回路接地に結合される。インバータ 434 は、ゲートが互いに結合され、ドレインが互いに結合された PMOS トランジスタ 522 と NMOS トランジスタ 524 とを含む。PMOS トランジスタ 522 のソースは、デューティサイクルコントローラ 436 の出力に結合され、調整可能なバイアス電流  $I_{b i a s}$  を受ける。NMOS トランジスタ 524 のソースは、回路接地に結合される。

10

#### 【0044】

[0038] 図 5 に示される設計では、デューティサイクルコントローラ 436 は、ルックアップテーブル 532 及びバイアス電流生成器 534 を含む。ルックアップテーブル 532 は、 $I_{a d j p}$  信号の所望のデューティサイクルを示すデューティ制御信号を受け、1 つ又は複数の制御信号を供給する。バイアス電流生成器 534 は、ルックアップテーブル 532 からの 1 つ又は複数の制御信号に基づいてインバータ 434 のための調整可能なバイアス電流を生成する。インバータ 434 のバイアス電流を変えること、これは次いで、 $I_{a d j p}$  信号のスルーレートを変え得る、によって、 $I_{a d j p}$  信号のデューティサイクルが調整され得る。より大きいバイアス電流は、より速いスルーレートに帰着し得、これは、次いで、より大きいデューティサイクルに帰着し得る。反対に、より小さいバイアス電流は、より遅いスルーレートに帰着し得、これは、次いで、より小さいデューティサイクルに帰着し得る。

20

30

#### 【0045】

[0039] 図 3 は、2 で分周する分周器の例示的な設計を示し、それは、フィードバックループ中で結合された 2 つのラッチ及び 2 つのデューティサイクル調整回路を備える。一般に、分周器は、任意の分周比でクロック信号を分周し、所望のデューティサイクルの分周信号を供給し得る。分周器は、分周信号にとって所望の分周比と所望のデューティサイクルとを得るために、フィードバックループ内に任意の数の回路及び任意のタイプの回路を含み得る。

#### 【0046】

[0040] 図 6 は、フィードバックループ内にデューティサイクル調整を有する分周器 600 の例示的な設計のブロック図を示す。分周器 600 は、フィードバックループ中で結合された  $K$  個の分周回路 610a - 610k と、 $K$  個のデューティサイクル調整回路 620a - 620k とを含み、ここで、 $K$  は、任意の整数値であり得る。一般に、分周器は、フィードバックループ中で結合された任意の数の分周回路と、任意の数のデューティサイクル調整回路とを含み得る。一設計では、同じ数の分周回路とデューティサイクル調整回路とが、フィードバックループ中で結合され得る。この設計では、各分周回路 610 は、先行のデューティサイクル調整回路 620 に結合されたその入力と、後続のデューティサイクル調整回路 620 に結合されたその出力とを有し得る。別の設計では、 $K$  個の分周回路と  $K$  個よりも少ない数のデューティサイクル調整回路が、フィードバックループ中で結合され得る。この設計では、1 つ又は複数の分周回路 610 は、デューティサイクル調整回路 620 に結合されたそれらの出力を有し得、1 つ又は複数の他の分周回路 610 は、

40

50

後続の分周回路 610 に結合されたそれらの出力を有し得る。

【0047】

[0041] 各分周回路 610 は、クロック信号の分周を容易にすることができる 1 つ又は複数のラッチ及び / 又は他の回路を備え得る。例えば、各分周回路 610 は、単一のラッチを備え得、分周器 600 は、フィードバックループ中で結合された K 個のラッチを有する K 分周分周器 (divide-by-K divider) を実装し得る。異なるタイプのラッチ (例えば、D タイプのラッチ、JK タイプのラッチ、等) が、分周回路 610 に使用され得る。

【0048】

[0042] 各デューティサイクル調整回路 620 は、図 4 のデューティサイクル調整回路 320 x と同様の手法で又は何らかの他の回路設計に基づいて実装され得る。K 個のデューティサイクル調整回路 620 a - 620 k は、同じ回路設計又は異なる回路設計で実装され得る。

10

【0049】

[0043] 本明細書で開示されるような、フィードバックループ内にデューティサイクル調整を有する分周器は、様々な用途に使用され得る。ワイヤレス通信デバイスにおける分周器の例示的な用途が以下で説明される。

【0050】

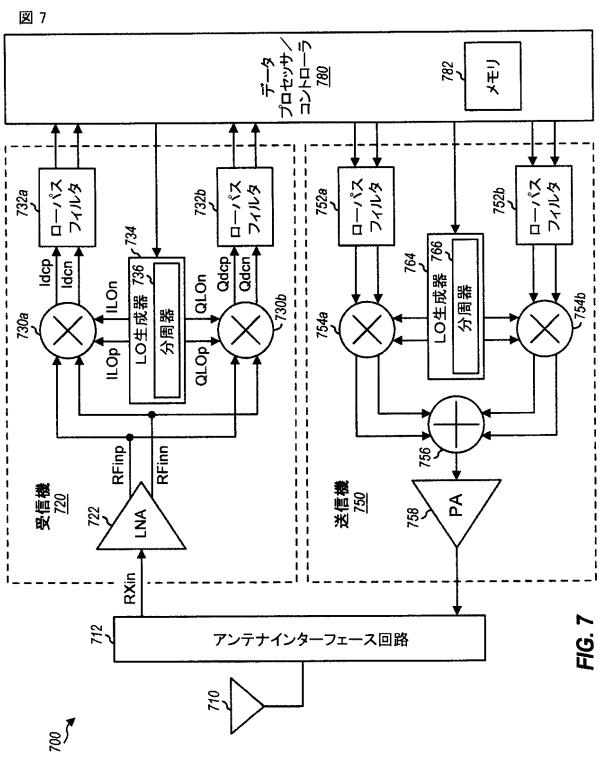

[0044] 図 7 は、セルラ電話、スマートフォン、タブレット、等であり得るワイヤレス通信デバイス 700 の例示的な設計のブロック図を示す。ワイヤレスデバイス 700 は、ロングタームエボリューション (LTE)、符号分割多元接続 (CDMA) 1X、広帯域 CDMA (WCDMA (登録商標))、モバイル通信のためのグローバルシステム (GSM (登録商標))、IEEE 802.11、等のような、ワイヤレス通信のための 1 つ又は複数の無線技法をサポートし得る。簡潔さのために、図 7 は、1 つのアンテナ 710 に対して 1 つの受信機 720 及び 1 つの送信機 750 を含むワイヤレスデバイス 700 を示す。一般に、ワイヤレスデバイス 700 は、任意の数の無線技術及び任意の数の周波数帯域のための通信をサポートするために、任意の数の送信機、任意の数の受信機、及び任意の数のアンテナを含み得る。

20

【0051】

[0045] 受信経路では、アンテナ 710 は、基地局及び / 又は他の送信機局からダウンリンク信号を受信し、アンテナ出力信号をアンテナインターフェース回路 712 に供給する。回路 712 は、アンテナ出力信号をルーティングし、受信 RF 信号 (RF in) を受信機 720 に供給する。回路 712 は、スイッチ、デュプレクサ、ダイプレクサ、フィルタ、整合回路、等を含み得る。

30

【0052】

[0046] 受信機 720 内で、低ノイズ増幅器 (LNA) 722 は、受信された RF 信号を増幅し、入力 RF 信号 (RF in) をミキサ 730 a 及び 730 b に供給する。ミキサ 730 a は、LO 生成器 734 からの ILO 信号 (ILO) で入力 RF 信号をダウンコンバートし、IDC 信号 (IDC) を供給する。受信機 720 内のいくつかの信号は、非反転信号 ('p' が末尾についている) 及び反転信号 ('n' が末尾についている) を備える差動信号であり得る。ローパスフィルタ 732 a は、この IDC 信号をフィルタリングし、I 入力ベースバンド信号をデータプロセッサ / コントローラ 780 に供給する。同様に、ミキサ 730 b は、LO 生成器 734 からの QLO 信号 (QLO) で入力 RF 信号をダウンコンバートし、QDC 信号 (QDC) を供給する。ローパスフィルタ 732 b は、この QDC 信号をフィルタリングし、Q 入力ベースバンド信号をデータプロセッサ 780 に供給する。プロセッサ 780 は、I 及び Q 入力ベースバンド信号をデジタル化し、処理して、ワイヤレスデバイス 700 に送られたデータを復元する。

40

【0053】

[0047] 送信経路では、データプロセッサ 780 は、送信されることとなるデータを処理し、I 及び Q 出力ベースバンド信号を送信機 750 に供給する。送信機 750 内で、I

50

及びQ出力ベースバンド信号は、ローパスフィルタ752a及び752bによってフィルタリングされ、ミキサ754a及び754bによってアップコンバートされ、加算器756によって合計され、電力増幅器(PA)758によって増幅されて、所望の出力電力レベルを有する出力RF信号が生成される。出力RF信号は、アンテナ710を介して送信される。LO生成器764は、ミキサ754a及び754bに対してそれぞれI及びQ LO信号を生成する。

【0054】

[0048] LO生成器734は、受信器720内のミキサ730a及び730bに対してI及びQ LO信号を生成する。LO生成器764は、送信機750内のミキサ754a及び754bに対してI及びQ LO信号を生成する。LO生成器734及び764は、各々、1つ又は複数の電圧制御型発振器(VCO)、位相ロックドリープ(PLL)、基準発振器、分周器、バッファ、等を含み得る。例えば、LO生成器734は、フィードバックループ内にデューティサイクル調整を有する分周器736を含み得る。LO生成器764は、フィードバックループ内にデューティサイクル調整を有する分周器766を含み得る。分周器736及び766は、各々、図3の分周器300、図6の分周器600、等で実装され得る。

10

【0055】

[0049] 図7は、受信機720及び送信機750の例示的な設計を示す。一般に、受信機又は送信機における信号の調整は、1つ又は複数の増幅器、フィルタ、ミキサ、等によって行われ得る。これら回路は、図7に示されている構成とは異なって配列され得る。その上、受信器及び/又は送信機は、整合回路のような、図7に示されていない他の回路を含み得る。受信機720及び送信機750の一部又は全ては、1つ又は複数のRF集積回路(RFIC)、アナログIC、混合信号IC、等の上に実装され得る。例えば、ミキサ730及びLO生成器734は、RFIC上に実装され得る。

20

【0056】

[0050] データプロセッサ/コントローラ780は、ワイヤレスデバイス700のための様々な機能を行い得る。例えば、データプロセッサ780は、受信機720を介して受信されているデータと、送信機750を介して送信されているデータのための処理を行い得る。コントローラ780は、受信機720及び送信機750の動作を制御し得る。例えば、コントローラ780は、分周器736及び766の動作を制御し得る。メモリ782は、データプロセッサ/コントローラ780のためのプログラムコード及びデータを記憶し得る。データプロセッサ/コントローラ780は、1つ又は複数の特定用途向け集積回路(ASIC)及び/又は他のIC上に実装され得る。

30

【0057】

[0051] ワイヤレスデバイス700内の回路は、様々な手法で実装され得る。その上、これら回路は、NMOSトランジスタ、PMOSトランジスタ、及び/又は他のタイプのトランジスタで実装され得る。

【0058】

[0052] 本明細書で開示されるような、フィードバックループ内にデューティサイクル調整を有する新規な分周器は、様々な利点を有し得る。第1に、新規な分周器は、フィードバックループの外側にデューティサイクル調整を有する従来の分周器よりも優れたデューティサイクル制御を供給し得る。より優れたデューティサイクル制御は、フィードバックループ内の信号のデューティサイクルの調整により、可能であり得る。これら信号は、フィードバックループの外側の信号のものほど鮮鋭ではない波形を有し得る。より優れたデューティサイクル制御は、例えば、分周器によって供給される分周信号から生成されたLO信号に基づいて動作するミキサにおける優れたIIP2性能のような優れた線形性性能を達成するために重要であり得る。第2に、新規な分周器は、より速いクロックスルーレートを有し得る。より速いスルーレートは、スイッチング速度を上げ得、これは、ミキサの線形性及びノイズ指数を改善し得る。第3に、デューティサイクル制御は、新しい分周器の通常動作から隔離され得る。第4に、分周信号をバッファし、出力信号を供給す

40

50

るために、より少ない数のバッファが使用され得る。これは、新しい分周器の電力消費を減らし得る。

【0059】

[0053] 例示的な設計では、装置（例えば、ワイヤレスデバイス、I C、回路モジュール、回路基板、等）は、少なくとも1つの分周回路及び少なくとも1つのデューティサイクル調整回路を含み得る。少なくとも1つの分周回路（例えば、図6の分周回路610a-610k）は、フィードバックループ中で結合され得、第1の周波数のクロック信号を受け得、第2の周波数の少なくとも1つの分周信号を供給し得る。第2の周波数は、第1の周波数のフラクションであり得る。少なくとも1つのデューティサイクル調整回路（例えば、図6のデューティサイクル調整回路620a-620k）は、フィードバックループ内で少なくとも1つの分周回路に結合され得、少なくとも1つの分周信号のデューティサイクルを調整し得、少なくとも1つのデューティサイクル調整信号を少なくとも1つの分周回路に供給し得る。

10

【0060】

[0054] 例示的な設計では、少なくとも1つの分周回路は、第1及び第2のラッチを含み得る。第1のラッチ（例えば、図3のラッチ310a）は、クロック信号を受け、第1の分周信号（例えば、I<sub>d i v p</sub>信号）を供給し得る。第2のラッチ（例えば、ラッチ310b）は、クロック信号を受け、第2の分周信号（例えば、Q<sub>d i v p</sub>信号）を供給し得る。少なくとも1つのデューティサイクル調整回路は、第1及び第2のデューティサイクル調整回路を含み得る。第1のデューティサイクル調整回路（例えば、デューティサイクル調整回路320a）は、第1のラッチから第1の分周信号を受け、第1のデューティサイクル調整信号（例えば、I<sub>a d j p</sub>信号）を第2のラッチに供給する。第2のデューティサイクル調整回路（例えば、デューティサイクル調整回路320b）は、第2のラッチから第2の分周信号を受け、第2のデューティサイクル調整信号（例えば、Q<sub>a d j p</sub>信号）を第1のラッチに供給する。第1及び第2のラッチ並びに第1及び第2のデューティサイクル調整回路は、2分周を行い得る。このケースでは、第2の周波数は、第1の周波数の2分の1であり得る。第1の分周信号は、同相の分周信号を備え得、第2の分周信号は、直交の分周信号を備え得る。

20

【0061】

[0055] 例示的な設計では、第1のデューティサイクル調整回路は、インバータ及びデューティサイクルコントローラを含み得る。インバータ（例えば、図4及び5のインバータ434）は、調整可能なバイアス電流を受け、この調整可能なバイアス電流に基づいて決定された調整可能なデューティサイクルを有する第1のデューティサイクル調整信号を供給し得る。デューティサイクルコントローラ（例えば、デューティサイクルコントローラ436）は、デューティサイクル制御信号を受け、インバータに調整可能なバイアス電流を供給し得る。調整可能なバイアス電流は、デューティサイクル調整信号のための所望のデューティサイクルに基づいて設定されても良く、及び／又は、所望のデューティサイクルを提供するために制御されても良い。第1のデューティサイクル調整回路は、他の手法でも実装され得る。

30

【0062】

[0056] 例示的な設計では、デューティサイクルコントローラは、ルックアップテーブル及びバイアス電流生成器を含み得る。ルックアップテーブル（例えば、図5のルックアップテーブル532）は、デューティサイクル制御信号を受け、少なくとも1つの制御信号を供給し得る。バイアス電流生成器（例えば、バイアス電流生成器534）は、少なくとも1つの制御信号を受け、インバータに調整可能なバイアス電流を供給し得る。デューティサイクルコントローラは、他の手法でも実装され得る。

40

【0063】

[0057] 例示的な設計では、第1のラッチは、更に、第2のデューティサイクル調整信号、（例えば、Q<sub>a d j p</sub>信号）を受け、第1の分周信号（例えば、I<sub>d i v p</sub>信号）を供給し得る。第1のラッチは、更に、第2の分周信号（例えば、Q<sub>d i v p</sub>信号）を受け

50

、第1の分周信号を供給し得る。

【0064】

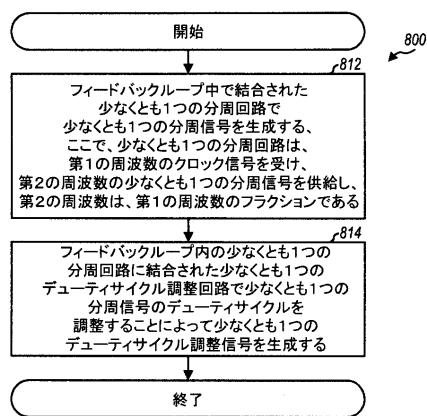

[0058] 図8は、分周信号を生成するためのプロセス800の設計を示す。少なくとも1つの分周信号は、フィードバックループ中で結合された少なくとも1つの分周回路で生成され得る(ブロック812)。少なくとも1つの分周回路は、第1の周波数のクロック信号を受け、第2の周波数の少なくとも1つの分周信号を供給し得る。第2の周波数は、第1の周波数のフラクションであり得る。少なくとも1つのデューティサイクル調整信号は、フィードバックループ内の少なくとも1つの分周回路に結合された少なくとも1つのデューティサイクル調整回路で少なくとも1つの分周信号のデューティサイクルを調整することによって生成され得る(ブロック814)。

10

【0065】

[0059] 一設計では、少なくとも1つの分周回路は、第1及び第2のラッチを備え得る。ブロック812について、第1の分周信号が、第1のラッチで生成され得、第2の分周信号が、第2のラッチで生成され得る。一設計では、少なくとも1つのデューティサイクル調整回路は、第1及び第2のデューティサイクル調整回路を備え得る。ブロック814について、第1のデューティサイクル調整信号は、第1のデューティサイクル調整回路で生成され得る。第2のデューティサイクル調整信号は、第2のデューティサイクル調整回路で生成され得る。第1のデューティサイクル調整回路は、インバータを備え得る。第1のデューティサイクル調整信号は、インバータの調整可能なバイアス電流に基づいて決定される調整可能なデューティサイクルを有し得る。インバータのための調整可能なバイアス電流は、デューティサイクル制御信号に基づいて生成され得る。例えば、少なくとも1つの制御信号は、デューティサイクル制御信号に基づいて(例えば、図5で示されるようなルックアップテーブルで)生成され得る。次いで、インバータのための調整可能なバイアス電流は、少なくとも1つの制御信号に基づいて(例えば、図5で示されるようなバイアス電流生成器で)生成され得る。

20

【0066】

[0060] 当業者は、多種多様な技術及び技法のいずれかを使用して情報及び信号が表され得ることを理解するであろう。例えば、上記説明の全体にわたって参照され得るデータ、命令、コマンド、情報、信号、ピット、シンボル、及びチップは、電圧、電流、電磁波、磁場又は磁性粒子、光場又は光粒子、或いはこれらの任意の組み合わせによって表され得る。

30

【0067】

[0061] 当業者は、本明細書の開示に関連して説明された実例となる様々な論理ブロック、モジュール、回路、及びアルゴリズムのステップが、電子ハードウェア、コンピュータソフトウェア、又は両者の組み合わせとして実装され得ることを更に認識するだろう。このハードウェア及びソフトウェアの互換性を明確に例示するために、実例となる様々な構成要素、ブロック、モジュール、回路、及びステップが、概ねそれらの機能性の観点から上に説明されている。そのような機能性がハードウェアとして実装されるかソフトウェアとして実装されるかは、特定の用途とシステム全体に課される設計の制約とに依存する。当業者は、上述された機能性を特定の用途ごとに様々な方法で実装し得るが、このような実装の決定は本開示の範囲からの逸脱をさせるものとして解釈されるべきでない。

40

【0068】

[0062] 本明細書の開示に関連して説明された実例となる様々な論理ブロック、モジュール、及び回路は、汎用プロセッサ、デジタルシグナルプロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)又は他のプログラマブル論理デバイス、ディスクリートゲート又はトランジスタ論理、ディスクリートハードウェア構成要素、或いは本明細書で説明された機能を行うよう設計されたそれらの任意の組み合わせに実装されるか又はそれで行われ得る。汎用プロセッサは、マイクロプロセッサであり得るが、代替的に、プロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、又はステートマシンであり得る。プロセッサはまた、

50

コンピューティングデバイスの組み合わせ、例えば、D S Pと、1つのマイクロプロセッサ、複数のマイクロプロセッサ、D S Pコアに連結した1つ又は複数のマイクロプロセッサ、或いは任意の他のそのような構成との組み合わせとして実装され得る。

【0069】

[0063] 本明細書の開示に関する説明されたアルゴリズム又は方法のステップは、直接ハードウェアで、プロセッサによって実行されるソフトウェアモジュールで、又は両者の組み合わせで具現化され得る。ソフトウェアモジュールは、R A Mメモリ、フラッシュメモリ、R O Mメモリ、E P R O Mメモリ、E E P R O M(登録商標)メモリ、レジスター、ハードディスク、リムーバブルディスク、C D - R O M、又は当技術分野で知られている任意の他の形式の記憶媒体に存在し得る。例示的な記憶媒体は、プロセッサがこの記憶媒体から情報を読み取り、この記憶媒体に情報を書き込むことができるようプロセッサに結合される。代替的に、記憶媒体は、プロセッサに一体化され得る。プロセッサ及び記憶媒体はA S I C内に存在し得る。A S I Cはユーザ端末内に存在し得る。代替的に、プロセッサ及び記憶媒体は、ユーザ端末においてディスクリート構成要素として存在し得る。

10

【0070】

[0064] 1つ又は複数の例示的な設計では、説明された機能は、ハードウェアで、ソフトウェアで、ファームウェアで、又はそれらの任意の組み合わせで実装され得る。ソフトウェアで実装される場合、これら機能は、コンピュータ可読媒体において、1つ又は複数の命令又はコードとして、記憶又は送信され得る。コンピュータ可読媒体は、ある箇所から別の箇所へのコンピュータプログラムの移送を容易にする任意の媒体を含む通信媒体及びコンピュータ記憶媒体の両方を含む。記憶媒体は、汎用コンピュータ又は専用コンピュータによりアクセスすることができる任意の利用可能な媒体であり得る。限定ではなく例として、そのようなコンピュータ可読媒体は、R A M、R O M、E E P R O M、C D - R O M又は他の光ディスク記憶装置、磁気ディスク記憶装置又は他の磁気記憶デバイス、或いは、命令又はデータ構造の形式で所望のプログラムコード手段を搬送又は記憶するために使用されることができ、かつ、汎用コンピュータ又は専用コンピュータ或いは汎用プロセッサ又は専用プロセッサによってアクセスすることができる任意の他の媒体を備え得る。また、任意の接続は厳密にはコンピュータ可読媒体と称される。例えば、ソフトウェアが、ウェブサイト、サーバ、又は他のリモートソースから、同軸ケーブル、光ファイバーケーブル、ツイストペア、デジタル加入者回線(D S L)、又は赤外線、電波、及びマイクロ波のようなワイヤレス技術を使用して送信される場合、同軸ケーブル、光ファイバーケーブル、ツイストペア、D S L、又は赤外線、電波、及びマイクロ波のようなワイヤレス技術は、媒体の定義に含まれる。本明細書で使用される場合、ディスク(disk)及びディスク(disc)は、コンパクトディスク(C D)、レーザー(登録商標)ディスク、光ディスク、デジタル多用途ディスク(D V D)、フロッピー(登録商標)ディスク、及びブルーレイ(登録商標)ディスクを含み、ここで、ディスク(disk)は、通常磁気的にデータを再生し、ディスク(disc)は、レーザーを用いて光学的にデータを再生する。上記の組み合わせもまた、コンピュータ可読媒体の範囲内に含まれるべきである。

20

【0071】

[0065] 本開示の先の説明は、当業者が本開示を実行又は使用することを可能にするために提供される。本開示に対する様々な修正は当業者には容易に明らかとなり、本明細書で定義された包括的な原理は、本開示の精神又は範囲から逸脱することなく、他の変形に適用され得る。このように、本開示は、本明細書で説明された例及び設計に限られることを意図せず、本明細書に開示された原理及び新しい特徴に合致する最も広い範囲が与えられるべきである。

30

40

【図1】

図1

FIG. 1

【図2A】

図2A

FIG. 2A

【図2B】

図2B

FIG. 2B

【図3】

図3

FIG. 3

【 図 4 】

## 【図5】

FIG. 4

FIG. 5

【 図 6 】

FIG. 6

【 四 7 】

FIG. 7

## 【図8】

図8

FIG. 8

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                             | International application No<br>PCT/US2014/042920                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>INV. H03K3/017 H03K5/156 H03K21/08<br>ADD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                             |                                                                      |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                             |                                                                      |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>H03K H03L H03B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                             |                                                                      |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                             |                                                                      |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>EPO-Internal, WPI Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                             |                                                                      |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                             |                                                                      |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Citation of document, with indication, where appropriate, of the relevant passages                                                          | Relevant to claim No.                                                |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 2013/015891 A1 (CICALINI ALBERTO [US])<br>17 January 2013 (2013-01-17)                                                                   | 1-3,<br>7-13,<br>17-19,21                                            |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | abstract<br>paragraphs [0002], [0003], [0008],<br>[0016], [0021], [0029], [0030].<br>[0058]; figures 1,2<br>-----                           | 4,14-16,<br>20                                                       |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | EP 2 056 459 A1 (AUSTRIAMICROSYSTEMS AG<br>[AT]) 6 May 2009 (2009-05-06)                                                                    | 1-3,<br>7-13,<br>17-19,22                                            |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | abstract; figures 1,3-5<br>paragraphs [0002], [0004], [0005],<br>[0009], [0021], [0022], [0035],<br>[0042], [0046], [0047], [0050]<br>----- | 4,14-16,<br>20,21                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                             | -/-                                                                  |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                             | <input checked="" type="checkbox"/> See patent family annex.         |

| * Special categories of cited documents :<br>*A* document defining the general state of the art which is not considered to be of particular relevance<br>*E* earlier application or patent but published on or after the international filing date<br>*L* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>*O* document referring to an oral disclosure, use, exhibition or other means<br>*P* document published prior to the international filing date but later than the priority date claimed                                                                  |                                                                                                                                             |                                                                      |

| *T* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention<br>*X* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone<br>*Y* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art<br>*&* document member of the same patent family |                                                                                                                                             |                                                                      |

| Date of the actual completion of the international search<br><br>15 September 2014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                             | Date of mailing of the international search report<br><br>22/09/2014 |

| Name and mailing address of the ISA/<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                             | Authorized officer<br><br>Mesic, Maté                                |

## INTERNATIONAL SEARCH REPORT

|                              |

|------------------------------|

| International application No |

| PCT/US2014/042920            |

| C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                                                 |                                                    |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Category*                                            | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                              | Relevant to claim No.                              |

| A                                                    | US 6 198 322 B1 (YOSHIMURA TSUTOMU [JP])<br>6 March 2001 (2001-03-06)<br>abstract; figures 3,13,14<br>-----                                                                                                                     | 1-9,<br>11-22                                      |

| A                                                    | WO 2007/146590 A2 (QUALCOMM INC [US]; DAI LIANG [US]; NGUYEN LAM V [US])<br>21 December 2007 (2007-12-21)<br>abstract; figures 1,2,8,9<br>paragraphs [0005], [0021], [0022],<br>[0045], [0060], [0064], [0069], [0070]<br>----- | 1-5,7-9,<br>11-22                                  |

| X,P                                                  | US 2013/187686 A1 (YUAN MIN-SHUEH [TW] ET AL) 25 July 2013 (2013-07-25)<br>abstract; figures 2,3a,4a,4b<br>paragraph [0002]<br>-----                                                                                            | 1-3,7-9,<br>11-13,<br>17-19,22<br>4,5,14,<br>20,21 |

| A,P                                                  |                                                                                                                                                                                                                                 |                                                    |

## INTERNATIONAL SEARCH REPORT

## Information on patent family members

|                              |

|------------------------------|

| International application No |

| PCT/US2014/042920            |

| Patent document cited in search report |    | Publication date | Patent family member(s)                                                                                  | Publication date                                                                 |

|----------------------------------------|----|------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| US 2013015891                          | A1 | 17-01-2013       | US 2013015891 A1<br>WO 2013012755 A1                                                                     | 17-01-2013<br>24-01-2013                                                         |

| EP 2056459                             | A1 | 06-05-2009       | AT 554529 T<br>EP 2056459 A1<br>JP 5005821 B2<br>JP 2011501547 A<br>US 2011044424 A1<br>WO 2009050039 A2 | 15-05-2012<br>06-05-2009<br>22-08-2012<br>06-01-2011<br>24-02-2011<br>23-04-2009 |

| US 6198322                             | B1 | 06-03-2001       | JP 3745123 B2<br>JP 2000068797 A<br>US 6198322 B1                                                        | 15-02-2006<br>03-03-2000<br>06-03-2001                                           |

| WO 2007146590                          | A2 | 21-12-2007       | US 2007290730 A1<br>WO 2007146590 A2                                                                     | 20-12-2007<br>21-12-2007                                                         |

| US 2013187686                          | A1 | 25-07-2013       | NONE                                                                                                     |                                                                                  |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,R,S,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,H,R,HU,ID,IL,IN,IR,IS,JP,KE,KG,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US

(72)発明者 チェン、ウ - シン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 スリダーラ、スリランゴバル

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 リウ、リ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

【要約の続き】

で結合され得、2分周を行い得る。

【選択図】図3