(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2010년10월18일

(11) 등록번호 10-0988690

(24) 등록일자 2010년10월12일

(51) Int. Cl.

H01L 27/10 (2006.01)

(21) 출원번호 10-2003-0053000

(22) 출원일자 2003년07월31일

심사청구일자 2008년07월09일

(65) 공개번호 10-2004-0012564

(43) 공개일자 2004년02월11일

### (30) 우선권주장

JP-P-2002-00224254 2002년07월31일 일본(JP)

JP-P-2003-00097210 2003년03월31일 일본(IP)

### (56) 서해기숙조사문현

卷二十一

JP10107280 A

JP10027905 A

JP06069512 A

JP08111526 A

전체 청구항 수 : 총 23 항

### (54) 반도체 기억 장치

### (57) 요약

구동 MISFET 및 전송 MISFET의 상부에는 종형 MISFET이 형성되어 있다. 종형 MISFET은 하부 반도체층(드레인), 중간 반도체층, 상부 반도체층(소스)을 적층한 4각 기동형의 적층체( $P_1$ ,  $P_2$ )와, 이 적층체( $P_1$ ,  $P_2$ )의 측벽에 게이트 절연막을 개재하여 형성된 게이트 전극에 의해 구성되어 있다. 종형 MISFET은 하부 반도체층이 드레인을 구성하고, 중간 반도체층이 기판(채널 영역)을 구성하며, 상부 반도체층이 소스를 구성하고 있다. 하부 반도체층, 중간 반도체층, 상부 반도체층 각각은 실리콘막으로 구성되며, 하부 반도체층 및 상부 반도체층은 p형으로 도핑되어 p형 실리콘으로 구성된다.

## 대 표 도

(72) 발명자

**모니와마사히로**

일본도쿄도지요다꾸마루노우찌1-5-1신마루노우찌빌

딩히타치세이사쿠쇼지적재산권본부내

**미즈노마코또**

일본도쿄도지요다꾸마루노우찌1-5-1신마루노우찌빌

딩히타치세이사쿠쇼지적재산권본부내

**오까모또케이지**

일본도쿄도고다이라시조스이혼초5조메22-1가부시키

가이샤히타치초엘에스아이시스템즈내

**노구찌미쓰히로**

일본도쿄도지요다꾸마루노우찌1-5-1신마루노우찌빌

딩히타치세이사쿠쇼지적재산권본부내

---

**요시다다다노리**

일본도쿄도지요다꾸마루노우찌1-5-1신마루노우찌빌

딩히타치세이사쿠쇼지적재산권본부내

**다까하시야스히코**

일본도쿄도지요다꾸마루노우찌1-5-1신마루노우찌빌

딩히타치세이사쿠쇼지적재산권본부내

**니시다아끼오**

일본도쿄도지요다꾸마루노우찌1-5-1신마루노우찌빌

딩히타치세이사쿠쇼지적재산권본부내

## 특허청구의 범위

### 청구항 1

한쌍의 상보성 데이터선과 워드선과의 교차부에 배치된 제1 및 제2 전송 MISFET과, 제1 및 제2 구동 MISFET과, 제1 및 제2 종형 MISFET을 구비하고, 상기 제1 구동 MISFET 및 상기 제1 종형 MISFET과, 상기 제2 구동 MISFET 및 상기 제2 종형 MISFET이 교차 결합된 메모리 셀을 갖는 반도체 기억 장치로서,

상기 제1 및 제2 전송 MISFET과, 상기 제1 및 제2 구동 MISFET은 반도체 기판의 주면에 형성되고,

상기 제1 및 제2 종형 MISFET은 상기 제1 및 제2 전송 MISFET과, 상기 제1 및 제2 구동 MISFET 각각보다도 상부에 형성되며,

상기 제1 종형 MISFET은 상기 반도체 기판의 주면에 수직인 방향으로 연장되는 제1 적층체에 형성된 소스, 채널 영역 및 드레인과, 상기 제1 적층체의 측벽부에 게이트 절연막을 개재하여 형성된 게이트 전극을 가지며,

상기 제2 종형 MISFET은 상기 반도체 기판의 주면에 수직인 방향으로 연장되는 제2 적층체에 형성된 소스, 채널 영역 및 드레인과, 상기 제2 적층체의 측벽부에 게이트 절연막을 개재하여 형성된 게이트 전극을 가지고,

상기 제1 및 제2 종형 MISFET 각각의 소스는 상기 제1 및 제2 적층체보다도 상부에 형성된 전원 전압선에 전기적으로 접속되어 있는 것을 특징으로 하는 반도체 기억 장치.

### 청구항 2

제1항에 있어서,

상기 제1 전송 MISFET의 소스, 드레인의 한쪽에 전기적으로 접속되는 상기 상보성 데이터선의 한쪽과, 상기 제2 전송 MISFET의 소스, 드레인의 한쪽에 전기적으로 접속되는 상기 상보성 데이터선의 다른 쪽은 상기 전원 전압선과 동일한 배선층에 형성되어 있는 것을 특징으로 하는 반도체 기억 장치.

### 청구항 3

제1항에 있어서,

상기 제1 및 제2 전송 MISFET 각각의 게이트 전극에 전기적으로 접속되는 상기 워드선은 상기 전원 전압선 및 상기 상보성 데이터선보다도 상층의 배선층에 형성되어 있는 것을 특징으로 하는 반도체 기억 장치.

### 청구항 4

제1항에 있어서,

상기 제1 및 제2 구동 MISFET 각각의 소스에 전기적으로 접속되는 기준 전압선은 상기 워드선과 동일한 배선층에 형성되어 있는 것을 특징으로 하는 반도체 기억 장치.

### 청구항 5

제4항에 있어서,

상기 기준 전압선은 상기 제1 구동 MISFET의 소스에 전기적으로 접속되는 제1 기준 전압선과, 상기 제2 구동 MISFET의 소스에 전기적으로 접속되는 제2 기준 전압선으로 이루어지며, 제1 기준 전압선과 상기 제2 기준 전압선은 상기 워드선을 이들 사이에 협지하여서 제1 방향으로 연장되어 있는 것을 특징으로 하는 반도체 기억 장치.

### 청구항 6

제5항에 있어서,

상기 상보성 데이터선의 한쪽과, 상기 상보성 데이터선의 다른 쪽은 상기 전원 전압선을 이들 사이에 협지하여, 상기 제1 방향과 교차하는 제2 방향으로 연장되어 있는 것을 특징으로 하는 반도체 기억 장치.

**청구항 7**

제4항에 있어서,

상기 상보성 데이터선, 상기 전원 전압선, 상기 기준 전압선 및 상기 워드선은 구리를 포함하는 메탈막으로 구성되어 있는 것을 특징으로 하는 반도체 기억 장치.

**청구항 8**

한쌍의 상보성 데이터선과 워드선과의 교차부에 배치된 제1 및 제2 전송 MISFET과, 제1 및 제2 구동 MISFET과, 제1 및 제2 종형 MISFET을 구비하며, 상기 제1 구동 MISFET 및 상기 제1 종형 MISFET과, 상기 제2 구동 MISFET 및 상기 제2 종형 MISFET이 교차 결합된 메모리 셀을 갖는 반도체 기억 장치로서,

상기 제1 및 제2 전송 MISFET과, 상기 제1 및 제2 구동 MISFET은 반도체 기판의 주면에 형성되며,

상기 제1 종형 MISFET은 상기 제2 구동 MISFET의 게이트 전극의 일단부 상에 배치되며, 상기 반도체 기판의 주면에 수직인 방향으로 연장되는 제1 적층체에 형성된 소스, 채널 영역 및 드레인과, 상기 제1 적층체의 측벽부에 게이트 절연막을 개재하여 형성된 게이트 전극을 가지고,

상기 제2 종형 MISFET은 상기 제1 구동 MISFET의 게이트 전극의 일단부 상에 배치되며, 상기 반도체 기판의 주면에 수직인 방향으로 연장되는 제2 적층체에 형성된 소스, 채널 영역 및 드레인과, 상기 제2 적층체의 측벽부에 게이트 절연막을 개재하여 형성된 게이트 전극을 갖는 것을 특징으로 하는 반도체 기억 장치.

**청구항 9**

제8항에 있어서,

상기 반도체 기판의 주면에 평행한 평면에서, 평면적으로 볼 때, 상기 제1 및 제2 종형 MISFET은 상기 제1 전송 MISFET 및 상기 제1 구동 MISFET 형성 영역과, 상기 제2 전송 MISFET 및 상기 제2 구동 MISFET 형성 영역 사이에 배치되어 있는 것을 특징으로 하는 반도체 기억 장치.

**청구항 10**

한쌍의 상보성 데이터선과 워드선과의 교차부에 배치된 제1 및 제2 전송 MISFET과, 제1 및 제2 구동 MISFET과, 제1 및 제2 종형 MISFET을 구비하며, 상기 제1 구동 MISFET 및 상기 제1 종형 MISFET과, 상기 제2 구동 MISFET 및 상기 제2 종형 MISFET이 교차 결합된 메모리 셀을 갖는 반도체 기억 장치로서,

상기 제1 및 제2 전송 MISFET과, 상기 제1 및 제2 구동 MISFET은 반도체 기판의 주면에 형성되고,

상기 제1 및 제2 종형 MISFET은 상기 제1 및 제2 전송 MISFET과, 상기 제1 및 제2 구동 MISFET 각각보다도 상부에 형성되며,

상기 제1 종형 MISFET은 상기 반도체 기판의 주면에 수직인 방향으로 연장되는 제1 적층체에 형성된 소스, 채널 영역 및 드레인과, 상기 제1 적층체의 측벽부에 게이트 절연막을 개재하여 형성된 제1 게이트 전극을 가지며,

상기 제2 종형 MISFET은 상기 반도체 기판의 주면에 수직인 방향으로 연장되는 제2 적층체에 형성된 소스, 채널 영역 및 드레인과, 상기 제2 적층체의 측벽부에 게이트 절연막을 개재하여 형성된 제2 게이트 전극을 가지고,

상기 제1 종형 MISFET의 드레인과, 상기 제2 구동 MISFET의 게이트 전극과, 상기 제1 구동 MISFET의 드레인은 제1 중간 도전층을 개재하여 상호 전기적으로 접속되며,

상기 제2 종형 MISFET의 드레인과, 상기 제1 구동 MISFET의 게이트 전극과, 상기 제2 구동 MISFET의 드레인은 제2 중간 도전층을 개재하여 상호 전기적으로 접속되고,

상기 제1 종형 MISFET의 제1 게이트 전극은 상기 제1 게이트 전극과 접하도록 형성된 제1 게이트 인출 전극과, 상기 제1 게이트 인출 전극 및 상기 제2 중간 도전층과 접하도록 형성된 제1 접속 구멍 내의 제1 도전층을 개재하여 상기 제2 중간 도전층과 전기적으로 접속되며,

상기 제2 종형 MISFET의 제2 게이트 전극은 상기 제2 게이트 전극과 접하도록 형성된 제2 게이트 인출 전극과, 상기 제2 게이트 인출 전극 및 상기 제1 중간 도전층과 접하도록 형성된 제2 접속 구멍 내의 제2 도전층을 개재하여 상기 제1 중간 도전층과 전기적으로 접속되어 있는 것을 특징으로 하는 반도체 기억 장치.

### 청구항 11

제10항에 있어서,

상기 반도체 기판의 주변에 주변 회로의 복수의 MISFET이 더 형성되며, 상기 주변 회로의 MISFET 간을 접속하는 배선과, 상기 제1 및 제2 중간 도전층은 동일한 배선층에 형성되어 있는 것을 특징으로 하는 반도체 기억 장치.

### 청구항 12

제10항에 있어서,

상기 제1 및 제2 중간 도전층은 메탈막으로 이루어지며, 상기 제1 종형 MISFET의 드레인과 상기 제1 중간 도전층과의 사이에 제1 배리어층이 형성되고, 상기 제2 종형 MISFET의 드레인과 상기 제2 중간 도전층과의 사이에 제2 배리어층이 형성되어 있는 것을 특징으로 하는 반도체 기억 장치.

### 청구항 13

제12항에 있어서,

상기 제1 및 제2 중간 도전층은 텅스텐막으로 이루어지며, 상기 제1 및 제2 배리어층은 질화 텅스텐(WN)막으로 이루어진 것을 특징으로 하는 반도체 기억 장치.

### 청구항 14

제10항에 있어서,

상기 제1 및 제2 중간 도전층은 내 산화성 도전막으로 이루어진 것을 특징으로 하는 반도체 기억 장치.

### 청구항 15

제10항에 있어서,

상기 제1 종형 MISFET의 제1 게이트 전극은 그 하단부에서 상기 제1 게이트 인출 전극과 전기적으로 접속되며, 상기 제2 종형 MISFET의 제2 게이트 전극은 그 하단부에서 상기 제2 게이트 인출 전극과 전기적으로 접속되어 있는 것을 특징으로 하는 반도체 기억 장치.

### 청구항 16

제10항에 있어서,

상기 제1 종형 MISFET의 제1 게이트 전극 및 상기 제2 종형 MISFET의 제2 게이트 전극 각각은 2층의 도전막으로 구성되어 있는 것을 특징으로 하는 반도체 기억 장치.

### 청구항 17

제10항에 있어서,

상기 제2 중간 도전층과, 상기 제1 게이트 인출 전극과, 상기 제1 접속 구멍은 상호 평면적으로 중첩되는 부분을 갖도록 배치되며, 상기 제1 중간 도전층과, 상기 제2 게이트 인출 전극과, 상기 제2 접속 구멍은 상호 평면적으로 중첩되는 부분을 갖도록 배치되어 있는 것을 특징으로 하는 반도체 기억 장치.

### 청구항 18

제10항에 있어서,

상기 제1 접속 구멍은 상기 제1 게이트 인출 전극을 관통하여 상기 제2 중간 도전층에 접속되며, 상기 제2 접속 구멍은 상기 제2 게이트 인출 전극을 관통하여 상기 제1 중간 도전층에 접속되어 있는 것을 특징으로 하는 반도체 기억 장치.

### 청구항 19

제10항에 있어서,

상기 제1 게이트 인출 전극은 상기 제1 적층체의 측벽부에서 상기 제1 종형 MISFET의 제1 게이트 전극과 접하여 있고, 상기 제2 게이트 인출 전극은 상기 제2 적층체의 측벽부에서 상기 제2 종형 MISFET의 제2 게이트 전극과 접하여 있는 것을 특징으로 하는 반도체 기억 장치.

#### 청구항 20

제10항에 있어서,

상기 제1 게이트 인출 전극은 상기 제1 종형 MISFET의 제1 게이트 전극과 일체로 구성되어 있고, 상기 제2 게이트 인출 전극은 상기 제2 종형 MISFET의 제2 게이트 전극과 일체로 구성되어 있는 것을 특징으로 하는 반도체 기억 장치.

#### 청구항 21

제10항에 있어서,

상기 제1 종형 MISFET의 게이트 전극은 상기 제1 적층체의 측벽부의 주위를 둘러싸도록 형성되어, 상기 제2 종형 MISFET의 게이트 전극은 상기 제2 적층체의 측벽부의 주위를 둘러싸도록 형성되어 있는 것을 특징으로 하는 반도체 기억 장치.

#### 청구항 22

제10항에 있어서,

상기 제1 및 제2 게이트 인출 전극은 실리콘계의 도전막과 그 표면에 형성된 실리사이드막으로 구성되어 있는 것을 특징으로 하는 반도체 기억 장치.

#### 청구항 23

제1항에 있어서,

상기 제1 및 제2 전송 MISFET과, 상기 제1 및 제2 구동 MISFET은 n채널형 MISFET로 구성되어, 상기 제1 및 제2 종형 MISFET은 p채널형 MISFET로 구성되어 있는 것을 특징으로 하는 반도체 기억 장치.

#### 청구항 24

삭제

#### 청구항 25

삭제

#### 청구항 26

삭제

#### 청구항 27

삭제

#### 청구항 28

삭제

#### 청구항 29

삭제

#### 청구항 30

삭제

청구항 31

삭제

청구항 32

삭제

청구항 33

삭제

청구항 34

삭제

청구항 35

삭제

청구항 36

삭제

청구항 37

삭제

청구항 38

삭제

청구항 39

삭제

청구항 40

삭제

청구항 41

삭제

청구항 42

삭제

청구항 43

삭제

청구항 44

삭제

청구항 45

삭제

청구항 46

삭제

청구항 47

삭제

청구항 48

삭제

청구항 49

삭제

청구항 50

삭제

청구항 51

삭제

청구항 52

삭제

청구항 53

삭제

청구항 54

삭제

청구항 55

삭제

청구항 56

삭제

청구항 57

삭제

청구항 58

삭제

청구항 59

삭제

청구항 60

삭제

청구항 61

삭제

청구항 62

삭제

청구항 63

삭제

청구항 64

삭제

청구항 65

삭제

청구항 66

삭제

청구항 67

삭제

청구항 68

삭제

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

[0217] 본 발명은 반도체 기억 장치 및 그 제조 기술, 종형 MISFET의 제조 방법 및 종형 MISFET, 반도체 장치의 제조 방법 및 반도체 장치에 관한 것으로, 특히, 메모리 셀을 종형 MISFET을 이용하여 구성한 SRAM(Static Random Access Memory)을 갖는 반도체 기억 장치에 적용할 때 유효한 기술에 관한 것이다.

[0218] 범용의 대용량 반도체 기억 장치의 일종인 SRAM(Static Random Access Memory)은 예를 들면, 4개의 n채널형 MISFET(Metal-Insulator-Semiconductor-Fiel d-Effect-Transistor)과 2개의 p채널형 MISFET으로 메모리 셀을 구성하고 있다. 그러나, 이러한 종류의 소위 완전 CMOS(Complementary-Metal-Oxide-Semiconductor)형 SRAM은 반도체 기판의 주면에 6개의 MISFET을 평면적으로 배치하기 때문에, 메모리 셀 사이즈의 축소가 곤란하다. 즉, CMOS를 형성하기 위한 p형 및 n형 웨이 영역 및 n채널형 MISFET과 p채널형 MISFET을 분리한 웨이 영역이 필요하게 되는 완전 CMOS형 SRAM은 메모리 셀 사이즈의 축소가 곤란하다.

#### 발명이 이루고자 하는 기술적 과제

[0219] 따라서, 6개의 MISFET으로 구성된 SRAM 셀에 대하여, 예를 들면, 미국특허 제5,364,810호의 대응일본출원인 특개평8-88328호 공보에 기재된 바와 같이, 메모리 셀을 구성하는 MISFET의 일부를 홈의 측벽에 채널부를 형성하고, 홈을 매립하도록 게이트를 형성한 MISFET을 이용하여 구성함으로써, 메모리 셀 사이즈의 축소를 도모하는 기술이 제안되고 있지만, 이 경우, 홈을 매립하도록 형성된 게이트는 MISFET 위를 절연막을 개재하여 패터닝에 의해 형성된 도전막으로 구성되며, 또한 다른 MISFET에 접속되기 때문에 포토리소그래피를 위한 정렬 마진을 포함한 스페이스를 필요로 하여, 메모리 셀 사이즈가 증대된다.

[0220] 또한, 예를 들면 미국특허 제5,550,396호의 대응일본출원인 특개평5-206394호 공보에 기재된 바와 같이 4개의 n 채널형 MISFET과 2개의 p채널형 MISFET을 반도체 기판 상에 나란히 배치하는 완전 CMOS형 SRAM의 경우는 트랜지스터 6 개분의 스페이스를 필요로 하여, 메모리 셀 사이즈가 증대됨과 함께 제조 공정이 복잡해진다.

[0221] 또한, 종형 트랜지스터에 대해서는 예를 들면, 미국특허 제6,060,723호의 대응일본출원인 특개평11-87541호 공보에 기재되어 있다. 이 공보에 도시된 바와 같이, 종형 트랜지스터의 소스, 드레인 및 게이트는 종형 트랜지스터를 덮는 절연막에 형성된 접속 구멍을 통해 절연막 상에 형성된 금속 배선층에 전기적으로 접속된다.

[0222] 본 발명자는 이러한 종류의 종형 트랜지스터를 검토한 결과, 이 종형 트랜지스터에서는 소스, 드레인 및 게이트를 금속 배선층에 접속하기 위해서 기판의 주면과 평행한 평면에 배치하기 때문에, 그 연장 방향에 각각의 영역이 필요해지고, 또한 종형 트랜지스터에 접속된 금속 배선층의 배치 등의 영역이 필요해져서, 트랜지스터 사이즈가 증대될 우려가 있다는 것을 발견하였다.

[0223] 본 발명의 목적은 SRAM 메모리 셀 사이즈를 축소할 수 있는 기술을 제공하는 것에 있다.

[0224] 본 발명의 상기 및 그 밖의 목적과 신규의 특징은 본 명세서의 기술 및 첨부 도면에서 분명해질 것이다.

### 발명의 구성 및 작용

[0225] 본원에서 개시되는 발명 중, 대표적인 것의 개요에 대하여 설명하면, 다음과 같다.

[0226] 본 발명의 반도체 기억 장치는, 한 쌍의 상보성 데이터선과 워드선과의 교차부에 배치된 제1 및 제2 전송 MISFET과, 제1 및 제2 구동 MISFET과, 제1 및 제2 종형 MISFET을 구비하며, 상기 제1 구동 MISFET 및 상기 제1 종형 MISFET과, 상기 제2 구동 MISFET 및 상기 제2 종형 MISFET이 교차 결합된 메모리 셀을 가지고,

[0227] 상기 제1 및 제2 전송 MISFET과, 상기 제1 및 제2 구동 MISFET은 반도체 기판의 주면에 형성되고,

[0228] 상기 제1 및 제2 종형 MISFET은 상기 제1 및 제2 전송 MISFET과, 상기 제1 및 제2 구동 MISFET 각각보다도 상부에 형성되며, 상기 제1 종형 MISFET은 상기 반도체 기판의 주면에 수직인 방향으로 연장되는 제1 적층체에 형성된 소스, 채널 영역 및 드레인과, 상기 제1 적층체의 측벽부에 게이트 절연막을 개재하여 형성된 제1 게이트 전극을 가지며,

[0229] 상기 제2 종형 MISFET은 상기 반도체 기판의 주면에 수직인 방향으로 연장되는 제2 적층체에 형성된 소스, 채널 영역 및 드레인과, 상기 제2 적층체의 측벽부에 게이트 절연막을 개재하여 형성된 제2 게이트 전극을 가지고,

[0230] 상기 제1 종형 MISFET의 소스와, 상기 제2 구동 MISFET의 게이트 전극과, 상기 제1 구동 MISFET의 드레인은 제1 중간 도전층을 개재하여 상호 전기적으로 접속되며,

[0231] 상기 제2 종형 MISFET의 소스와, 상기 제1 구동 MISFET의 게이트 전극과, 상기 제2 구동 MISFET의 드레인은 제2 중간 도전층을 개재하여 상호 전기적으로 접속되고,

[0232] 상기 제1 종형 MISFET의 제1 게이트 전극은 상기 제1 게이트 전극과 접하도록 형성된 제1 게이트 인출 전극과, 상기 제1 게이트 인출 전극 및 상기 제2 중간 도전층에 접하도록 형성된 제1 접속 구멍 내의 제1 도전층을 개재하여 상기 제2 중간 도전층과 전기적으로 접속되며,

[0233] 상기 제2 종형 MISFET의 제2 게이트 전극은 상기 제2 게이트 전극과 접하도록 형성된 제2 게이트 인출 전극과, 상기 제2 게이트 인출 전극 및 상기 제1 중간 도전층과 접하도록 형성된 제2 접속 구멍 내의 제2 도전층을 개재하여 상기 제1 중간 도전층과 전기적으로 접속되어 있는 것이다.

[0234] 또한, 상기 반도체 기억 장치는 예를 들면, 하기의 공정 (a)~(f)에 의해 제조된다.

[0235] (a) 반도체 기판의 주면의 제1 영역에 제1 및 제2 전송 MISFET과, 제1 및 제2 구동 MISFET을 형성하는 공정,

[0236] (b) 상기 제1 및 제2 전송 MISFET과 상기 제1 및 제2 구동 MISFET의 상부에, 상기 제2 구동 MISFET의 게이트 전극과, 상기 제1 구동 MISFET의 드레인을 전기적으로 접속하는 제1 중간 도전층을 형성하며, 상기 제1 구동 MISFET의 게이트 전극과, 상기 제2 구동 MISFET의 드레인을 전기적으로 접속하는 제2 중간 도전층을 형성하는 공정,

[0237] (c) 상기 제1 및 제2 중간 도전층의 상부에 제1 절연막을 개재하여 제1 및 제2 게이트 인출 전극을 형성하는 공정,

[0238] (d) 상기 (c) 공정 이후, 상기 제1 및 제2 게이트 인출 전극의 상부에 제1 및 제2 적층체를 형성함으로써, 상기 제1 적층체에 형성된 제1 종형 MISFET의 드레인과 상기 제1 중간 도전층을 전기적으로 접속하며, 상기 제2 적층체에 형성된 제2 종형 MISFET의 드레인과 상기 제2 중간 도전층을 전기적으로 접속하는 공정,

[0239] (e) 상기 제1 적층체의 측벽부에 게이트 절연막을 개재하여 형성된 상기 제1 종형 MISFET의 게이트 전극과 상기 제1 게이트 인출 전극을 전기적으로 접속하고, 상기 제2 적층체의 측벽부에 게이트 절연막을 개재하여 형성된 상기 제2 종형 MISFET의 게이트 전극과 상기 제2 게이트 인출 전극을 전기적으로 접속하는 공정, 및

[0240] (f) 상기 제1 게이트 인출 전극의 상부에, 상기 제1 게이트 인출 전극과 상기 제2 중간 도전층에 접하도록 제1 접속 구멍을 형성하여 그 내부에 제1 도전층을 매립하고, 상기 제2 게이트 인출 전극의 상부에, 상기 제2 게이트 인출 전극과 상기 제1 중간 도전층에 접하도록 제2 접속 구멍을 형성하여 그 내부에 제2 도전층을 매립하는 공정.

[0241] <발명의 실시예>

[0242] 이하, 본 발명의 실시예를 도면에 기초하여 상세히 설명한다. 또, 실시예를 설명하기 위한 전체 도면에서, 동일한 기능을 갖는 부재에는 동일한 부호를 붙여서, 그 반복되는 설명은 생략한다.

[0243] (실시예 1)

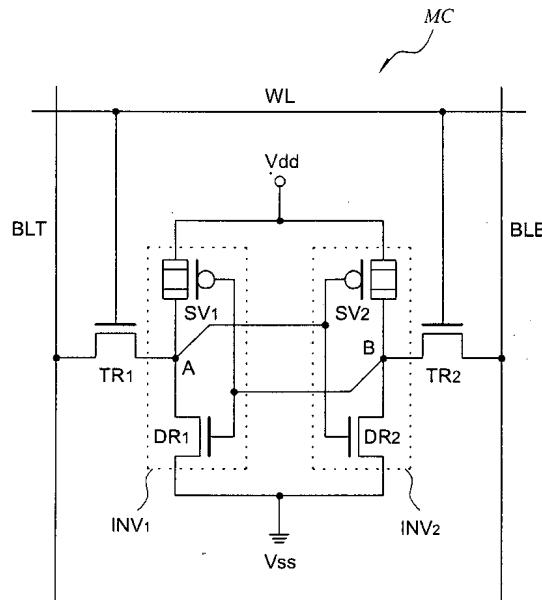

[0244] 도 1은 본 발명의 일 실시예인 SRAM 메모리 셀의 등가 회로도이다. 도 1에 도시한 바와 같이, 이 SRAM 메모리 셀(MC)은, 한 쌍의 상보성 데이터선(BLT, BLB)과 워드선(WL)과의 교차부에 배치된 2개의 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>), 2개의 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>) 및 2개의 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)에 의해 구성되어 있다.

[0245] 메모리 셀(MC)을 구성하는 상기 6개의 MISFET 중, 2개의 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>) 및 2개의 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>)은 n채널형 MISFET으로 구성되어 있다. 또한, 2개의 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)은 p채널형 MISFET으로 구성되어 있다. 이 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)은 주지의 완전 CMOS형 SRAM에서의 부하 MISFET에 상당하는 것이지만, 통상의 부하 MISFET과는 달리, 후술하는 종형 구조로 구성되어 있고, 또한 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>) 및 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>) 형성 영역의 상부에 배치되어 있다.

[0246] 메모리 셀(MC)의 구동용 MISFET(DR<sub>1</sub>) 및 종형 MISFET(SV<sub>1</sub>)은 제1 인버터(INV<sub>1</sub>)를 구성하고, 구동용 MISFET(DR<sub>2</sub>) 및 종형 MISFET(SV<sub>2</sub>)는 제2 인버터 INV<sub>2</sub>를 구성하고 있다. 이를 한쌍의 인버터(INV<sub>1</sub>, INV<sub>2</sub>)는 메모리 셀(MC) 내에서 교차 결합되어, 1비트의 정보를 기억하는 정보 축적부로서의 플립플롭 회로를 구성하고 있다.

[0247] 즉, 구동용 MISFET(DR<sub>1</sub>)의 드레인과, 종형 MISFET(SV<sub>1</sub>)의 드레인과, 구동용 MISFET(DR<sub>2</sub>)의 게이트와, 종형 MISFET(SV<sub>2</sub>)의 게이트는 상호 전기적으로 접속되어, 메모리 셀의 한쪽의 축적 노드(A)를 구성한다. 구동용 MISFET(DR<sub>2</sub>)의 드레인과, 종형 MISFET(SV<sub>2</sub>)의 드레인과, 구동용 MISFET(DR<sub>1</sub>)의 게이트와, 종형 MISFET(SV<sub>1</sub>)의 게이트는 상호 전기적으로 접속되어, 메모리 셀의 다른 쪽의 축적 노드(B)를 구성한다.

[0248] 상기 플립플롭 회로의 한쪽의 입출력 단자는 전송 MISFET(TR<sub>1</sub>)의 소스, 드레인의 한쪽에 전기적으로 접속되며, 또한 한쪽의 입출력 단자는 전송 MISFET(TR<sub>2</sub>)의 소스, 드레인의 한쪽에 전기적으로 접속되어 있다. 전송 MISFET(TR<sub>1</sub>)의 소스, 드레인의 다른 쪽은 한 쌍의 상보성 데이터선 내의 한쪽의 데이터선(BLT)에 전기적으로 접속되며, 전송 MISFET(TR<sub>2</sub>)의 소스, 드레인의 다른 쪽은 한 쌍의 상보성 데이터선 내의 다른 쪽의 데이터선(BL B)에 전기적으로 접속되어 있다. 또한, 플립플롭 회로의 일단, 즉 2개의 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 소스는 기준 전압(V<sub>ss</sub>)보다도 전위가 높은 예를 들면, 3V의 전원 전압(V<sub>dd</sub>)을 공급하는 전원 전압선(V<sub>dd</sub>)에 전기적으로 접속되며, 타단 즉, 2개의 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>)의 소스는 예를 들면, 0V의 기준 전압(V<sub>ss</sub>)을 공급하는 기준 전압선(V<sub>ss</sub>)에 전기적으로 접속되어 있다. 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>)의 게이트 전극은 워드선(WL)에 전기적으로 접속되어 있다. 상기 메모리 셀(MC)은 한 쌍의 축적 노드(A, B)의 한쪽을 High, 다른 쪽을 Low로 함으로써 정보를 기억한다.

[0249] 상기 메모리 셀(MC)에서의 정보의 유지, 판독 및 기입 동작은 주지의 완전 CMOS형 SRAM의 동작과 기본적으로 동일하다. 즉, 정보의 판독 시에는 선택된 워드선(WL)에, 예를 들면, 전원 전압(V<sub>dd</sub>)을 인가하고, 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>)를 ON으로 하여 한쌍의 축적 노드(A, B)의 전위차를 상보성 데이터선(BLT, BLB)에서 판독한다. 또한, 기입 시에는 선택된 워드선(WL)에, 예를 들면, 전원 전압(V<sub>dd</sub>)을 인가하고, 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>)을 ON으로 함과 함께, 상보성 데이터선(BLT, BLB)의 한쪽을 전원 전압(V<sub>dd</sub>)에 접속하고, 다른 쪽을 기준 전압(V<sub>ss</sub>)에 접속함으로써, 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>)의 ON, OFF를 반전시킨다.

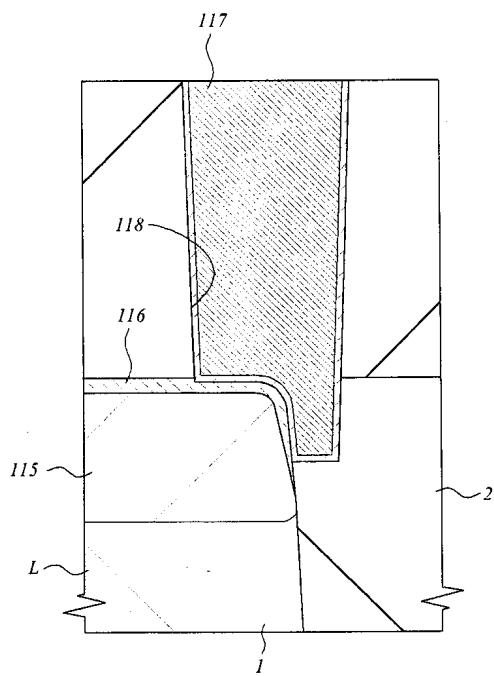

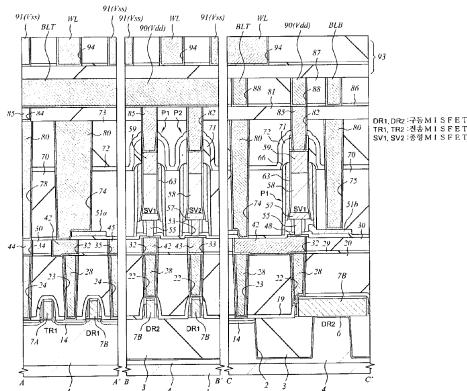

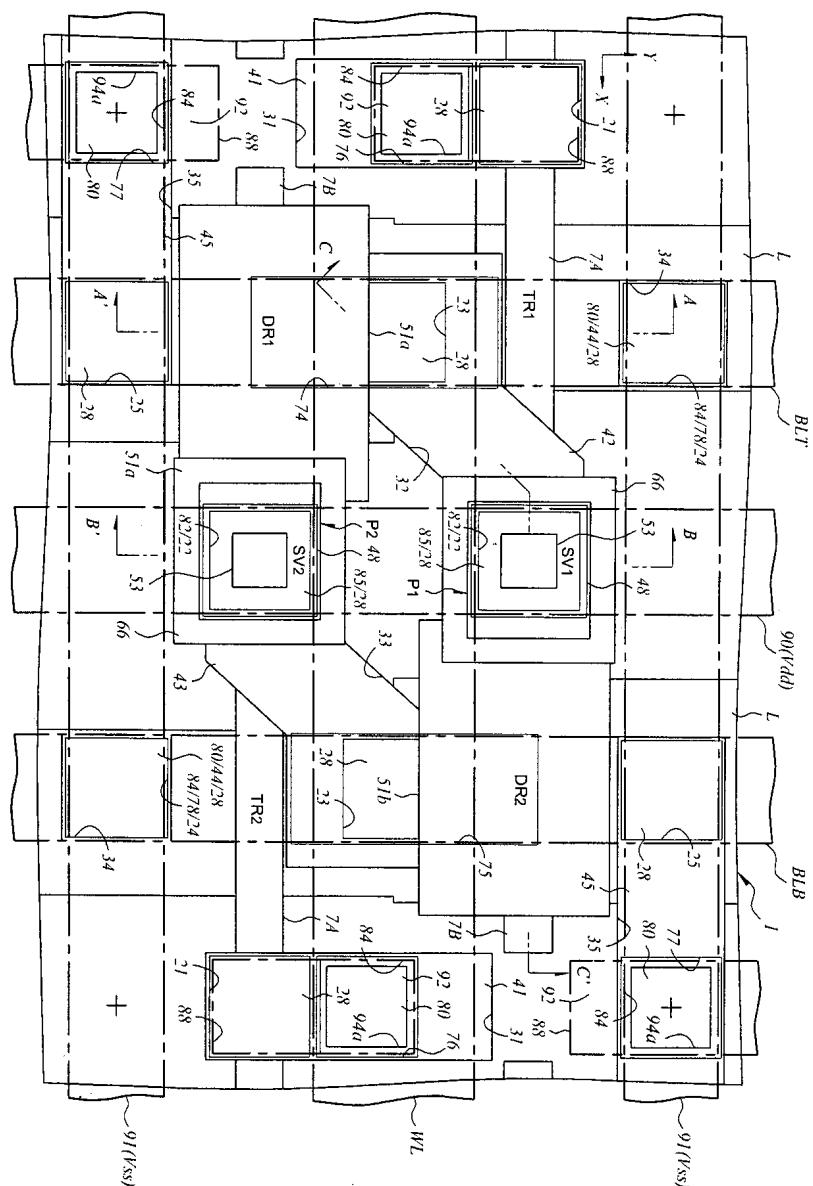

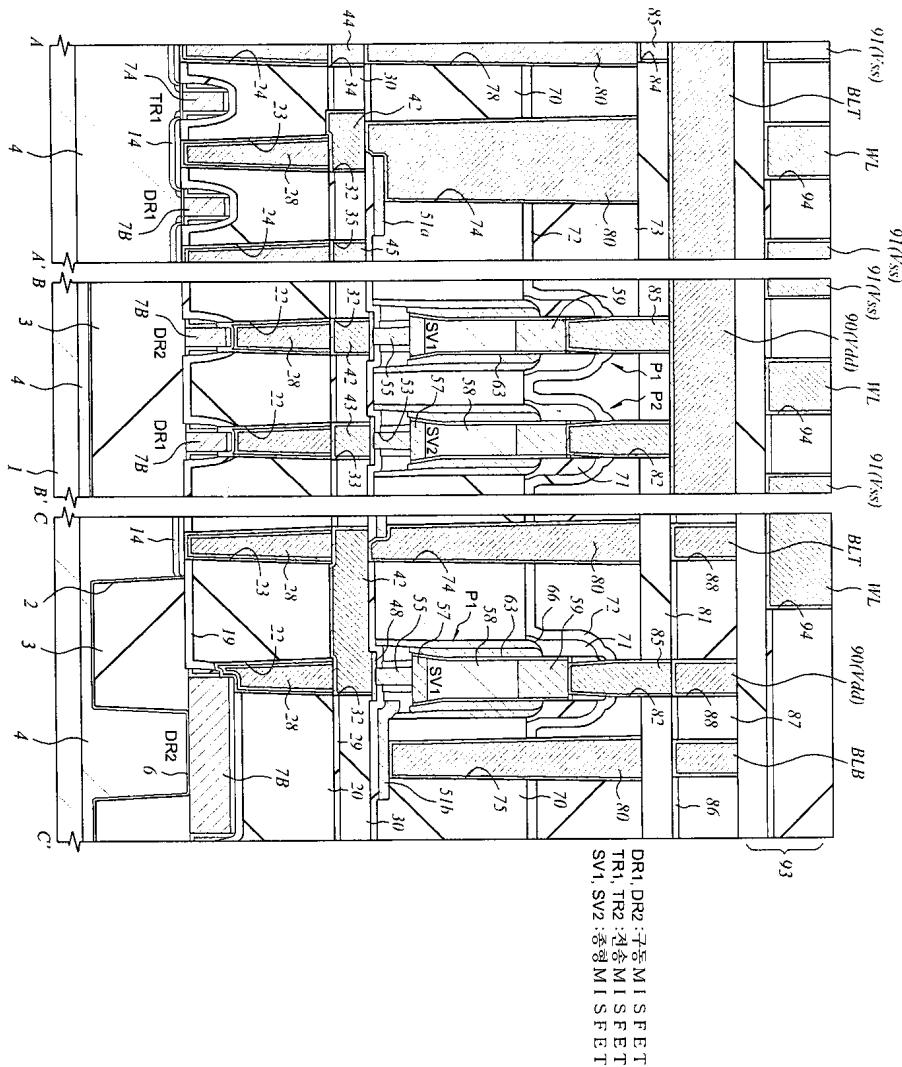

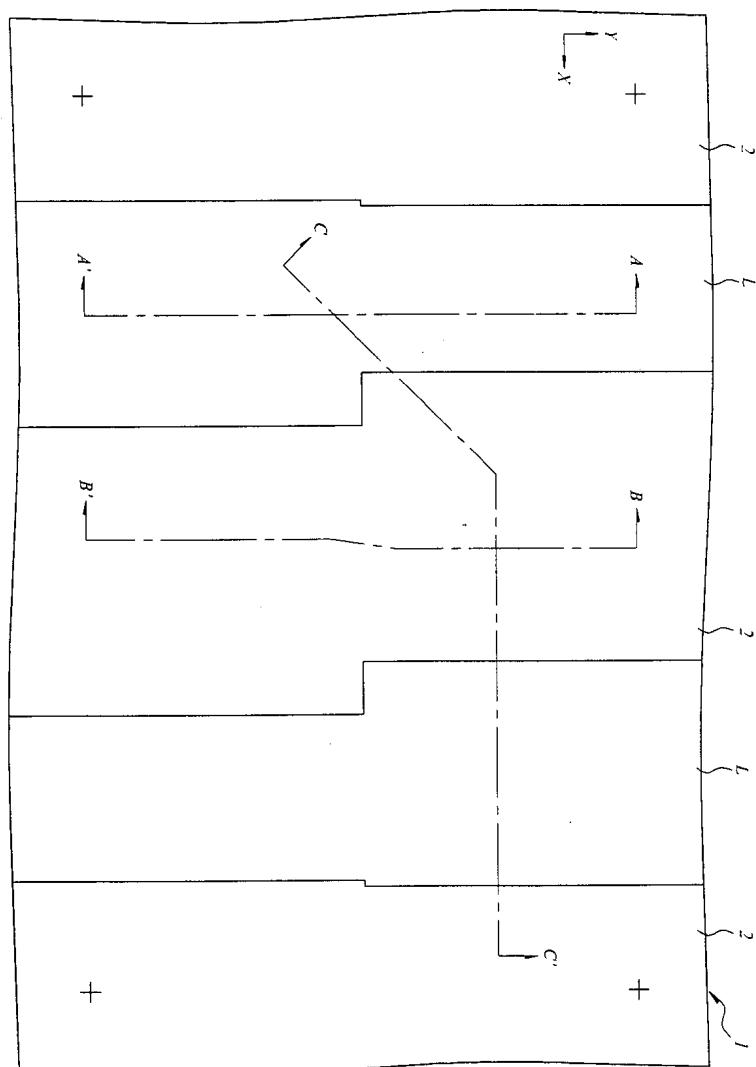

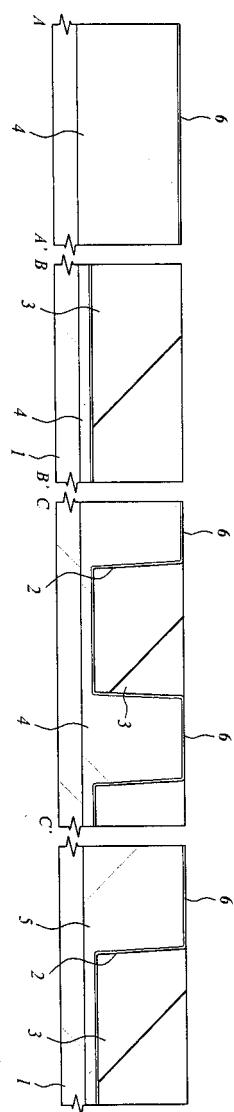

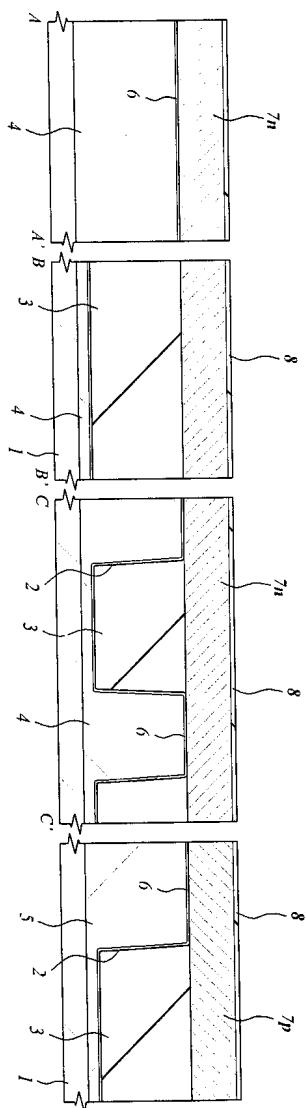

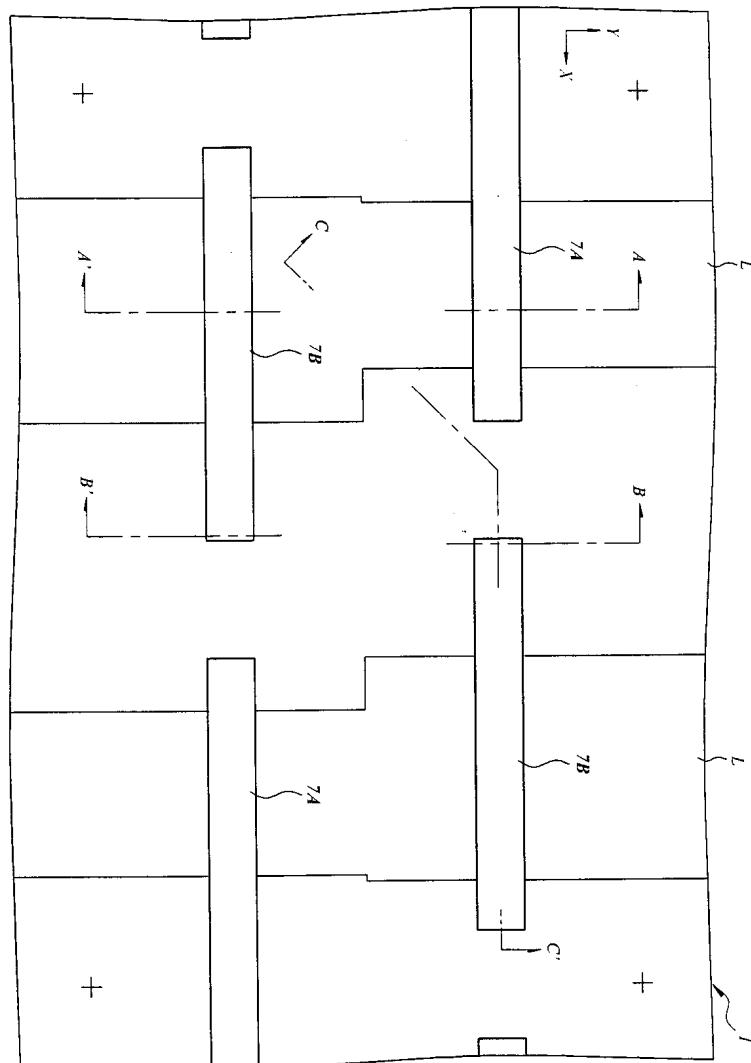

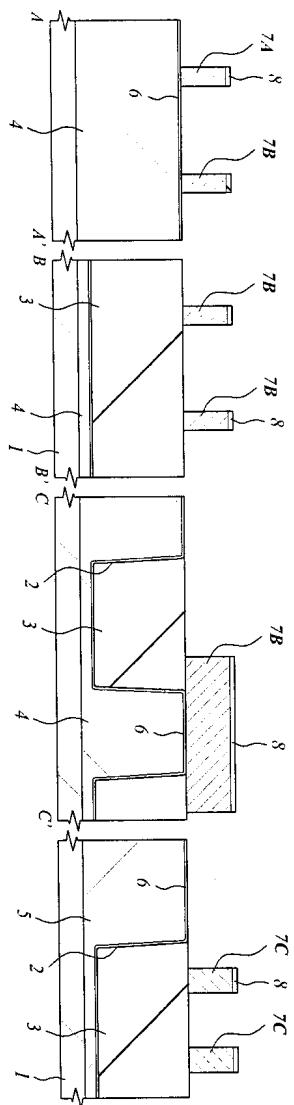

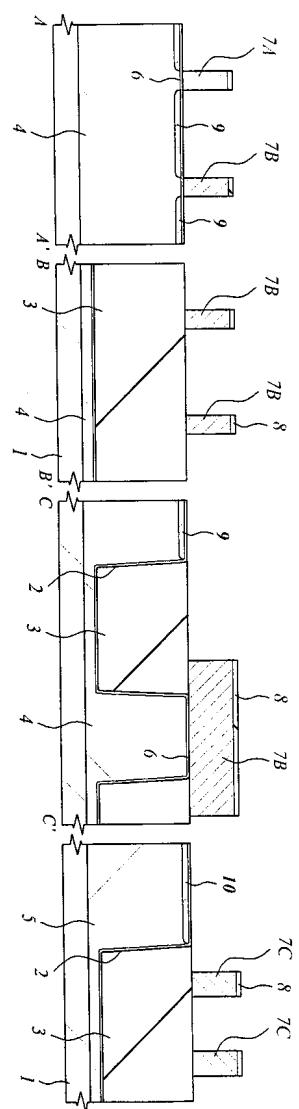

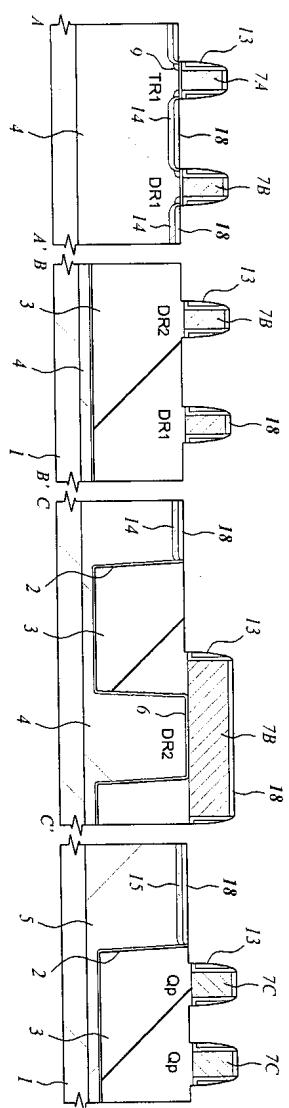

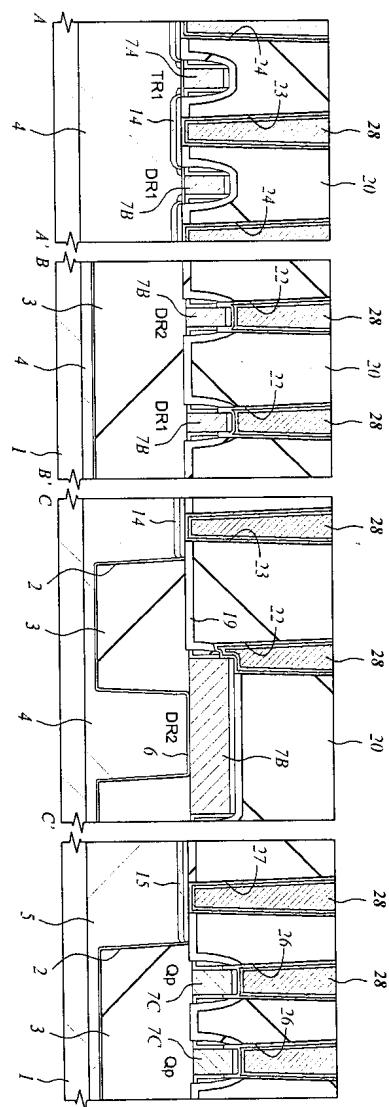

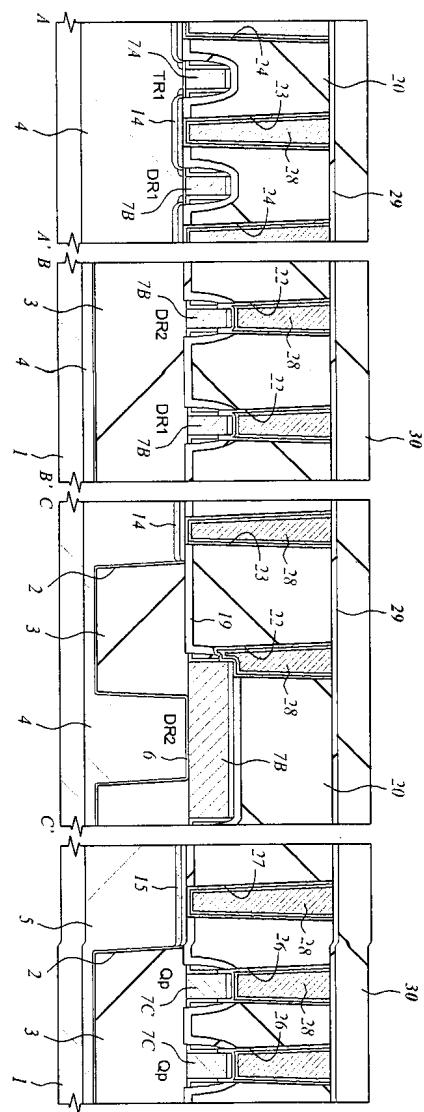

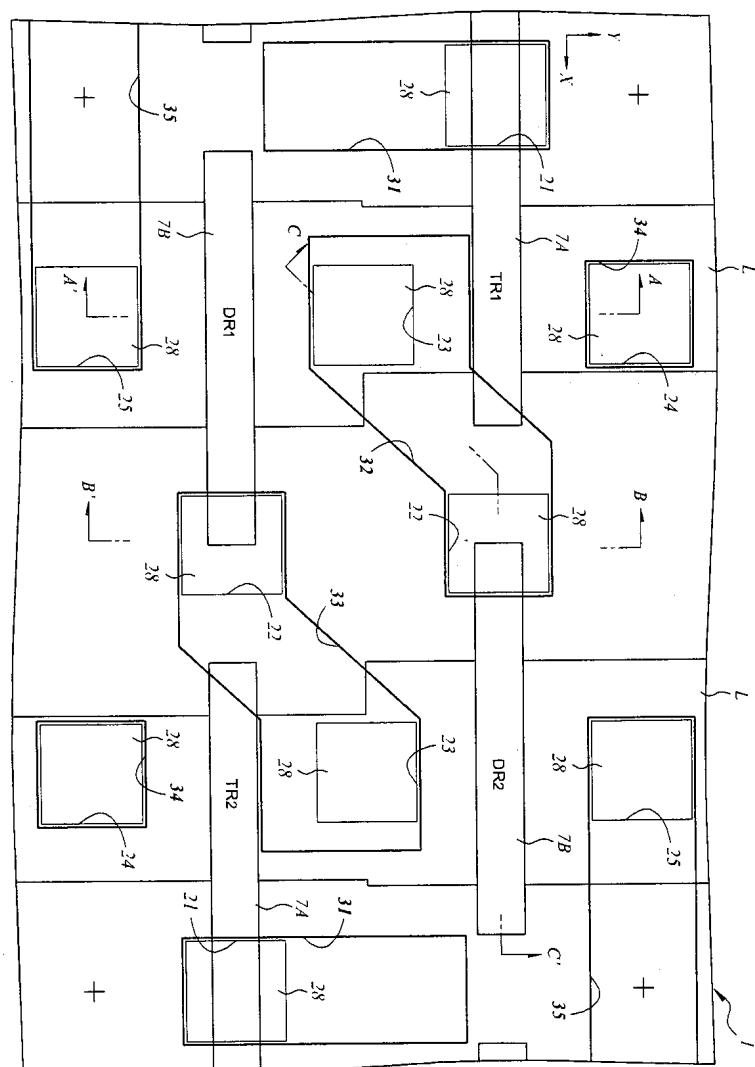

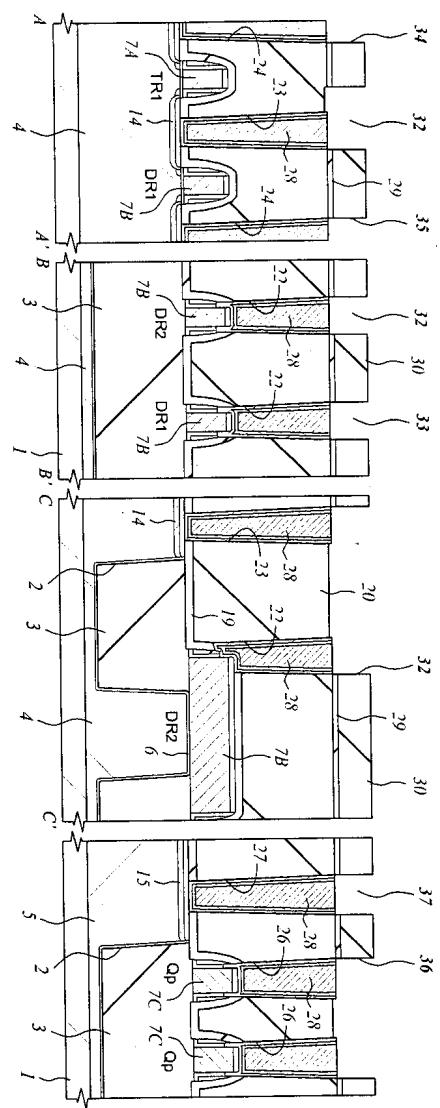

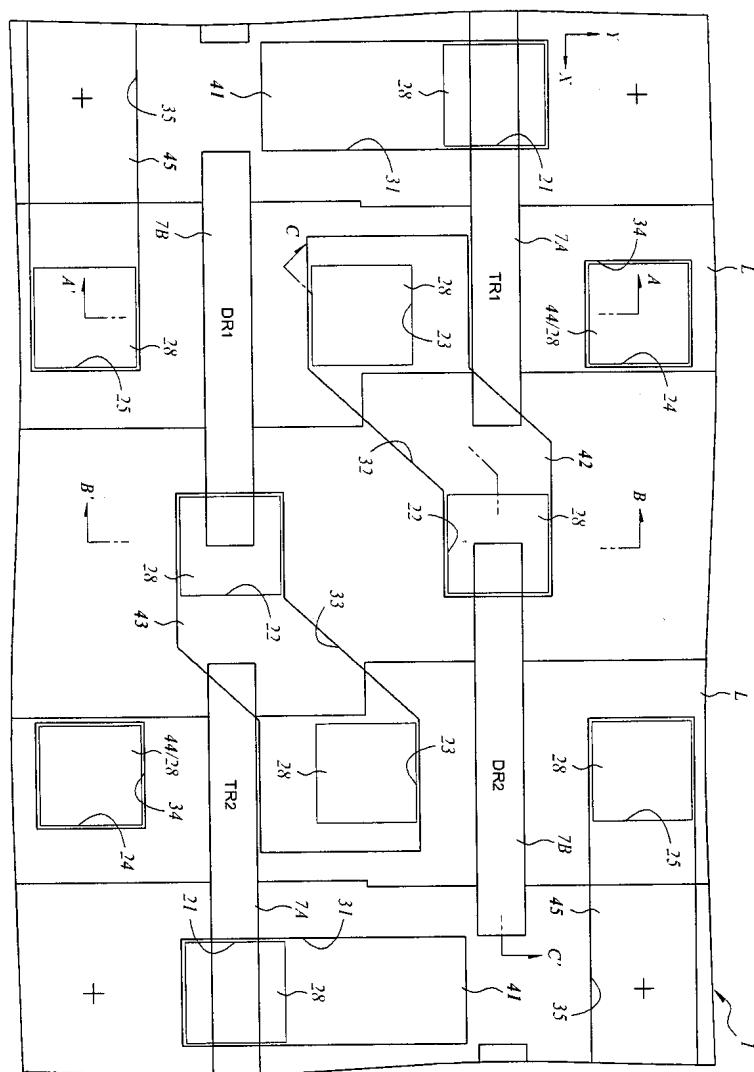

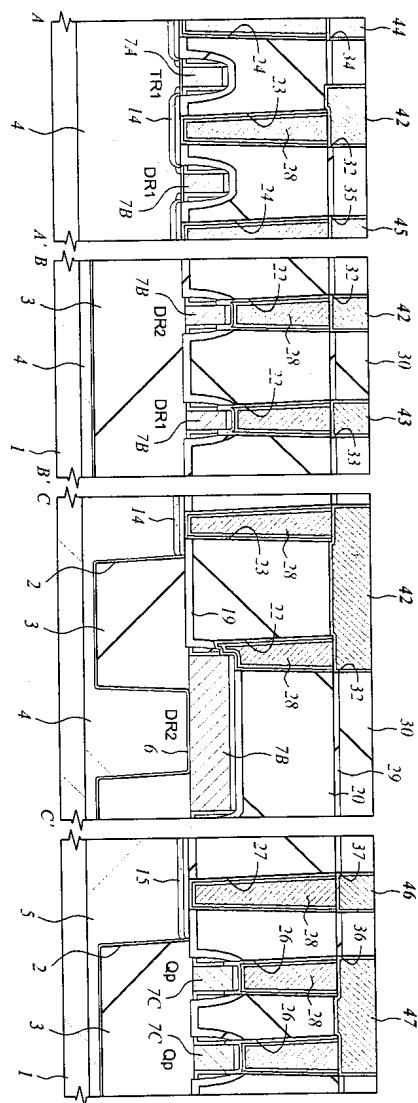

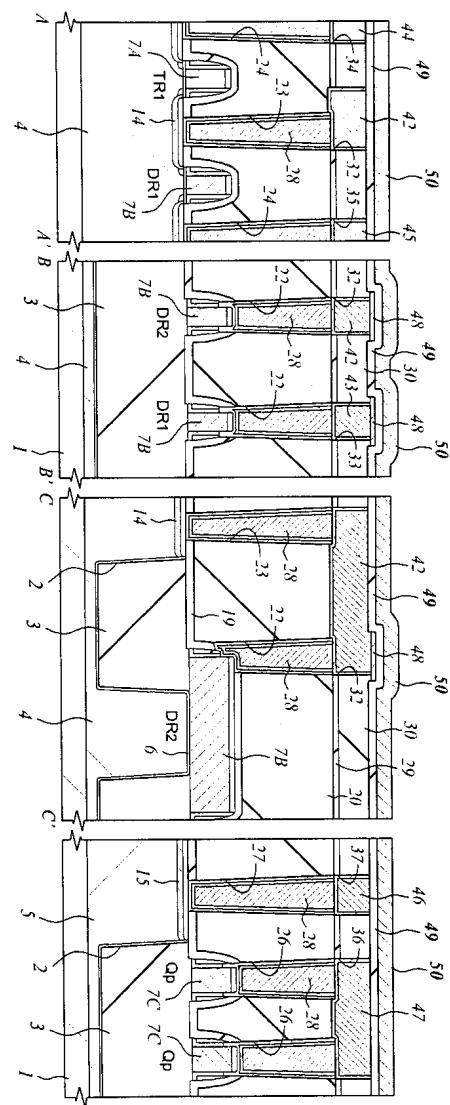

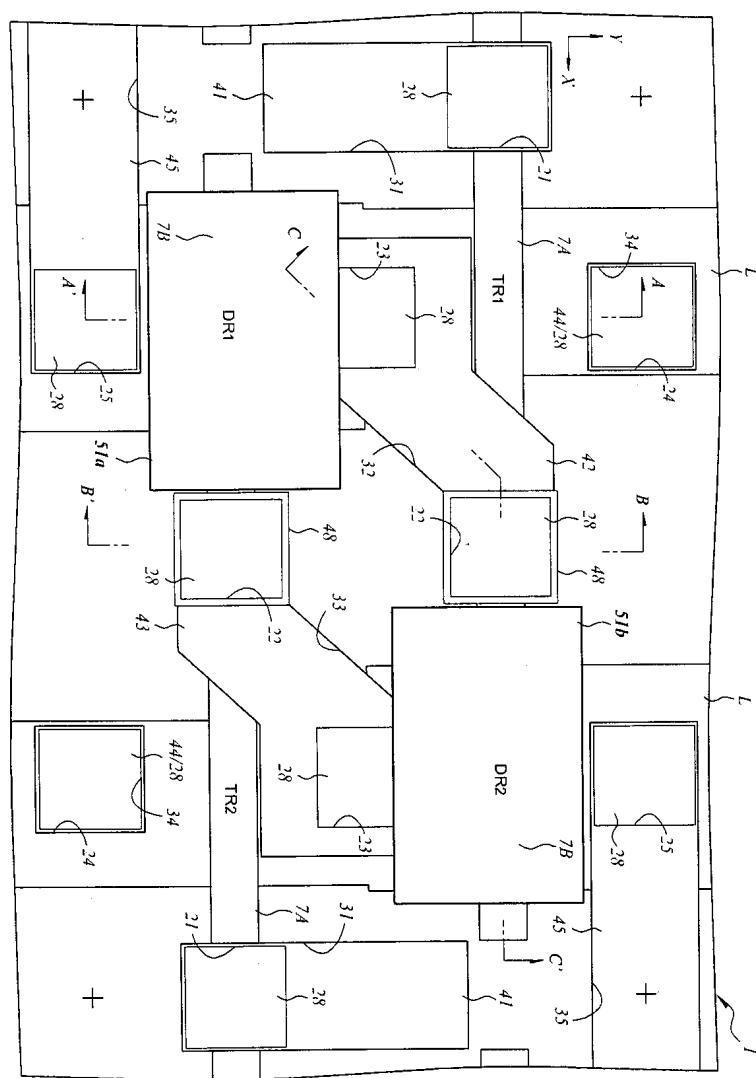

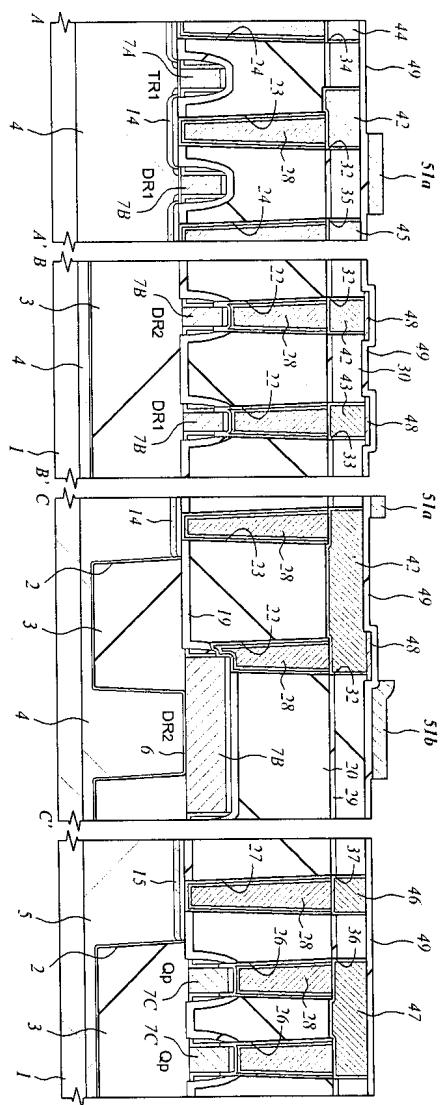

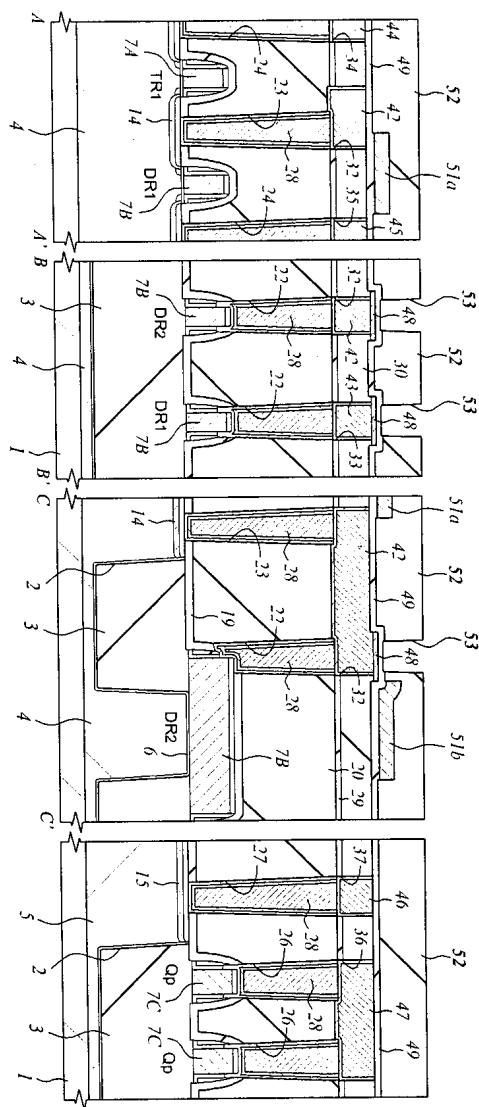

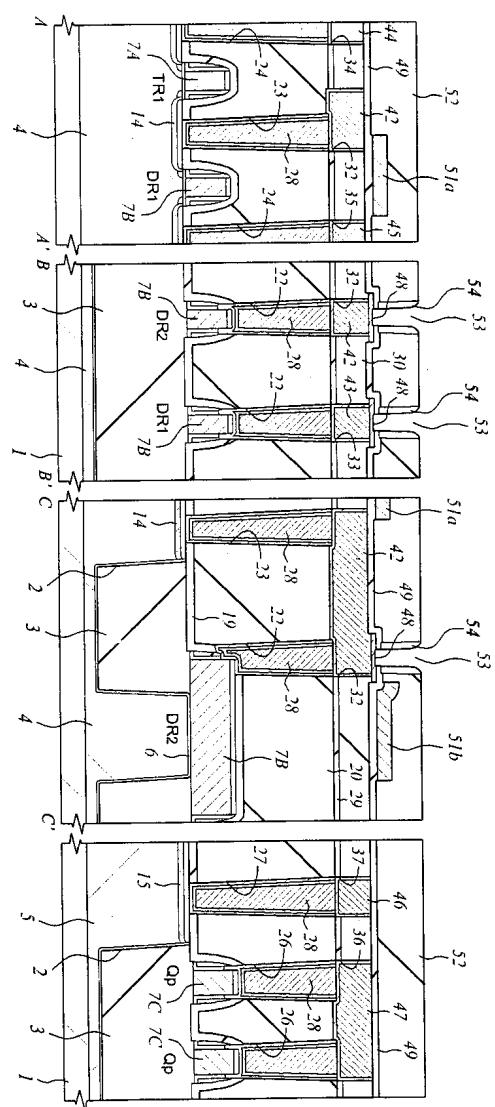

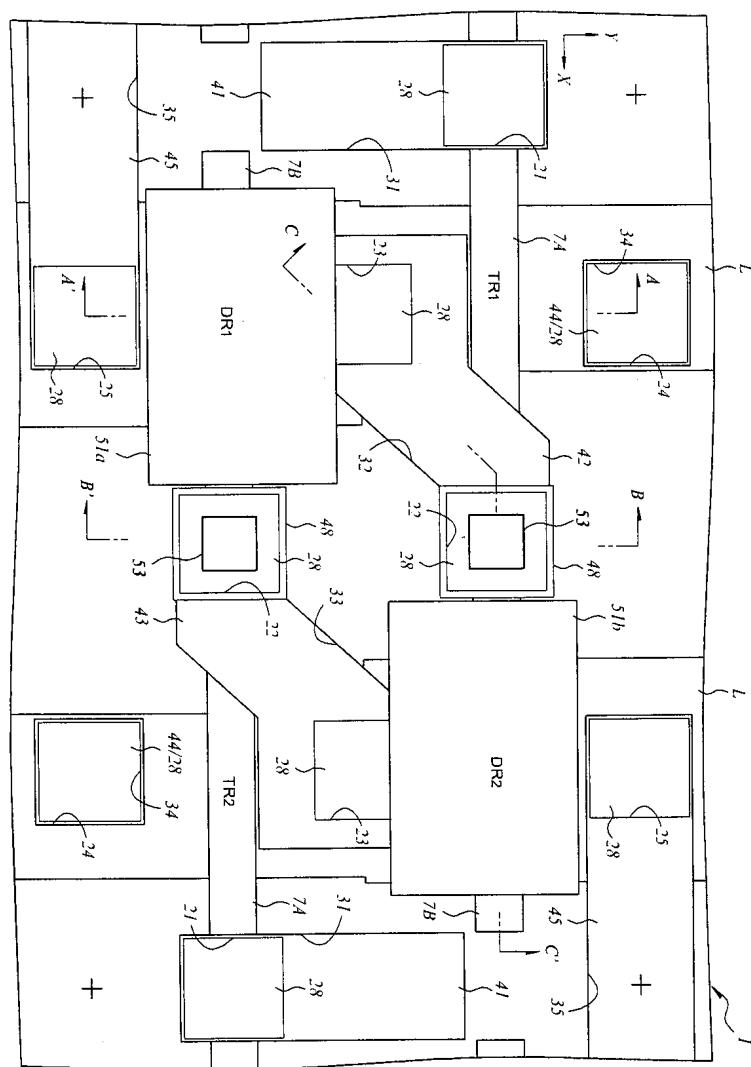

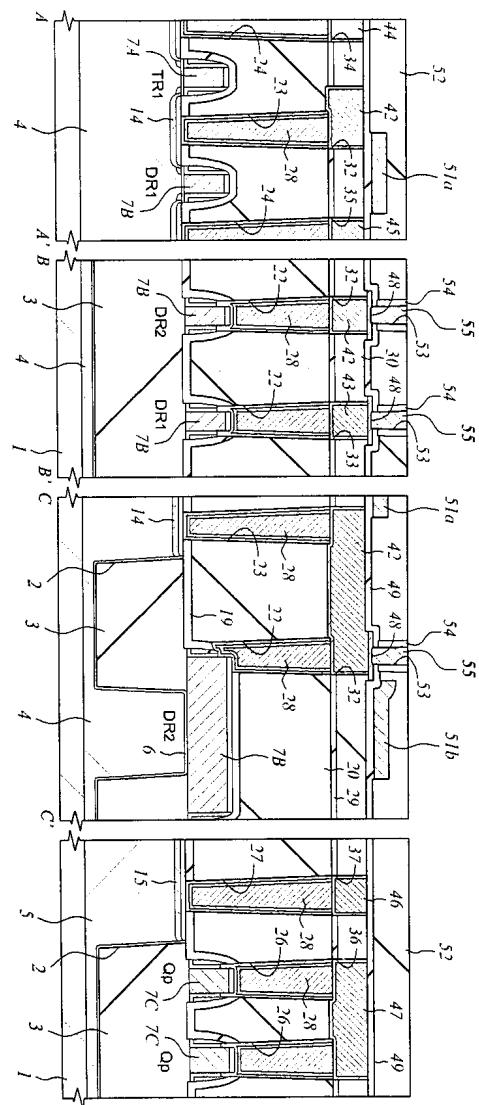

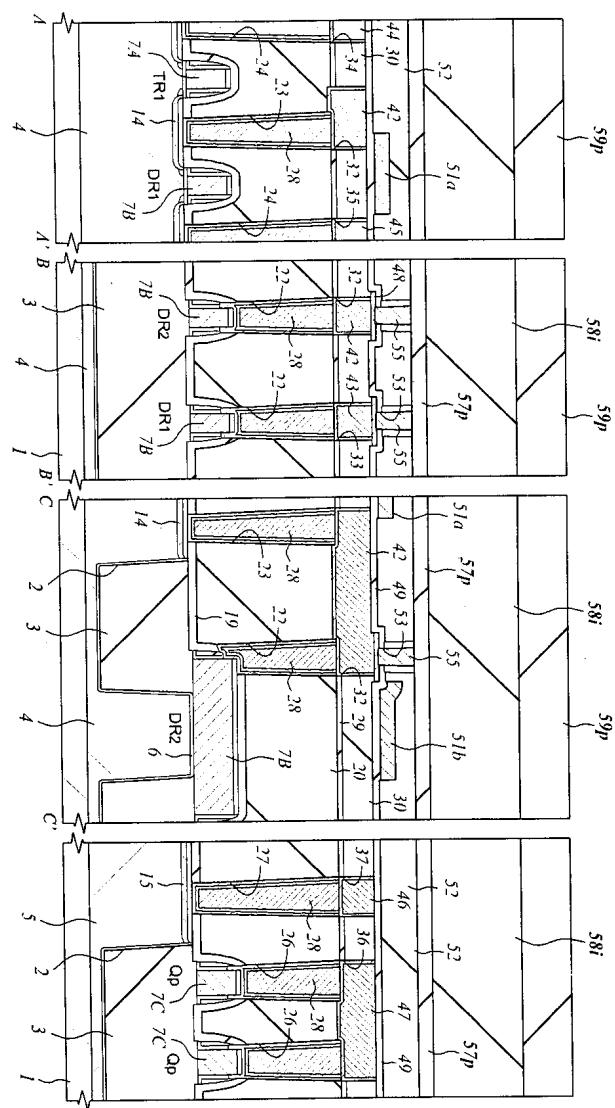

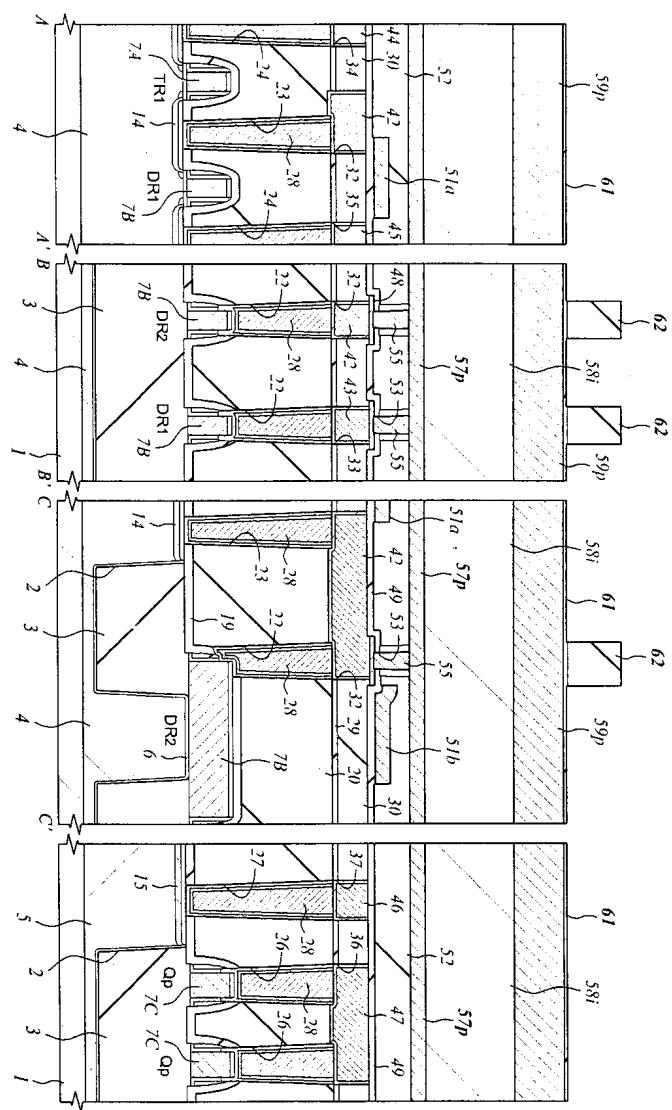

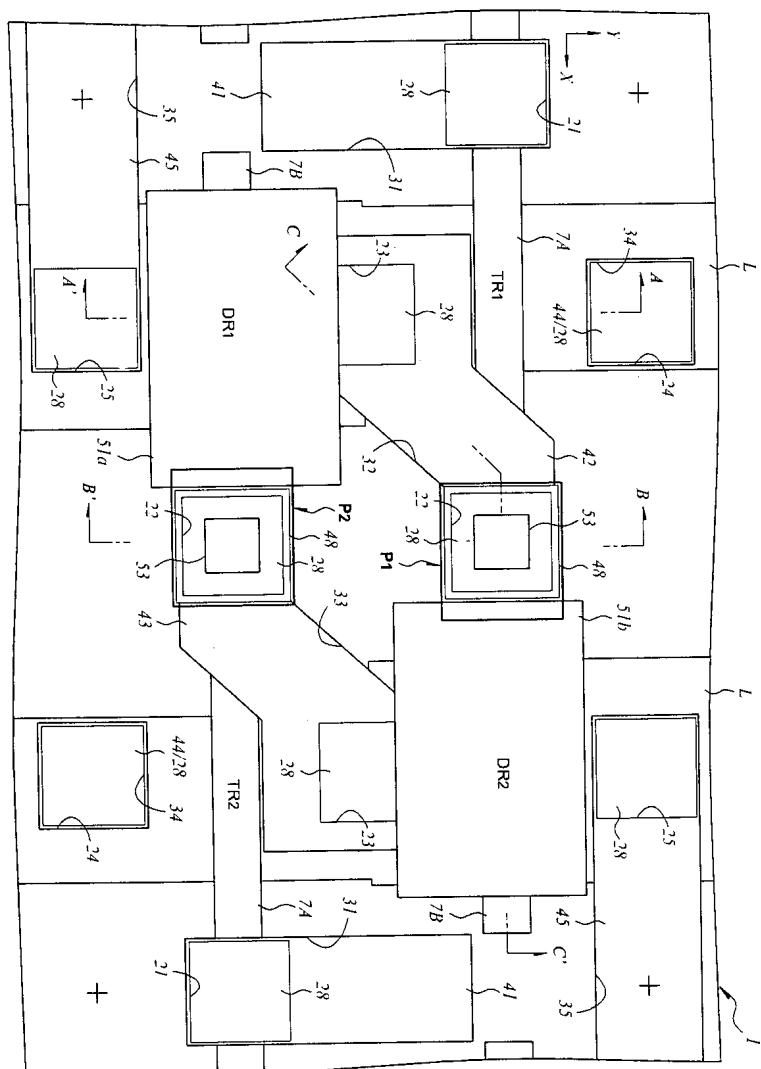

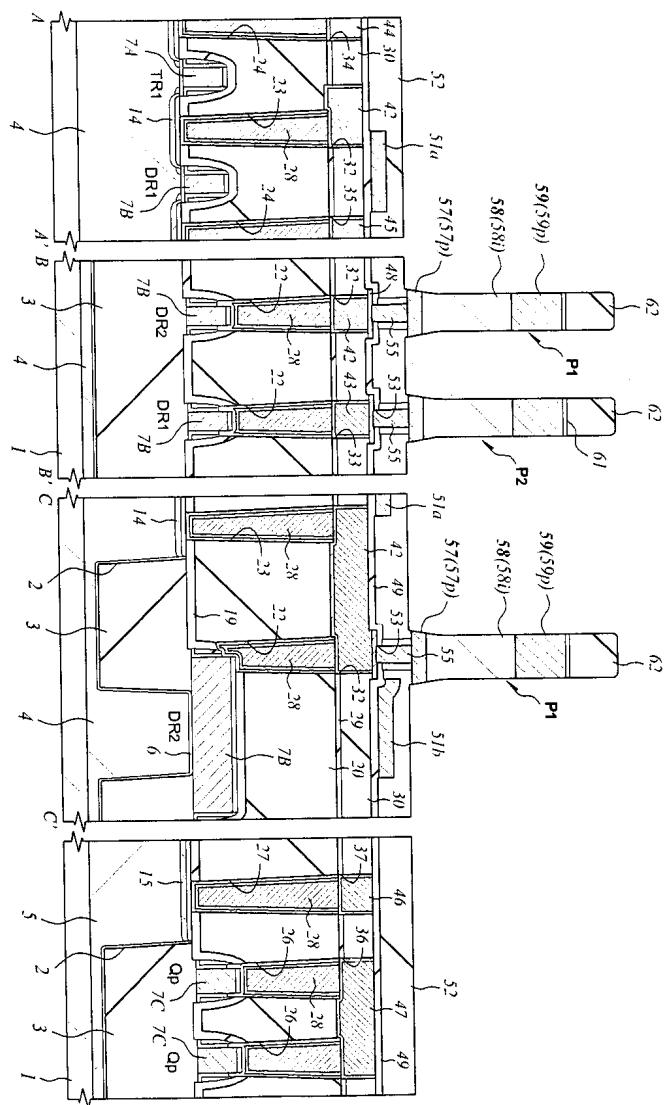

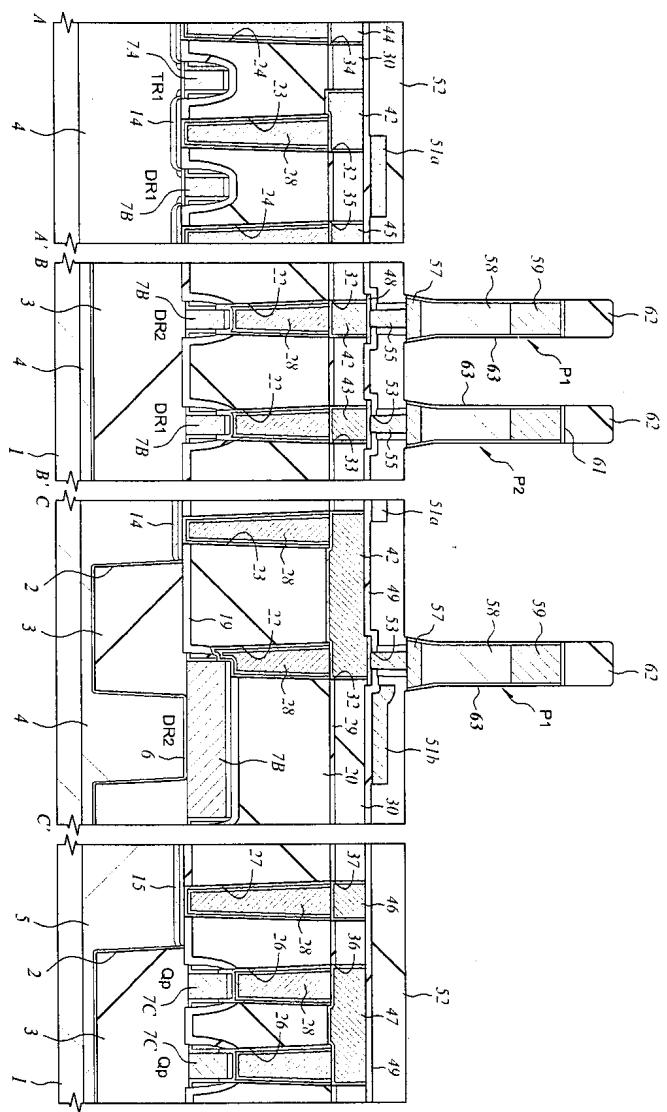

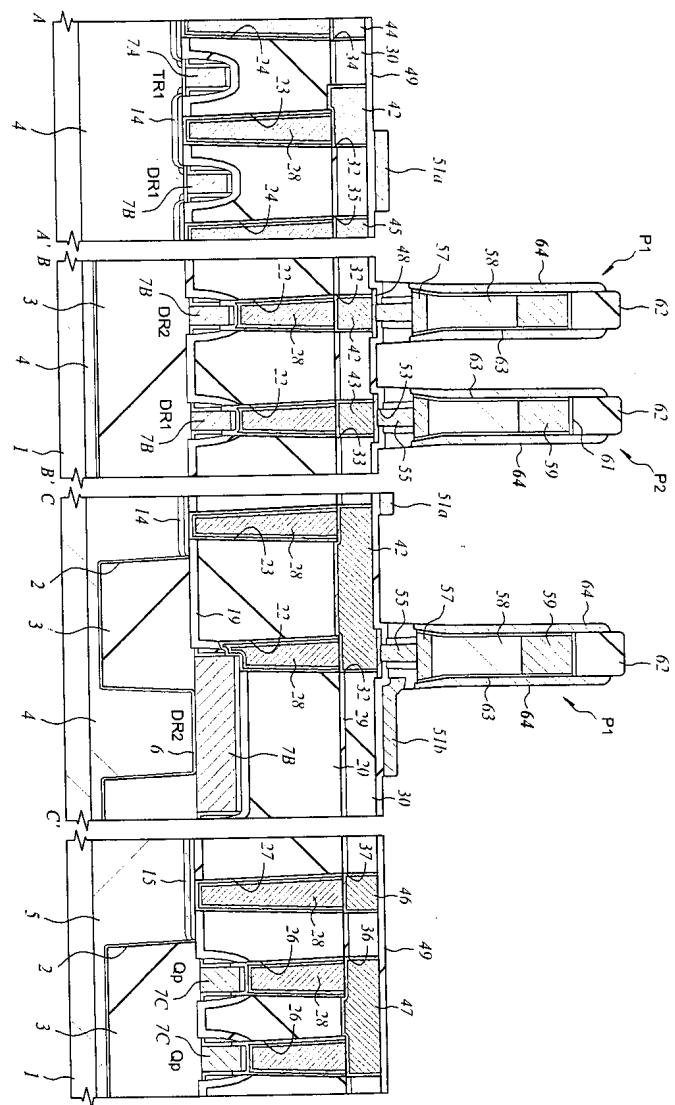

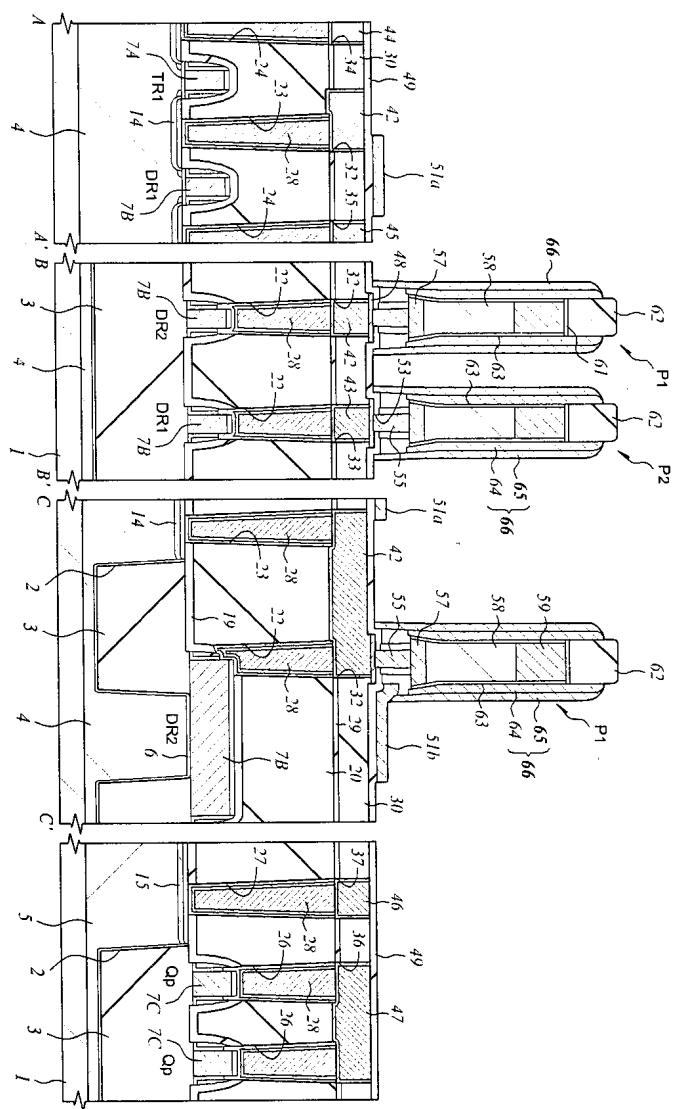

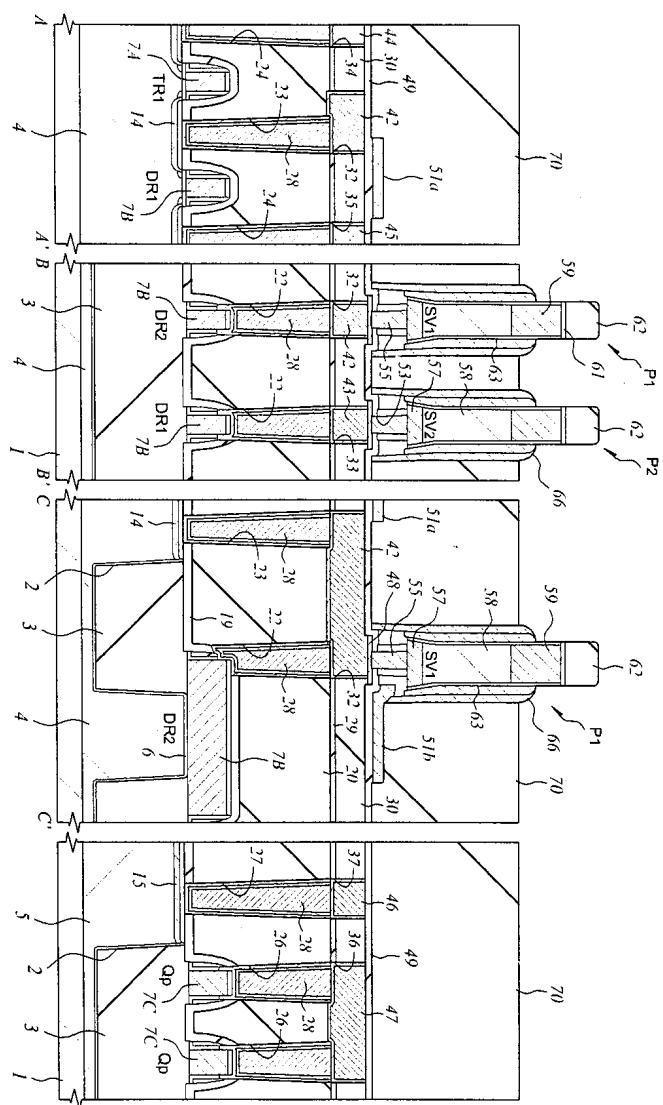

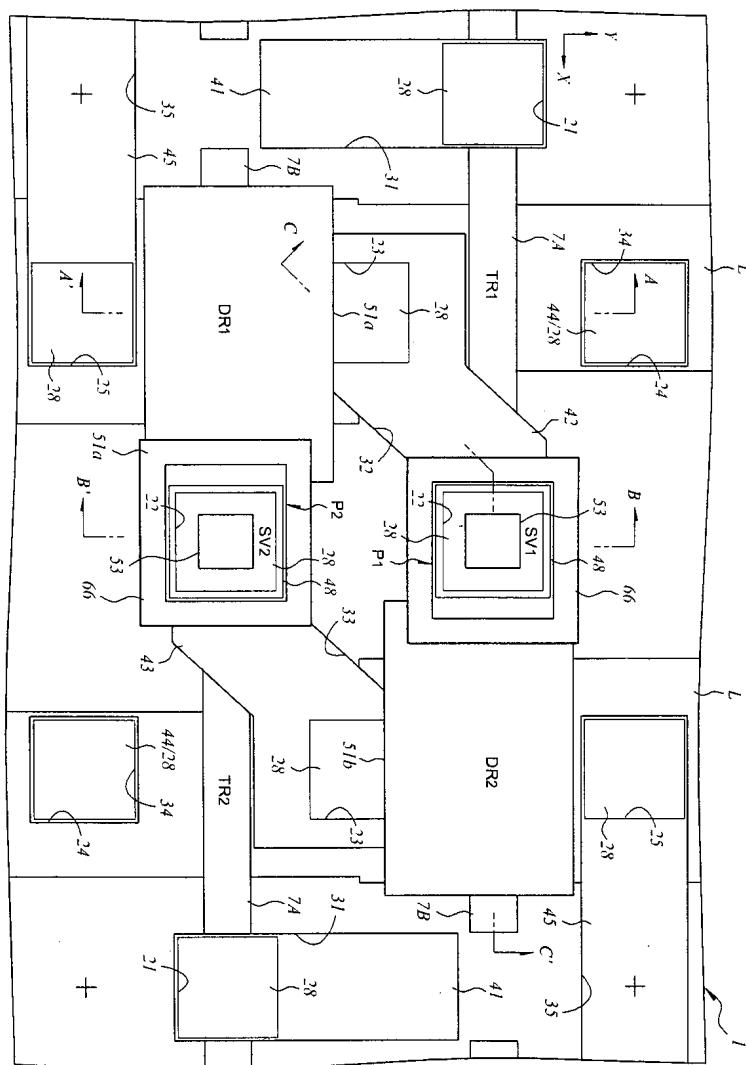

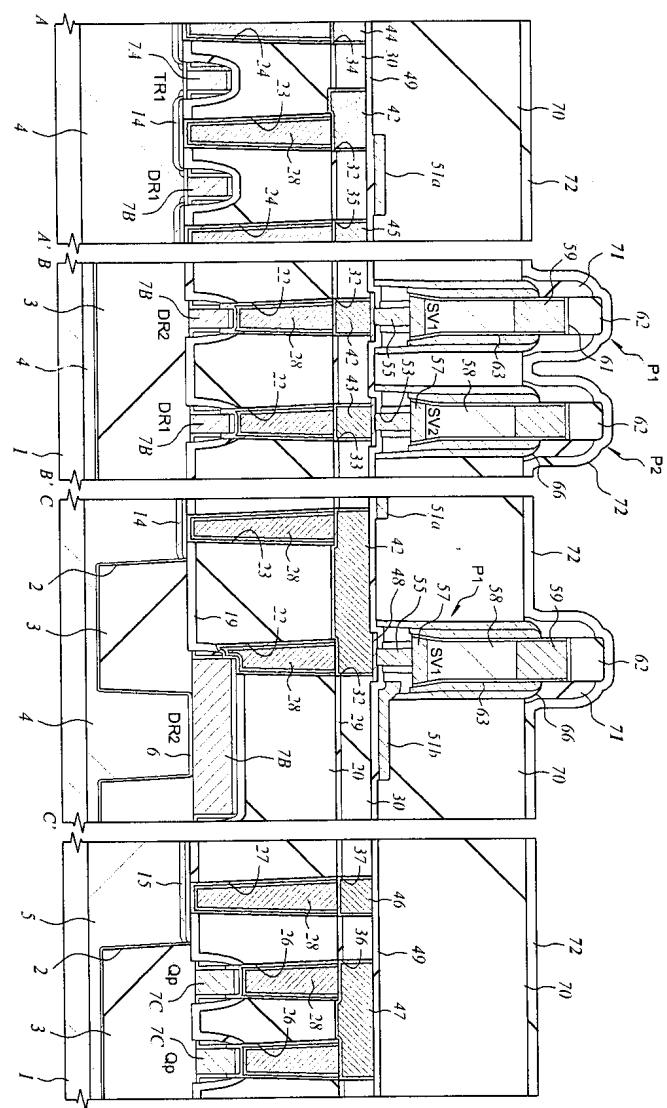

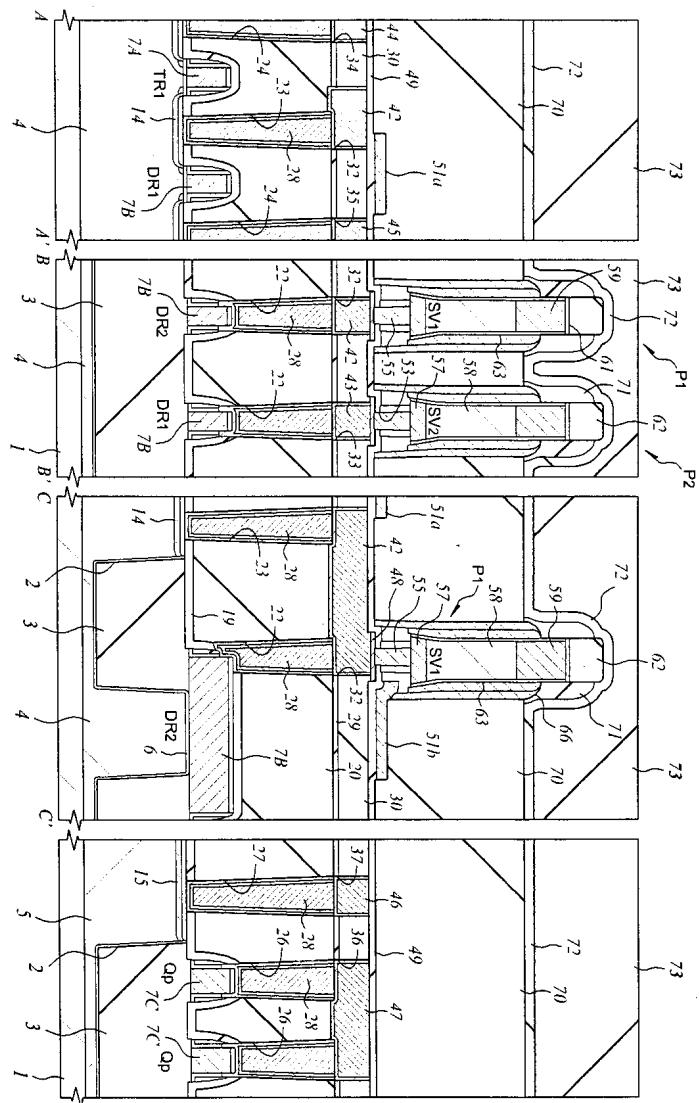

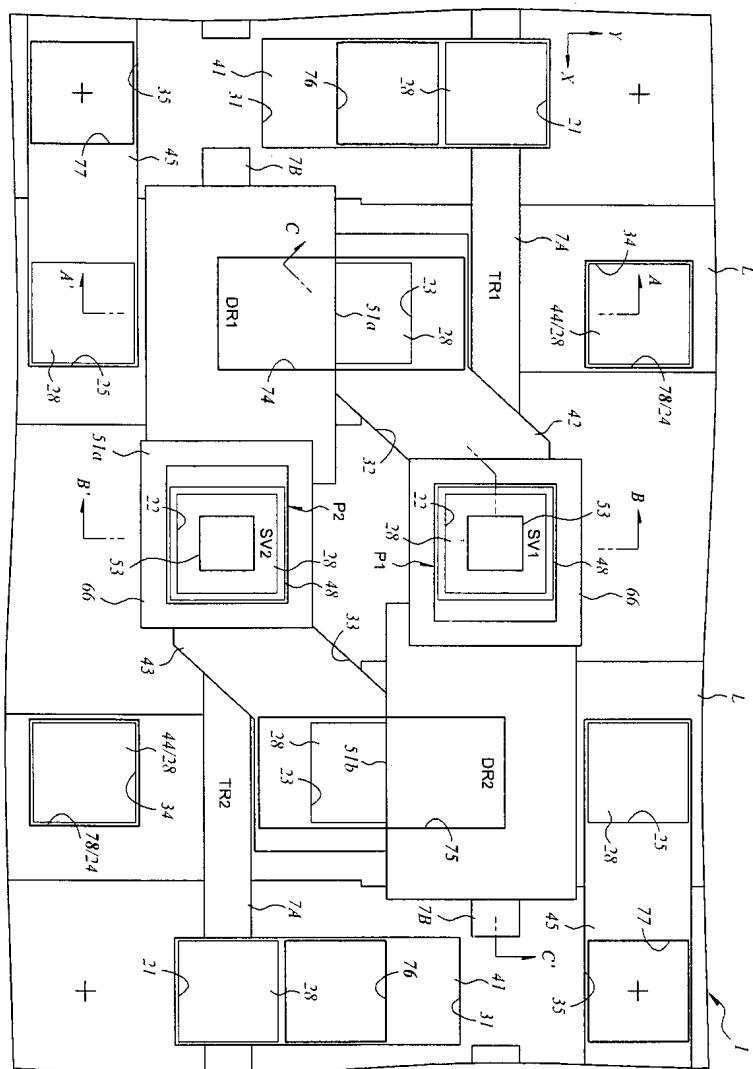

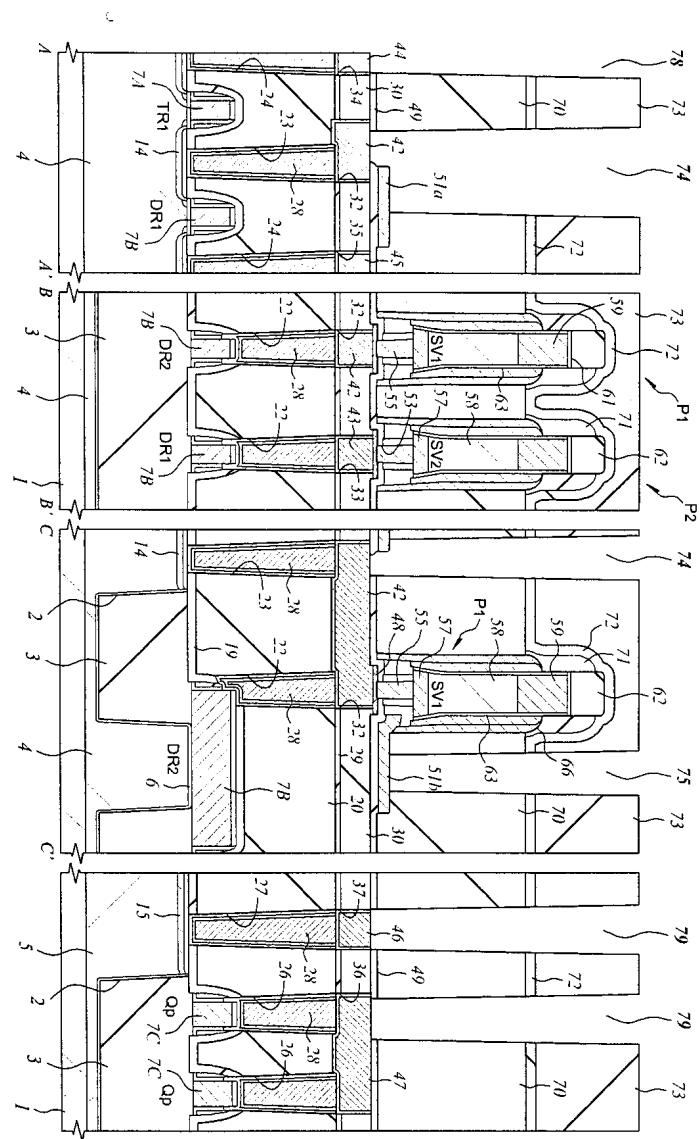

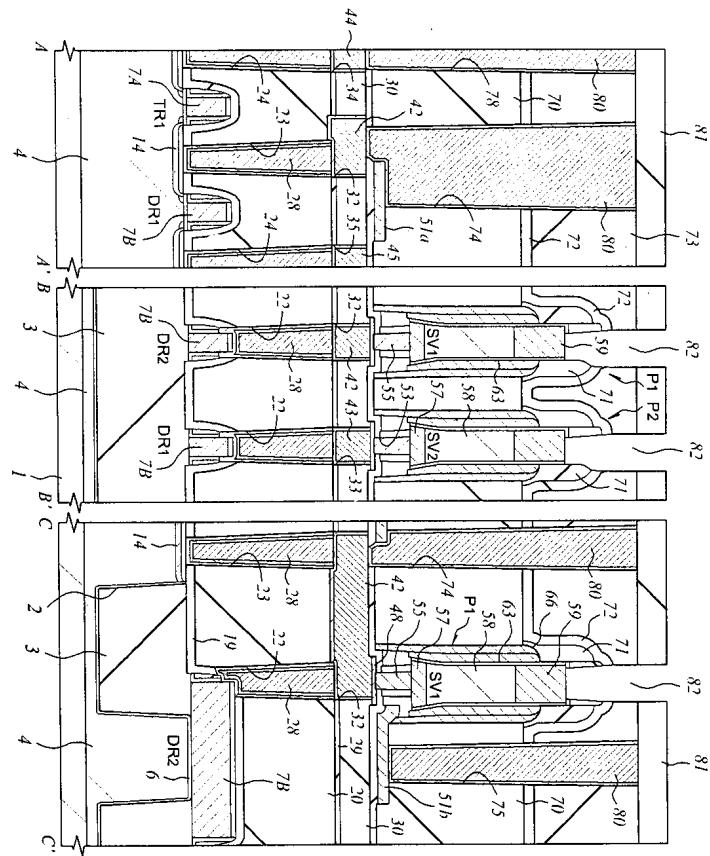

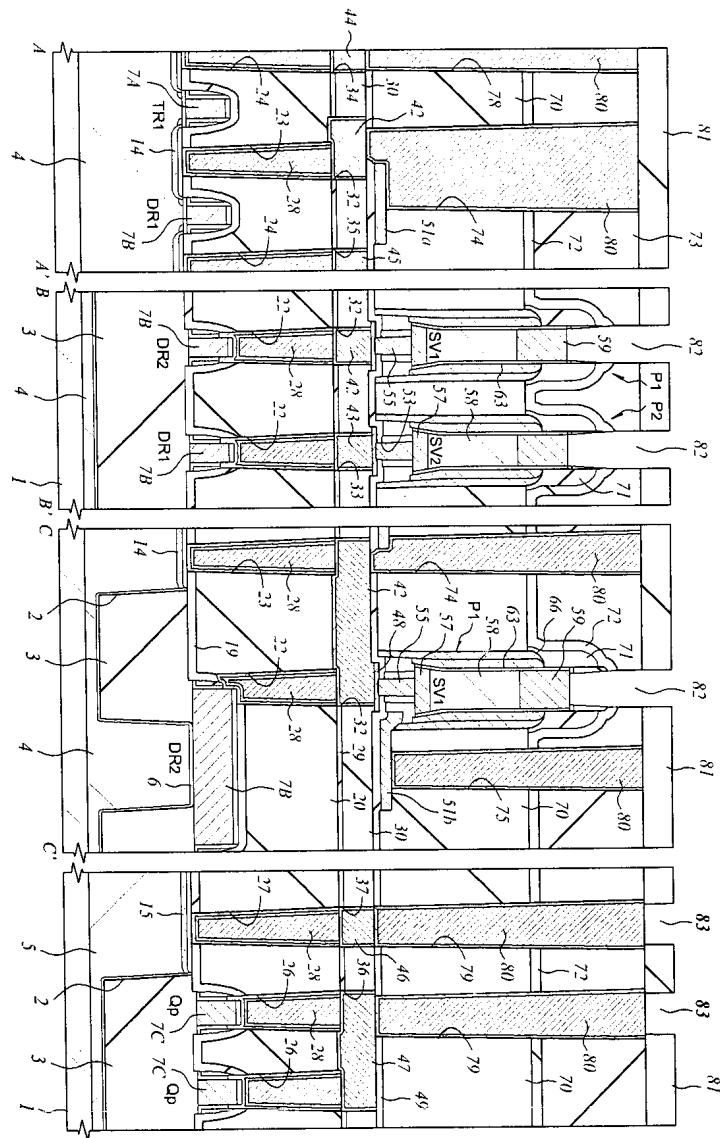

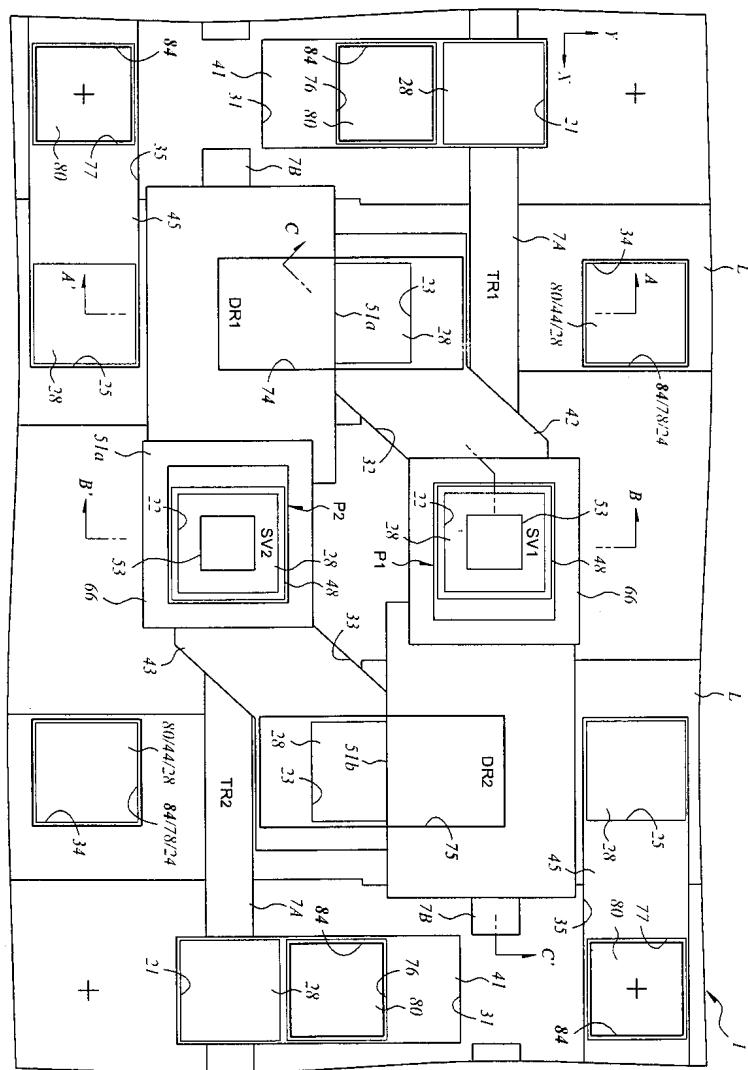

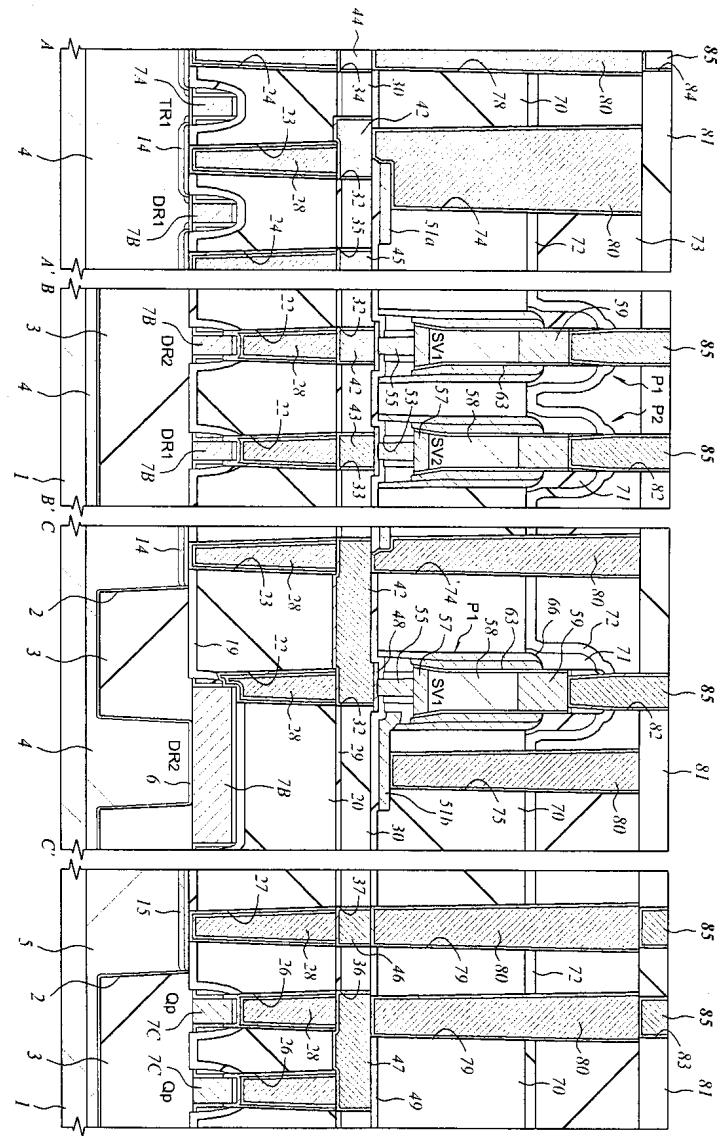

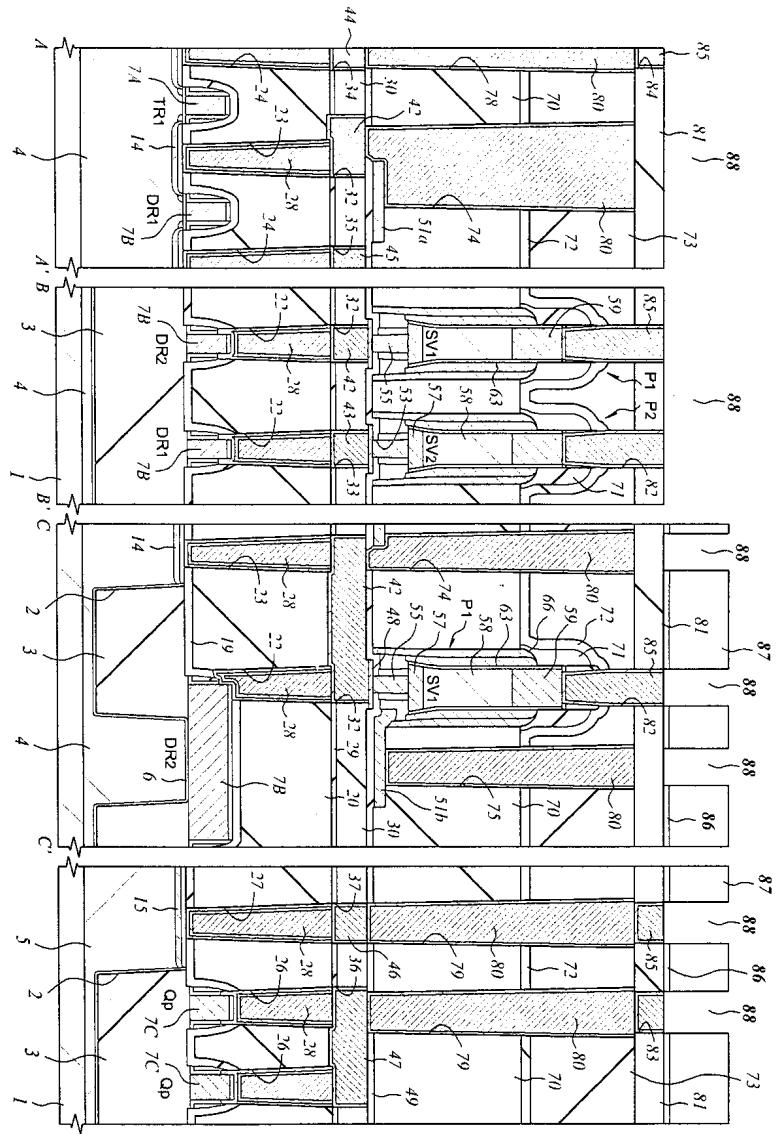

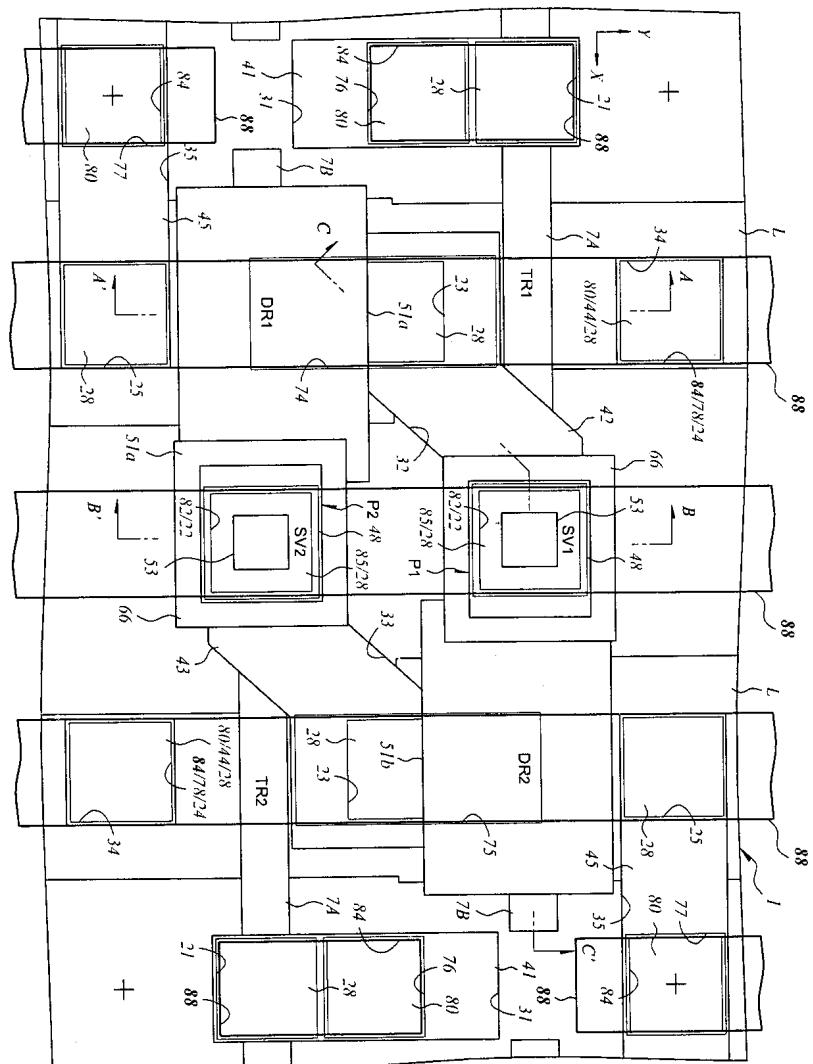

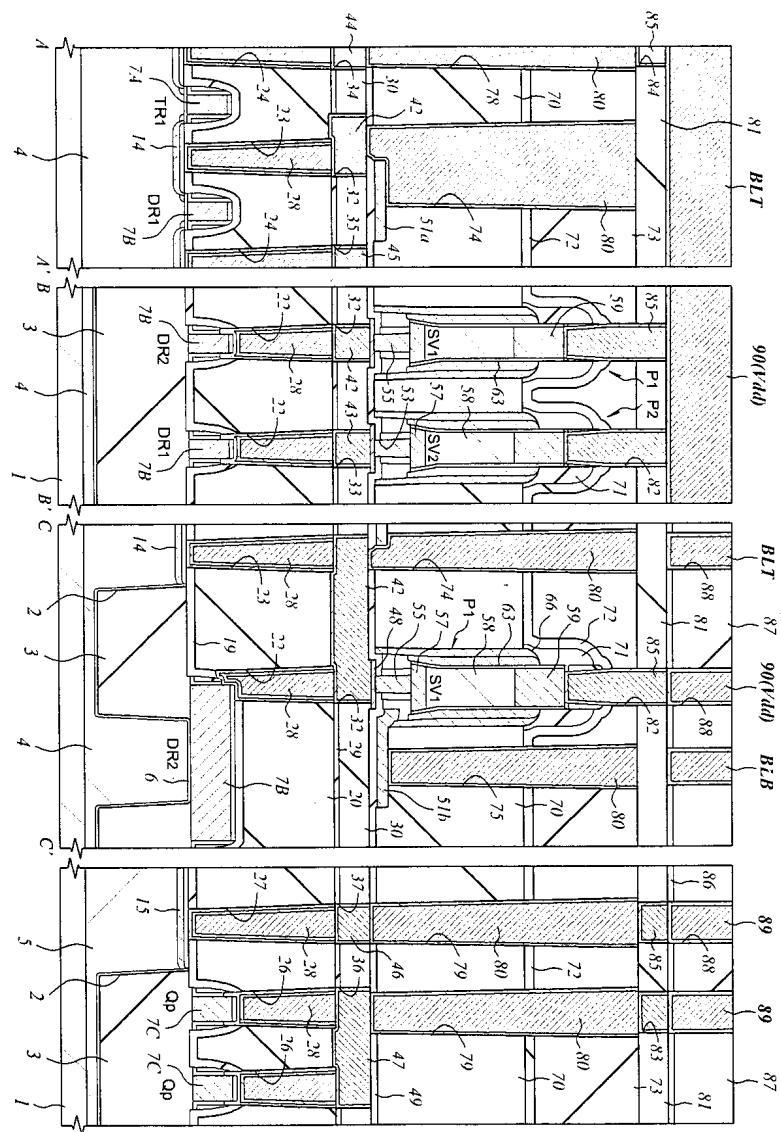

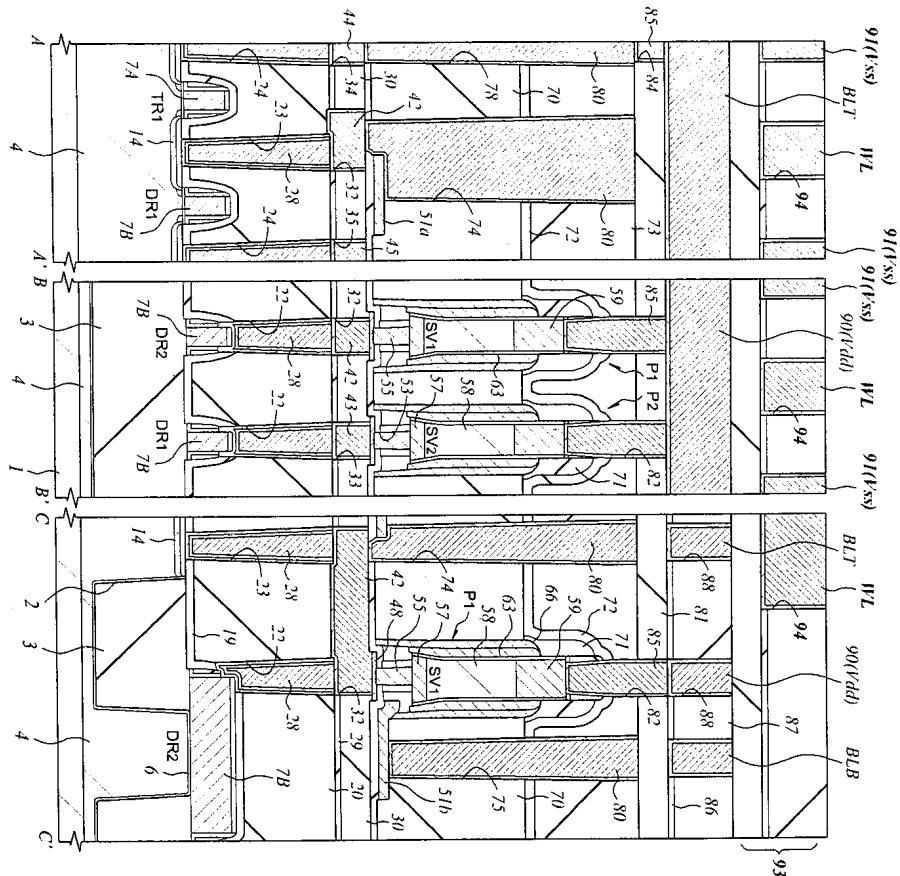

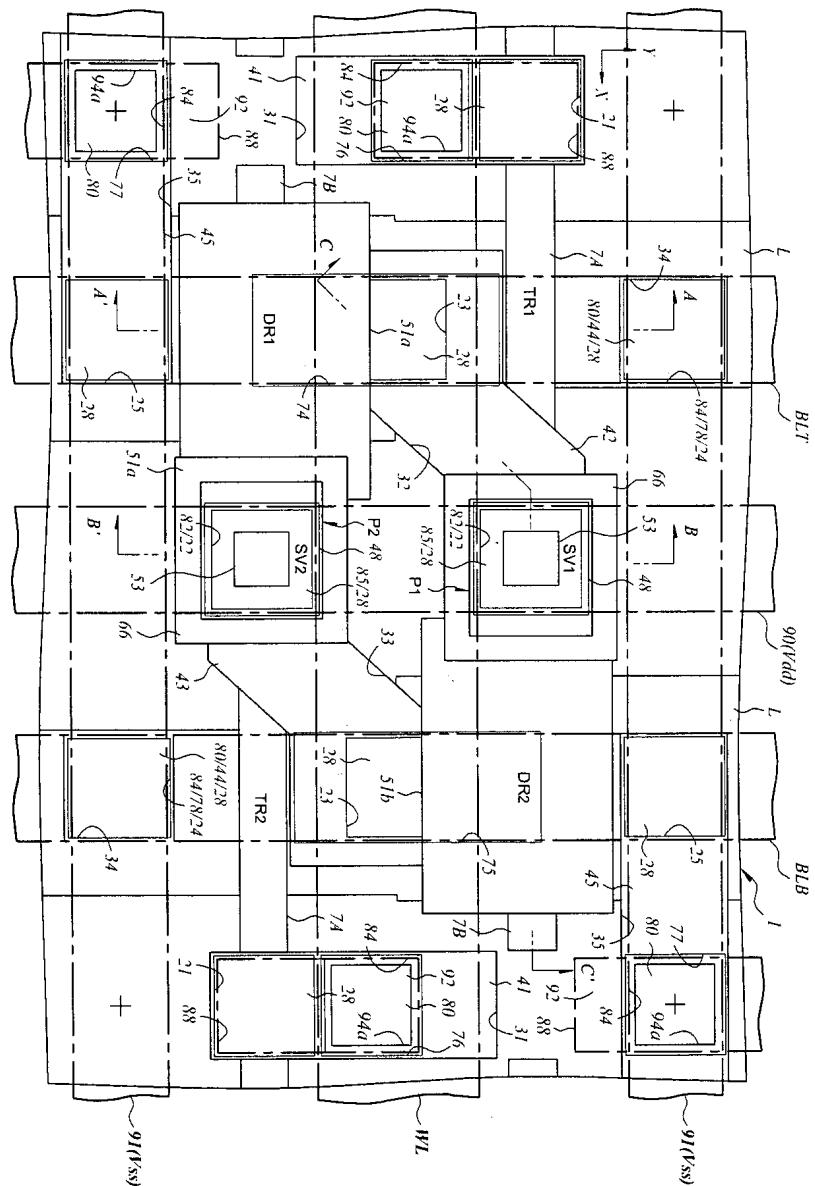

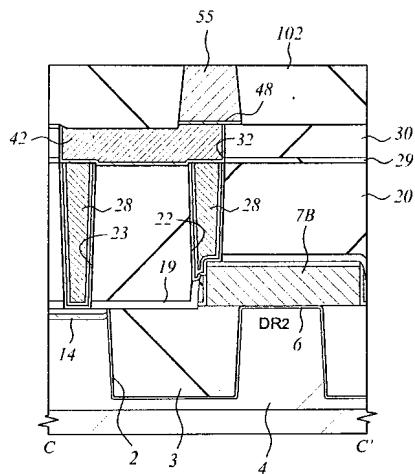

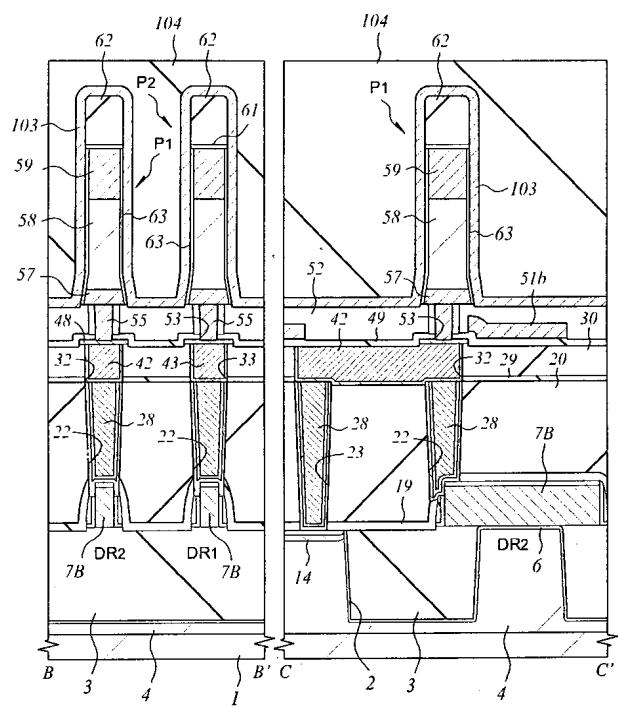

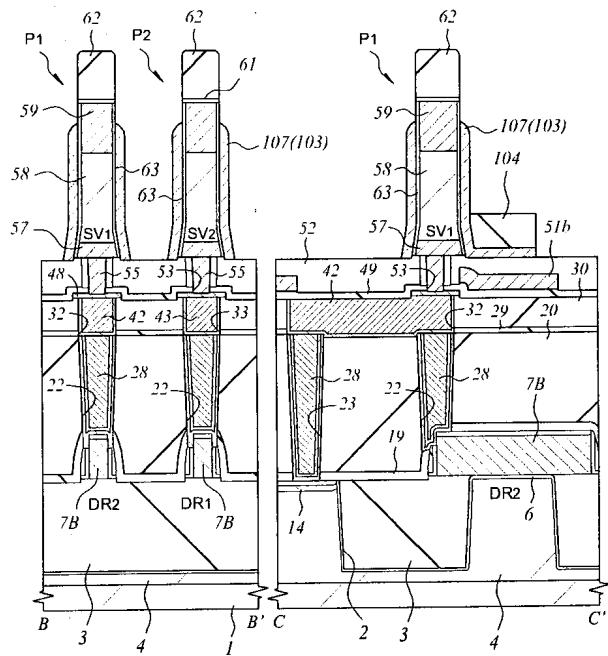

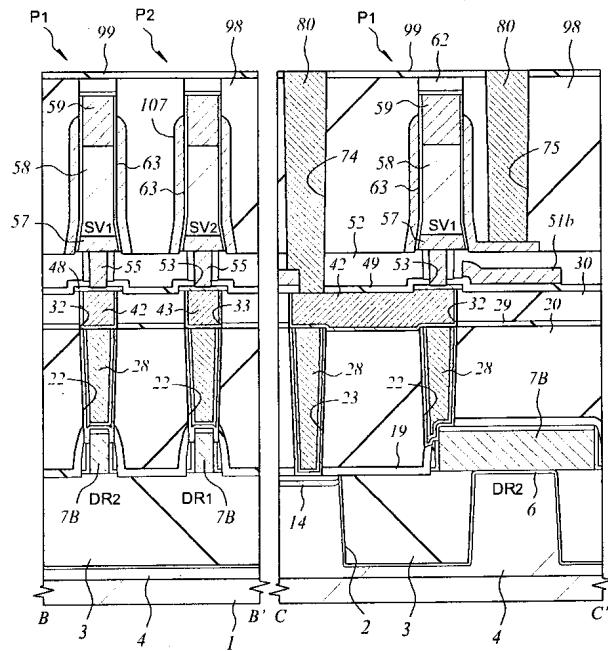

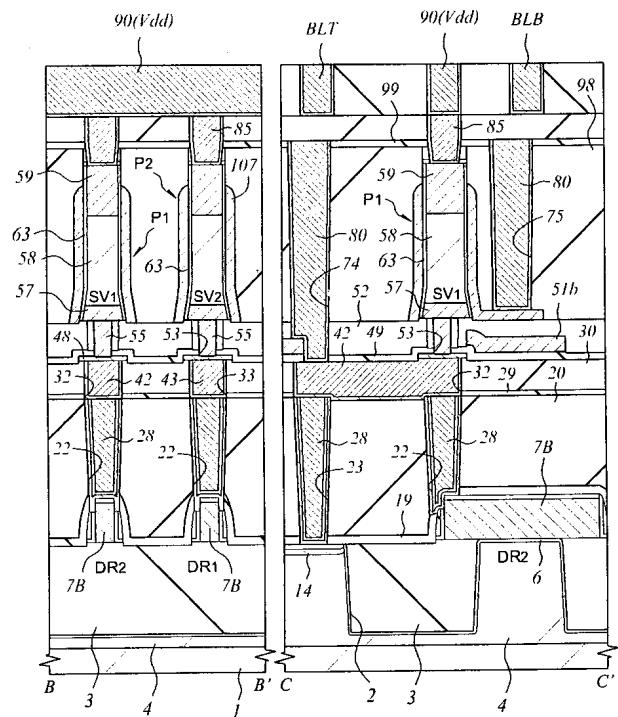

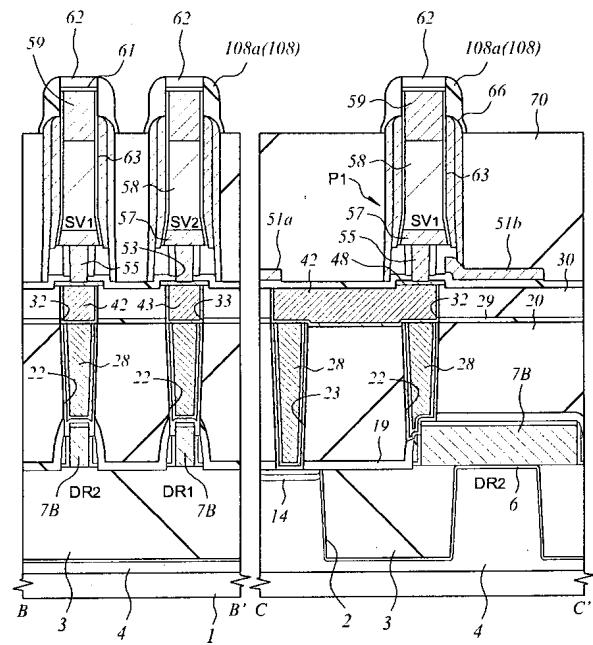

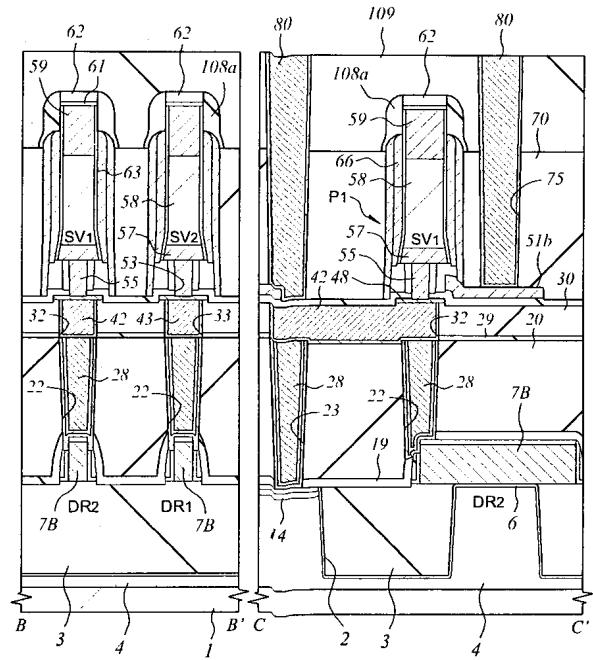

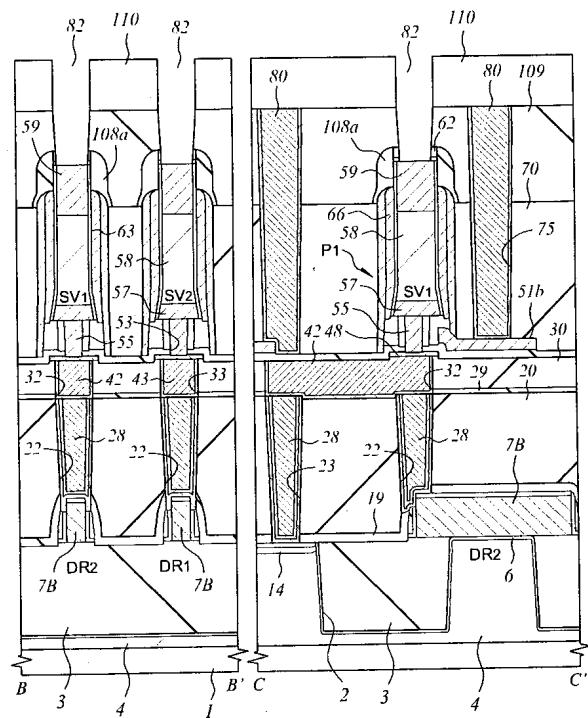

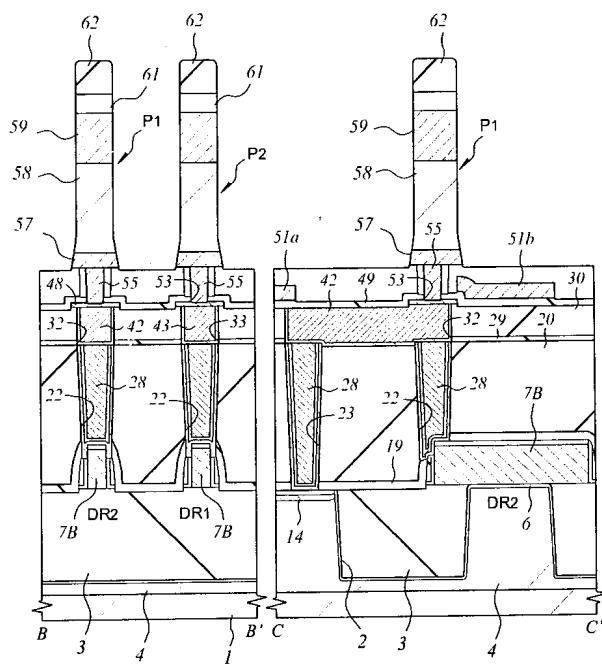

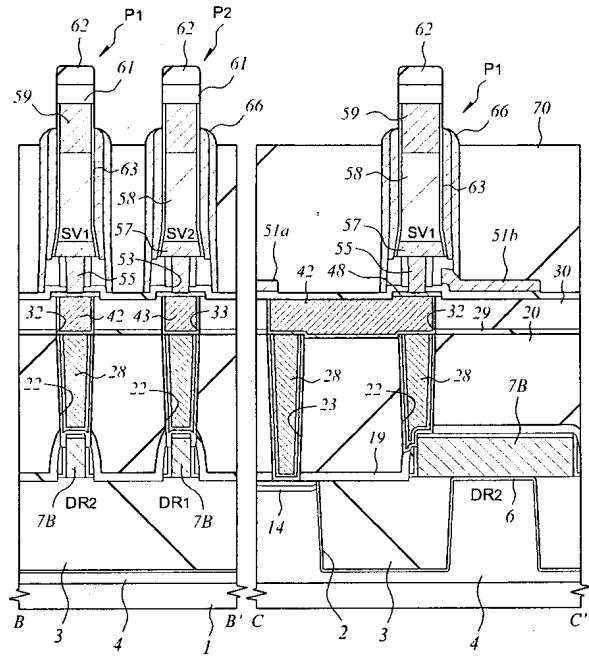

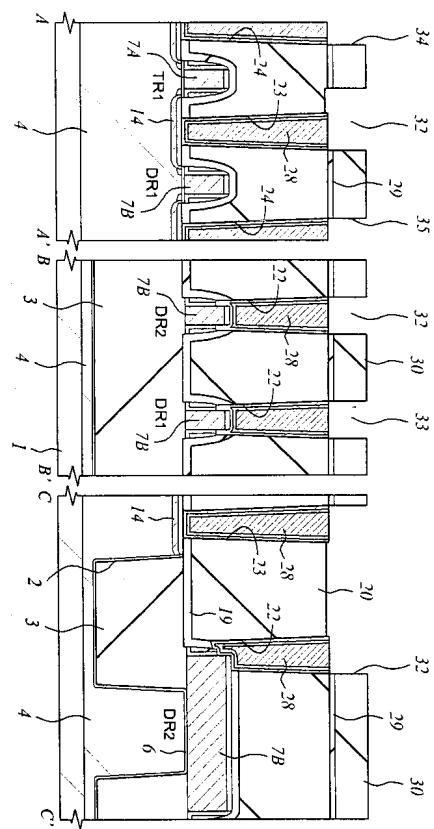

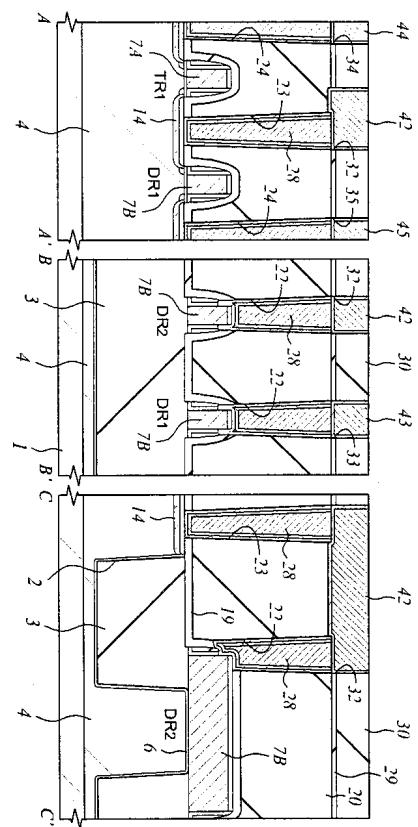

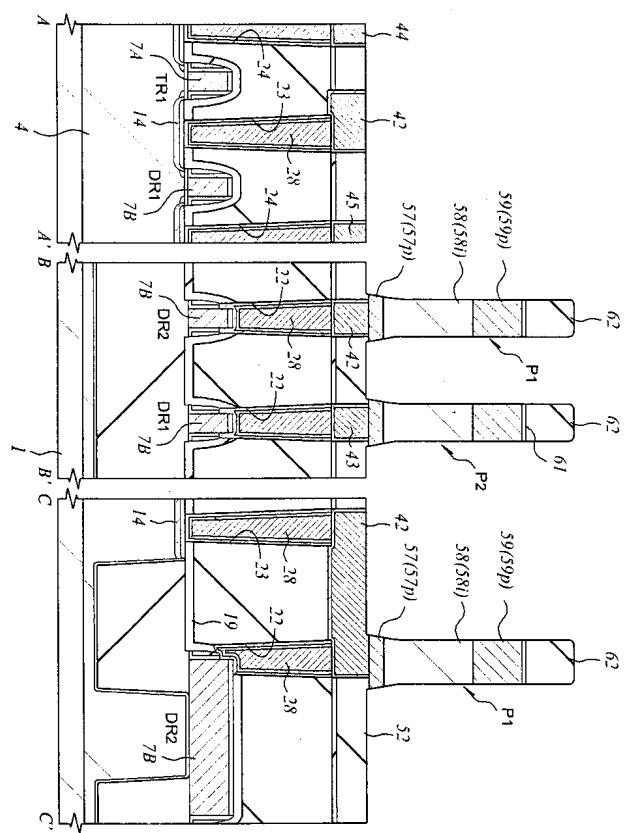

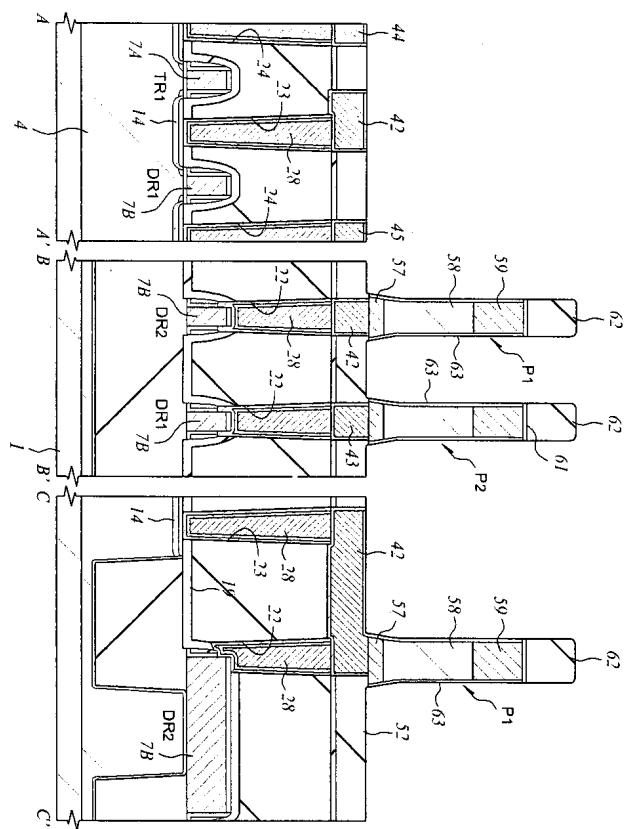

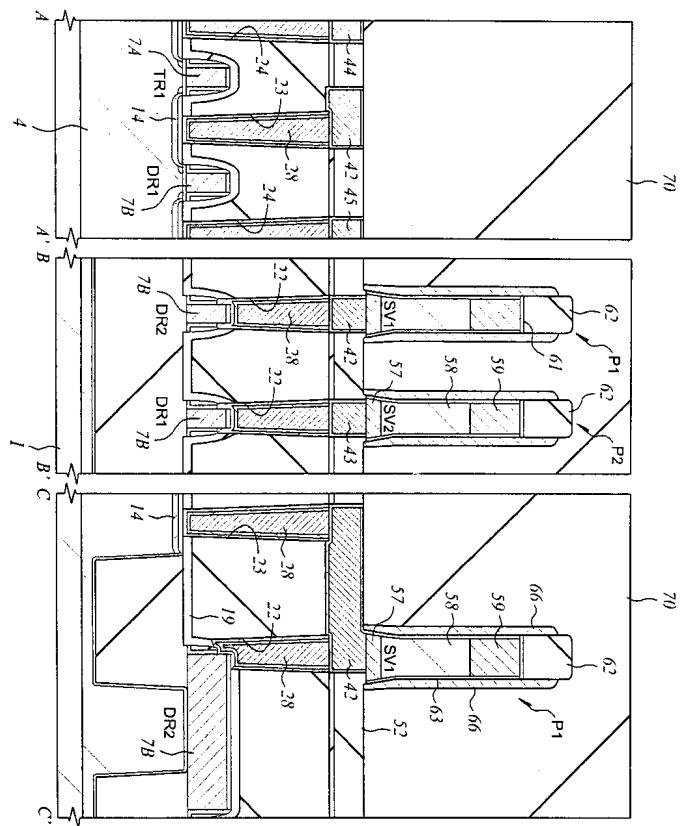

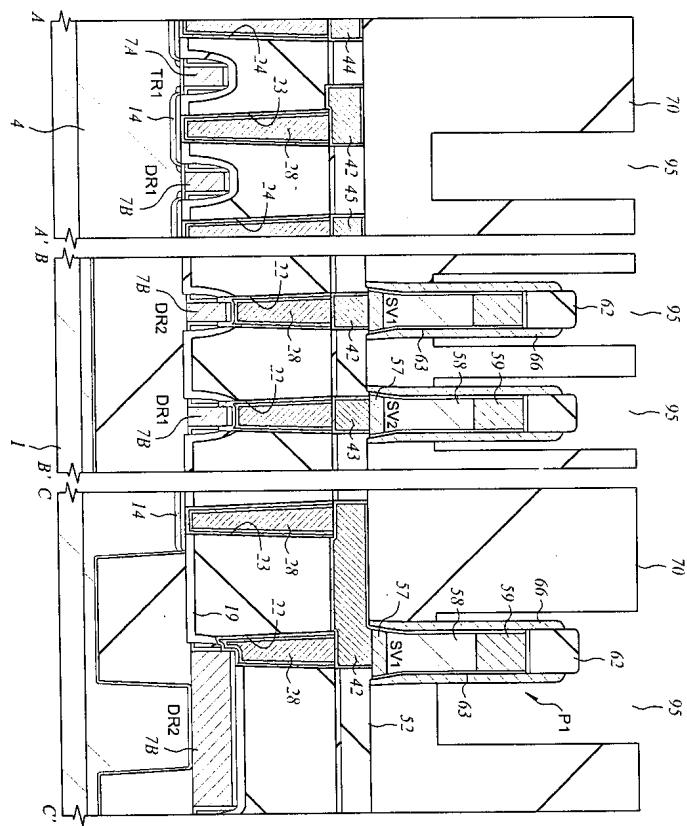

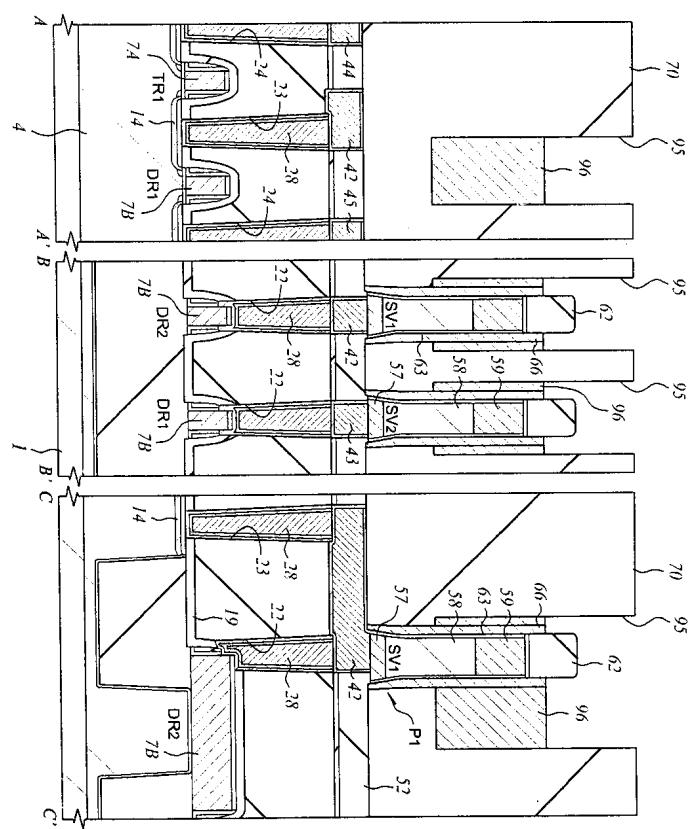

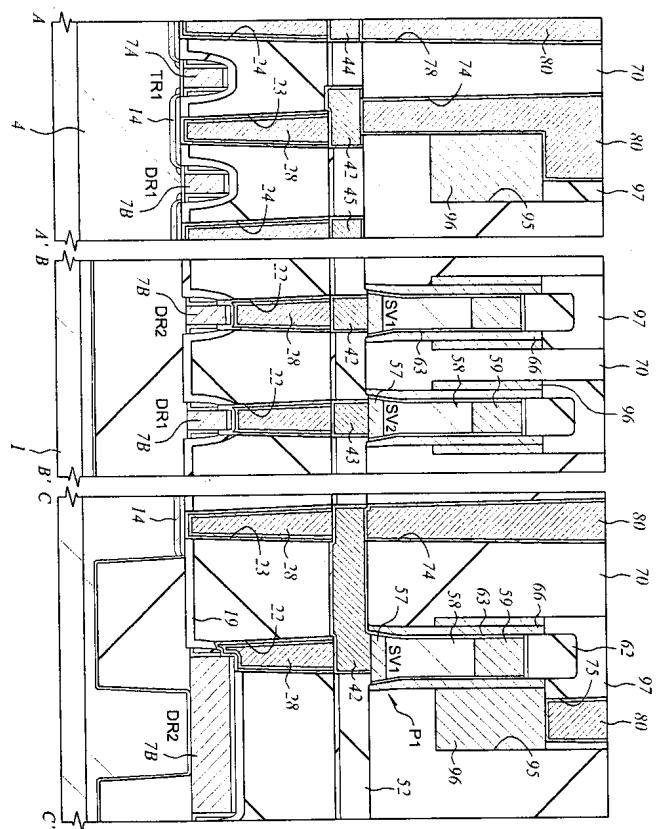

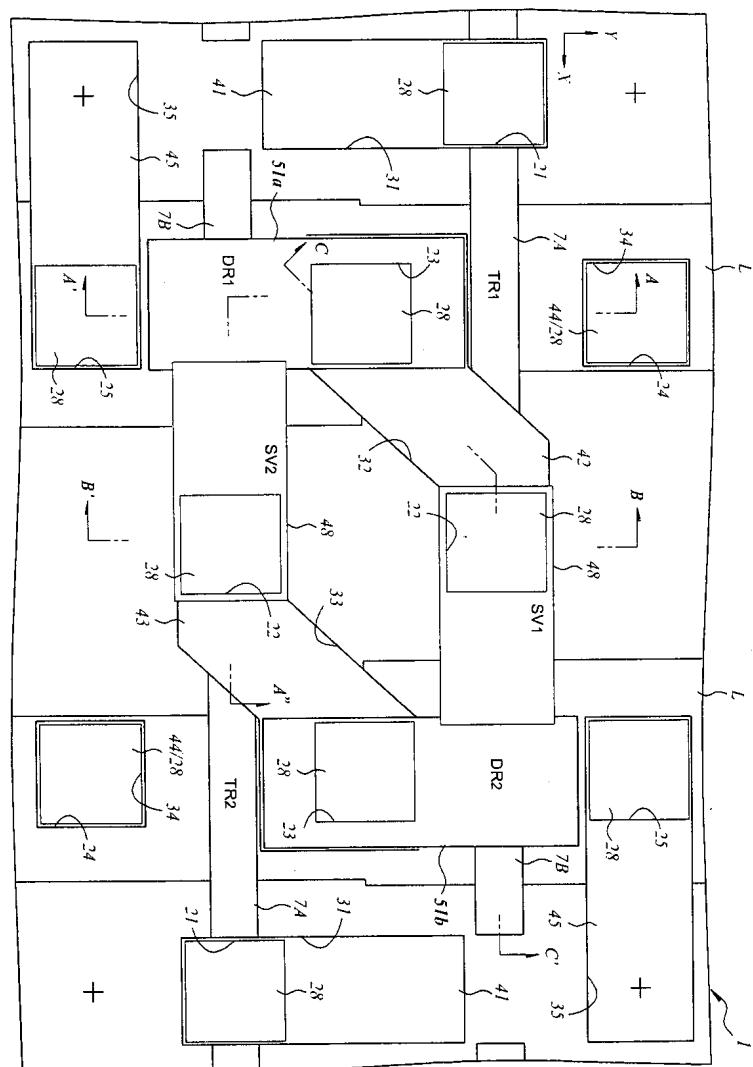

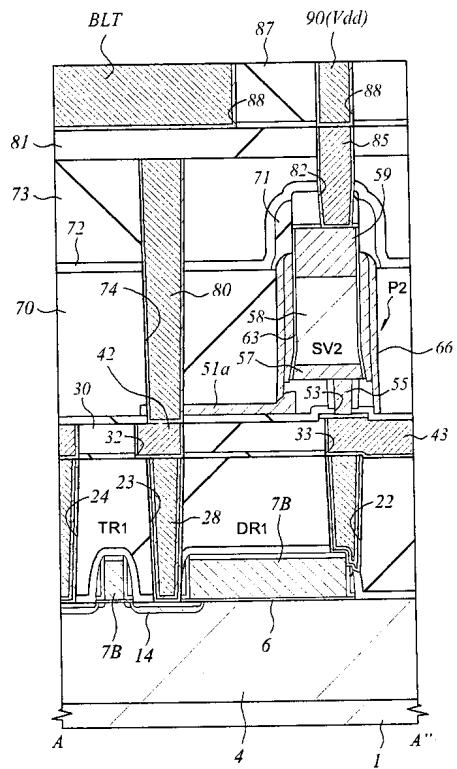

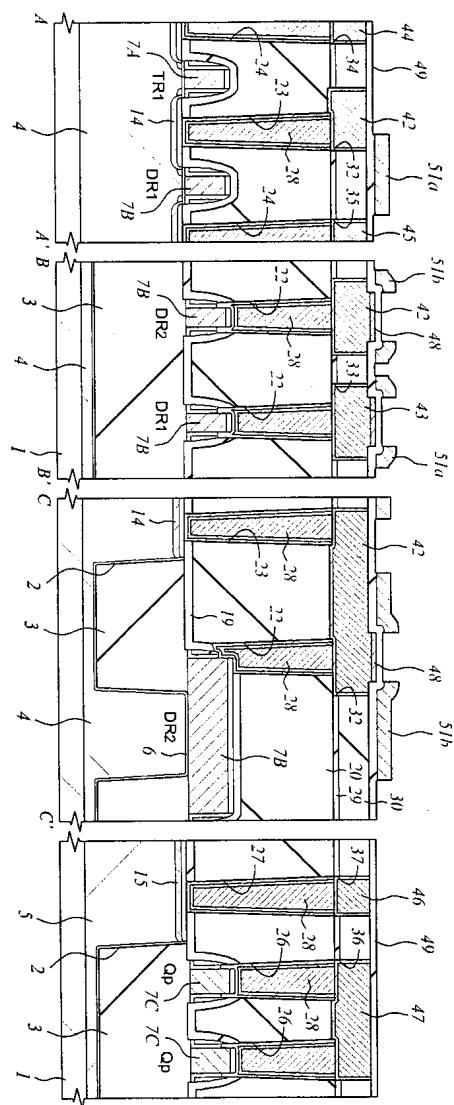

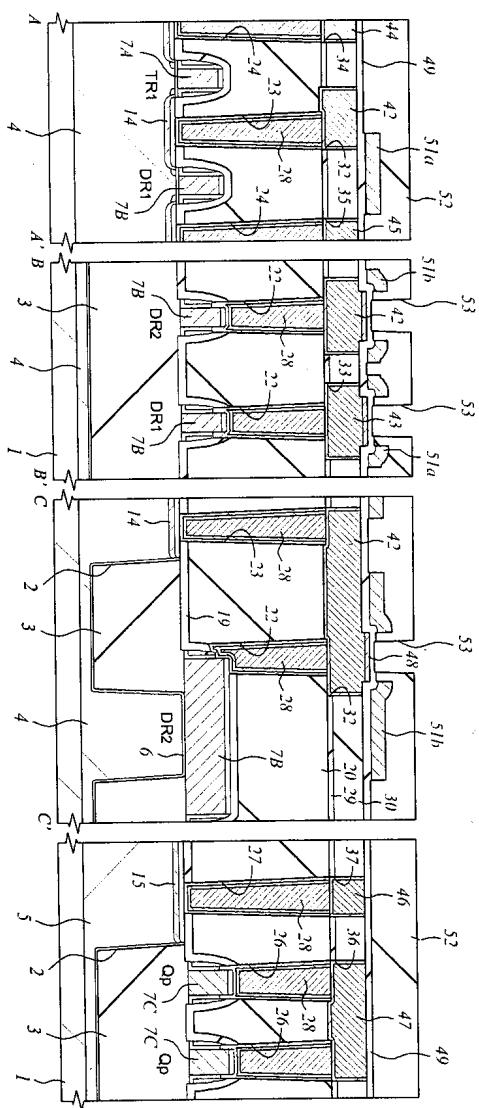

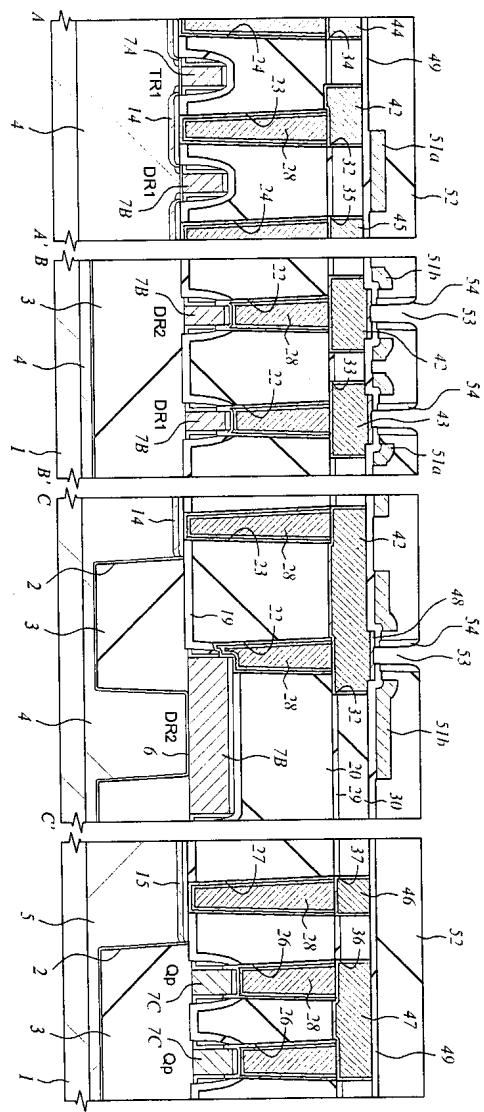

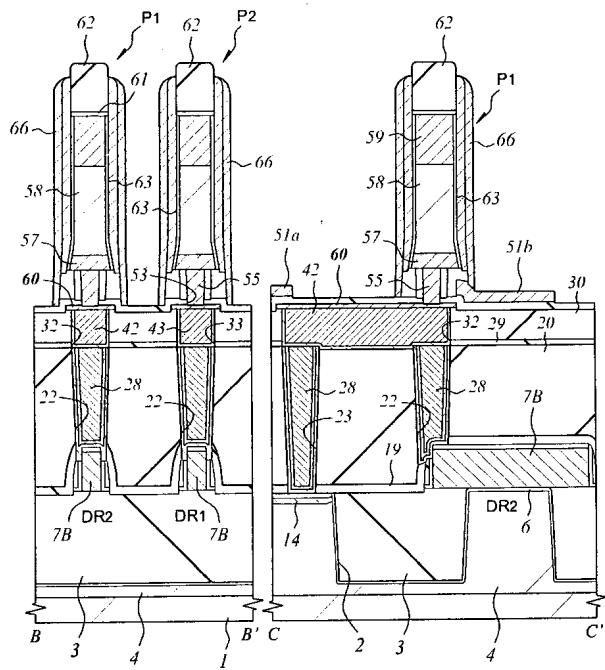

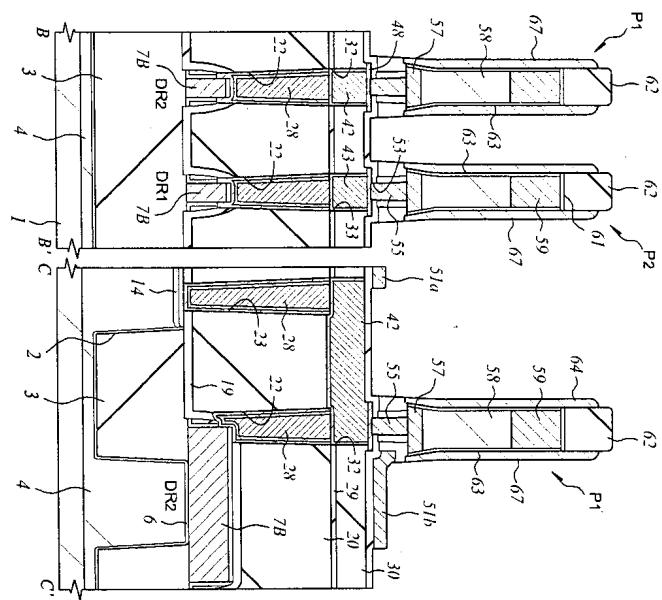

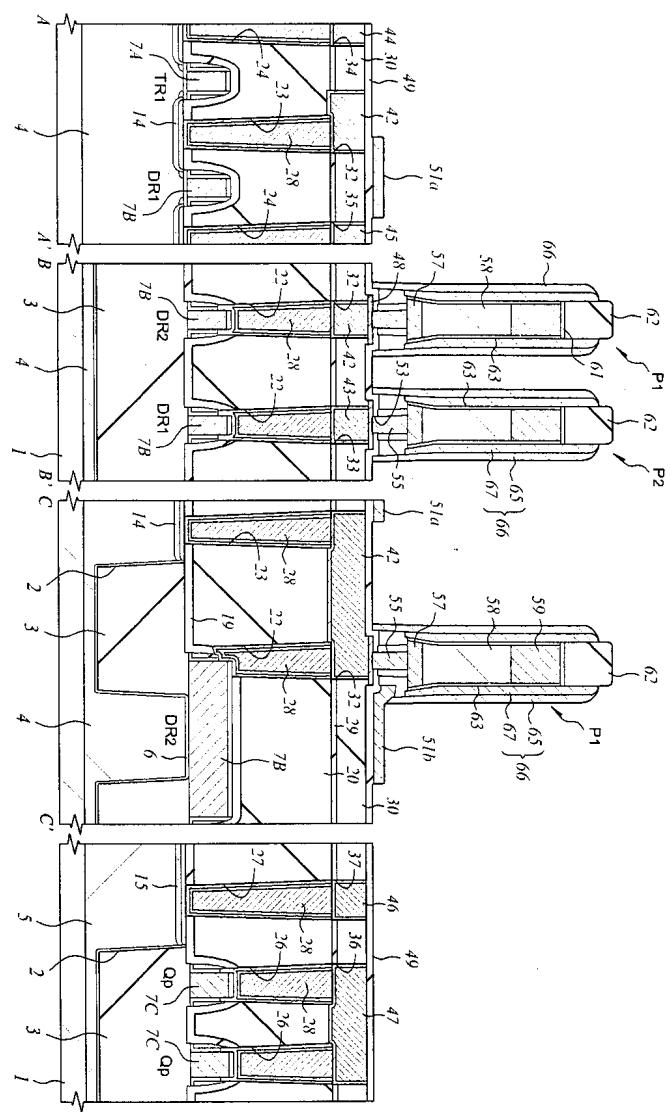

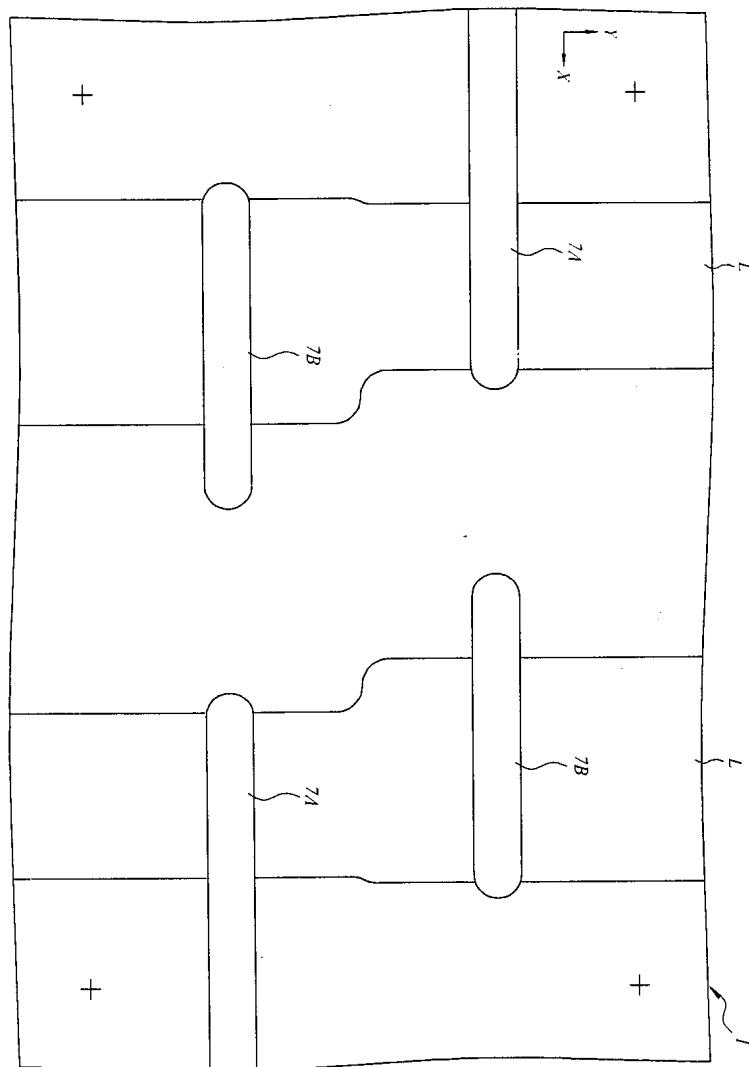

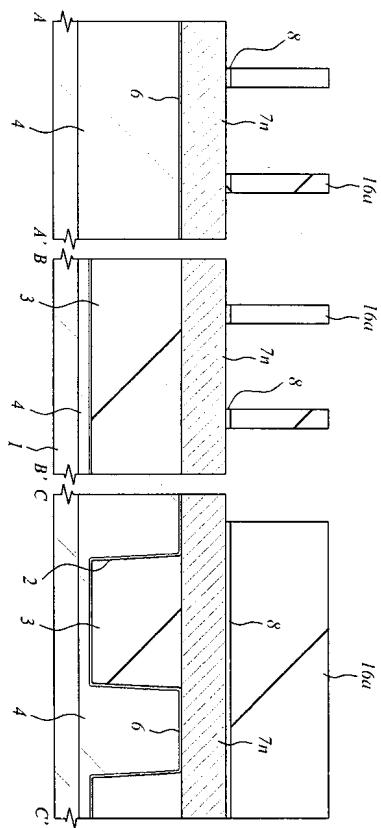

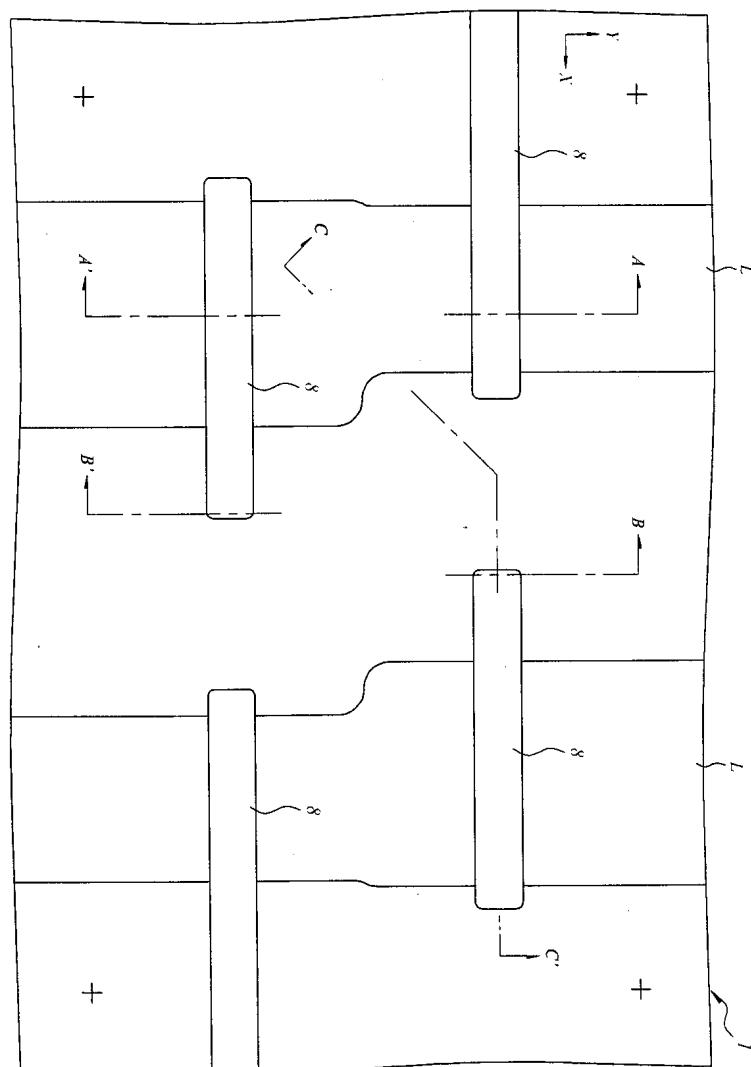

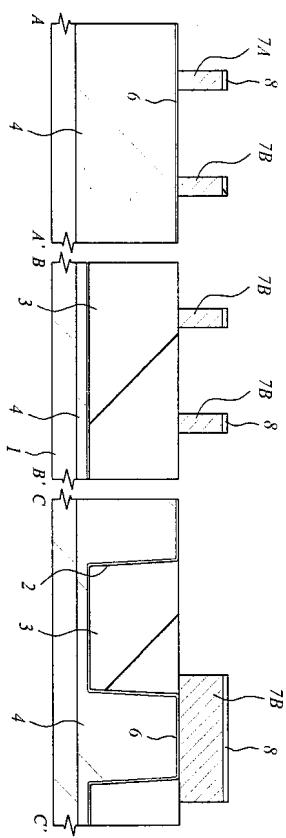

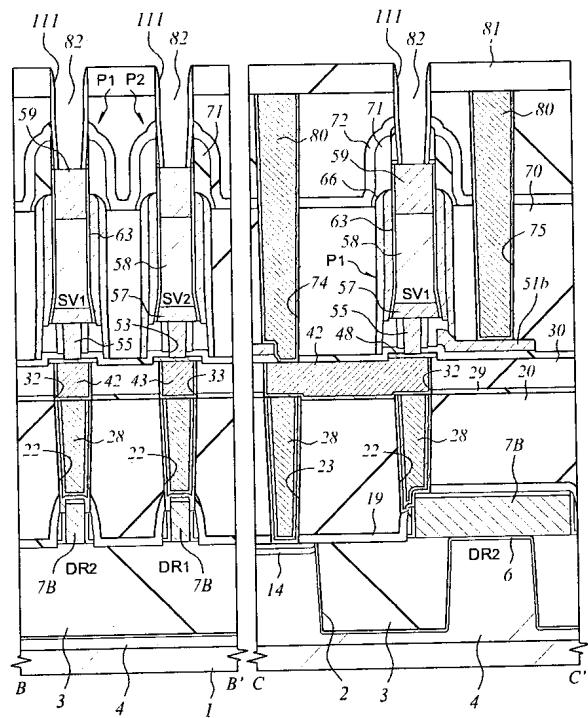

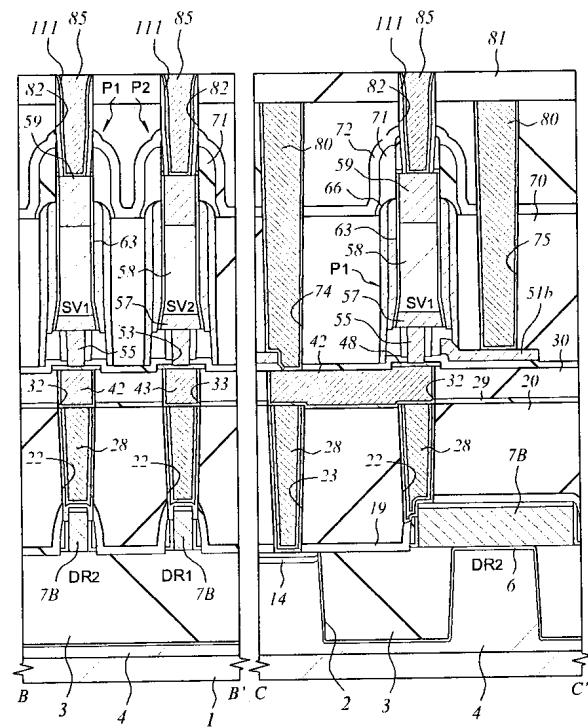

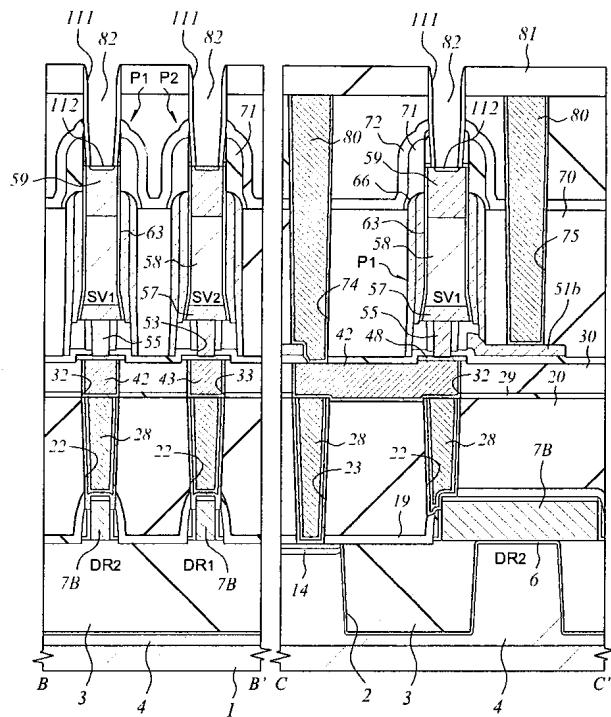

[0250] 도 2는 상기 메모리 셀(MC)의 구체적인 구조를 도시하는 평면도, 도 3의 좌측 부분은 도 2의 A-A'선을 따른 단

면도, 중앙 부분은 도 2의 B-B'선을 따른 단면도, 우측 부분은 도 2의 C-C'선을 따른 단면도이다. 또, 도 2에 도시한 4개의 (+) 표시로 둘러싼 구형 영역은 메모리 셀 1개의 점유 영역(메모리 셀 형성 영역)을 나타내고 있지만, 이 (+) 표시는 도면을 알기 쉽게 하기 위해 나타낸 표시로, 실제로 반도체 기판 상에 형성되는 것이 아니다. 또한, 도 2는 도면을 알기 쉽게 하기 위해서 메모리 셀을 구성하는 주요한 도전층과 이들 접속 영역만을 도시하고 있고, 도전층 사이에 형성된 절연막 등의 도시는 생략되어 있다.

[0251] 예를 들면, p형의 단결정 실리콘으로 이루어진 반도체 기판(이하, 기판이라 함)(1)의 주면에는 p형 웨(4)이 형성되어 있다. 이 p형 웨(4)의 소자 분리홈(2)에 의해 주위가 규정된 활성 영역(L)에는 메모리 셀(MC)의 일부를 구성하는 2개의 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>) 및 2개의 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>)이 형성되어 있다. 소자 분리홈(2)에는 예를 들면, 실리콘 산화막 등으로 이루어진 절연막(3)이 매립되어, 소자 분리부를 구성하고 있다.

[0252] 또, 도시하지 않지만, 주변 회로 영역의 기판(1)의 n형 웨(5)과 p형 웨에, 주변 회로를 구성하는 n채널 및 p채널 MISFET이 구성된다. 주변 회로용 MISFET에 의해 X 디코더 회로, Y 디코더 회로, 감지 증폭기 회로, 입출력 회로, 논리 회로 등이 구성되지만, 이들에 한하지 않고 마이크로 프로세서, CPU 등의 논리 회로를 구성해도 된다.

[0253] 도 2에 도시한 바와 같이, 활성 영역(L)은 도면의 세로 방향(Y 방향)으로 연장된 대략 장방형의 평면 패턴을 갖고 있으며, 메모리 셀 1개의 점유 영역에는 2개의 활성 영역(L, L)이 상호 평행하게 배치되어 있다. 2개의 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>) 및 2개의 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>) 중, 한쪽의 전송 MISFET(TR<sub>1</sub>) 및 구동 MISFET(DR<sub>1</sub>)은 한쪽의 활성 영역(L)에 형성되며, 이들 소스, 드레인의 한쪽을 상호 공유하고 있다. 또한, 다른 쪽의 전송 MISFET(TR<sub>2</sub>) 및 구동 MISFET(DR<sub>2</sub>)은 다른 쪽의 활성 영역(L)에 형성되고, 이들 소스, 드레인의 한쪽을 상호 공유하고 있다.

[0254] 한쪽의 전송 MISFET(TR<sub>1</sub>) 및 구동 MISFET(DR<sub>1</sub>)과, 다른 쪽의 전송 MISFET(TR<sub>2</sub>) 및 구동 MISFET(DR<sub>2</sub>)은, 소자 분리부를 개재하여 도면의 가로 방향(X 방향)으로 이격되어 배치되고, 또한 메모리 셀 형성 영역의 중심점에 대하여 점대칭으로 배치된다. 또한, 구동 MISFET(DR<sub>2</sub>) 및 구동 MISFET(DR<sub>1</sub>)의 게이트 전극(7B)은 도면의 가로 방향(X 방향)으로 연장되도록 배치되며, X 방향에서 한쪽의 전송 MISFET(TR<sub>1</sub>) 및 구동 MISFET(DR<sub>1</sub>)과, 다른 쪽의 전송 MISFET(TR<sub>2</sub>) 및 구동 MISFET(DR<sub>2</sub>) 사이의 소자 분리부 상에서 그 일단이 종단하여, 그 일단부 상에 후술하는 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)이 형성된다. 이것에 의해, 메모리 셀 사이즈를 축소할 수 있다. 또한, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)는 도면의 세로 방향(Y 방향)으로 인접하여 배치되며, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 상부에 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 소스에 전기적으로 접속되는 전원 전압선(Vdd)(90)이 도면의 세로 방향(Y 방향)으로 연장되도록 배치된다. 이것에 의해, 메모리 셀 사이즈를 축소할 수 있다. 또한, 전원 전압선(Vdd)(90)과 상보성 데이터선(BLT, BLB)를 동일한 배선층에 형성하며, 도면의 세로 방향(Y 방향)으로 연장되는 상보성 데이터선(BLT, BLB)의 사이에 전원 전압선(Vdd)(90)을 형성함으로써, 메모리 셀 사이즈를 축소할 수 있다. 즉, 도면의 가로 방향(X 방향)에서, 한쪽의 전송 MISFET(TR<sub>1</sub>) 및 구동 MISFET(DR<sub>1</sub>)과, 다른 쪽의 전송 MISFET(TR<sub>2</sub>) 및 구동 MISFET(DR<sub>2</sub>)과의 사이의 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)을 배치함과 함께, 도면의 가로 방향(X 방향)에서 상보성 데이터선(BLT, BLB)의 사이에 전원 전압선(Vdd)(90)을 배치함으로써 메모리 셀 사이즈를 축소할 수 있다.

[0255] 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>)은 주로 p형 웨(4)의 표면에 형성된 게이트 절연막(6)과, 게이트 절연막(6)의 상부에 형성된 게이트 전극(7A)과, 게이트 전극(7A)의 양측의 p형 웨(4)에 형성된 n<sup>+</sup>형 반도체 영역(14)(소스, 드레인)으로 구성되어 있다. 또한, 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>)은 주로 p형 웨(4)의 표면에 형성된 게이트 절연막(6)과, 게이트 절연막(6)의 상부에 형성된 게이트 전극(7B)과, 게이트 전극(7B)의 양측의 p형 웨(4)에 형성된 n<sup>+</sup>형 반도체 영역(14)(소스, 드레인)으로 구성되어 있다.

[0256] 전송 MISFET(TR<sub>1</sub>)의 소스, 드레인의 한쪽과, 구동 MISFET(DR<sub>1</sub>)의 드레인은 n<sup>+</sup>형 반도체 영역(14)에 의해 일체로 형성되며, 이 n<sup>+</sup>형 반도체 영역(14)의 상부에는 플리그(28)가 매립된 컨택트홀(23)이 형성되어 있다. 또한, 구동 MISFET(DR<sub>2</sub>)의 게이트 전극(7B)의 상부에는 플리그(28)가 매립된 컨택트홀(22)이 형성되며, 컨택트홀(22, 23)의 상부에는 컨택트홀(22) 내의 플리그(28)와 컨택트홀(23) 내의 플리그(28)를 접속하는 중간 도전층(42)이

형성되어 있다. 그리고, 전송 MISFET(TR<sub>1</sub>)의 소스, 드레인의 한쪽 및 구동 MISFET(DR<sub>1</sub>) 드레인인 n<sup>+</sup>형 반도체 영역(14)과 구동 MISFET(DR<sub>2</sub>)의 게이트 전극(7B)은, 이를 플러그(28, 28)와 중간 도전층(42)을 개재하여 상호 전기적으로 접속되어 있다.

[0257] 전송 MISFET(TR<sub>2</sub>)의 소스, 드레인의 한쪽과, 구동 MISFET(DR<sub>2</sub>)의 드레인은 n<sup>+</sup>형 반도체 영역(14)에 의해 일체로 형성되며, 이 n<sup>+</sup>형 반도체 영역(14)의 상부에는 플러그(28)가 매립된 컨택트홀(23)이 형성되어 있다. 구동 MISFET(DR<sub>1</sub>)의 게이트 전극(7B)의 상부에는 플러그(28)가 매립된 컨택트홀(22)이 형성되며, 컨택트홀(22, 23)의 상부에는 컨택트홀(22) 내의 플러그(28)와 컨택트홀(23) 내의 플러그(28)를 접속하는 중간 도전층(43)이 형성되어 있다. 그리고, 전송 MISFET(TR<sub>2</sub>)의 소스, 드레인의 한쪽 및 구동 MISFET(DR<sub>2</sub>)의 드레인인 n<sup>+</sup>형 반도체 영역(14)과 구동 MISFET(DR<sub>1</sub>)의 게이트 전극(7B)은 이를 플러그(28, 28)와 중간 도전층(43)을 개재하여 상호 전기적으로 접속되어 있다.

[0258] 플러그(28)는 예를 들면, 텅스텐(W) 등의 금속(메탈)막으로 구성되며, 중간 도전층(42, 43)은 예를 들면, 텅스텐(W) 등의 금속(메탈)막으로 구성된다. 이와 같이 중간 도전층(42, 43)을 금속막으로 구성함으로써, 저항을 저감할 수 있고, 메모리 셀의 특성을 향상시킬 수 있다.

[0259] 또한, 후술하는 바와 같이 플러그(28) 및 중간 도전층(42, 43)과 동층의 플러그(28) 및 중간 도전층(46, 47)에 의해, 주변 회로를 구성하는 n채널 및 p채널 MISFET의 소스·드레인 및 게이트 사이가 전기적으로 접속된다. 이것에 의해, 주변 회로를 구성하는 MISFET 간의 전기적 접속의 자유도를 향상시킬 수 있고, 고집적화가 가능해진다. 또한, 중간 도전층(46, 47)을 금속막으로 구성함으로써, MISFET 간의 접속 저항을 저감할 수 있고, 회로의 동작 스피드를 향상시킬 수 있다. 즉, 후술하는 바와 같이 상층에 형성된 금속(메탈) 배선층(89)은 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)보다도 상부에 형성되기 때문에, 그 상층의 금속 배선층(89)만으로, MISFET 간의 전기적 접속을 행하는 경우보다도, 배선의 자유도를 향상시킬 수 있음과 함께, 고집적화할 수 있다.

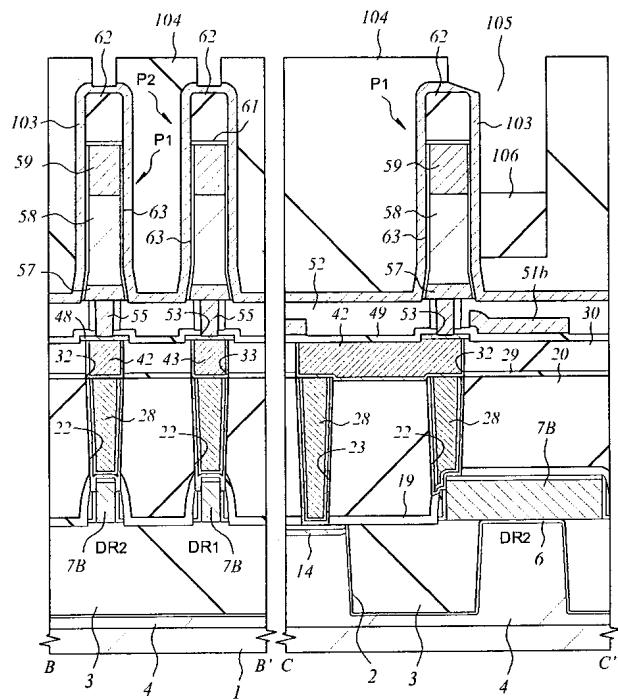

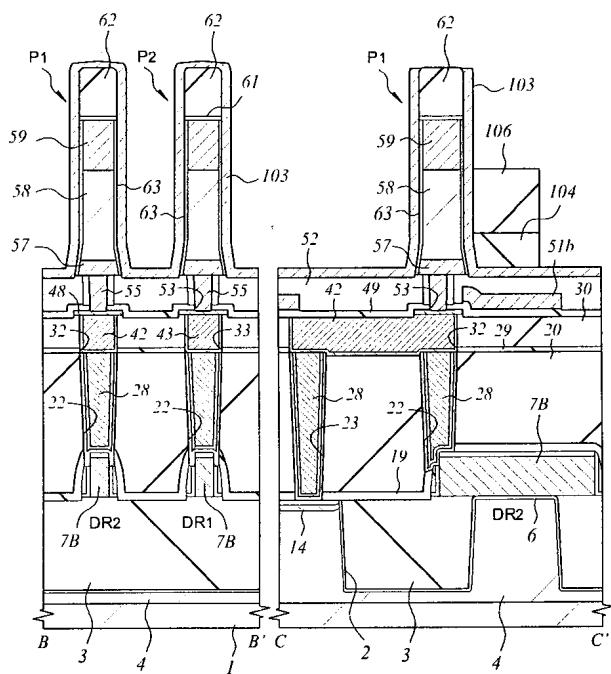

[0260] 구동 MISFET(DR<sub>2</sub>)의 게이트 전극(7B)의 일단부 상에는 종형 MISFET(SV<sub>1</sub>)이 형성되고, 구동 MISFET(DR<sub>1</sub>)의 게이트 전극(7B)의 일단부 상에는 종형 MISFET(SV<sub>2</sub>)이 형성되어 있다.

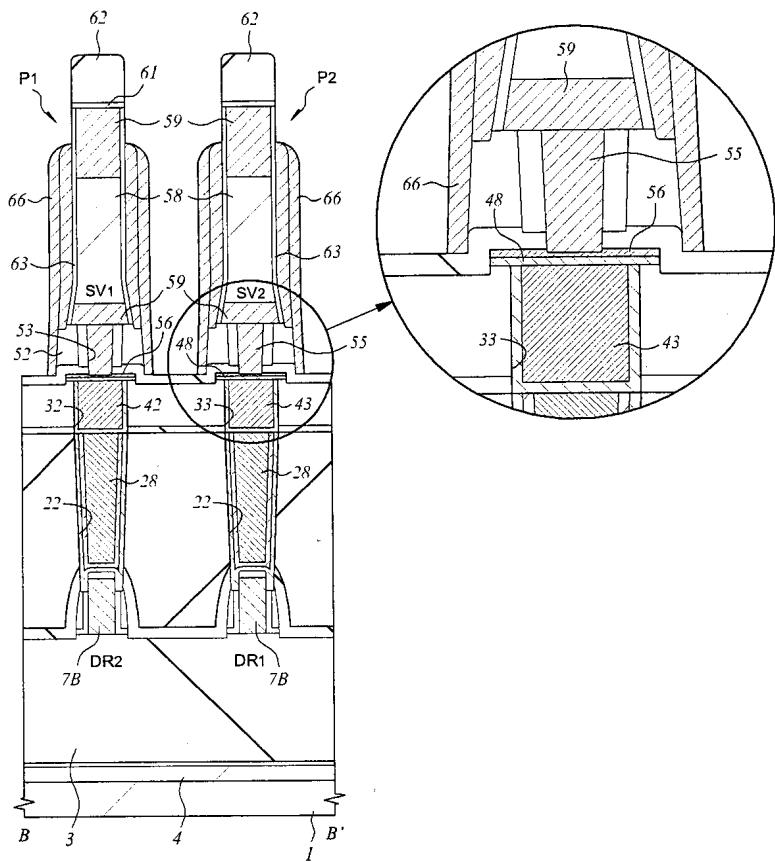

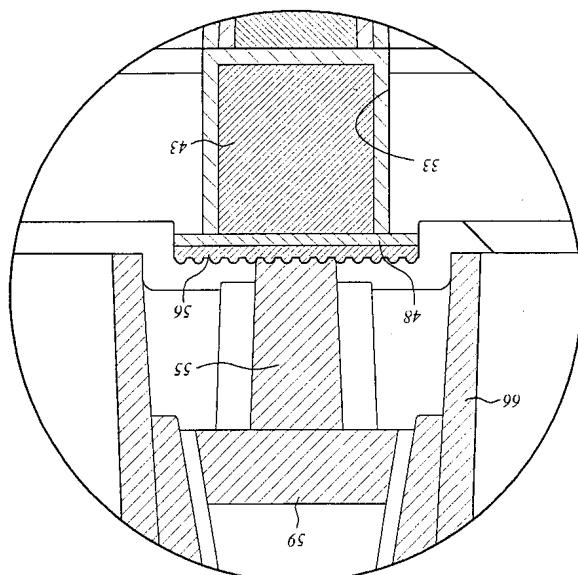

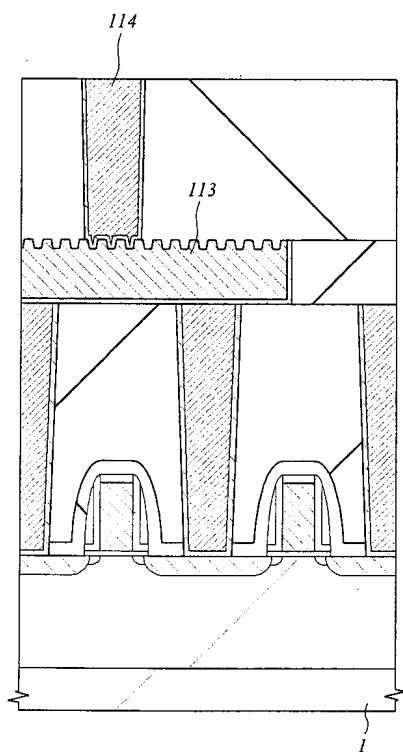

[0261] 종형 MISFET(SV<sub>1</sub>)은 하부 반도체층(드레인)(57), 중간 반도체층(58), 상부 반도체층(소스)(59)을 적층한 사각 기동형의 적층체(P<sub>1</sub>)와, 이 적층체(P<sub>1</sub>)의 측벽에 게이트 절연막(63)을 개재하여 형성된 게이트 전극(66)에 의해 구성되어 있다. 종형 MISFET(SV<sub>1</sub>)의 하부 반도체층(드레인)(57)은 그 하부에 형성된 플러그(55) 및 배리어층(48)을 개재하여 상기 중간 도전층(42)에 접속되어 있고, 또한 이 중간 도전층(42) 및 그 하부의 상기 플러그(28, 28)를 개재하여 상기 전송 MISFET(TR<sub>1</sub>)의 소스, 드레인의 한쪽 및 구동 MISFET(DR<sub>1</sub>)의 드레인인 n<sup>+</sup>형 반도체 영역(14)과, 구동 MISFET(DR<sub>2</sub>)의 게이트 전극(7B)에 전기적으로 접속되어 있다.

[0262] 종형 MISFET(SV<sub>2</sub>)은 하부 반도체층(드레인)(57), 중간 반도체층(58), 상부 반도체층(소스)(59)을 적층한 사각 기동형의 적층체(P<sub>2</sub>)와, 이 적층체(P<sub>2</sub>)의 측벽에 게이트 절연막(63)을 개재하여 형성된 게이트 전극(66)을 따라 구성되어 있다. 종형 MISFET(SV<sub>2</sub>)의 하부 반도체층(드레인)(57)은 그 하부에 형성된 플러그(55) 및 배리어층(48)을 개재하여 상기 중간 도전층(43)에 접속되어 있고, 또한 이 중간 도전층(43) 및 그 하부의 상기 플러그(28, 28)를 개재하여 상기 전송 MISFET(TR<sub>2</sub>)의 소스, 드레인의 한쪽 및 구동 MISFET(DR<sub>2</sub>)의 소스인 n<sup>+</sup>형 반도체 영역(14)과 구동 MISFET(DR<sub>1</sub>)의 게이트 전극(7B)에 전기적으로 접속되어 있다.

[0263] 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)은 하부 반도체층(57)이 드레인을 구성하며, 중간 반도체층(58)이 기판(채널 영역)을 구성하고, 상부 반도체층(59)이 소스를 구성하고 있다. 하부 반도체층(57), 중간 반도체층(58), 상부 반도체층(59) 각각은 실리콘막으로 구성되며, 하부 반도체층(57) 및 상부 반도체층(59)은 p형으로 도핑되어 p형 실리콘 막으로 구성된다. 즉, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)은 실리콘막으로 형성된 p채널형 MISFET으로 구성된다.

[0264] 또한, 플러그(55)를 구성하는 실리콘막은 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 하부 반도체층(57)을 구성하는 다결정 실리콘

막과 동일한 도전형(p형)으로 하기 위해서는, 성막 시 또는 성막 후에 붕소를 도핑하여 p형 실리콘막으로 구성된다.

[0265] 소스인 하부 반도체층(57)은 실리콘막으로 형성되어 있기 때문에, 실리콘막(플러그(55))과 텅스텐으로 이루어진 중간 도전층(42, 43)과의 계면에서 원하지 않는 실리사이드 반응이 생기는 것을 방지하기 위해서, 이들 사이에 배리어층(48)을 형성하고 있다. 이것에 의해, 텅스텐으로 이루어진 중간 도전층(42, 43)의 상부에, 실리콘막으로 형성된 하부 반도체층(57), 중간 반도체층(58), 상부 반도체층(59)을 형성할 수 있고, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)을 중간 도전층(42, 43)의 상부에 형성할 수 있다. 즉, 중간 도전층(42, 43)은 텅스텐(W) 등의 금속막으로 구성하고, 배리어층(48)을 개재하여 중간 도전층(42, 43)의 상부에 실리콘막으로 형성된 종형 MISFET을 형성함으로써, MISFET 간의 접속 저항을 저감할 수 있고, 메모리 셀의 특성을 향상시킬 수 있음과 함께, 메모리 셀 사이즈를 축소할 수 있다.

[0266] 또, 배리어층(48)은 예를 들면, WN막, Ti막, TiN막의 단층막, 또는 WN막과 W막과의 적층막, TiN막과 W막과의 적층막 등, 이들 막을 2 종류 이상 적층한 적층막으로 구성된다.

[0267] 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>) 각각의 게이트 전극(66)은 사각 기둥형의 적층체(P<sub>1</sub>, P<sub>2</sub>) 각각의 측벽을 둘러싸도록 형성된다. 또, 후술하는 바와 같이 게이트 전극(66)은 측벽 형상으로, 사각 기둥형의 적층체(P<sub>1</sub> P<sub>2</sub>)에 대하여 자기 정합적으로 형성된다.

[0268] 이와 같이, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)은 소스, 기판(채널 영역), 드레인인 기판의 주면에 대하여 수직 방향으로 적층되며, 채널 전류가 기판의 주면에 대하여 수직 방향으로 흐르는, 소위 종형 채널 MISFET을 구성한다. 즉, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 채널 길이 방향은 기판의 주면에 대하여 수직인 방향이고, 채널 길이는 기판의 주면에 대하여 수직인 방향에서의 하부 반도체층(57)과 상부 반도체층(59) 사이의 길이로 규정된다. 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 채널 폭은 사각 기둥형의 적층체의 측벽 일주의 길이로 규정된다. 이것에 의해, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 채널 폭을 크게 할 수 있다.

[0269] 종형 MISFET(SV<sub>1</sub>)의 게이트 전극(66)은 그 하단부에 형성된 게이트 인출 전극(51)(51b)에 전기적으로 접속되어 있다. 후술하는 바와 같이, 종형 MISFET(SV<sub>2</sub>)의 게이트 전극(66)은 사각 기둥형의 적층체(P<sub>1</sub>)에 대하여 자기 정합적으로 측벽 형상으로 형성하는 공정을 이용하여, 종형 MISFET(SV<sub>1</sub>)의 게이트 전극(66)은 게이트 전극(66)의 하부에서, 예를 들면, 게이트 전극(66)의 저면이 게이트 인출 전극(51)(51b)에 대하여 자기 정합적으로 접속된다. 이것에 의해, 메모리 셀 사이즈를 축소할 수 있다.

[0270] 이 게이트 인출 전극(51)(51b)의 상부에는 플러그(80)가 매립된 관통 홀(75)이 형성되어 있다. 또한, 이 플러그(80)는 그 일부가 상기 중간 도전층(43)에 접속되어 있고, 종형 MISFET(SV<sub>1</sub>)의 게이트 전극(66)은 게이트 인출 전극(51)(51b), 플러그(80), 중간 도전층(43) 및 그 하부의 상기 플러그(28, 28)를 개재하여 상기 전송 MISFET(TR<sub>2</sub>)의 소스, 드레인의 한쪽 및 구동 MISFET(DR<sub>2</sub>)의 드레인인 n<sup>+</sup>형 반도체 영역(14)과, 구동 MISFET(DR<sub>1</sub>)의 게이트 전극(7B)에 전기적으로 접속되어 있다. 후술하는 바와 같이, 플러그(80)는 플러그(80)보다 상층의 배선과는 전기적으로 접속되지 않고, 상보성 데이터선(BLT)이 평면적으로 보았을 때 플러그(80)와 중첩하도록, 플러그(80)의 상부를 도면의 세로 방향(Y 방향)으로 연장되어 배치된다. 이와 같이 플러그(80)의 바닥부를 이용하여, 게이트 인출 전극(51)(51b)과 중간 도전층(43)을 전기적으로 접속함으로써, 메모리 셀 사이즈를 축소할 수 있다. 또한, 플러그(80)의 상부에 상보성 데이터선(BLT)을 배치할 수가 있어서, 메모리 셀 사이즈를 축소할 수 있다.

[0271] 종형 MISFET(SV<sub>2</sub>)의 게이트 전극(66)은 그 하단부에 형성된 게이트 인출 전극(51)(51a)에 전기적으로 접속되어 있다. 후술하는 바와 같이, 종형 MISFET(SV<sub>2</sub>)의 게이트 전극(66)은 사각 기둥형의 적층체(P<sub>2</sub>)에 대하여 자기 정합적으로 측벽 형상으로 형성하는 공정을 이용하여, 종형 MISFET(SV<sub>2</sub>)의 게이트 전극(66)은 게이트 전극(66)의 하부에서, 예를 들면, 게이트 전극(66)의 저면이 게이트 인출 전극(51)(51a)에 대하여 자기 정합적으로 접속된다. 이것에 의해, 메모리 셀 사이즈를 축소할 수 있다.

[0272] 상기 게이트 인출 전극(51)(51a)의 상부에는 플러그(80)가 매립된 관통 홀(74)이 형성되어 있다. 또한, 이 플

러그(80)는 그 일부가 상기 중간 도전층(42)에 접속되어 있고, 종형 MISFET(SV<sub>2</sub>)의 게이트 전극(66)은 게이트 인출 전극(51)(51a), 플러그(80), 중간 도전층(42) 및 그 하부의 상기 플러그(28, 28)를 개재하여 상기 전송 MISFET(TR<sub>1</sub>)의 소스, 드레인의 한쪽 및 구동 MISFET(DR<sub>2</sub>)의 드레인인 n<sup>+</sup>형 반도체 영역(14)과, 구동 MISFET(DR<sub>2</sub>)의 게이트 전극(7B)에 전기적으로 접속되어 있다.

[0273] 후술하는 바와 같이, 플러그(80)는 플러그(80)보다 상층의 배선(금속 배선층)은 전기적으로 접속되지 않고, 상보성 데이터선(BLB)가 평면적으로 볼 때 플러그(80)와 중첩되도록, 플러그(80)의 상부를 연장하여 배치된다. 이와 같이, 플러그(80)의 바닥부를 이용하여, 게이트 인출 전극(51)(51a)과 중간 도전층(42)을 전기적으로 접속함으로써, 메모리 셀 사이즈를 축소할 수 있다. 또한, 플러그(80)의 상부에 상보성 데이터선(BLB)를 배치할 수가 있고, 메모리 셀 사이즈를 축소할 수 있다. 플러그(80)는 예를 들면, 텅스텐(W) 등의 금속(메탈)막으로 구성된다.

[0274] 이와 같이, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(66)은 게이트 전극(66)의 하부에서, 예를 들면, 게이트 전극(66)의 저면이 도전막인 게이트 인출 전극(51)(51a, 51b)에 접촉하도록, 게이트 인출 전극(51)(51a, 51b)에 대하여 자기 정합적으로 측벽 형상으로 접속된다. 이것에 의해, 메모리 셀 사이즈를 축소할 수 있다.

[0275] 상기 구동 MISFET의 상부에 절연막을 개재하여 형성된 상기 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트(66)는 게이트(66)의 하부에서 하층의 도전막인 게이트 인출 전극(51)(51a, 51b)에 전기적으로 접속된다. 또한, 상기 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트(66)와, 상기 구동 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트(7B) 또는 드레인(14)과의 사이의 전류 패스는 도전막인 게이트 인출 전극(51)(51a, 51b)을 개재하여 상기 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트(66)의 하부를 경유하여 형성된다. 즉, 상기 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트(66)는 게이트 인출 전극(51)(51a, 51b)에 대하여 자기 정합적으로 접속되며, 또한 그 게이트(66)의 하부에서, 전류 패스가 기판의 주면에 대하여 수직 방향으로 흐르도록 게이트 인출 전극(51)(51a, 51b), 도전막인 중간 도전층(42, 43), 플러그(28)를 경유하여, 그 하부에 형성되는 상기 구동 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트(7B) 또는 드레인(14)에 전기적으로 접속된다. 즉, 상기 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트(66)는 플러그(28)의 상부에, 플러그(28) 및 상기 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트(66)는, 평면적으로 중첩되도록 배치된다. 이것에 의해, 메모리 셀의 특성을 향상시킬 수 있음과 함께, 메모리 셀 사이즈를 축소할 수 있다.

[0276] 또한, 플러그(80)는 플러그(28)의 상부에, 플러그(28)와 플러그(80)는, 평면적으로 중첩되도록 배치된다. 이것에 의해, 메모리 셀의 특성을 향상시킬 수 있음과 함께, 메모리 셀 사이즈를 축소할 수 있다.

[0277] 종형 MISFET(SV<sub>1</sub>)의 일부를 구성하는 적층체(P<sub>1</sub>) 및 종형 MISFET(SV<sub>2</sub>)의 일부를 구성하는 적층체(P<sub>2</sub>) 각각의 상부에는 중간 절연막을 개재하여 전원 전압선(Vdd)(90)이 형성되어 있다. 전원 전압선(Vdd)(90)은 적층체(P<sub>1</sub>) 상부의 관통 홀(82) 내에 매립된 플러그(85)를 개재하여 종형 MISFET(SV<sub>1</sub>)의 상부 반도체층(소스)(59)와 전기적으로 접속되며, 또한 적층체(P<sub>2</sub>) 상부의 관통 홀(82) 내에 매립된 플러그(85)를 개재하여 종형 MISFET(SV<sub>2</sub>)의 상부 반도체층(소스)(59)과 전기적으로 접속되어 있다.

[0278] 상기 전원 전압선(Vdd)(90)과 동일한 배선층에는 상보성 데이터선(BLT, BLB)이 형성되어 있다. 전원 전압선(Vdd)(90) 및 상보성 데이터선(BLT, BLB)은 도 2의 Y 방향을 따라 평행하게 연장되어 있다. 즉, 상보성 데이터선(BLT)은 평면적으로 볼 때 한쪽의 전송 MISFET(TR<sub>1</sub>) 및 구동 MISFET(DR<sub>1</sub>)과 중첩되도록 전송 MISFET(TR<sub>1</sub>) 및 구동 MISFET(DR<sub>1</sub>)의 상부를 도 2의 Y 방향을 따라 연장되도록 배치된다. 상보성 데이터선(BLB)은 평면적으로 볼 때 다른 쪽의 전송 MISFET(TR<sub>2</sub>) 및 구동 MISFET(DR<sub>2</sub>)과 중첩되도록 전송 MISFET(TR<sub>2</sub>) 및 구동 MISFET(DR<sub>2</sub>)의 상부를 도 2의 Y 방향을 따라 연장되도록 배치된다. 이것에 의해, 메모리 셀 사이즈를 축소할 수 있다.

[0279] 상보성 데이터선(BLT)은 상기 플러그(85)와 동층의 플러그(85), 상기 플러그(80)와 동층의 플러그(80), 상기 중간 도전층(42, 43)과 동층의 중간 도전층(44), 및 상기 플러그(28)와 동층의 플러그(28)를 개재하여 전송 MISFET(TR<sub>1</sub>)의 소스, 드레인(n<sup>+</sup>형 반도체 영역(14))의 다른 쪽과 전기적으로 접속되어 있다. 또한, 상보성 데이터선(BLB)은 상기 플러그(85)와 동층의 플러그(85), 상기 플러그(80)와 동층의 플러그(80), 상기 중간 도전층(42, 43)과 동층의 중간 도전층(44), 및 상기 플러그(28)와 동층의 플러그(28)를 개재하여 전송 MISFET(TR<sub>2</sub>)의

소스, 드레인( $n^+$ 형 반도체 영역(14))의 다른 쪽과 전기적으로 접속되어 있다. 전원 전압선(Vdd)(90) 및 상보성 데이터선(BLT, BLB)은 예를 들면, 구리(Cu)를 주성분으로 한 금속막으로 구성되어 있다.

[0280] 이와 같이 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)은 도면의 세로 방향(Y 방향)으로 인접하여 배치되어, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 상부에, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 소스에 전기적으로 접속된 전원 전압선(Vdd)(90)이 도면의 세로 방향(Y 방향)으로 연장되도록 배치된다. 이것에 의해, 메모리 셀 사이즈를 축소할 수 있다. 또한, 전원 전압선(Vdd)(90)과 상보성 데이터선(BLT, BLB)을 동일한 배선층에 형성하여, 도면의 세로 방향(Y 방향)으로 연장된 상보성 데이터선(BLT, BLB)의 사이에 전원 전압선(Vdd)(90)을 형성함으로써, 메모리 셀 사이즈를 축소할 수 있다. 즉, 도면의 가로 방향(X 방향)에서, 한쪽의 전송 MISFET(TR<sub>1</sub>) 및 구동 MISFET(DR<sub>1</sub>)과, 다른 쪽의 전송 MISFET(TR<sub>2</sub>) 및 구동 MISFET(DR<sub>2</sub>)과의 사이의 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)을 배치하고, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 상부에 도면의 세로 방향(Y 방향)으로 연장된 전원 전압선(Vdd)(90)을 배치하며, 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>) 및 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>)의 상부에 도면의 세로 방향(Y 방향)으로 연장된 상보성 데이터선(BLT, BLB)을 배치함으로써, 메모리 셀 사이즈를 축소할 수 있다.

[0281] 상기 전원 전압선(Vdd)(90) 및 상보성 데이터선(BLT, BLB)의 상층에는 절연막(93)을 개재하여, 도 2의 X 방향을 따라 평행하게 연장된 워드선(WL) 및 기준 전압선(Vss)(91)이 형성되어 있다. 워드선(WL)은 도 2의 Y 방향에서, 기준 전압선(Vss)(91)의 사이에 배치된다. 워드선(WL)은 상기 플러그나 중간 도전층과 동층의 플러그 및 중간 도전층을 개재하여 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>)의 게이트 전극(7A)과 전기적으로 접속되고, 기준 전압선(Vss)(91)은 동일하게 상기 플러그나 중간 도전층과 동층의 플러그 및 중간 도전층을 개재하여 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>)의  $n^+$ 형 반도체 영역(소스)(14)에 전기적으로 접속되어 있다. 워드선(WL) 및 기준 전압선(Vss)(91)은 예를 들면, 구리(Cu)를 주성분으로 한 금속막으로 구성되어 있다.

[0282] 플러그(80, 85), 전원 전압선(Vdd)(90) 및 상보성 데이터선(BLT, BLB)과 동층의 플러그(80, 83, 85) 및 제1 금속 배선층(89)에 의해, 주변 회로를 구성하는 n채널 및 p채널 MISFET의 소스·드레인 및 게이트 사이가 전기적으로 접속된다. 플러그(도시하지 않음), 기준 전압선(91)(Vss), 워드선(WL)과 동층의 플러그 및 제2 금속 배선층에 의해, 주변 회로를 구성하는 n채널 및 p채널 MISFET의 소스·드레인 및 게이트 사이가 전기적으로 접속된다. 제1 금속 배선층(89)과 제2 금속 배선층은 플러그(도시하지 않음)에 의해 전기적으로 접속된다.

[0283] 이와 같이 주변 회로를 구성하는 MISFET 간의 전기적 접속을 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)보다도 하부에 형성되는 플러그(28) 및 중간 도전층(46, 47)으로 행함과 함께, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)보다도 상부에 형성된 플러그, 제1 및 제2 금속 배선층을 이용하여 행함으로써, 배선의 자유도를 향상시킬 수 있고, 고집적화할 수 있다. 또한, MISFET 간의 접속 저항을 저감할 수 있고, 회로의 동작 스피드 향상시킬 수 있다.

[0284] 이와 같이, 본 실시예의 SRAM은 2개의 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>) 및 2개의 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>)을 기판(1)의 p형 웨爾(4)에 형성하고, 이들 4개의 MISFET(TR<sub>1</sub>, TR<sub>2</sub>, DR<sub>1</sub>, DR<sub>2</sub>)의 상부에 2개의 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)을 형성하고 있다.

[0285] 이 구성에 의해, 메모리 셀의 점유 면적은 실질적으로 4개의 MISFET(TR<sub>1</sub>, TR<sub>2</sub>, DR<sub>1</sub>, DR<sub>2</sub>)의 점유 면적에 상당하기 때문에, 6개의 MISFET으로 구성된 동일한 디자인 률의 완전 CMOS형 메모리 셀에 비해 1개의 메모리 셀의 점유 면적을 축소할 수 있다. 또, 본 실시예의 SRAM은 p채널형의 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)을 4개의 MISFET(TR<sub>1</sub>, TR<sub>2</sub>, DR<sub>1</sub>, DR<sub>2</sub>)의 상측에 형성하기 때문에, p채널형의 종형 MISFET을 기판의 n형 웨爾에 형성하는 완전 CMOS형 메모리 셀과 다르고, 메모리 셀 1개의 점유 영역 내에 p형 웨爾과 n형 웨爾을 분리시키는 영역이 불필요하다. 따라서, 메모리 셀의 점유 면적을 더 축소할 수 있으므로, 고속 및 대용량의 SRAM을 실현할 수 있다.

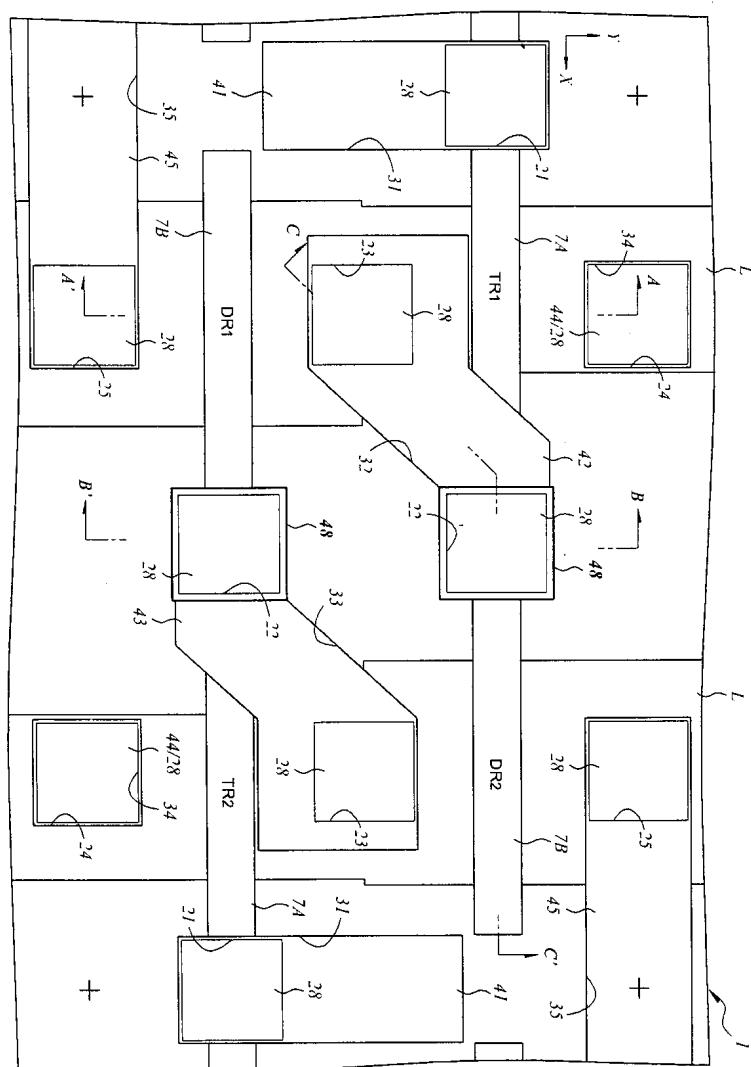

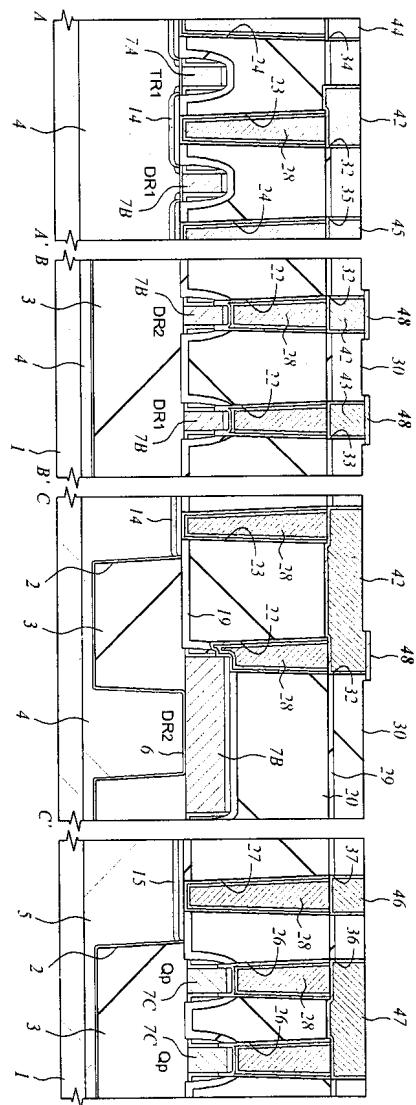

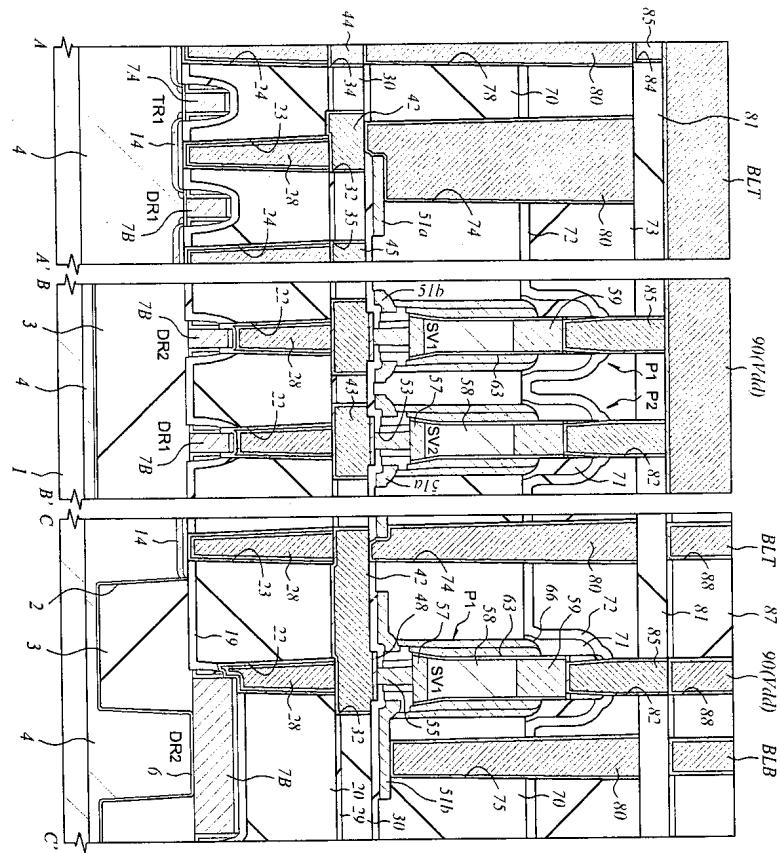

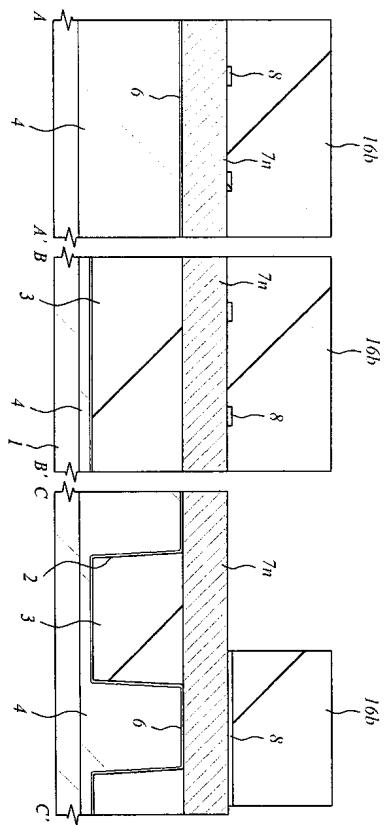

[0286] 다음으로, 도 4~도 61를 이용하여 본 실시예의 SRAM의 보다 상세한 구조를 그 제조 방법과 함께 설명한다. SRAM의 제조 방법을 설명하는 각 단면도에서, 부호 A, A'를 붙인 부분은 상기 도 2의 A-A'선을 따른 메모리 셀의 단면, 부호 B, B'를 붙인 부분은 상기 도 2의 B-B'선을 따른 메모리 셀의 단면, 부호 C, C'를 붙인 부분은 상기 도 2의 C-C'선을 따른 메모리 셀의 단면, 그 밖의 부분은 주변 회로 영역의 일부 단면을 나타내고 있다. SRAM의 주변 회로는 n채널형 MISFET과 p채널형 MISFET으로 구성되지만, 이들 2 종류의 MISFET은 도전형이 상호 반대로 되어 있는 것을 제외하면, 거의 동일한 구조를 갖고 있기 때문에, 도면에는 그 한쪽(p채널형 MISFET)만

을 나타낸다. SRAM의 제조 방법을 설명하는 각 평면도(메모리 어레이의 평면도)에는 메모리 셀을 구성하는 주요한 도전층과 이를 접속 영역만을 나타내며, 도전층 간에 형성된 절연막 등의 도시는 원칙으로서 생략한다. 또한, 각 평면도중, 4개의 (+) 표시로 둘러싼 구형 영역은 메모리 셀 1개의 점유 영역을 나타내고 있다. 또, 주변 회로를 구성하는 n채널 및 p채널 MISFET에 의해 X 디코더 회로, Y 디코더 회로, 감지 증폭기 회로, 입출력 회로, 논리 회로 등이 구성되지만, 이들에 한하지 않고, 마이크로 프로세서, CPU 등의 논리 회로를 구성해도 된다.

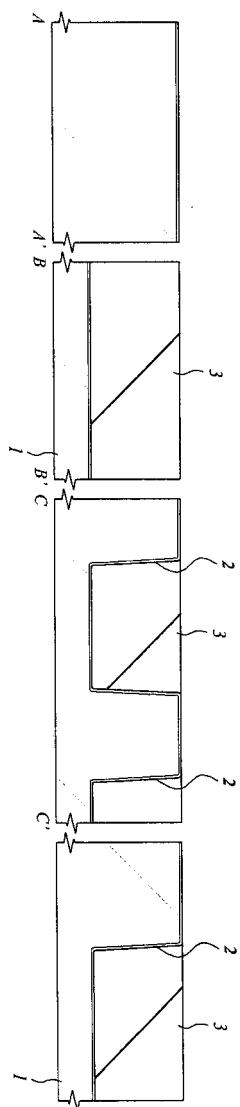

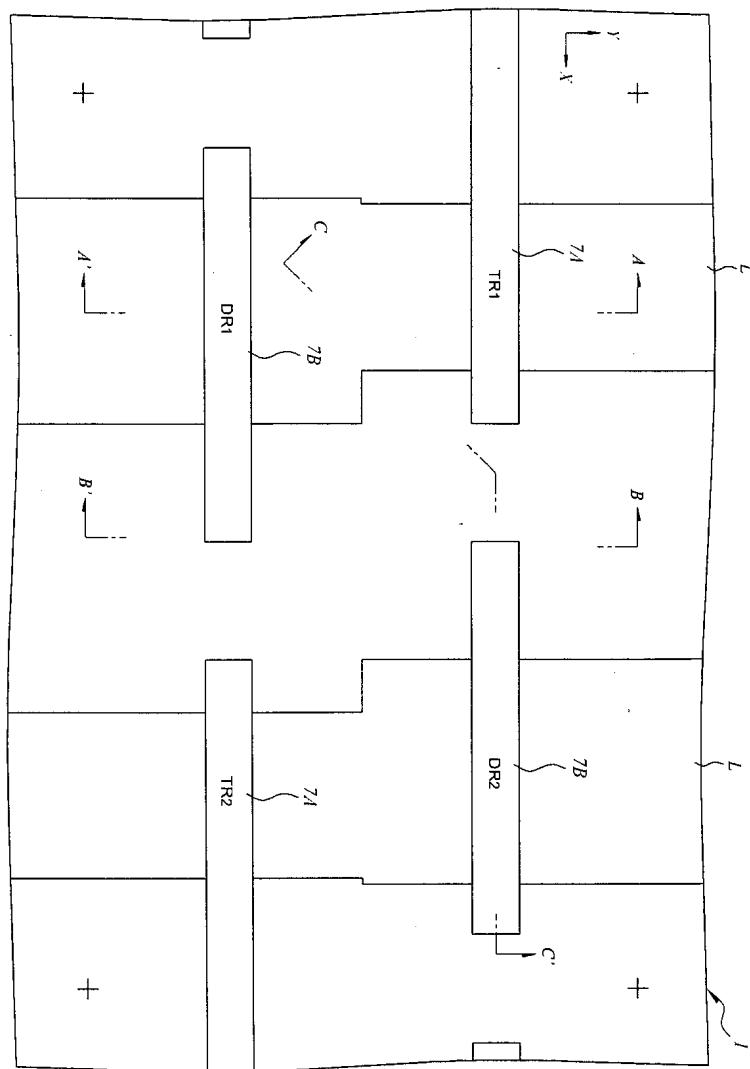

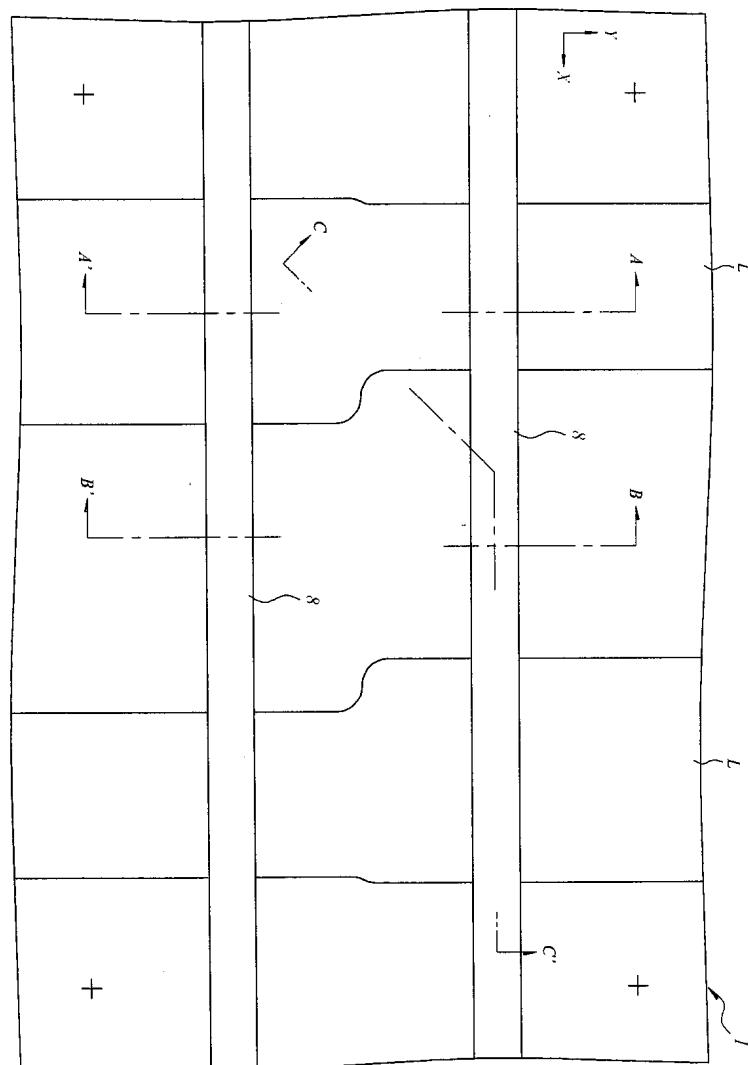

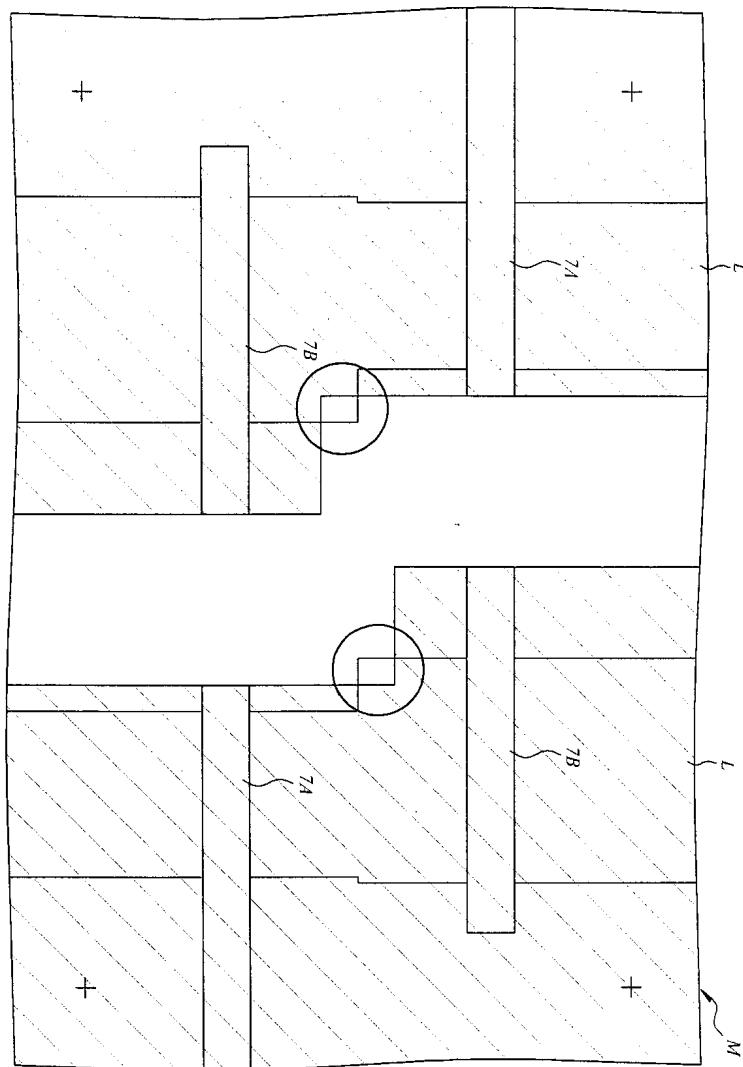

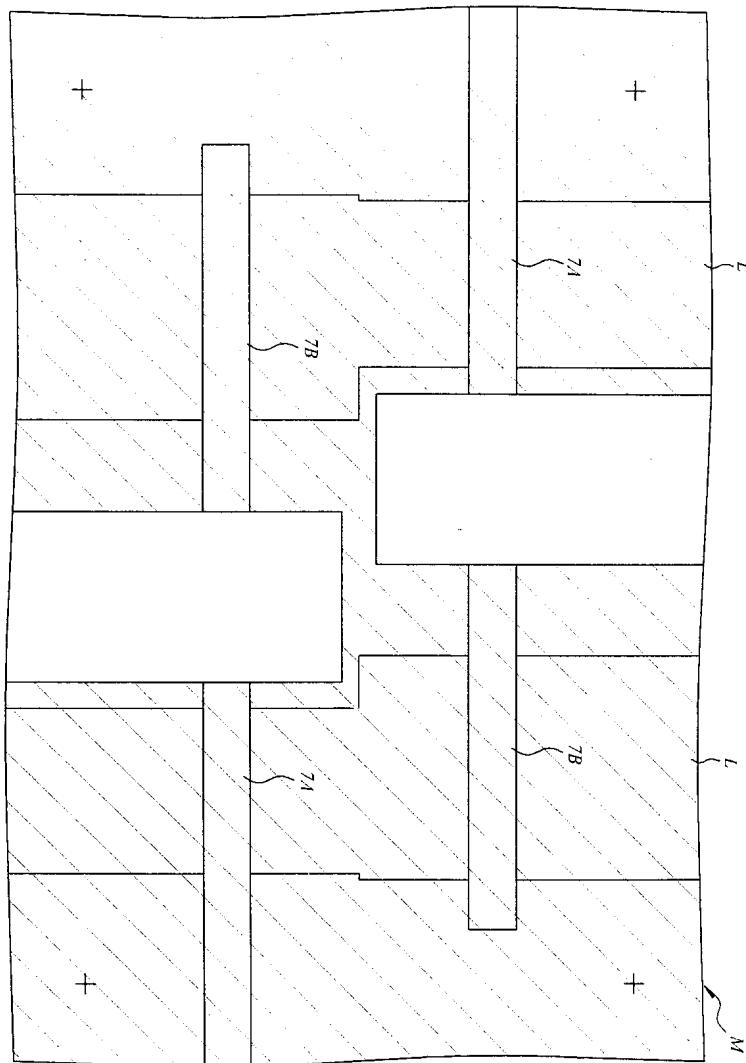

[0287] 먼저, 도 4 및 도 5에 도시한 바와 같이, 예를 들면, p형의 단결정 실리콘으로 이루어진 기판(1)의 주면의 소자 분리 영역에 소자 분리홈(2)을 형성한다. 소자 분리홈(2)을 형성하기 위해서는 예를 들면, 기판(1)의 주면을 드라이 에칭하여 홈을 형성하고, 계속해서 이 홈의 내부를 포함하는 기판(1) 상에 CVD법으로 산화 실리콘막(3) 등의 절연막을 퇴적한 후, 홈의 외부의 불필요한 산화 실리콘막(3)을 화학적 기계 연마(Chemical Mechanical Polishing; CMP)법으로 연마, 제거함으로써, 홈의 내부에 산화 실리콘막(3)을 남긴다. 이 소자 분리홈(2)을 형성함으로써, 메모리 어레이의 기판(1)의 주면에는 소자 분리홈(2)에 의해 주위가 규정된 섬 형상의 활성 영역(L)이 형성된다.

[0288] 다음으로, 도 6에 도시한 바와 같이, 예를 들면, 기판(1)의 일부에 인(P)을 이온 주입하고, 다른 일부에 봉소(B)를 이온 주입한 후, 기판(1)을 열 처리하여 이들 불순물을 기판(1) 내에 확산시킴에 따라, 기판(1)의 주면에 p형 웨爾(4) 및 n형 웨爾(5)을 형성한다. 도 6에 도시한 바와 같이, 메모리 어레이의 기판(1)에는 p형 웨爾(4)만이 형성되고, n형 웨爾(5)은 형성되지 않는다. 한편, 주변 회로 영역의 기판(1)에는 n형 웨爾(5)과 p형 웨爾(도시하지 않음)이 형성된다.

[0289] 다음으로, 도 7에 도시한 바와 같이 기판(1)을 열 산화하여 p형 웨爾(4) 및 n형 웨爾(5) 각각의 표면에, 예를 들면, 산화 실리콘으로 이루어진 막 두께 3nm~4nm 정도의 게이트 절연막(6)을 형성한다. 계속해서, 도 8에 도시한 바와 같이 예를 들면, p형 웨爾(4)의 게이트 절연막(6) 상에 도전막으로서 n형 다결정 실리콘막(7n)을 형성하고, n형 웨爾(5)의 게이트 절연막(6) 상에 도전막으로서 p형 다결정 실리콘막(7p)을 형성한 후, n형 다결정 실리콘막(7n) 및 p형 다결정 실리콘막(7p) 각각의 상부에 캡 절연막으로서 예를 들면, CVD법으로 산화 실리콘막(8)을 퇴적한다.

[0290] n형 다결정 실리콘막(7n) 및 p형 다결정 실리콘막(7p)을 형성하기 위해서는 예를 들면, 게이트 절연막(6) 상에 CVD법으로 비도핑의 다결정 실리콘막(또는, 비정질 실리콘막)을 퇴적한 후, p형 웨爾(4) 상의 비도핑 다결정 실리콘막(또는, 비정질 실리콘막)에 인(또는, 비소)을 이온 주입하고, n형 웨爾(5) 상의 비도핑 다결정 실리콘막(또는, 비정질 실리콘막)에 봉소를 이온 주입한다.

[0291] 다음으로, 도 9 및 도 10에 도시한 바와 같이, n형 다결정 실리콘막(7n) 및 p형 다결정 실리콘막(7p)을 예를 들면, 드라이 에칭함으로써, 메모리 어레이의 p형 웨爾(4) 상에 n형 다결정 실리콘막(7n)으로 이루어진 게이트 전극(7A, 7B)을 형성하고, 주변 회로 영역의 n형 웨爾(5) 상에 p형 다결정 실리콘막(7p)으로 이루어진 게이트 전극(7C)을 형성한다. 도시하지 않았지만, 주변 회로 영역의 p형 웨爾(4) 상에는 n형 다결정 실리콘막(7n)으로 이루어진 게이트 전극이 형성된다.

[0292] 게이트 전극(7A)은 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>)의 게이트 전극을 구성하며, 게이트 전극(7B)은 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>)의 게이트 전극을 구성한다. 또한, 게이트 전극(7C)은 주변 회로의 p채널형 MISFET의 게이트 전극을 구성한다. 도 9에 도시한 바와 같이, 메모리 어레이에 형성된 게이트 전극(7A, 7B)은 도 9의 X 방향으로 연장되는 장방형의 평면 패턴을 갖고 있으며, Y 방향의 폭, 즉 게이트 길이는 예를 들면, 0.13~0.14μm이다.

[0293] 게이트 전극(7A, 7B, 7C)을 형성하기 위해서는 예를 들면, 포토레지스트막을 마스크로 한 드라이 에칭으로 산화 실리콘막(8)을 게이트 전극(7A, 7B, 7C)과 동일한 평면 형상이 되도록 패터닝하며, 계속해서, 패터닝한 산화 실리콘막(8)을 마스크로 하여 n형 다결정 실리콘막(7n) 및 p형 다결정 실리콘막(7p)을 드라이 에칭한다. 산화 실리콘은 포토레지스트에 비해 다결정 실리콘에 대한 에칭 선택비가 크기 때문에, 포토레지스트막을 마스크로 하여 산화 실리콘막(8)과 다결정 실리콘막(7n, 7p)을 연속하여 에칭하는 경우에 비해, 미세한 게이트 길이를 갖는 게이트 전극(7A, 7B, 7C)을 높은 정밀도로 패터닝할 수 있다.

[0294] 다음으로, 도 11에 도시한 바와 같이 예를 들면, p형 웨爾(4)에 n형의 불순물로서 인 또는 비소를 이온 주입함으로써, 비교적 저농도의 n<sup>-</sup>형 반도체 영역(9)을 형성하고, n형 웨爾(5)에 p형의 불순물로서 봉소를 이온 주입함에 따라, 비교적 저농도의 p<sup>-</sup>형 반도체 영역(10)을 형성한다. n<sup>-</sup>형 반도체 영역(9)은 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>), 구

동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>) 및 주변 회로의 n채널형 MISFET 각각의 소스, 드레인을 LDD(lightly doped drain) 구조로 하기 위해서 형성하고, p형 반도체 영역(10)은 주변 회로의 p채널형 MISFET의 소스, 드레인을 LDD 구조로 하기 위해서 형성한다.

[0295] 다음으로, 도 12에 도시한 바와 같이 게이트 전극(7A, 7B, 7C) 각각의 측벽에 절연막으로 이루어진 측벽 스페이서(13)를 형성한다. 측벽 스페이서(13)를 형성하기 위해서는 예를 들면, 기판(1) 상에 CVD법으로 산화 실리콘막 및 질화 실리콘막을 퇴적한 후, 이 질화 실리콘막과 산화 실리콘막을 이방성 에칭한다. 이 때, 게이트 전극(7A, 7B, 7C) 각각의 상면을 덮는 산화 실리콘막(8) 및 기판(1)의 표면의 산화 실리콘막(게이트 절연막(6))을 에칭함으로써, 게이트 전극(7A, 7B, 7C) 각각의 표면, 및 n형 반도체 영역(9), p형 반도체 영역(10) 각각의 표면을 노출시킨다.

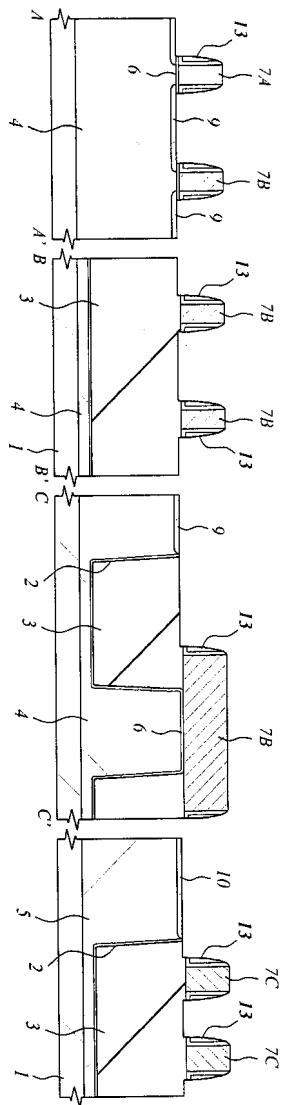

[0296] 다음으로, 도 13에 도시한 바와 같이 p형 웨(4)에 n형의 불순물로서 인 또는 비소를 이온 주입함으로써 비교적 고농도의 n<sup>+</sup>형 반도체 영역(14)을 형성하고, n형 웨(5)에 p형의 불순물로서 봉소를 이온 주입함에 따라 비교적 고농도의 p<sup>+</sup>형 반도체 영역(15)을 형성한다. 메모리 어레이의 p형 웨(4)에 형성된 n<sup>+</sup>형 반도체 영역(14)은 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>) 및 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>) 각각의 소스, 드레인을 구성하고, 주변 회로 영역의 n형 웨(5)에 형성된 p<sup>+</sup>형 반도체 영역(15)은 p채널형 MISFET의 소스, 드레인을 구성한다. 또한, 주변 회로 영역의 p형 웨(도시하지 않음)에는 n형의 불순물로서 인 또는 비소를 이온 주입하여, n채널형 MISFET의 소스, 드레인을 구성하는 비교적 고농도의 n<sup>+</sup>형 반도체 영역을 형성한다.

[0297] 다음으로, 도 14에 도시한 바와 같이, 예를 들면, 기판(1) 상에 스퍼터링법으로 코발트(Co)막(17)을 퇴적한다. 계속해서, 도 15에 도시한 바와 같이, 기판(1)을 열 처리하여 Co막(17)과 게이트 전극(7A, 7B, 7C)과의 계면, 및 Co막(17)과 기판(1)과의 계면에 실리사이드 반응을 생기게 한 후, 미반응의 Co막(17)을 에칭으로 제거한다. 이것에 의해, 게이트 전극(7A, 7B, 7C)의 표면과 소스, 드레인(n<sup>+</sup>형 반도체 영역(14), p<sup>+</sup>형 반도체 영역(15))의 표면과 실리사이드층인 Co 실리사이드층(18)이 형성된다. 도 15 및 도 16에 도시한 바와 같이, 지금까지의 공정에 의해, 메모리 어레이에 n채널형의 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>) 및 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>)이 형성되며, 주변 회로 영역에 p채널형 MISFET(Qp) 및 n채널형 MISFET(도시하지 않음)이 형성된다.

[0298] 도 16에 도시한 바와 같이, 한쪽의 전송 MISFET(TR<sub>1</sub>) 및 구동 MISFET(DR<sub>1</sub>)과, 다른 쪽의 전송 MISFET(TR<sub>2</sub>) 및 구동 MISFET(DR<sub>2</sub>)은, 소자 분리부를 개재하여 도면의 가로 방향(X 방향)으로 이격되어 배치되며, 또한 메모리 셀 형성 영역의 중심점에 대하여 점대칭으로 배치된다. 또한, 구동 MISFET(DR<sub>2</sub>) 및 구동 MISFET(DR<sub>1</sub>)의 게이트 전극(7B)은 도면의 가로 방향(X 방향)으로 연장되도록 배치되며, X 방향에서, 한쪽의 전송 MISFET(TR<sub>1</sub>) 및 구동 MISFET(DR<sub>1</sub>)과, 다른 쪽의 전송 MISFET(TR<sub>2</sub>) 및 구동 MISFET(DR<sub>2</sub>)과의 사이의 소자 분리부 상에서 그 일단이 종단하며, 그 일단부 상에 후술하는 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)이 형성된다.

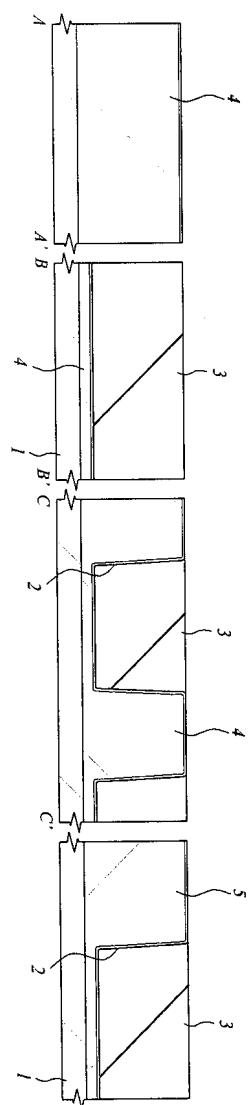

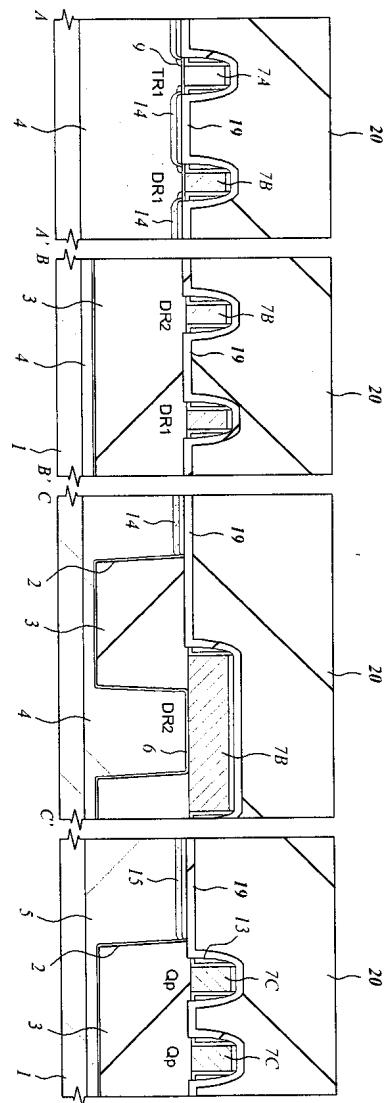

[0299] 다음으로, 도 17에 도시한 바와 같이, MISFET(TR<sub>1</sub>, TR<sub>2</sub>, DR<sub>1</sub>, DR<sub>2</sub>, Qp)을 덮는 절연막으로서, 예를 들면, CVD법으로 질화 실리콘막(19) 및 산화 실리콘막(20)을 퇴적하고, 계속해서 화학적 기계 연마법으로 산화 실리콘막(20)의 표면을 평탄화한다.

[0300] 다음으로, 도 18 및 도 19에 도시한 바와 같이, 포토레지스트막을 마스크로 하여 상기 산화 실리콘막(20) 및 질화 실리콘막(19)을 드라이 에칭함으로써, 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>)의 게이트 전극(7A)의 상부에 컨택트홀(21)을 형성하며, 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>)의 게이트 전극(7B)의 상부에 컨택트홀(22)을 형성한다. 또한, 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>) 및 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>) 각각의 소스, 드레인(n<sup>+</sup>형 반도체 영역(14))의 상부에 컨택트홀(23, 24, 25)을 형성하며, 주변 회로 영역의 p채널형 MISFET(Qp)의 게이트 전극(7C) 및 소스, 드레인(p<sup>+</sup>형 반도체 영역(15)) 각각의 상부에 컨택트홀(26, 27)을 형성한다.

[0301] 다음으로, 도 20에 도시한 바와 같이, 상기 컨택트홀(21~27)의 내부에 플러그(28)를 형성한다. 플러그(28)를 형성하기 위해서는 예를 들면, 컨택트홀(21~27)의 내부를 포함하는 산화 실리콘막(20) 상에 스퍼터링법으로 티탄(Ti)막 및 질화 티탄(TiN)막을 퇴적하고, 계속해서 CVD법으로 TiN막 및 금속막으로서 텉스텐(W)막을 퇴적한

후, 컨택트홀(21~27)의 외부의 W막, TiN막 및 Ti막을 화학적 기계 연마법에 의해 제거한다.

[0302] 다음으로, 도 21에 도시한 바와 같이, 절연막으로서 예를 들면, 기판(1) 상에 CVD법으로 질화 실리콘막(29) 및 산화 실리콘막(30)을 퇴적한 후, 도 22 및 도 23에 도시한 바와 같이, 포토레지스트막을 마스크로 하여 산화 실리콘막(29) 및 질화 실리콘막(30)을 드라이 에칭함으로써, 상기 컨택트홀(21~27) 각각의 상부에 흄(31~37)을 형성한다. 이들 흄(31~37) 중, 메모리 어레이에 형성된 흄(32, 33)은 도 22에 도시한 바와 같이, 컨택트홀(22)의 상부와 컨택트홀(23)의 상부에 걸치도록 형성된다.

[0303] 산화 실리콘막(30) 하층의 질화 실리콘막(29)은 산화 실리콘막(30)을 에칭할 때의 스토퍼막으로서 사용된다. 즉, 흄(31~37)을 형성할 때는 먼저 산화 실리콘막(30)을 에칭하여 하층의 질화 실리콘막(29)의 표면에서 에칭을 정지하고, 그 후, 질화 실리콘막(29)을 에칭한다. 이것에 의해, 포토마스크의 오정렬에 의해 흄(31~37)과 그 하층의 컨택트홀(21~27)의 상대적인 위치가 어긋난 경우라도, 흄(31~37) 하층의 산화 실리콘막(20)이 지나치게 에칭될 일은 없다.

[0304] 다음으로, 도 24 및 도 25에 도시한 바와 같이, 메모리 어레이에 형성된 흄(31~35) 각각의 내부에 중간 도전층(41~45)을 형성하고, 주변 회로 영역에 형성된 흄(36, 37) 각각의 내부에 제1층 배선(46, 47)을 형성한다. 중간 도전층(41~45) 및 제1층 배선(46, 47)을 형성하기 위해서는 예를 들면, 흄(31~37)의 내부를 포함하는 산화 실리콘막(30) 상에 스퍼터링법으로 TiN막을 퇴적하고, 계속해서 금속막으로서 CVD법으로 W막을 퇴적한 후, 흄(31~37) 외부의 TiN막 및 TiN막을 화학적 기계 연마법에 의해 제거한다.

[0305] 메모리 어레이에 형성된 중간 도전층(41~45) 중, 중간 도전층(41)은 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>)의 게이트 전극(7A)과, 후의 공정에서 형성된 워드선(WL)을 전기적으로 접속하기 위해서 사용된다. 또한, 중간 도전층(44)은 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>)의 n<sup>+</sup>형 반도체 영역(14)(소스, 드레인의 한쪽)과 상보성 데이터선(BLT, BLB)을 전기적으로 접속하기 위해서 사용된다. 또한, 중간 도전층(45)은 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>)의 n<sup>+</sup>형 반도체 영역(14)(소스)과 후의 공정에서 형성되는 기준 전압선(91)(V<sub>ss</sub>)을 전기적으로 접속하기 위해서 사용된다.

[0306] 각 메모리 셀 영역의 거의 중앙부에 형성된 한쌍의 중간 도전층(42, 43)의 한쪽(중간 도전층(42))은 전송 MISFET(TR<sub>1</sub>)의 소스, 드레인의 한쪽 및 구동 MISFET(DR<sub>1</sub>)의 드레인을 구성하는 n<sup>+</sup>형 반도체 영역(14)과, 구동 MISFET(DR<sub>2</sub>)의 게이트 전극(7B)과, 후의 공정에서 형성되는 종형 MISFET(SV<sub>1</sub>)의 하부 반도체층(57)(드레인)을 전기적으로 접속하는 국소 배선으로서 사용된다. 또한, 다른 쪽(중간 도전층(43))은 전송 MISFET(TR<sub>2</sub>)의 소스, 드레인의 한쪽 및 구동 MISFET(DR<sub>2</sub>)의 드레인을 구성하는 n<sup>+</sup>형 반도체 영역(14)과, 구동 MISFET(DR<sub>1</sub>)의 게이트 전극(7B)과, 후의 공정에서 형성되는 종형 MISFET(SV<sub>2</sub>)의 하부 반도체층(57)(드레인)을 전기적으로 접속하는 국소 배선으로서 사용된다.

[0307] 상기 중간 도전층(41~45)은 W막 등의 메탈막으로 구성한다. 이것에 의해, 중간 도전층(41~45)을 형성하는 공정에서 주변 회로의 메탈 배선(제1층 배선46, 47)을 동시에 형성할 수 있으므로, SRAM의 제조 공정 수 및 마스크 수를 줄일 수 있다.

[0308] 텅스텐 등의 금속막으로 이루어진 플러그(28) 및 중간 도전층(42, 43)과 동층의 플러그(28) 및 중간 도전층(46, 47)에 의해, 주변 회로를 구성하는 n채널 및 p채널 MISFET의 소스·드레인 및 게이트 사이가 전기적으로 접속된다. 이것에 의해, 주변 회로를 구성하는 MISFET 간의 전기적 접속의 자유도를 향상시킬 수 있고, 고집적화가 가능해짐과 함께, MISFET 간의 접속 저항을 저감할 수 있고, 회로의 동작 스피드를 향상시킬 수 있다.

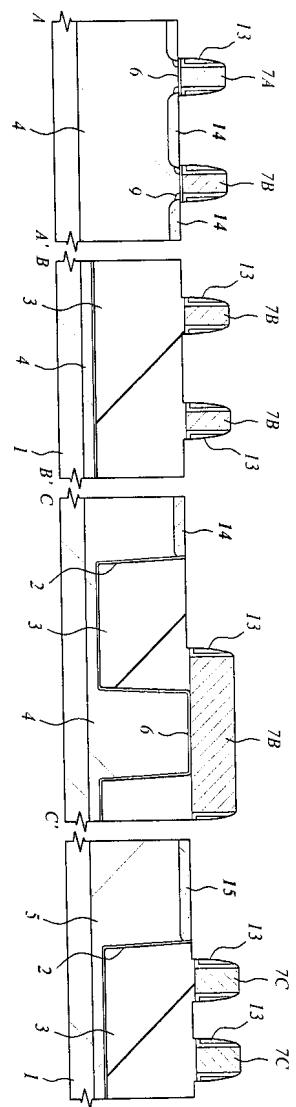

[0309] 다음으로, 도 26 및 도 27에 도시한 바와 같이 중간 도전층(42, 43) 각각의 표면에 배리어층(48)을 형성한다. 배리어층(48)은 중간 도전층(42, 43)의 표면 영역 중, 주로 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)이 형성되는 영역의 아래쪽에 위치하는 영역에 형성된다. 배리어층(48)을 형성하기 위해서는 기판(1) 상에 스퍼터링법으로 WN막을 퇴적한 후, 포토레지스트막을 마스크로 한 드라이 에칭으로 WN막을 패터닝한다. 이와 같이 실리콘막과 중간 도전층(42, 43)과의 계면에서 원하지 않는 실리사이드 반응이 생기는 것을 방지할 수 있는 배리어층(48)을 실리콘막과, 중간 도전층(42, 43)을 구성하는 W막과의 사이에 개재시킨다.

[0310] 배리어층(48)은 WN막 이외의 Ti막, TiN막, WN막과 W막과의 적층막, TiN막과 W막과의 적층막, Ti막과 TiN막과의 적층막, Co 실리사이드막, W 실리사이드막 등으로 구성해도 된다. Ti계 박막은 WN막에 의해 산화 실리콘막과의

밀착성이나 내열성이 좋아진다는 특징을 갖는다. 한편, WN막은 산화에 의해 용이하게 부동태화되기 때문에, 장치 오염 가능성이 낮아서 간편하게 취급할 수 있다. 밀착성, 내열성, 간편성 중 어느 하나를 중시할지에 따라 선택이 가능하다. 따라서, MISFET을 형성한 후의 배선 형성 공정과 같이, Ti계 박막이 기판(1)에 재부착되어도 MISFET의 특성을 변동시킬 우려가 적은 공정에서 배리어막을 필요로 하는 경우 등은 WN막보다도 Ti계 박막을 사용한 쪽이 좋다.

[0311] 이와 같이 중간 도전층(42, 43)은 텅스텐(W) 등의 금속막으로 구성하고, 배리어층(48)을 개재하여 중간 도전층(42, 43)의 상부에 실리콘막으로 형성된 종형 MISFET을 형성함으로써, MISFET 간의 접속 저항을 저감할 수 있고, 메모리 셀의 특성을 향상시킬 수 있음과 함께, 메모리 셀 사이즈를 축소할 수 있다. 또, 배리어층(48)을 형성하는 수단 대신 텅스텐으로 이루어진 중간 도전층(42, 43)의 표면을 질화 처리하여 질화 텅스텐으로 바꾸어도 된다. 이와 같이 하면 배리어층(48)을 형성하기 위한 마스크가 불필요해진다.

[0312] 다음으로, 도 28에 도시한 바와 같이 기판(1) 상에 CVD법으로 질화 실리콘막(49)을 퇴적하고, 계속해서 질화 실리콘막(49)의 상부에 CVD법으로 다결정 실리콘막(또는, 비정질 실리콘막)(50)을 퇴적한다. 질화 실리콘막(49)은 후의 공정에서 질화 실리콘막(49)의 상부에 퇴적되는 산화 실리콘막(52)을 예치할 때에, 하층의 산화 실리콘막(20)이 예치되는 것을 방지하는 예치 스토퍼막으로서 사용된다. 다결정 실리콘막(50)은 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(66)을 구성하는 다결정 실리콘층(64, 65)과 동일한 도전형(예를 들면, p형)으로 하기 위해서, 성막 시 또는 성막 후에 붕소를 도핑한다.

[0313] 다음으로, 도 29 및 도 30에 도시한 바와 같이 포토레지스트막을 마스크로 한 드라이 예치으로 다결정 실리콘막(50)을 패터닝함으로써, 질화 실리콘막(49)의 상부에 한쌍의 게이트 인출 전극(51)(51a, 51b)을 형성한다. 게이트 인출 전극(51)(51a, 51b)은 후의 공정에서 형성되는 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)에 인접하는 영역에 배치되며, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(66)과 하층의 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>) 및 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>)과의 접속에 사용된다.

[0314] 다음으로, 도 31에 도시한 바와 같이 질화 실리콘막(48)의 상부에 절연막으로서 CVD법으로 산화 실리콘막(52)을 퇴적함으로써, 게이트 인출 전극(51)의 상부를 괴복한 후, 포토레지스트막을 마스크로 하여 산화 실리콘막(52)을 드라이 예치함으로써, 배리어층(48)의 상부 영역, 즉 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)이 형성되는 영역의 산화 실리콘막(52)에 관통 홀(53)을 형성한다.

[0315] 다음으로, 도 32에 도시한 바와 같이 관통 홀(53)의 측벽에 절연막으로 이루어진 측벽 스페이서(54)를 형성한다. 측벽 스페이서(54)를 형성하기 위해서는 관통 홀(53)의 내부를 포함하는 산화 실리콘막(52) 상에 CVD법으로 산화 실리콘막을 퇴적하고, 계속해서 이 산화 실리콘막을 이방성 예치하여 관통 홀(53)의 측벽에 남긴다. 이 때, 상기 산화 실리콘막의 예치에 이어서 관통 홀(53)의 바닥부의 질화 실리콘막(49)을 예치함으로써, 관통 홀(53)의 바닥부에 배리어층(48)을 노출시킨다.

[0316] 이와 같이, 측벽에 절연막으로 이루어진 측벽 스페이서(54)를 형성하여 관통 홀(53)의 직경을 작게 함으로써, 도 33에 도시한 바와 같이 배리어층(48)의 상부에 그 면적보다도 작은 직경을 갖는 관통 홀(53)이 형성된다. 이것에 의해, 포토마스크의 오정렬에 의해 관통 홀(53)의 위치가 배리어층(48)에 대하여 어긋난 경우라도, 관통 홀(53)의 바닥부에 배리어층(48)만을 노출시킬 수 있기 때문에, 다음 공정에서 관통 홀(53)의 내부에 형성된 플러그(55)와 배리어층(48)의 접촉 면적을 확보할 수 있다.

[0317] 다음으로, 도 34에 도시한 바와 같이 관통 홀(53)의 내부에 플러그(55)를 형성한다. 플러그(55)를 형성하기 위해서는 관통 홀(53)의 내부를 포함하는 산화 실리콘막(52) 상에 CVD법으로 다결정 실리콘막(또는, 비정질 실리콘막)을 퇴적한 후, 관통 홀(53) 외부의 다결정 실리콘막(또는, 비정질 실리콘막)을 화학적 기계 연마법(또는, 에치백법)에 의해 제거한다. 플러그(55)를 구성하는 다결정 실리콘막(또는, 비정질 실리콘막)은 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 하부 반도체층(57)을 구성하는 다결정 실리콘막과 동일한 도전형(p형)으로 하기 위해서, 성막 시 또는 성막 후에 붕소를 도핑한다.

[0318] 관통 홀(53)의 내부에 형성된 플러그(55)는 배리어층(48)을 개재하여 하층의 중간 도전층(42, 43)과 전기적으로 접속된다. 플러그(55)를 구성하는 다결정 실리콘막(또는, 비정질 실리콘막)과 중간 도전층(42, 43)을 구성하는 WN막 사이에 WN막으로 이루어진 배리어층(48)을 개재시킴에 따라, 플러그(55)와 중간 도전층(42, 43)과의 계면에서 원하지 않는 실리사이드 반응이 생기는 것을 방지할 수 있다. 또, 플러그(55)는 다결정 실리콘막(또는, 비정질 실리콘막) 대신 텅스텐으로 구성하여, 그 표면을 질화 처리하여 질화 텅스텐에 바꾸어도 된다. 이와 같이

하면 배리어층(48)을 형성하기 위한 마스크가 불필요해진다.

[0319] 다음으로, 도 35에 도시한 바와 같이 산화 실리콘막(52)의 상부에 p형 실리콘막(57p), 실리콘막(58i) 및 p형 실리콘막(59p)을 형성한다. 이들 3층의 실리콘막(57p, 58i, 59p)을 형성하기 위해서는 예를 들면, 붕소를 도핑한 비정질 실리콘막 및 비도핑의 비정질 실리콘막을 CVD법으로 순차 퇴적한 후, 열 처리를 행하여 이들 비정질 실리콘막을 결정화함으로써, p형 실리콘막(57p) 및 실리콘막(58i)를 형성한다. 다음으로, 실리콘막(58i)에 채널 형성용의 n형 또는 p형 불순물을 이온 주입한 후, 실리콘막(58i)의 상부에 붕소를 도핑한 비정질 실리콘막을 CVD법으로 퇴적하고, 계속해서 열 처리에 의해 이 비정질 실리콘막을 결정화함으로써, p형 실리콘막(59p)을 형성한다.

[0320] 이와 같이, 비정질 실리콘막을 결정화하여 실리콘막(57p, 58i, 59p)을 형성함으로써, 다결정 실리콘막에 비해 막 내의 결정립을 크게 할 수 있기 때문에, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 특성이 향상한다. 또, 실리콘막(58i)에 채널 형성용의 불순물을 이온 주입할 때는 실리콘막(58i)의 표면에 산화 실리콘막으로 이루어진 쓰루 절연막을 형성하고, 이 쓰루 절연막(through insulating film)을 통해 불순물을 이온 주입해도 된다. 또한, 비정질 실리콘막의 결정화는 후술하는 게이트 절연막을 형성하기 위한 열 산화 공정 등을 이용하여 행하여도 된다.

[0321] 다음으로, 도 36에 도시한 바와 같이 p형 실리콘막(59p)의 상부에 CVD법으로 산화 실리콘막(61) 및 질화 실리콘막(62)을 순차 퇴적한 후, 포토레지스트막을 마스크로 하여 질화 실리콘막(62)을 드라이 에칭함으로써, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)을 형성하는 영역의 상부에 질화 실리콘막(62)을 남긴다. 이 질화 실리콘막(62)은 3층의 실리콘막(57p, 58i, 59p)을 에칭할 때의 마스크로서 사용된다. 질화 실리콘은 실리콘에 대한 에칭 선택비가 포토레지스트에 비해 크기 때문에, 포토레지스트막을 마스크로 한 에칭에 비해, 실리콘막(57p, 58i, 59p)을 높은 정밀도로 패터닝할 수 있다.

[0322] 다음으로, 도 37 및 도 38에 도시한 바와 같이 질화 실리콘막(62)을 마스크로 하여 3층의 실리콘막(57p, 58i, 59p)을 드라이 에칭한다. 이것에 의해, p형 실리콘막(57p)으로 이루어진 하부 반도체층(57), 실리콘막(58i)으로 이루어진 중간 반도체층(58), p형 실리콘막(59p)으로 이루어진 상부 반도체층(59)에 의해 구성되는 사각 기둥형의 적층체(P<sub>1</sub>, P<sub>2</sub>)가 형성된다.

[0323] 상기 적층체(P<sub>1</sub>)의 하부 반도체층(57)은 종형 MISFET(SV<sub>1</sub>)의 드레인을 구성하며, 상부 반도체층(59)은 소스를 구성한다. 하부 반도체층(57)과 상부 반도체층(59)과의 사이에 위치하는 중간 반도체층(58)은 실질적으로 종형 MISFET(SV<sub>1</sub>)의 기판을 구성하며, 그 측벽은 채널 영역을 구성한다. 또한, 적층체(P<sub>2</sub>)의 하부 반도체층(57)은 종형 MISFET(SV<sub>2</sub>)의 드레인을 구성하며, 상부 반도체층(59)은 소스를 구성한다. 중간 반도체층(58)은 실질적으로 종형 MISFET(SV<sub>2</sub>)의 기판을 구성하며, 그 측벽은 채널 영역을 구성한다.

[0324] 또한, 평면적으로 본 경우, 적층체(P<sub>1</sub>)는 그 하층의 관통 홀(53), 배리어층(48), 중간 도전층(42)의 일단부, 컨택트홀(22) 및 구동 MISFET(DR<sub>2</sub>)의 게이트 전극(7B)의 일단부와 중첩되도록 배치된다. 또한, 적층체(P<sub>2</sub>)는 그 하층의 관통 홀(53), 배리어층(48), 중간 도전층(43)의 일단부, 컨택트홀(22) 및 구동 MISFET(DR<sub>1</sub>)의 게이트 전극(7B)의 일단부와 중첩되도록 배치된다.

[0325] 상기 실리콘막(57p, 58i, 59p)을 드라이 에칭할 때에는 예를 들면, 도 38에 도시한 바와 같이 적층체(P<sub>1</sub>, P<sub>2</sub>)의 측벽 바닥부에 테이퍼를 형성하고, 적층체(P<sub>1</sub>, P<sub>2</sub>)의 하부(하부 반도체층(57)) 면적을 상부(중간 반도체층(58) 및 상부 반도체층(59)) 면적보다 크게 해도 된다. 이와 같이 하면, 포토마스크의 오정렬에 의해 적층체(P<sub>1</sub>, P<sub>2</sub>)의 위치가 관통 홀(53)에 대하여 어긋난 경우라도, 관통 홀(53) 내의 플러그(55)와 하부 반도체층(57)과의 접촉 면적의 감소가 방지되기 때문에, 하부 반도체층(57)과 플러그(55)의 컨택트 저항의 증가를 억제할 수 있다.

[0326] 또한, 적층체(P<sub>1</sub>, P<sub>2</sub>)를 형성할 때, 상부 반도체층(59)과 중간 반도체층(58)과의 계면 근방, 하부 반도체층(57)과 중간 반도체층(58)과의 계면 근방, 중간 반도체층(58)의 일부 등에 질화 실리콘막 등으로 구성된 1층 또는 복수층의 터널 절연막을 설치해도 된다. 이와 같이 하면, 하부 반도체층(57)이나 상부 반도체층(59)을 구성하는 p형 실리콘막(57p, 59p) 내의 불순물을 중간 반도체층(58)의 내부로 확산되는 것을 방지할 수 있기 때문에, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 성능을 향상시킬 수 있다. 이 경우, 터널 절연막은 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 드레인

전류(Ids)의 저하를 억제할 수 있을 정도의 얇은 막 두께(수 nm 이하)로 형성한다.

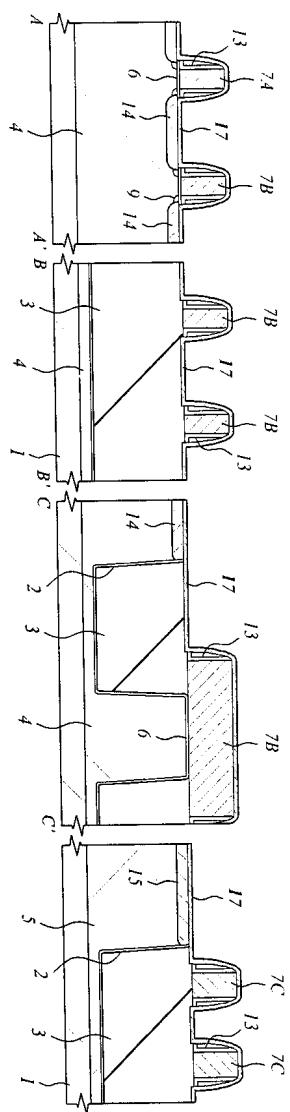

[0327] 다음으로, 도 39에 도시한 바와 같이 기판(1)을 열 산화함에 의해, 적층체(P<sub>1</sub>, P<sub>2</sub>)를 구성하는 하부 반도체층(57), 중간 반도체층(58) 및 상부 반도체층(59) 각각의 측벽 표면에 산화 실리콘막으로 이루어진 게이트 절연막(63)을 형성한다. 이 때, 적층체(P<sub>1</sub>, P<sub>2</sub>)의 하층에 형성되어 있는 다결정 실리콘막으로 이루어진 게이트 인출 전극(51)이나 관통 홀(53)의 내부의 플러그(55)는 산화 실리콘계의 절연막(산화 실리콘막(52)), 측벽 스페이서(54)으로 폐복되어 있기 때문에, 게이트 인출 전극(51)이나 플러그(55)의 표면이 산화되어 저항이 커질 우려는 없다. 또한, 적층체(P<sub>1</sub>, P<sub>2</sub>)와 그 상부의 질화 실리콘막(62)과의 사이에는 산화 실리콘막(61)이 형성되어 있기 때문에, 상부 반도체층(59)의 표면에 형성된 게이트 절연막(63)과 질화 실리콘막(62)과의 접촉이 방지되어, 적층체(P<sub>1</sub>, P<sub>2</sub>)의 상단부 근방에서의 게이트 절연막(63)의 내압 저하를 방지할 수 있다.

[0328] 적층체(P<sub>1</sub>, P<sub>2</sub>)의 측벽의 게이트 절연막(63)은 예를 들면, 800°C 이하의 저온 열 산화(예를 들면, 웨트 산화)에 의해 형성되지만, 이것에 한정되지 않고 예를 들면, CVD법에 의해 퇴적된 산화 실리콘막이나, CVD법에 의해 퇴적된 산화하프늄(HfO<sub>2</sub>), 산화 탄탈(Ta<sub>2</sub>O<sub>5</sub>) 등의 고 유전체막으로 구성해도 된다. 이 경우에는, 게이트 절연막(63)을 보다 저온으로 형성할 수 있으므로, 불순물의 확산 등에 기인하는 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 임계값 전압의 변동을 억제할 수 있다.

[0329] 다음으로, 도 40에 도시한 바와 같이 사각 기둥형의 적층체(P<sub>1</sub>, P<sub>2</sub>) 및 그 상부의 질화 실리콘막(62)의 측벽에 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(66)의 일부를 구성하는 도전막으로서, 예를 들면, 제1 다결정 실리콘층(64)을 형성한다. 제1 다결정 실리콘층(64)을 형성하기 위해서는 산화 실리콘막(52)의 상부에 CVD법으로 다결정 실리콘막을 퇴적한 후, 이 다결정 실리콘막을 이방적으로 예칭함으로써, 사각 기둥형의 적층체(P<sub>1</sub>, P<sub>2</sub>) 및 질화 실리콘막(62)의 측벽을 둘러싸도록 측벽 스페이서형으로 남긴다. 이와 같이, 게이트 전극(66)의 일부를 구성하는 제1 다결정 실리콘층(64)은 사각 기둥형의 적층체(P<sub>1</sub>, P<sub>2</sub>) 및 게이트 절연막(63)에 대하여 자기 합적으로 형성되기 때문에, 메모리 셀 사이즈를 축소할 수 있다. 제1 다결정 실리콘층(64)을 구성하는 다결정 실리콘막은 그 도전형을 p형으로 하기 위해서 봉소를 도핑한다.

[0330] 상기 다결정 실리콘막을 예칭하여 제1 다결정 실리콘층(64)을 형성할 때는 다결정 실리콘막의 예칭에 이어서 하층의 산화 실리콘막(52)을 예칭한다. 이것에 의해, 사각 기둥형의 적층체(P<sub>1</sub>, P<sub>2</sub>)의 바로 아래를 제외한 영역의 산화 실리콘막(52)이 제거되어, 게이트 인출 전극(51) 및 질화 실리콘막(49)이 노출된다. 또, 제1 다결정 실리콘층(64)의 하단부와 게이트 인출 전극(51)과의 사이에는 산화 실리콘막(52)이 남아있기 때문에, 제1 다결정 실리콘층(64)과 게이트 인출 전극(51)에 전기적으로 접속되지 않는다.

[0331] 다음으로, 도 41에 도시한 바와 같이 제1 다결정 실리콘층(64)의 표면에 도전막으로서 예를 들면, 제2 다결정 실리콘층(65)을 형성한다. 제2 다결정 실리콘층(65)을 형성하기 위해서는 기판(1)의 표면을 세정액으로 웨트 세정한 후, 산화 실리콘막(52)의 상부에 CVD법으로 다결정 실리콘막을 퇴적하고, 계속해서, 이 다결정 실리콘막을 이방적으로 예칭함으로써, 제1 다결정 실리콘층(64)의 표면을 둘러싸도록 측벽 스페이서형으로 남긴다. 제2 다결정 실리콘층(65)을 구성하는 다결정 실리콘막은 그 도전형을 p형으로 하기 위해서 봉소를 도핑한다.

[0332] 제2 다결정 실리콘층(65)을 구성하는 상기 다결정 실리콘막은 사각 기둥형의 적층체(P<sub>1</sub>, P<sub>2</sub>)의 바로 아래에 남은 산화 실리콘막(52)의 측벽이나 게이트 인출 전극(51)의 표면에도 퇴적되기 때문에, 이 다결정 실리콘막을 이방적으로 예칭하면, 그 하단부가 게이트 인출 전극(51)의 표면과 접촉한다.

[0333] 이와 같이 하단부가 게이트 인출 전극(51)에 전기적으로 접속하는 제2 다결정 실리콘층(65)을 제1 다결정 실리콘층(64)에 대하여 자기 정합적으로 형성되기 때문에, 메모리 셀 사이즈를 축소할 수 있다.

[0334] 지금까지의 공정에 의해, 사각 기둥형의 적층체(P<sub>1</sub>, P<sub>2</sub>) 및 질화 실리콘막(62)의 측벽에, 제1 다결정 실리콘층(64)과 제2 다결정 실리콘막(65)의 적층막으로 이루어진 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(66)이 형성된다. 이 게이트 전극(66)은 그 일부를 구성하는 제2 다결정 실리콘막(65)을 개재하여 게이트 인출 전극(51)과 전기적으로 접속된다.

[0335] 즉, 종형 MISFET(SV<sub>1</sub>)의 게이트 전극(66)을 구성하는 제1 다결정 실리콘층(64)과 제2 다결정 실리콘막(65)은 하

단부가 게이트 인출 전극(51b)에 전기적으로 접속되며, 종형 MISFET(SV<sub>2</sub>)의 게이트 전극(66)을 구성하는 제1 다결정 실리콘층(64)과 제2 다결정 실리콘막(65)은 하단부가 게이트 인출 전극(51a)에 전기적으로 접속된다.

[0336] 이와 같이, 게이트 전극(66)의 일부를 구성하는 제1 다결정 실리콘층(64)을 사각 기둥형의 적층체(P<sub>1</sub>, P<sub>2</sub>) 및 게이트 절연막(63)에 대하여 측벽 스페이서형으로 자기 정합적으로 형성한다. 하단부가 게이트 인출 전극(51a, 51b)에 전기적으로 접속하는 제2 다결정 실리콘층(65)을 제1 다결정 실리콘층(64)에 대하여 측벽 스페이서형으로 자기 정합적으로 형성한다. 이것에 의해, 메모리 셀 사이즈를 축소할 수 있다. 즉, 게이트 전극(66)을 사각 기둥형의 적층체(P<sub>1</sub>, P<sub>2</sub>) 및 게이트 절연막(63)에 대하여 자기 정합적으로 형성한다. 또한, 게이트 전극(66)을 게이트 인출 전극(51a, 51b)에 대하여 자기 정합적으로 접속한다. 이것에 의해, 메모리 셀 사이즈를 축소할 수 있다.

[0337] 상기와 같이, 게이트 전극(66)을 2층의 도전막(제1 다결정 실리콘층(64) 및 제2 다결정 실리콘막(65))으로 구성하는 경우에는 제2 다결정 실리콘막(65) 대신 W 실리사이드막이나 W막을 이용함으로써, 게이트 전극(66)을 저저항의 실리사이드 구조 혹은 폴리 메탈 구조로 할 수 있다.

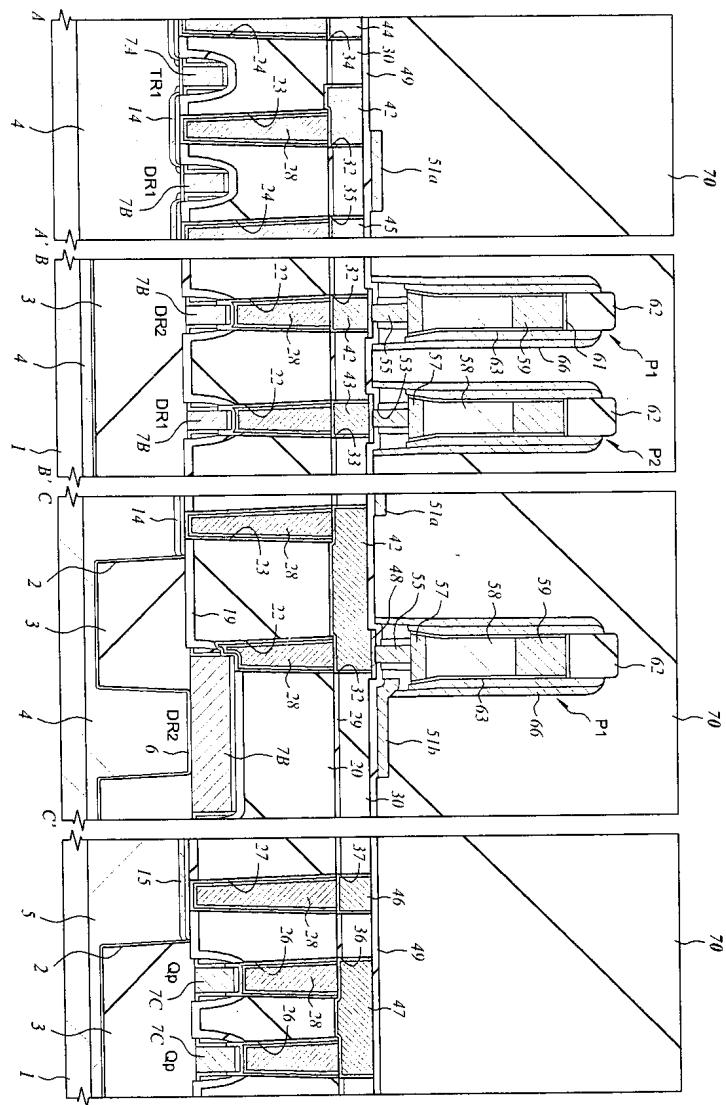

[0338] 다음으로, 도 42에 도시한 바와 같이 기판(1) 상에 절연막으로서 예를 들면, 산화 실리콘막(70)을 CVD법에 의해 퇴적한 후, 화학적 기계 연마법에 의해 그 표면을 평탄화한다. 산화 실리콘막(70)은 평탄화 후의 표면의 높이가 질화 실리콘막(62)의 표면보다 높게 되도록 두꺼운 막 두께로 퇴적하며, 평탄화 처리 시에 질화 실리콘막(62)의 표면이 깎이지 않도록 한다.

[0339] 다음으로, 도 43에 도시한 바와 같이 산화 실리콘막(70)을 에칭하여 그 표면을 적층체(P<sub>1</sub>, P<sub>2</sub>)의 중도부까지 후퇴시킨 후, 도 44에 도시한 바와 같이 적층체(P<sub>1</sub>, P<sub>2</sub>) 및 질화 실리콘막(62)의 측벽에 형성된 게이트 전극(66)을 에칭하여 그 상단부를 아래쪽으로 후퇴시킨다.

[0340] 상기 게이트 전극(66)의 에칭은 후의 공정에서 적층체(P<sub>1</sub>, P<sub>2</sub>)의 상부에 형성되는 전원 전압선(90)과 게이트 전극(66)과의 단락을 방지하기 위해서 행한다. 따라서, 게이트 전극(66)은 그 상단부가 상부 반도체층(59)의 상단부보다도 아래쪽으로 위치할 때까지 후퇴시킨다. 단, 게이트 전극(66)과 상부 반도체층(소스)(59)과의 오프셋을 방지하기 위해서, 게이트 전극(66)의 상단부가 중간 반도체층(58)의 상단부보다 상측에 위치하도록 에칭량을 제어한다.

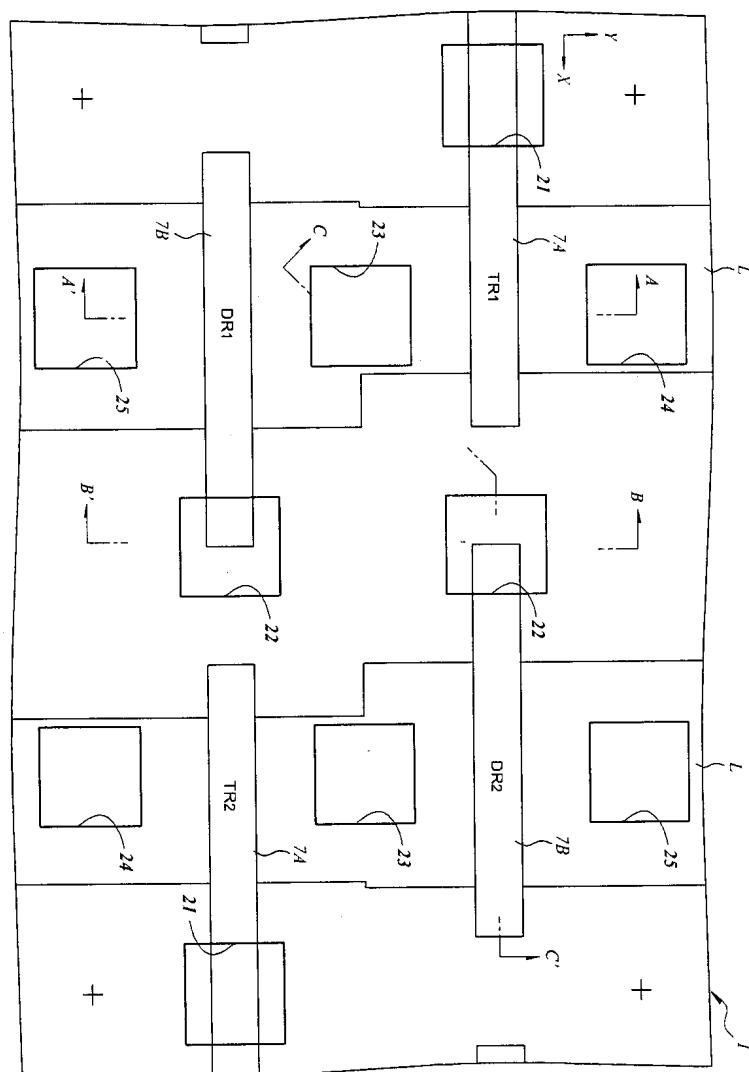

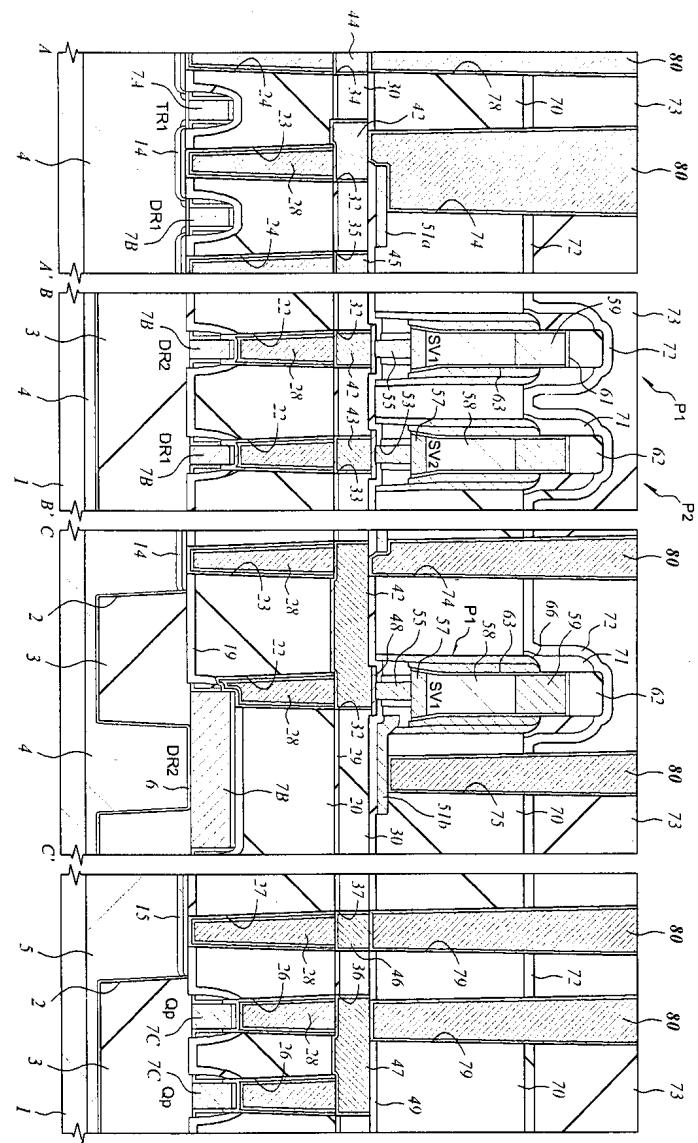

[0341] 도 44 및 도 45에 도시한 바와 같이, 지금까지의 공정에 의해, 메모리 어레이의 각 메모리 셀 영역에, 하부 반도체층(드레인)(57), 중간 반도체층(기판)(58) 및 상부 반도체층(소스)으로 이루어진 적층체(P<sub>1</sub>, P<sub>2</sub>)와, 적층체(P<sub>1</sub>, P<sub>2</sub>)의 측벽에 형성된 게이트 절연막(63) 및 게이트 전극(66)을 갖는 p채널형의 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)이 형성된다.

[0342] 다음으로, 도 46에 도시한 바와 같이, 산화 실리콘막(70)의 상부에 노출된 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(66) 및 상부 반도체층(59)과 그 상부의 질화 실리콘막(62)의 측벽에 산화 실리콘막으로 이루어진 측벽 스페이서(71)를 형성한 후, 산화 실리콘막(70)의 상부에 CVD법으로 질화 실리콘막(72)을 퇴적한다. 측벽 스페이서(71)는 CVD법에 의해 퇴적된 산화 실리콘막을 이방성 에칭함으로써 형성한다.

[0343] 다음으로, 도 47에 도시한 바와 같이 질화 실리콘막(72)의 상부에 CVD법으로 산화 실리콘막(73)을 퇴적한 후, 산화 실리콘막(73)의 표면을 화학적 기계 연마법으로 평탄화한다.

[0344] 다음으로, 도 48 및 도 49에 도시한 바와 같이 포토레지스트막을 마스크로 하여 산화 실리콘막(73), 질화 실리콘막(72) 및 산화 실리콘막(70)을 드라이 에칭함으로써, 게이트 인출 전극(51) 및 중간 도전층(42)의 표면이 노출되는 관통 홀(74)과, 게이트 인출 전극(51) 및 중간 도전층(43)의 표면이 노출되는 관통 홀(75)을 형성한다. 또한, 이 때 도 48에 도시한 바와 같이 중간 도전층(41, 44, 45) 각각의 표면이 노출되는 관통 홀(76, 77, 78)을 형성하여, 주변 회로의 제1층 배선(46, 47)의 표면이 노출되는 관통 홀(79)을 형성한다.

[0345] 다음으로, 도 50에 도시한 바와 같이 상기 관통 홀(74~79)의 내부에 플러그(80)를 형성한다. 플러그(80)를 형성하기 위해서는 예를 들면, 관통 홀(74~79)의 내부를 포함하는 산화 실리콘막(73) 상에 스퍼터링법으로 Ti막 및 TiN막을 퇴적하고, 계속해서 CVD법으로 TiN막 및 W막을 퇴적한 후, 관통 홀(74~79)의 외부의 W막, TiN막 및 Ti막을 화학적 기계 연마법에 의해 제거한다.

[0346] 지금까지의 공정에 의해, 게이트 인출 전극(51a)과, 플러그(80)와, 중간 도전층(42)과, 플러그(28)를 개재하여,

종형 MISFET( $SV_2$ )의 게이트 전극(66)과, 전송 MISFET( $TR_1$ )의 소스, 드레인의 한쪽 및 구동 MISFET( $DR_1$ )의 소스를 구성하는  $n^+$ 형 반도체 영역(14)과, 구동 MISFET( $DR_2$ )의 게이트 전극(7B)이 상호 전기적으로 접속된다. 또한, 게이트 인출 전극(51b)과, 플러그(80)와, 중간 도전층(43)과, 플러그(28)를 개재하여, 종형 MISFET( $SV_1$ )의 게이트 전극(66)과, 전송 MISFET( $TR_2$ )의 소스, 드레인의 한쪽 및 구동 MISFET( $DR_2$ )의 소스를 구성하는  $n^+$ 형 반도체 영역(14)과, 구동 MISFET( $DR_1$ )의 게이트 전극(7B)이 상호 전기적으로 접속된다.

[0347] 또한, 지금까지의 공정에 의해, 2개의 전송 MISFET( $TR_1$ ,  $TR_2$ ), 2개의 구동 MISFET( $DR_1$ ,  $DR_2$ ) 및 2개의 종형 MISFET( $SV_1$ ,  $SV_2$ )에 의해 구성되는 메모리 셀이 대략 완성한다.

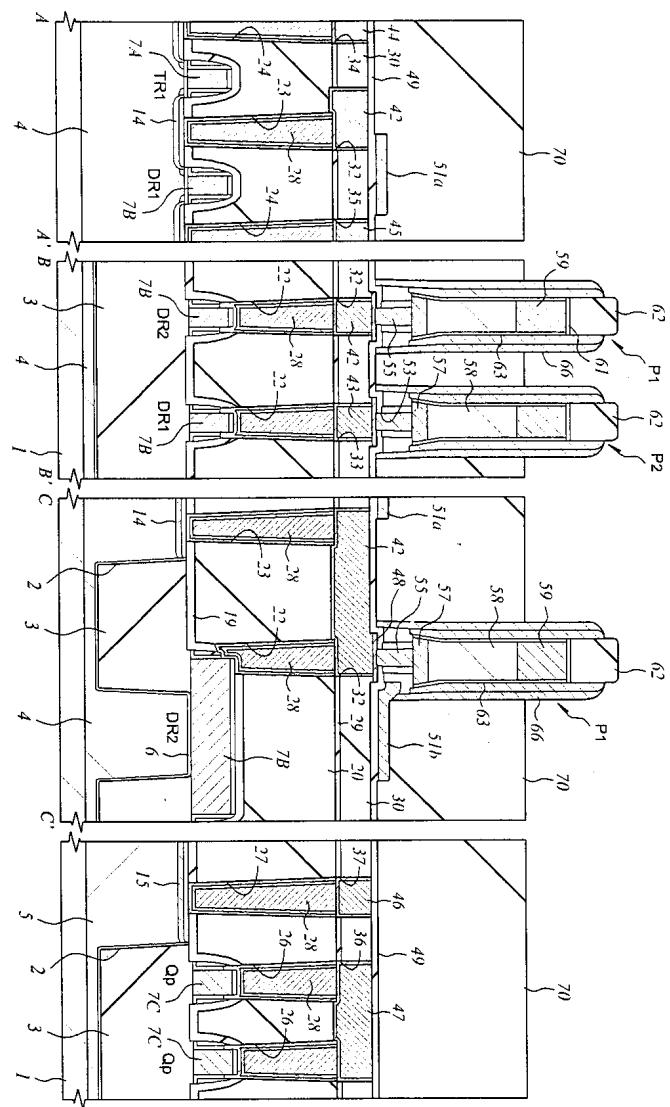

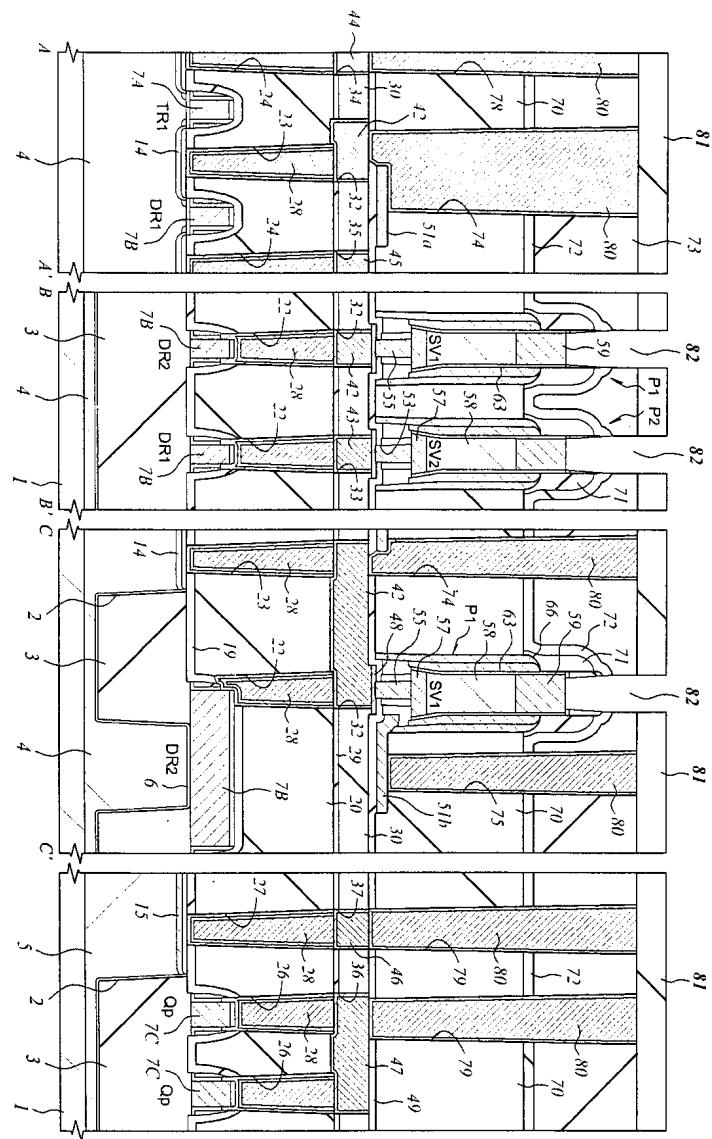

[0348] 다음으로, 도 51에 도시한 바와 같이 산화 실리콘막(73)의 상부에 절연막으로서 CVD법으로 산화 실리콘막(81)을 퇴적한 후, 포토레지스트막을 마스크로 한 드라이 에칭으로 적층체( $P_1$ ,  $P_2$ ) 상부의 산화 실리콘막(81, 73) 및 질화 실리콘막(72, 62)을 제거함으로써, 종형 MISFET( $SV_1$ ,  $SV_2$ )의 상부 반도체층(소스)(59)이 노출된 관통 홀(82)을 형성한다.

[0349] 상기 드라이 에칭을 행할 때는 먼저, 적층체( $P_1$ ,  $P_2$ ) 상부의 산화 실리콘막(81, 73)이 제거된 단계에서 에칭을 일단 정지하고, 다음으로 질화 실리콘막(72, 62)을 에칭한다. 이 때, 도 52에 도시한 바와 같이 포토마스크의 오정렬에 의해, 관통 홀(82)과 상부 반도체층(59)의 상대적인 위치가 예를 들면, B-B' 선 방향으로 어긋난 경우라도, 질화 실리콘막(62) 및 상부 반도체층(59)의 측벽에는 산화 실리콘막으로 이루어진 측벽 스페이서(71)가 형성되어 있기 때문에, 질화 실리콘막(72, 62)을 에칭했을 때에, 게이트 전극(66)의 상부가 측벽 스페이서(71)에 의해 보호되어, 게이트 전극(66)의 노출이 방지된다.

[0350] 다음으로, 도 53에 도시한 바와 같이 주변 회로의 관통 홀(79)의 상부를 덮고 있는 산화 실리콘막(81)을 에칭하여 관통 홀(83)을 형성함으로써, 관통 홀(79)에 매립된 플러그(80)의 표면을 노출시킨다. 또한, 메모리 어레이에 형성된 관통 홀(76~78)의 상부를 덮고 있는 산화 실리콘막(81)을 에칭하고 관통 홀(84)(도 54)을 형성함으로써, 관통 홀(76~78)에 매립된 플러그(80)의 표면을 노출시킨다.

[0351] 다음으로, 도 55에 도시한 바와 같이, 관통 홀(82, 83, 84)의 내부에 플러그(85)를 형성한다. 플러그(85)를 형성하기 위해서는 예를 들면, 관통 홀(82, 83, 84)의 내부를 포함한 산화 실리콘막(81) 상에 스퍼터링법으로 TiN막을 퇴적하고, 계속해서 CVD법으로 TiN막 및 W막을 퇴적한 후, 관통 홀(82, 83, 84) 외부의 TiN막 및 W막을 화학적 기계 연마법에 의해 제거한다.

[0352] 다음으로, 도 56 및 도 57에 도시한 바와 같이 산화 실리콘막(81)의 상부에 CVD법으로 탄화 실리콘막(86)과 산화 실리콘막(87)을 퇴적한 후, 포토레지스트막을 마스크로 하여 관통 홀(82, 83, 84)의 상부의 산화 실리콘막(87)과 탄화 실리콘막(86)을 드라이 에칭함으로써, 배선홈(88)을 형성한다. 도 57에 도시한 바와 같이, 종형 MISFET( $SV_1$ ,  $SV_2$ )의 상측에 위치하는 관통 홀(82)의 상부에 형성된 배선홈(88)과, 이 배선홈(88)의 양측에 인접하여 형성된 2개의 배선홈(88)은 Y 방향으로 연장되는 띠 형상의 평면 패턴을 갖고 있다. 또한, 메모리 셀의 단부에 형성된 4개의 배선홈(88)은 Y 방향에 긴 변을 갖는 구형의 평면 패턴을 갖고 있다.

[0353] 다음으로, 도 58 및 도 59에 도시한 바와 같이 종형 MISFET( $SV_1$ ,  $SV_2$ )의 상측을 통한 배선홈(88)의 내부에 전원 전압선(90)(Vdd)을 형성하고, 주변 회로 영역의 배선홈(88)의 내부에 제2층 배선(89)을 형성한다. 또한, 전송 MISFET( $TR_1$ ) 및 구동 MISFET( $DR_1$ )의  $n^+$ 형 반도체 영역(14)(소스, 드레인) 및 플러그(80)의 상측을 통하는 배선홈(88)의 내부에 상보성 데이터선(BLT, BLB)의 한쪽(데이터선(BLT))을 형성하고, 전송 MISFET( $TR_2$ ) 및 구동 MISFET( $DR_2$ )의  $n^+$ 형 반도체 영역(14)(소스, 드레인) 및 플러그(80)의 상측을 통한 배선홈(88)의 내부에 상보성 데이터선(BLT, BLB)의 다른 쪽(데이터선(BLB))을 형성한다. 또한, 메모리 셀의 단부에 형성된 4개의 배선홈(88)의 내부에 인출 배선(92)을 형성한다.

[0354] 전원 전압선(90)(Vdd), 상보성 데이터선(BLT, BLB), 제2층 배선(89) 및 인출 배선(92)을 형성하기 위해서는 배선홈(88)의 내부를 포함하는 산화 실리콘막(87) 상에 도전성 배리어막으로서 예를 들면, 스퍼터링법으로 질화 탄탈(TaN)막 또는 Ta막을 퇴적하고, 또한 스퍼터링법 또는 도금법으로 금속막인 Cu막을 퇴적한 후, 배선홈(88) 외부의 불필요한 Cu막 및 TaN막을 화학적 기계 연마법으로 제거한다.

[0355] 전원 전압선(90)(Vdd)은 플러그(85)를 개재하여 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 상부 반도체층(소스)(59)과 전기적으로 접속된다. 또한, 상보성 데이터선(BLT, BLB)의 한쪽(데이터선(BLT))은 플러그(84, 80), 중간 도전층(44) 및 플러그(28)를 개재하여 전송 MISFET(TR<sub>1</sub>)의 n<sup>+</sup>형 반도체 영역(14)(소스, 드레인의 다른 쪽)과 전기적으로 접속되며, 다른 쪽(데이터선(BLB))은 플러그(84, 80), 중간 도전층(44) 및 플러그(28)를 개재하여 전송 MISFET(TR<sub>2</sub>)의 n<sup>+</sup>형 반도체 영역(14)(소스, 드레인의 다른 쪽)과 전기적으로 접속된다.

[0356] 다음으로, 도 60 및 도 61에 도시한 바와 같이 상기 전원 전압선(90)(Vdd), 상보성 데이터선(BLT, BLB), 제2층 배선(89) 및 인출 배선(92)이 형성된 배선층의 상부에 기준 전압선(91)(Vss) 및 워드선(WL)을 형성한다. 기준 전압선(91)(Vss) 및 워드선(WL)은 도 61의 X 방향으로 연장된 띠 형상의 평면 패턴을 갖고 있다.

[0357] 기준 전압선(91)(Vss) 및 워드선(WL)을 형성하기 위해서는 먼저, 산화 실리콘막(87)의 상부에 절연막(93)을 퇴적한 후, 이 절연막(93)에 배선홈(94)을 형성하고, 계속해서 이 배선홈(94)의 내부를 포함한 절연막(93) 상에 상술한 방법으로 Cu막 및 TaN막을 퇴적한 후, 배선홈(94)의 외부의 불필요한 Cu막 및 TaN막을 화학적 기계 연마법으로 제거한다. 절연막(93)은 예를 들면, CVD법에 의해 퇴적된 산화 실리콘막과 탄화 실리콘막과 산화 실리콘막과의 적층막으로 구성한다. 또한, 절연막(93)에 배선홈(94)을 형성할 때에는 메모리 셀의 단부에 형성된 4개의 인출 배선(92) 각각의 상부의 배선홈(94)에 개구(94a)를 형성하고, 이들 개구(94a)를 통해 4개의 인출 배선(92)의 각각의 일부를 배선홈(94)의 바닥부에 노출시킨다.

[0358] 기준 전압선(91)(Vss)은 인출 배선(92), 플러그(84, 80), 중간 도전층(45) 및 플러그(28)를 개재하여 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>) 각각의 n<sup>+</sup>형 반도체 영역(14)(소스)과 전기적으로 접속된다. 또한, 워드선(WL)은 인출 배선(92), 플러그(84, 80), 중간 도전층(41) 및 플러그(28)를 개재하여 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>)의 각각의 n<sup>+</sup>형 반도체 영역(14)(소스, 드레인의 다른 쪽)과 전기적으로 접속된다. 지금까지의 공정에 의해, 상기 도 2, 도 3에 도시한 본 실시예의 SRAM이 완성된다.

[0359] 이와 같이, 주변 회로를 구성하는 MISFET 간의 전기적 접속을 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)보다도 하부에 형성된 플러그(28) 및 중간 도전층(46, 47)으로 행함과 함께, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)보다도 상부에 형성된 플러그, 제1 및 제2 금속 배선층을 이용하여 행함으로써, 배선의 자유도를 향상시킬 수 있고, 고집적화할 수 있다. 또한, MISFET 간의 접속 저항을 저감할 수 있고, 회로의 동작 스피드 향상시킬 수 있다.

[0360] (실시예 2)

[0361] 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 하부의 플러그(55) 및 배리어층(48)은 다음과 같은 방법으로 형성할 수도 있다.

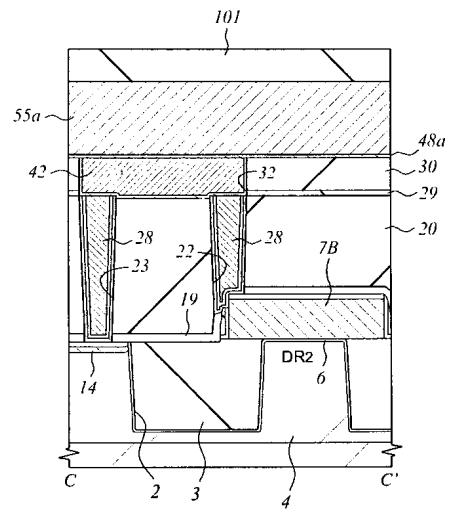

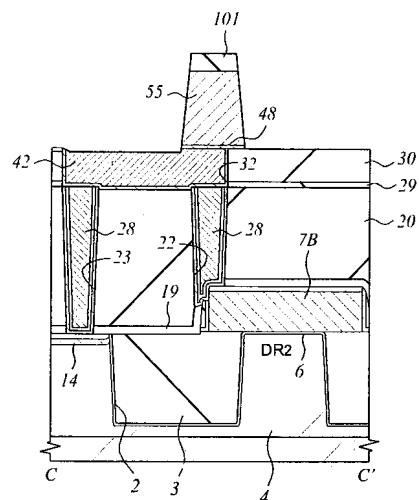

[0362] 먼저, 도 62에 도시한 바와 같이 상기 실시예 1과 마찬가지의 방법으로 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>) 및 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>)을 형성하고, 이들 상부에 중간 도전층(42)을 형성한다.

[0363] 다음으로, 본 실시예에서는 중간 도전층(42)의 상부에 배리어층(48)을 구성한 WN막(48a)을 스퍼터링법으로 퇴적하며, 또한 그 상부에 플러그(55)를 구성하는 다결정 실리콘막(또는, 비정질 실리콘막)(55a)을 CVD법으로 퇴적하고, 또한 그 상부에 CVD법으로 산화 실리콘막(101)을 퇴적한다. 다결정 실리콘막(50)은 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(66)을 구성하는 다결정 실리콘막(64, 65)과 동일한 도전형(예를 들면, p형)으로 하기 위해서 붕소를 도핑한다.

[0364] 다음으로, 도 63에 도시한 바와 같이 포토레지스트막을 마스크로 하여 산화 실리콘막(101)을 드라이 에칭함으로써, 플러그(55)를 형성하는 영역에 산화 실리콘막(101)을 남기고, 계속해서 이 산화 실리콘막(101)을 마스크로 하여 다결정 실리콘막(50) 및 WN막(48a)을 드라이 에칭함으로써, 플러그(55) 및 배리어층(48)을 형성한다.

[0365] 다음으로, 도 64에 도시한 바와 같이, CVD법에 의해 퇴적된 산화 실리콘막(102)을 화학적 기계 연마법으로 평탄화한다. 이 때, 플러그(55)의 상부에 남긴 에칭 마스크용의 산화 실리콘막(101)을 플러그(55)의 표면이 노출할 때까지 연마한다.

[0366] 상기한 방법에 따르면, 플러그(55) 및 배리어층(48)을 1회의 에칭으로 동시에 형성하기 때문에, 배리어층(48)을 형성하기 위한 포토마스크가 불필요해져서, 공정을 간략화할 수 있다.

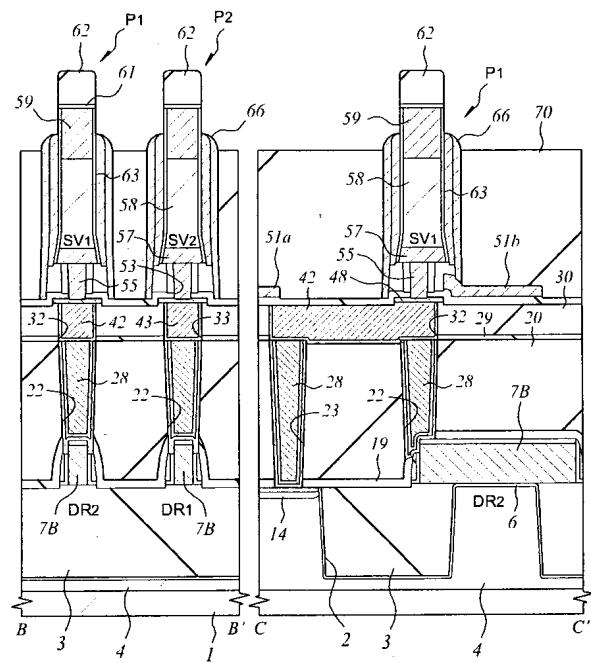

[0367] (실시예 3)

[0368] 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극과 하층의 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>) 및 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>)과의 접속에 사용되는 게이트 인출 전극은 다음과 같은 방법으로 형성할 수도 있다.

[0369] 먼저, 도 65에 도시한 바와 같이 상기 실시예 1과 마찬가지의 방법으로 전송 MISFET(TR<sub>1</sub>, TR<sub>2</sub>) 및 구동 MISFET(DR<sub>1</sub>, DR<sub>2</sub>)의 상부에 적층체(P<sub>1</sub>, P<sub>2</sub>)를 형성한 후, 예를 들면, 기판(1)을 열 산화함으로써, 중간 반도체층(58) 및 상부 반도체층(59) 각각의 측벽 표면에 산화 실리콘막으로 이루어진 게이트 절연막(63)을 형성한다.

[0370] 다음으로, 적층체(P<sub>1</sub>, P<sub>2</sub>)의 상부에 게이트 인출 전극용의 다결정 실리콘막(또는, 비정질 실리콘막)(103)을 CVD법으로 퇴적하고, 계속해서, CVD법으로 산화 실리콘막(104)을 퇴적한 후, 화학적 기계 연마법으로 그 표면을 평탄화한다. 산화 실리콘막(104)은 평탄화 후의 표면의 높이가 질화 실리콘막(62)의 표면보다 높아지도록 두꺼운 막 두께로 퇴적되어, 평탄화 처리 시에 질화 실리콘막(62)의 표면이 깎이지 않도록 한다.

[0371] 다음으로, 도 66에 도시한 바와 같이 포토레지스트막을 마스크로 한 드라이 에칭에 의해 게이트 인출 전극 형성 영역의 산화 실리콘막(104)을 적층체(P<sub>1</sub>, P<sub>2</sub>)의 중도부까지 제거함으로써, 게이트 인출 전극 형성 영역의 산화 실리콘막(104)에 홈(105)을 형성한다. 다음으로, 예를 들면, 포토레지스트막(106) 또는 반사 방지막과 같이 산화 실리콘막(104)은 에칭의 선택비가 다른 재료를 홈(105)의 내부에 매립한다. 포토레지스트막(106)을 매립하는 경우에는 홈(105)의 내부를 포함한 산화 실리콘막(104) 상에 포토레지스트막(106)을 도포한 후, 노광, 현상을 행하여, 홈(105)의 내부에 미 노광의 포토레지스트막(106)을 남긴다.

[0372] 다음으로, 도 67에 도시한 바와 같이 홈(105)의 내부에 매립된 포토레지스트막(106)을 마스크로 하여 산화 실리콘막(104)을 드라이 에칭함으로써, 게이트 인출 전극 형성 영역에만 산화 실리콘막(104)을 남긴다.

[0373] 다음으로, 산화 실리콘막(104) 상의 포토레지스트막(106)을 제거한 후, 도 68에 도시한 바와 같이 산화 실리콘막(104)을 마스크로 하여 다결정 실리콘막(103)을 이방성 에칭하고, 적층체(P<sub>1</sub>, P<sub>2</sub>)의 측벽 및 산화 실리콘막(104)의 하부에, 다결정 실리콘막(103)으로 이루어진 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(107)을 형성한다. 이 때, 산화 실리콘막(104)의 하부에 남은 게이트 전극(107)의 일부가 게이트 인출 전극으로 된다. 지금까지의 공정에 의해, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)이 완성된다.

[0374] 다음으로, 산화 실리콘막(104)을 제거한 후, 도 69에 도시한 바와 같이 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 상부에 CVD법으로 산화 실리콘막(98) 및 질화 실리콘막(99)을 퇴적하고, 계속해서 상기 실시예 1과 마찬가지의 방법으로 관통 홀(74, 75) 및 플러그(80)를 형성함으로써, 게이트 전극(107)의 일부(게이트 인출 전극) 및 중간 도전층(42, 43) 각각과 플러그(80)를 전기적으로 접속한다. 그 후, 도 70에 도시한 바와 같이, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 상부에 플러그(85), 전원 전압선(90)(Vdd) 및 상보성 데이터선(BLT, BLB)을 형성한다.

[0375] 상기한 방법에 따르면, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(107)과 게이트 인출 전극을 동시에 형성할 수 있음과 함께, 게이트 전극(107)을 한층의 다결정 실리콘막(103)으로 구성할 수 있기 때문에, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 형성 공정을 간략화할 수 있다.

[0376] (실시예 4)

[0377] 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 상부 반도체층(59)과 상보성 데이터선(BLT, BLB)을 접속하는 관통 홀은 다음과 같은 방법으로 형성할 수도 있다.

[0378] 먼저, 도 71에 도시한 바와 같이 상기 실시예 1과 마찬가지의 방법으로 적층체(P<sub>1</sub>, P<sub>2</sub>)의 측벽에 게이트 전극(66)을 형성한 후, 기판(1) 상에 퇴적된 산화 실리콘막(70)을 에칭하여 그 표면을 적층체(P<sub>1</sub>, P<sub>2</sub>)의 중도부까지 후퇴시킨 후, 적층체(P<sub>1</sub>, P<sub>2</sub>) 및 질화 실리콘막(62)의 측벽에 형성된 게이트 전극(66)을 에칭하고 그 상단부를 아래쪽으로 후퇴시킨다. 지금까지의 공정은 상기 실시예 1과 동일하다(도 44 참조).

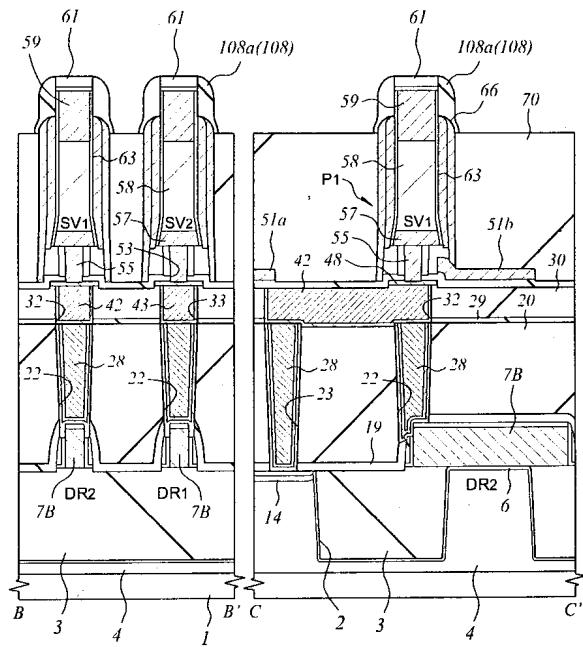

[0379] 다음으로, 도 72에 도시한 바와 같이, 산화 실리콘막(70) 상에 CVD법에 의해 퇴적된 질화 실리콘막(108)을 이방성 에칭함으로써, 산화 실리콘막(70)의 상부에 노출된 적층체(P<sub>1</sub>, P<sub>2</sub>) 및 게이트 전극(66)의 측벽에 질화 실리콘

막(108)으로 이루어진 측벽 스페이서(108a)를 형성한다. 이 때, 적층체( $P_1, P_2$ )의 상부에 형성된 질화 실리콘막(62)도 예칭되어, 그 막 두께가 얇아진다.

[0380] 다음으로, 도 73에 도시한 바와 같이 산화 실리콘막(70) 상에 CVD법으로 산화 실리콘막(109)을 퇴적한 후, 상기 실시예 1과 마찬가지의 방법으로 게이트 인출 전극(51)의 상부에 관통 홀(75)을 형성하며, 관통 홀(75)의 내부에 플러그(80)를 형성한다.

[0381] 다음으로, 도 74에 도시한 바와 같이 산화 실리콘막(109) 상에 CVD법으로 산화 실리콘막(110)을 퇴적한 후, 포토레지스트막을 마스크로 하여, 적층체( $P_1, P_2$ ) 상부의 산화 실리콘막(110, 109) 및 질화 실리콘막(62)을 순차 드라이 예칭함으로써, 적층체( $P_1, P_2$ )의 상부에 상부 반도체층(59)이 노출하는 관통 홀(82)을 형성한다.

[0382] 이 때, 포토마스크의 오정렬에 의해, 관통 홀(82)과 상부 반도체층(59)이 상대적인 위치가 어긋난 경우라도, 상부 반도체층(59)의 상부의 질화 실리콘막(62)은 게이트 전극(66)의 상부의 질화 실리콘막(108)으로 이루어진 측벽 스페이서(108a)에 비해 막 두께가 얇기 때문에, 측벽 스페이서(108a)로 덮힌 영역의 게이트 전극(66)이 노출되기 전에 상부 반도체층(59)을 노출시킬 수 있다.

[0383] 도시는 생략하겠지만, 그 후, 상기 실시예 1과 마찬가지의 방법으로 관통 홀(82)의 내부에 플러그(85)를 형성하고, 또한 플러그(85)의 상부에 상보성 데이터선(BLT, BLB)을 형성한다.

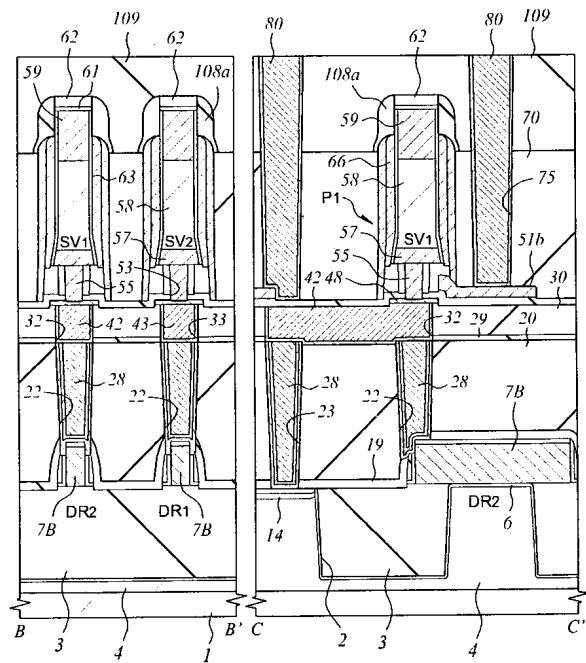

[0384] 상기 관통 홀(82)은 다음과 같은 방법으로 형성할 수도 있다. 이 방법은 도 75에 도시한 바와 같이, 종형 MISFET( $SV_1, SV_2$ )의 상부 반도체층(59)을 구성한 p형 실리콘막(59p)과 그 상부의 질화 실리콘막(62)과의 사이에 개재된 산화 실리콘막(61)의 막 두께를 상기 실시예 1보다도 두텁게 형성해 두고, 그 후, 상기 실시예 1과 마찬가지의 방법으로 적층체( $P_1, P_2$ )를 형성한다.

[0385] 다음으로, 도 76에 도시한 바와 같이, 상기 실시예 1과 마찬가지의 방법으로 적층체( $P_1, P_2$ )의 측벽에 게이트 전극(66)을 형성한 후, 기판(1) 상에 퇴적된 산화 실리콘막(70)를 예칭하여 그 표면을 적층체( $P_1, P_2$ )의 중도부까지 후퇴시키고, 또한 적층체( $P_1, P_2$ ) 및 질화 실리콘막(62)의 측벽에 형성된 게이트 전극(66)을 예칭하여 그 상단부를 아래쪽으로 후퇴시킨다.

[0386] 다음으로, 도 77에 도시한 바와 같이 산화 실리콘막(70) 상에 CVD법에 의해 퇴적된 질화 실리콘막(108)을 이방성 예칭함으로써, 산화 실리콘막(70)의 상부에 노출된 적층체( $P_1, P_2$ ) 및 게이트 전극(66)의 측벽에 질화 실리콘막(108)으로 이루어진 측벽 스페이서(108a)를 형성한다. 이 때, 적층체( $P_1, P_2$ )의 상부에 형성된 질화 실리콘막(62)을 동시에 예칭하고, 그 하층의 산화 실리콘막(61)을 노출시킨다.

[0387] 다음으로, 도 78에 도시한 바와 같이, 산화 실리콘막(70) 상에 CVD법으로 산화 실리콘막(109)을 퇴적한 후, 상기 실시예 1과 마찬가지의 방법으로 게이트 인출 전극(51)의 상부에 관통 홀(75)을 형성하여, 관통 홀(75)의 내부에 플러그(80)를 형성한다.

[0388] 다음으로, 도 79에 도시한 바와 같이 산화 실리콘막(109) 상에 CVD법으로 산화 실리콘막(110)을 퇴적한 후, 포토레지스트막을 마스크로 하여, 적층체( $P_1, P_2$ ) 상부의 산화 실리콘막(109) 및 산화 실리콘막(61)을 드라이 예칭함으로써, 적층체( $P_1, P_2$ )의 상부에 상부 반도체층(59)이 노출되는 관통 홀(82)을 형성한다.

[0389] 이 때, 포토마스크의 오정렬에 의해, 관통 홀(82)과 상부 반도체층(59)의 상대적인 위치가 어긋난 경우라도, 게이트 전극(66)의 상부는 질화 실리콘막(108)으로 이루어진 측벽 스페이서(108a)로 덮여져 있기 때문에, 게이트 전극(66)을 노출시키지 않고 상부 반도체층(59)을 노출시킬 수 있다.

[0390] 도시는 생략하겠지만, 그 후, 상기 실시예 1과 마찬가지의 방법으로 관통 홀(82)의 내부에 플러그(85)를 형성하며, 또한 플러그(85)의 상부에 상보성 데이터선(BLT, BLB)을 형성한다.

[0391] (실시예 5)

[0392] 종형 MISFET( $SV_1, SV_2$ )의 게이트 전극과 하층의 전송 MISFET( $TR_1, TR_2$ ) 및 구동 MISFET( $DR_1, DR_2$ )과의 접속은 다음과 같은 방법으로 행할 수도 있다.

[0393] 먼저, 도 80에 도시한 바와 같이, p형 웨(4)의 주면에 전송 MISFET( $TR_1, TR_2$ ) 및 구동 MISFET( $DR_1, DR_2$ )을 형성

하고, 계속해서 전송 MISFET( $TR_1$ ,  $TR_2$ ) 및 구동 MISFET( $DR_1$ ,  $DR_2$ )의 상부를 덮는 산화 실리콘막에 컨택트홀(22~24)을 형성한 후, 컨택트홀(22~24)의 내부에 W막을 주성분으로 하는 플러그(28)를 매립한다. 그리고, 산화 실리콘막(20)의 상부에 질화 실리콘막(29)과 산화 실리콘막(30)을 퇴적한 후, 포토레지스트막을 마스크로 하여 산화 실리콘막(29) 및 질화 실리콘막(30)을 드라이 에칭함으로써, 컨택트홀(22~24) 각각의 상부에 홈(31~34)을 형성한다. 지금까지의 공정은 상기 실시예 1의 도 4~도 23에 도시한 공정과 동일하다

[0394] 다음으로, 도 81에 도시한 바와 같이 홈(31~34)의 내부에 중간 도전층(42~44)을 형성한다. 중간 도전층(42~44)은 예를 들면, W 실리사이드( $WSi_2$ )막과 같은 내 산화성의 도전막으로 구성된다. 중간 도전층(42~44)을 W 실리사이드막으로 구성하는 경우에는 예를 들면, 홈(31~34)의 내부를 포함하는 산화 실리콘막(30) 상에 스퍼터링법으로 TiN막 등의 접착층을 퇴적하고, 다음으로 스퍼터링법으로 그 상부에 W 실리사이드막을 퇴적한 후, 홈(31~34) 외부의 W 실리사이드막 및 TiN막을 화학적 기계 연마법에 의해 제거한다.

[0395] 중간 도전층(42~44)을 W 실리사이드막과 같은 내 산화성의 도전막으로 구성한 경우에는 중간 도전층(42~44)의 표면에 배리어층(48)을 형성하거나, 배리어층(48)의 상부에 다결정 실리콘막으로 이루어진 플러그(55)를 형성하였기도 하는 공정이 불필요해진다.

[0396] 다음으로, 도 82에 도시한 바와 같이 상기 실시예 1의 도 35~도 38에 도시한 공정에 따라, 산화 실리콘막(20)의 상부에 3층의 실리콘막(57p, 58i, 59p)과 산화 실리콘막(61) 및 질화 실리콘막(62)을 퇴적하고, 계속해서 질화 실리콘막(62)을 마스크로 하여 3층의 실리콘막(57p, 58i, 59p)을 드라이 에칭함으로써, p형 실리콘막(57p)으로 이루어진 하부 반도체층(57), 실리콘막(58i)으로 이루어진 중간 반도체층(58), p형 실리콘막(59p)으로 이루어진 상부 반도체층(59)에 의해 구성되는 적층체( $P_1$ ,  $P_2$ )를 형성한다.

[0397] 다음으로, 도 83에 도시한 바와 같이 기판(1)을 열 산화함으로써, 적층체( $P_1$ ,  $P_2$ )를 구성하는 하부 반도체층(57), 중간 반도체층(58) 및 상부 반도체층(59) 각각의 측벽 표면에 산화 실리콘막으로 이루어진 게이트 절연막(63)을 형성한다. 이 때, 적층체( $P_1$ ,  $P_2$ )로 덮어져 있지 않은 영역의 중간 도전층(42~44)도 산화 분위기에 노출되지만, 중간 도전층(42~44)은 내 산화성의 도전막으로 구성되어 있기 때문에, 표면이 산화되더라도 내부까지 산화되는 경우는 없다.

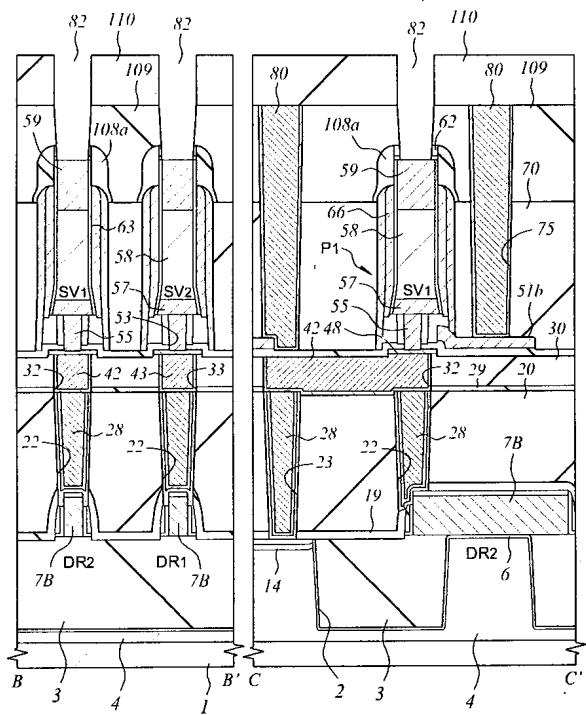

[0398] 다음으로, 도 84에 도시한 바와 같이 상기 실시예 1의 도 40~도 42에 도시한 공정에 따라, 적층체( $P_1$ ,  $P_2$ ) 및 그 상부의 질화 실리콘막(62)의 측벽에 종형 MISFET( $SV_1$ ,  $SV_2$ )의 게이트 전극(66)을 형성하고, 계속해서, 기판(1) 상에 CVD법으로 산화 실리콘막(70)을 퇴적한 후, 화학적 기계 연마법으로 그 표면을 평탄화한다. 게이트 전극(66)은 예를 들면, p형의 다결정 실리콘막으로 구성하지만, 도면에 도시한 바와 같이 1층의 다결정 실리콘막으로 구성할 수도 있다.

[0399] 다음으로, 도 85에 도시한 바와 같이 포토레지스트막을 마스크로 하여 산화 실리콘막(70)을 드라이 에칭함으로써, 적층체( $P_1$ ,  $P_2$ )의 주위를 개구하는 홈(95)을 형성한다.

[0400] 다음으로, 도 86에 도시한 바와 같이 홈(95)의 내부를 포함하는 산화 실리콘막(70) 상에 CVD법으로 p형 다결정 실리콘막을 퇴적한 후, 홈(95) 외부의 다결정 실리콘막을 화학적 기계 연마 또는 에치백에 의해 제거한다. 계속해서, 홈(95) 내부의 다결정 실리콘막 및 게이트 전극(63)을 에치백함으로써, 다결정 실리콘막 및 게이트 전극(63) 각각의 상면을 산화 실리콘막(70)의 상면보다도 아래쪽으로 후퇴시켜, 홈(95)의 내부에 다결정 실리콘막으로 이루어진 게이트 인출 전극(96)을 형성한다. 그 후, 게이트 인출 전극(96)의 표면에 예를 들면, Co 실리사이드 등의 실리사이드층을 형성함으로써, 다음의 공정에서 게이트 인출 전극(96)의 상부에 형성한 플러그(80)와 게이트 인출 전극(96)의 컨택트 저항을 저감해도 된다.

[0401] 다음으로, 도 87에 도시한 바와 같이 홈(95)의 내부에 산화 실리콘막(97)을 매립하여 그 표면을 평탄화한 후, 상기 실시예 1의 도 48~도 50에 도시한 공정에 따라, 산화 실리콘막(70)을 드라이 에칭함으로써, 게이트 인출 전극(96) 및 중간 도전층(42)의 표면이 노출되는 관통 홀(74)을 형성하고, 계속해서 관통 홀(74)의 내부에 플러그(80)를 형성한다. 플러그(80)를 형성하기 위해서는 예를 들면, 관통 홀(74~79)의 내부를 포함하는 산화 실리콘막(73) 상에 스퍼터링법으로 Ti막 및 TiN막을 퇴적하고, 계속해서 CVD법으로 TiN막 및 W막을 퇴적한 후, 관통 홀(74~79)의 외부의 W막, TiN막 및 Ti막을 화학적 기계 연마법에 의해 제거한다. 이것에 의해, 게이트 인출 전극(96)과, 플러그(80)와, 중간 도전층(42)과, 플러그(28)를 개재하여, 종형 MISFET( $SV_2$ )의 게이트 전극

(66)과, 전송 MISFET(TR<sub>1</sub>) 및 구동 MISFET(DR<sub>1</sub>)에 공통의 n<sup>+</sup>형 반도체 영역(14)(소스 또는 드레인)과, 구동 MISFET(DR<sub>2</sub>)의 게이트 전극(7B)이 상호 전기적으로 접속된다.

[0402] 본 실시예에 따르면, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(66)과 게이트 인출 전극(96)과의 접촉 면적을 넓게 할 수 있기 때문에, 게이트 전극(66)과 게이트 인출 전극(96)의 컨택트 저항을 저감할 수 있다.

[0403] (실시예 6)

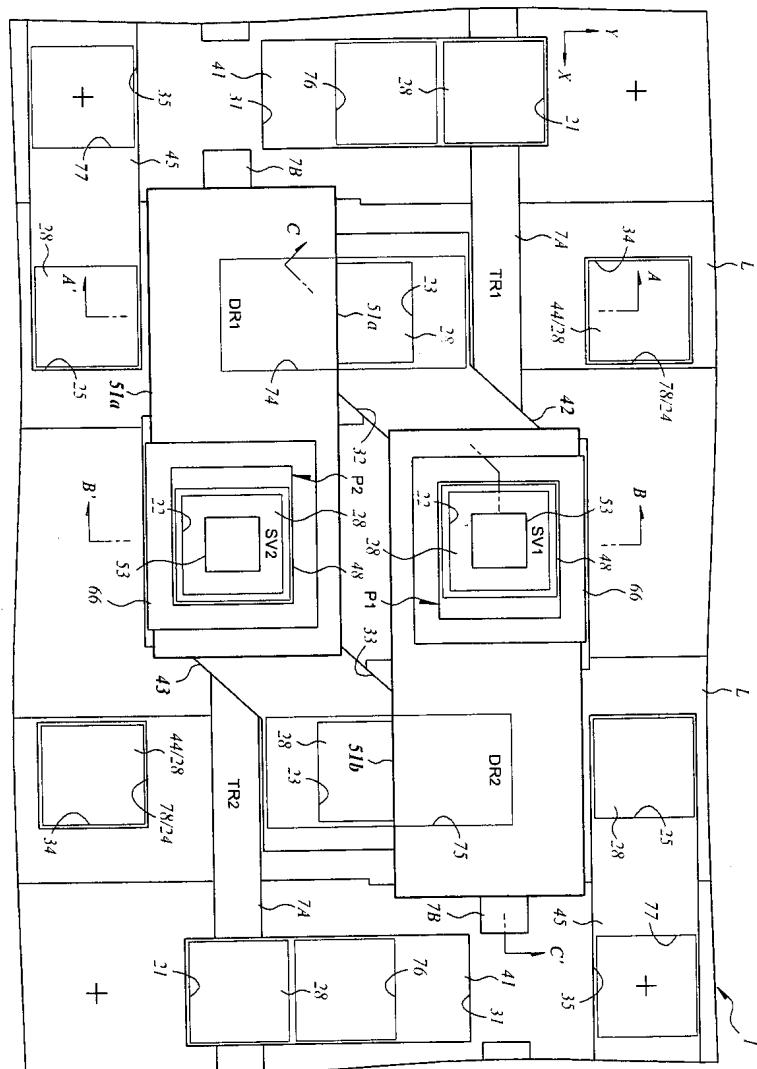

[0404] 도 88은 본 실시예의 메모리 셀의 평면도, 도 89는 도 88의 A-A"선을 따른 단면도이다.

[0405] 상기 도 29에 도시한 바와 같이, 실시예 1의 메모리 셀은 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(66)에 접속되는 게이트 인출 전극(51)을 도면의 X 방향으로 긴 변을 갖는 구형의 평면 패턴으로 구성하고 있다. 이것에 대하여, 도 88에 도시한 바와 같이, 본 실시예의 메모리 셀은 게이트 인출 전극(51)을 도면의 Y 방향으로 긴 변을 갖는 구형의 평면 패턴으로 구성하고 있다.

[0406] 게이트 인출 전극(51)을 이러한 평면 패턴으로 구성한 경우에는 게이트 인출 전극(51)의 X 방향의 치수가 작아진 만큼, 적층체(P<sub>1</sub>, P<sub>2</sub>)의 X 방향의 치수를 크게 할 수 있다. 이것에 의해, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 면적을 크게 할 수 있기 때문에, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 드레인 전류(Ids)를 증대할 수 있다.

[0407] 또한, 게이트 인출 전극(51)을 이러한 평면 패턴으로 구성한 경우에는, 도 89에 도시한 바와 같이, 게이트 인출 전극(51)과 관통 홀(74)과 중간 도전층(42, 43)의 평면 패턴이 중첩하기 때문에, 포토마스크의 정합 어긋남에 의해 게이트 인출 전극(51)과 관통 홀(74)과의 상대적인 위치가 어긋난 경우라도, 양자의 접촉 면적의 감소를 억제할 수 있다. 이 경우, 관통 홀(74)은 게이트 인출 전극(51)을 관통하여 하층의 중간 도전층(42, 43)의 표면에 도달하는 것이 되기 때문에, 관통 홀(74) 내의 플러그(80)는 관통 홀(74)의 내벽에 노출된 게이트 인출 전극(51)의 측면에 접촉한다.

[0408] (실시예 7)

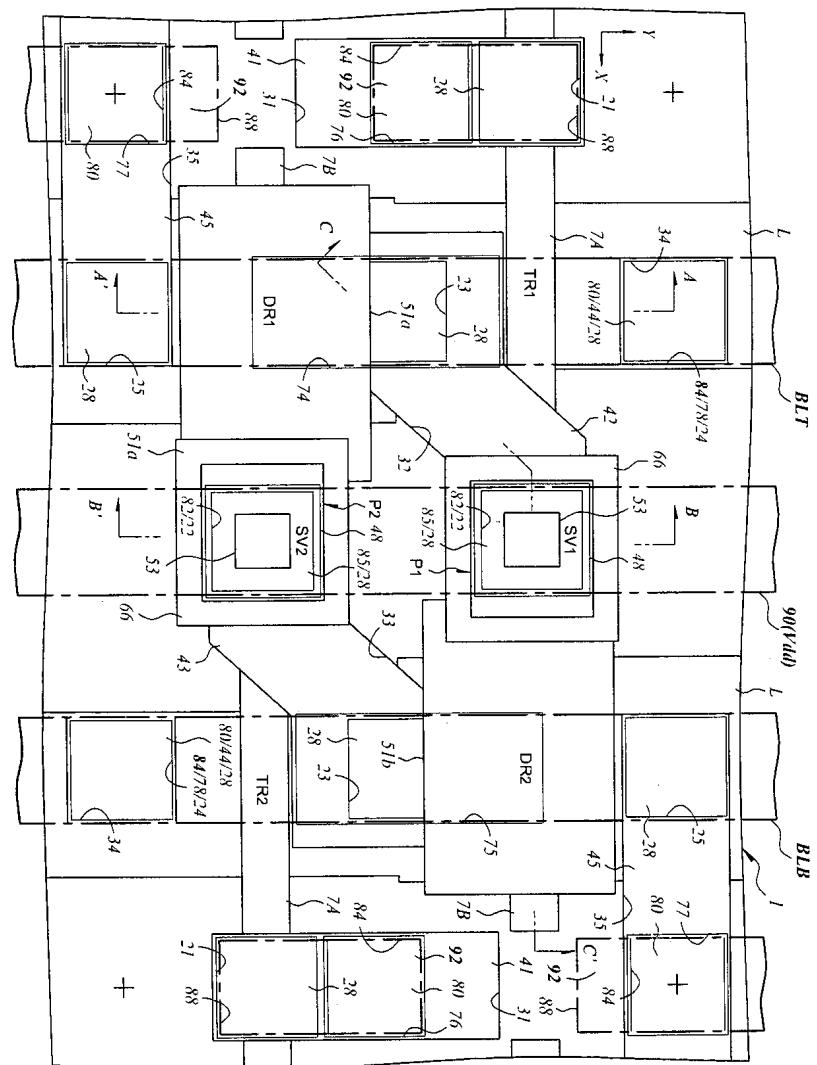

[0409] 도 90은 본 실시예의 메모리 셀의 평면도, 도 91은 도 90의 주요부 단면도이다. 도 90에 도시한 바와 같이 본 실시예와 실시예 1과는 중간 도전막(42, 43) 및 게이트 인출 전극(51a, 51b)의 평면 패턴이 다른 것 이외에는 동일하다. 또, 도 90은 실시예 1의 도 48에 대응하며, 도 91은 실시예 1의 도 3에 대응한다.

[0410] 도 90 및 도 91에 도시한 바와 같이, 게이트 인출 전극(51a, 51b)은 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(66) (제2 다결정 실리콘층(65))의 하단부를 덮도록 평면 패턴으로 구성된다. 이것에 의해, 게이트 전극(66) (제2 다결정 실리콘층(65))은 측벽 스페이서형으로 형성된 게이트 전극(66) (제2 다결정 실리콘층(65))의 하단부의 거의 전체 둘레의 게이트에 걸쳐 인출 전극(51a, 51b)과 접촉하기 때문에, 인출 전극(51a, 51b)과, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(66) (제2 다결정 실리콘층(65))과의 접촉 면적을 증대할 수 있어서, 접속 저항을 저감할 수 있고, 메모리 셀의 특성을 향상시킬 수 있다. 또, 게이트 인출 전극(51a, 51b)과, 플러그(55)는 절연막으로 이루어진 측벽 스페이서(54) 및 절연막(52)에 의해 전기적으로 분리되어 있다. 또, 본 실시예의 제조 공정은 실질적으로 실시예 1과 마찬가지이다. 도 92~도 94에, 본 실시예의 제조 공정을 나타내는 주요부 단면도를 도시한다. 도 92는 실시예 1의 도 30에 대응하며, 도 93은 실시예 1의 도 31에 대응하고, 도 94는 실시예 1의 도 32에 대응한다. 도 92, 도 93에 도시한 바와 같이, 게이트 인출 전극(51a, 51b)에 관통 홀(53)이 형성되며, 도 94에 도시한 바와 같이, 관통 홀(53)의 측벽에 절연막으로 이루어진 측벽 스페이서(54)가 관통 홀(53)에 대하여 자기 정합적으로 형성된다. 이와 같이, 게이트 인출 전극(51a, 51b)과, 플러그(55)는 절연막으로 이루어진 측벽 스페이서(54) 및 절연막(52)에 의해 전기적으로 분리되어 있다.

[0411] 또한, 도 90 및 도 91에 도시한 바와 같이, 중간 도전막(42)은 게이트 인출 전극(51b)과 정합 마진이 허용되는 범위 내에서 평면적으로 볼 때 중첩되도록 구성되며, 중간 도전막(43)은 게이트 인출 전극(51a)과 정합 마진이 허용되는 범위 내에서 평면적으로 볼 때 중첩되도록 구성된다. 이것에 의해, 중간 도전막(42)을 한쪽의 전극으로 하며, 게이트 인출 전극(51b)을 다른 쪽의 전극으로 하고, 그 사이에 형성된 질화 실리콘막(49)을 용량 절연막으로 한 제1 용량 소자가 형성된다. 또한, 중간 도전막(43)을 한쪽의 전극으로 하며, 게이트 인출 전극(51a)을 다른 쪽의 전극으로 하고, 그 사이에 형성된 질화 실리콘막(49)을 용량 절연막으로 한 제2 용량 소자가 형성된다. 제1 용량 소자 및 제2 용량 소자 각각은 한쪽의 전극이 축적 노드 A에 전기적으로 접속되며, 다른 쪽의 전극이 축적 노드 B에 전기적으로 접속된다. 즉, 제1 용량 소자 및 제2 용량 소자는, 한 쌍의 축적 노드 A,

B 사이에 부가되어, 메모리 셀의 소프트 에러 내성을 향상시킬 수 있다. 또, 용량 절연막을 실리콘 산화막보다도 유전율이 높은 질화 실리콘막(49)으로 구성되어 있기 때문에, 용량값을 증대할 수 있다.

[0412] (실시예 8)

[0413] 상기 실시예 1의 메모리 셀은 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(66)과 축적 노드를 접속하는 게이트 인출 전극(51)(51a, 51b)을 p형의 다결정 실리콘막(50)으로 구성하고 있다.

[0414] 상기 게이트 인출 전극(51a, 51b)은 적층체(P<sub>1</sub>, P<sub>2</sub>)의 측벽에 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(66)의 일부를 구성하는 제1 다결정 실리콘층(64)을 형성하는 공정 (도 40 참조), 게이트 전극(66)의 다른 부분을 구성하는 제2 다결정 실리콘층(65)을 형성하는 공정 (도 41 참조) 및 게이트 인출 전극(51a, 51b)의 상부에 관통 홀(74, 75)을 형성하는 공정 (도 49 참조)에서 그 표면이 에칭된다. 그 때문에, 게이트 인출 전극(51a, 51b)을 다결정 실리콘막(50)으로 구성한 경우에는 상기 3회의 에칭 공정을 거친 후에 게이트 인출 전극(51a, 51b)의 막 두께가 얇아지고, 최악의 경우에는 관통 홀(74, 75)의 내부에 형성된 플러그(80)와 게이트 인출 전극(51a, 51b)의 접촉 저항이 큰 폭으로 증가될 우려가 있다.

[0415] 그 대책으로서, 게이트 인출 전극(51a, 51b)을 WN막이나 TiN막과 같은 질화 금속막으로 구성하는 것이 유효하다.

[0416] 질화 금속막은 절연막에 대한 에칭 선택이 다결정 실리콘막에 비해 크기 때문에, 상기 3회의 에칭에 의한 막의 각임이 적다. 그 때문에, 게이트 인출 전극(51a, 51b)의 막 두께를 당초부터 얇게 할 수 있으므로, 게이트 인출 전극(51a, 51b)을 덮는 산화 실리콘막(52)의 막 두께도 얇게 할 수 있다. 이것이 의해, 산화 실리콘막(52)에 형성되는 관통 홀(53)(도 31 참조)의 어스펙트비를 작게 할 수 있기 때문에, 프로세스 마진이 향상된다.

[0417] 또한, 질화 금속막은 배리어성이 높기 때문에, 다결정 실리콘막으로 구성된 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(66)과의 접촉 계면에 원치않는 반응 생성물이 생길 우려가 없다.

[0418] 또한, 게이트 인출 전극(51a, 51b)의 상부에 관통 홀(74, 75)을 형성하는 공정 (도 49 참조)에서는 TiN막과 WN막의 적층막으로 이루어진 중간 도전층(42, 43)의 표면도 에칭되지만, 게이트 인출 전극(51a, 51b)과 중간 도전층(42, 43)을 함께 금속계 재료로 구성한 경우에는 양자의 에칭 선택비의 차가 적어지기 때문에, 관통 홀(74, 75)의 가공이 용이해진다. 게이트 인출 전극(51a, 51b)은 WN 실리사이드막, Ti 실리사이드막과 같은 금속 실리사이드막으로 구성할 수도 있다.

[0419] 또한, 게이트 인출 전극(51a, 51b)을 상기한 바와 같은 금속계 재료로 구성한 경우에는 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(66)을 구성하는 2층의 다결정 실리콘층(64, 65) 중, 게이트 인출 전극(51a, 51b)과 접하는 제2 다결정 실리콘층(65)을 WN 등의 금속막으로 치환하여도 된다. 이와 같이 하면, 게이트 인출 전극(51a, 51b)과 게이트 전극(66)이 접촉하는 부분은 면적이 작더라도 금속계 재료끼리의 접촉으로 되기 때문에, 양자의 접촉 저항을 작게 할 수 있다. 또, 게이트 전극(66)을 구성하는 제1 다결정 실리콘층(64)과 상기 금속막이 접촉하는 부분은 금속계 재료끼리의 접촉에 비해 단위 면적당의 접촉 저항은 커지지만, 양자의 접촉 면적이 크기 때문에, 전체의 접촉 저항은 작아진다.

[0420] (실시예 9)

[0421] 상기 실시예 1의 메모리 셀은 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)과 하층의 MISFET(DR<sub>1</sub>, DR, TR<sub>1</sub>, TR<sub>2</sub>)을 접속하는 중간 도전층(42, 43)의 표면에 WN막 등으로 이루어진 배리어층(48)을 형성함에 따라, WN막으로 이루어진 중간 도전층(42, 43)과, 그 상부의 관통 홀(53) 내에 형성된 다결정 실리콘막으로 이루어진 플러그(55)와의 계면에서 원하지 않는 실리사이드 반응이 생기는 것을 방지하고 있다.

[0422] 그러나, 배리어층(48)을 WN막으로 구성한 경우에는 다결정 실리콘막으로 이루어진 플러그(55)와 배리어층(48)과의 계면의 접촉 저항이 비교적 높은 것이 문제로 된다. 특히, 플러그(55)가 매립되는 관통 홀(53)은 그 직경이 매우 작은 것이기 때문에, 메모리 셀의 미세화에 따라 상기 접촉 저항이 커져서, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 드레인 전류의 저감을 야기한다.

[0423] 플러그(55)와 배리어층(48)의 계면의 접촉 저항이 커지는 원인은 배리어층(48)을 구성하는 WN막이 열적으로 불안정하기 위해서, 제조 공정 중의 열 처리에서 WN의 일부가 W와 N으로 분해되고, 이 N이 플러그(55)를 구성하는 다결정 실리콘막과 반응함으로써, 플러그(55)와 배리어층(48)과의 계면에 고저항의 질화 실리콘층이 생성되기

때문이라고 생각된다.

[0424] 그 대책으로서, 본 실시예에서는, 도 95에 도시한 바와 같이 플러그(55)와 배리어층(48)과의 사이에, 양자의 반응을 방지하기 위한 반응층(56)을 형성한다.

[0425] 배리어층(48)은 상술한 바와 같이 예를 들면, WN막, Ti막, TiN막 등의 단층막이나, WN막과 W막, TiN막과 W막 등의 적층막으로 구성된다. 한편, 반응층(56)은 예를 들면, Co막, Ti막, W막 등과 같이 플러그(55)를 구성하는 다결정 실리콘막과 반응하여 실리사이드를 형성하는 금속막으로 구성한다. 또한, Co 실리사이드막, Ti 실리사이드막, W 실리사이드막 등과 같은 미리 실리사이드화된 금속막을 이용하여도 된다.

[0426] 상기 반응층(56)을 형성하기 위해서는 상기 실시예 1의 도 27에 도시한 공정에서, 기판(1) 상에 스퍼터링법으로 배리어층 재료(예를 들면, WN막)와 반응층 재료(예를 들면, Co막)를 연속하여 퇴적한 후, 포토레지스트막을 마스크로 한 드라이 에칭으로 배리어층 재료와 반응층 재료를 패터닝하면 된다.

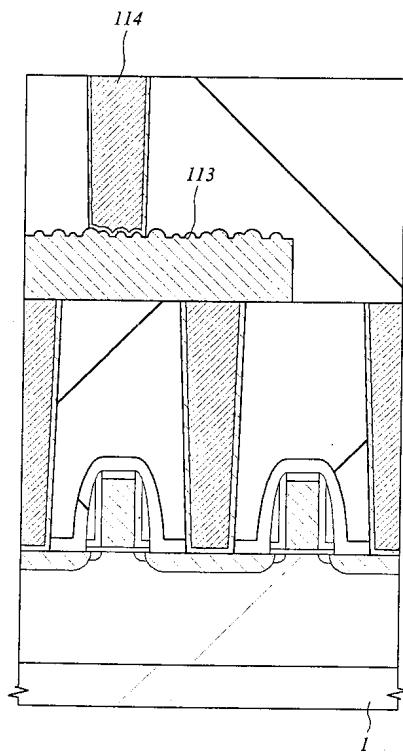

[0427] 또한, 도 96에 도시한 바와 같이 반응층(56)의 표면에 미소한 요철을 형성하고, 반응층(56)과 플러그(55)와의 접촉 면적을 늘림으로써, 양자의 접촉 저항을 보다 저감할 수 있다. 이 요철은 예를 들면, 반응층(56)을 구성하는 재료(Co막 등)를 성막할 때, 막 내의 결정립의 성장 속도를 제어함에 의해 형성할 수 있다.

[0428] 이와 같이, 중간 도전층(42, 43)과 플러그(55)와의 계면에 배리어층(48) 및 반응층(56)을 개재시키는 본 실시예에 따르면, 플러그(55)로부터 중간 도전층(42, 43)으로의 실리콘의 확산을 배리어할 수 있음과 함께, 상기 계면의 접촉 저항의 증대를 억제할 수 있으므로, 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 드레인 전류의 저감을 억제하는 것이 가능해진다.

[0429] 또, 일반적으로 LSI 제조 공정의 열 처리 온도는 반도체 소자의 미세화에 따라 저하하는 경향에 있다. 따라서, SRAM인 경우에도, 제조 공정의 열 처리 온도가 낮아지면, 예를 들면, W 실리사이드막과 같은 금속 실리사이드막의 단층막으로 배리어층(48)과 반응층(56)을 겸용시키거나, 배리어층(48)이나 반응층(56)을 생략하여, 중간 도전층(42, 43)의 표면에 직접 플러그(55)를 접촉시키거나 하는 것도 가능하다.

[0430] 중간 도전층(42, 43)의 표면에 플러그(55)를 직접 접촉시키는 경우에는 예를 들면, 도 97에 도시한 바와 같이 플러그(55)와 동일한 도전형의 다결정 실리콘막(60)을 중간 도전층(42, 43)의 표면 전체에 형성해도 된다. 혹은, 중간 도전층(42, 43)을 W막과 다결정 실리콘막(60)의 적층막으로 구성해도 된다. 이와 같이 한 경우에는 중간 도전층(42, 43)을 구성하는 W막과 다결정 실리콘막(60)이 넓은 면적에서 접촉하기 때문에, 중간 도전층(42, 43)의 표면에 면적이 작은 플러그(55)를 직접 접촉시키는 경우에 비해, 중간 도전층(42, 43)과 플러그(55)의 접촉 저항을 낮게 할 수 있다.

[0431] (실시예 10)

[0432] 상기 실시예 1의 메모리 셀은 종형 MISFET(SV<sub>1</sub>, SV<sub>2</sub>)의 게이트 전극(66)을 2층의 다결정 실리콘막(제1 다결정 실리콘층(64) 및 제2 다결정 실리콘층(65))으로 구성하고 있지만, 메모리 셀 사이즈를 미세화하도록 하면, 이들 2층의 다결정 실리콘막을 얇은 막 두께로 형성할 필요가 있다.

[0433] 그러나, 상기 2층의 다결정 실리콘막을 얇게 하려고 하면, 적층체(P<sub>1</sub>, P<sub>2</sub>)의 측벽에 제1 다결정 실리콘층(64)을 형성한 후, 그 표면에 제2 다결정 실리콘층(65)을 형성하는 공정에 앞서서, 기판(1)의 표면을 세정액으로 웨트 세정할 때, 세정액의 일부가 얇은 제1 다결정 실리콘층(64)의 결정입계를 거쳐 게이트 절연막(63)의 표면에 도달하여, 게이트 절연막(63)의 일부를 용해, 소실시킬 우려가 있다.

[0434] 그 대책으로서, 본 실시예에서는 제1 다결정 실리콘층(64) 대신 비정질 실리콘막을 사용한다. 즉, 본 실시예의 게이트 전극 형성 방법은 적층체(P<sub>1</sub>, P<sub>2</sub>)의 측벽 표면에 산화 실리콘막으로 이루어진 게이트 절연막(63)을 형성(도 39 참조)한 후, 먼저 도 98에 도시한 바와 같이 기판(1) 상에 CVD법으로 비정질 실리콘막을 퇴적하고, 계속해서 이 비정질 실리콘막을 이방적으로 에칭함으로써, 적층체(P<sub>1</sub>, P<sub>2</sub>)의 측벽에 측벽 스페이서형의 비정질 실리콘층(67)을 형성한다.

[0435] 다음으로, 비정질 실리콘층(67)의 표면의 이물을 제거하기 위해서, 기판(1)의 표면을 세정액으로 웨트 세정한다. 비정질 실리콘층(67)은 막 내에 결정립이 실질적으로 존재하지 않기 때문에, 막의 표면은 매우 평坦하다. 따라서, 그 막 두께를 얇게 해도 세정액이 게이트 절연막(63)의 표면에 도달할 일은 없기 때문에, 게이트 절연막(63)의 국소적인 용해, 소실을 방지할 수 있다.

[0436] 다음으로, 도 99에 도시한 바와 같이 비정질 실리콘층(67)의 표면에 상기 실시예 1과 동일한 방법으로 제2 다결정 실리콘층(65)을 형성함으로써, 적층체( $P_1$ ,  $P_2$ )의 측벽에 비정질 실리콘층(67)과 제2 다결정 실리콘막(65)의 적층막으로 이루어진 게이트 전극(66)을 형성한다.

[0437] 다음으로, 기판(1)을 열 처리하여 상기 비정질 실리콘층(67)을 다결정화한다. 또, 비정질 실리콘층(67)은 그 후의 공정에서 행해지는 열 처리에 의해 다결정화되기 때문에, 비정질 실리콘층(67)을 다결정화하기 위한 특별한 열 처리 공정은 생략할 수도 있다.

[0438] 이와 같이, 게이트 전극(66)을 구성하는 2층의 도전막 중, 1층째의 도전막을 비정질 실리콘막으로 구성함으로써, 이들 2층의 도전막의 막 두께를 얇게 할 수 있으므로, 종형 MISFET( $SV_1$ ,  $SV_2$ )의 가로 방향의 면적을 축소하여 메모리 셀 사이즈의 미세화를 추진할 수 있다.

[0439] 또, 전송 MISFET( $TR_1$ ,  $TR_2$ ) 및 구동 MISFET( $DR_1$ ,  $DR_2$ )의 상부에 종형 MISFET( $SV_1$ ,  $SV_2$ )을 배치하는 SRAM에서는 종형 MISFET( $SV_1$ ,  $SV_2$ )을 형성하는 프로세스를 가능한 한 저온화함으로써, 하층의 MISFET( $TR_1$ ,  $TR_2$ ,  $DR_1$ ,  $DR_2$ )의 특성 열화를 억제할 필요가 있다. 따라서, 본 실시예와 같이 종형 MISFET( $SV_1$ ,  $SV_2$ )의 게이트 전극(66)의 일부를 비정질 실리콘층(67)으로 구성한 경우에는 비정질 실리콘층(67)을 다결정화하기 위한 열 처리를 가능한 한 저온으로 행할 필요가 있다.

[0440] 본 실시예에서는, 비정질 실리콘층(67)의 표면에 2층째의 도전막으로서 제2 다결정 실리콘층(65)을 형성하기 때문에, 비정질 실리콘층(67)을 열 처리할 때에 제2 다결정 실리콘층(65)이 종결정(種結晶)으로서 기능한다. 그 때문에, 비정질 실리콘층(67)을 다결정화할 때의 열 처리 온도를 낮게 하여도, 비정질 실리콘층(67)이 빠르게 다결정화된다. 즉, 본 실시예에 따르면, 종형 MISFET( $SV_1$ ,  $SV_2$ )을 형성하는 공정에서 비정질 실리콘막을 사용해도, 그 다결정화를 낮은 온도로 행할 수 있기 때문에, 하층의 MISFET( $TR_1$ ,  $TR_2$ ,  $DR_1$ ,  $DR_2$ )의 특성의 열화를 회피할 수 있다.

[0441] (실시예 11)

[0442] SRAM 메모리 셀 사이즈를 미세화해 가면, 전송 MISFET( $TR_1$ ,  $TR_2$ )의 게이트 전극(7A) 및 구동 MISFET( $DR_1$ ,  $DR_2$ )의 게이트 전극(7B)은 이들 폭(게이트 길이)이 노광광의 과장에 매우 가깝게 된다. 이 경우, 상기 실시예 1과 같이 게이트 전극(7A, 7B)을 1회의 에칭으로 패터닝하면, 도 100에 도시한 바와 같이 게이트 전극(7A, 7B) 각각의 4개의 모서리가 노광광의 간섭에 의해 둑글게 되고, 게이트 전극(7A, 7B)의 단부가 활성 영역(L)의 내측으로 후퇴한 결과, 활성 영역(L)의 주연부에서 게이트 길이가 좁아져서, MISFET( $TR_1$ ,  $TR_2$ ,  $DR_1$ ,  $DR_2$ )의 특성이 열화된다 는 문제가 생긴다.

[0443] 따라서, 미리 게이트 전극(7A, 7B)의 단부를 활성 영역(L)으로부터 멀리 떨어뜨리여 놓으면, 이들 4개의 모서리가 둑글어져도 활성 영역(L)의 주연부에서 게이트 길이가 좁아질 일은 없기 때문에, 상기한 문제를 회피할 수 있다. 그러나, 이 경우에는 도 100의 X 방향을 따라 인접하는 2개의 게이트 전극(7A, 7B)의 거리가 접근하는 것을 방지하기 위해서, 2개의 활성 영역(L)의 스페이스를 넓게 하지 않으면 안되기 때문에, 메모리 셀 사이즈를 미세화할 수 없게 된다.

[0444] 그 대책으로서, 본 실시예에서는, 다음과 같은 방법으로 게이트 전극(7A, 7B)을 형성한다. 먼저, 도 101에 도시한 바와 같이 게이트 전극 재료( $n$ 형 다결정 실리콘막( $7n$ ))를 덮는 캡 절연막(산화 실리콘막(8))의 상부에 제1 포토레지스트막(16a)를 형성하고, 이 포토레지스트막(16a)을 마스크로 한 드라이 에칭으로 산화 실리콘막(8)을 패터닝한다. 이 때, 산화 실리콘막(8)은 도 102에 도시한 바와 같이 그 평면 패턴이 X 방향을 따라 띠 형상으로 연장되도록 패터닝된다.

[0445] 다음으로, 포토레지스트막(16a)을 제거한 후, 도 103에 도시한 바와 같이 제2 포토레지스트막(16b)을 마스크로 한 드라이 에칭으로 산화 실리콘막(8)을 패터닝한다. 이 때, 산화 실리콘막(8)은 도 104에 도시한 바와 같이, 그 평면 패턴이 게이트 전극(7A, 7B)과 동일하게 되도록 패터닝된다. 그 후, 도 105에 도시한 바와 같이 산화 실리콘막(8)을 마스크로 하여  $n$ 형 다결정 실리콘막( $7n$ )을 드라이 에칭함으로써, 게이트 전극(7A, 7B)를 형성한다.

[0446] 상기한 게이트 전극(7A, 7B)의 형성 방법은 게이트 전극(7A, 7B)과 동일한 평면 형상을 갖는 산화 실리콘막(8)을 2개의 포토마스크를 사용한 2회의 에칭으로 형성하기 때문에, 노광광의 간섭 영향이 없어진 결과, 산화 실리

콘막(8)의 4개의 모서리의 둑글어짐이 적어진다. 따라서, 이 산화 실리콘막(8)을 마스크로 한 드라이 에칭에 의해 얻어지는 게이트 전극(7A, 7B)의 4개의 모서리의 둑글어짐도 적어지기 때문에, 이를 단부를 활성 영역(L)으로부터 멀리 떨어뜨리지 않더라도, 활성 영역(L)의 주연부에서 게이트 길이가 좁아질 일은 없다. 또한, 산화 실리콘은 포토레지스트에 비해 다결정 실리콘에 대한 에칭 선택비가 크기 때문에, 포토레지스트막을 마스크로 하여 다결정 실리콘막(7n, 7p)을 에칭하거나, 산화 실리콘막(8)과 다결정 실리콘막(7n, 7p)을 연속하여 에칭하였기도 한 경우에 비해, 게이트 전극(7A, 7B)을 높은 정밀도로 패터닝할 수 있다.

[0447] 이것에 대하여, 1회의 에칭으로 게이트 전극(7A, 7B)을 형성한 경우에는 도 100에 도시한 바와 같이 게이트 전극(7A, 7B)의 4개의 모서리의 둑글어짐이 커진다. 따라서, 이 경우에는 게이트 전극(7A, 7B)의 단부를 활성 영역(L)으로부터 멀리 떨어뜨려 두지 않으면, 이를 단부의 둑글어짐이 활성 영역(L)의 내측에까지 도달하여, MISFET( $TR_1$ ,  $TR_2$ ,  $DR_1$ ,  $DR_2$ )의 특성을 열화시킨다.

[0448] 이와 같이, 상기한 게이트 전극(7A, 7B)의 형성 방법에 따르면, 포토마스크의 매수와 에칭 횟수는 증가하지만, 게이트 전극(7A, 7B)의 단부가 활성 영역(L)의 내측으로 후퇴하는 양을 줄일 수 있다. 이것에 의해, 게이트 전극(7A, 7B)의 단부를 활성 영역(L)의 근방에 배치하는 것이 가능해지므로, 그 만큼 2개의 활성 영역(L)의 스페이스를 좁게 할 수 있어서, 메모리 셀 사이즈를 미세화할 수 있다.

[0449] 또, SRAM의 주변 회로의 일부에는 예를 들면, 전원 회로와 같이 게이트 길이가 비교적 긴 MISFET을 비교적 저밀도로 배치하는 회로가 있다. 이러한 회로의 MISFET은 게이트 전극(7C)의 단부를 활성 영역(L)으로부터 멀리 떨어뜨리더라도 지장이 없기 때문에, 1회의 에칭으로 게이트 전극(7C)을 형성해도 된다. 즉, 상술한 2개의 마스크를 사용한 2회의 에칭 공정 중, 어느 한쪽의 공정에서 게이트 전극(7C)을 형성하면 된다. 한편, SRAM의 주변 회로 중, 게이트 길이가 짧은 MISFET을 포함하는 회로나 MISFET이 고밀도로 배치되는 회로에서는 이를 회로를 구성하는 MISFET의 게이트 전극(7C)을 형성할 때, 2개의 다른 마스크를 사용한 2회의 에칭으로 게이트 전극 재료(다결정 실리콘막)를 패터닝하는 것이 바람직하다.

[0450] 또한, 2개의 포토마스크를 사용한 2회의 에칭으로 게이트 전극(7A, 7B)과 동일한 평면 형상을 갖는 산화 실리콘막(8)을 형성하는 경우에는 제1 포토레지스트막(16a)에 패턴을 전사할 때의 노광 광원에 ArF(불화 아르곤)을 이용하며, 제2 포토레지스트막(16b)에 패턴을 전사할 때의 노광 광원에 KrF(불화 크립톤)를 이용하는 것도 가능하다.

[0451] 즉, 제1 포토레지스트막(16a)을 마스크로 하여 산화 실리콘막(8)을 드라이 에칭할 때는 산화 실리콘막(8)을 게이트 전극(7A, 7B)의 게이트 길이와 동일한 폭으로 가공하기 때문에, 제2 포토레지스트막(16b)을 마스크로 하여 산화 실리콘막(8)을 드라이 에칭할 때에 비해 높은 가공 정밀도가 요구된다. 따라서, 제1 포토레지스트막(16a)에 포토마스크의 패턴을 전사할 때에는 KrF보다도 파장이 짧은 ArF를 노광 광원으로서 이용함에 따라, 산화 실리콘막(8)을 고정밀도로 드라이 에칭할 수 있다. 한편, ArF용의 포토레지스트는 KrF용의 포토레지스트보다도 고가인 것이므로, 제2 포토레지스트막(16b)에 포토마스크의 패턴을 전사할 때의 노광 광원으로서 KrF를 이용하면, 염가인 KrF용 포토레지스트를 사용하여 포토레지스트막(16b)을 구성할 수 있다.

[0452] 또, 도 106에 도시한 바와 같이, 제2 포토레지스트막(16b)에 패턴을 전사하는 포토마스크(M)에 형성되는 차광 패턴(사선으로 나타낸 부분)과 빛 투과 패턴과의 경계부가 활성 영역(L)의 일부(동그라미 표시로 나타낸 부분)와 중첩되면, 에칭 공정으로서 상기 활성 영역(L)의 일부의 기판(1)이 깨일 우려가 있다. 따라서, 예를 들면, 도 107에 도시한 바와 같이 차광 패턴과 빛 투과 패턴과의 경계부는 활성 영역(L)과 중첩되지 않도록 레이아웃하는 것이 바람직하다.

[0453] (실시예 12)

[0454] 상기 실시예 1에서는, 종형 MISFET( $SV_1$ ,  $SV_2$ )과 하층의 MISFET( $DR_1$ ,  $DR$ ,  $TR_1$ ,  $TR_2$ )을 접속하는 관통 홀(53)의 내부에 다결정 실리콘막으로 이루어진 플러그(55)를 형성한다(도 34 참조).