(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4546117号

(P4546117)

(45) 発行日 平成22年9月15日(2010.9.15)

(24) 登録日 平成22年7月9日(2010.7.9)

(51) Int.Cl.

F 1

H01L 21/8247 (2006.01)

H01L 29/788 (2006.01)

H01L 29/792 (2006.01)

H01L 27/115 (2006.01)

H01L 29/78 371

H01L 27/10 434

請求項の数 7 (全 23 頁)

(21) 出願番号 特願2004-66767 (P2004-66767)

(22) 出願日 平成16年3月10日 (2004.3.10)

(65) 公開番号 特開2005-259843 (P2005-259843A)

(43) 公開日 平成17年9月22日 (2005.9.22)

審査請求日 平成19年2月28日 (2007.2.28)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 110000350

ボレール特許業務法人

(74) 代理人 100068504

弁理士 小川 勝男

(74) 代理人 100086656

弁理士 田中 恭助

(72) 発明者 峰 利之

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 横山 夏樹

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

最終頁に続く

(54) 【発明の名称】不揮発性半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ソースサイドインジェクションを用いた電子注入、バンド間トンネリングを用いた正孔注入を行うスプリット構造のメモリセルを備えた不揮発性半導体記憶装置であつて、前記メモリセルは、

- (a) 半導体基板中に形成された第1および第2半導体領域と、

- (b) 前記第1および第2半導体領域間に前記半導体基板の上部に形成された選択ゲートおよび前記選択ゲート形成後に形成されたメモリゲートと、

- (c) 前記選択ゲートと前記半導体基板との間に形成された第1絶縁膜と、

- (d) 前記メモリゲートと前記半導体基板との間に形成された第2絶縁膜と、

- (e) 前記選択ゲートとメモリゲートとの間の前記選択ゲート側壁部に形成された第3絶縁膜とを備え、

前記第2絶縁膜は、前記半導体基板上の第1の電位障壁膜と、その上部に形成されたシリコン窒化膜と、その上部に形成された第2の電位障壁膜から成り、

前記第3絶縁膜は、前記選択ゲート側壁部上の前記第1の電位障壁膜と、その上部に形成された前記第2の電位障壁膜から成り、

前記第1の電位障壁膜と前記第2の電位障壁膜の間に前記シリコン窒化膜が存在せず、

前記選択ゲートの側壁の一面が、その断面において逆テープ形状を有していることを特徴とする不揮発性半導体記憶装置。

## 【請求項 2】

10

20

請求項 1 記載の不揮発性半導体記憶装置において、前記選択ゲートの側壁の一面がメモリゲートに隣接する側の側壁であり、前記選択ゲート側壁の延長線と Si 基板の作る角度が 75° ~ 90° 未満であることを特徴とする不揮発性半導体記憶装置。

**【請求項 3】**

請求項 1 に記載の不揮発性半導体記憶装置において、前記選択ゲートの一方の側壁に形成された第1の電位障壁膜の膜厚が、シリコン基板側に近い部分で薄くなっていることを特徴とする不揮発性半導体記憶装置。

**【請求項 4】**

請求項 1 に記載の不揮発性半導体記憶装置において、前記選択ゲートの上に絶縁膜パターンが形成されており、前記絶縁膜の一方のパターンエッジより前記選択ゲートのパターンエッジが内側に配置されていることを特徴とする不揮発性半導体記憶装置。

10

**【請求項 5】**

請求項 4 に記載の不揮発性半導体記憶装置において、前記選択ゲートの側壁の一面がメモリゲートに隣接する側の側壁であり、前記選択ゲート上に形成された絶縁膜のパターンエッジと前記絶縁膜パターンより内側に配置された選択ゲートのパターンエッジとの長さが、40 nm 以下であることを特徴とする不揮発性半導体記憶装置。

**【請求項 6】**

ソースサイドインジェクションを用いた電子注入、バンド間トンネリングを用いた正孔注入を行うスプリット構造のメモリセルを備えた不揮発性半導体記憶装置であって、前記メモリセルは、

20

- (a) 半導体基板中に形成された第 1 および第 2 半導体領域と、

- (b) 前記第 1 および第 2 半導体領域間上の前記半導体基板の上部に形成された選択ゲートおよび前記選択ゲート形成後に形成されたメモリゲートと、

- (c) 前記選択ゲートと前記半導体基板との間に形成された第 1 絶縁膜と、

- (d) 前記メモリゲートと前記半導体基板との間に形成された第 2 絶縁膜と、

- (e) 前記選択ゲートとメモリゲートとの間の前記選択ゲート側壁部に形成された第 3 絶縁膜とを備え、

前記第 2 絶縁膜は、前記半導体基板上の第 1 の電位障壁膜と、その上部に形成されたシリコン窒化膜と、その上部に形成された第 2 の電位障壁膜から成り、

前記第 3 絶縁膜は、前記選択ゲート側壁部上の前記第 1 の電位障壁膜と、その上部に形成されたシリコン窒化膜と、その上部に形成された前記第 2 の電位障壁膜から成り、

30

前記第 3 絶縁膜の前記シリコン窒化膜の膜厚が、前記第 2 絶縁膜の前記シリコン窒化膜の膜厚よりも薄いことを特徴とする不揮発性半導体記憶装置。

**【請求項 7】**

請求項 6 に記載の不揮発性半導体記憶装置において、前記半導体基板からソースサイドインジェクションにより前記第 2 絶縁膜の前記シリコン窒化膜に電子を注入する書き込み手段と、前記半導体基板からバンド間トンネリングにより前記第 2 絶縁膜の前記シリコン窒化膜に正孔を注入して電子を消去する消去手段とを備えたことを特徴とする不揮発性半導体記憶装置。

**【発明の詳細な説明】**

40

**【技術分野】**

**【0001】**

本発明は、不揮発性半導体記憶装置の構造とその製造方法に係り、特に低電圧、高速プログラミングが可能な高信頼性の不揮発性半導体記憶装置及びその製造方法に関する。

**【背景技術】**

**【0002】**

半導体不揮発性メモリセルを論理用半導体装置と同一のシリコン(Si)基板上に混載することで、高機能の半導体装置を実現することが可能になる。それらは、組み込み型マイクロコンピュータとして、産業用機械、家電品、自動車搭載装置などに広く用いられている。

50

## 【0003】

一般的には混載された不揮発性メモリには、そのマイクロコンピュータが必要とするプログラムを格納し、隨時、読み出して使用する。このような論理用半導体装置との混載に適した不揮発性メモリのセル構造として、選択用MOS型トランジスタと記憶用MOS型トランジスタからなるスプリットゲート構造のメモリセルが挙げられる。

## 【0004】

この構造を採用するとメモリを制御する周辺回路の面積が小さくて済むために、混載用途では主流となっている記憶用（メモリ）MOS型トランジスタの電荷保持方式には、電気的に孤立した導電性の多結晶シリコンに電荷を蓄えるフローティングゲート方式と、Si窒化膜のような電荷を蓄積する性質をもつ絶縁膜に電荷を蓄えるMONOS方式がある。

10

## 【0005】

これら、いずれの電荷保持方式においても、電荷を蓄える領域を絶縁性に優れたSi酸化膜で覆う構成であるが、MONOS方式は絶縁膜に電荷を蓄えるため離散記憶が可能であること、Si酸化膜の欠陥による極端な保持寿命低下がないため信頼性予測が容易なこと、メモリセル構造が単純で論理回路部と混載し易い等の利点がある。更に、Si酸化膜の欠陥による極端な保持寿命低下がないため、Si酸化膜にダメージを与え易いホットホール消去を採用でき、消去時間を飛躍的に短くできることから、近年注目を集めている。なお、ホットホール消去については後で詳述するが、絶縁膜に書き込み情報として蓄えたホットエレクトロンを消去する手段として、メモリセルにホットホールを誘起し、蓄積情報であるエレクトロンを中和して消去する方法である。

20

## 【0006】

特に微細化に適したスプリットゲート構造として、自己整合を利用してメモリMOS型トランジスタをサイドウォールで形成する構造（以下、自己整合スプリットゲート構造という）がある（例えば、特許文献1～3参照）。20

## 【0007】

この自己整合スプリットゲート構造を採用したMONOSメモリは、メモリMOS型トランジスタのゲート長をリソグラフィーの最小解像寸法以下にできるため、動作電流を大きくできる（動作周波数が増加）、メモリセル面積を大幅に微細化できるなどの利点がある。以下、従来のMONOS型メモリセルの構造と動作を、図15を用いて簡単に説明する。

## 【0008】

30

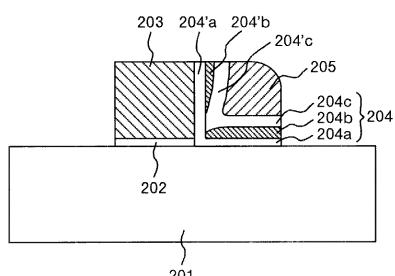

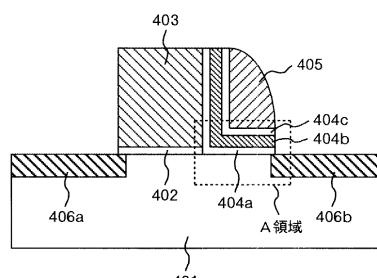

この不揮発性メモリは、記憶部を構成するメモリMOS型トランジスタQ<sub>1</sub>と、そのメモリ部を選択して情報を読み出すための選択MOS型トランジスタQ<sub>2</sub>の、2つのMOS型トランジスタから構成されている。選択MOS型トランジスタQ<sub>2</sub>の拡散層（ソース領域）406aは共通ソース線に、選択ゲート電極403はワード配線に接続されている。一方、メモリMOS型トランジスタQ<sub>1</sub>の拡散層（ドレイン領域）406bはビット線に、メモリゲート電極405はメモリゲート配線に接続されている。

## 【0009】

メモリMOS型トランジスタQ<sub>1</sub>のゲート絶縁膜404は3層膜で構成されており、例えばSi基板401の表面側から、Si酸化膜（第1層膜）404a、Si窒化膜（第2層膜）404bおよびSi酸化膜（第3層膜）404cで構成されている。

40

## 【0010】

ゲート絶縁膜404の膜厚は、第1層膜404aが5～15nm、第2層膜404bが5～15nm、第3層膜404cが5～15nm程度である。

## 【0011】

メモリMOS型トランジスタQ<sub>1</sub>のゲート絶縁膜404は、選択MOS型トランジスタQ<sub>2</sub>のゲート電極403形成後に成膜を行うため、上記選択ゲート電極403の側壁部にも形成される。

## 【0012】

第1層膜のSi酸化膜404aの形成には熱酸化法が用いられている。第2層膜のSi窒化膜404bの形成は、段差被覆性に優れた減圧熱CVD法が用いられており、原料ガス

50

にジクロルシラン( $\text{SiH}_2\text{Cl}_2$ )とアンモニア( $\text{NH}_3$ )を用いた方法が一般的である。第3層膜のSi酸化膜404cの形成は、熱酸化法と減圧熱CVD法の2つに大別されるが、一般的には熱酸化法が主流である。

#### 【0013】

書き込み動作は、選択MOS型トランジスタQ<sub>2</sub>の拡散層(ソース領域)406aおよびそのゲート電極403に所定の電圧を印加して選択MOS型トランジスタQ<sub>2</sub>をオン状態にすると同時に、メモリMOS型トランジスタQ<sub>1</sub>の拡散層(ドレイン領域)406bおよびそのゲート電極405に所定の電圧を印加する。例えば、ソース領域406aに0V、選択MOS型トランジスタQ<sub>2</sub>のゲート電極403に1~2V、ドレイン領域406bに3~5V、メモリMOS型トランジスタQ<sub>1</sub>のゲート電極405に8~10Vの高電圧を印加する。10

#### 【0014】

このような電圧条件下では、選択MOS型トランジスタQ<sub>2</sub>とメモリMOS型トランジスタQ<sub>1</sub>の境界領域に高電界がかかるため、エネルギーの大きいホットエレクトロンがSi基板401中で発生する。このホットエレクトロンの一部は、高電圧に印加されたメモリゲート電極405側へ注入される。この際、ホットエレクトロンの大部分はメモリMOS型トランジスタQ<sub>1</sub>のゲート絶縁膜の一部であるSi窒化膜404bに捕獲される。一般には、このような電子注入法をソースサイド・ホットエレクトロン注入、もしくはソースサイドインジェクションと呼んでいる。20

#### 【0015】

消去動作は、メモリMOS型トランジスタQ<sub>1</sub>のメモリゲート電極405に負バイアス、その拡散層406b(ドレイン領域)に正バイアスを印加し、バンド間トンネリング(BTB T)を用いてホットホールを発生させ、そのホットホールをSi窒化膜404bに注入する方式で行う(ホットホール消去)。例えば、ドレイン領域406bに5~7V、メモリMOS型トランジスタQ<sub>1</sub>のゲート電極405に-9~-11V、ソース領域406aと選択MOS型トランジスタQ<sub>2</sub>のゲート電極403を0Vもしくはオープン状態として消去を行う。20

#### 【0016】

読み出し動作は、選択MOS型トランジスタQ<sub>2</sub>をオン状態にした時、メモリMOS型トランジスタQ<sub>1</sub>のしきい値電圧の状態により、所定の電流が流れるか否かに応じて記憶情報を読み出す。30

#### 【0017】

【特許文献1】特開平11-74389号公報

#### 【0018】

【特許文献2】特開2003-46002号公報

【特許文献3】特開2002-237540号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0019】

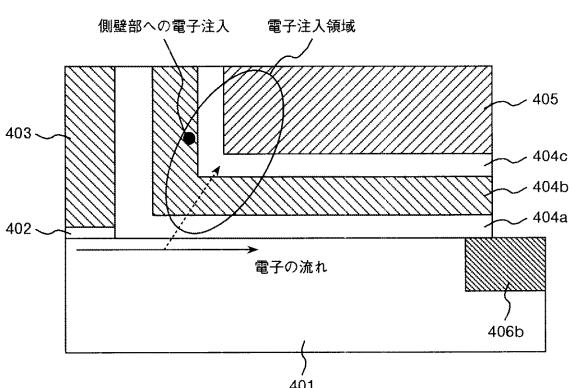

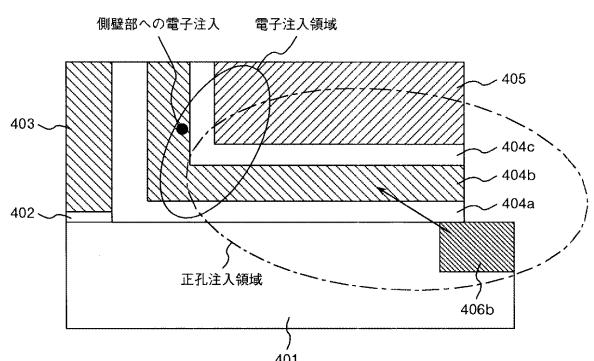

図15に示したスプリットゲート構造のMONOSメモリの課題を、図を用いて説明する。40

図16、図17は、それぞれ図15のA領域を拡大した図である。

#### 【0020】

上記したように、書き込み時にSi基板401中でホットエレクトロンが発生する領域は、選択MOS型トランジスタQ<sub>2</sub>の選択ゲート電極403とメモリMOS型トランジスタQ<sub>1</sub>のメモリゲート電極405を電気的に分離している領域近傍の直下である。その位置から発生したホットエレクトロンの一部は、メモリMOS型トランジスタQ<sub>1</sub>のゲート電界によりゲート電極405エッジ方向へ注入される。この注入されたホットエレクトロンの大部分は捕獲断面積の大きいSi窒化膜404bに捕獲され書き込みが行われる。

#### 【0021】

図16に示したように、上記書き込みではホットエレクトロンが、横方向の拡がりを持つ50

て矢印方向に注入されるので、その一部が選択MOS型トランジスタQ<sub>2</sub>のゲート電極403側壁部分、言い換ればL字型になっているSi窒化膜404bの縦方向領域(Si基板に垂直方向)にも注入される。また、捕獲された電子が作るSi窒化膜404b中の内部電界や約150の高温環境により、捕獲された電子分布は更に拡がると考えられる。

#### 【0022】

一方、消去のためのホットホール注入は、図17に示したようにメモリMOS型トランジスタQ<sub>1</sub>のドレイン406b端から矢印方向に行われる。ドレイン406b端の高電界領域で発生したホットホールは、メモリゲート電極405の電界の影響を受け選択MOS型トランジスタQ<sub>2</sub>側にわずかに拡がりながらSi窒化膜404bへ注入される。

#### 【0023】

ホットホールの横方向注入拡がりは注入条件に依存するが、50nm～80nmと考えられる。図17に示したように、正孔注入領域内に存在する電子はマイクロ秒オーダーで消去されるが、正孔注入領域以外の電子は、正孔密度が非常に小さいため電子の消し残り現象が発生する。電子の消し残り量は、書き換え回数を増す毎に蓄積されるため、最終的には消去を行っても所定のしきい電圧にならない不良を招く。

#### 【0024】

電子の消し残りを防止するには、メモリMOS型トランジスタQ<sub>1</sub>のゲート長(L<sub>mg</sub>)を更に短くするか、消去時間を非常に長くするかの何れかが必要である。しかし、L<sub>mg</sub>を小さくするとパンチスルーアンプが起こるため、L<sub>mg</sub>は60nm程度が下限である。

#### 【0025】

一方、ホットホール注入時間を長くすると、以下の弊害が顕在化してくる。(1)供給電流を確保するためのチャージポンプ電源回路面積が増大する。(2)ボトムゲート酸化膜404aが劣化し電荷保持時間が減少する。(3)ドレイン406b近傍のSi窒化膜404bに正孔が蓄積し、ホットホール発生効率が低下する。

#### 【0026】

したがって、本発明の目的は、メモリMOS型トランジスタQ<sub>1</sub>が選択MOS型トランジスタQ<sub>2</sub>のゲート電極側壁部に自己整合的に形成されたスプリットゲート構造のMONOS不揮発性メモリの特性向上することにある。特に、消し残り電子を少なくして、書き換え耐性を向上させることにある。また、消去時間を短縮させることで消去電流を低減し、電源回路面積を縮小させることにある。また、消去時間を短縮させることで、ゲート酸化膜404aの劣化を抑制し、電荷保持特性の劣化を防止することにある。

#### 【課題を解決するための手段】

#### 【0027】

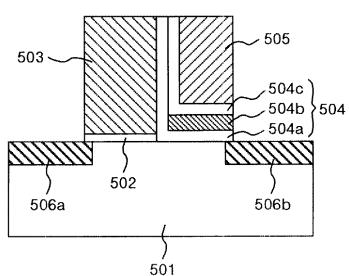

上記目的を達成することのできる本発明の不揮発性半導体記憶装置の概要を図面により説明する。図18、図19及び図20は、本発明を代表する3つの不揮発性半導体記憶装置の要部断面構成例を模式的に示したものである。

#### 【0028】

まず、図18を用いて第1の構造例について説明する。

すなわち、本発明の第1の構造例による不揮発性半導体記憶装置の特徴は、

(a) 半導体基板501中に形成された第1半導体領域(ソース)506aおよび第2半導体領域(ドレイン)506bと、

(b) 前記第1半導体領域506aおよび第2半導体領域506b間上の前記半導体基板501の上部に形成された第1導電体(選択ゲートSG)503および第2導電体(メモリゲートMG)505と、

(c) 前記第1導電体503と前記半導体基板501との間に形成された第1絶縁膜502と、

(d) 前記第2導電体505と前記半導体基板501との間に形成された3層の第2絶縁膜(Si酸化膜504a/Si窒化膜504b/Si酸化膜504c)504と、

(e) 前記第1導電体503と前記第2導電体との間に形成された2層の第2絶縁膜(Si酸化膜504a/Si酸化膜504c)504を有し、

10

20

30

40

50

(f) 前記第2導電体505と前記半導體基板501との間に形成された3層の第2絶縁膜504は、前記半導體基板501上の電位障壁膜(Si酸化膜)504aと、その上部のSi窒化膜504bと、その上部の電位障壁膜(Si酸化膜)504cよりなり、

(g) 前記第1導電体(SG)503と前記第2導電体(MG)505との間に形成された2層の第2絶縁膜504は、電位障壁膜(Si酸化膜)504aと、その上部の電位障壁膜(Si酸化膜)504cとからなる構造としたことである。

#### 【0029】

つまり、この発明の特徴は、第1導電体(SG)503と第2導電体(MG)505との間に形成される第2絶縁膜504の構造を、電位障壁膜(Si酸化膜)504a及び504cの2層構造としたことにある。 10

#### 【0030】

従来であれば、この領域の第2絶縁膜504は、2層の電位障壁膜(Si酸化膜)504a、504cの間に電荷保持膜(Si窒化膜)504bの一部を挟持した3層構造であるが、本発明では上記のように、この領域には電荷保持膜(Si窒化膜)504bを形成せず、電位障壁膜(Si酸化膜)504a及び504cの2層構造としたものである。 20

#### 【0031】

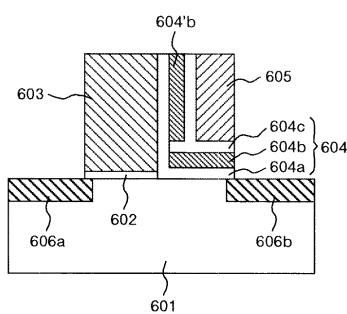

次に、図19を用いて第2の構造例について説明する。

すなわち、本発明の第2の構造例による不揮発性半導體記憶装置の特徴は、

(a) 半導體基板601中に形成された第1半導體領域(ソース)606aおよび第2半導體領域(ドレイン)606bと、 20

(b) 前記第1半導體領域606aおよび第2半導體領域606b間上の前記半導體基板601の上部に形成された第1導電体(選択ゲートSG)603および第2導電体(メモリゲートMG)605と、

(c) 前記第1導電体603と前記半導體基板601との間に形成された第1絶縁膜602と、

(d) 前記第2導電体605と前記半導體基板601との間、及び前記第1導電体(SG)603と前記第2導電体(MG)605との間に形成された3層の第2絶縁膜(Si酸化膜604a/Si窒化膜604b及び604'b/Si酸化膜604c)604を有し、

前記第2導電体605と前記半導體基板601との間の前記第2絶縁膜604は、電位障壁膜(Si酸化膜)604aと、その上部のSi窒化膜(電荷保持膜)604bと、その上部の電位障壁膜(Si酸化膜)604cとよりなり、 30

前記第1導電体(SG)603の側壁部に位置するSi窒化膜604'bのSi基板601に近い側の少なくとも一部が、上記Si窒化膜604bの上部に位置する電位障壁膜(Si酸化膜)604cによって切断されている構造としたことにある。

#### 【0032】

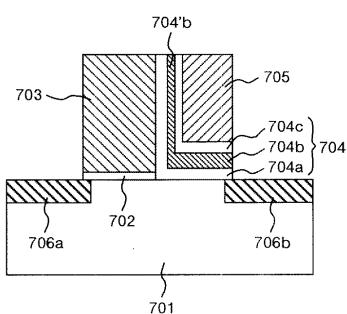

次に、図20を用いて第3の構造例について説明する。

すなわち、本発明の第3の構造例による不揮発性半導體記憶装置の特徴は、

(a) 半導體基板701中に形成された第1半導體領域(ソース)706aおよび第2半導體領域(ドレイン)706bと、

(b) 前記第1半導體領域706aおよび第2半導體領域706b間上の前記半導體基板701の上部に形成された第1導電体(選択ゲートSG)703および第2導電体(メモリゲートMG)705と、 40

(c) 前記第1導電体703と前記半導體基板701との間に形成された第1絶縁膜702と、

(d) 前記第2導電体705と前記半導體基板701との間、及び前記第1導電体(SG)703と前記第2導電体(MG)705との間に形成された3層の第2絶縁膜(Si酸化膜704a/Si窒化膜704b及び704'b/Si酸化膜704c)704を有し、

前記第2導電体705と前記半導體基板701との間の前記第2絶縁膜704は、電位障壁膜(Si酸化膜)704aと、その上部のSi窒化膜(電荷保持膜)704bと、その上部の電位障壁膜(Si酸化膜)704cとからなり、 50

前記第1導電体(SG)703と前記第2導電体(MG)705との間に位置するSi窒化膜704'bの膜厚が、前記第2導電体705と前記半導体基板701との間に位置するSi窒化膜704の膜厚に比べ薄い構造としたことにある。

#### 【0033】

つまり、選択MOS型トランジスタQ<sub>2</sub>のゲート電極側壁部のSi窒化膜に注入、あるいは拡散した電子は、他の領域の電子に比べ最も電子の消し残りが発生し易い。

#### 【0034】

そこで、この第3の構造例では、選択MOS型トランジスタQ<sub>2</sub>のゲート電極側壁部のSi窒化膜に注入、あるいは拡散する電子量を、他の領域、特に第2導電体(メモリゲートMG)と半導体基板との間の第2絶縁膜の一部を構成するSi窒化膜(電荷保持膜)よりも小さくする点にある。10

#### 【0035】

以上、3つの代表的構造例を基に本発明を概説したが、本発明の要点は、第1の構造例(図18)で説明したように、選択ゲート電極側壁部のSi窒化膜を全て削除する、もしくは第2の構造例(図19)で説明したように、選択ゲート電極側壁部のSi窒化膜の一部分を削除する、もしくは、第3の構造例(図20)で説明したように、選択ゲート電極側壁部のSi窒化膜の膜厚を他の領域(メモリゲートMGと半導体基板との間)の膜厚よりも薄くして消し残り電子の影響を小さくする点にある。

#### 【発明の効果】

#### 【0036】

本発明によれば、ホットホール消去による電子の消し残りが飛躍的に減少し書き換え耐性を向上させることができる。20

#### 【0037】

また、本発明によればホットホールによる消去時間が大幅に短縮されるので、消去にかかる消去電流を小さくすることが可能になる。これにより、電源回路の面積が小さくなり製造コストが低減される。

#### 【0038】

また、本発明によれば、消去時間が大幅に短縮されるので、消去に伴う下層電位障壁膜(ボトムSi酸化膜)の劣化を抑制することができる。これにより電荷保持特性が向上する。30

#### 【0039】

以上の効果を合わせて、本発明によれば、書き換え耐性、及び電荷保持特性に優れた、スプリットゲート構造のMONOS型不揮発メモリを低成本で実現できる。

#### 【発明を実施するための最良の形態】

#### 【0040】

以下、本発明の実施例の詳細を、図を用いて説明する。

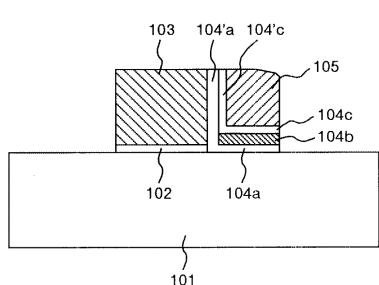

まず、本発明の中で共通なメモリアレーの構成を図7に示す。各メモリセルは溝型素子分離領域(STI)11で分離されており、ソース線14を共通として、MONOS型不揮発メモリの選択ゲート電極となるワード線12、及びメモリMOS型トランジスタのゲート配線13を平行に配置し、上記ゲート配線12、13を挟んでソース領域14と対称の位置にドレイン15を形成している。図中の16は、ドレイン15とビット線17を接続するための開口部である。ビット線17は、不図示の層間絶縁膜を介してワード線12と直交するように配置されている。40

#### 【実施例】

#### 【0041】

以下、上記図18で説明した第1の構造例を実施例1～2により、図19で説明した第2の構造例を実施例3により、そして図20で説明した第3の構造例を実施例4により、それぞれ図面にしたがって具体的に説明する。

#### 【0042】

<実施例1>

10

20

30

40

50

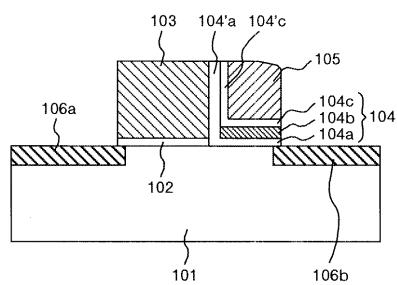

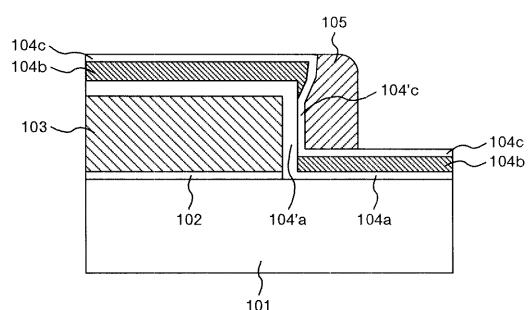

図1は、本発明の第1の実施例の断面図であり、図7に示したX-Y断面に相当する。図7にはピット線17を示しているが、図1には図示していない。

#### 【0043】

本実施例で作製したスプリットゲート構造のMONOS型メモリセルは、Si基板(半導体基板)上に設けたp型ウエル領域(Si基板)101、ソース領域106aとなるn型拡散層(n型半導体領域)、ドレイン領域106bとなるn型拡散層を有した2つのMOS型トランジスタQ<sub>1</sub>、Q<sub>2</sub>から構成されている。

#### 【0044】

選択MOS型トランジスタQ<sub>2</sub>は、ゲート絶縁膜102となるSi酸化膜、選択ゲート電極(導電体)103となるn型多結晶シリコン膜(以下、「Si膜」という)から構成されている。

10

#### 【0045】

メモリMOS型トランジスタQ<sub>1</sub>は、p型ウエル領域(Si基板)101との下層電位障壁膜104aとなるSi酸化膜、電荷保持膜104bとなるSi窒化膜、メモリゲート電極105との上層電位障壁膜104cとなるSi酸化膜およびメモリゲート電極105となるn型多結晶Si膜から構成されている。本図に示したように、メモリMOS型トランジスタQ<sub>1</sub>は、選択MOS型トランジスタQ<sub>2</sub>に対し自己整合的に形成されている。なお、図1の104'aは、選択MOS型トランジスタQ<sub>2</sub>の選択ゲート電極側壁部の下層電位障壁膜(Si酸化膜)であり、104'cは、選択ゲート電極側壁部の上層電位障壁膜(Si酸化膜)である。

20

#### 【0046】

次に、本実施例の書き込み、消去、読み出し動作の電圧関係を図8に示す。図8に示した印加電圧の各名称は本実施例では共通にしており、選択MOS型トランジスタQ<sub>2</sub>、及びメモリMOS型トランジスタQ<sub>1</sub>のゲート電極203、および205に印加する電圧を、それぞれV<sub>sg</sub>、V<sub>mg</sub>で示している。また、ドレイン電圧、ソース電圧は、それぞれV<sub>d</sub>、V<sub>s</sub>で示している。なお、V<sub>well</sub>はウエル電圧であり、本実施例ではSi基板101に印加する電圧となる。なお、図8に示した電圧条件の絶対値は一例であり、この数値をもって本発明が限定されるわけではない。

#### 【0047】

以下、図1～図6を用いて本実施例の製造方法の詳細を記述する。

30

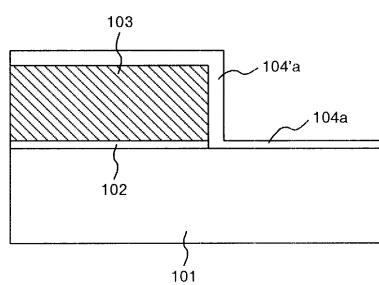

まず、図2の断面工程図に示したように、Si基板101上に、周知の技術を用いて不図示の溝形素子分離領域を形成した。この溝形素子分離領域は、図7に示した符合11に相当する。

#### 【0048】

次に、選択MOS型トランジスタQ<sub>2</sub>のゲート絶縁膜102となる3.5nmのSi酸化膜102を熱酸化法で形成した後、窒素ガスで10%に希釈した一酸化窒素(NO)雰囲気中で900℃、10分のNO酸窒化処理を行った。このNO酸窒化処理によれば、Si基板101界面に窒素が約3%程度導入され選択ゲート絶縁膜102としての信頼性が向上する。本実施例では選択ゲート絶縁膜102の信頼性向上のためにNO酸窒化処理を行ったが、一酸化窒素(NO)の代わりに亜酸化窒素(N<sub>2</sub>O)により酸窒化処理を行ってSi基板101界面に窒素を導入しても同様の効果が得られる。

40

#### 【0049】

次に、化学気相成長法(CVD法)により、選択ゲート電極103となるリンドープ多結晶Si膜103を200nm堆積した後、周知のリソグラフィー、及びドライエッティング法により所定の電極パターン形状に加工した。なお、上記リンドープ多結晶Si膜103のリン濃度は4e20 atms/cm<sup>3</sup>とした。続いて、希フッ酸水溶液により上記多結晶Siパターン103以外のゲート絶縁膜102を除去しSi基板101表面を露出させた後、熱酸化法によりSi基板101表面、及びリンドープ多結晶Si膜パターン103表面に熱酸化膜104a、および104'aを形成した。図2に示したように、リンドープ多結晶Si膜パターン103表面の熱酸化膜104'aの膜厚は、単結晶Si基板101表面の熱

50

酸化膜 104a の膜厚に比べ厚く形成される。この現象は Si 中の不純物（リン）濃度差によるものであるが、この熱酸化膜の膜厚比は、熱酸化雰囲気中の酸素や水分濃度、及び酸化温度で調整することで任意に設定できる。

#### 【 0050 】

本発明では、Si 基板 101 上、及びリンドープ多結晶 Si パターン 103 表面の熱酸化膜の膜厚を、それぞれ 5 nm、及び 13 nm に設定した。Si 基板 101 上に形成された 5 nm の熱酸化膜 104a は、図 1 に示したメモリ MOS 型トランジスタ Q<sub>1</sub> の下層電位障壁膜 104a（以後、ボトム Si 酸化膜と略称）となる。なお、上記 Si 酸化膜 104a、及び 104'a の個々の膜厚は一例であり、この数値をもって本発明が限定されるわけではない。

10

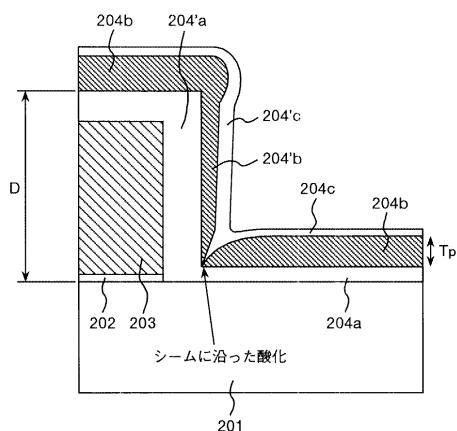

#### 【 0051 】

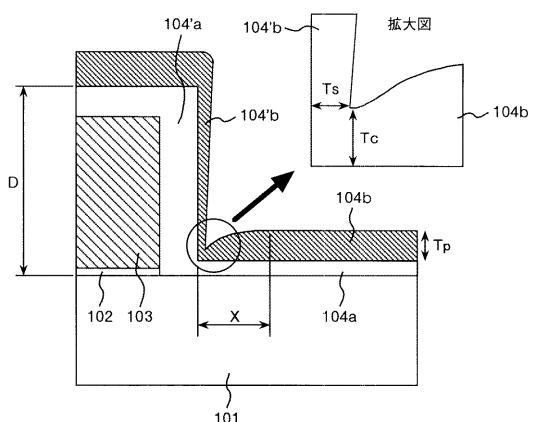

次に、図 1 に示したメモリ MOS 型トランジスタの電荷保持膜 104b となる Si 室化膜 104b の形成方法を図 3 により説明する。本発明では、Si 室化膜 104b の形成に反応性スパッタ法を適用した。図 3 には、矢印方向に示したように、リンドープ多結晶 Si 膜パターン 103 側壁底部近傍の拡大部分図をも示している。周知のように、Si をターゲットとした平行平板型の反応性スパッタ法によれば、窒素と希ガス（アルゴンガス等）の流量比、電極電力を調整することで高品質の Si 室化膜を堆積することが出来る。

#### 【 0052 】

3 図の拡大部分図に示したように、一般に反応性スパッタ法で形成する薄膜は、段差被覆性が非常に悪く、垂直段差側壁部の Si 室化膜 104'b の膜厚；Ts、及び段差側壁底部の膜厚；Tc は、段差部から十分離れた平坦部の膜厚；Tp に比べ薄くなる。パターン段差底部の Si 室化膜の膜厚は、パターン段差エッジ部からの距離に依存し、図に示したようにパターン段差エッジ部が最も近い薄い膜厚；Tc となり、パターン段差エッジから距離；X 以上離れた領域で Tp となる。

20

#### 【 0053 】

ここで、段差被覆性 Rsp と Rcp を、それぞれ  $Rsp = Ts/Tp$ 、 $Rcp = Tc/Tp$  と定義すれば、Rs<sub>p</sub>、Rcp、及び X は、スパッタ条件とパターン段差の高さ（図中の D に対応）に依存する（但し、 $0 < Rsp < 1$ 、 $0 < Rcp < 1$ ）。

#### 【 0054 】

反応性スパッタ法で Si 室化膜を成膜する場合、例えば、イオンの垂直成分の方向性を重視したロングスロースパッタ法（ターゲットと Si 基板の距離を長くしてイオンの方向性を揃える）、コリメーションスパッタ法（コリメータを用いてイオンの方向性を揃える）、2 周波励起スパッタ法（Si 基板側に低周波電圧を印加してイオンの方向性を揃える）等では、Rsp、X は小さくなり、Rcp は大きくなる。一方、スパッタ条件が同じであれば、パターン段差；D が大きいほど Rsp、Rcp は小さくなり、X は大きくなる。すなわち、スパッタ方法、スパッタ条件、パターン段差；D を調整することで、上記 Rsp、Rcp、及び X を任意の大きさにすることができる。

30

#### 【 0055 】

本実施例では、Si 室化膜 104b の形成にアスペクト比の大きいコリメータを用いたコリメーションスパッタ法を適用し、平坦部の Si 室化膜 104b の膜厚；Tp が 12 nm となるように設定した。この時、リンドープ多結晶 Si パターン 103 側壁エッジ部の Si 室化膜 104'b の膜厚；Ts、及び Tc は、それぞれ約 2.2 nm、約 6 nm、であり、X は約 20 nm であった。なお、この Ts、Tc、Tp、および X の絶対値は一例であり、この数値をもって本発明が限定されるわけではない。また、本実施例では、Si 室化膜の形成にコリメーションスパッタ法を用いたが、上述した他のスパッタ法、及び電子サイクロotron 共鳴スパッタ法（ECR スパッタ法）等を用いることも無論可能である。

40

#### 【 0056 】

続いて、図 4 に示したように、950 °C の ISSG 酸化（In-Situ Steam Generation）法を用いて、上記 Si 室化膜 104b を酸化して、約 6 nm の上層電位障壁膜（以後、トップ Si 酸化膜と略称）となる Si 酸化膜 104c を形成した後、減圧 CVD 法により、リンを 5

50

e 2 0 atms/cm<sup>3</sup>含んだ厚さ 6 0 nm のリンドープ多結晶 Si 膜 1 0 5 を堆積した。

#### 【 0 0 5 7 】

上記ISSG酸化法で Si 窒化膜 1 0 4 b 上に約 6 nm のトップ Si 酸化膜を形成した場合、 Si 窒化膜 1 0 4 は堆積膜厚から約 3 nm ~ 3 . 5 nm 薄くなる。つまり、トップ Si 酸化膜を形成する過程で、リンドープ多結晶 Si パターン 1 0 3 側壁部の熱酸化膜 1 0 4 'a 上の Si 窒化膜 1 0 4 'b は全て酸化され、厚さ約 4 . 5 nm の Si 酸化膜 1 0 4 'c に変換される。すなわち、本発明によれば、電荷保持膜となる Si 窒化膜 1 0 4 b は、リンドープ多結晶 Si パターン 1 0 3 側壁部には存在しない構造となる。

#### 【 0 0 5 8 】

本実施例では、トップ Si 酸化膜 1 0 4 c の形成にISSG酸化法を用いたが、通常のウエット酸化法を適用することも可能である。また、プラズマ酸化やオゾン酸化を用いることも勿論可能である。更に、上記酸化を実施した後、CVD法によりトップ Si 酸化膜を追加する方法も可能である。但し、ISSG酸化、プラズマ酸化、及びオゾン酸化はラジカル成分による酸化が主体であるため、酸化量を増やしても選択ゲート電極 1 0 3 側壁部分が極端に酸化される形状にはならない。しかし、通常のウエット酸化は水による酸化が主体であるため、酸化量を増やすと選択ゲート電極 1 0 3 側壁部が大幅に酸化される可能性があり、酸化の際には十分注意が必要である。

10

#### 【 0 0 5 9 】

上述した Si 窒化膜 1 0 4 b の酸化に伴う、選択ゲート電極 1 0 3 側壁部の酸化を抑制するには、メモリMOS型トランジスタのボトム Si 酸化膜 1 0 4 a 形成後にNO酸窒化処理、もしくはN<sub>2</sub>O酸窒化処理を行う方法が有効である。これらの処理を行えば、ボトム Si 酸化膜 1 0 4 a の信頼性を向上できると同時に、選択ゲート電極 1 0 3 側壁部の酸化を抑制できる。無論、Si 窒化膜 1 0 4 b の酸化方法にかかわらず酸窒化処理を予め行うことでのボトム Si 酸化膜の信頼性は向上する。

20

#### 【 0 0 6 0 】

次に、図 5 に示したように、異方性ドライエッティングによりリンドープ多結晶 Si 膜 1 0 5 を選択的にエッティングして、パターン段差側壁部に多結晶 Si 膜 1 0 5 のサイドスペーサ電極 1 0 5 を形成する。半導体基板上におけるこのサイドスペーサ電極 1 0 5 の幅は、図 4 で形成した多結晶 Si 膜 1 0 5 の堆積膜厚で決まり、メモリMOS型トランジスタ Q<sub>1</sub> のゲート長となる。本実施例では、メモリMOS型トランジスタのゲート長を 6 0 nm とした。

30

#### 【 0 0 6 1 】

次に、図 5 の異方性ドライエッティングにより露出したトップ Si 酸化膜 1 0 4 c 、 Si 窒化膜 1 0 4 b 、及びボトム Si 酸化膜 1 0 4 a を順次エッティングして、図 6 に示したように、選択ゲート電極 1 0 3 となる多結晶 Si 膜 1 0 3 表面、及び Si 基板 1 0 1 表面を露出させた。続いて、所定のレジストパターンを形成して、エッティングにより、もう一方の領域の、リンドープ多結晶 Si 膜 1 0 3 及び Si 酸化膜 1 0 2 のパターンニングを行い、選択MOS型トランジスタ Q<sub>2</sub> のゲート長を規定する。

#### 【 0 0 6 2 】

次に、図 1 に示したように、イオン注入法でリンを 1e15 atms/cm<sup>2</sup> の密度で Si 基板に注入した後、950 、 60 秒の熱処理を行いソース 1 0 6 a 、ドレイン 1 0 6 b を形成する。

40

#### 【 0 0 6 3 】

この後、選択MOS型トランジスタ Q<sub>2</sub> 、及びメモリMOS型トランジスタ Q<sub>1</sub> のゲート電極 1 0 3 及び 1 0 5 側壁部へ Si 酸化膜のサイドスペーサの形成、上記両電極 1 0 3 及び 1 0 5 表面、ソース領域 1 0 6 a 表面、及びドレイン領域 1 0 6 b 表面のCoシリサイド化、及びビット線、引き出し配線の形成など一連の周知の工程を経て、図 7 に示したメモリアレイアウトの不揮発性半導体記憶装置を作成し本発明の実施例を完了する。

#### 【 0 0 6 4 】

本実施例で作製したスプリットゲート構造のMONOS不揮発メモリの電気的特性を、図 8

50

に示した電圧条件で測定し従来構造と比較した。その結果、読み出し電流、書き込み時間は従来メモリと同等の値を示したが、消去時間が約30%短縮した。

これにより、ホットホール消去電流を約30%低減できた。また、繰り返し書き込み/消去特性においては電子の消し残りが観測されず、1e5回以上の書き換え耐性が得られた。更に、1e4回の書き込み/消去動作後に150の放置リテンション特性（しきい電圧の変動量で定義では）を評価した結果、従来構造に比べ約2桁の改善があった。

#### 【0065】

##### <実施例2>

次に、図21～図26を用いて本発明の第2の実施例を説明する。この実施例では、実施例1と同様に、選択ゲート電極側底部に電荷保持膜であるSi窒化膜を形成しない、他の3つの方法について検討した。その結果について以下に順次説明する。

10

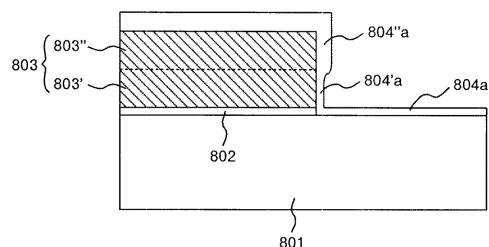

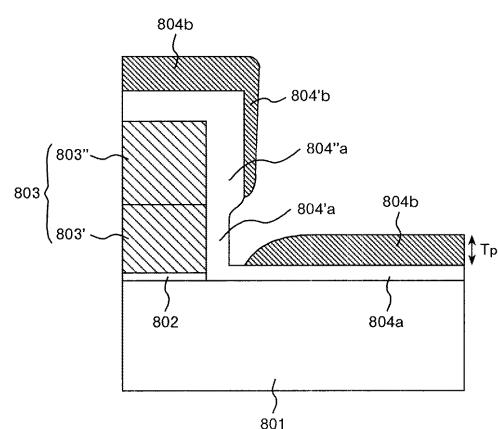

##### (1) 第1の方法について：

図21と図22とを用いて説明する。先ず、図21の断面図に示したように、実施例1と同様にSi基板801上に選択MOS型トランジスタQ<sub>2</sub>のゲート絶縁膜802を形成した後、ノンドープ多結晶Si膜803を200nm堆積した。

#### 【0066】

次に、選択ゲート電極803となる多結晶Si膜803の表面から約100nmの領域803'に、イオンインプラ法により8e15atms/cm<sup>2</sup>のリンを注入した。次に、上記多結晶Si膜803を所定の選択ゲート電極の形状にエッチング加工した後、ウエット酸化法によりSi基板801上に5nmのSi酸化膜804aを形成した。このウエット酸化で上記多結晶Si膜803のノンドープ領域803'表面には膜厚約6nmのSi酸化膜804'aが形成された。一方、リンを高濃度に含んだ領域803''には、不純物が高濃度含まれているため、Si酸化膜804'aよりも厚い膜厚約20nmのSi酸化膜804''aが形成された。図21は、その断面形状を示している。

20

#### 【0067】

続いて、図22の断面図に示すように、2周波励起反応性スパッタ法で、平坦部；Tp膜厚が10nmとなるSi窒化膜804bを堆積した。同スパッタの電極側印加周波数は13.56MHz、基板側周波数は400kHz、基板温度は200とした。図22は堆積直後のパターン形状を示す。本実施例においては、多結晶Siパターン803側壁部の形状が、パターン下部に比べパターン上部側壁部のSi酸化膜厚804''aの方が厚くなっているため、Si窒化膜804b堆積前の断面形状はオーバーハング形状となる。

30

#### 【0068】

本実施例で適用した2周波励起スパッタ法は、実施例1で示したコリメーションスパッタ法に比べ段差被覆性が若干向上するため、多結晶Siパターン803側壁部の上部には約3nmのSi窒化膜804'bが形成された。しかし、本実施例においては、多結晶Siパターン803側壁部の形状が、オーバーハング形状となっているため、Si窒化膜804bは側壁段差底部には形成されなかった（図22）。

#### 【0069】

続いて、トップSi酸化膜804cを形成した。ここでは、図23に示したように、トップSi酸化膜804cを減圧CVD法で形成した場合、及び図24に示したように、ISSG酸化を行った後、減圧CVD法でSi酸化膜を堆積した場合の、2つの試料を作製した。この後、実施例1と同様の製法を用いてスプリットゲート構造のMONOSメモリ（図1参照）を作製した。

40

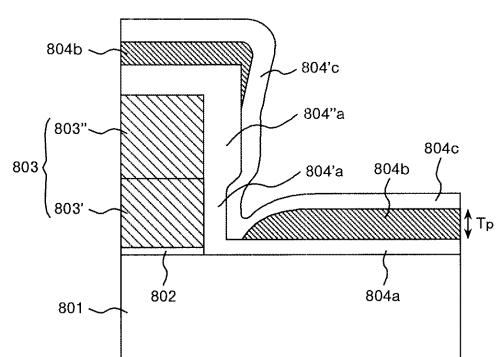

##### (2) 第2の方法について：

次に、図25を用いて第2の方法の説明を行う。上記第1の方法と同様に、Si基板901上に選択MOS型トランジスタQ<sub>2</sub>のゲート酸化膜902を形成した後、リンを5e20atms/cm<sup>3</sup>含んだ150nmの多結晶Si膜903を堆積した。

#### 【0070】

続いて、減圧CVD法により、厚さ50nmのSi酸化膜907を堆積した後、周知の技術を用いて、上記Si酸化膜907、及び多結晶Si膜903を所定の選択ゲート電極の

50

形状に加工した。多結晶 Si 膜 903 をパターンニングした後、等方性ドライエッティング法により上記多結晶 Si 膜 903 を Si 酸化膜 907 パターンエッジから後退させた。この多結晶 Si 膜 903 の後退量；Z は、ドライエッティング時間により任意に設定できる。本実施例では、後退量；Z を 30 nm としたが、Z を大きくしすぎると電荷保持膜となる Si 窒化膜 904b に電子が注入できなくなるため、後退量 Z は 40 nm 以下にすることが好ましい。

#### 【0071】

続いて、上記第 1 の方法と同じ方法でボトム Si 酸化膜 904a 及び Si 窒化膜 904b を形成した。本方法によれば、選択ゲート電極 903 上部に形成した Si 酸化膜パターン 907 がオーバーハング形状となるため、図 25 に示したように、選択ゲート電極 903 側壁部には Si 窒化膜 904 が形成されない構造となる。

#### 【0072】

本実施例では、多結晶 Si 膜 903 の後退量；Z を 30 nm としたが、この絶対値は一例であり、この数値をもって本発明が限定されるわけではない。この後、実施例 1 と同様の製法を用いてスプリットゲート構造のMONOSメモリ（図 1 参照）を作製した。

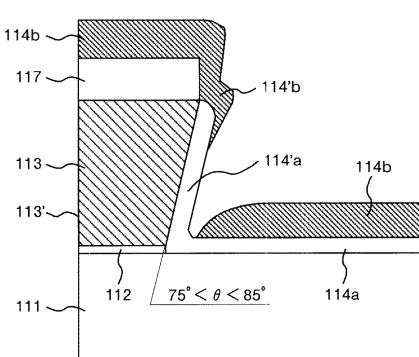

（3）第 3 の方法について：

次に、図 26 を用いて第 3 の方法の説明を行う。上記第 1 の方法と同様に、Si 基板 111 上に選択MOS型トランジスタ Q<sub>2</sub> のゲート酸化膜 112 を形成した後、リンを 5e20 atms/cm<sup>3</sup> 含んだ 150 nm の多結晶 Si 膜 113 を堆積した。続いて、減圧CVD法により、厚さ 50 nm の Si 酸化膜 117 を堆積した後、周知の技術を用いて、上記 Si 酸化膜 117 を所定の形状に加工し、下地の多結晶 Si 膜 113 を露出させた。

#### 【0073】

続いて、ドライエッティングの条件を最適化して、多結晶 Si 膜 113 を逆テーオ形状に加工した。この多結晶 Si 膜 113 の逆テーオ角度；θ は、ドライエッティング条件により任意に設定できる。本実施例では、逆テーオ角度；θ を 80° としたが、逆テーオ角度を小さくすると加工バラツキが増える。従って、上記逆テーオの角度；θ は、75° 以上 90° 以下にすることが好ましい。

#### 【0074】

続いて、上記第 1 の方法と同じ方法でボトム Si 酸化膜 114a 及び Si 窒化膜 114b を形成した。本方法によれば、選択ゲート電極 113 をオーバーハング形状にしているため、図 26 に示したように、選択ゲート電極 113 側壁部には Si 窒化膜 114 が形成されない構造となる。この後、実施例 1 と同様の製法を用いてスプリットゲート構造のMONOSメモリ（図 1 参照）を作製した。

#### 【0075】

以上、本実施例で示した 3 つの方法で作製したスプリットゲート構造のMONOS不揮発メモリの電気的特性を、図 8 に示した電圧条件で測定し従来構造と比較した。その結果、読み出し電流、書き込み時間は従来メモリと同等の値を示したが、消去時間が約 30 % 短縮した。

これにより、ホットホール消去電流を約 30 % 低減できた。

#### 【0076】

また、繰り返し書き込み/消去特性においては電子の消し残りが観測されず、第 1 の実施例と同様に 1e6 回以上の書き換え耐性が得られた。更に、1e4 回の書き込み/消去動作後に 150 の放置リテンション特性（しきい電圧の変動量で定義では）を評価した結果、従来構造に比べ約 2 枠の改善があった。

#### 【0077】

< 実施例 3 >

次に、本発明の第 3 の実施例を説明する。この実施例は先に図 19 で概説した第 2 の構造例に該当するものであり、図 9 ~ 図 13 の断面工程図にしたがって説明する。本実施例でも、メモリアレーの構成（図 7 参照）、及び各電圧の設定（図 8 参照）は実施例 1 と同様である。

10

20

30

40

50

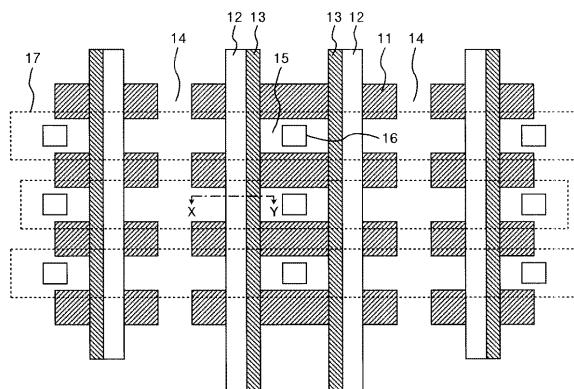

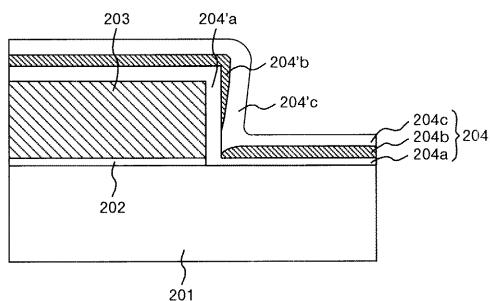

## 【0078】

図9に示したように、まず、実施例1と同様の方法で、p型ウエル領域201(Si基板)上に選択MOS型トランジスタQ<sub>2</sub>のゲート絶縁膜202の形成、選択ゲート電極203となるリンドープ多結晶Si膜203のパターン形成、及びメモリMOS型トランジスタQ<sub>1</sub>のボトムSi酸化膜204aを形成した。続いて、電荷保持膜となるSi窒化膜204bをプラズマCVD法で形成した。

## 【0079】

周知のように、SiH<sub>2</sub>Cl<sub>2</sub>とNH<sub>3</sub>を原料ガスとする熱CVD法で形成するSi窒化膜は、ほぼ100%の段差被覆性を示すが、プラズマCVD法は熱CVD法に比べ大幅に段差被覆性が劣化する。例えば、SiH<sub>4</sub>(モノシラン)とNH<sub>3</sub>、及びN<sub>2</sub>を原料ガスとするプラズマCVD法で形成したSi窒化膜は、図9に示したように、パターンの上部段差部でオーバーハング形状になり、段差側壁部204'bの膜厚は、段差の上部から底面に向かって堆積膜厚が減少する。10

## 【0080】

特に、パターン側壁底部(パターン下部のエッジ領域、矢印でシームと表示)は、堆積条件によっては平坦部の膜厚にくらべ約40%程度の膜厚まで減少する。本実施例で示すプラズマCVDで形成したSi窒化膜の堆積形状は、実施例1で示した反応性プラズマスパッタ法で形成したSi窒化膜の形状と酷似している。但し、段差被覆性を比較した場合、反応性プラズマスパッタ法が20%~30%に対し、プラズマCVD法は40%~60%であり、プラズマCVD法の方が優れている。20

## 【0081】

プラズマCVD法では、段差側壁部のSi窒化膜204'bは、プラズマイオン照射が起こり難いために十分なエネルギーが与えられず、平坦部のSi窒化膜に比べ密度やSi-N結合エネルギーが小さい膜になる。このため、平坦部のSi窒化膜204bに比べ薬品耐性や耐酸化性が小さい膜になることは周知の事実である。

## 【0082】

更に、図9に示したようにパターン側壁底部(シームと表示)は、側壁部から成長したSi窒化膜204'bと平坦部から成長したSi窒化膜204bの境目となるため、シームが発生する。このシームは、先に示した薬品耐性や耐酸化性が最も小さい領域であり、例えば希フッ酸水溶液によるエッチングや酸化によって段差側壁部のSi窒化膜204'bと底面部のSi窒化膜204bを分離することは極めて容易である。30

## 【0083】

本実施例では、上記Si窒化膜204b、204'bの形成に、SiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>を原料ガスとする2周波励起型のプラズマCVD装置を用いた。電極側には13.56MHzの高周波電圧を、Si基板側には380kHzの低周波電圧を印加し、基板温度は430とした。

## 【0084】

本実施例で形成した平坦部のSi窒化膜204bの膜厚は12nm、選択ゲート電極203パターン側壁部の平均膜厚は6nmであり、パターン側壁底部のシーム寄りの最も薄いSi窒化膜204'bの膜厚は約4.8nmであった(図9)。

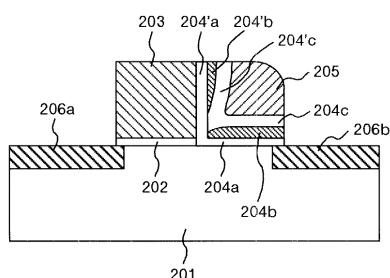

## 【0085】

次に、図10に示したように、実施例1と同様の方法で、上記Si窒化膜204bをISSG酸化してメモリMOS型トランジスタQ<sub>1</sub>のトップSi酸化膜204cを形成した。トップSi酸化膜204cの膜厚は、パターン側壁底部のSi窒化膜シーム部分の酸化分離を目的として、3nm~7nmの範囲で検討した。なお、上記トップSi酸化膜204cの膜厚はパターンエッジから十分に離れた平坦部での膜厚の値を示している。40

## 【0086】

ISSG酸化後のトップSi酸化膜の膜厚を評価した結果、選択ゲート電極203パターン側壁部のSi窒化膜204'b上のトップSi酸化膜204'cの膜厚は、平面部分のSi窒化膜204b上のトップSi酸化膜204cの膜厚に比べ、約1.3~1.6倍の厚さになっていた。これは、先に示したプラズマイオン照射量の違いにより、Si窒化膜50

の膜質が異なるためである。

**【0087】**

更に、ISSG酸化形状の経過を詳細に調べた結果、図11に示すように、Si窒化膜の酸化は、パターン側壁底部のシームに沿って進行しパターン側壁部のSi窒化膜204'bと底面部のSi窒化膜204bとを分離することが分かった。

**【0088】**

すなわち、本実施例によれば、プラズマCVD法で形成するSi窒化膜204bの堆積条件、堆積膜厚、及びその酸化量を調整することで、パターン側壁底部に存在するSi窒化膜のシームを完全に酸化でき、パターン側壁部のSi窒化膜204'bと底面部のSi窒化膜204bとを任意の幅で分離できる。本実施例では、Si窒化膜204bの堆積条件と酸化量を調整し、上記分離幅を約2nmから6nmとした試料を作製した。

10

**【0089】**

次に、図12に示したように、メモリゲート電極205となるリンドープ多結晶Si膜を60nm堆積した後、実施例1と同様の方法でメモリゲート電極205、および選択ゲート電極203を形成した。

**【0090】**

この後、半導体基板201にソース、ドレインなどを形成し、実施例1と同様の製法を用いて図19に示した第2の構造例となるスプリットゲート構造のMONOSメモリを作製した。

**【0091】**

本実施例で作製したスプリットゲート構造のMONOS不揮発メモリの電気的特性を図8に示した電圧条件で従来構造と比較した。本実施例では図12に示したように、選択ゲート電極203とメモリゲート電極205の間に位置するSi窒化膜204'bが、Si基板201とメモリゲート電極205の間に位置するSi窒化膜204bよりも薄い構造になっている。このため、選択ゲート電極203パターン側壁部のSi窒化膜204'bへのホットエレクトロン注入量が大幅に減少した。

20

**【0092】**

また、トップSi酸化膜204cの形成過程で、選択ゲート電極203パターン側壁底部のSi窒化膜204'bと平面部分のSi窒化膜204bとはトップSi酸化膜204cで分離されているため、パターン側壁底部のSi窒化膜204'bへの電子の拡散[自己電界による電子の拡散、及び高温保持(150)]による熱拡散]が抑制された。

30

**【0093】**

この結果、実施例1の検討結果と同様に、読み出し電流、書き込み時間は従来メモリと同等の値を示したが、パターン側壁部のSi窒化膜204'b中の捕獲電子量が少ないため消去時間が約20%短縮した。これにより、本実施例においてもホットホールを発生させるための消去電流を約20%低減できた。また、繰り返し書き込み/消去特性においては、5e5回まで電子の消し残りが観測されなかった。更に、1e4回の書き込み/消去動作後に150の放置リテンション特性(しきい電圧の変動量で定義では)を評価した結果、従来構造に比べ約1.5桁の改善があった。

**【0094】**

なお、本実施例では、Si窒化膜形成前の選択ゲート電極側壁形状を垂直に加工したが、実施例2に示したように、オーバーハング形状や逆テープ形状にすることも無論可能である。

**【0095】**

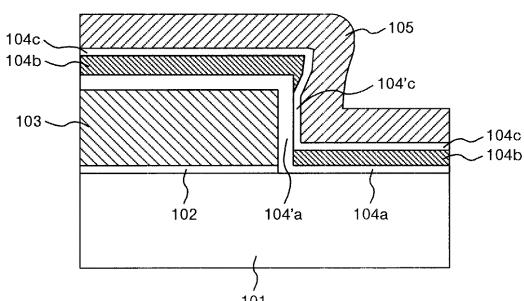

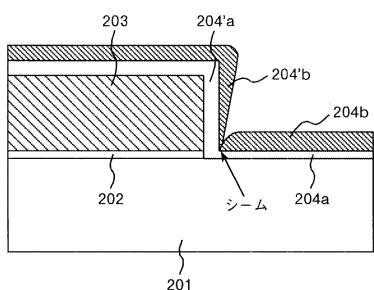

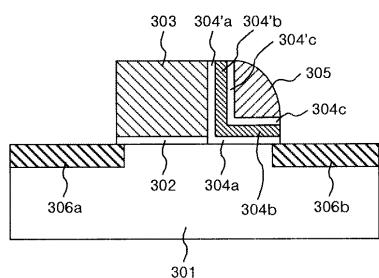

<実施例4>

次に、図14を用いて、本発明の第4の実施例を説明する。この実施例は先に図20で概説した第3の構造例に該当するものであり、本実施例でも、メモリアレーの構成、及び各電圧の設定は実施例1と同様である。本実施例では、実施例1に示した方法を用いて、図14に示すメモリセルを作製した。

**【0096】**

50

20

30

40

50

図14において、301はウエル領域(Si基板)、302及び303は、それぞれ選択MOS型トランジスタQ<sub>2</sub>のゲート絶縁膜及びゲート電極である。また、304a、304b、304cはメモリMOS型トランジスタQ<sub>1</sub>のゲート絶縁膜204で、それぞれボトムSi酸化膜、Si窒化膜、トップSi酸化膜である。304'a、304'b、304'cは、それぞれ上記メモリMOS型トランジスタのゲート絶縁膜204と同時に形成される絶縁膜で、選択MOS型トランジスタのゲート電極303とメモリMOS型トランジスタのゲート電極305を電気的に分離する絶縁膜である。306a、306bは、それぞれMONOSメモリのソース領域、ドレイン領域に対応する。

#### 【0097】

本実施例(図14)が、実施例1と異なる点は、電荷保持膜であるSi窒化膜304b及び304'bの形成方法である。本実施例では、Si窒化膜の形成に減圧熱CVD法を適用した。ここでは、従来から用いられているジクロロシラン(SiH<sub>2</sub>Cl<sub>2</sub>)とアンモニア(NH<sub>3</sub>)を原料ガスとして形成したSi窒化膜に比べ、段差被覆性が悪いモノシリコン(SiH<sub>4</sub>)とNH<sub>3</sub>、及びジシラン(Si<sub>2</sub>H<sub>6</sub>)とNH<sub>3</sub>を原料ガスとしてSi窒化膜の形成を行った。以下、個々Si窒化膜の成膜条件を示す。

(1) SiH<sub>2</sub>Cl<sub>2</sub>とNH<sub>3</sub>を原料ガスとしたSi窒化膜は、温度；780、圧力；60Pa～200Pa、SiH<sub>2</sub>Cl<sub>2</sub>流量；20cc/min、NH<sub>3</sub>流量；220cc/minとした。

(2) SiH<sub>4</sub>とNH<sub>3</sub>を原料ガスとしたSi窒化膜は、温度；700、圧力；100Pa～400Pa、SiH<sub>4</sub>流量；30cc/min、NH<sub>3</sub>流量；220cc/minとした。

(3) Si<sub>2</sub>H<sub>6</sub>とNH<sub>3</sub>を原料ガスとしたSi窒化膜は、温度；650、圧力；200Pa～400Pa、Si<sub>2</sub>H<sub>6</sub>流量；10cc/min、NH<sub>3</sub>流量；400cc/minとした。

#### 【0098】

電荷保持膜であるSi窒化膜304bの膜厚は、平坦部の膜厚で12nmとなるようにそれぞれ調整した。このとき、選択MOS型トランジスタのゲート電極303側壁部に堆積されたSi窒化膜304'bの膜厚は、上記(1)が12nm、(2)が8.5nm(70%)、(3)が6nm(50%)であった。以上のように、選択MOS型トランジスタのゲート電極303側壁部に堆積されたSi窒化膜304'bの膜厚を変えて電気的な測定を行った。

#### 【0099】

本実施例で作製したスプリットゲート型MONOS不揮発メモリの電気的特性を図8に示した電圧条件で従来構造と比較した。その結果、上記(1)と比較した場合、読み出し電流、書き込み時間は全て同等の値を示したが、消去時間は上記(3)の条件が最も短く、次に(2)の条件となった。本実施例により、選択MOS型トランジスタのゲート電極303側壁部に堆積されたSi窒化膜304'bの膜厚を薄くする方が、消し残り電子が少なくなり、ホットホールを発生させるための消去電流を低減できることが分かった。

#### 【0100】

また、繰り返し書き込み/消去特性においては、上記(2)(3)の条件は1e4回までは電子の消し残りが観測されなかったが、更に、150の放置リテンション特性(しきい電圧の変動量で定義では)、従来構造に比べ1桁の改善があった。

#### 【0101】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

また、本発明の不揮発性メモリは、マイクロコンピュータに用いるなど、種々の装置に搭載可能である。また、本発明は、Si窒化膜に代表される電荷保持機能を有する絶縁膜を用いた不揮発性半導体装置全般に適用可能である。

#### 【図面の簡単な説明】

#### 【0102】

【図1】本発明の第1の実施例となるスプリットゲート構造メモリセルの要部を示した断

10

20

30

40

50

面図である。

【図2】本発明の第1の実施例の製造工程を示したセル断面図である。

【図3】本発明の第1の実施例の製造工程を示したセル断面図である。

【図4】本発明の第1の実施例の製造工程を示したセル断面図である。

【図5】本発明の第1の実施例の製造工程を示したセル断面図である。

【図6】本発明の第1の実施例の製造工程を示したセル断面図である。

【図7】本発明の実施例を示したメモリアレーayoutである。

【図8】本発明の実施例を示した印加電圧の設定図である。

【図9】本発明の第3の実施例の製造工程を示したセル断面図である。

【図10】本発明の第3の実施例の製造工程を示したセル断面図である。 10

【図11】本発明の第3の実施例の製造工程を示したセル断面図である。

【図12】本発明の第3の実施例の製造工程を示したセル断面図である。

【図13】本発明の第3の実施例の製造工程を示したセル断面図である。

【図14】本発明の第4の実施例の製造工程を示したセル断面図である。

【図15】従来のスプリットゲート構造を示したセル断面図である。

【図16】従来のセル構造にホットエレクトロン注入(書き込み)を説明する断面模式図である。

【図17】従来構造にホットホール注入(消去)を説明する断面模式図である。

【図18】本発明の第1のスプリットゲート構造例を説明するセル断面図である。

【図19】本発明の第2のスプリットゲート構造例を説明するセル断面図である 20

【図20】本発明の第3のスプリットゲート構造例を説明するセル断面図である

【図21】本発明の第2の実施例となる第1の製造工程を示したセル断面図である。

【図22】本発明の第2の実施例となる第1の製造工程を示したセル断面図である。

【図23】本発明の第2の実施例となる第1の製造工程を示したセル断面図である。

【図24】本発明の第2の実施例となる第1の製造工程を示したセル断面図である。

【図25】本発明の第2の実施例となる第2の製造工程を示したセル断面図である。

【図26】本発明の第2の実施例となる第3の製造工程を示したセル断面図である。

【符号の説明】

【0103】

101...p型ウエル領域(Si基板)、 30

102...ゲート絶縁膜(選択MOS型トランジスタ)、

103...選択ゲート電極(選択MOS型トランジスタ)、

104a...下層電位障壁膜(Si酸化膜)、

104b...Si窒化膜(電荷保持膜)、

104c...上層電位障壁膜(Si酸化膜)、

104'a...選択ゲート電極側壁部の下層電位障壁膜(Si酸化膜)、

104'b...選択ゲート電極側壁部のSi窒化膜(電荷保持膜)、

104'c...選択ゲート電極側壁部の上層電位障壁膜(Si酸化膜)、

105...メモリゲート電極(メモリMOS型トランジスタ)、

106a...ソース領域、 40

106b...ドレイン領域

201...p型ウエル領域(Si基板)、

202...ゲート絶縁膜(選択MOS型トランジスタ)、

203...選択ゲート電極(選択MOS型トランジスタ)、

204a...下層電位障壁膜(Si酸化膜)、

204b...Si窒化膜(電荷保持膜)、

204c...上層電位障壁膜(Si酸化膜)、

204'a...選択ゲート電極側壁部の下層電位障壁膜(Si酸化膜)、

204'b...選択ゲート電極側壁部のSi窒化膜(電荷保持膜)、

204'c...選択ゲート電極側壁部の上層電位障壁膜(Si酸化膜)、 50

- 205...メモリゲート電極（メモリMOS型トランジスタ）、

206a...ソース領域、

206b...ドレイン領域、

301...p型ウエル領域（Si基板）、

302...ゲート絶縁膜（選択MOS型トランジスタ）、

303...選択ゲート電極（選択MOS型トランジスタ）、

304a...下層電位障壁膜（Si酸化膜）、

304b...Si窒化膜（電荷保持膜）、

304c...上層電位障壁膜（Si酸化膜）、

304'a...選択ゲート電極側壁部の下層電位障壁膜（Si酸化膜）、

304'b...選択ゲート電極側壁部のSi窒化膜（電荷保持膜）、

304'c...選択ゲート電極側壁部の上層電位障壁膜（Si酸化膜）、

305...メモリゲート電極（メモリMOS型トランジスタ）、

306a...ソース領域、

306b...ドレイン領域、

401...p型ウエル領域（Si基板）、

402...ゲート絶縁膜（選択MOS型トランジスタ）、

403...選択ゲート電極（選択MOS型トランジスタ）、

404a...下層電位障壁膜（Si酸化膜）、

404b...Si窒化膜（電荷保持膜）、

404c...上層電位障壁膜（Si酸化膜）、

405...メモリゲート電極（メモリMOS型トランジスタ）、

406a...ソース領域、

406b...ドレイン領域、

501...p型ウエル領域（Si基板）、

502...ゲート絶縁膜（選択MOS型トランジスタ）、

503...選択ゲート電極（選択MOS型トランジスタ）、

504a...下層電位障壁膜（Si酸化膜）、

504b...Si窒化膜（電荷保持膜）、

504c...上層電位障壁膜（Si酸化膜）、

505...メモリゲート電極（メモリMOS型トランジスタ）、

506a...ソース領域、

506b...ドレイン領域、

601...p型ウエル領域（Si基板）、

602...ゲート絶縁膜（選択MOS型トランジスタ）、

603...選択ゲート電極（選択MOS型トランジスタ）、

604a...下層電位障壁膜（Si酸化膜）、

604b...Si窒化膜（電荷保持膜）、

604'b...選択ゲート電極側壁部のSi窒化膜（電荷保持膜）、

604c...上層電位障壁膜（Si酸化膜）、

605...ゲート電極（メモリゲート電極）、

606a...ソース領域、

606b...ドレイン領域、

701...p型ウエル領域（Si基板）、

702...ゲート絶縁膜（選択MOS型トランジスタ）、

703...選択ゲート電極（選択MOS型トランジスタ）、

704a...下層電位障壁膜（Si酸化膜）、

704b...Si窒化膜（電荷保持膜）、

704'b...選択ゲート電極側壁部のSi窒化膜（電荷保持膜）、

704c...上層電位障壁膜（Si酸化膜）、

10

20

30

40

50

7 0 5 ... ゲート電極（メモリゲート電極）、

7 0 6 a... ソース領域、

7 0 6 b... ドレイン領域、

8 0 1 ... p型ウエル領域（S i 基板）、

8 0 2 ... ゲート絶縁膜（選択M O S型トランジスタ）、

8 0 3 '... 選択ゲート電極（ノンドープ多結晶S i）、

8 0 3 ''... 選択ゲート電極（リンドープ多結晶S i）、

8 0 4 a ... 下層電位障壁膜（S i 酸化膜）、

8 0 4 ' a ... 選択ゲート電極側壁部の下層電位障壁膜（S i 酸化膜）、

8 0 4 '' a ... 選択ゲート電極側壁部の下層電位障壁膜（S i 酸化膜）、

8 0 4 b ... S i 窒化膜（電荷保持膜）、

8 0 4 ' b ... 選択ゲート電極側壁部のS i 窒化膜（電荷保持膜）、

8 0 4 c ... 上層電位障壁膜（S i 酸化膜）、

8 0 4 ' c ... 選択ゲート電極側壁部の上層電位障壁膜（S i 酸化膜）、

9 0 1 ... p型ウエル領域（S i 基板）、

9 0 2 ... ゲート絶縁膜（選択M O S型トランジスタ）、

9 0 3 ... 選択ゲート電極、

9 0 4 a ... 下層電位障壁膜（S i 酸化膜）、

9 0 4 ' a ... 選択ゲート電極側壁部の下層電位障壁膜（S i 酸化膜）、

9 0 4 b ... S i 窒化膜（電荷保持膜）、

9 0 4 ' b ... S i 酸化膜側壁部のS i 窒化膜、

9 0 7 ... S i 酸化膜、

1 1 1 ... p型ウエル領域（S i 基板）、

1 1 2 ... ゲート絶縁膜（選択M O S型トランジスタ）、

1 1 3 ... 選択ゲート電極、

1 1 4 a ... 下層電位障壁膜（S i 酸化膜）、

1 1 4 ' a ... 選択ゲート電極側壁部の下層電位障壁膜（S i 酸化膜）、

1 1 4 b ... S i 窒化膜（電荷保持膜）、

1 1 4 ' b ... S i 酸化膜側壁部のS i 窒化膜、

1 1 7 ... S i 酸化膜、

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

| 印加電圧   | Vsg  | Vmg  | Vd | Vs   | Vwell | 手法                 |

|--------|------|------|----|------|-------|--------------------|

| 書込(注入) | 1.5V | 11V  | 6V | 0.8V | 0V    | ソースサイトホットエクレクトロン注入 |

| 消去(放出) | 0V   | -5V  | 7V | OPEN | 0V    | トレインサイトホットホール注入    |

| 読出     | 1.5V | 1.5V | 0V | 1.0V | 0V    | 書込時ソース・トレインと逆方向    |

【図9】

9

【図10】

図 10

【 図 1 3 】

13

【図 1-4】

図 14

【 図 1 1 】

1 1

【 义 1 2 】

図 1 2

【図15】

四 15

【図16】

図 16

【図17】

図17

【図18】

図18

【図19】

図19

【図20】

図20

【図21】

図21

【図22】

図22

【図23】

図23

【図 2 4】

図 2 4

【図 2 6】

図 2 6

【図 2 5】

図 2 5

---

フロントページの続き

(72)発明者 安井 感

東京都国分寺市東恋ヶ窪一丁目280番地株式会社日立製作所中央研究所内

審査官 井原 純

(56)参考文献 特開2003-046002(JP,A)

特開2003-318290(JP,A)

米国特許第05408115(US,A)

特開2004-1111749(JP,A)

特開2003-051558(JP,A)

特表2004-503113(JP,A)

特開2004-343014(JP,A)

特開2002-026149(JP,A)

Wei-Ming Chen, et al, A Novel Flash Memory Device with SPLIT Gate Source Side Injection and ONO Charge Storage Stack(SPIN), 1997 Symposium on VLSI Technology Digest of Technical Papers, 米国, IEEE, 1997年 6月10日, p.63-64

(58)調査した分野(Int.Cl., DB名)

H01L 21/8247

H01L 27/115

H01L 29/788

H01L 29/792