(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년02월25일

(11) 등록번호 10-1597845

(24) 등록일자 2016년02월19일

(51) 국제특허분류(Int. Cl.)

H01L 27/10 (2006.01) G11C 13/02 (2006.01)

H01L 27/102 (2006.01) H01L 51/00 (2006.01)

(21) 출원번호 10-2010-7022345

(22) 출원일자(국제) 2009년04월10일

심사청구일자 2014년04월09일

(85) 번역문제출일자 2010년10월06일

(65) 공개번호 10-2011-0005692

(43) 공개일자 2011년01월18일

(86) 국제출원번호 PCT/US2009/040183

(87) 국제공개번호 WO 2009/126871

국제공개일자 2009년10월15일

(30) 우선권주장

12/418,855 2009년04월06일 미국(US)

61/044,399 2008년04월11일 미국(US)

(56) 선행기술조사문헌

EP01892722 A1

US20080099752 A1

WO2007062014 A1

WO2008021900 A2

(73) 특허권자

샌디스크 3디 엘엘씨

미국, 캘리포니아 95035-7933, 밀피타스, 샌디스크 드라이브 951

(72) 발명자

슈얼라인, 로이, 이.

미국, 캘리포니아 95014, 쿠퍼티노, 오챠드 코트 22145

일크바하, 앤퍼

미국, 캘리포니아 95131, 산 호세, 포 옥스 로드 1418

슈리커, 에이프렐, 디.

미국, 캘리포니아 94306, 팔로 알토, 맨자나타 애비뉴 255

(74) 대리인

양영준, 백만기, 정은진

전체 청구항 수 : 총 25 항

심사관 : 류정현

(54) 발명의 명칭 탄소계 메모리 소자를 포함한 메모리 셀과 이를 형성하는 방법

**(57) 요약**

발명의 면에 따라서, 메모리 셀을 형성하는 방법이 제공되고, 상기 방법은, 기판 위에 스티어링 소자를 형성하는 단계; 및 스티어링 소자에 결합된 메모리 소자를 형성하는 단계로서, 메모리 소자는 10개 이하의 원자층의 두께를 갖는 탄소계 물질을 포함하는, 단계를 포함한다. 메모리 소자는 약 하나의 모노층의 두께를 갖는, 탄소계 물질의 층을 형성하는 단계와, 탄소계 물질층에 열 어닐링을 가하는 단계를 반복적으로 수행함으로써, 형성된다.

**대 표 도 - 도3**

## 명세서

### 청구범위

#### 청구항 1

메모리 셀을 형성하는 방법에 있어서,

기판 위에 스티어링 소자(steering element)를 형성하는 단계와,

상기 스티어링 소자에 결합된 메모리 소자를 형성하는 단계로서, 상기 메모리 소자는 10개 이하의 원자층의 두

께를 갖는 탄소계 물질을 포함하는, 상기 메모리 소자를 형성하는 단계를

포함하는, 메모리 셀 형성 방법.

#### 청구항 2

제 1항에 있어서, 상기 스티어링 소자는 p-n 또는 p-i-n 다이오드를 포함하는, 메모리 셀 형성 방법.

#### 청구항 3

제 2항에 있어서, 상기 스티어링 소자는 다결정 다이오드를 포함하는, 메모리 셀 형성 방법.

#### 청구항 4

제 1항에 있어서, 상기 메모리 소자는 가역 저항 스위칭 소자를 포함하는, 메모리 셀 형성 방법.

#### 청구항 5

제 4항에 있어서, 상기 탄소계 물질은 무정형 탄소를 포함하는, 메모리 셀 형성 방법.

#### 청구항 6

제 1항에 있어서, 상기 메모리 소자를 형성하는 단계는 플라즈마 인핸스드 화학 증기 증착 기술을 사용하여 상

기 탄소계 물질을 증착하는 단계를 포함하는, 메모리 셀 형성 방법.

#### 청구항 7

제 6항에 있어서, 상기 플라즈마 인핸스드 화학 증기 증착 기술은 300°C 내지 600°C의 가공 온도에서 수행되는,

메모리 셀 형성 방법.

#### 청구항 8

제 7항에 있어서, 상기 플라즈마 인핸스드 화학 증기 증착 기술은 300°C 내지 450°C의 가공 온도에서 수행되는,

메모리 셀 형성 방법.

#### 청구항 9

제 1항의 방법을 사용하여 형성된 메모리 셀.

#### 청구항 10

메모리 셀 형성 방법에 있어서,

기판 위에 스티어링 소자를 형성하는 단계와,

하나의 모노층의 두께를 갖는, 탄소계 물질의 층을 형성하는 단계와, 상기 탄소계 물질층에 열 어닐링을 가하는

단계를 반복적으로 수행함으로써, 상기 스티어링 소자에 결합되는 메모리 소자를 형성하는 단계를

포함하는, 메모리 셀 형성 방법.

**청구항 11**

제 10항에 있어서, 상기 스티어링 소자는 p-n 또는 p-i-n 다이오드를 포함하는, 메모리 셀 형성 방법.

**청구항 12**

제 11항에 있어서, 상기 스티어링 소자는 다결정 다이오드를 포함하는, 메모리 셀 형성 방법.

**청구항 13**

제 10항에 있어서, 상기 메모리 소자는 가역 저항 스위칭 소자를 포함하는, 메모리 셀 형성 방법.

**청구항 14**

제 10항에 있어서, 상기 탄소계 물질은 무정형 탄소를 포함하는, 메모리 셀 형성 방법.

**청구항 15**

제 10항에 있어서, 상기 메모리 소자를 형성하는 단계는 플라즈마 인핸스드 화학 증기 증착 기술을 사용하여 상기 탄소계 물질을 증착하는 단계를 포함하는, 메모리 셀 형성 방법.

**청구항 16**

제 15항에 있어서, 상기 플라즈마 인핸스드 화학 증기 증착 기술은 300°C 내지 900°C의 가공 온도에서 수행되는, 메모리 셀 형성 방법.

**청구항 17**

제 15항에 있어서, 상기 플라즈마 인핸스드 화학 증기 증착 기술은 300°C 내지 600°C의 가공 온도에서 수행되는, 메모리 셀 형성 방법.

**청구항 18**

제 15항에 있어서, 상기 플라즈마 인핸스드 화학 증기 증착 기술은 300°C 내지 450°C의 가공 온도에서 수행되는, 메모리 셀 형성 방법.

**청구항 19**

제 10항에 있어서, 상기 열 어닐링은 250°C 내지 850°C의 가공 온도에서 수행되는, 메모리 셀 형성 방법.

**청구항 20**

제 10항에 있어서, 상기 열 어닐링은 350°C 내지 650°C의 가공 온도에서 수행되는, 메모리 셀 형성 방법.

**청구항 21**

제 10항에 있어서, 상기 열 어닐링은 600°C의 가공 온도에서 수행되는, 메모리 셀 형성 방법.

**청구항 22**

제 10항에 있어서, 상기 열 어닐링은 비-산화 분위기를 사용하여 수행되는, 메모리 셀 형성 방법.

**청구항 23**

제 10항에 있어서, 하나의 모노층은 1개의 원자층의 탄소계 물질을 포함하는, 메모리 셀 형성 방법.

**청구항 24**

제 10항의 방법을 사용하여 형성된 메모리 셀.

**청구항 25**

메모리 셀에 있어서,

기판 위에 스티어링 소자와,

상기 스티어링 소자에 결합된 메모리 소자로서, 상기 메모리 소자는 10개 이하의 원자층의 두께를 갖는 탄소계 물질을 포함하는, 상기 메모리 소자를

포함하는, 메모리 셀.

### 발명의 설명

#### 기술 분야

관련 출원에 대한 상호 참조

이 출원은 "Thin Deposited Carbon Switchable Resistor And Diode Matrix Cell For 3D Arrays"의 명칭으로 2008년 4월 11일에 출원된 미국 특허출원 61/044,399의 헤택을 청구하며, "A Memory Cell That Includes A Carbon-Based Memory Element And Damascene Integration Methods Of Forming The Same" 명칭으로 2008년 4월 6일에 출원된 미국 특허 출원번호 12/418,855로부터 우선권을 주장하며, 이들은 모든 목적을 위해 전체 내용이 본 명세서에 참조로 포함된다.

이 발명은, 비휘발성 메모리에 관한 것이고, 보다 구체적으로는 탄소계 메모리 소자를 포함한 메모리 셀과 이를 형성하는 방법에 관한 것이다.

#### 배경 기술

가역 저항-스위칭 소자로부터 형성된 비휘발성 메모리가 공지되어 있다. 예를 들어, 모든 목적을 위해 전체 내용이 본 명세서에 포함되는 "Memory Cell That Employs A Selectively Fabricated Carbon Nano-Tube Reversible Resistance Switching Element And Methods Of Forming The Same" 명칭의 2007년 12월 31일에 출원된 미국 특허 출원번호 11/968,154("'154 출원")은 탄소계 가역 저항 스위칭 물질과 직렬로 결합된 다이오드를 포함하는 재기록 가능한 비휘발성 메모리 셀을 기술한다.

#### 발명의 내용

##### 해결하려는 과제

그러나, 탄소계 물질로 메모리 장치를 제조하는 것은 기술적으로 과제가 되고 있고, 탄소계 물질을 사용한 메모리 장치를 형성하는 개선된 방법들이 바람직하다.

##### 과제의 해결 수단

발명의 제 1 면에 따라서, 기판 위에 스티어링 소자를 형성하는 단계; 및 상기 스티어링 소자에 결합된 메모리 소자를 형성하는 단계로서, 상기 메모리 소자는 10개 이하의 원자층의 두께를 갖는 탄소계 물질을 포함하는, 단계를 포함하는, 메모리 셀 형성 방법이 제공된다.

발명의 제 2 면에 따라서, 기판 위에 스티어링 소자를 형성하는 단계; 및 약 하나의 모노층의 두께를 갖는, 탄소계 물질의 층을 형성하는 단계와, 상기 탄소계 물질층에 열 어닐링을 가하는 단계를 반복적으로 수행함으로써, 상기 스티어링 소자에 결합되는 메모리 소자를 형성하는 단계를 포함하는, 메모리 셀 형성 방법이 제공된다.

발명의 제 3 면에 따라서, 기판 위에 스티어링 소자; 및 상기 스티어링 소자에 결합된 메모리 소자로서, 상기 메모리 소자는 10개 이하의 원자층의 두께를 갖는 탄소계 물질을 포함하는, 상기 메모리 소자를 포함하는, 메모리 셀이 제공된다.

본 발명의 다른 특징들 및 면들은 다음의 상세한 설명, 첨부한 청구항들 및 도면으로부터 더 완전하게 명백하게 될 것이다.

#### 발명의 효과

본 발명은, 탄소계 물질로 메모리 장치를 제조하고, 탄소계 물질을 사용한 메모리 장치를 형성하는 개선된 방법을 제공하는 효과를 갖는다.

## 도면의 간단한 설명

[0011]

본 발명의 특징은 동일 구성요소에 동일 참조부호를 사용한 다음 도면에 관련하여 고찰된 다음 상세한 설명으로부터 더 명확하게 이해될 수 있다.

도 1은, 본 발명에 따른 메모리 셀 도면.

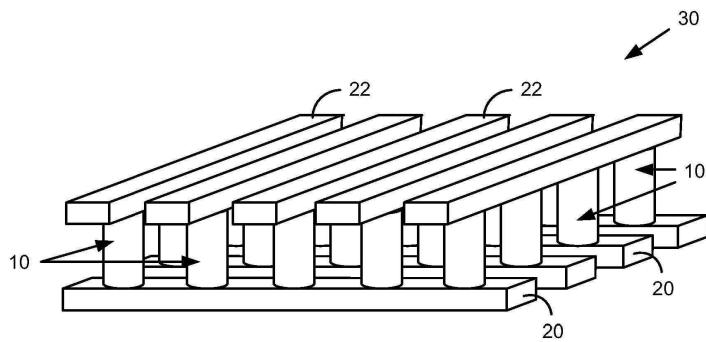

도 2a는, 본 발명에 따른 메모리 셀의 간이화한 사시도.

도 2b는, 도 2a의 복수의 메모리 셀로부터 형성된 제 1 메모리 레벨의 부분의 간이화한 사시도.

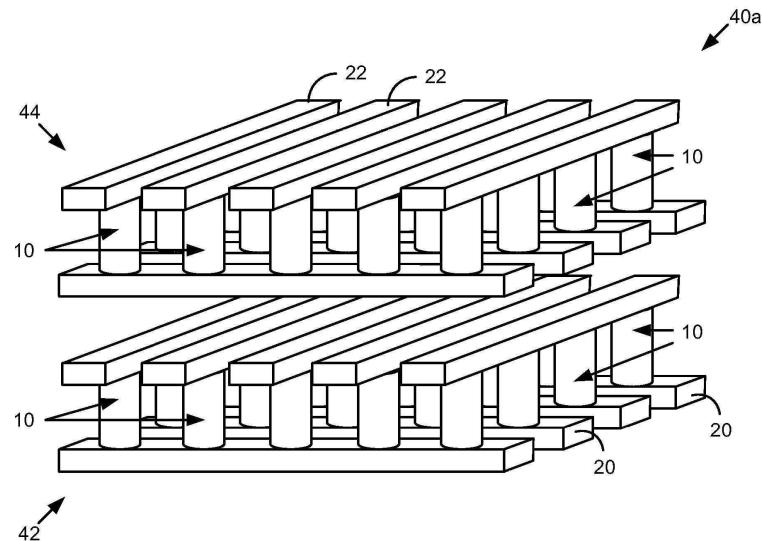

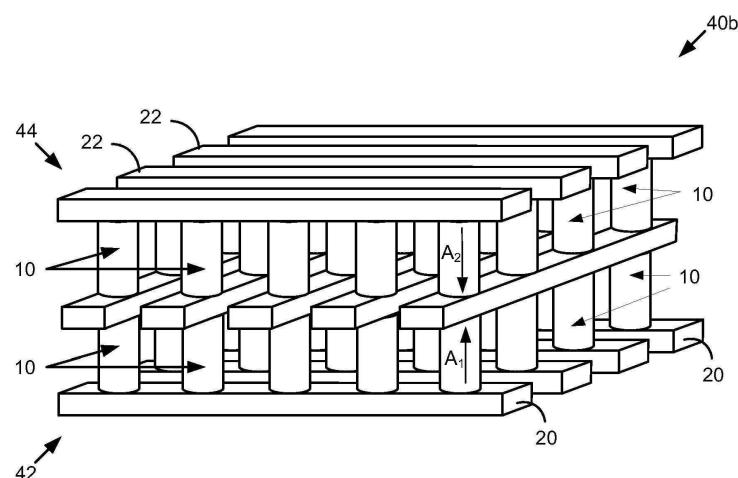

도 2c는, 본 발명에 따른 제 1의 3차원 메모리 어레이의 부분의 간이화한 사시도.

도 2d는, 본 발명에 따른 제 2의 3차원 메모리 어레이의 부분의 간이화한 사시도.

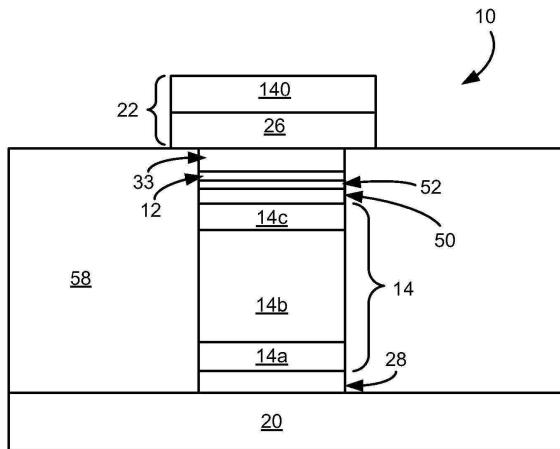

도 3은, 본 발명에 따른 메모리 셀의 실시예의 단면도.

도 4a 내지 도 4e는, 본 발명에 따른 단일 메모리 레벨의 제조 동안 기판의 부분의 단면도.

## 발명을 실시하기 위한 구체적인 내용

[0012]

그라펜(graphene), 무정형 탄소("aC") 함수 마이크로결정 또는 다른 영역들의 그라펜, 이외 흑연 탄소 막 등으로 제한되는 것은 아니지만, 이들을 포함하는 어떤 탄소계 막들은 마이크로전자 비휘발성 메모리들을 형성하기 위해 사용될 수 있는 저항률 스위칭 특성을 나타낼 수 있다. 그러므로, 이러한 막들이 3차원 메모리 어레이 내에 집적하기 위한 후보들이다.

[0013]

사실, 탄소계 물질은 실험실 규모의 장치들에서 온 상태와 오프 상태 사이에  $100\times$  분리와 중간 내지 고 범위 저항 변화들을 가진 메모리 스위칭 특성을 나타내었다. 온 상태와 오프 상태 사이에 이러한 분리는 탄소계 물질을, 탄소계 물질이 수직 다이오드, 박막 트랜지스터들 또는 그외 스티어링 소자와 직렬로 결합되는 메모리 셀들 용으로 사용 가능한 후보들이 되게 한다. 예를 들어, 2개의 금속 또는 아니면 도전성 층들 사이에 개재된 탄소계 물질로부터 형성된 금속-절연체-금속("MIM") 적층은 메모리 셀용으로 저항-스위칭 소자로서 작용할 수 있다.

[0014]

탄소계 물질은 흔히 플라즈마-인핸스드 화학 증기 증착("PECVD") 기술을 사용하여 증착된다. 이러한 탄소계 물질은 주변 물질들의 저항률들에 비해 낮을 수 있는 "초기 저항률"(즉, 형성될 때 물질의 저항률)을 가질 수 있다. 결국, 탄소계 물질을 포함하는 저항-스위칭 소자는 이를테면 이웃 다이오드와 같이 저항-스위칭 소자를 통하는 전류를 제어하기 위해 사용되는 스티어링 소자에 호환되지 않는 높은 초기 전류를 도통시킬 수 있다. 추가로 또는 대안적으로, 탄소계 물질의 초기 저항률은 초기 사용시 물질을 리셋시키기 위해서 고 전압 및 전류를 요구할 수 있다.

[0015]

이 발명의 실시예에 따라서, 탄소계 물질을 포함하는 MIM 적층을 포함하고 다이오드로서 스티어링 소자에 결합되는 메모리 셀이 형성된다. 메모리 셀은 약 10개의 원자층들 또는 더 적은 수의 원자층의 두께를 갖는 얇은 층의 탄소계 물질을 증착함으로써 형성된다.

[0016]

이 발명의 또 다른 실시예에 따라서, 탄소계 물질을 포함하는 MIM 적층을 포함하고 다이오드로서 스티어링 소자에 결합되는 메모리 셀이 형성된다. 메모리 셀은 탄소계 물질의 복수의 모노층들(monolayer) 또는 근(near)-모노층들을 형성하기 위해 복수의 증착들을 수행함으로써 형성된다. 여기에서 사용되는 바와 같이, 모노층의 탄소계 물질은 약 1 원자층의 탄소계 물질이다. 각각의 모노층의 탄소계 물질이 형성된 후에, 물질은 다음의 연속된 층을 형성하기 전에 약  $600^{\circ}\text{C}$  미만의 가공 온도에서 어닐링된다. 각각의 층에 어닐링을 가함으로써 평면내 탄소본드들의 형성이 용이해지고 평면외 탄소본드들의 수가 제한되어 물질 표면에 수직한 방향으로 흐르는 전류에 대한 탄소계 물질의 저항률이 증가한다. 이러한 식으로 탄소계 물질의 저항률의 증가는 탄소계 물질로부터 형성된 가역-저항 스위칭 소자의 저항을 증가시키고, 그럼으로써 가역-저항 스위칭 소자를 통하는 초기 전류 흐름을 감소시킨다.

[0017]

### 본 발명의 메모리 셀

[0018]

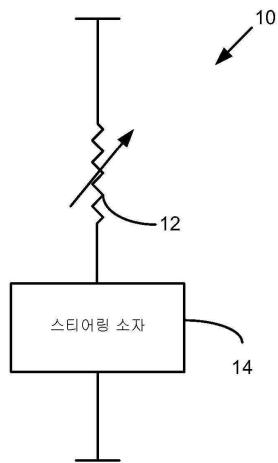

도 1은 이 발명에 따라 제공된 메모리 셀(10)의 개략도이다. 메모리 셀(10)은 스티어링 소자(14)에 결합된 가역 저항-스위칭 소자(12)를 포함한다. 가역 저항-스위칭 소자(12)는 2 이상의 상태 사이에 가역적으로 전환될 수

있는 저항률을 갖는 가역 저항-스위칭 물질(별도로 도시되지 않았음)을 포함한다.

[0019] 예를 들어, 소자(12)의 가역 저항-스위칭 물질은 제조시 초기엔 저-저항률 상태에 있을 수 있다. 제 1 전압 및/또는 전류의 인가시, 물질은 고-저항률 상태로 전환될 수 있다. 제 2 전압 및/또는 전류의 인가는 가역 저항-스위칭 물질을 저-저항률 상태로 복귀시킬 수 있다. 대안적으로, 가역 저항-스위칭 소자(12)는 적합한 전압(들) 및/또는 전류(들)의 인가시 저-저항 상태로 가역적으로 전환할 수 있는, 제조시 초기의 고-저항 상태에 있을 수 있다. 메모리 셀에서 사용될 때, 2 이상의 데이터/저항상태들이 사용될 수 있을지라도, 한 저항상태는 2진수 "0"을 나타낼 수 있고 또 다른 저항상태는 2진수 "1"을 나타낼 수 있다. 수많은 가역 저항-스위칭 물질들 및 가역 저항-스위칭 소자를 사용한 메모리 셀들의 동작은 예를 들어, 모든 목적을 위해 전체 내용이 본 명세서에 참조로 포함된 "Rewriteable Memory Cell Comprising A Diode And A Resistance-Switching Material" 명칭의 2005년 5월 9일에 출원된 미국 특허 출원번호 11/125,939("939" 출원")에 기술되어 있다.

[0020] 스티어링 소자(14)는 박막 트랜지스터, 다이오드, 금속 절연체 터널링 전류 장치, 또는 가역 저항-스위칭 소자(12)에 걸리는 전압 및/또는 이를 통하는 전류 흐름을 선택적으로 제한시킴으로써 비-오믹 도전을 나타내는 또 다른 유사한 스티어링 소자를 포함할 수 있다. 따라서, 메모리 셀(10)은 2차원 또는 3차원 메모리 어레이의 일부로서 사용될 수 있고 데이터는 어레이 내 다른 메모리 셀들의 상태에 영향을 미침이 없이 메모리 셀(10)에 기록될 수 있고/있거나 이로부터 판독될 수 있다.

[0021] 메모리 셀(10), 가역 저항-스위칭 소자(12) 및 스티어링 다이오드(14)의 실시예들을 도 2a 내지 도 2d 및 도 3을 참조하여 이하 기술한다.

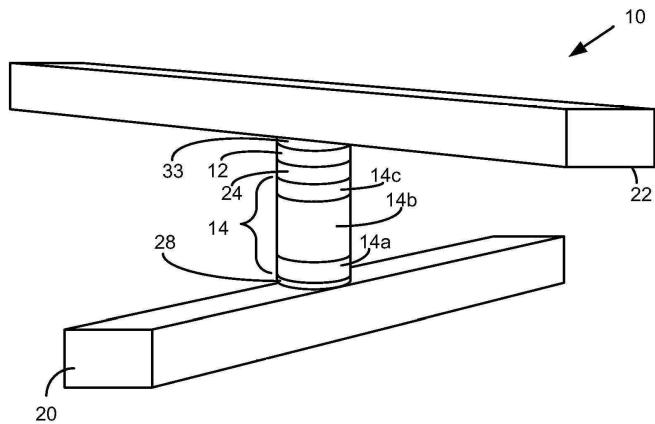

#### 메모리 셀과 메모리 어레이의 예시적인 실시예

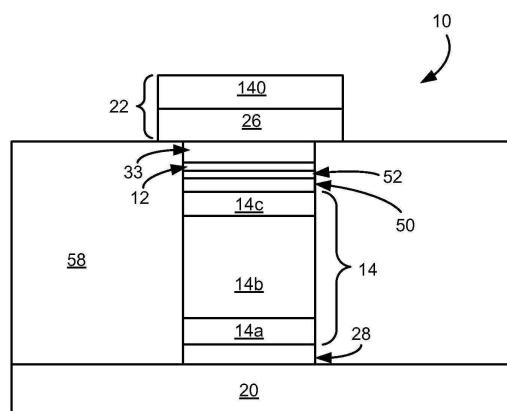

[0023] 도 2a는 스티어링 소자(14) 및 탄소계 가역 저항 스위칭 소자(12)를 포함하는 본 발명에 따른 메모리 셀(10)의 실시예의 간략화한 사시도이다. 가역 저항 스위칭 소자(12)는 제 1 도체(20)와 제 2 도체(22) 사이에 스티어링 소자(14)와 직렬로 결합된다. 일부 실시예에서, 장벽층(24)이 가역 저항-스위칭 소자(12)와 스티어링 소자(14) 사이에 제공될 수 있고, 장벽층(33)은 가역 저항 스위칭 소자(12)와 제 2 도체(22) 사이에 형성될 수 있다. 추가로 장벽층(28)이 스티어링 소자(14)와 제 1 도체(20) 사이에 형성될 수 있다. 예를 들어, 장벽층들(24, 28, 33)은 질화티탄, 질화탄탈, 질화텅스텐, 또는 그외 유사한 장벽층을 포함할 수 있다.

[0024] 위에 논의된 바와 같이, 스티어링 소자(14)는 박막 트랜지스터, 다이오드, 금속 절연체 터널링 전류 장치, 또는 가역 저항-스위칭 소자(12)에 걸리는 전압 및/또는 이를 통하는 전류 흐름을 선택적으로 제한시킴으로써 비-오믹 도전을 나타내는 또 다른 유사한 스티어링 소자를 포함할 수 있다. 도 2a의 예에서, 스티어링 소자(14)는 다이오드이다. 따라서, 스티어링 소자(14)를 여기에서는 종종 "다이오드(14)"라고도 한다.

[0025] 다이오드(14)는 다이오드의 p-영역 위에 n-영역을 갖고 위쪽을 향하든 다이오드의 n-영역 위에 p-영역을 갖고 아래쪽으로 향하든, 수직 다결정질의 p-n 또는 p-i-n 다이오드와 같은 임의의 적합한 다이오드를 포함할 수 있다. 예를 들어, 다이오드(14)는 고농도로 도핑된 n<sup>+</sup> 폴리실리콘 영역(14a), n<sup>+</sup> 폴리실리콘 영역(14a) 위에 저농도로 도핑된 또는 진성(도핑이 의도적이 아닌) 폴리실리콘 영역(14b) 및 진성영역(14b) 위에 고농도 도핑된 p<sup>+</sup> 폴리실리콘 영역(14c)을 포함할 수 있다. n<sup>+</sup> 및 p<sup>+</sup> 영역들의 위치들은 역전될 수도 있음이 이해될 것이다. 다이오드(14)의 실시예들을 도 3을 참조하여 이하 기술한다.

[0026] 가역 저항-스위칭 소자(12)는 2 이상의 상태 사이에 가역적으로 전환될 수 있는 저항률을 갖는 탄소계 물질(별도로 도시되지 않았음)을 포함할 수 있다. 예를 들어, 가역 저항 스위칭 소자(12)는 aC 함유 마이크로결정 또는 그외 그라펜의 다른 영역들을 포함할 수 있다. 간단하게 하기 위해서, 가역 저항 스위칭 소자(12)를 나머지 논의에서 "탄소 소자(12)"라 할 것이다.

[0027] 제 1 및/또는 제 2 도체(20, 22)는 텅스텐, 임의의 적합한 금속, 고농도 도핑된 반도체 물질, 도전성 실리사이드, 도전성 실리사이드-게르마나이드, 도전성 게르마나이드 등과 같은 임의의 적합한 물질을 포함할 수 있다. 도 2a의 실시예에서, 제 1 및 제 2 도체들(20, 22)은 레일(rail) 형상이고 서로 다른 방향들(예를 들면, 서로 실질적으로 수직하게)로 확장한다. 이외 도체 형상들 및/또는 구성들이 사용될 수 있다. 일부 실시예에서, 장치 성능을 개선하고 및/또는 장치 제조에 도움이 되게 장벽층, 부착층, 반반사 코팅들 및/또는 등(도시되지 않음)이 제 1 및/또는 제 2 도체들(20, 22)과 함께 사용될 수도 있다.

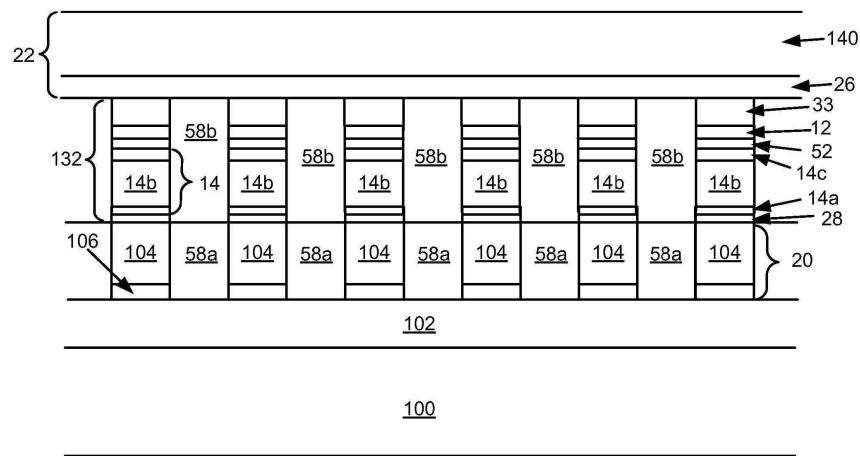

[0028] 도 2b는 도 2a의 메모리 셀(10)과 같은 복수의 메모리 셀들(10)로부터 형성된 제 1 메모리 어레이 레벨(30)의

부분의 간이화한 사시도이다. 간략성을 위해서, 탄소 소자(12), 다이오드(14), 및 장벽충들(24, 28, 33)은 별도로 도시되지 않았다. 메모리 어레이(30)는 복수의 비트라인들(제 2 도체들(22)), 및 복수의 메모리 셀들이 결합되는(도시된 바와 같이) 워드라인들(제 1 도체들(20))을 포함하는 "교차-점" 어레이이다. 복수 레벨들의 메모리와 같이, 그의 메모리 어레이 구성들이 사용될 수도 있다.

[0029] 예를 들어, 도 2c는 제 2 메모리 레벨(44) 밑에 위치된 제 1 메모리 레벨(42)을 포함하는 모노리식 3차원 어레이(40a)의 부분의 간이화한 사시도이다. 메모리 레벨들(42, 44) 각각은 교차-점 어레이로 복수의 메모리 셀들(10)을 포함한다. 당업자는 추가 층들(예를 들면, 레벨간 유전체)이 제 1 메모리 레벨(42)과 제 2 메모리 레벨(44) 사이에 있을 수 있는데, 그러나 간략성을 위해 도 2c엔 도시되지 않은 것을 이해할 것이다. 레벨들이 추가된 메모리와 같이, 다른 메모리 어레이 구성들이 사용될 수도 있다. 도 2c의 실시예에서, 다이오드들의 하부 또는 상부 상에 p-도핑된 영역을 갖는 p-i-n 다이오드들이 사용되는지 여부에 따라 모든 다이오드들은 위쪽 또는 아래쪽과 같이 동일 방향으로 "향할(point)" 수 있어, 다이오드 제조를 단순화한다.

[0030] 예를 들어, 일부 실시예에서, 메모리 레벨들은 모든 목적을 위해 전체 내용이 본 명세서에 참조로 포함된 "High-density three-dimensional memory cell" 명칭의 미국특허 6,952,030에 기술된 바와 같이 형성될 수 있다. 예를 들어, 제 1 메모리 레벨의 상측 도체는 도 2d에 도시된 대안적 3차원 어레이(40b)에 도시된 바와 같이 제 1 메모리 레벨 위에 위치된 제 2 메모리 레벨의 하측 도체들로서 사용될 수 있다. 이러한 실시예에서, 이웃한 메모리 레벨들 상에 다이오드들은 바람직하게는 모든 목적을 위해 전체 내용이 본 명세서에 참조로 포함된 2007년 3월 27일에 출원된 "LARGE ARRAY OF UPWARD POINTING P-I-N DIODES HAVING LARGE AND UNIFORM CURRENT" 명칭의 미국 특허 출원번호 11/692,151에 기술된 바와 같이 서로 대향하는 방향들로 향한다. 예를 들어, 제 1 메모리 레벨(42)의 다이오드들은 화살표(A1)로 나타낸 바와 같이 위로 향하는 다이오드들일 수 있고(예를 들면, 다이오드들의 하부에 p 영역들을 가진), 제 2 메모리 레벨(44)의 다이오드들은 화살표(A2)로 나타낸 바와 같이 아래로 향하는 다이오드들일 수 있고(예를 들면, 다이오드들의 하부에 n 영역들을 가진), 그 반대일 수도 있다.

[0031] 모노리식 3차원 메모리 어레이에는 개재되는 어떠한 기판들도 없이 복수의 메모리 레벨들이 웨이퍼와 같은 단일 기판 위에 형성되는 어레이이다. 한 메모리 레벨을 형성하는 층들은 현존 레벨 또는 레벨들의 층들 상에 직접 증착 또는 성장된다. 반대로, 적층된 메모리들은 "Thress dimensional structure memory" 명칭의 Leedy의 미국 특허 5,915,167에서와 같이, 별도의 기판들 상에 메모리 레벨들을 형성하고 메모리 레벨들을 서로 수직으로 부착함으로써 구축되었다. 기판들은 본딩 전에 얇게 하거나 메모리 레벨들로부터 제거될 수도 있는데, 그러나 메모리 레벨들이 초기에 별도의 기판들 상에 형성되기 때문에, 이러한 메모리들은 진정한 모노리식 3차원 메모리 어레이들이 아니다.

[0032] 전술한 바와 같이, 임의의 적합한 탄소계 스위칭 물질이 탄소 소자(12)로서 사용될 수 있다. 일부 실시예에서, 탄소 소자(12)를 형성하기 위해 사용되는 물질의 바람직한 저항률은 탄소 소자(12)가 온-상태에 있을 때 적어도  $1 \times 10^1$  오옴-cm이고, 탄소 소자(12)를 형성하기 위해 사용되는 물질의 바람직한 저항률은 탄소 소자(12)가 오프-상태에 있을 때 적어도  $1 \times 10^3$  오옴-cm이다.

[0033] 도 3은 도 1의 메모리 셀(10)의 실시예의 단면도이다. 특히, 도 3은 탄소 소자(12), 다이오드(14) 및 제 1 및 제 2 도체들(20, 22)을 포함하는 메모리 셀(10)을 도시한 것이다. 또한, 메모리 셀(10)은 장치 성능을 개선하고 및/또는 장치 제조를 용이하게 하기 위해서, 제 1 및/또는 제 2 도체들(20, 22)에 사용될 수 있는 부착층, 반반사 코팅층들 및/또는 등(도시되지 않음) 뿐만 아니라, 장벽충들(26, 28, 33), 실리사이드충(50), 실리사이드-형성 금속충(52), 및 유전충(58)을 포함한다.

[0034] 도 3에서, 다이오드(14)는 위쪽을 향할 수도 있고 아니면 아래쪽을 향할 수 있는 수직 p-n 또는 p-i-n 다이오드일 수 있다. 이웃한 메모리 레벨들이 도체들을 공유하는 도 2d의 실시예에서, 이웃한 메모리 레벨들은 제 1 메모리 레벨에 대해선 아래로 향하는 p-i-n 다이오드들 및 이웃한 제 2 메모리 레벨에 대해선 위로 향하는 p-i-n 다이오드들(또는 그 반대)과 같이 서로 반대되는 방향들로 향하는 다이오드들을 갖는 것이 바람직하다.

[0035] 일부 실시예에서, 다이오드(14)는 폴리실리콘, 다결정질 실리콘-게르마늄 합금, 폴리게르마늄 또는 이외 다른 적합한 물질과 같은 다결정 반도체 물질로부터 형성될 수 있다. 예를 들어, 다이오드(14)는 고농도로 도핑된 n+ 폴리실리콘 영역(14a), n+ 폴리실리콘 영역(14a) 위에 저농도로 도핑된 또는 전성(도핑이 의도적이 아닌) 폴리실리콘 영역(14b) 및 전성영역(14b) 위에 고농도 도핑된 p+ 폴리실리콘 영역(14c)을 포함할 수 있다. n+ 영역 및 p+ 영역의 위치들은 반대로 될 수 있음이 이해될 것이다.

[0036]

일부 실시예에서, n+ 폴리실리콘 영역(14a)으로부터 진성영역(14b)으로 도편트 이주를 방지 및/또는 감소시키기 위해서 얇은 게르마늄 및/또는 실리콘-게르마늄 합금층(도시되지 않음)이 n+ 폴리실리콘 영역(14a) 상에 형성될 수 있다. 이러한 층의 사용은 예를 들어, 모든 목적을 위해 전체 내용이 본 명세서에 참조로 포함된 2005년 12 월 9일에 출원된 "DEPOSITED SEMICONDUCTOR STRUCTURE TO MINIMIZE N-TYPE DOPANT DIFFUSION AND METHOD OF MAKING"(이하, "'331 출원") 명칭의 2005년 12월 9일에 출원된 미국 특허 출원번호 11/298,331에 기술되어 있다. 일부 실시예에서, 약 10 at% 이상의 게르마늄을 가진 몇백 이하의 옹스트롬의 실리콘-게르마늄 합금이 사용될 수도 있다.

[0037]

질화티탄, 질화탄탈, 질화텅스텐 등과 같은 장벽층(28)이 제 1 도체(20)와 n+ 영역(14a) 사이에 형성될 수 있다 (예를 들어, 폴리실리콘 영역 내로 금속 원자들의 이주를 방지 및/또는 감소시키기 위해서).

[0038]

다이오드(14)가 증착된 실리콘(예를 들어, 비정질 또는 다결정질)으로부터 형성된다면, 증착된 실리콘을 제조될 때 저 저항률 상태에 두기 위해서 다이오드(14) 상에 실리사이드층(50)이 형성될 수 있다. 이러한 저 저항률 상태는 증착된 실리콘을 저 저항률 상태로 전환하기 위해 큰 전압이 요구되지 않기 때문에 메모리 셀(10)이 더 용이하게 프로그래밍될 수 있게 한다. 예를 들어, 티탄 또는 코발트와 같은 실리사이드 형성 금속층(52)이 p+ 폴리실리콘 영역(14c) 상에 증착될 수도 있다. 다이오드(14)를 형성하는 증착된 실리콘을 결정화하기 위해 사용되는 후속되는 어닐링 단계(이하 기술됨) 동안에, 실리사이드 형성 금속층(52) 및 다이오드(14)의 증착된 실리콘이 상호작용하여 실리사이드 형성 금속층(52)의 전부 또는 일부를 소비하여 실리사이드층(50)을 형성한다. 일부 실시예에서, 질화층(도시되지 않음)은 실리사이드-형성 금속층(52)의 상면에 형성될 수 있다. 예를 들어, 실리사이드-형성 금속층(52)이 티탄이라면, TiN 층이 실리사이드-형성 금속층(52)의 상면에 형성될 수 있다.

[0039]

p+ 영역(14c)에 실리사이드-형성 금속층(52)의 반응에 의해서 실리사이드 영역들을 형성하기 위해 급속 열 어닐링("RTA") 단계가 수행될 수 있다. RTA는 약 1분 동안 약 540°C에서 수행될 수 있고 실리사이드-형성 금속층(52)의 전부 또는 일부를 소비하여, 실리사이드-형성 금속층(52) 및 다이오드(14)의 증착된 실리콘이 상호작용 하여 실리사이드층(50)을 형성한다. 모든 목적을 위해 전체 내용이 본 명세서에 참조로 포함된 "Memory Cell Comprising a Semiconductor Junction Diode Crystallized Adjacent to a Silicides" 명칭의 미국특허 7,176,064에 기술된 바와 같이, 티탄 및/또는 코발트와 같은 실리사이드 형성 물질은 어닐링 동안, 증착된 실리콘과 반응하여 실리사이드층을 형성한다.

[0040]

질화층이 실리사이드-형성 금속층(52)의 상면에 형성되었던 실시예에서, RTA 단계에 이어, 질화층을 습식 화학물을 사용하여 벗겨낼 수 있다. 예를 들어, 실리사이드-형성 금속층(52)이 TiN 상층을 포함한다면, 습식 화학물(예를 들어, 1:1:1 비로 암모늄, 폐록사이드, 물)이 임의의 잔류 TiN을 벗겨내기 위해 사용될 수 있다.

[0041]

도 4a 내지 도 4e에 관하여 더 상세히 기술된 적어도 일부 실시예에서, 가역 저항 스위칭 소자(12)는 약 10개의 원자층들 또는 더 적은 수의 원자들의 두께를 갖는 aC와 같은 얇은 층의 탄소계 물질을 증착함으로써 형성될 수 있다.

[0042]

다른 실시예에서, 탄소 소자(12)는 탄소계 물질의 복수의 모노층들 또는 근(near)-모노층들을 형성하기 위해 복수의 증착들을 수행하고 연속된 층을 증착하기 전에 각 층을 어닐링함으로써 형성된다. 이러한 식으로 탄소계 물질을 형성하는 것은 물질 표면에 수직한 방향으로 흐르는 전류에 대한 물질의 저항률을 증가시킬 수 있다.

[0043]

탄소 소자(12)를 형성하기 위해 2개 및 약 10개의 모노층들 또는 근-모노층들간에 증착되는 것이 바람직하다. 탄소 소자(12)의 총 두께는 약 1 옹스트롬 내지 약 800 옹스트롬이고 바람직하게는 약 5 옹스트롬 내지 100 옹스트롬이다.

[0044]

특정 실시예에서, 탄소계 스위칭 물질은 1000 옹스트롬 막에 대해 시트 저항("Ω/□" 또는 "오옴/스퀘어")을 약  $1 \times 10^5 \Omega/\square$  내지 약  $1 \times 10^8 \Omega/\square$ , 더 바람직하게는 약  $1 \times 10^4 \Omega/\square$  또는 그 이상을 나타내게 형성될 수 있다. 유사하게, 일부 실시예들은 나노결정의 aC 막을 포함한다. 이외 막 파라미터들 및 특징들도 추구될 수 있다(예를 들어, 증착율, 막 두께, 시트 저항/저항률 등의 대안적 값들).

[0045]

질화티탄, 질화탄탈, 질화텅스텐 등과 같은 장벽층(33)이 탄소 소자(12)와 제 2 도체(22) 사이에 형성될 수 있다. 제 2 도체(22)는 도 3에 도시된 바와 같이, 장벽층(33) 위에 형성될 수 있다. 제 2 도체(22)는 하나 이상의 장벽 및/또는 부착층들(25) 및 도전층(140)을 포함할 수 있다.

[0046] 메모리 셀을 위한 예시적인 제조 공정

이제 도 4a 내지 도 4e를 참조하여, 이 발명에 따라 메모리 레벨을 형성하는 방법이 기술된다. 특히, 도 4a 내지 도 4e는 도 3의 메모리 셀들(10)을 포함하는 메모리 레벨을 형성하는 방법을 도시한 것이다. 이하 기술되는 바와 같이, 제 1 메모리 레벨은 각각이 스티어링 소자 및 이 스티어링 소자에 결합된 탄소계 가역 저항 스위칭 소자를 포함하는 복수의 메모리 셀들을 포함한다. 추가 메모리 레벨들이 제 1 메모리 레벨 위에 제조될 수도 있다(도 2c 내지 도 2d를 참조하여 앞에서 기술된 바와 같이).

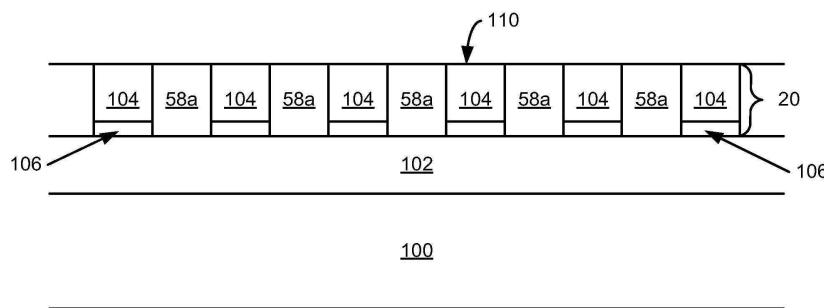

도 4a를 참조하면, 기판(100)은 이미 몇 가지 처리 단계들을 거친 것으로 도시되었다. 기판(100)은 실리콘, 게르마늄, 실리콘-게르마늄, 도핑되지 않은, 도핑된, 벌크, 실리콘-온-인슐레이터(SOI) 또는 이외 추가 회로를 가진 또는 없는 기판과 같은 임의의 적합한 기판일 수 있다. 예를 들어, 기판(100)은 하나 이상의 n-웰 또는 p-웰 영역들(도시되지 않음)을 포함할 수 있다.

[0049] 격리층(102)이 기판(100) 상에 형성된다. 일부 실시예에서, 격리층(102)은 이산화규소, 질화규소, 실리콘 옥시질화물층, 또는 이외 어떤 다른 적합한 절연층일 수 있다.

[0050] 격리층(102)의 형성에 이어, 부착층(104)이 격리층(102) 상에 형성된다(예를 들어, 물리기상증착 또는 또 다른 방법에 의해). 예를 들어, 부착층(104)은 약 20 내지 약 500 옹스트롬, 바람직하게 약 100 옹스트롬의 질화티탄, 또는 질화탄탈, 질화텅스텐과 같은 또 다른 적합한 부착층, 하나 이상의 부착층의 조합 등일 수 있다. 다른 부착층 물질들 및/또는 두께들이 사용될 수 있다. 일부 실시예에서, 부착층(104)은 선택적일 수 있다.

[0051] 부착층(104)의 형성 후에, 도전층(106)이 부착층(104) 상에 증착된다. 도전층(106)은 임의의 적합한 방법에 의해 증착되는(예를 들어, 화학 증기 증착("CVD"), 물리기상증착("PVD" 등) 텅스텐 또는 또 다른 적합한 금속, 고농도 도핑된 반도체 물질, 도전성 실리사이드, 도전성 실리사이드-게르마나이드, 도전성 게르마나이드 등과 같은 임의의 적합한 도전성 물질을 포함할 수 있다. 적어도 일실시예에서, 도전층(106)은 약 200 내지 약 2500 옹스트롬의 텅스텐을 포함할 수 있다. 이외 다른 도전층 물질들 및/또는 두께들이 사용될 수도 있다.

[0052] 도전층(106)의 형성 후에, 접착층(104) 및 도전층(106)이 패터닝되고 에칭된다. 예를 들어, 부착층(104) 및 도전층(106)은 소프트 또는 하드 마스크를 사용한 통상의 리소그래피 기술, 및 습식 또는 건식 에칭 가공을 사용하여 패터닝되고 에칭될 수 있다. 적어도 일실시예에서, 실질적으로 평행하고, 실질적으로 공면(co-planar)의 도체들(20)을 형성하기 위해 부착층(104) 및 도전층(106)이 패터닝되고 에칭된다. 제 1 도체들(20)의 폭들 및/또는 제 1 도체들(20) 사이의 간격들은 다른 도체 폭들 및/또는 간격들이 사용될 수도 있을지도, 약 200 내지 약 2500 옹스트롬의 범위이다.

[0053] 제 1 도체들(20)이 형성된 후에, 제 1 도체들(20) 사이에 보이드들을 채우기 위해서 유전층(58a)이 기판(100) 상에 형성된다. 예를 들어, 근사적으로 3000 내지 7000 옹스트롬의 이산화규소가 기판(100) 상에 증착되고 평탄한 표면(110)을 형성하기 위해 화학기계식 연마 또는 애치백 공정을 사용하여 평탄화될 수 있다. 평탄한 표면(110)은 유전물질에 의해 분리된(도시된 바와 같이) 제 1 도체들(20)의 노출된 상면들을 포함한다. 질화규소, 실리콘 옥시질화물, 저 K 유전체 등과 같은 그외 유전물질, 및/또는 그외 유전층 두께들이 사용될 수 있다. 바람직한 저 K 유전체는 탄소가 도핑된 산화물, 실리콘 카본층 등을 포함한다.

[0054] 발명의 다른 실시예에서, 유전층(58a)이 형성되고, 패터닝되고 에칭되어 도체들(20)을 위한 개구들 또는 보이드들을 생성하는 다마센 공정을 사용하여 제 1 도체들(20)이 형성될 수 있다. 이어서 개구들 또는 보이드들은 부착층(104) 및 도전층(106)(및/또는 필요하다면 도전성 시드, 도전성 충전 및/또는 장벽층)으로 채워질 수 있다. 부착층(104) 및 도전층(106)은 이어서 평탄한 표면(110)을 형성하기 위해 평탄화될 수 있다. 이러한 실시예에서, 부착층(104)은 각 개구 또는 보이드의 바닥 및 측벽들을 정렬시킨다.

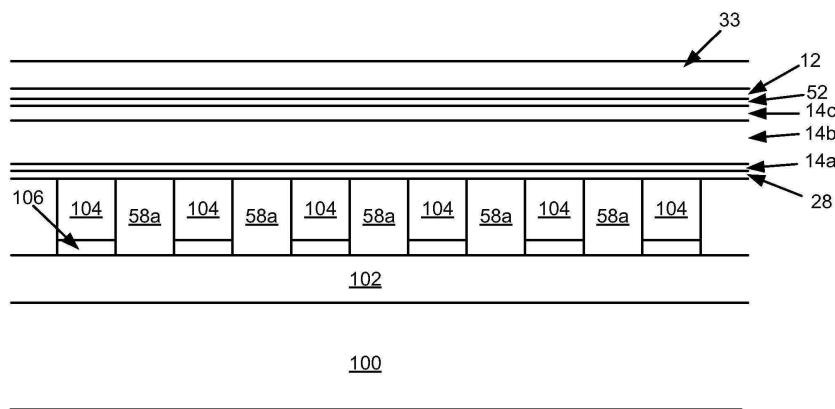

[0055] 평탄화에 이어, 각 메모리 셀의 다이오드 구조들이 형성된다. 도 4b를 참조하면, 장벽층(28)이 기판(100)의 평탄화된 상면(110) 상에 형성된다. 장벽층(28)은 약 20 내지 약 500 옹스트롬, 바람직하게 약 100 옹스트롬의 질화티탄, 또는 질화탄탈과 같은 또 다른 적합한 장벽층, 질화텅스텐, 하나 이상의 장벽층의 조합, 티탄/질화티탄, 탄탈/질화탄탈 또는 텅스텐/질화텅스텐 적층 등과 같은 다른 층들과 조합한 장벽층들일 수 있다. 이외의 장벽층 물질들 및/또는 두께들이 사용될 수 있다.

[0056] 장벽층(28)의 증착 후에, 각 메모리 셀의 다이오드를 형성하기 위해 사용되는 반도체 물질의 증착이 시작된다(예를 들어, 도 1 및 도 3에서 다이오드(14)). 각각의 다이오드는 앞서 기술된 바와 같이 수직 p-n 또는 p-i-n 다이오드일 수 있다. 일부 실시예에서, 각 다이오드는 폴리실리콘, 폴리실리콘-게르마늄 합금, 게르마늄 또는

이외 어떤 적합한 물질과 같은 다결정질 반도체 물질로부터 형성된다. 편의상, 폴리실리콘 하향 다이오드의 형성이 여기에서 기술된다. 이외의 물질 및/또는 다이오드 구성들이 사용될 수 있음이 이해될 것이다.

[0057] 도 4b를 참조하면, 장벽층(28)의 형성에 이어, 고농도 도핑된 n+ 실리콘층(14a)이 장벽층(28) 상에 증착된다. 일부 실시예에서, n+ 실리콘층(14a)은 증착시 비정질 상태에 있다. n+ 실리콘층(14a)을 증착하기 위해 CVD 또는 또 다른 적합한 공정이 사용될 수 있다. 적어도 일 실시예에서, 예를 들어 약 100 내지 약 1000 옹스트롬, 바람직하게는 약 100 옹스트롬의, 약  $10^{21} \text{ cm}^{-3}$ 의 도핑 농도를 갖는 인 또는 비소가 도핑된 실리콘의 n+ 실리콘층(14a)이 형성될 수 있다. 이외의 층 두께, 도편트 유형들 및/또는 도핑 농도들이 사용될 수 있다. 예를 들어 증착 동안 도너 기체를 흘림으로써, n+ 실리콘층(14a)이 인 시튜로 도핑될 수 있다. 이외의 도핑 방법들이 사용될 수도 있다(예를 들어, 주입).

[0058] n+ 실리콘층(14a)의 증착 후에, 저농도 도핑된, 진성 및/또는 비의도적 도핑된 실리콘층(14b)이 n+ 실리콘층(14a) 상에 형성될 수 있다. 일부 실시예에서, 진성 실리콘층(14b)은 증착시 비정질 상태에 있다. 다른 실시예에서, 진성 실리콘층(14b)은 증착시 다결정질 상태에 있다. 진성 실리콘층(14b)을 증착하기 위해 CVD 또는 또 다른 적합한 증착방법이 사용될 수 있다. 적어도 일 실시예에서, 진성 실리콘층(14b)은 약 500 내지 약 4800 옹스트롬, 바람직하게는 약 2500 옹스트롬 두께일 수 있다. 이외 진성층의 두께들이 사용될 수 있다.

[0059] n+ 실리콘층(14a)으로부터 진성 실리콘층(14b) 내로 도편트 이주를 방지 및/또는 감소시키기 위해서(앞서 포함시킨, '331 출원에 기술된 바와 같이) 얇은(예를 들어, 몇 백 이하의 옹스트롬) 게르마늄 및/또는 실리콘-게르마늄 합금층(도시되지 않음)이 진성 실리콘층(14a)의 증착에 앞서 n+ 실리콘층(14a) 상에 형성될 수 있다.

[0060] 고농도 도핑된 p형 실리콘이 이온주입에 의해 증착되고 도핑되거나, p+ 실리콘층(14c)을 형성하기 위해 증착 동안 인 시튜로 도핑된다. 예를 들어, 진성 실리콘층(14b) 내에 소정 깊이에 보론을 주입하기 위해 블랭킷 p+ 주입이 사용될 수 있다. 바람직한 주입가능한 분자 이온들은  $\text{BF}_2$ ,  $\text{BF}_3$ , B 등을 포함한다. 일부 실시예에서, 약 1 내지  $5 \times 10^{15} \text{ ions/cm}^2$ 의 주입 도우즈가 사용될 수 있다. 이외 주입 종들 및/또는 도우즈들이 사용될 수 있다. 또한, 일부 실시예에서, 확산공정이 사용될 수도 있다. 적어도 일 실시예에서, 결과적인 p+ 실리콘 영역들(14c)은 약 100 내지 700 옹스트롬의 깊이를 갖는데, 그러나 이외 p+ 실리콘 영역 크기들이 사용될 수도 있다.

[0061] p+ 실리콘층(14c)의 형성에 이어, 실리사이드-형성 금속층(52)이 p+ 실리콘층(14c) 상에 증착된다. 바람직한 실리사이드-형성 금속들은 스펀터 또는 아니면 증착된 티탄 또는 코발트를 포함한다. 일부 실시예에서, 실리사이드-형성 금속층(52)은 약 10 내지 약 200 옹스트롬, 바람직하게는 약 20 내지 약 50 옹스트롬, 더 바람직하게는 약 20 옹스트롬의 두께를 갖는다. 이외 실리사이드-형성 금속층 물질들 및/또는 두께들이 사용될 수 있다. 질화층(도시되지 않음)이 실리사이드-형성 금속층(52) 위에 형성될 수 있다.

[0062] 실리사이드-형성 금속층(52)의 형성에 이어, 실리사이드-형성 금속층(52)의 전부 또는 일부를 소비하면서, 실리사이드층(50)을 형성하기 위해 약 1분 동안 약 540°C에서 RTA 단계가 수행될 수 있다. RTA 단계에 이서, 실리사이드-형성 금속층(52)으로부터 임의의 잔류한 질화층이 위에 기술된 바와 같이, 그리고 이 기술에 공지된 바와 같이, 습식 화학물을 사용하여 벗겨낼 수 있다.

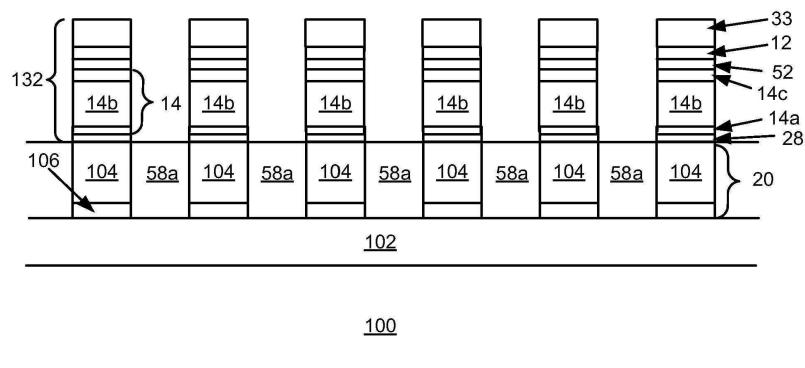

[0063] RTA 단계 및 질화물 제거 단계에 이어, 탄소 소자(12)가 실리사이드-형성 금속층(52) 상에 형성된다. 여기에 기술된 적어도 일부 실시예에서, aC와 같은 탄소계 가역 저항률 스위칭 물질을 증착시켜 탄소 소자(12)가 형성된다. 대안적 실시예에서, 제한이 없이 그라펜, 흑연 등을 포함한, 다른 탄소계 물질들이 사용될 수 있다. 각각의 물질에 대해서,  $\text{sp}^2$ (이중 탄소-탄소 본드들) 대  $\text{sp}^3$ (단일 탄소-탄소 본드들)의 비는 D 및 G 밴드들을 평가함으로써 예를 들어 라만 스펙트로스코피를 통해 결정될 수 있다. 사용 가능한 물질들의 범위는  $\text{M}_x\text{N}_z$ 와 같은 비에 의해 확인될 수 있는데, M은  $\text{sp}^3$  물질이고 N은  $\text{sp}^2$  물질이며, y 및 z은 0 내지 1의 임의의 분수 값이며  $y + z = 1$ 이다.

[0064] 위에 논의한 바와 같이, 탄소 소자(12)는 소수의 원자층들만의 두께(예를 들어, 근사적으로 10개의 원자층들 또는 더 적은 수의 원자층들)를 갖는 얇은 aC 층을 증착함으로써 형성될 수 있다. 연구자들은 이러한 식으로 탄소계 물질을 증착하는 것은 탄소계 물질에 탄소-탄소 링 구조들의 형성을 용이하게 함을 확인하였다. 예를 들어, 흑연 물질에서 전형인  $\text{sp}^2$  탄소-탄소 pi 본드들의 형성이 용이해질 수 있다.

[0065] 예를 들어, 탄소 소자(12)는 수소와 헥산의 혼합물을 사용하여, 약 300°C 내지 900°C, 바람직하게는 약 600°C 미만, 더 바람직하게는 약 450°C 미만의 가공 온도에서 수행되는, PECVD와 같은, 플라즈마 인핸스트 분해

(decomposition) 및 증착 절차를 사용하여 형성될 수 있다. 다른 실시예에서, 제한없이, 타겟으로부터 스퍼터 증착, CVD, 아크 방전 기술들 및 레이저 제거(ablation)을 포함한, 그외 증착 방법들이 사용될 수 있다.

[0066] 다른 실시예에서, 탄소 소자(12)는 복수의 모노층들 또는 근(near)-모노층들을 형성하기 위해 aC 물질의 복수의 증착들을 수행하고 연속된 층을 증착하기 전에 각각의 모노층 또는 근-모노층을 어닐링함으로써 형성될 수 있다. 이러한 식으로 탄소계 물질을 형성하는 것은 물질 표면에 수직한 방향으로 흐르는 전류에 대한 물질의 저항률을 증가시킬 수 있다.

[0067] 각각의 모노층 또는 근-모노층은 연속된 층의 증착 전에 비-산화(non-oxidizing) 분위기에서 약 250°C 내지 약 850°C, 더 일반적으로 약 350°C 내지 약 650°C의 가공 온도에서 어닐링될 수 있다. 적어도 일 실시예에서 각 모노층 또는 근-모노층은 연속된 층의 증착 전에 비-산화 분위기에서 약 600°C의 가공 온도에서 어닐링될 수 있다. 각각의 층을 어닐링함으로써 평면내 탄소 본드들의 형성이 용이해지고 평면외 탄소 본드들의 수가 제한되어 물질 표면에 수직한 방향으로 aC 물질의 저항률이 증가한다. 이러한 식으로 aC 물질의 저항률의 증가는 aC 물질로부터 형성된 가역-저항 스위칭 소자(12)의 저항을 증가시키고, 그럼으로써 가역-저항 스위칭 소자(12)를 통하는 초기 전류 흐름을 감소시킨다.

[0068] 가역 저항 스위칭 소자(12)를 형성하기 위해 2개 및 약 10개의 aC 물질간에 증착되는 것이 바람직하다. 가역 저항 스위칭 소자(12)의 총 두께는 약 1 옹스트롬 내지 약 800 옹스트롬이고 바람직하게는 약 5 옹스트롬 내지 100 옹스트롬이다.

[0069] 장벽층(33)이 가역 저항 스위칭 소자(12) 상에 형성된다. 장벽층(33)은 약 5 내지 약 800 옹스트롬, 바람직하게 약 100 옹스트롬의 질화티탄, 또는 질화탄탈과 같은 또 다른 적합한 장벽층, 질화텅스텐, 하나 이상의 장벽층의 조합, 티탄/질화티탄, 탄탈/질화탄탈 또는 텡스텐/질화텅스텐 적층 등과 같은 다른 층들과 조합한 장벽층들일 수 있다. 이외의 장벽층 물질들 및/또는 두께들이 사용될 수 있다.

[0070] 도 4c에 도시된 바와 같이, 장벽층(33), 가역 저항 스위칭 소자(12), 실리사이드-형성 금속층(52), 다이오드 층들(14a ~ 14c) 및 장벽층(28)이 패터닝 및 에칭되어 필라들(132)을 형성한다. 필라들(132)은, 각 필라(132)가 도체(20) 위에 형성되며, 밑에 도체들(20)과 약 동일한 퍼치 및 약 동일한 폭을 가질 수 있다. 얼마간의 오정렬이 용인될 수 있다.

[0071] 예를 들어, 표준 포토리소그래피 기술들을 사용하여 포토레지스트가 증착되고, 패터닝될 수 있고, 층들(28, 14a ~ 14c, 52, 12, 33)이 에칭될 수 있고, 이어서 포토레지스트가 제거될 수 있다. 대안적으로, 어떤 다른 물질, 예를 들어 이산화규소 하드 마스크가 맨위에 하부 반반사 코팅("BARC")를 갖고 장벽층(33) 위에 형성될 수 있고, 이어서 패터닝되고 에칭될 수 있다. 유사하게, 유전 반반사 코팅("DARC")이하드 마스크로서 사용될 수도 있다.

[0072] 필라들(132)은 임의의 적합한 마스킹 및 에칭 공정을 사용하여 형성될 수 있다. 예를 들어, 표준 포토리소그래피 기술들을 사용하여 층들(28, 14a ~ 14c, 52, 12, 33)이 약 1 내지 약 1.5 마이크론, 더 바람직하게는 약 1.2 내지 약 1.4 마이크론의 포토레지스터("PR")을 사용하여 패터닝될 수 있다. 더 작은 임계적 치수들 및 기술 노드들엔 더 얇은 PR 층들이 사용될 수 있다. 일부 실시예에서, 패턴 전사를 개선하고 에칭 동안 하지의 층들을 보호하기 위해서 PR 층 밑에 산화물 하드 마스크가 사용될 수 있다.

[0073] 어떤 적합한 에칭 화학물, 및 임의의 적합한 에칭 파라미터, 유속, 챔버 압력, 파워 레벨, 공정온도, 및/또는 에칭율들이 사용될 수 있다. 일부 실시예에서, 장벽층(33), 가역 저항 스위칭 소자(12), 실리사이드-형성 금속층(52), 다이오드 층들(14a ~ 14c) 및 장벽층(28)이 단일 에칭 단계를 사용하여 패터닝될 수 있다. 다른 실시예에서, 별도의 에칭 단계들이 사용될 수도 있다. 에칭은 유전층(58a)까지 아래로 진행된다. 이러한 에칭된 필라들(132)은 거의 수직한 측면들을 가지며 가역 저항 스위칭 소자(120)의 언더컷이 거의 또는 전혀 없는 것으로 관찰되었다.

[0074] 에칭 후에 필라들(132)은 희석 플루오르화수소/황산 세정을 사용하여 세정될 수 있다. 이러한 세정은, PR 애싱(ashing)이 에칭 전에 수행되든간에, 몬타나에 칼리스펠의 세미톨로부터 입수될 수 있는 레이더 툴과 같은 임의의 적합한 세정 도구에서 수행될 수 있다. 에칭 후 세정은 약 60초 동안 극-희석 황산(예를 들어, 약 1.5 내지 1.8 wt%) 및 60초 동안 극-희석 플루오르화수소("HF")산(예를 들어, 0.4 내지 0.6 wt%)를 포함할 수 있다. 메가 소닉스가 사용될 수도 있고 사용되지 않을 수도 있다.

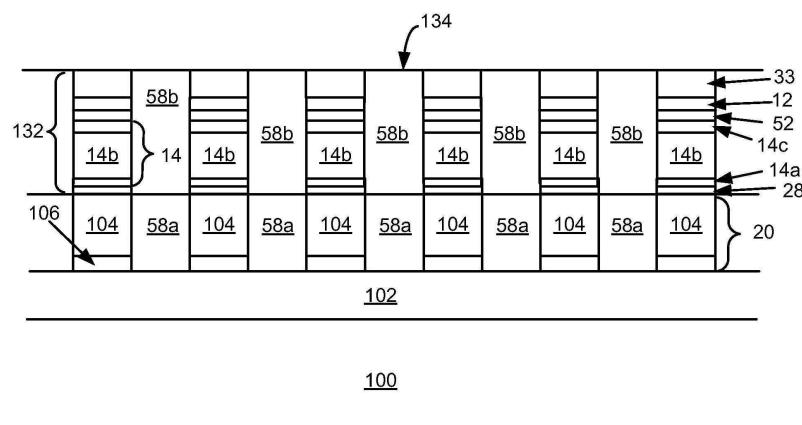

[0075] 필라들(132)이 세정된 후에, 필라들(132) 사이에 보이드들을 채우기 위해서 유전층(58b)이 필라들(132) 상에 증착될 수 있다. 예를 들어, 근사적으로 200 내지 7000 옹스트롬의 이산화규소가 증착되고 과잉의 유전물질(58b)을 제거하고 평탄한 표면(134)을 형성하기 위해 화학기계식 연마 또는 에치백 공정을 사용하여 평탄화됨으로써,

도 4d에 도시된 구조가 될 수 있다. 평탄한 표면(134)은 유전물질(58b)에 의해 분리된(도시된 바와 같이) 필라들(132)의 노출된 상면들을 포함한다. 질화규소, 실리콘 옥시질화물, 저 K 유전체 등과 같은 그외 유전물질, 및 /또는 그외 유전층 두께들이 사용될 수 있다. 바람직한 저 K 유전체는 탄소가 도핑된 산화물, 실리콘 탄소층 등을 포함한다.

[0076] 도 4e를 참조하면, 제 1 도체들(20)의 형성과 유사한 방식으로 필라들(132) 위에 제 2 도체들(22)이 형성될 수 있다. 예를 들어, 일부 실시예에서, 제 2 도체들(22)을 형성하기 위해 사용되는 도전층(140)의 증착에 앞서 필라들(132) 위에 하나 이상의 장벽층들 및/또는 부착층들(26)이 형성될 수 있다.

[0077] 도전층(140)은 임의의 적합한 방법에 의해 증착되는(예를 들어, CVD, PVD 등) 텅스텐, 또 다른 적합한 금속, 고농도 도핑된 반도체 물질, 도전성 실리사이드, 도전성 실리사이드-게르마나이드, 도전성 게르마나이드 등과 같은 임의의 적합한 도전성 물질로부터 형성될 수 있다. 이외 도전층 물질들이 사용될 수 있다. 장벽층들 및/또는 부착층들(26)은 질화티탄 또는 질화탄탈과 같은 또 다른 적합한 층, 질화텅스텐, 하나 이상의 층의 조합, 또는 이외 어떤 다른 적합한 물질(들)을 포함할 수 있다. 증착된 도전층(140) 및 장벽 및/또는 부착층(26)이 패터닝 및 에칭되어 제 2 도체들(22)을 형성할 수 있다. 적어도 일 실시예에서, 제 2 도체들(22)은 제 1 도체들(20)과는 다른 방향으로 확장하는 실질적으로 평행하고, 실질적으로 공면의 도체들이다.

[0078] 발명의 다른 실시예에서, 제 2 도체들(22)은 유전층이 형성되고, 패터닝되고 에칭되어 도체들(22)을 위한 개구들 또는 보이드들을 생성하는 다마센 공정을 사용하여 형성될 수 있다. 개구들 또는 보이드들은 부착층(26) 및 도전층(140)(및/또는 필요하다면 도전성 시드, 도전성 충전 및/또는 장벽층)으로 채워질 수 있다. 부착층(26) 및 도전층(140)은 이어서 평탄한 표면을 형성하기 위해 평탄화될 수 있다.

[0079] 제 2 도체들(22)의 형성에 이어, 결과적인 구조는 증착된 반도체 물질의 다이오들(14)을 결정화하기 위해서{및/또는 p+ 영역(14c)에 실리사이드-형성 금속층(52)의 반응에 의해 실리사이드 영역들을 형성하기 위해서} 어닐링 될 수 있다. 티탄 실리사이드 및 코발트 실리사이드의 격자 간격은 실리콘의 격자 간격에 가깝고, 실리사이드 층들(50)은 증착된 실리콘의 결정화될 때(예를 들어, 실리사이드 층(50)은 약 600 ~ 800°C의 온도에서 어닐링 동안 실리콘 다이오드(14)의 결정 구조를 향상시킨다) 인접한 증착된 실리콘에 대해 "결정화 템플레이트" 또는 "시드"로서 작용할 수 있는 것으로 보인다. 그럼으로써 더 낮은 저항률의 다이오드 물질이 제공된다. 실리콘-게르마늄 합금 및/또는 게르마늄 다이오드들에 대해서도 유사한 결과들이 달성될 수 있다.

[0080] 이에 따라, 적어도 일 실시예에서, 약 600 내지 800°C의 온도, 더 바람직하게는 약 650 내지 750°C의 온도에서 질소에서 약 10 내지 약 2분 동안 결정화 어닐링 수행될 수 있다. 다른 어닐링 시간, 온도 및/또는 환경이 사용될 수 있다.

[0081] 당업자들은 본 발명에 따른 대안적 메모리 셀들이 다른 유사한 기술들로 제조될 수 있음을 알 것이다. 예를 들어, 다이오드(14) 아래 가역 저항 스위칭 소자(12)를 포함하는 메모리 셀들이 형성될 수 있다.

[0082] 전술한 바는 발명의 단지 바람직한 실시예들을 개시한다. 발명의 범위 내에 드는 위에 개시된 장치 및 방법들의 수정예들은 당업자들에게 쉽게 명백하게 될 것이다.

[0083] 따라서, 본 발명이 이의 바람직한 실시예에 관련하여 개시되었지만, 이외 실시예들은 다음 청구항들에 정의된 바와 같은 발명의 정신 및 범위 내에 포함됨을 알아야 한다.

도면

도면1

도면2a

도면2b

도면2c

도면2d

## 도면3

## 도면4a

## 도면4b

## 도면4c

## 도면4d

## 도면4e