(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6141908号

(P6141908)

(45) 発行日 平成29年6月7日(2017.6.7)

(24) 登録日 平成29年5月12日(2017.5.12)

(51) Int.Cl.

F 1

H02M 3/28 (2006.01)

H02M 3/335 (2006.01)H02M 3/28

H02M 3/335Q

E

請求項の数 6 (全 13 頁)

(21) 出願番号 特願2015-101166 (P2015-101166)

(22) 出願日 平成27年5月18日 (2015.5.18)

(65) 公開番号 特開2016-220347 (P2016-220347A)

(43) 公開日 平成28年12月22日 (2016.12.22)

審査請求日 平成29年2月16日 (2017.2.16)

早期審査対象出願

(73) 特許権者 390010308

東芝デベロップメントエンジニアリング株

式会社

神奈川県川崎市幸区堀川町 580番地

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100103034

弁理士 野河 信久

(74) 代理人 100075672

弁理士 峰 隆司

(74) 代理人 100153051

弁理士 河野 直樹

(74) 代理人 100140176

弁理士 砂川 克

最終頁に続く

(54) 【発明の名称】電流共振型DC-DCコンバータ

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のトランジスタと、前記第1のトランジスタに直列接続される第2のトランジスタと、第3のトランジスタと、前記第3のトランジスタに直列接続される第4のトランジスタとを含み、前記第1のトランジスタおよび前記第2のトランジスタと前記第3のトランジスタおよび前記第4のトランジスタとが並列に配置される、スイッチング回路と、

前記第1のトランジスタおよび前記第2のトランジスタに共通に接続される第1の入力端子と、前記第3のトランジスタおよび前記第4のトランジスタに共通に接続される第2の入力端子とを備える共振回路と、

(a) 第1の制御モードにおいて、前記第1のトランジスタを前記共振回路の出力電圧または出力電流に基づく駆動周波数でON/OFFし、前記第2のトランジスタを前記第1のトランジスタと交互にON/OFFし、前記第3のトランジスタを前記第1のトランジスタのON/OFFタイミングと略同一のタイミングで当該第1のトランジスタと逆の状態に切り替え、前記第4のトランジスタを前記第3のトランジスタと交互にON/OFFし、(b) 第2の制御モードにおいて、前記第1のトランジスタをON/OFFし、前記第2のトランジスタを前記第1のトランジスタのON/OFFと交互にON/OFFし、前記第3のトランジスタを前記第1のトランジスタのON/OFFタイミングから前記共振回路の出力電圧または出力電流に基づく位相シフト量だけずれたタイミングで当該第1のトランジスタと逆の状態に切り替え、前記第4のトランジスタを前記第3のトランジスタと交互にON/OFFする駆動回路と

10

20

を具備し、

前記駆動回路は、前記第1の制御モードでの動作時に前記共振回路の出力電圧または出力電流に基づく駆動周波数が第1の閾値以上になると前記第2の制御モードに切り替わり

、前記第1の閾値は、前記スイッチング回路の入力電圧が高いほど大きな値へと動的に変化する、

電流共振型DC-D<sub>C</sub>変換器。

【請求項2】

第1のトランジスタと、前記第1のトランジスタに直列接続される第2のトランジスタと、第3のトランジスタと、前記第3のトランジスタに直列接続される第4のトランジスタとを含み、前記第1のトランジスタおよび前記第2のトランジスタと前記第3のトランジスタおよび前記第4のトランジスタとが並列に配置される、スイッチング回路と、

10

前記第1のトランジスタおよび前記第2のトランジスタに共通に接続される第1の入力端子と、前記第3のトランジスタおよび前記第4のトランジスタに共通に接続される第2の入力端子とを備える共振回路と、

(a) 第1の制御モードにおいて、前記第1のトランジスタを前記共振回路の出力電圧または出力電流に基づく駆動周波数でON/OFFし、前記第2のトランジスタを前記第1のトランジスタと交互にON/OFFし、前記第3のトランジスタを前記第1のトランジスタのON/OFFタイミングと略同一のタイミングで当該第1のトランジスタと逆の状態に切り替え、前記第4のトランジスタを前記第3のトランジスタと交互にON/OFFし、(b) 第2の制御モードにおいて、前記第1のトランジスタをON/OFFし、前記第2のトランジスタを前記第1のトランジスタのON/OFFと交互にON/OFFし、前記第3のトランジスタを前記第1のトランジスタのON/OFFタイミングから前記共振回路の出力電圧または出力電流に基づく位相シフト量だけずれたタイミングで当該第1のトランジスタと逆の状態に切り替え、前記第4のトランジスタを前記第3のトランジスタと交互にON/OFFする駆動回路と

20

を具備し、

前記駆動回路は、前記第1の制御モードでの動作時に前記共振回路の出力電圧または出力電流に基づく駆動周波数が第1の閾値以上になると前記第2の制御モードに切り替わり

30

、前記第1の閾値は、前記共振回路の出力電流が大きいほど小さな値へと動的に変化する、

電流共振型DC-D<sub>C</sub>変換器。

【請求項3】

前記駆動回路は、前記第2の制御モードでの動作時に前記共振回路の出力電圧または出力電流に基づく位相シフト量が第2の閾値以下となると前記第1の制御モードに切り替わる、請求項1または請求項2に記載の電流共振型DC-D<sub>C</sub>変換器。

【請求項4】

前記第2の閾値は、前記スイッチング回路の入力電圧が高いほど小さな値へと動的に変化する、請求項3記載の電流共振型DC-D<sub>C</sub>変換器。

40

【請求項5】

前記第2の閾値は、前記共振回路の出力電流が大きいほど大きな値へと動的に変化する、請求項3記載の電流共振型DC-D<sub>C</sub>変換器。

【請求項6】

前記第2の閾値は、前記電流共振型DC-D<sub>C</sub>変換器における入力電力から当該電流共振型DC-D<sub>C</sub>変換器における出力電力を差し引いた損失が大きいほど大きな値へと動的に変化する、請求項3記載の電流共振型DC-D<sub>C</sub>変換器。

【発明の詳細な説明】

【技術分野】

【0001】

50

実施形態は、電流共振型 DC - DC コンバータに関する。

【背景技術】

【0002】

電流共振型 DC ( Direct Current ) - DC コンバータは、典型的には、スイッチング回路の駆動周波数を制御することにより、安定した出力電圧を負荷に供給する。しかしながら、駆動周波数の制御による出力電圧の可変範囲には限界があり、入力電圧を極端に大きくまたは小さく変換することは困難である。換言すれば、このような電流共振型 DC - DC コンバータは、入力電圧の許容範囲が狭いという問題がある。故に、実用上は、入力電圧が許容範囲を逸脱しないようにするために、例えば PWM ( Pulse Width Modulation ) 制御の定電圧 DC - DC コンバータが電流共振型 DC - DC コンバータの前段に設けられてきた。このような付加的な機構は、全体的なコストおよびサイズを増加させると共に電力変換効率も低下させることになる。10

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2012-235621号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

実施形態は、電流共振型 DC - DC コンバータの入力電圧の許容範囲を拡大することを目的とする。20

【課題を解決するための手段】

【0005】

実施形態は、スイッチング回路と、共振回路と、駆動回路とを含む。スイッチング回路は、第1のトランジスタと、第1のトランジスタに直列接続される第2のトランジスタと、第3のトランジスタと、第3のトランジスタに直列接続される第4のトランジスタとを含み、第1のトランジスタおよび第2のトランジスタと第3のトランジスタおよび第4のトランジスタとが並列に配置される。共振回路は、第1のトランジスタおよび第2のトランジスタに共通に接続される第1の入力端子と、第3のトランジスタおよび第4のトランジスタに共通に接続される第2の入力端子とを備える。駆動回路は、(a) 第1の制御モードにおいて、第1のトランジスタを共振回路の出力電圧または出力電流に基づく駆動周波数で ON / OFF し、第2のトランジスタを第1のトランジスタと交互に ON / OFF し、第3のトランジスタを第1のトランジスタの ON / OFF タイミングと略同一のタイミングで当該第1のトランジスタと逆の状態に切り替え、第4のトランジスタを第3のトランジスタと交互に ON / OFF し、(b) 第2の制御モードにおいて、第1のトランジスタを ON / OFF し、第2のトランジスタを第1のトランジスタの ON / OFF と交互に ON / OFF し、第3のトランジスタを第1のトランジスタの ON / OFF タイミングから共振回路の出力電圧または出力電流に基づく位相シフト量だけずれたタイミングで当該第1のトランジスタと逆の状態に切り替え、第4のトランジスタを第3のトランジスタと交互に ON / OFF する。3040

【図面の簡単な説明】

【0006】

【図1】第1の実施形態に係る電流共振型 DC - DC コンバータを例示する回路図。

【図2】電流共振型 DC - DC コンバータの基本回路を例示する回路図。

【図3】図2の電流共振型 DC - DC コンバータに含まれる LCR 共振回路の利得の周波数特性を例示するグラフ。

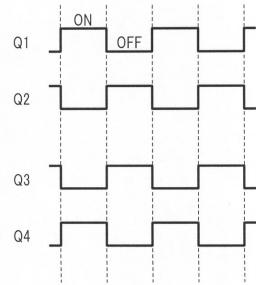

【図4】図1のFET 駆動回路が第1の制御モードで動作する場合に各 FET のゲート端子に供給される制御信号を例示するタイミングチャート。

【図5】図1のFET 駆動回路が第1の制御モードで動作する場合に LCR 共振回路に入力される電圧の波形を例示するグラフ。50

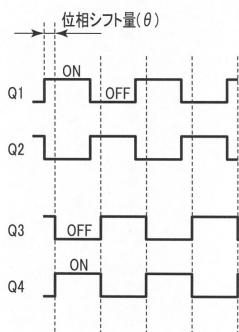

【図6】図1のFET駆動回路が第2の制御モードで動作する場合に各FETのゲート端子に供給される制御信号を例示するタイミングチャート。

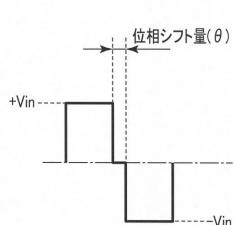

【図7】図1のFET駆動回路が第2の制御モードで動作する場合にLCR共振回路に入力される電圧の波形を例示するグラフ。

【発明を実施するための形態】

【0007】

以下、図面を参照しながら実施形態の説明が述べられる。尚、以降、説明済みの要素と同一または類似の要素には同一または類似の符号が付され、重複する説明は基本的に省略される。

【0008】

10

(第1の実施形態)

図2には、電流共振型DC-DCコンバータの基本回路が例示される。図2の基本回路は、ハーフブリッジ型のDC-DCコンバータに相当するので、図1に示されるフルブリッジ型のDC-DCコンバータとは一部の構成において異なるものの基本的な動作原理では共通する。図2のDC-DCコンバータは、スイッチング回路と、FET(Field Effect Transistor)駆動回路200とを含む。

【0009】

20

スイッチング回路は、第1の入力端子、第2の入力端子、出力端子、第1の制御端子および第2の制御端子を備える。スイッチング回路の第1の入力端子は、図示されない電圧源に接続され、入力電圧( $V_{in}$ )が印加される。スイッチング回路の第2の入力端子は接地(GNDに接続)される。スイッチング回路の出力端子は、LCR共振回路の入力端子に接続される。スイッチング回路の第1の制御端子および第2の制御端子は、FET駆動回路200の第1の出力端子および第2の出力端子にそれぞれ出力される。

【0010】

スイッチング回路は、入力電圧( $V_{in}$ )に基づいて矩形波を生成し、この矩形波をLCR共振回路の入力端子へと供給する。この矩形波の周波数および位相は、第1の制御端子および第2の制御端子を介して受け取られる第1の制御信号および第2の制御信号によって制御される。スイッチング回路は、FET Q1と、FET Q2とを含む。

【0011】

FET Q1のゲート端子は、スイッチング回路の第1の制御端子に接続される。FET Q1のドレイン端子は、スイッチング回路の第1の入力端子に接続される。FET Q1のソース端子は、FET Q2のドレイン端子およびスイッチング回路の出力端子に接続される。すなわち、FET Q2は、FET Q1に直列接続される。

【0012】

FET Q2のゲート端子は、スイッチング回路の第2の制御端子に接続される。FET Q2のドレイン端子は、FET Q1のソース端子およびスイッチング回路の出力端子に接続される。FET Q2のソース端子は、スイッチング回路の第2の入力端子に接続される。

【0013】

40

FET Q1およびFET Q2は、FET駆動回路200から第1の制御信号および第2の制御信号を受け取り、当該第1の制御信号および第2の制御信号のレベルに応じて交互にON/OFFする。ここで、第1の制御信号および第2の制御信号は、共に、周波数がfに等しくデューティー比が約50%に等しいパルス信号に相当する。換言すれば、FET Q2は、第1の制御信号の反転信号に概ね相当する第2の制御信号のレベルに応じて、FET Q1のON/OFFタイミングと略同一のタイミングでFET Q1と逆の状態に切り替わる。

【0014】

FET駆動回路200は、制御端子、第1の出力端子および第2の出力端子を備える。FET駆動回路200の制御端子は、LCR共振回路の第1の出力端子に接続される。FET駆動回路200の第1の出力端子は、スイッチング回路の第1の制御端子に接続され

50

る。FET駆動回路200の第2の出力端子は、スイッチング回路の第2の制御端子に接続される。

【0015】

FET駆動回路200は、制御端子を介してLCR共振回路の出力電圧または出力電流を検知する。FET駆動回路200は、FET Q1およびFET Q2をそれぞれ駆動するための第1の制御信号および第2の制御信号を、LCR共振回路の出力電圧または出力電流に基づいて生成する。FET駆動回路200は、第1の出力端子および第2の出力端子を介して、第1の制御信号および第2の制御信号をFET Q1およびFET Q2へと出力する。

【0016】

具体的には、FET駆動回路200は、FET Q1をLCR共振回路の出力電圧または出力電流に基づく駆動周波数( $f$ )でON/OFFする。そして、スイッチング回路は、LCR共振回路に含まれるトランジスタT1の一次側インダクタに矩形波交流電圧を印加することになる。この矩形波交流電圧は、そのピーク電圧が $\pm V_{in}/2$ に等しく、その周波数が $f$ に等しい。さらに、この矩形波交流電圧の基本波成分( $V_0$ )は、下記式(1)で表すことができる。

【0017】

【数1】

$$V_0 = \frac{2}{\pi} \times V_{in} \quad (1)$$

【0018】

LCR共振回路は、入力端子、第1の出力端子および第2の出力端子を備える。LCR共振回路は、入力端子を介してスイッチング回路から供給される矩形波交流電圧を昇圧または降圧することで出力電圧を生成する。そして、LCR共振回路は、第1の出力端子と第2の出力端子との間に接続された負荷に出力電圧を印加する。

【0019】

LCR共振回路は、共振キャパシタC1と、共振キャパシタC2と、トランジスタT1と、整流回路Dと、平滑キャパシタC3と、負荷とを含む。このLCR共振回路の共振特性は、共振キャパシタC1および共振キャパシタC2の合成キャパシタンス( $C_1 + C_2$ )と、トランジスタT1の漏洩インダクタンス( $L_s$ )および励磁インダクタンス( $L_p$ )と、負荷の抵抗値( $R_L$ )によって決まる。なお、整流回路Dおよび平滑キャパシタC3は、トランジスタT1の二次側に接続され、当該トランジスタT1からの交流入力電圧を整流および平滑化することによって直流出力電圧を生成する。

【0020】

具体的には、図3に例示されるように、LCR共振回路の利得(すなわち、出力電圧/入力電圧)は周波数に依存して変動する。図3に示される $f_s$ は、利得を略最大化する周波数を表しており、下記式(2)で導出することができる。他方、 $f_o$ は、上記 $f_s$ よりも高周波側で利得が1(0dB)に略等しくなる周波数を表しており、下記式(3)で導出することができる。

【0021】

【数2】

$$f_s \approx \frac{1}{2\pi\sqrt{(L_s+L_p)(C_1+C_2)}} \quad (2)$$

【0022】

## 【数3】

$$f_0 \approx \frac{1}{2\pi\sqrt{L_S(C1+C2)}} \quad (3)$$

## 【0023】

FET駆動回路200は、駆動周波数( $f$ )を $f_s$ から $f_o$ までの範囲で制御することにより、LCR共振回路の出力電圧または出力電流を調整することができる。例えば、入力電圧( $V_{in}$ )がある程度変動したとしても、FET駆動回路200はLCR共振回路の出力電圧または出力電流を安定化させることができる。

10

## 【0024】

具体的には、FET駆動回路200は、LCR共振回路の出力電圧が目標値に比べて低い場合には駆動周波数( $f$ )を $f_s$ に近づける(すなわち、低下させる)ことにより、当該出力電圧を高めることができる。他方、FET駆動回路200は、LCR共振回路の出力電圧が目標値に比べて高い場合には駆動周波数( $f$ )を $f_o$ に近づける(すなわち、高める)ことにより、当該出力電圧を低下させることができる。

10

## 【0025】

しかしながら、図3の周波数特性では、 $f_o$ よりも高域では利得が殆ど変化しないので、FET駆動回路200が駆動周波数( $f$ )を $f_o$ よりも高めたとしても出力電圧は殆ど低下しない。故に、図2の電流共振型DC-DCコンバータは、入力電圧( $V_{in}$ )がある程度高くなると目標の出力電圧を生成することが困難であるので、当該入力電圧を安定化させる機構(例えば、定電圧DC-DCコンバータ)を必要とする。

20

## 【0026】

第1の実施形態に係る電流共振型DC-DC変換器は、後述される第1の制御モードおよび第2の制御モードを併用することにより、入力電圧の許容範囲を拡大する(特に、許容上限を引き上げる)。本実施形態に係る電流共振型DC-DC変換器が図1に例示される。図1の電流共振型DC-DC変換器は、スイッチング回路と、FET駆動回路100と、LCR共振回路とを含む。

## 【0027】

スイッチング回路は、第1の入力端子、第2の入力端子、第1の出力端子、第2の出力端子、第1の制御端子、第2の制御端子、第3の制御端子および第4の制御端子を備える。スイッチング回路の第1の入力端子は、図示されない電圧源に接続され、入力電圧( $V_{in}$ )が印加される。スイッチング回路の第2の入力端子は接地(GNDに接続)される。スイッチング回路の第1の出力端子および第2の出力端子は、LCR共振回路の第2の入力端子および第1の入力端子にそれぞれ接続される。スイッチング回路の第1の制御端子、第2の制御端子、第3の制御端子および第4の制御端子は、FET駆動回路100の第1の出力端子、第2の出力端子、第3の出力端子および第4の出力端子にそれぞれ接続される。

30

## 【0028】

スイッチング回路は、入力電圧( $V_{in}$ )に基づいて2つの矩形波を生成し、この2つの矩形波をLCR共振回路の第1の入力端子および第2の入力端子へとそれぞれ供給する。この矩形波の周波数および位相は、第1の制御端子、第2の制御端子、第3の制御端子および第4の制御端子を介して受け取られる第1の制御信号、第2の制御信号、第3の制御信号および第4の制御信号によって制御される。

40

## 【0029】

スイッチング回路は、FET Q1と、FET Q2と、FET Q3と、FET Q4とを含む。なお、FET Q1、FET Q2、FET Q3およびFET Q4は、他の種別のトランジスタに置き換えられてもよい。

## 【0030】

FET Q1のゲート端子は、スイッチング回路の第1の制御端子に接続される。FET

50

T Q 1 のドレイン端子は、スイッチング回路の第 1 の入力端子に接続される。FET Q 1 のソース端子は、FET Q 2 のドレイン端子およびスイッチング回路の第 1 の出力端子に接続される。すなわち、FET Q 2 は、FET Q 1 に直列接続される。

#### 【0031】

FET Q 2 のゲート端子は、スイッチング回路の第 2 の制御端子に接続される。FET Q 2 のドレイン端子は、FET Q 1 のソース端子およびスイッチング回路の第 1 の出力端子に接続される。FET Q 2 のソース端子は、スイッチング回路の第 2 の入力端子に接続される。

#### 【0032】

FET Q 1 および FET Q 2 は、FET 駆動回路 100 が第 1 の制御モードおよび第 2 の制御モードのいずれで動作中であるかに関わらず、FET 駆動回路 100 から第 1 の制御信号および第 2 の制御信号を受け取り、当該第 1 の制御信号および第 2 の制御信号のレベルに応じて交互に ON / OFF する。ここで、第 1 の制御信号および第 2 の制御信号は、共に、周波数が  $f$  に等しくデューティー比が約 50 % に等しいパルス信号に相当する。換言すれば、FET Q 2 は、第 1 の制御信号の反転信号に概ね相当する第 2 の制御信号のレベルに応じて、FET Q 1 の ON / OFF タイミングと略同一のタイミングで FET Q 1 と逆の状態に切り替わる。

#### 【0033】

FET Q 3 のゲート端子は、スイッチング回路の第 3 の制御端子に接続される。FET Q 3 のドレイン端子は、スイッチング回路の第 1 の入力端子に接続される。すなわち、図 1 の例では、FET Q 3 は、FET Q 1 に並列接続される。FET Q 3 のソース端子は、FET Q 4 のドレイン端子およびスイッチング回路の第 2 の出力端子に接続される。すなわち、FET Q 4 は、FET Q 3 に直列接続される。

#### 【0034】

FET Q 4 のゲート端子は、スイッチング回路の第 4 の制御端子に接続される。FET Q 4 のドレイン端子は、FET Q 3 のソース端子およびスイッチング回路の第 2 の出力端子に接続される。FET Q 4 のソース端子は、スイッチング回路の第 2 の入力端子に接続される。すなわち、図 1 の例では、FET Q 4 は、FET Q 2 に並列接続される。

#### 【0035】

FET Q 3 および FET Q 4 は、FET Q 1 および FET Q 2 と並列に配置されており、FET 駆動回路 100 が後述される第 1 の制御モードおよび第 2 の制御モードのいずれで動作中であるかに関わらず、FET 駆動回路 100 から第 3 の制御信号および第 4 の制御信号を受け取り、当該第 3 の制御信号および第 4 の制御信号のレベルに応じて交互に ON / OFF する。ここで、第 3 の制御信号および第 4 の制御信号は、共に、周波数が  $f$  に等しくデューティー比が約 50 % に等しいパルス信号に相当する。換言すれば、FET Q 4 は、第 3 の制御信号の反転信号に概ね相当する第 4 の制御信号のレベルに応じて、FET Q 3 の ON / OFF タイミングと略同一のタイミングで FET Q 3 と逆の状態に切り替わる。

#### 【0036】

LCR 共振回路は、第 1 の入力端子、第 2 の入力端子、第 1 の出力端子および第 2 の出力端子を備える。LCR 共振回路の第 1 の入力端子および第 2 の入力端子は、スイッチング回路の第 2 の出力端子および第 1 の出力端子にそれぞれ接続される。LCR 共振回路の第 1 の出力端子および第 2 の出力端子は、負荷の第 1 の端子および第 2 の端子にそれぞれ接続可能である。さらに、LCR 共振回路の出力電圧または出力電流の測定のために、LCR 共振回路の第 1 の出力端子または第 2 の出力端子は FET 駆動回路 100 の制御端子にも接続される。

#### 【0037】

LCR 共振回路は、第 1 の入力端子および第 2 の入力端子を介してスイッチング回路から供給される矩形波交流電圧を昇圧または降圧することで出力電圧を生成する。そして、

10

20

30

40

50

L C R 共振回路は、第1の出力端子と第2の出力端子との間に接続された負荷に出力電圧を印加する。

#### 【0038】

L C R 共振回路は、共振キャパシタ  $C_r$  と、トランス  $T_1$  と、整流回路  $D_1$  と、平滑キャパシタ  $C_o$  と、負荷とを含む。この L C R 共振回路の共振特性は、共振キャパシタ  $C_r$  のキャパシタンスと、トランス  $T_1$  の漏洩インダクタンス ( $L_s$ ) および励磁インダクタンスと、負荷の抵抗値 ( $R_L$ ) によって決まる。L C R 共振回路の利得は、図3に例示される周波数特性と同様に周波数に依存して変化する。なお、整流回路  $D_1$  および平滑キャパシタ  $C_o$  は、トランス  $T_1$  の二次側に接続され、当該トランス  $T_1$  からの交流入力電圧を整流および平滑化することによって直流出力電圧 ( $V_o$ ) を生成する。

10

#### 【0039】

F E T 駆動回路100は、制御端子、第1の出力端子、第2の出力端子、第3の出力端子および第4の出力端子を備える。F E T 駆動回路100の制御端子は、L C R 共振回路の第1の出力端子に接続される。F E T 駆動回路100の第1の出力端子は、スイッチング回路の第1の制御端子に接続される。F E T 駆動回路100の第2の出力端子は、スイッチング回路の第2の制御端子に接続される。F E T 駆動回路100の第3の出力端子は、スイッチング回路の第3の制御端子に接続される。F E T 駆動回路100の第4の出力端子は、スイッチング回路の第4の制御端子に接続される。

#### 【0040】

F E T 駆動回路100は、制御端子を介してL C R 共振回路の出力電圧または出力電流を検知する。F E T 駆動回路100は、F E T Q1、F E T Q2、F E T Q3およびF E T Q4をそれぞれ駆動するための第1の制御信号、第2の制御信号、第3の制御信号および第4の制御信号を、L C R 共振回路の出力電圧または出力電流に基づいて生成する。F E T 駆動回路100は、第1の出力端子、第2の出力端子、第3の出力端子および第4の出力端子を介して、第1の制御信号、第2の制御信号、第3の制御信号および第4の制御信号をスイッチング回路へと出力する。

20

#### 【0041】

具体的には、F E T 駆動回路100は、第1の制御モードまたは第2の制御モードで動作することができる。

第1の制御モードにおいて、F E T 駆動回路100は、F E T Q1をL C R 共振回路の出力電圧または出力電流に基づく駆動周波数 ( $f$ ) でON/OFFし、F E T Q3をF E T Q1のON/OFFタイミングと略同一のタイミングでF E T Q1と逆の状態に切り替える。

30

#### 【0042】

すなわち、F E T 駆動回路100は、図4に例示されるように、第1の制御信号、第2の制御信号、第3の制御信号および第4の制御信号を生成する。そして、スイッチング回路は、図5に例示される矩形波交流電圧をL C R 共振回路に印加することになる。

#### 【0043】

この矩形波交流電圧は、そのピーク電圧が  $\pm V_{in}$  に等しく、その周波数が  $f$  に等しい。さらに、この矩形波交流電圧の基本波成分 ( $V_1$ ) は、下記式(4)で表すことができる。

40

#### 【0044】

#### 【数4】

$$V_1 = \frac{4}{\pi} \times V_{in} \quad (4)$$

#### 【0045】

前述のように、L C R 共振回路の利得は周波数に依存して変動する。故に、第1の制御モードでは、F E T 駆動回路100は、駆動周波数 ( $f$ ) を制御することにより、L C R

50

共振回路の出力電圧または出力電流を調整することができる。

【0046】

他方、第2の制御モードにおいて、FET駆動回路100は、FET Q1を駆動周波数(f)でON/OFFし、FET Q3をFET Q1のON/OFFタイミングからLCR共振回路の出力電圧または出力電流に基づく位相シフト量(θ)だけずれた(遅延した)タイミングでFET Q1と逆の状態に切り替える。

【0047】

すなわち、FET駆動回路100は、図6に例示されるように、第1の制御信号、第2の制御信号、第3の制御信号および第4の制御信号を生成する。そして、スイッチング回路は、図7に例示される3値矩形波交流電圧をLCR共振回路に印加することになる。

10

【0048】

この3値矩形波交流電圧は、そのピーク電圧が $\pm V_{in}$ に等しく、その中間電圧が0[V]に等しく、その周波数がfに等しい。さらに、この3値矩形波交流電圧の基本波成分( $V_2$ )は、下記数式(5)で表すことができる。

【0049】

【数5】

$$\begin{aligned} V_2 &= \frac{4}{\pi} \times V_{in} \times \cos \frac{\theta}{2} \\ &= V_1 \cos \frac{\theta}{2} \end{aligned} \quad (5)$$

20

【0050】

$V_2$ はの関数であるから、FET駆動回路100は位相シフト量(θ)を制御することでLCR共振回路の入力電圧を調整することができる。故に、FET駆動回路100は、駆動周波数(f)を制御しなくても位相シフト量(θ)を制御すれば、LCR共振回路の出力電圧または出力電流を調整できる。なお、FET駆動回路100は、第2の制御モードにおいて、位相シフト量(θ)の制御と駆動周波数(f)の制御とを併用してもよい。

30

【0051】

また、数式(2)より、 $V_2 = V_1$ が成立する。故に、第2の制御モードによれば、LCR共振回路の出力電圧を第1の制御モードに比べて低くすることが可能である。換言すれば、FET駆動回路100は、第2の制御モードでは、スイッチング回路の入力電圧( $V_{in}$ )の大きさに関わらず、 $V_2$ を0以上 $V_1$ 以下の範囲に制限することができる。故に、FET駆動回路100は、第2の制御モードを利用することで、常に第1の制御モードで動作する場合と比べてスイッチング回路の入力電圧( $V_{in}$ )の許容上限を引き上げることが可能である。

【0052】

FET駆動回路100は、第1の制御モードおよび第2の制御モードを以下に説明するように切り替えてよい。

40

例えば、FET駆動回路100は、第1の制御モードにおいて設定可能な駆動周波数(f)の上限値(以降、第1の閾値と称される)を設けてもよい。すなわち、FET駆動回路100は、第1の制御モードでの動作時に、LCR共振回路の出力電圧または出力電流に基づく駆動周波数(f)が第1の閾値以上になると第2の制御モードに切り替わってよい。なお、出力電圧または出力電流に基づく駆動周波数(f)は、計算を通じて導出されてもよいし、例えばLCR回路の利得の周波数特性に基づいて予め作成されたテーブル(LUT(Look Up Table)など)から探索されてもよい。

【0053】

他方、FET駆動回路100は、第2の制御モードにおいて設定可能な位相シフト量(θ)

50

) の下限値 (以降、第 2 の閾値と称される) を設けてもよい。すなわち、FET 駆動回路 100 は、第 2 の制御モードでの動作時に、LCR 共振回路の出力電圧または出力電流に基づく位相シフト量 ( ) が第 2 の閾値以下となると第 1 の制御モードに切り替わってもよい。なお、出力電圧または出力電流に基づく位相シフト量 ( ) は、計算を通じて導出されてもよいし、例えば予め作成されたテーブル (LUT など) から探索されてもよい。

#### 【0054】

第 1 の閾値および第 2 の閾値は、固定であってもよいし、FET 駆動回路 100 (または、図示されない閾値設定回路) によって動的に制御されてもよい。

例えば、第 1 の閾値は、スイッチング回路の入力電圧 ( $V_{in}$ ) が高いほど大きな値へと変化してもよい。他方、第 2 の閾値は、この入力電圧 ( $V_{in}$ ) が高いほど小さな値へと動的に変化してもよい。このような動的制御によれば、電源変換効率を向上させたり、スイッチング回路の入力電圧 ( $V_{in}$ ) の急変に対する応答性を向上させたりすることができる。

#### 【0055】

或いは、第 1 の閾値は、LCR 共振回路の出力電流が大きいほど小さな値へと変化してもよい。他方、第 2 の閾値は、この出力電流が大きいほど大きな値へと動的に変化してもよい。このような動的制御によれば、LCR 共振回路の出力電流の急変に対する応答性を向上させることができる。

#### 【0056】

或いは、第 1 の閾値は、図 1 の電流共振型 DC - DC 変換器における入力電力から当該電流共振型 DC - DC 変換器における出力電力を差し引いた損失が大きいほど (換言すれば、効率が低いほど) 大きな値へと動的に変化してもよい。他方、第 2 の閾値は、この損失が大きいほど大きな値へと動的に変化してもよい。このような動的制御によれば、電源変換効率を向上させることができる。

#### 【0057】

以上説明したように、第 1 の実施形態に係る電流共振型 DC - DC 変換器は、スイッチング回路の駆動周波数を制御することで出力電圧または出力電流を調整する第 1 の制御モードと、当該スイッチング回路に含まれる 2 つのトランジスタ対によって生成される 2 つの矩形波の位相差を制御することで出力電圧または出力電流を調整する第 2 の制御モードとを併用する。従って、この電流共振型 DC - DC 変換器によれば、第 1 の制御モードでは許容されない高レベルの電圧が入力された場合であっても、第 2 の制御モードを利用して目標の出力電圧を生成することができる。すなわち、この電流共振型 DC - DC 変換器は入力電圧の許容範囲が広いので、当該入力電圧を安定化させる機構 (例えば、定電圧 DC - DC コンバータ) を省略 (ないし簡略化) することができる。故に、この電流共振型 DC - DC 変換器によれば、係る機構に伴うコストおよびサイズの増加ならびに電力変換効率の低下を回避 (ないし抑制) することができる。

#### 【0058】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

#### 【符号の説明】

#### 【0059】

100, 200 . . . FET 駆動回路

C1, C2, Cr . . . 共振キャパシタ

C3, Co . . . 平滑キャパシタ

D, D1 . . . 整流回路

10

20

30

40

50

T 1 . . . トランス

Q 1 , Q 2 , Q 3 , Q 4 . . . F E T

【図 1】

図1

【図 2】

図2

【図3】

図3

【図5】

図5

矩形波交流電圧

【図4】

図4

【図6】

図6

【図7】

図7

3値矩形波交流電圧

---

フロントページの続き

(74)代理人 100179062

弁理士 井上 正

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(72)発明者 森岡 静夫

東京都青梅市新町3丁目3番地の5 東芝デジタルメディアエンジニアリング株式会社内

(72)発明者 鶴谷 守

埼玉県坂戸市塚越1220-1 パワーアシストテクノロジー株式会社内

(72)発明者 水谷 彰

埼玉県坂戸市塚越1220-1 パワーアシストテクノロジー株式会社内

審査官 栗栖 正和

(56)参考文献 特開2002-262569(JP,A)

特開2014-003764(JP,A)

国際公開第2013/114758(WO,A1)

特開2014-039383(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 3 / 28

H02M 3 / 335