(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) Int. Cl. 5

H01L 21/328

(11) 공개번호 특 1992-0007124

(43) 공개일자 1992년04월28일

(21) 출원번호 특 1990-0013935

(22) 출원일자 1990년 09월 04일

윤종밀

서울특별시 서초구 반포2동 신반포아파트 9동 403호

김양호, 김원호

(74) 대리인

## (74) 대리인 김양호, 김원호

### 심사청구 : 있음

#### (54) 폴리 에미터 바이폴라 트랜지스터의 제조 방법

## 요약

내용 없음

## 대표도

도 1

명세서

## 〔발명의 명칭〕

## 풀리 예미터 바이폴라 트랜지스터의 제조방법

### [도면의 간단한 설명]

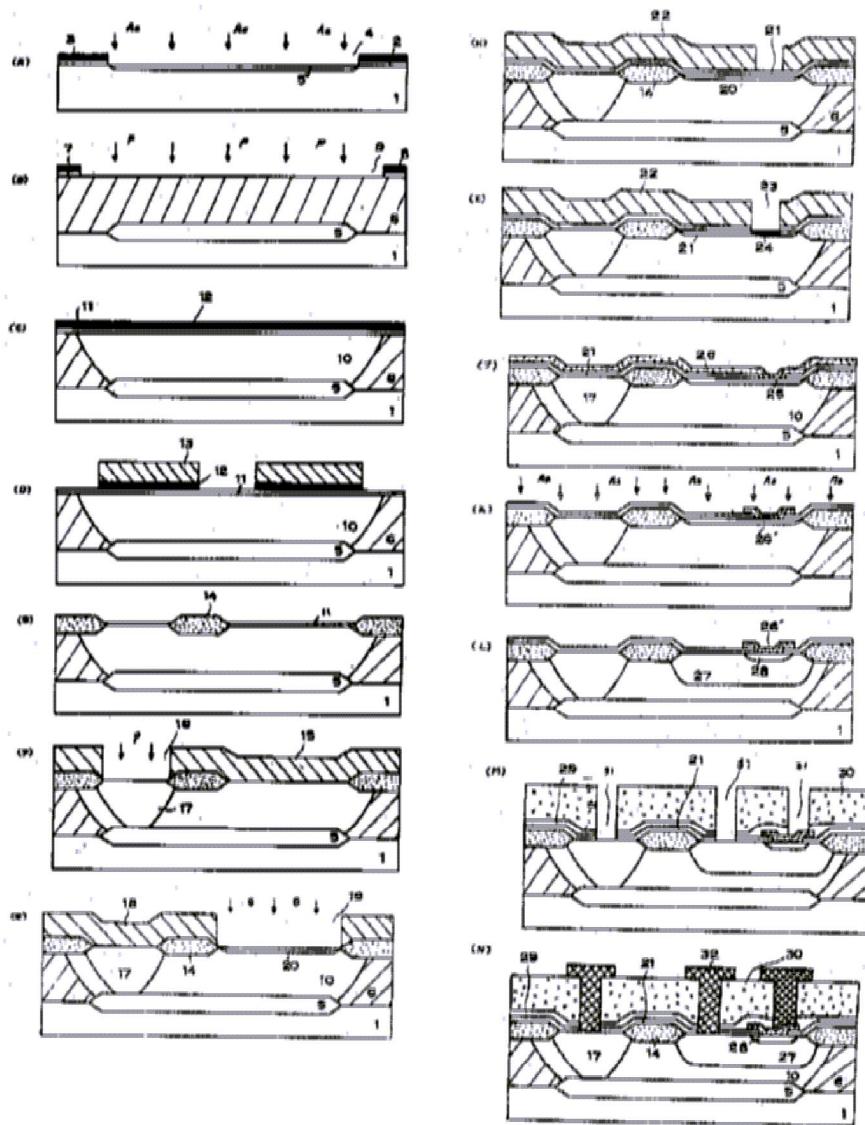

제1도(A) 내지 (N)는 본 발명의 낮은 에미터 저항을 갖는 바이폴라 트랜지스터의 제조공정도이다.

본 내용은 일부 공개 것이므로 전문 내용을 수록하지 않았음

### (57) 청구의 범위

청구항 1

실리콘기판(1)상에 매몰층(5)과 N형 에피택셜층(6)을 형성하는 공정과, 에피택셜층(6)상에 N형 불순물을 이온주입하여 바이폴라 트랜지스터가 형성될 영역인 N형 웨л(10)을 형성하는 공정과, 통상의 산화공정으로 필드산화막(145)을 형성하는 공정과 콜렉터 영역(10)내에 N+확산층(17)을 형성하는 공정과, P형 불순물을 이온주입하여 베이스영역 형성용 이온 주입영역(20)을 형성하는 공정과, 산화막(21)을 도포하는 공정과, 상기 산화막(21)을 식각하여 접촉장(23)을 형성하는 공정과, 램프-업 도포법을 이용하여 폴리실리콘막(26)을 도포한 다음 패터닝하여 폴리패널(26')을 형성하는 공정과, 기판전면에 걸쳐 에미터 영역을 형성하기 위한 이온주입 공정과, 확산공정을 통하여 이온주입된 불순물을 동시에 확산시켜 베이스영역(27)과 에미터영역(28)을 형성하는 공정과, 산화막(29)과 BPSG막(30)을 형성하는 공정과, 상기 BPSG막(30)과 산화막(29,21)을 사진식각공정으로 순차 식각하여 금속 접촉구(31)를 형성하는 공정과, 금속막을 도포하고 패터닝하여 금속전극패턴(32)을 형성하는 공정으로 이루어지는 것을 특징으로 하는 폴리 에미터 바이폴라 트랜지스터의 제조방법.

## 청구항 2

제1항에 있어서, 접촉장(23)은 단결정 실리콘 기판과 폴리 패턴(26')을 접촉시키기 위한 것을 특징으로 하는 폴리 에미터 바이플라 트랜지스터의 제조방법.

### 청구항 3

제1항 또는 제2항에 있어서, 접촉장을 형성하는 공정은, 산화막(21)위에 감광성 물질(22)을 전면 도포하는 스텝과, 사진식각 공정으로 감광성 물질(22)을 식각하여 접촉장이 형성될 부위를 노출시키는 스텝과, 식각하는 스텝과, 산화막(21)이 식각될 때 발생한 단결정 실리콘

기판의 순상된 부분(24)을 식각하는 스텝으로 이루어지는 것을 특징으로 하는 폴리 에미터 바이플라 트랜지스터의 제조방법.

#### 청구항 4

제3항에 있어서, 단결정 실리콘 기판의 손상된 부분(24)을 플라즈마 방식으로 식각하는 것을 특징으로 하는 폴리 에미터 바이폴라 트랜지스터의 제조방법.

### 청구항 5

제1항에 있어서, 상기 폴리실리콘막(26)의 도포시, 웨이퍼를 도포튜브로 인입시킬때에는 도포튜브의 온도를 400°C정도의 저온으로 유지하고, 웨이퍼를 도포튜브로 완전히 인입시킨 후에는 서서히 온도를 정상적인 폴리실리콘의 도포 온도까지 상승시켜 폴리실리콘막(26)을 도포하는 것을 특징으로 하는 폴리 에미터 바이폴라 트랜지스터의 제조방법.

### 청구항 6

제1항에 있어서, 살기 폴리 패턴(26')이 에미터 영역의 확산 소오스가 되는 것을 특징으로 하는 폴리 에미터 바이플라 트랜지스터의 제조방법.

※ 참고사항 : 최초출원 내용에 의하여 공개하는 것임.

도면

## 도면1