## (10) **DE 10 2006 020 098 A1** 2007.10.31

(12)

# Offenlegungsschrift

(21) Aktenzeichen: 10 2006 020 098.5

(22) Anmeldetag: **29.04.2006** (43) Offenlegungstag: **31.10.2007**

(71) Anmelder:

Infineon Technologies AG, 81669 München, DE

(74) Vertreter:

Wilhelm & Beck, 80639 München

(72) Erfinder:

Proell, Manfred, 84405 Dorfen, DE; Schröder, Stephan, Dr., 81543 München, DE; Ruf, Wolfgang, 86316 Friedberg, DE; Haas, Hermann, 85635 Höhenkirchen-Siegertsbrunn, DE (56) Für die Beurteilung der Patentfähigkeit in Betracht

(51) Int Cl.8: **G11C 11/406** (2006.01)

gezogene Druckschriften:

DE 103 44 625 A1

DE 693 19 372 T2

EP 11 50 301 A1

Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen

Prüfungsantrag gemäß § 44 PatG ist gestellt.

(54) Bezeichnung: Speicherschaltung und Verfahren zum Auffrischen von dynamischen Speicherzellen

(57) Zusammenfassung: Die Erfindung betrifft eine Speicherschaltung, umfassend: ein Speicherzellenfeld mit an Wortleitungen und Bitleitungen angeordneten dynamischen Speicherzellen, eine Auswahleinheit zum Bereitstellen einer Auswahlinformation und eine Auffrischschaltung, um jeweils abhängig von der Auswahlinformation die Speicherzellen auszuwählen und die ausgewählten Speicherzellen aufzufrischen, so dass jeweils eine darin gespeicherte Information erhalten bleibt.

(12)

#### **Beschreibung**

**[0001]** Die Erfindung betrifft eine Speicherschaltung mit einem Speicherzellenfeld, das an Wortleitungen und Bitleitungen angeordnete dynamische Speicherzellen aufweist, die zum Aufrechterhalten der gespeicherten Information aufgefrischt werden müssen. Die Erfindung betrifft weiterhin ein Verfahren zum Auffrischen von Speicherzellen einer Speicherschaltung.

[0002] Ein Speicherzellenfeld einer DRAM-Speicherschaltung weist Wortleitungen und Bitleitungen auf. Bei einem Speicherzugriff wird zunächst eine der Wortleitungen aktiviert und dadurch die an der Wortleitung angeordneten Speicherzellen jeweils mit einer zugeordneten Bitleitung leitend verbunden. Dabei fließt eine Ladung von einer Speicherzellenkapazität der Speicherzelle die Bitleitung. Dies führt zu einer Auslenkung der Bitleitungsspannung, die mithilfe eines Leseverstärkers detektiert werden kann.

[0003] Die Speicherzellenkapazität eines dynamischen Speicherbausteins ist üblicherweise mit einen Speicherkondensator gebildet, der in dem Substrat des Speicherbausteins angeordnet ist. Eine in dem gespeicherte Speicherkondensator Ladung schwächt sich jedoch im Laufe der Zeit ab, da Ladungen in das umgebende Substrat abfließen. Dies kann zu einem Datenverlust in der Speicherzelle führen. Um die Speicherzelle mit dem korrekten Dateninhalt auslesen zu können, darf eine Restladung in der Speicherzelle nicht unterschritten werden. Das Abfließen der Speicherzellenladung wird kompensiert, indem die Speicherzelle innerhalb eines definierten Zeitraums aufgefrischt wird, d.h. neu mit der entsprechenden Ladung aufgeladen wird, so dass permanent eine ausreichende Restladung der Speicherzelle vorliegt.

[0004] Ein Speicherbaustein kann neben anderen Betriebsmodi auch in einem Selbstauffrischmodus betrieben werden, indem der Speicherbaustein selbst für das Auffrischen der Speicherzellen sorgt. Dazu müssen von extern keine Kommandos oder Adressen an den Speicherbaustein angelegt werden. Das Erhalten der Ladungen in den Speicherkapazitäten wird durch intern generierte Auffrischkommandos gewährleistet, wobei die zeitlichen Abstände zwischen den Auffrischkommandos so definiert sind, dass permanent eine ausreichende Restladung in den Speicherzellen vorliegt, die zu einem korrekten Auslesen des Inhalts der Speicherzelle führt. Der Abstand zwischen den Auffrischvorgängen zum Auffrischen einer Speicherzelle bestimmt in wesentlichem Maße die Stromaufnahme in dem Selbstauffrischmodus. Sind die Zeiträume zwischen den Auffrischvorgängen kurz, sinkt die Gefahr eines Verlusts von Daten in den Speicherzellen, es steigt jedoch die Stromaufnahme an. Werden die Intervalle zwischen den Auffrischvorgängen verlängert, um die Stromaufnahme zu verringern, besteht die Gefahr der Verringerung der gespeicherten Ladung unter eine Mindestladung, so dass ein Datenverlust auftreten kann.

[0005] Es ist Aufgabe der vorliegenden Erfindung eine Speicherschaltung zur Verfügung zu stellen, dessen Stromaufnahme im Selbstauffrischmodus reduziert ist. Es ist weiterhin Aufgabe der vorliegenden Erfindung, ein Verfahren zum Auffrischen von Speicherzellen zur Verfügung zu stellen, bei dem die Stromaufnahme minimiert ist.

**[0006]** Diese Aufgabe wird durch die Speicherschaltung nach Anspruch 1 sowie durch das Verfahren nach Anspruch 11 gelöst.

**[0007]** Weitere vorteilhafte Ausgestaltungen der Erfindung sind in den abhängigen Ansprüchen angegeben.

[0008] Gemäß einem ersten Aspekt der vorliegenden Erfindung ist eine Speicherschaltung vorgesehen, die ein Speicherzellenfeld mit an Wortleitungen und Bitleitungen angeordneten dynamischen Speicherzellen, eine Auswahleinheit zum Bereitstellen einer Auswahlinformation und eine Auffrischschaltung umfasst, um die Speicherzellen jeweils abhängig von der Auswahlinformation auszuwählen und die ausgewählten Speicherzellen aufzufrischen, so dass eine jeweilige darin gespeicherte Information erhalten wird, oder nicht aufzufrischen.

[0009] Die erfindungsgemäße Speicherschaltung ermöglicht es, nur diejenigen Speicherzellen aufzufrischen, die durch die Auswahlinformation bestimmt sind. Somit kann das Auffrischen durch die Auswahlinformation auf die relevanten Speicherzellen beschränkt werden, z.B. auf die Speicherzellen, die zuvor tatsächlich von einer Anwendung beschrieben wurden. Dies kann zu einer erheblichen Stromeinsparung führen, da Speicheranwendungen häufig nur auf Teile des Speicherzellenfeldes zugreifen, so dass nur ein Teil der Speicherzellen aufgefrischt werden muss. Da das Auffrischen der Inhalte der Speicherzellen einen bestimmten Strom benötigt, kann durch das Vermeiden eines Auffrischens von Speicherbereichen entsprechend Strom eingespart werden.

[0010] Gemäß einem weiteren Aspekt der vorliegenden Erfindung ist ein Verfahren zum Auffrischen von dynamischen Speicherzellen in einem Speicherzellenfeld vorgesehen, wobei die Speicherzellen an Wortleitungen und Bitleitungen angeordnet sind. Das Verfahren umfasst die Schritte des Bereitstellens einer Auswahlinformation des Auswählens von Speicherzellen abhängig von der Auswahlinformation und des Auffrischens der ausgewählten Speicherzellen abhängig von der Auswahlinformation.

**[0011]** Weitere vorteilhafte Ausgestaltungen der Erfindung sind in den abhängigen Ansprüchen angegeben.

[0012] Gemäß einer bevorzugten Ausführungsform der Erfindung kann die Auswahleinheit einen Zustandsspeicher aufweisen, um die Auswahlinformation zu speichern. Insbesondere kann die Auswahleinheit weiterhin eine Programmierschaltung aufweisen, um den Zustandsspeicher abhängig von einem Schreibbefehl auf einer Adresse des Speicherzellenfeldes so mit einem ersten Zustand zu beschreiben, dass die Auffrischschaltung bei einem nachfolgenden Auffrischen die Speicherzellen an der Adresse auffrischt, und um den Zustandsspeicher abhängig von einem Freigabesignal bezüglich einer Adresse des Speicherzellenfeldes so mit einem zweiten Zustand zu beschreiben, dass die Auffrischschaltung bei einem nachfolgenden Auffrischen das Auffrischen der Speicherzellen an der Adresse unterdrückt. Auf diese Weise kann ein einmal benutzter Speicherbereich auch während des Betriebs der Speicherschaltung wieder freigegeben werden, so dass die darin enthaltene Information verworfen wird, indem kein weiteres Auffrischen der betreffenden Speicherzellen durchgeführt wird.

[0013] Es kann weiterhin ein Wortleitungsdekoder vorgesehen sein, um abhängig von einer Adressinformation eine der Wortleitungen zum Aktivieren auszuwählen, wobei die Auffrischschaltung einen Adressgeber aufweist, der nacheinander eine Adressinformation zum Adressieren jeder der Wortleitungen bereitstellt.

**[0014]** Gemäß einer weiteren Ausführungsform der Erfindung kann die Auffrischschaltung weiterhin Auswahlschalter aufweisen, die jeweils zwischen dem Wortleitungsdekoder und jeder der Wortleitungen angeordnet sind, um abhängig von der von der Auswahleinheit bereitgestellten Auswahlinformation ein Aktivieren der entsprechenden Wortleitung durch die Auffrischschaltung zuzulassen oder zu verhindern.

**[0015]** Es können weitere Auswahlschalter vorgesehen sein, die parallel zu den Auswahlschaltern angeordnet sind, wobei die Auffrischschaltung gestaltet ist, um die weiteren Auswahlschalter in einem Auffrischmodus zu öffnen und in einem Normalbetriebsmodus zu schließen.

**[0016]** Ferner ist es möglich, dass der Zustandsspeicher Zustandsspeicherelemente aufweist, die jeweils einer der Wortleitungen zugeordnet sind, wobei jeder der Auswahlschalter mit einem zugeordneten Zustandsspeicherelement verbunden ist, so dass der Schaltzustand jedes der Auswahlschalter von einem in dem Zustandsspeicherelement gespeicherten Datum abhängt.

[0017] Insbesondere kann jedes der Zustandsspeicherelemente eine Programmierschaltung aufweisen, um beim Beschreiben einer Speicherzelle an einer der Wortleitungen das zugeordnete Zustandsspeicherelement in einen ersten Zustand zu versetzen, und um das zugeordnete Zustandsspeicherelement in einen zweiten Zustand zu versetzen, wenn die Speicherschaltung eingeschaltet wird oder ein Freigabesignal bereitgestellt wird. Die Auswahlschalter sind bei einem ersten Zustand des jeweils zugeordneten Zustands des Speicherelementes geschlossen und bei einem zweiten Zustand des jeweils zugeordneten Zustandsspeicherelementes geöffnet.

[0018] Gemäß einer weiteren bevorzugten Ausführungsform sind die Zustandsspeicherelemente als dynamische Speicherzellen entlang einer oder mehrerer Bitleitungen in dem Speicherzellenfeld vorgesehen, so dass an jeder der Wortleitungen eine Zustandsspeicherzelle angeordnet und durch Aktivieren der Wortleitung auslesbar ist, wobei erste Ausleseverstärker vorgesehen sind, die jeweils mit mindestens einer der Bitleitungen, die mit den dynamischen Speicherzellen verbunden sind, verbunden sind und wobei ein zweiter Ausleseverstärker vorgesehen ist. der mit einer der mehreren Bitleitungen, die mit den Zustandsspeicherzellen verbunden sind, verbunden ist, wobei die ersten und zweiten Ausleseverstärker zum Auffrischen aktivierbar sind, wobei die Auffrischschaltung die Ausleseverstärker nacheinander aktiviert, so dass der Zustand der Zustandsspeicherzelle an der aktivierten Wortleitung durch den zweiten Ausleseverstärker detektierbar ist und die ersten Ausleseverstärker abhängig von dem Zustand in der Zustandsspeicherzelle zum Verstärken der Ladung auf der zugeordneten Bitleitung oder den mehreren zugeordneten Bitleitungen aktivierbar oder deaktivierbar sind.

**[0019]** Es kann eine Programmierschaltung vorgesehen sein, um die Zustandsspeicherzellen mit einem ersten Zustand eines Auffrischdatums, der angibt, dass ein Auffrischen erfolgen soll, oder einem zweiten Zustand, der angibt, dass kein Auffrischen erfolgen soll, zu beschreiben, wobei der erste Zustand einem Potenzialpegel entspricht, in dessen Richtung sich die Zustandsspeicherzellen durch Leckströme im nicht adressierten Zustand entladen.

**[0020]** Gemäß einer weiteren Ausführungsform kann vorgesehen sein, dass die Zustandsspeicherzelle durch mehrere dynamische Speicherzellen gebildet ist, um eine größere Ladung zur Speicherung des ersten oder zweiten Zustands in der Zustandsspeicherzelle bereitzustellen.

**[0021]** Vorzugsweise können die Wortleitungen mit mehreren lokalen Wortleitungstreibern versehen sein, um jeweils Abschnitte der entsprechenden Wortleitung zu aktivieren, wobei die Wortleitungstrei-

ber abhängig von dem Inhalt der der entsprechenden Wortleitung zugeordneten Zustandsspeicherzelle aktivierbar sind.

**[0022]** Jedem Abschnitt der jeweiligen Wortleitung kann eine entsprechende Zustandsspeicherzelle zugeordnet sein, so dass eine Wortleitung abhängig von der Auswahlinformation abschnittsweise auffrischbar ist.

[0023] Gemäß einer weiteren bevorzugten Ausführungsform der Erfindung kann die Auffrischschaltung weiterhin eine Auswahlschaltung aufweisen, um die Adressinformation abhängig von der von der Auswahleinheit bereitgestellten Auswahlinformation an den Wortleitungsdekoder weiterzuleiten. Insbesondere können mehrere Wortleitungsdekoder für mehrere Speicherzellenfelder vorgesehen sein, wobei die Auswahleinheit ausgebildet ist, um die Adressinformation abhängig von der von der Auswahleinheit bereitgestellten Auswahlinformation an jeden der Wortleitungsdekoder weiterzuleiten.

**[0024]** Bevorzugte Ausführungsformen der Erfindung werden nachfolgend anhand der beigefügten Zeichnungen ausführlicher erläutert. Es zeigen:

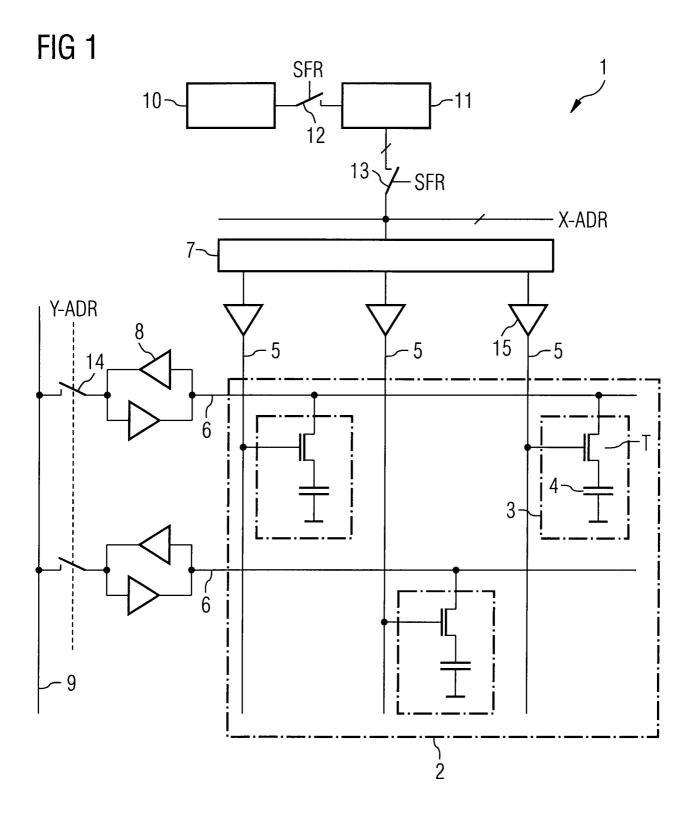

[0025] Fig. 1 eine schematische Darstellung einer Speicherschaltung gemäß dem Stand der Technik;

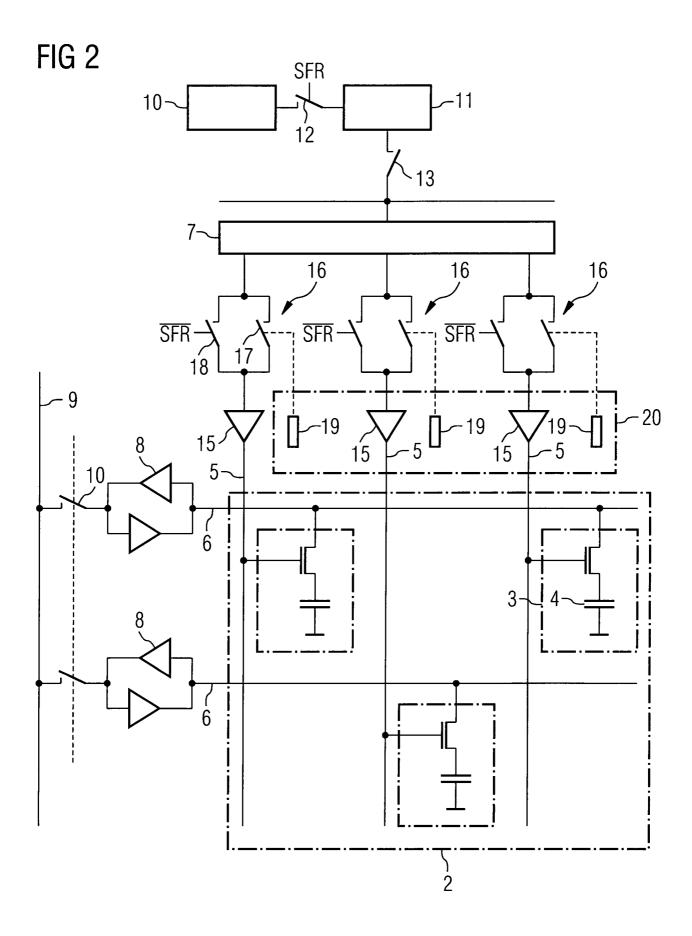

**[0026]** Fig. 2 eine schematische Darstellung einer Speicherschaltung gemäß einer ersten Ausführungsform der vorliegenden Erfindung;

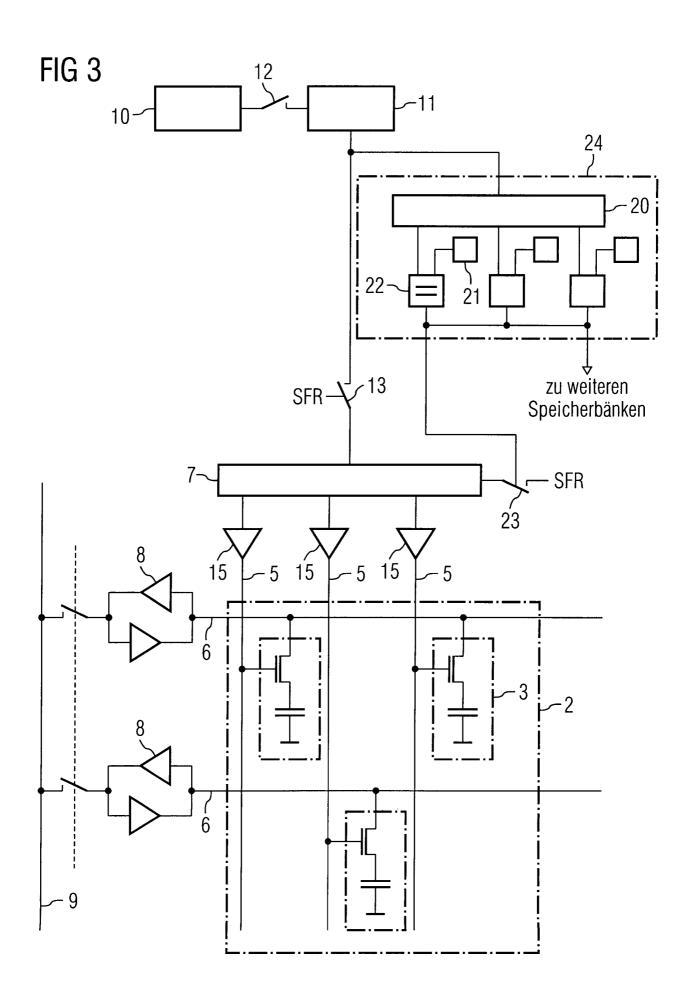

**[0027]** Fig. 3 eine schematische Darstellung einer Speicherschaltung gemäß einer weiteren Ausführungsform der vorliegenden Erfindung;

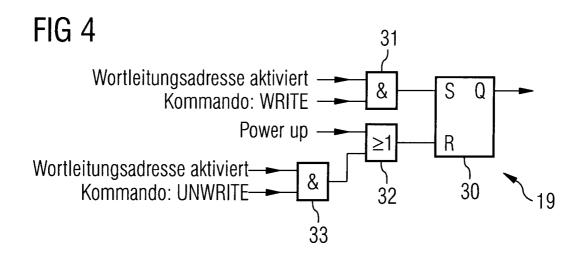

**[0028]** Fig. 4 eine beispielhafte Schaltung eines Zustandsspeicherelements zum Zulassen bzw. Verhindern des Auffrischens von an einer Wortleitung befindlichen Speicherzelle;

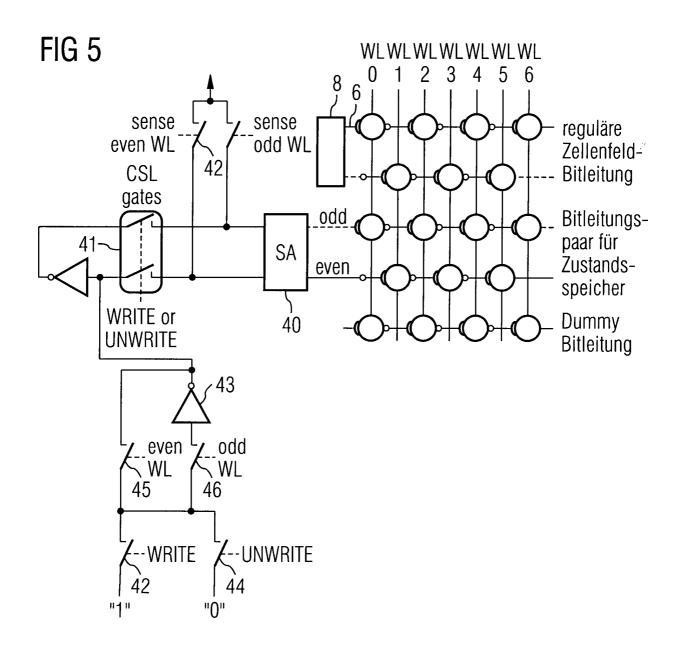

**[0029]** Fig. 5 zeigt einen Ausschnitt aus einer Speicherschaltung gemäß einer weiteren Ausführungsform der Erfindung, bei dem die Zustandsspeicherelemente als Teil des Speicherzellenfeldes ausgebildet sind;

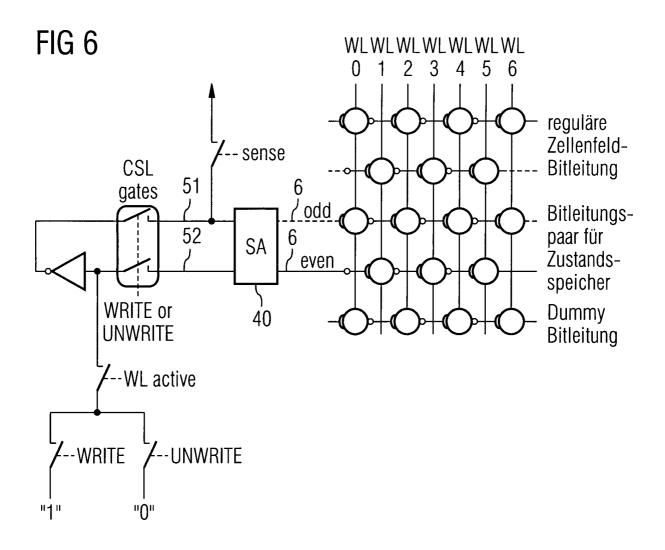

[0030] Fig. 6 eine schematische Darstellung einer Speicherschaltung gemäß einer weiteren Ausführungsform der Erfindung, wobei die Zustandsspeicherelemente ebenfalls als Teil des Speicherzellenfeldes vorgesehen sind;

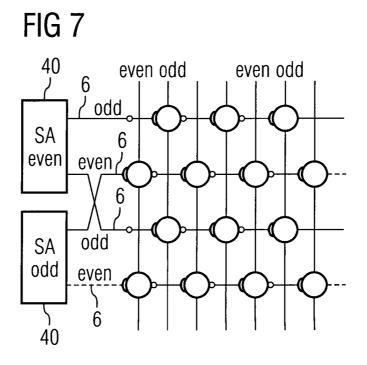

**[0031]** Fig. 7 einen Ausschnitt aus einer erfindungsgemäßen Speicherschaltung gemäß einer weiteren Ausführungsform der Erfindung, bei dem die Zustandsspeicherelemente mit zwei dynamischen Speicherzellen des Speicherzellenfeldes ausgebildet

sind:

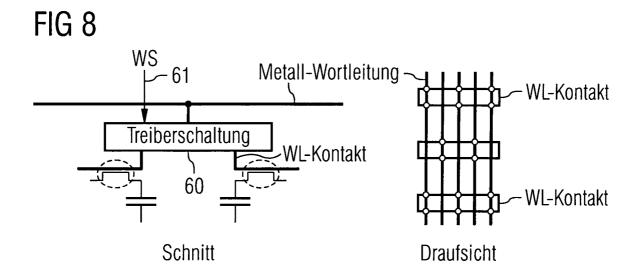

**[0032]** Fig. 8 zeigt eine Darstellung einer durch lokale Wortleitungstreiber unterteilte Wortleitung, die wahlweise aktiviert werden können, gemäß einer weiteren Ausführungsform der Erfindung;

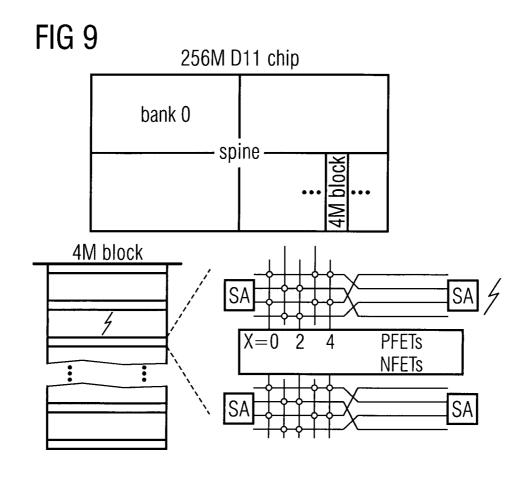

**[0033]** Fig. 9 eine Darstellung einer Ausführungsform der Erfindung, bei der die lokalen Wortleitungstreiber durch jeweils ein Zustandsspeicherelement auswählbar sind.

[0034] In Fig. 1 ist eine schematische Darstellung einer herkömmlichen Speicherschaltung 1 mit einem Speicherzellenfeld 2 dargestellt. Das Speicherzellenfeld 2 umfasst dynamische Speicherzellen 3, bei denen jeweils eine Information in Form einer Ladung in einem Kondensator 4 gespeichert wird. Die Speicherzellen 3 des Speicherzellenfeldes 2 sind an Wortleitungen 5 und Bitleitungen 6 angeordnet, so dass bei einer Aktivierung einer der Wortleitungen 5 ein entsprechender Auswahltransistor T der an dieser Wortleitung befindlichen Speicherzellen 3 leitend geschaltet wird, so dass die Ladung auf die entsprechende Bitleitung 6 fließt. Die Auswahl der betreffenden Wortleitung 5 erfolgt über das Anlegen einer Wortleitungsadresse X-ADR an einen Wortleitungsdekoder 7, die abhängig von der Wortleitungsadresse X-ADR über einen entsprechenden Wortleitungstreiber 15 eine der Wortleitungen 5 aktiviert und die anderen im deaktivierten Zustand belässt. Jede Bitleitung 6 ist mit einem Ausleseverstärker 8 verbunden, um die von der adressierten Speicherzelle auf die Bitleitung 6 fließende Ladung zu verstärken und auf eine Datenleitung 9 auszugeben. Beim Schreiben wird ein entsprechendes Signal an die Datenleitung 9 angelegt, und einer der mit den Bitleitungen 6 verbundenen Ausleseverstärker 8 über einen entsprechenden Schalter 14 abhängig von einer Bitleitungsadresse Y-ADR ausgewählt, so dass das entsprechende Datensignal als Ladung auf die entsprechende Bitleitung 6 angelegt wird, so dass der Kondensator 4 der adressierten Speicherzelle 3 entsprechend aufgeladen wird.

[0035] Bei dynamischen Speicherzellen ist die Ladung in dem Kondensator 4 gespeichert. Im nicht adressierten Zustand verliert der Kondensator 4 jedoch im Laufe der Zeit seine Ladung, so dass nach einiger Zeit die in der Speicherzelle 3 gespeicherte Information nicht korrekt ausgelesen werden kann. Aus diesem Grunde werden die Speicherzellen in bekannter Weise in regelmäßigen Abständen aufgefrischt, indem die Wortleitungen 5 nacheinander adressiert und aktiviert werden, so dass die Ladungen der an der Wortleitung befindlichen Speicherzellen auf die zugehörigen Bitleitungen 6 fließen und dort durch einen Verstärkungsvorgang mithilfe der Ausleseverstärker 8 in die entsprechenden Speicherzellen 3 zurückgeschrieben wird, so dass die darin

gespeicherte Information aufgefrischt wird und dadurch gegenüber einem Informationsverlust geschützt wird.

[0036] Üblicherweise sind die Ausleseverstärker 8 mit jeweils zwei Bitleitungen verbunden, wobei pro Wortleitung 5 nur eine Speicherzelle 3 für jedes der Bitleitungspaare vorgesehen ist. Eine Ladung des Kondensators 4 der Speicherzelle 3 wird detektiert, indem ein Ladungsvergleich auf den Bitleitungen 6 des Bitleitungspaares mit Hilfe eines der Ausleseverstärker 8 vorgenommen wird, da nach dem Adressieren der entsprechenden Wortleitung 5 an einer der beiden Bitleitungen 6 des Bitleitungspaares befindlichen Speicherzellen die Ladung der betreffenden Bitleitung sich gegenüber der Ladung der anderen Bitleitung des Bitleitungspaares ändert.

[0037] In einem Selbstauffrischmodus führt die Speicherschaltung 1 das Auffrischen der Speicherzellen 3 selbsttätig durch. Dazu ist ein Auffrischzähler 10 vorgesehen, der in einem Auffrischadressdekoder 11 eine Auffrischadresse generiert und diese an den Wortleitungsdekoder 7 anlegt. Der Auffrischadressdekoder 11 generiert im einfachsten Fall aufeinander folgende Wortleitungsadressen X-ADR, so dass jede der Wortleitungen 5 nacheinander für eine bestimmte Zeitdauer, z.B. 40 ns, aktiviert und anschließend deaktiviert wird, so dass die Ladung der entsprechenden Speicherzelle 3 auf die Bitleitung fließen kann, dort durch die Ausleseverstärker 8 verstärkt werden und dadurch aufgrund des geschlossenen leitend geschaltenen Auswahltransistors T die entsprechende Ladung in die Kondensatoren 4 der betreffenden Speicherzellen zurückgeschrieben wird. Anschließend werden die Wortleitungen wieder deaktiviert und die Bitleitungen auf ein gemeinsames Ausgleichspotenzial gebracht. Anschließend wird der Auffrischzähler 10 weitergezählt, so dass eine weitere Auffrischadresse in dem Auffrischadressdekoder 11 generiert wird. Erreicht der Auffrischadressdekoder die höchstmögliche Wortleitungsadresse X-ADR, so wird das nächste Auffrischen an der Wortleitung mit der niedrigsten X-Adresse durchgeführt. Der Selbstauffrischmodus wird durch ein externes Selbstauffrischsignal SFR bestimmt, mit dem ein erster Schalter 12 und ein zweiter Schalter 13 angesteuert werden. Bei aktivem Selbstauffrischsignal SFR ist der Auffrischzähler 10 mit dem Auffrischadressdekoder 11 und dieser mit dem Wortleitungsdekoder 7 verbunden.

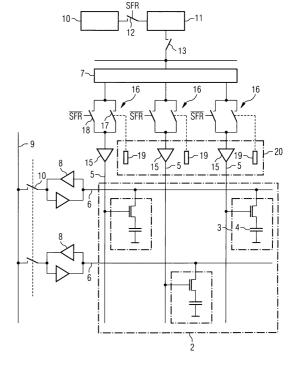

[0038] In Fig. 2 ist eine Speicherschaltung gemäß einer ersten Ausführungsform der Erfindung dargestellt. Gleiche Bezugszeichen entsprechen in den nachfolgenden Figuren Elementen gleicher oder ähnlicher Funktion. In der gezeigten Ausführungsform ist zwischen dem Wortleitungsdekoder 7 und dem jeweiligen Wortleitungstreiber 15 eine Schalteinrichtung 16 vorgesehen, die einen Auswahlschalter

17 und einen Modusschalter 18 aufweist. Der Auswahlschalter 17 und der Modusschalter 18 sind jeweils parallel zueinander geschaltet. Der Modusschalter 18 ist geschlossen, wenn sich die Speicherschaltung 1 nicht in dem Selbstauffrischmodus befindet, was durch das Selbstauffrischsignal SFR angegeben wird. D.h., der Wortleitungsdekoder 7 ist über die Wortleitungstreiber 15 mit den entsprechenden Wortleitungen verbunden, wenn sich die Speicherschaltung in einem Normalbetriebsmodus befindet. Die Auswahlschalter 17 sind über jeweilige Zustandsspeicherelemente 19 angesteuert, die abhängig von ihrem Zustand den entsprechenden Auswahlschalter 17 entweder schließen oder öffnen. Beispielsweise gibt eine logische "0" in dem Zustandsspeicherelement 19 an, dass der Auswahlschalter 17 geöffnet und eine logische "1" an, dass der zugeordnete Auswahlschalter 17 geschlossen ist. Bei einer logischen "1" kann der Wortleitungsdekoder 7 nun im Selbstauffrischmodus die entsprechende Wortleitung 5 aktivieren, um die daran befindlichen Speicherzellen aufzufrischen. Bei einer logischen "0" wird während des Selbstauffrischmodus eine solche Aktivierung der Wortleitung 5 unterbunden, da sowohl der Modusschalter 18 als auch der Auffrischschalter 17 der entsprechenden Wortleitung 5 geöffnet sind.

[0039] Wenn die Wortleitungen 5 nicht in regelmäßigen Abständen aktiviert werden, um die daran befindlichen Speicherzellen aufzufrischen, verlieren die Kondensatoren 4 der Speicherzellen 3 ihre Ladung, so dass eine darin gespeicherte Information verloren geht. Die Zustandsspeicherelemente 19 sind Teil eines Zustandsspeichers 20, wobei bei Anlegen der Betriebsspannung an die Speicherschaltung die Zustandsspeicherelemente 19 zunächst mit einer logischen "0" geladen sind, die angibt, dass die Auffrischschalter 17 geöffnet sind, so dass, wenn sich die Speicherschaltung im Selbstauffrischmodus befindet, kein Auffrischen der Speicherzellen 3 durch Aktivieren der Wortleitungen 5 erfolgen kann. Erst durch ein erstmaliges Beschreiben von Speicherzellen des Speicherzellenfeldes 2 werden einzelne Wortleitungen, an denen diese Speicherzellen angeordnet sind, ausgewählt, indem das der entsprechenden Wortleitung zugeordnete Zustandsspeicherelement 19 eine logische "1" eingeschrieben wird, so dass der zugehörige Auswahlschalter 17 geschlossen ist. Dadurch kann in dem Selbstauffrischmodus die entsprechende Wortleitung 5 kurzzeitig zum Auffrischen aktiviert werden.

[0040] Um Chipfläche zu sparen, kann ein Zustandsspeicherelement 19 für mehrere Wortleitungen vorgesehen sein, d.h. das Zustandsspeicherelement 19 dient zum Öffnen und Schließen mehrerer Auffrischschalter 17 für entsprechend mehrere Wortleitungen 5. Wurde zuvor zumindest eine der Speicherzellen der entsprechenden Wortleitungen 5 beschrieben, wird in das den Wortleitungen zugeordne-

te Zustandsspeicherelement 19 eine logische "1" gespeichert, so dass in dem Selbstauffrischmodus die entsprechenden Wortleitungen 5 regelmäßig aufgefrischt werden. Auch kann ein Zustandsspeicherelement 19 Wortleitungen verschiedener Speicherzellenfelder 2 (Speicherbänke) auswählen, so dass diese für ein Auffrischen vorgemerkt werden, wenn in einem entsprechenden Speicherbereich eines der Speicherzellenfelder hineingeschrieben wurde.

[0041] In Fig. 3 ist eine weitere Ausführungsform der erfindungsgemäßen Speicherschaltung 2 dargestellt. Ausgehend von der herkömmlichen Speicherschaltung, wie sie in Fig. 1 dargestellt ist, ist bei der Ausführungsform der Fig. 3 ein weiterer Wortleitungsdekoder 20 vorgesehen, der die von dem Auffrischadressdekoder 11 gelieferte Auffrischadresse dekodiert und jeweils an einem den Auffrischadressen zugeordneten Dekodrerausgang mit einem ersten Eingang eines UND-Gatters 22 verbindet, an dessen zweiten Eingängen ein jeweiliges Zustandsspeicherelement 21 angeschlossen ist. Die Zustandsspeicherelemente 21 geben wie bei der Ausführungsform der Fig. 2 an, welche Wortleitungen 5 mit den entsprechenden Speicherzellen aktiviert werden sollen und welche nicht. Die Ausgänge der UND-Gatter 22 sind miteinander verbunden, so dass die dort ausgegebenen Ausgangssignale miteinander verodert werden, so dass eine logische "1" an einem dritten Schalter 23 anliegt, wenn die durch die Auffrischadresse angegebene Wortleitung aktiviert werden soll, und dass eine logische "0" ausgegeben wird, wenn die durch die Auffrischadresse angegebene Wortleitung nicht aktiviert werden soll. Bei einer logischen "0" bleibt der dritte Schalter 23 geöffnet, so dass das Selbstauffrischungssignal nicht an dem Wortleitungsdekoder 7 anliegt und dieser somit deaktiviert ist. Das Vorsehen der durch den weiteren Wortleitungsdekoder 20, die Zustandsspeicherelemente 21, und die UND-Gatter 22 bereitgestellten Auswahlschaltung 24 zum Bereitstellen eines Auswahlsignals für den dritten Schalter 23 sind vorteilhaft, wenn mehrere Bänke von Speicherzellenfeldern 2 in der Speicherschaltung 1 vorgesehen sind, so dass mithilfe der Auswahlschaltung 24 gleichzeitig mehrere Wortleitungsdekoder 7 aktivierbar bzw. deaktivierbar sind, um das Auffrischen von Speicherzellen durch Aktivieren der betreffenden Wortleitung durchzuführen. Ebenso wie in der Ausführungsform der Fig. 2 ist eine Reduzierung der Zustandsspeicherelemente 21 möglich, wenn ein Zustandsspeicherelement 21 mehreren Wortleitungen 5 zugeordnet wird.

[0042] Mit Bezug auf Fig. 4 werden die Zustandsspeicherelemente 19, 21, wie sie in den Ausführungsformen der Fig. 2 und Fig. 3 sowie in den nachfolgend beschriebenen Ausführungsformen verwendet werden können, dargestellt. Fig. 4 zeigt ein Zustandsspeicherelement 19 mit einem SR-Flip-Flop 30 zum Speichern des Zustandssignals. Der Setzein-

gang S ist mit einem Ausgang eines ersten UND-Gatters 31 verbunden. Ein erster Eingang des ersten UND-Gatters 31 ist mit einem der Ausgänge für die Wortleitungen des Wortleitungsdekoders 7 (Ausführungsform der Fig. 2) bzw. des weiteren Wortleitungsdekoders **20** (Ausführungsform der Fig. 3) verbunden, so dass bei Aktivieren der dem Zustandsspeicherelement 19 zugeordneten Wortleitung eine logische "1" an dem ersten Eingang des ersten UND-Gatters 31 anliegt. Ein zweiter Eingang des ersten UND-Gatters 31 empfängt ein internes oder extern angelegtes Schreibsignal WRITE, das angibt, dass auf die durch die Wortleitungsadresse adressierte Wortleitung geschrieben werden soll. Dies führt dazu, dass an den Setzeingang S des Flip-Flops 30 eine logische "1" angelegt wird, so dass das Flip-Flop 30 eine logische "1" speichert und diese an einem Ausgang Q des Flip-Flops 30 ausgibt. Wie bereits zuvor mit Bezug auf die Fig. 2 und Fig. 3 beschrieben, bewirkt eine in dem Zustandsspeicherelement 19, 21 gespeicherte logische "1", dass die dem Zustandsspeicherelement 19, 21 zugeordnete Wortleitung 5 bei einem Auffrischen berücksichtigt wird, so dass die Inhalte der mit der Wortleitung verbundenen Speicherzellen 3 im Selbstauffrischmodus aufgefrischt werden. Ein Rücksetzeingang R des Flip-Flops 30 ist mit einem Ausgang eines ODER-Gatters 32 verbunden. An einen ersten Eingang des ODER-Gatters 32 ist ein Einschaltsignal POWERUP angelegt, das mit einer logischen "1" angibt, wenn die Speicherschaltung eingeschaltet wird und nach einer vorgegebenen Zeitspanne wieder eine logische "0" annimmt. Das Einschaltsignal bewirkt am Ausgang des ODER-Gatters eine logische "1", so dass das Flip-Flop 30 zurückgesetzt wird und eine logische "0" am Ausgang Q des Flip-Flops 30 anliegt. Da die gezeigte Schaltung der Zustandsspeicherelemente für alle Zustandsspeicherelemente 19, 21 identisch ist, ist somit nach dem Einschalten der Speicherschaltung in allen Zustandsspeicherelementen 19, 21 eine logische "0" gespeichert.

[0043] Ein zweiter Eingang des ODER-Gatters 32 ist mit einem Ausgang eines zweiten UND-Gatters 33 verbunden, an dessen ersten Eingang der zugeordnete Dekoderausgang des Wortleitungsdekoders 7 bzw. des weiteren Wortleitungsdekoders 20 angelegt ist. An einen zweiten Eingang des zweiten UND-Gatters 33 ist ein Freigabesignal UNWRITE angelegt, das angibt, dass die Speicherzellen, die an der durch die Wortleitungsadresse angegebenen Wortleitung angeordnet sind, nachfolgend bei einem Auffrischvorgang nicht mehr berücksichtigt werden müssen, da die darin gespeicherten Daten verworfen werden können. Das Freigabesignal UNWRITE ermöglicht es, einmal benötigte Speicherbereiche der Speicherschaltung freizugeben, d.h. von dem nachfolgenden Auffrischen wieder auszunehmen, um für das Auffrischen der freigegebenen Speicherzellen den Stromverbrauch zu reduzieren.

[0044] Bei mehreren Bänken der Speicherschaltung muss entweder zum Unterscheiden der mehreren Bänke bei der Aktivierung der entsprechenden Wortleitungen die jeweilige Bankadresse berücksichtigt werden, oder es werden durch Anlegen der Wortleitungsadresse X-ADR die entsprechenden Wortleitungen aller Bänke parallel aktiviert, so dass bei einem nachfolgenden Schreibbefehl WRITE oder Freigabesignal UNWRITE der Zustand der Flip-Flops 30 aller den entsprechenden Wortleitungen zugeordneten Zustandsspeicherelementen 19, 21 eingestellt wird.

[0045] Werden wie zuvor beschrieben mehrere Wortleitungen einem Zustandsspeicherelement zugeordnet, so wird das Zustandsspeicherelement 19, 21 anstatt durch eine spezifische Wortleitungsadresse X-ADR durch eine beliebige Wortleitungsadresse X-ADR dem dem Zustandsspeicherelement zugeordneten Wortleitungsadressbereich in Verbindung mit dem Schreibbefehl WRITE gesetzt. Zur Realisierung sind dazu weitere ODER-Schaltungen an den ersten Eingängen des ersten und zweiten UND-Gatters 31, 33 vorgesehen, an deren jeweiligen Eingänge alle entsprechenden Dekoderausgänge des Wortleitungsadressbereiches des Wortleitungsdekoders 7 bzw. des weiteren Wortleitungsdekoders 20 angelegt sind.

[0046] In Fig. 5 ist eine schematische Darstellung einer weiteren Ausführungsform der Speicherschaltung gemäß der Erfindung dargestellt, bei dem die Zustandsspeicherelemente als Teil der dynamischen Speicherzellen des Speicherzellenfeldes ausgebildet sind. Zur Vereinfachung der Darstellung sind die Speicherzellen als Kreise an den Schnittstellen von Wortleitungen 5 und Bitleitungen 6 angeordnet. Die Ausleseverstärker 8 sind jeweils mit zwei zueinander benachbarten Bitleitungen eines Bitleitungspaares verbunden, um den Inhalt einer Speicherzelle durch Detektieren eines Ladungsunterschiedes auf den Bitleitungen 6 des Bitleitungspaares nach dem Aktivieren einer der Wortleitungen 5 festzustellen. Bei dieser Ausführungsform werden die Zustandsspeicherelemente nicht separat, sondern als Teil des Speicherzellenfeldes 2 ausgebildet. Vorzugsweise werden dazu Speicherzellen am Rand des Speicherzellenfeldes vorgesehen, die zwischen prozesstechnisch notwendigen, so genannten Dummy-Speicherzellen und den regulären Speicherzellen zum Speichern der Nutzdaten angeordnet sind. Um ein Zustandsspeicherelement für jede der Wortleitungen vorzusehen, sind Speicherzellen an einem gemeinsamen Bitleitungspaar ausreichend. Das betreffende Bitleitungspaar ist mit einem weiteren Ausleseverstärker 40 verbunden, der nach dem Aktivieren einer der Wortleitungen 5 mithilfe des Wortleitungsdekoders zunächst die entsprechend aktivierte Zustandsspeicherzelle ausliest und bewertet. Die Ausleseverstärker 8 als auch der weitere Ausleseverstärker 40 können nach kurzer Zeit eine Bewertung der auf den Bitleitungen befindlichen Signale durchführen. Der Hauptteil des Stromverbrauchs betrifft jedoch das Trennen der Ladungen auf den Bitleitungen 6 des entsprechenden Bitleitungspaares auf den vollen Signalpegel. Abhängig von dem zuvor in der betreffenden ausgelesenen Zustandsspeicherzelle gespeicherten Wert werden nun die Ausleseverstärker 8 angesteuert. Ein Spreizen der Ladungen auf den Bitleitungen 6 des Bitleitungspaares durch den jeweiligen Ausleseverstärker 8 erfolgt nur dann, wenn in der Zustandsspeicherzelle eine entsprechende Information, z.B. eine logische "1" gespeichert ist und nicht eine logische "0" gespeichert ist. Dadurch wird nach dem Aktivieren der entsprechenden Wortleitung 5 verhindert, dass ein Stromverbrauch aus dem Spreizen von Ladungen von an der aktivierten Wortleitung befindlichen Speicherzellen erfolgt, obwohl die darin gespeicherten Informationen nicht erhalten werden sollen, da die Speicherzellen an der betreffenden Wortleitung 5 entweder nach dem Einschalten der Speicherschaltung noch nicht benutzt wurden oder die darin zuvor gespeicherte Information verworfen werden kann.

[0047] Da die Zustandsspeicherzellen an Wortleitungen mit gerader Wortleitungsadresse an einer ersten Bitleitung des Bitleitungspaares und Zustandsspeicherzellen an Wortleitungen mit einer ungeraden Wortleitungsadresse an einer zweiten Bitleitung des Bitleitungspaares angeordnet sind, muss je nachdem über welche der Wortleitungen, d.h. gerade oder ungerade, die Zustandsspeicherzelle ausgelesen wird, entweder das Datum von der ersten oder zweiten Bitleitung des Bitleitungspaares, an dem die Zustandsspeicherzellen angeordnet sind, ausgelesen werden. Auf gleiche Weise ist darauf zu achten, dass je nach Wortleitungsadresse die Zustandsspeicherzellen abhängig von dem Schreibbefehl, dem Freigabesignal UNWRITE und der Wortleitungsadresse in richtiger Weise über die CSL-Schalter 41 beschrieben werden. Um den Inhalt der betreffenden adressierten Zustandsspeicherzelle korrekt auszugeben, sind die Ausgänge des weiteren Ausleseverstärkers 40 mit einem Demultiplexer 42 verbunden, um entweder den Signalpegel der ersten Bitleitung oder der zweiten Bitleitung des Bitleitungspaares, an dem die Zustandsspeicherzellen angeordnet sind, auszugeben und in geeigneter Weise den Ausleseverstärkern 8 zur Verfügung zu stellen, so dass diese ein Auslesen nur dann vornehmen, wenn z.B. eine logische "1" angelegt ist.

[0048] Die Ausleseverstärker 8 werden zumindest nach dem Aktivieren der entsprechenden Wortleitung leicht verzögert, so dass zunächst die betreffende Zustandsspeicherzelle durch den weiteren Ausleseverstärker 40 bewertet werden kann, und anschließend abhängig von dem Zustandsspeicherwert der Zustandsspeicherzelle die Ausleseverstärker 8 aktiviert oder deaktiviert werden. Bei Aktivieren der Aus-

leseverstärker 8 wird ein Ladungsunterschied auf dem mit ihnen verbundenen Bitleitungspaar verstärkt und dadurch die durch die aktivierte Wortleitung adressierte Speicherzelle erneut geladen, d.h. die Ladung des Kondensators der Speicherzelle aufgefrischt. Wird eine logische "0" aus der Zustandsspeicherzelle ausgelesen und ein entsprechendes Steuersignal 55 an die Ausleseverstärker 8 angelegt, bewerten die Ausleseverstärker 8 den Ladungsunterschied auf den entsprechen Bitleitungspaaren nicht bzw. nicht vollständig und der Bewertungsstrom wird dadurch eingespart. Die Potenzialdifferenz von ca. 200 mV durch das Aufschalten der Speicherzellen auf die Bitleitungen des jeweiligen Bitleitungspaares werden anschließend durch eine (nicht gezeigte) Ausgleichsschaltung ausgeglichen und dadurch in die betreffenden Speicherzellen ein Mittenpotenzial geladen. Wird im Normalbetriebsmodus eine Wortleitung aktiviert, so wird auch die entsprechende Zustandsspeicherzelle über den weiteren Ausleseverstärker 40 ausgelesen. Wird dann ein Schreibbefehl WRITE (bei gleicher Bankadresse) empfangen, so wird ein WRITE-Schalter 42 geschlossen. Abhängig davon, ob eine gerade oder ungerade Wortleitung aktiviert (angezeigt durch ein entsprechendes an den Schaltern 45, 46 angelegtes Signal) ist, findet eine Invertierung des Schreibsignals in dem Inverter 43 statt und das resultierende Signal wird als differenzielles Signal über die CSL-Schalter 41 an den weiteren Ausleseverstärker 40 weitergegeben. Lediglich ein Freigabekommando UNWRITE, das zum Bereitstellen einer logischen "0" über einen Freigabeschalter 44 führt, kann dazu führen, dass eine logische "0" in der betreffenden Speicherzelle gespeichert wird. Dazu wird ebenfalls berücksichtigt, ob sich die Zustandsspeicherzelle der betreffenden Wortleitung an einer geraden oder ungeraden Wortleitung befinden und mithilfe des Inverters 43 der korrekte Zustand in die Zustandsspeicherzelle geschrieben.

**[0049]** Das Beschreiben und das Auswerten der Zustandsspeicherzellen lässt sich auch vornehmen, wenn die Bitleitungen miteinander vertwistet sind. In diesem Fall ist die Schaltung des weiteren Ausleseverstärkers **40** in entsprechender Weise anzupassen.

[0050] Da nach dem Einschalten der Speicherschaltung die Zustandsspeicherzellen nicht vordefiniert sind, kann das Auslesen der Zustandsspeicherzellen anfänglich zu willkürlichen Bewertungsergebnissen führen. Es ist jedoch notwendig, die Zustandsspeicherzellen nach dem Einschalten der Speicherzellen eindeutig vorzudefinieren, so dass zunächst die Zustandsspeicherzellen mit einer logischen "0" beschrieben werden. Dies kann beispielsweise durch einen geeigneten Testmodus erfolgen, bei dem alle Wortleitungen gleichzeitig aktiviert werden und wobei alle Zustandsspeicherzellen gleichzeitig mit einem entsprechenden Freigabekommando UNWRITE vordefiniert werden können. Aus diesem Grunde ist es

sinnvoll, dem Anwender der Speicherschaltung einen zusätzlich entsprechenden Freigabebefehl zur vollständigen Freigabe aller Speicherzellen zur Verfügung zu stellen, d.h. zum Einstellen aller Zustandsspeicherzellen auf einen Zustand, bei dem keine der Wortleitungen bei einem Selbstauffrischmodus aufgefrischt werden. Zur Unterscheidung eines Befehls zur vollständigen Freigabe gegenüber einem Freigabebefehl für eine einzelne Wortleitungsadresse kann ein beliebiges Adressbit der mit dem Freigabebefehl übergebenen Bitleitungsadresse benutzt werden.

[0051] Dynamische Speicherzellen haben in der Regel einen bevorzugten Potenzialzustand, der sich einstellt, wenn längere Zeit kein Auffrischen der Speicherzellen stattgefunden hat oder der Leckstrom zu hoch ist. Üblicherweise ist ein hoher Potenzialpegel als Ladung in den Kondensatoren der Speicherzelle der instabile Potenzialzustand, so dass sich die Speicherzellen typischerweise zu einem niedrigen Potenzialzustand, d.h. zu einer physikalischen "0" entladen. Zuvor wurde eine gespeicherte physikalische "1" als Zustandsspeicherwert für eine bereits beschriebene, d.h. aufzufrischende Wortleitung und eine physikalische "0" als Zustandsspeicherwert für eine nicht aufzufrischende Wortleitung gewählt. Diese zunächst willkürliche Definition der Zustandsspeicherwerte ist vertretbar, solange sichergestellt ist, dass die Zustandsspeicherzellen auf mindestens die gleiche Retentionsspezifikation getestet sind wie die regulären Speicherzellen, d.h. die gespeicherte Information mindestens solange ohne ein Auffrischen speichern können wie die regulären Speicherzellen. Das Verlieren der Ladung einer Zustandsspeicherzelle könnte ansonsten bis zum nächsten Auffrischvorgang zu einem Wechsel des Zustandsspeicherwertes führen. Ein solcher Wechsel des Zustandsspeicherwertes findet bei einem Speicherzellenfeld der oben angegebenen Art typischerweise von einer physikalischen "1" auf eine physikalische "0" statt, was bei der gegenwärtigen Definition zur Folge hätte, dass der Zustandsspeicherwert einer benutzten Wortleitung in dem Zustandsspeicherwert zu einer unbenutzten Wortleitung, d.h. einer Wortleitung, die nicht aufgefrischt werden soll, übergeht. Dadurch könnte ein notwendiges Auffrischen einer der Wortleitungen unterdrückt werden und die Daten in allen auf dieser Wortleitung tatsächlich zum Speichern von Daten verwendeten Speicherzellen zerstört werden. Daher ist ein ausführliches Testen der Zustandsspeicherzellen notwendig, um eine zuverlässige Speicherwirkung zu garantieren.

[0052] Wird die Zuordnung invertiert, d.h. eine physikalische "0" entspricht einer Wortleitung, die aufgefrischt werden soll und eine physikalische "1" entspricht einer Wortleitung, bei der das Auffrischen unterbleiben kann, so ist eine schlechte Retentionszeit einer Zustandsspeicherzelle für die weitere Funktion im Autoauffrischmodus unkritisch. Ist die Zustands-

speicherzelle schwach, d.h. verliert sie ihre gespeicherte Ladung sehr schnell von einem hohen Ladungspotenzial auf ein niedriges Ladungspotenzial (von einer physikalischen "1" auf eine physikalische "0"), so erfolgt eine Bewertung dieser eigentlich unbenutzten Wortleitung zugeordneten Speicherzellen, was sich in einer geringfügigen aber unnötigen Stromerhöhung im Selbstauffrischmodus auswirkt. Eine funktionelle Störung im Falle von schlechten Zustandsspeicherzellen, d.h. Zustandsspeicherzellen mit einer geringen Datenhaltezeit (Retention) wird also verhindert durch eine unter Umständen weniger Reduktion der Stromaufnahme optimierte Selbstauffrischmodus. Es ist möglich, bei einer solchen Zuordnung der Zustandssignale völlig auf das Testen der Zustandsspeicherzellen durch einen weiteren Testmodus zu verzichten.

[0053] Im Allgemeinen ist in den Zustandsspeicherzellen ein erster Zustand eines Zustandsspeicherwertes definiert, der angibt, dass ein Auffrischen erfolgen soll und ein zweiter Zustand des Auffrischdatums definiert, der angibt, dass kein Auffrischen erfolgen soll, wobei der erste Zustand einem Potenzialpegel entspricht, in dessen Richtung sich die Zustandsspeicherzelle durch Leckströme im nicht adressierten Zustand entladen. Ändert sich die Ladung in den Zustandsspeicherzellen in Richtung eines hohen Ladungspotenzials, d.h. in Richtung einer physikalischen "1", so wird entsprechend die physikalische "1" so definiert, dass die entsprechende Wortleitung bei einem Auffrischen berücksichtigt wird und eine physikalische "0" entspricht einer Wortleitung, die bei einem Auffrischen unberücksichtigt bleiben soll.

[0054] In der in Fig. 6 gezeigten Ausführungsform wird eine alternative Möglichkeit dargestellt, die Speicherschaltung auszubilden. Dabei werden die physikalischen Zustandsspeicherwerte der Zustandsspeicherzellen nicht fest mit einem Zulassen eines Auffrischens bzw. Blockieren eines Auffrischens der Speicherzellen an der betreffenden Wortleitung verbunden. Im gezeigten Ausführungsbeispiel erlaubt wie zuvor beschrieben eine logische "0" die Bewertung der übrigen Bitleitungen durch die Ausleseverstärker 8 und eine logische "1" verhindert das Auswerten bzw. das Spreizen der Ladungen auf den Bitleitungspaaren, mit denen die Ausleseverstärker 8 verbunden sind. Eine logische "0" kann aus den entsprechenden Zustandsspeicherzellen ausgelesen werden, wenn entweder ein niedriges Ladungspotenzial der Kondensatoren der betreffenden Speicherzellen an der ersten Bitleitung 6<sub>opp</sub> oder ein hohes Ladungspotenzial in den Kondensatoren der Speicherzellen an der entsprechenden zweiten Bitleitung 6<sub>EVEN</sub> des Bitleitungspaares, an dem die Zustandsspeicherzellen angeordnet sind, gespeichert ist. Da der weitere Ausleseverstärker 40 die auf dem Bitleitungspaar bestehende Ladungsdifferenz an die beiden Ausgangsleitungen 51 und 52 verstärkt ausgibt, kann ein Zustand einer positiven Potenzialdifferenz zwischen der ersten und der zweiten Ausgangsleitung 51, 52 oder in einer negativen Potenzialdifferenz zwischen den beiden Ausgangsleitungen festgelegt werden. Eine positive Potenzialdifferenz bedeutet für die Zustandsspeicherzellen an der ersten Bitleitung  $6_{\text{ODD}}$  ein hohes Ladungspotenzial in dem Kondensator und für die Zustandsspeicherzellen an der zweiten Bitleitung  $6_{\text{EVEN}}$  ein niedriges Ladungspotenzial in dem Kondensator der betreffenden Zustandsspeicherzelle. Dies gilt umgekehrt für eine negative Potenzialdifferenz an den Ausgangsleitungen 51, 52. Dadurch lässt sich die Schreibschaltung zum Beschreiben der Zustandsspeicherzellen etwas vereinfachen.

[0055] In Fig. 7 ist ein Ausschnitt aus einer Speicherschaltung gemäß einer weiteren Ausführungsform der Fig. 6 dargestellt, bei dem lediglich die Zustandsspeicherzellen und entsprechende weitere Ausleseverstärker 40 gezeigt sind. Bei dieser Ausführungsform wird der Zustandsspeicherwert, der angibt, ob die betreffende Wortleitung aufgefrischt werden soll oder nicht, in zwei Speicherzellen gespeichert. Ein solches Doppelzellenkonzept sieht vor, an beiden Bitleitungen eines Bitleitungspaares und an einer Wortleitung eine Speicherzelle vorzusehen, die zueinander entgegengesetzt geladen werden, so dass je nach zu speichernder Information eine positive oder eine negative Ladungsdifferenz beim Aktivieren der Wortleitung auf die Bitleitung des Bitleitungspaares fließen. Ein solches Doppelzellenkonzept ist bereits für reguläre Speicherzellen bekannt und ermöglicht eine erhöhte Auswertesicherheit der Zustandsspeicherzellen, indem zwei Speicherzellen für das Speichern des Zustandsspeicherwertes zur Verfügung stehen. Um die Anordnung der Speicherzellen im Speicherzellenfeld dazu nicht zu verändern, werden zwei weitere Ausleseverstärker 40 vorgesehen, die an zwei benachbarten Bitleitungspaaren angeordnet sind, wobei die beiden ersten Bitleitungen 6<sub>odd</sub> der Bitleitungspaare mit einem ersten der weiteren Ausleseverstärker 40 und die beiden zweiten Bitleitungen 6<sub>even</sub> der beiden Bitleitungspaare mit einem zweiten weiteren Ausleseverstärker 40 verbunden sind, wobei zwei Bitleitungen zum Anschluss an die entsprechenden Ausleseverstärker über Kreuz geführt sein können.

[0056] In Fig. 8 ist ein Ausschnitt aus einer erfindungsgemäßen Speicherschaltung mit einem lokalen Wortleitungstreiber 60 dargestellt, der Wortleitungsabschnitte einer Wortleitung 6 separat treibt. Die lokalen Wortleitungstreiber 60 sind üblicherweise vorgesehen, um das Aktivieren der Wortleitung, d.h. zu deren Umladen, zu beschleunigen, so dass die Ladungen schneller aus den betreffenden Speicherzellen ausgelesen werden können. Es kann nun vorgesehen sein, dass die lokalen Wortleitungstreiber 60 mit einem Steueranschluss 61 versehen sind, um ein Steuersignal WS zu empfangen, das angibt, ob der

### DE 10 2006 020 098 A1 2007.10.31

lokale Wortleitungstreiber **60** aktiviert werden soll oder nicht, abhängig von dem in der zugeordneten Zustandsspeicherzelle gespeicherten Zustandsspeicherwert. So kann bereits die Funktion der lokalen Wortleitungstreiber unterdrückt werden, wenn der weitere Ausleseverstärker **40** in dem der Wortleitung zugeordneten Speicherzelle detektiert hat, dass kein Auffrischen erfolgen soll. Auf diese Weise kann das Aufschalten der Speicherkondensatoren auf die betreffenden Bitleitungen unterbunden werden, so dass durch die abgeschalteten lokalen Wortleitungstreiber der Stromverbrauch weiter gesenkt werden kann.

[0057] Es kann weiterhin vorgesehen sein, dass bei mehreren lokalen Wortleitungstreibern, die eine Wortleitung in mehrere Wortleitungsabschnitte unterteilt, für jeden der Wortleitungsabschnitte eigene Zustandsspeicherzellen vorgesehen sein können, so dass sich für jeden Wortleitungsabschnitt festlegen lässt, ob ein Auffrischen stattfinden soll oder unterbunden werden soll. Dazu werden Zustandsspeicherzellen an mehreren Bitleitungspaaren vorgesehen, wobei die Anzahl der Bitleitungspaare mit Zustandsspeicherzellen der Anzahl mindestens der separat voneinander auffrischbaren Wortleitungsabschnitte entspricht. Selbstverständlich ist es auch denkbar, für mehrere Wortleitungsabschnitte eine gemeinsame Zustandsspeicherzelle vorzusehen.

[0058] Die vorstehenden Ausführungsformen wurden anhand von Ausführungsbeispielen mit intern generierten Auffrischsignalen beschrieben. Es ist jedoch auch möglich, das Konzept der vorliegenden Erfindung auf Speicherschaltungen anzuwenden, bei dem Auffrischsignale extern an die Speicherschaltung angelegt werden. Die in den Ausführungsformen beschriebenen Konzepte zur Realisierung eines reduzierten Stromverbrauchs in der Speicherschaltung können auch miteinander kombiniert werden, um weitere Ausführungsformen der Erfindung zu erhalten.

#### Bezugszeichenliste

| •  | operations                |

|----|---------------------------|

| 2  | Speicherzellenfeld        |

| 3  | Speicherzelle             |

| 4  | Kondensator               |

| 5  | Wortleitung               |

| 6  | Bitleitung                |

| 7  | Wortleitungsdekoder       |

| 8  | Ausleseverstärker         |

| 9  | Datenleitung              |

| 10 | Auffrischzähler           |

| 11 | Auffrischadressdekoder    |

| 12 | Erster Auffrischschalter  |

| 13 | Zweiter Auffrischschalter |

| 14 | Schalter                  |

| 15 | Wortleitungstreiber       |

| 16 | Schalteinrichtung         |

|    |                           |

Speicherschaltung

| • •    | / tabwai iiboi laitoi       |

|--------|-----------------------------|

| 18     | Modusschalter               |

| 19     | Zustandsspeicherelemente    |

| 20     | Zustandsspeicher            |

| 21     | Zustandsspeicherelemente    |

| 22     | UND-Gatter                  |

| 23     | Dritter Schalter            |

| 24     | Auswahlschaltung            |

| 30     | SR-Flip-Flop                |

| 31     | erstes UND-Gatter           |

| 32     | ODER-Gatter                 |

| 33     | Zweites UND-Gatter          |

| 34     | weiterer Ausleseverstärker  |

| 41     | CSL-Schalter                |

| 42     | Demultiplexer               |

| 43     | Inverter                    |

| 44     | Freigabeschalter            |

| 51, 52 | Ausgangsleitungen           |

| 60     | lokaler Wortleitungstreiber |

| 61     | Steueranschluss             |

| Т      | Auswahltransistor           |

Auswahlschalter

#### Patentansprüche

- 1. Speicherschaltung (1) umfassend:

- ein Speicherzellenfeld (2) mit an Wortleitungen (5) und Bitleitungen (6) angeordneten dynamischen Speicherzellen (3);

- eine Auswahleinheit (20) zum Bereitstellen einer Auswahlinformation; und

- eine Auffrischschaltung (**10**, **11**, **16**), um jeweils abhängig von der Auswahlinformation die Speicherzellen (**3**) auszuwählen und die ausgewählten Speicherzellen aufzufrischen, so dass jeweils eine darin gespeicherte Information erhalten bleibt.

- 2. Speicherschaltung (1) nach Anspruch 1, wobei die Auswahleinheit (20) einen Zustandsspeicher aufweist, um die Auswahlinformation zu speichern.

- 3. Speicherschaltung (1) nach Anspruch 2, wobei die Auswahleinheit weiterhin eine Programmierschaltung (31, 32, 33) aufweist, um den Zustandsspeicher abhängig von einem Schreibbefehl auf eine Adresse des Speicherzellenfeldes (2) so mit einem ersten Zustand zu beschreiben, dass die Auffrischschaltung (10, 11, 16) bei einem nachfolgenden Auffrischen die Speicherzellen (3) an der Adresse auffrischt, und um den Zustandsspeicher abhängig von einem Freigabesignal bezüglich einer Adresse des Speicherzellenfeldes so mit einem zweiten Zustand zu beschreiben, dass die Auffrischschaltung bei einem nachfolgenden Auffrischen das Auffrischen der Speicherzellen an der Adresse unterdrückt.

- 4. Speicherschaltung (1) nach Anspruch 2 oder 3, wobei ein Wortleitungsdekoder (7) vorgesehen ist, um abhängig von einer Adressinformation eine der Wortleitungen (5) zum Aktivieren auszuwählen; wobei die Auffrischschaltung (10, 11, 16) einen Adress-

geber aufweist, der nacheinander eine Adressinformation zum Adressieren jeder der Wortleitungen (5) bereitstellt.

- 5. Speicherschaltung nach Anspruch 4, wobei die Auffrischschaltung (10, 11, 16) weiterhin Auswahlschalter aufweist, die jeweils zwischen dem Wortleitungsdekoder (7) und jeder der Wortleitungen (5) angeordnet sind, um abhängig von der von der Auswahleinheit (20) bereitgestellten Auswahlinformation ein Aktivieren der entsprechenden Wortleitung durch die Auffrischschaltung (10, 11, 16) zuzulassen oder zu verhindern.

- 6. Speicherschaltung (1) nach Anspruch 5, wobei weitere Auswahlschalter vorgesehen sind, die parallel zu den Auswahlschaltern angeordnet sind, wobei die Auffrischschaltung gestaltet ist, um die weiteren Auswahlschalter in einem Auffrischmodus zu öffnen und in einem Normalbetriebsmodus zu schließen.

- 7. Speicherschaltung (1) nach Anspruch 5 oder 6, wobei der Zustandsspeicher Zustandsspeicherelemente (19, 21) aufweist, die jeweils einer der Wortleitungen (5) zugeordnet sind, wobei jeder der Auswahlschalter (16) mit einem zugeordneten Zustandsspeicherelement (19, 21) verbunden ist, so dass der Schaltzustand jedes der Auswahlschalter (16) von einem in dem Zustandsspeicherelement (19, 21) gespeicherten Datum abhängt.

- 8. Speicherschaltung (1) nach Anspruch 7, wobei jedes der Zustandsspeicherelemente eine Programmierschaltung (31, 32, 33) aufweist, um bei Beschreiben einer Speicherzelle an einer der Wortleitungen das zugeordnete Zustandsspeicherelement in einen ersten Zustand zu versetzen, und um das zugeordnete Zustandsspeicherelement in einen zweiten Zustand zu versetzen, wenn die Speicherschaltung eingeschaltet wird oder ein Freigabesignal bereitgestellt wird, wobei die Auswahlschalter bei einem ersten Zustand des jeweils zugeordneten Zustandsspeicherelementes geschlossen sind und bei einem zweiten Zustand des jeweils zugeordneten Zustandsspeicherelementes geöffnet sind.

- 9. Speicherschaltung (1) nach Anspruch 2, wobei die Zustandsspeicherelemente (19, 21) als dynamische Speicherzellen entlang einer oder mehrerer Bitleitungen (6) in dem Speicherzellenfeld vorgesehen sind, so dass an jeder der Wortleitungen (5) eine Zustandsspeicherzelle angeordnet und durch Aktivieren der Wortleitung auslesbar ist, wobei erste Ausleseverstärker vorgesehen sind, die jeweils mit mindestens einer der Bitleitungen, die mit den dynamischen Speicherzellen verbunden sind, verbunden sind, und wobei ein zweiter Ausleseverstärker vorgesehen ist, der mit einer oder mehreren Bitleitungen, die mit den Zustandsspeicherzellen verbunden sind, verbunden ist, wobei die ersten und zweiten Ausleseverstärker

zum Auffrischen aktivierbar sind, wobei die Auffrischschaltung (10, 11, 16) die Ausleseverstärker nacheinander aktiviert, um den Zustand der Zustandsspeicherzelle (19) an der aktivierten Wortleitung durch den zweiten Ausleseverstärker (40) zu detektieren und um die ersten Ausleseverstärker (8) abhängig von dem Zustand in der Zustandsspeicherzelle zum Verstärken der Ladung auf der zugeordneten einen oder mehreren zugeordneten Bitleitungen zu aktivieren oder zu deaktivieren.

- 10. Speicherschaltung (1) nach Anspruch 9, wobei eine Programmierschaltung (31, 32, 33) vorgesehen ist, um die Zustandsspeicherzellen mit einem ersten Zustand eines Auffrischdatums, der angibt, dass ein Auffrischen erfolgen soll, oder einem zweiten Zustand, der angibt, dass kein Auffrischen erfolgen soll, zu beschreiben, wobei der erste Zustand einem Potentialpegel entspricht, in dessen Richtung sich die Zustandsspeicherzellen durch Leckströme im nicht adressierten Zustand entladen.

- 11. Speicherschaltung (1) nach Anspruch 9 oder 10, wobei eine Zustandsspeicherzelle durch mehrere dynamische Speicherzellen gebildet ist.

- 12. Speicherschaltung (1) nach einem der Ansprüche 9 bis 11, wobei die Wortleitungen (5) mit mehreren lokalen Wortleitungstreibern versehen sind, um jeweils Abschnitte der entsprechenden Wortleitung (5) zu aktivieren, wobei die Wortleitungstreiber abhängig von dem Inhalt der der entsprechenden Wortleitung (5) zugeordneten Zustandsspeicherzelle (19) aktivierbar sind.

- 13. Speicherschaltung (1) nach Anspruch 12, wobei jedem Abschnitt der jeweiligen Wortleitung (5) eine entsprechende Zustandsspeicherzelle (19) zugeordnet ist.

- 14. Speicherschaltung (1) nach Anspruch 4, wobei die Auffrischschaltung (10, 11, 16) weiterhin eine Auswahlschaltung aufweist, um die Adressinformation abhängig von der von der Auswahleinheit bereitgestellten Auswahlinformation an den Wortleitungsdekoder weiterzuleiten.

- 15. Speicherschaltung (1) nach Anspruch 14, wobei mehrere Wortleitungsdekoder (7) für mehrere Speicherzellenfelder vorgesehen sind, wobei die Auswahleinheit ausgebildet ist, um die Adressinformation abhängig von der von der Auswahleinheit bereitgestellten Auswahlinformation an jeden der Wortleitungsdekoder weiterzuleiten.

- 16. Verfahren zum Auffrischen von dynamischen Speicherzellen (3) in einem Speicherzellenfeld (2), wobei die Speicherzellen (3) an Wortleitungen (5) und Bitleitungen (6) angeordnet sind, mit den folgenden Schritten:

- Bereitstellen einer Auswahlinformation;

- Auswählen von Speicherzellen abhängig von der Auswahlinformation;

- Auffrischen der ausgewählten Speicherzellen abhängig von der Auswahlinformation.

- 17. Verfahren nach Anspruch 16, wobei die Auswahlinformation gespeichert wird.

- 18. Verfahren nach Anspruch 17, wobei eine der Wortleitungen (5) zum Aktivieren abhängig von einer Adressinformation ausgewählt wird; wobei nacheinander eine Adressinformation zum Adressieren jeder der Wortleitungen (5) bereitgestellt wird.

- 19. Verfahren nach Anspruch 16, wobei abhängig von der bereitgestellten Auswahlinformation ein Aktivieren der entsprechenden Wortleitung (**5**) zugelassen oder verhindert wird.

- 20. Verfahren nach Anspruch 17, wobei bei Beschreiben mindestens einer Speicherzelle (3) an einer der Wortleitungen (5) das zugeordnete Zustandsspeicherelement (19) in einen ersten Zustand versetzt wird, und das zugeordnete Zustandsspeicherelement in einen zweiten Zustand versetzt wird, wenn die Speicherschaltung eingeschaltet wird oder ein Freigabesignal bereitgestellt wird, wobei die entsprechende Wortleitung bei einem ersten Zustand des jeweils zugeordneten Zustandsspeicherelementes aktivierbar sind und bei einem zweiten Zustand des jeweils zugeordneten Zustandsspeicherelementes nicht aktivierbar sind.

- 21. Verfahren nach Anspruch 16, wobei die Adressinformation abhängig von der von der Auswahleinheit bereitgestellten Auswahlinformation an den Wortleitungsdekoder weitergeleitet wird.

- 22. Verfahren nach Anspruch 16, wobei der Zustandsspeicher als Teil des Speicherzellenfeldes ausgebildet ist, so dass an jeder der Wortleitungen eine Zustandsspeicherzelle angeordnet ist, wobei erste Ausleseverstärker vorgesehen sind, die jeweils mit mindestens einer der Bitleitungen verbunden sind, und wobei ein zweiter Ausleseverstärker vorgesehen ist, der mit der einen oder mehreren Bitleitungen, die mit den Zustandsspeicherzellen verbunden sind, vorgesehen ist, wobei die Ausleseverstärker nacheinander aktiviert werden, um den Zustand der Zustandsspeicherzelle an der aktivierten Wortleitung zunächst durch den zweiten Ausleseverstärker zu detektieren und die ersten Ausleseverstärker abhängig von dem Zustand in der Zustandsspeicherzelle zum Verstärken der Ladung auf der zugeordneten einen oder den zugeordneten mehreren Bitleitungen aktiviert werden oder deaktiviert werden.

Es folgen 6 Blatt Zeichnungen

## Anhängende Zeichnungen