(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6975721号

(P6975721)

(45) 発行日 令和3年12月1日(2021.12.1)

(24) 登録日 令和3年11月10日(2021.11.10)

|              |           |      |       |     |

|--------------|-----------|------|-------|-----|

| (51) Int.Cl. | F 1       |      |       |     |

| H04R 3/00    | (2006.01) | H04R | 3/00  | 330 |

| A61B 8/14    | (2006.01) | A61B | 8/14  |     |

| H04R 19/00   | (2006.01) | H04R | 19/00 | 330 |

請求項の数 11 (全 23 頁)

|                    |                               |

|--------------------|-------------------------------|

| (21) 出願番号          | 特願2018-550321 (P2018-550321)  |

| (86) (22) 出願日      | 平成29年3月31日 (2017.3.31)        |

| (65) 公表番号          | 特表2019-514256 (P2019-514256A) |

| (43) 公表日           | 令和1年5月30日 (2019.5.30)         |

| (86) 国際出願番号        | PCT/US2017/025269             |

| (87) 国際公開番号        | W02017/173211                 |

| (87) 国際公開日         | 平成29年10月5日 (2017.10.5)        |

| 審査請求日              | 令和2年3月25日 (2020.3.25)         |

| (31) 優先権主張番号       | 15/087, 943                   |

| (32) 優先日           | 平成28年3月31日 (2016.3.31)        |

| (33) 優先権主張国・地域又は機関 | 米国 (US)                       |

|           |                                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 515244151<br>バタフライ ネットワーク, インコーポレイテッド<br>アメリカ合衆国, コネチカット州 O 6 4<br>3 7 ギルフォード, オールド ウィット<br>フィールド ストリート 530 |

| (74) 代理人  | 100079108<br>弁理士 稲葉 良幸                                                                                      |

| (74) 代理人  | 100109346<br>弁理士 大貫 敏史                                                                                      |

| (74) 代理人  | 100117189<br>弁理士 江口 昭彦                                                                                      |

| (74) 代理人  | 100134120<br>弁理士 内藤 和彦                                                                                      |

最終頁に続く

(54) 【発明の名称】両極性パルサー用の対称受信スイッチ

## (57) 【特許請求の範囲】

## 【請求項 1】

静電容量型超音波トランステューサと、

前記静電容量型超音波トランステューサに結合され、かつ、出力端子から前記静電容量型超音波トランステューサに両極性入力信号を供給するように構成された両極性パルサーと、

前記静電容量型超音波トランステューサによって出力された電気信号を処理するように構成された受信回路と、

第1のトランジスタ及び第2のトランジスタを備える対称スイッチであって、前記両極性パルサーの前記出力端子と前記静電容量型超音波トランステューサとの間に結合された入力端子を有し、かつ前記受信回路に結合された出力端子を有する、対称スイッチと、を備え、

前記第1のトランジスタは、第1のゲート、第1のソース、及び、第1のドレインを有し、

前記第2のトランジスタは、第2のゲート、第2のソース、及び、第2のドレインを有し、

前記第1のゲートは、前記第2のゲートに接続され、前記第1のゲート及び前記第2のゲートの電位は、第1の端子を介して第1の制御信号により制御され、前記第1のソースは、前記第2のソースに接続され、前記第1のソース及び前記第2のソースの電位は、第2の端子を介して第2の制御信号により制御され、

10

20

前記第1のゲート及び前記第1のソースは、第1の時間で第1の同じ電位に、かつ第2の時間で第2の同じ電位に結合されているか又は結合可能である、超音波機器。

**【請求項2】**

前記受信回路は、電流／電圧変換器を備える、請求項1に記載の超音波機器。

**【請求項3】**

前記電流／電圧変換器は、トランスインピーダンス増幅器(TIA)を備える、請求項2に記載の超音波機器。

**【請求項4】**

前記対称スイッチの前記第1のトランジスタ及び前記第2のトランジスタは、p型金属酸化膜半導体(PMOS)トランジスタである、請求項1に記載の超音波機器。 10

**【請求項5】**

前記対称スイッチの前記第1のトランジスタ及び前記第2のトランジスタは、n型金属酸化膜半導体(NMOS)トランジスタである、請求項1に記載の超音波機器。

**【請求項6】**

超音波機器を動作させる方法であって、

両極性パルサーから静電容量型超音波トランスデューサの第1の端子に両極性パルサー信号を前記超音波機器の送信動作モード中に供給することと、

前記静電容量型超音波トランスデューサの前記第1の端子と受信回路との間に結合されている対称スイッチを前記送信動作モード中に開状態で動作させることであって、前記対称スイッチは、第1のゲート、第1のソース、及び第1のドレインを有する第1のトランジスタと、第2のゲート、第2のソース、及び第2のドレインを有する第2のトランジスタとを備え、前記第1のゲートは、前記第2のゲートに接続され、前記第1のソースは、前記第2のソースに接続されていることと、 20

前記対称スイッチを前記超音波機器の受信動作モード中に閉状態で動作させることと、を含み、

前記対称スイッチを前記送信動作モード中に開状態で動作させることは、

前記第1のゲート、前記第2のゲート、前記第1のソース、及び前記第2のソースを第1の時間で第1の同じ電位に結合させること、

前記第1のゲート、前記第2のゲート、前記第1のソース、及び前記第2のソースを第2の時間で第2の同じ電位に結合させること、 30

前記第1のゲート、前記第2のゲート、前記第1のソース、及び前記第2のソースを第3の時間で前記第1の同じ電位に再び結合させること、

を含む、方法。

**【請求項7】**

前記受信回路の電流／電圧変換器を使用して、前記受信動作モード中に、前記静電容量型超音波トランスデューサからの電流を電圧に変換することを更に含む、請求項6に記載の方法。

**【請求項8】**

前記静電容量型超音波トランスデューサからの前記電流を前記電圧に変換することは、トランスインピーダンス増幅器(TIA)を用いて行われる、請求項7に記載の方法。 40

**【請求項9】**

前記超音波機器の受信動作モード中に前記対称スイッチを開状態で動作させることは、前記静電容量型超音波トランスデューサの出力信号を前記対称スイッチの前記第1のトランジスタの前記第1のドレイン上で受け取ることと、前記出力信号を前記対称スイッチの前記第2のトランジスタの前記第2のドレインから前記受信回路に供給することと、を含む、請求項6に記載の方法。

**【請求項10】**

前記第1の同じ電位は、接地電位であり、前記第2の同じ電位は、前記両極性パルサーのバイアス電圧である、請求項6に記載の方法。

**【請求項11】**

10

20

30

40

50

前記第1の同じ電位は、接地電位であり、前記第2の同じ電位は、前記両極性パルサーのバイアス電圧である、請求項1に記載の超音波機器。

【発明の詳細な説明】

【技術分野】

【0001】

関連出願の相互参照

本出願は、「SYMMETRIC RECEIVER SWITCH FOR BIPOLAR PULSER」と題された、2016年3月31日に代理人整理番号B1348.70027US00の下で出願された米国特許出願第15/087,943号の、米国特許法第120条の下での利益を主張する継続出願であり、その出願はその全体が参照により本明細書に組み込まれる。

10

【0002】

本出願は、超音波撮像及び高密度焦点式超音波(HIFU)用の超音波機器に関する。

【背景技術】

【0003】

幾つかの従来の超音波機器は、超音波トランスデューサにパルスを供給するように構成されたパルス化回路を含む。しばしば、超音波トランスデューサは送信及び受信を行う。

【発明の概要】

【課題を解決するための手段】

【0004】

本出願の態様は、フィードバックを備えるパルサーを有する集積回路を含む超音波オンチップ機器を提供する。超音波オンチップ機器には、対称受信スイッチも設けられ、超音波トランスデューサの出力に結合されて、超音波トランスデューサを駆動するためのマルチレベルパルサーの使用を容易にする。

20

【0005】

本出願の態様は、静電容量型超音波トランスデューサと、静電容量型超音波トランスデューサに結合され、かつ出力端子から両極性入力信号を静電容量型超音波トランスデューサに供給するように構成された両極性パルサーと、静電容量型超音波トランスデューサによって出力された電気信号を処理するように構成された受信回路と、第1のトランジスタ及び第2のトランジスタを含む対称スイッチと、を含む超音波機器に関する。対称スイッチは、両極性パルサーの出力端子と静電容量型超音波トランスデューサとの間に結合された入力端子を有し、受信回路に結合された出力端子を有する。

30

【0006】

本出願の態様は、超音波機器を動作させる方法に関し、この方法は、超音波機器の送信動作モード中は両極性パルサーから静電容量型超音波トランスデューサの第1の端子に両極性パルサー信号を供給することと、送信動作モード中は静電容量型超音波トランスデューサの第1の端子と受信回路との間に結合された対称スイッチを開状態で動作させることと、超音波機器の受信動作モード中は対称スイッチを閉状態で動作させることと、を含む。

【0007】

本出願の様々な態様及び実施形態について、以降の図を参照して説明する。図は必ずしも正確な縮尺で描かれてはいないことを理解されたい。複数の図に現れる項目は、それらが現れる図の全てにおいて、同じ参照符号によって示される。

40

【図面の簡単な説明】

【0008】

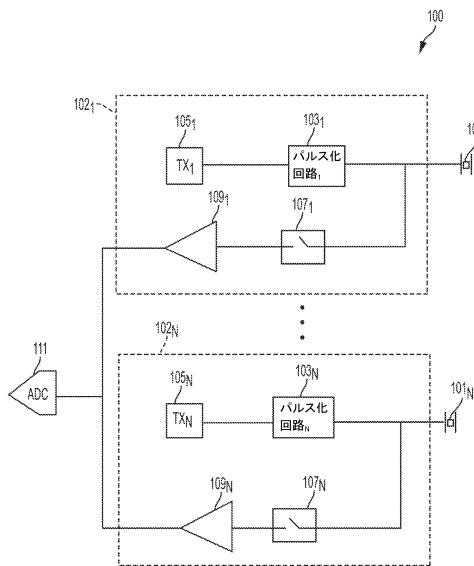

【図1】本出願の非限定的な実施形態による、複数のパルス化回路及び複数の受信スイッチを含む超音波機器を示すブロック図である。

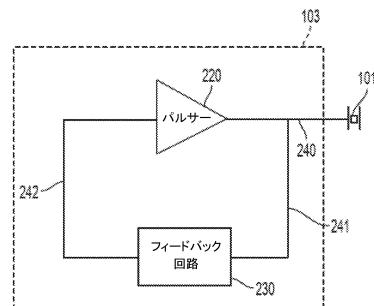

【図2】本出願の非限定的な実施形態による、静電容量型超音波トランスデューサに結合されたパルス化回路を示すブロック図である。

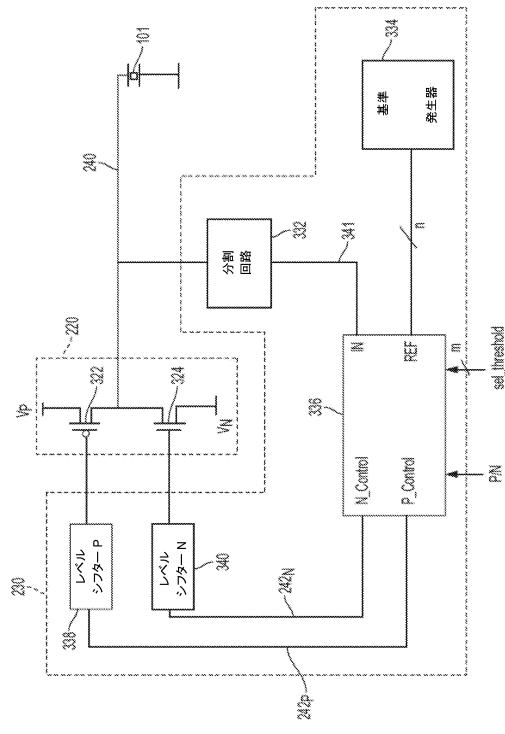

【図3】本出願の非限定的な実施形態による、パルサー及びフィードバック回路を備えるパルス化回路を示すブロック図である。

50

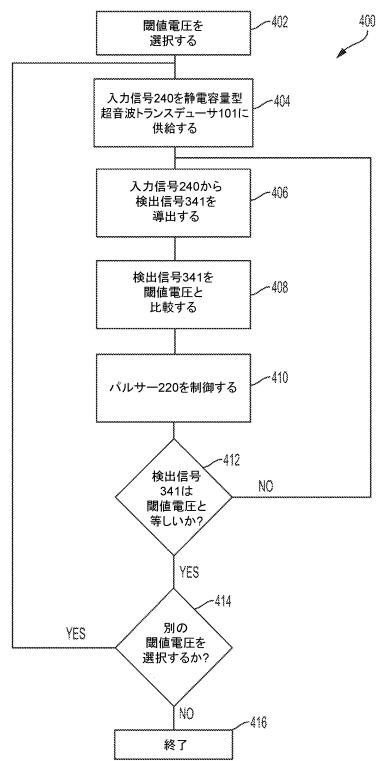

【図4】本出願の非限定的な実施形態による、静電容量型超音波トランスデューサに結合されたパルス化回路を動作させる方法の動作を示すブロック図である。

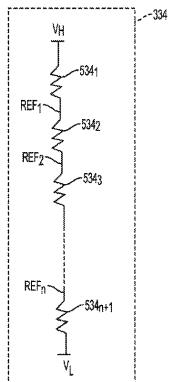

【図5A】本出願の非限定的な実施形態による、複数の閾値電圧を生成するように構成された抵抗ラダーを示す回路図である。

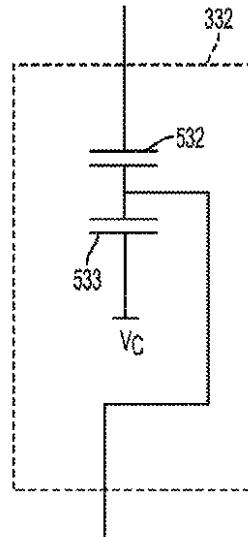

【図5B】本出願の非限定的な実施形態による、検出信号を生成するように構成された分割回路を示す回路図である。

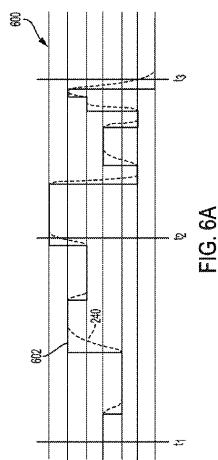

【図6A】本出願の非限定的な実施形態による、パルス化回路によって静電容量型超音波トランスデューサに供給される例示的な信号を示すタイミング図を示す。

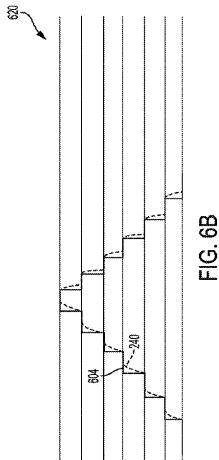

【図6B】本出願の非限定的な実施形態による、パルス化回路によって静電容量型超音波トランスデューサに供給されるアポダイズされた信号を示すタイミング図を示す。 10

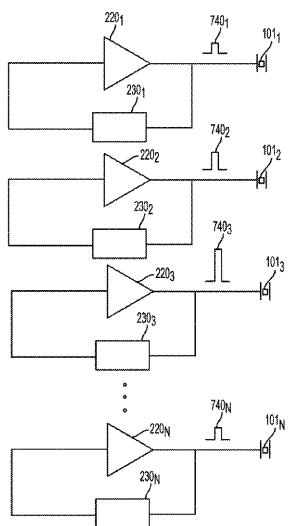

【図7】本出願の非限定的な実施形態による、複数の静電容量型超音波トランスデューサに結合された複数のパルス化回路を示すブロック図である。

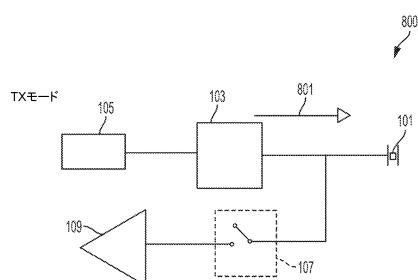

【図8A】本出願の非限定的な実施形態による、送信モードで動作している超音波機器を示すブロック図である。

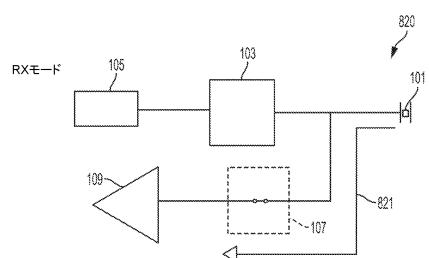

【図8B】本出願の非限定的な実施形態による、受信モードで動作している超音波機器を示すブロック図である。

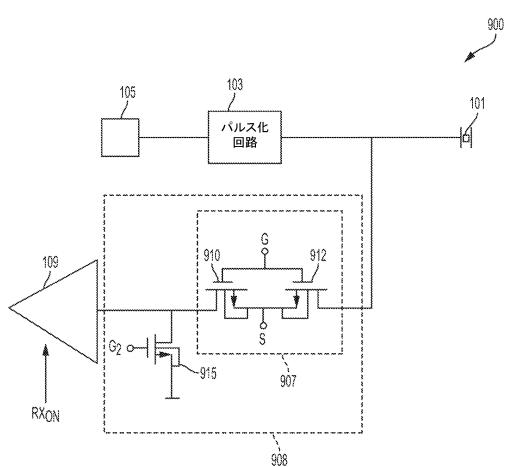

【図9】本出願の非限定的な実施形態による、対称スイッチを備える超音波機器を示すブロック図である。

【図10】本出願の非限定的な実施形態による、図9の対称スイッチを駆動するように構成された制御信号を示すタイミング図を示す。 20

【図11】本出願の非限定的な実施形態による、対称スイッチを備える代替機器を示すブロック図である。

#### 【発明を実施するための形態】

##### 【0009】

超音波オンチップ機器は、本明細書では「チップ」とも呼ばれる半導体ダイ上の回路と一体化された超音波トランスデューサを含むことがある。超音波オンチップ機器は、超音波プローブ内部で使用されて、超音波撮像、治療（例えば、高密度焦点式超音波（HIFU））、又はその両方を行うことができる。従って、超音波トランスデューサと一体化された回路は、そのような機能をサポートし、プローブ又は聴診器などの他のフォームファクター内で使用するのに適した形状を取ることがある。回路は、撮像及び／又はHIFUに適した超音波信号を生成するために、超音波オンチップ機器の超音波トランスデューサを駆動するために使用される電気パルスを生成するパルス化回路を含むことがある。パルス化回路は、デジタル、アナログ、又はアナログ・デジタル混合であることがある。 30

##### 【0010】

本出願の態様は、フィードバックを有する両極性のマルチレベルパルス化回路を提供する。単極性パルスを送信するように構成された超音波機器は、単極性パルスに関連した直流（DC）成分が受信回路を飽和させることがあるのでダイナミックレンジが制限され、従って、生成される画像のコントラストを低下させる、ということを本出願人は理解している。単極性パルスとは、ゼロ（0）以上の電圧、又は代替的に、ゼロ（0）以下の電圧しか取らないパルスである。対照的に、両極性パルスの使用により、DC成分の影響が制限され、従って、単極性パルスを利用する超音波機器と比較すると著しく増加したダイナミックレンジ及び画像コントラストがもたらされることを、本出願人は理解している。従って、本出願の態様は、両極性パルスを送信するように構成された超音波機器を提供する。両極性パルスは、ゼロ（0）より大きいか、小さいか、又はゼロ（0）に等しい電圧を取ることができる。 40

##### 【0011】

超音波画像のコントラストは、画像化されるターゲットに送信されるパルスの時間領域及び空間領域のアポダイゼーションを行うことにより大幅に向上され得るという本出願人の認識から、フィードバックを有するマルチレベルパルス化回路の使用が生まれた。アポダイゼーションは、送信されるパルスに関連するサイドロープの範囲を低減することがで 50

き、従って、生成される画像の解像度を高めることができる。時間的かつ空間的にアボダイズされたパルスの生成は、複数の値を取ることができる信号を制御する能力によって、促進することができる。本明細書で説明するタイプのマルチレベルパルスは、選択可能な値の集合の中から選択される任意の値を取ることができ、この集合は少なくとも3つの値を含むことがある。そのようなマルチレベルパルスの生成は、複数の供給電圧が供給される複雑なパルサー設計を必要とすることがある。複数の供給電圧を供給することは、実用的ではないことがある。これは、超音波機器が手持ち式の超音波プローブか又は他のコンパクトな形態の中に配置されることになる場合には、追加のオフチップの供給回路が必要となり得るので、特に当てはまることがある。本出願人は、フィードバック回路を使用することにより、複数の供給電圧に頼ることなく、マルチレベルパルスの生成及びアボダイズされたパルスの生成が容易になり、従って超音波機器の設計を単純化することができるこ<sup>10</sup>とを理解している。

#### 【0012】

本出願の態様は、超音波トランスデューサを受信回路に結合する対称スイッチを含む超音波機器を提供する。少なくとも上述した理由により、両極性パルス化回路の使用は有益であり得るが、それらの回路は超音波機器の受信回路にとっては好ましくないことがある。送信回路によって生成されたパルスは、不注意で直接的に電気的に受信回路に結合されることがあり、受信回路は、大きな正及び負の電圧スパイクに耐えるように設計されていないことがある。結果として、適切な保護が設けられていない場合、超音波機器は損傷を受けることがある。本出願人は、両極性パルスに関連した正及び負の電圧スパイクを阻止するように設計された適切に配置された対称スイッチが、受信回路への損傷を防ぐことができ、従って、超音波機器を保護し、両極性パルス化回路の使用を容易にすることを、理<sup>20</sup>解している。

#### 【0013】

上述したC M O S回路の特徴は、商業的に価値のあるフォームファクターで超音波撮像及び／又はH I F Uを行うのに適した超音波オンチップ機器を生成するのを容易にすることがある。

#### 【0014】

上述した態様及び実施形態並びに追加の態様及び実施形態について、以下で更に説明する。これらの態様及び／又は実施形態は、個々に、全て纏めて、又は2つ以上の任意の組み合わせで使用することができる、というのも、本出願はこの点で限定されないからである。

#### 【0015】

上述したように、本出願の態様は、両極性のマルチレベルパルス化回路と、この両極性のマルチレベルパルス化回路を受信回路に結合する対称スイッチとを有する超音波機器を提供する。図1は、本出願の態様に従ったそのような特徴を含むことがある超音波機器の全体的なアーキテクチャを示す。超音波機器100は、複数の静電容量型超音波トランスデューサ<sub>101, ..., 101\_N</sub>を有し、ここでNは整数である。超音波機器100は、複数の回路チャネル<sub>102, ..., 102\_N</sub>を含むことがある。回路チャネル<sub>102, ..., 102\_N</sub>は、それぞれの静電容量型超音波トランスデューサ<sub>101, ..., 101\_N</sub>に電気的に接続されることがある。超音波機器100は、アナログ／デジタル変換器（A D C）111を更に含むことがある。<sup>40</sup>

#### 【0016】

静電容量型超音波トランスデューサは、実施形態によってはセンサであり、受信した超音波信号を表す電気信号を生成する。静電容量型超音波トランスデューサは、実施形態によっては、超音波信号を送信することもある。静電容量型超音波トランスデューサは、実施形態によっては、容量性微細加工超音波トランスデューサ（C M U T）であることがある。しかしながら、他の実施形態では、他のタイプの静電容量型超音波トランスデューサを使用することができる。

#### 【0017】

10

20

30

40

50

回路チャネル $102_1 \dots 102_N$ は、送信回路、受信回路、又はその両方を含むことがある。送信回路は、それぞれのパルス化回路 $103_1 \dots 103_N$ に結合された送信デコーダー $105_1 \dots 105_N$ を含むことがある。パルス化回路 $103_1 \dots 103_N$ は、それぞれの超音波トランスデューサ $101_1 \dots 101_N$ を制御して超音波信号を放出することがある。

#### 【0018】

本出願の態様は、パルス化回路 $103_1 \dots 103_N$ に関する。実施形態によっては、パルス化回路 $103_1 \dots 103_N$ は両極性パルスを生成するように構成されることがある。実施形態によっては、パルス化回路 $103_1 \dots 103_N$ はマルチレベルパルスを生成するように構成されることがある。以下で更に説明するように、実施形態によっては、パルス化回路 $103_1 \dots 103_N$ は、パルサーに加えて追加の回路を含むことがある。実施形態によっては、パルス化回路 $103_1 \dots 103_N$ は、パルサー及びフィードバック回路を含むことがある。

10

#### 【0019】

回路チャネル $102_1 \dots 102_N$ の受信回路は、それぞれの静電容量型超音波トランスデューサ $101_1 \dots 101_N$ から出力された電気信号を受信することができる。図示した例では、各回路チャネル $102_1 \dots 102_N$ は、それぞれの受信スイッチ $107_1 \dots 107_N$ 及び受信回路 $109_1 \dots 109_N$ を含む。受信スイッチ $107_1 \dots 107_N$ は、所与の超音波トランスデューサ $101_1 \dots 101_N$ からの電気信号の読み出しを活性化／不活性化するように制御されることがある。受信回路 $109_1 \dots 109_N$ は、電流／電圧変換器を含むことがある。電流／電圧変換器は、トランスインピーダンス増幅器(TIA)を含むことがあり、その理由のために受信回路 $109_1 \dots 109_N$ はTIAとして示されているが、追加のかつ／又は代替の回路が受信回路を構成してもよい。

20

#### 【0020】

本出願の態様は、受信スイッチ $107_1 \dots 107_N$ に関する。実施形態によっては、受信スイッチ $107_1 \dots 107_N$ は、正及び／又は負の電圧を示す電圧スパイクを阻止するように構成された対称スイッチを含むことがある。受信スイッチ $107_1 \dots 107_N$ は、送信モードの間、送信回路から及び静電容量型超音波トランスデューサから受信回路を電気的に切り離すために開回路を形成するように構成されることがある。受信スイッチ $107_1 \dots 107_N$ は、受信モードの間、受信回路を静電容量型超音波トランスデューサに電気的に結合するために短絡回路を形成するように更に構成されることがある。

30

#### 【0021】

超音波機器 $100$ は、ADC $111$ を更に含むことがある。ADC $111$ は、静電容量型超音波トランスデューサ $101_1 \dots 101_N$ によって受信された信号をデジタル化するように構成されることがある。様々な受信信号のデジタル化は、直列で又は並列で行われることがある。単一のADCが示されており、従って複数の回路チャネルによって共有されるものとして示されているが、代替の実施形態は回路チャネル毎に1つのADCを供給する。

#### 【0022】

図1は、超音波機器の回路の一部として幾つかの構成要素を示しているが、本明細書で説明する様々な態様は、図示した通りの構成要素又は構成要素の構成に限定されないことを、理解されたい。

40

#### 【0023】

図1の構成要素は、单一の基板上に又は異なる基板上に配置することができる。单一の基板上に配置される場合、基板は一例としてシリコン基板などの半導体基板であることがあり、構成要素はその基板上にモノリシックに集積されることがある。図示した構成要素が同一の基板上にはない場合、一例として、静電容量型超音波トランスデューサ $101_1 \dots 101_N$ は第1の基板上にあり、残りの図示した構成要素は第2の基板上にあることがある。更なる代替案として、超音波トランスデューサと図示した回路の一部とが同一の基板上にあり、他の回路構成要素が異なる基板上にあることがある。複数の基板が使用さ

50

れる場合、それらの基板はシリコン基板などの半導体基板であることがある。

**【0024】**

一実施形態によれば、図1の構成要素は超音波プローブの一部を形成する。超音波プローブは、手持ち式であり得る。実施形態によっては、図1の構成要素は、患者によって装着されるように構成された超音波パッチの一部を形成する。

**【0025】**

図2は、幾つかの非限定的な実施形態による、図1のパルス化回路103<sub>1</sub>...103<sub>N</sub>のうちのいずれかとして機能することができるパルス化回路103の一例を示す。実施形態によっては、パルス化回路103は、パルサー220及びフィードバック回路230を含むことがある。パルス化回路103は、静電容量型超音波トランスデューサ101に電気的に接続された出力端子を有することがあり、静電容量型超音波トランスデューサ101に入力信号240を供給するように構成されることがある。実施形態によっては、パルサー220は、ゼロに加えて正及び/又は負の値を取り得る両極性パルスを生成するよう構成されることがある。両極性パルスを生成することにより、パルサー220は、パルスに関連したDC成分を減少させるか又は抑制することができる。前述のように、DC成分を有する送信パルスは、超音波機器100によって生成される画像の品質を劣化させることがある。従って、通過帯域成分と比較すると、DC成分は、画像化される媒体を通じて伝搬する間の減衰が大幅により少ないことがある。その結果、受信回路は、通過帯域成分よりもはるかに大きなDC成分を有する信号を受信することができる。結果として、受信回路は飽和し、画像のダイナミックレンジを制限することがある。

10

20

**【0026】**

実施形態によっては、フィードバック回路は、パルサーを制御してマルチレベルパルスを生成するように構成されることがある。本明細書で説明するタイプのマルチレベルパルスは、選択可能な値の集合から選択された任意の値を取ることができ、この集合は、少なくとも3つの値を含むことがある、少なくとも幾つかの実施形態では、4つ以上の値（例えば、3個～30個の値の間、4個～20個の値の間、4個～10個の値の間、又はこれらの範囲内の任意の数）を含むことがある。マルチレベルパルスの使用により、パルスの包絡線を最適化して、形成される超音波画像のパラメータを最大化することが可能になり得る。例えば、パルスの包絡線は、画像コントラストを最大化するように設計されることがある。特に、時間領域のアポダイゼーションを使用することにより、パルスの結果として得られる周波数成分は、大きなメインロープと抑制されたサイドロープとを呈し、従って、画像化解像度を高めることができる。時間領域のアポダイゼーションは、ほぼ連続的な窓関数を生成するために、可能な限り多数の電圧レベルをとるパルスを必要とする。しかしながら、多数のレベルを有するパルスを生成するには、複雑なパルス化回路が必要であることがある。従って、時間領域のアポダイゼーションを行う能力を最大にする一方で、パルス化回路を比較的単純でコンパクトに保つように、レベル数を選択するべきである。実施形態によっては、パルサー220は、3～30レベルの間、5～10レベルの間、又は任意の適切な値若しくは値の範囲の間を有するマルチレベルパルスを生成するように構成されることがある。

30

40

**【0027】**

マルチレベルパルスの使用により、空間領域のアポダイゼーションも可能になることがある。空間領域のアポダイゼーションを行うために、様々な静電容量型超音波トランスデューサが、空間依存振幅を有する入力信号で駆動されなければならない。空間依存振幅を有する入力信号の供給は、複数の基準電圧へのアクセスを有することによって容易になることがある。

**【0028】**

実施形態によっては、フィードバック回路230は、マルチレベルパルスの生成を容易にするように構成されることがある。とりわけ、フィードバック回路230は、複数の基準電圧を供給するように構成されることがある。前述したように、本明細書で説明するタイプのフィードバック回路の使用により、複数の供給電圧に頼ることなく、マルチレベル

50

パルサーの設計を容易にすることができます。実施形態によっては、複数の供給電圧を含めることは望ましくないことがある、というのも、複数の供給電圧は、手持ち式のフォームファクターに収めるのは困難であり得る相当に大きな超音波プローブをもたらすことがあるからである。これに反して、本明細書で説明するタイプのフィードバック回路は、基準電圧を生成するためのコンパクトな回路を提供することができ、手持ち式の超音波プローブ内に容易に含めることができる。

#### 【0029】

フィードバック回路230の出力端子は、パルサー220の入力端子に電気的に結合されることがある。フィードバック回路230の入力端子は、パルサー220の出力端子に電気的に結合されることがある。フィードバック回路230の入力端子は、入力信号240を表す検出信号241を受信するように構成されることがある。実施形態によっては、入力信号240及び検出信号241は電圧である。実施形態によっては、検出信号241は入力信号240から導き出されることがある。実施形態によっては、検出信号241は入力信号240に比例していることがある。フィードバック回路230は、検出信号241を閾値電圧と比較することができる。実施形態によっては、前述の閾値電圧は選択可能な閾値電圧の集合の中から選択されることがある。

10

#### 【0030】

比較の結果に基づいて、フィードバック回路230は、パルサー220の入力端子に制御信号242を供給することができる。実施形態によっては、フィードバック回路230は、検出信号241が閾値電圧より大きいか、小さいか、又は等しいかを判定するように構成されることがある。実施形態によっては、フィードバック回路230は、検出信号241が閾値電圧の範囲内にあるかどうか、例えば、閾値電圧の10%以内にあるかどうか、閾値電圧の5%以内にあるかどうか、又は任意の適切な範囲内にあるかどうか、などを判定するように構成されることがある。閾値電圧と比べた検出信号241の値に基づいて、フィードバック回路230は、パルサー220を制御して、入力信号240の現在の値を保持するか、又は入力信号240を変化させることができる。限定ではなく例として、検出信号241の値が閾値電圧より小さい場合、フィードバック回路230はパルサー220を制御して、検出信号241が閾値電圧と等しくなるか、又は閾値電圧のある範囲内になるまで、入力信号240の値を増加させることができる。検出信号241の値が閾値電圧よりも大きい場合には、フィードバック回路230はパルサー220を制御して、検出信号241が閾値電圧と等しくなるか、又は閾値電圧のある範囲内になるまで、入力信号240の値を減少させることができる。

20

#### 【0031】

実施形態によっては、静電容量型超音波トランスデューサ101に関連したキャパシタスが、電荷を保持して、検出信号241が選択された閾値電圧に達したときにその端子間に一定の電圧を維持することができる。検出信号241が閾値電圧よりも小さい場合、パルサー220を制御して静電容量型超音波トランスデューサ101に関連したキャパシタスを充電し、従って入力信号240を増加させることができる。検出信号241が閾値電圧よりも大きい場合、パルサー220を制御して静電容量型超音波トランスデューサ101に関連したキャパシタスを放電させるか又は負に充電し、従って入力信号240を低減させることができる。

30

#### 【0032】

実施形態によっては、フィードバック回路230は、パルサー220を非同期式に制御することができる。従って、制御信号242、入力信号240、及び検出信号241は、任意の時点で変化することが許されることがある。実施形態によっては、パルス化回路100は、クロック信号によってタイミングをはかられることがある。しかしながら、制御信号242は、クロック信号によって規定されない期間中に変化することが依然として許されることがある。

40

#### 【0033】

実施形態によっては、静電容量型超音波トランスデューサ101は、バイアス回路(図

50

示せず)に結合されることがある、ゼロより大きな絶対値を有するバイアス電圧を受け取るように構成されることがある。バイアス電圧は、10V～100Vの間、30V～80Vの間、又は任意の適切な値若しくは値の範囲の間にある絶対値を有することがある。実施形態によっては、静電容量型超音波トランステューサをバイアスすることにより、程度が高められた線形性を示す応答がもたらされることがある。

#### 【0034】

図3は、図2のパルス化回路の非限定的な詳細な実施態様である。実施形態によっては、パルサー220は2つのトランジスタ、例えば322及び324などを含むことがある。しかしながら、パルサー220はこの点で限定はされず、任意の適切な数のトランジスタを使用することができる。トランジスタは、金属酸化膜半導体電界効果トランジスタ(MOSFET)、接合型電界効果トランジスタ(JFET)、バイポーラ接合トランジスタ(BJT)、金属-半導体電界効果トランジスタ(MESFET)、絶縁ゲート型電界効果トランジスタ(IGFET)、横方向拡散金属酸化膜半導体トランジスタ(LDMOS)、又はそれらの任意の適切な組み合わせ、を含むことがある。パルサー220は、トランジスタ322及びトランジスタ324を含むことがある。トランジスタ322は、トランジスタ324の導電型とは異なる導電型を有することがある。例えば、トランジスタ322は、電界の作用の下で移動する正孔によって維持されるドリフト電流に基づく導電性を有することがある。トランジスタ324は、電界の作用の下で移動する電子によって維持されるドリフト電流に基づく導電性を有することがある。実施形態によっては、トランジスタ324はnMOSFETであり、トランジスタ322はpMOSFETであることがある。これらのトランジスタは、nMOSトランジスタ324のドレインがpMOSトランジスタ324のドレインに接続されるように構成されることがある。これらのドレインは、静電容量型超音波トランステューサ101の端子に更に接続されることがある。nMOSトランジスタ324のソースは、供給電圧 $V_N$ に接続されることがある。実施形態によっては、 $V_N$ はゼロよりも小さいことがある。 $V_N$ は、-100V～-1Vの間、-50V～-20Vの間、又は任意の適切な値若しくは値の範囲の間であり得る。pMOSトランジスタ322のソースは、供給電圧 $V_P$ に接続されることがある。実施形態によっては、 $V_P$ はゼロよりも大きいことがある。 $V_P$ は、1V～100Vの間、20V～50Vの間、又は任意の適切な値若しくは値の範囲の間であり得る。トランジスタ322及び324のゲートに供給される電圧は、図2のフィードバック回路230によって生成されることがある。

#### 【0035】

実施形態によっては、フィードバック回路230は、コントローラ336、分割回路332、及び基準発生器334を含むことがある。実施形態によっては、フィードバック回路230は、レベルシフター338及びレベルシフター340を更に含むことがある。分割回路332は、入力信号240に対応する電圧を受け取り、検出信号341を出力するように構成されることがある。分割回路332は、入力信号240に比例する検出信号341を供給するように構成されることがある。検出信号341は、「In」とラベル付けされた入力端子を通じてコントローラ336に供給されることがある。

#### 【0036】

基準発生器334は、コントローラ336の「Ref」とラベル付けされた端子に、選択可能な閾値電圧の集合を供給するように構成されることがある。実施形態によっては、基準発生器334は、n個のコネクタを介してコントローラ336に接続され、対応するコネクタを介してn個の閾値電圧を供給するように構成され、ここでnは、2よりも大きな任意の適切な値を取ることができる。閾値電圧は、ゼロに等しいか、ゼロよりも大きいか、又はゼロよりも小さいことがある。

#### 【0037】

実施形態によっては、フィードバック回路230は、デジタル制御されがあり、コントローラ336は、デジタル方式のコントローラを含むことがある。コントローラ336は、パルサー220を制御して、n個の閾値電圧の中から選択された閾値電圧と検出

信号 341との比較に基づいて、入力信号 240に対応する電圧を保持、増加、又は低減させるように構成されることがある。コントローラ 336は、基準発生器 334によって供給された n 個の閾値電圧からある閾値電圧を選択することがある。この閾値電圧は、信号 sel\_threshold を介してデジタル処理で選択されることがある。信号 sel\_threshold は m ビットを含むことがある、m は、n が  $2^m$  に等しいか、また  $2^m$  未満であるような値である。各ビットの組み合わせは、n 個の閾値電圧から 1 つの閾値電圧を選択することがある。限定ではなく例として、000 に等しい sel\_threshold のシーケンスは、8 個の閾値電圧のうちの最小のものを選択するがあり、111 に等しい sel\_threshold のシーケンスは、8 個の閾値電圧のうちの最大のものを選択するがある。更に、信号 sel\_threshold は、非同期式に変化することがある。

10

#### 【0038】

実施形態によっては、分割回路 332 は、入力信号 240 にある倍率で比例する検出信号 341 を供給するがある。そのような実施形態では、基準発生器 334 は、同じ倍率で入力信号 240 に対してスケール変更された閾値電圧の集合を供給するように構成されることがある。その結果、それら 2 つの信号のうちの一方を更にスケール変更する必要なく、検出信号 341 を選択された閾値電圧と直接的に比較することができる。

#### 【0039】

実施形態によっては、信号 p / n を使用して、トランジスタ 322 及び 324 の状態を制御するがある。実施形態によっては、p / n は単一ビットの信号であり得る。信号 p / n は、トランジスタ 322 を活性化するために「p」に設定されるか、又はトランジスタ 324 を活性化するために「n」に設定されることがある。しかしながら、トランジスタ 322 及び 324 の状態を制御するように構成された、任意の適切な数のビットを使用することもできる。単一ビットの値は、トランジスタ 322 又はトランジスタ 324 のいずれかを、線形モードであろうと飽和モードであろうと、導通状態にするがある。そのような実施形態では、1 度に 1 つのトランジスタのみが導通状態に設定することができる。

20

#### 【0040】

sel\_threshold 及び p / n の値に基づいて、コントローラ 336 は、「N\_control」及び「P\_control」とラベル付けされた出力端子を介して、制御信号 242<sub>p</sub> 及び 242<sub>N</sub> を出力するがある。制御信号 242<sub>p</sub> 及び 242<sub>N</sub> はまとめて、図 2 で示した制御信号 242 を表すがある。実施形態によっては、信号 242<sub>p</sub> は、p MOS トランジスタ 322 の状態を制御するように構成された単一ビットを含むがある。実施形態によっては、信号 242<sub>N</sub> は、n MOS トランジスタ 324 の状態を制御するように構成された単一ビットを含むがある。これら 2 つのトランジスタは、同時に遮断状態になることが許されているがある。

30

#### 【0041】

実施形態によっては、制御信号 242<sub>p</sub> 及び 242<sub>N</sub> は、それぞれトランジスタ 322 及び 324 のゲートを直接的に駆動するがある。他の実施形態では、図 3 に示すように、制御信号 242<sub>p</sub> 及び 242<sub>N</sub> は、それぞれレベルシフター 338 及びレベルシフター 340 の入力端子に結合されるがある。レベルシフター 338 及びレベルシフター 340 の出力端子は、それぞれトランジスタ 322 及び 324 のゲートに結合されるがある。レベルシフター 338 及びレベルシフター 340 は、コントローラ 336 によって生成された電圧をトランジスタ 322 及び 324 に適合した電圧に適合させて、これらのトランジスタを、信号 242<sub>p</sub> 及び 242<sub>N</sub> に基づいて、遮断状態又は導通状態に駆動するように構成されるがある。

40

#### 【0042】

検出信号 341 が選択された閾値電圧よりも小さい場合、コントローラ 336 は、p MOS トランジスタ 322 を導通状態にし、n MOS トランジスタ 324 を遮断状態にするのに適した値を有する制御信号 242<sub>p</sub> 及び 242<sub>N</sub> を出力するように構成されるがある。この場合、電圧源 V<sub>p</sub> から静電容量型超音波トランステューサ 101 に流れる電流

50

は、検出信号 341 が選択された閾値電圧又は選択された閾値電圧の所定の範囲に達するまで、静電容量型超音波トランスデューサ 101 を充電することがある。

#### 【0043】

検出信号 341 が選択された閾値電圧よりも大きい場合、コントローラ 336 は、nMOS ドラッグステラ 324 を導通状態にし、pMOS ドラッグステラ 322 を遮断状態にするのに適した値を有する制御信号  $242_p$  及び  $242_N$  を出力するように構成されることがある。この場合、静電容量型超音波トランスデューサ 101 から電圧源  $V_N$  に流れる電流は、検出信号 341 が選択された閾値電圧又は選択された閾値電圧の所定の範囲に達するまで、静電容量型超音波トランスデューサ 101 を放電させるか、又は負に充電することがある。

10

#### 【0044】

検出信号 241 が選択された閾値電圧に等しいか又は選択された閾値電圧の所定の範囲内にある場合、pMOS ドラッグステラ 322 及び nMOS ドラッグステラ 324 は、信号  $242_p$  及び  $242_N$  を介して、共に遮断状態になるように制御されることがある。この場合、静電容量型超音波トランスデューサ 101 に又は静電容量型超音波トランスデューサ 101 から電流は流れない。結果として、静電容量型超音波トランスデューサ 101 は、電荷を保持することがあり、従って、その端子間に、選択された閾値電圧に対応する目標電圧を保持することがある。

#### 【0045】

上述したように、少なくとも幾つかの実施形態では、超音波トランスデューサ 101 が電荷を保持することが望ましいことがあるので、そのような実施形態では、超音波トランスデューサは静電容量型であることがある。対照的に、抵抗性の超音波トランスデューサを使用すると、そのような状況では適切に動作しないことがある。

20

#### 【0046】

コントローラ 336 は、図 3 に関連して説明した非限定的な実施形態において信号  $p/n$  及び  $sel\_threshold$  に基づいてパルサー 220 を制御するように構成されることがあるが、パルス化回路 103 はこの点で限定されない。従って、閾値電圧又は閾値電圧の範囲に達するまで入力信号 240 を保持、増加、又は低減するようにパルサー 220 を制御するように構成された、任意の信号、又は信号の組み合わせを、利用することもできる。

#### 【0047】

30

図 4 は、幾つかの非限定的な実施形態による、静電容量型超音波機器を駆動するようにパルス化回路を動作させる方法を示す。図 4 の方法は、図 2 のパルス化回路又は図 3 のパルス化回路に関連して行われることがある。方法 400 は、動作 402 で開始し、閾値電圧を  $n$  個の選択可能な閾値電圧の集合の中から選択することができる。n は 2 よりも大きな任意の適切な値を取ることができる。実施形態によっては、閾値電圧は  $m$  ビットを有するデジタル信号を通じて選択されることがある、n は、 $2^m$  に等しいか又は  $2^m$  未満である。

#### 【0048】

方法 400 は動作 404 に続き、入力信号 240 などの入力信号が、パルサー 220 によって静電容量型超音波トランスデューサ 101 に供給されることがある。本出願の一態様によれば、パルサー 220 は、正及び / 又は負の電圧を示すことがある両極性入力信号を供給するように構成されることがある。本明細書で説明するタイプの両極性入力信号は、超音波機器の受信回路を飽和させないエコー信号をもたらすことがある。

40

#### 【0049】

本出願の別の態様によれば、パルサー 220 は、複数の選択可能な値の中から選択された値を示すことがあるマルチレベルパルスを供給するように構成されることがある。マルチレベルパルスを生成することができるパルス化回路は、画像コントラストの向上をもたらすことがある時間領域及び空間領域のアボダイゼーションを容易にすることがある。閾値電圧の集合から選択された閾値電圧を供給するように設計されたフィードバック回路によって、手持ち式の超音波プローブをより大型化してしまうことがある追加の電圧源回路

50

に頼ることなく、本明細書で説明するタイプのマルチレベルパルスの生成が容易になることがある。

#### 【0050】

動作406において、検出信号341などの検出信号を、入力信号240から導き出すことがある。検出信号341は、入力信号240を表すことがある。従って、検出信号341は、入力信号240と等しいか、又は入力信号240に比例していることがある。

#### 【0051】

動作408では、検出信号341を、動作402で選択された閾値電圧と比較することができる。実施形態によっては、検出信号341はある倍率で入力信号240に比例している。そのような実施形態では、閾値電圧を、同じ倍率で入力信号240に対してスケール変更することがある。比較の結果、検出信号341は、閾値電圧と等しいか、閾値電圧より大きいか、又は閾値電圧より小さいことがある。10

#### 【0052】

動作410において、動作408で行った比較の結果に基づいて、制御信号242をパルサー220に供給して入力信号240を制御することがある。制御信号は、フィードバック回路230によって供給されることがある。フィードバック回路230は、デジタル制御されることがある。動作412において、検出信号341が選択された閾値電圧よりも小さい場合、制御信号242はパルサー220を制御して、入力信号240に対応する電圧を増加させることができる。実施形態によっては、制御信号242はpMOSトランジスタ322を導通状態にして、静電容量型超音波トランスデューサ101に関連したキャパシタンスを充電することができる。20

#### 【0053】

動作412において、検出信号341が選択された閾値電圧よりも大きい場合、制御信号242はパルサー220を制御して、入力信号240に対応する電圧を低減することがある。実施形態によっては、制御信号242はnMOSトランジスタ324を導通状態にして、静電容量型超音波トランスデューサ101に関連したキャパシタンスを放電させるか、又は負に充電することができる。

#### 【0054】

どちらの場合でも、方法400は動作406に戻ることがあり、方法400は、検出信号341が選択された閾値電圧に等しいか又は選択された閾値電圧の所定の範囲内になるまで、繰り返されることがある。30

#### 【0055】

動作412において、検出信号341が選択された閾値電圧と等しいか又は選択された閾値電圧の所定の範囲内にあると判った場合、制御信号242はパルサー220を制御して、入力信号240の現在の値を保持することがある。実施形態によっては、制御信号242はnMOSトランジスタ324及びpMOSトランジスタ322を遮断状態にして、静電容量型超音波トランスデューサ101に関連したキャパシタンスが現在の電荷を保持できるようにすることができる。所定の範囲は、選択された閾値電圧の10%以内、選択された閾値電圧の5%以内、又は任意の適切な範囲内として規定されることがある。

#### 【0056】

一旦入力信号240が閾値電圧に対応する電圧に達すると、動作414において、別の閾値電圧を、n個の選択可能な閾値電圧の中から選択することができる。動作414において別の閾値電圧を選択した場合、方法400は、この新たに選択された閾値電圧について、動作404から繰り返されることがある。新たな閾値電圧の選択は、非同期式に行われることがある。さもなければ、新たな閾値電圧が選択されない場合には、方法400は動作416で終了することがある。40

#### 【0057】

図5Aは、幾つかの非限定的な実施形態による、図3の基準発生器の回路図を示す。基準発生器334は、n個の閾値電圧 $ref_1 \dots ref_n$ を生成するように構成された抵抗ラダーを含むことがあり、nは2より大きな任意の値を取り得る。実施形態によっては50

、抵抗ラダーは、直列に接続された  $n + 1$  個の抵抗器  $534_1 \dots 534_{n+1}$  を含むことがある。抵抗器  $534_1$  は、供給電圧  $V_H$  に結合されることがある。供給電圧  $V_H$  は、図 3 に示した供給電圧  $V_P$  と等しいことがある。抵抗器  $534_{n+1}$  は、供給電圧  $V_L$  に結合されることがある。供給電圧  $V_L$  は、図 3 に示した供給電圧  $V_N$  に等しいことがある。実施形態によっては、これらの  $n + 1$  個の抵抗器は、全てが等しい抵抗値を有して、 $V_H - V_L$  に相当する電圧範囲を  $n$  個の等しいセグメントに分割することができる。他の実施形態では、抵抗器  $534_2 \dots 534_{n+1}$  は  $R$  に等しい抵抗値を有し、一方抵抗器  $534_1$  は  $xR$  に等しい抵抗値を有することができ、ここで  $x$  は、 $0.01 \sim 100$  の間の任意の値を取ることができる。しかしながら、他の値も可能である。そのような実施形態では、 $V_H - V_L$  に比例したスケール変更された電圧範囲が、 $n$  個の等しいセグメントに分割されることがある。10

#### 【0058】

図 5B は、幾つかの非限定的な実施形態による、図 3 の分割回路の回路図を示す。分割回路は、入力信号 240 に比例する検出信号 341 を生成するように構成された、容量分圧器を含むことがある。容量分圧器は、コンデンサ 532 及びコンデンサ 533 を含むことがある。コンデンサ 532 は、パルサー 220 の出力に結合された 1 つの端子と、コントローラ 336 の入力に結合された 1 つの端子とを有することができる。実施形態によっては、コンデンサ 532 は、パルサー 220 によって生成された入力信号 240 を受け取るように構成されることがある。コンデンサ 533 は、コントローラ 336 の同じ入力に結合された 1 つの端子と、供給電圧  $V_C$  に結合された 1 つの端子とを有することができる。実施形態によっては、コンデンサ 336 は、入力信号 240 のスケール変更された信号を受け取るように構成されることがある。実施形態によっては、供給電圧  $V_C$  は、図 3 に示した供給電圧  $V_N$  と等しいことがある。コンデンサ 532 及び 533 の静電容量は、図 5A の閾値電圧をスケール変更したのと同じ倍率で検出信号 341 をスケール変更するように構成されることがある。そのような実施形態では、検出信号 341 は、それら 2 つの信号のうちのいずれもまずスケール変更する必要なく、 $n$  個の閾値電圧の中から選択された閾値電圧と直接的に比較されることがある。20

#### 【0059】

図 6A は、本出願の非限定的な実施形態による、パルス化回路によって静電容量型超音波トランスデューサに供給される例示的な信号を示すタイミング図を示す。特に、タイミング図 600 は、例示的なターゲット信号 602 及び例示的な入力信号 240 を示す。図 6A に関連して提示される非限定的な実施形態では、閾値電圧は 7 個の閾値電圧の中から選択されることがある。ターゲット信号 602 は、入力信号 240 が追従するべき信号を表す。入力信号 240 がターゲット信号 602 と等しい場合、例えば  $t_1$  において、検出信号 341 は現在の閾値電圧と等しくなる。この場合、フィードバック回路 230 は、パルサー 220 を制御して、入力電圧 240 を現在の値で一定に保つことがある。入力電圧 240 がターゲット電圧 602 よりも小さい場合、例えば  $t_2$  において、フィードバック回路 230 はパルサー 220 を制御して、現在のターゲット電圧に達するまで入力電圧 240 を増加させることがある。入力電圧 240 がターゲット電圧 602 よりも大きい場合、例えば  $t_3$  において、フィードバック回路 230 はパルサー 220 を制御して、現在のターゲット電圧に達するまで入力電圧 240 を減少させることがある。実施形態によっては、ターゲット信号 602 は、非同期式に変化することがある。その結果、ターゲット電圧 602 の各セグメントの持続時間は、他のセグメントの持続時間とは独立して設定されることがある。3040

#### 【0060】

実施形態によっては、パルス化回路 103 は、ゼロより大きな DC 成分を有する入力信号 240 を生成するように構成されることがある。DC 成分の大きさは、受信回路が飽和状態に達することなく受信回路をバイアスするように選択されることがある。

#### 【0061】

実施形態によっては、入力信号 240 は、ターゲット信号 602 をオーバーシュートす50

ることがある（図示せず）。そのようなオーバーシュートの発生を軽減するために、フィードバック回路 230 は、閾値電圧を歪めるように構成されることがある。実施形態によつては、閾値電圧は、この閾値電圧に電圧オフセットを加えること（又は引くこと）によつて、歪められることがある。例えば、所望の出力電圧が  $x$  ボルトである場合、閾値電圧は、 $x$  と  $y$  との差がオーバーシュート電圧に等しくなるように、 $y$  ボルトに設定されることがある。実施形態によつては、閾値電圧は、不均一な抵抗ラダーを介して歪められることがある。

#### 【 0 0 6 2 】

図 6B は、本出願の非限定的な実施形態による、パルス化回路によって静電容量型超音波トランスデューサに供給されるアポダイズされた信号を示すタイミング図を示す。特に、タイミング図 620 は、アポダイズされたターゲット信号 604 及びアポダイズされた入力信号 240 を示す。フィードバック回路 230 は、ガウス窓、ハミング窓、フラットトップ窓、コサイン窓、又は任意の適切な窓関数に基づいて、入力信号 240 の時間領域アポダイゼーションを行うように構成されることがある。本明細書で説明するタイプのマルチレベルパルスは、連続的な窓関数を忠実に生成するのに十分な程度の細かさを提供する。

#### 【 0 0 6 3 】

図 7 は、本出願の非限定的な実施形態による、複数の静電容量型超音波トランスデューサに結合された複数のパルス化回路を示すブロック図である。実施形態によつては、静電容量型超音波トランスデューサ  $101_1, 101_2, 101_3, \dots, 101_N$  は、1D アレイを形成するように配置されることがある。他の実施形態では、静電容量型超音波トランスデューサ  $101_1 \dots 101_N$  は、2D アレイを形成するように配置されることがある。静電容量型超音波トランスデューサ  $101_1 \dots 101_N$  は、パルサー  $220_1, 220_2, 220_3, \dots, 220_N$  の中のそれぞれのパルサーの出力端子に結合されることがある。フィードバック回路  $230_1, 230_2, 230_3, \dots, 230_N$  は、パルサー  $220_1 \dots 220_N$  の中のそれぞれのパルサーの入力端子及び出力端子に結合されることがある。実施形態によつては、フィードバック回路  $230_1 \dots 230_N$  は、別個の回路であり得る。他の実施形態では、フィードバック回路  $230_1 \dots 230_N$  は、パルサー  $220_1 \dots 220_N$  を制御するように構成された単一の回路の一部であり得る。

図 7 に示すように、フィードバック回路  $230_1 \dots 230_N$  は、パルサー  $220_1 \dots 220_N$  を制御して、空間依存の振幅を示す入力信号  $740_1, 740_2, 740_3, \dots, 740_N$  を生成することができる。実施形態によつては、フィードバック回路は、パルサーを制御して、入力信号の空間領域のアポダイゼーションを行うことがある。限定期間ではなく例として、入力信号  $740_1 \dots 740_N$  は、アレイの中央より大きくなり、所定のプロファイルに従ってアレイの縁に向かって減衰する振幅を示すことがある。空間領域のアポダイゼーション関数は、ガウス窓、ハミング窓、フラットトップ窓、コサイン窓、又は任意の適切な窓関数であり得る。空間領域のアポダイゼーションは、一空間次元又は二空間次元に渡って行われることがある。空間領域のアポダイゼーションを行うことにより、アレイの開口を効果的に変化させることができ、従って、放出される超音波の空間プロファイルを最適化する手段がもたらされる。実施形態によつては、空間的なサイドロープを最小にするように空間プロファイルを最適化することができる。最小の又は抑制されたサイドロープを有する空間プロファイルを放出することができる超音波機器は、空間解像度が高くなり、従って画像コントラストを向上させる。

#### 【 0 0 6 4 】

実施形態によつては、静電容量型超音波トランスデューサ  $101$  は、送受信回路に接続されることがある。送信中、パルス化回路によって生成される両極性入力信号は、不注意に受信回路に結合されることがある。実施形態によつては、受信回路は、パルサー  $220$  を用いて生成されるタイプの大きな正及び負の電圧スパイクに耐えるように設計されていない構成要素を含むことがある。従って、受信回路に両極性パルスを直接的に結合すると、1つ又は複数の構成要素に損傷を与えるという影響があることがある。

10

20

30

40

50

## 【0065】

本出願の態様によれば、両極性パルスが生成されている間は送信回路から受信回路を切り離すように構成された対称スイッチが提供される。本明細書で使用する場合、対称スイッチは、同じタイプの入力端子及び出力端子を有する、トランジスタベースのスイッチである。例えば、スイッチの入力端子及び出力端子は、両方ともソース、両方ともドレイン、両方ともエミッタ、両方ともコレクタ、又は他の端子タイプであり得る。図8A及び図8Bは、本出願の非限定的な実施形態による、送信モード及び受信モードでそれぞれ動作している超音波機器を示すブロック図である。対称スイッチ107は、パルス化回路103の出力端子に接続された入力端子を有することがある。実施形態によっては、対称スイッチ107の入力端子は、パルス化回路103のパルサー220の出力端子に接続されることがある。対称スイッチ107の入力端子は、静電容量型超音波トランスデューサ101の端子に更に接続されることがある。実施形態によっては、対称スイッチ107の入力端子は、パルサー220の出力端子と静電容量型超音波トランスデューサ101の端子との間に結合されることがある。対称スイッチは、受信回路109の入力端子に結合された出力端子を有することもある。実施形態によっては、受信回路109は、エコー信号を受信するのに応答して、静電容量型超音波トランスデューサ101によって生成された電流を変換するように構成された電流／電圧変換器を含む。実施形態によっては、電流／電圧変換器は、トランスインピーダンス増幅器(TIA)を含むことがある。

## 【0066】

図8Aに示すように、送信モード(TXモード)では、対称スイッチ107は高インピーダンスを提供して、パルス化回路103によって生成されたパルスを受信回路109から切り離すように構成されることがある。実施形態によっては、対称スイッチ107は、送信モード中は開回路として動作するように構成されることがある。矢印801は、送信モード中の入力信号240に対応する信号経路を表すことがある。

## 【0067】

図8Bに示すように、受信モード(RXモード)では、対称スイッチ107は、低インピーダンスを提供して、エコー信号(又は他の受信信号)を受信するのに応答して静電容量型超音波トランスデューサ101によって生成されたパルスを受信回路109に結合するように構成されることがある。実施形態によっては、対称スイッチ107は、受信モード中に受信回路109を静電容量型超音波トランスデューサ101に短絡させるように構成されることがある。実施形態によっては、パルス化回路103は、受信モード中は高インピーダンス状態になるように構成されることがある。矢印821は、受信モード中の受信信号に対応する信号経路を表すことがある。

## 【0068】

図9は、本出願の非限定的な実施形態による、対称スイッチを備える超音波機器のブロック図900を示す。対称スイッチ907は、パルス化回路103によって生成された両極性パルスに関連した正及び負の電圧を阻止し、従って受信回路109への損傷を防ぐよう構成されることがある。

## 【0069】

実施形態によっては、対称スイッチ907は2つのトランジスタ910及び912を含むことがある。しかしながら、対称スイッチ907は、送信モード中に両極性パルスを阻止するように構成される、任意の適切な数のトランジスタを含むことがある。トランジスタ910及び912は、nMOS及びpMOSを含む金属酸化膜半導体電界効果トランジスタ(MOSFET)、接合型電界効果トランジスタ(JFET)、バイポーラ接合トランジスタ(BJT)、金属-半導体電界効果トランジスタ(MESFET)、絶縁ゲート型電界効果トランジスタ(IGFET)、横方向拡散金属酸化膜半導体トランジスタ(LDMOS)、又はそれらの任意の適切な組み合わせ、などの任意のタイプのものであり得る。実施形態によっては、トランジスタ910及び912は両方ともnMOSである。トランジスタ910のゲートは、トランジスタ912のゲートに短絡されていることがある。実施形態によっては、トランジスタ910のゲート以外の第2の端子が、トランジスタ

10

20

30

40

50

912のゲート以外の第2の端子に短絡されていることがある。限定ではなく例として、トランジスタ910のソースが、トランジスタ912のソースに短絡されていることがある。トランジスタ912の第3の端子、例えばドレインは、パルス化回路103の出力端子と静電容量型超音波トランスデューサ101の端子との間に結合されることがある。トランジスタ910の第3の端子、例えばドレインは、受信回路109の入力端子に結合されることがある。実施形態によっては、トランジスタ910のドレインは、受信回路109の入力端子に短絡されていることがある。実施形態によっては、トランジスタ910のボディ端子は、トランジスタ910のソースに短絡されていることがあり、トランジスタ912のボディ端子は、トランジスタ912のソースに短絡されていることがある。

## 【0070】

10

実施形態によっては、スイッチング回路908を使用して、送信モード中に両極性パルスを阻止することがある。スイッチング回路908は、対称スイッチ907及びトランジスタ915を含むことがある。トランジスタ915は、任意の適切なタイプのトランジスタであり得る。限定ではなく例として、トランジスタ915はnMOSであり得る。トランジスタ915は、受信回路109の入力端子に短絡されたドレインを有するように構成されることがある。トランジスタ915のソースは、接地端子に短絡されていることがある。トランジスタ915のボディ端子は、そのソースに短絡されていることがある。

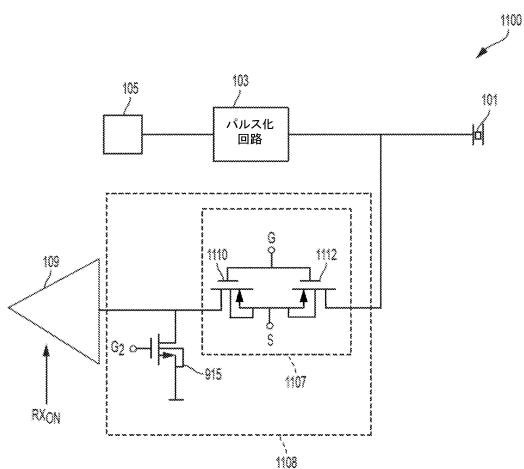

## 【0071】

実施形態によっては、対称スイッチはpMOSトランジスタを含むことがある。図11は、本出願の非限定的な実施形態による、対称スイッチを備える超音波機器のブロック図1100を示しており、この対称スイッチは2つのpMOSトランジスタ1110及び1112を含む。図11は2つのpMOSトランジスタを含む対称スイッチを示しているが、任意の他の適切な数のpMOSトランジスタを使用することもできる。

20

## 【0072】

30

対称スイッチ1107は、トランジスタ1110のゲートがトランジスタ1112のゲートに短絡されるように、構成されることがある。実施形態によっては、トランジスタ1110のゲート以外の第2の端子が、トランジスタ1112のゲート以外の第2の端子に短絡されることがある。限定ではなく例として、トランジスタ1110のソースが、トランジスタ1112のソースに短絡されていることがある。トランジスタ1112の第3の端子、例えばドレインは、パルス化回路103の出力端子と静電容量型超音波トランスデューサ101の端子との間に結合されることがある。トランジスタ1110の第3の端子、例えばドレインは、受信回路109の入力端子に結合されることがある。実施形態によっては、トランジスタ1110のドレインは、受信回路109の入力端子に短絡されていることがある。実施形態によっては、トランジスタ1110のボディ端子は、トランジスタ1110のソースに短絡されていることがあり、トランジスタ1112のボディ端子は、トランジスタ1112のソースに短絡されていることがある。実施形態によっては、スイッチング回路1108は、対称スイッチ1107及びトランジスタ915を含むことがある。

## 【0073】

40

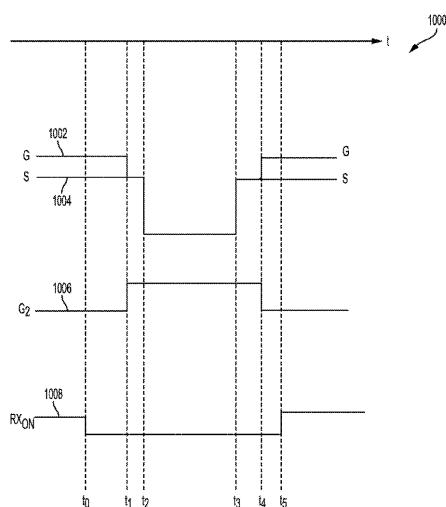

スイッチング回路908は、送信モード中はパルス化回路103によって生成された両極性パルスを阻止するように構成され、かつ、受信モード中は静電容量型超音波トランスデューサ101を受信回路109に結合するように更に構成された、任意の適切なタイプ及び数の制御信号によって、制御されることがある。限定ではなく例として、図10は、本出願の非限定的な実施形態による、図9の対称スイッチを駆動するように構成された制御信号を示すタイミング図1000を示す。制御信号1002は、端子Gを介してトランジスタ910及び912のゲートを制御することができる。制御信号1004は、端子Sを介してトランジスタ910及び912のソースを制御することができる。制御信号1006は、端子G<sub>2</sub>を介してトランジスタ915のゲートを制御することができる。実施形態によっては、受信回路109は、制御信号1008を用いてオン及びオフにされることがある。例えば、制御信号1008は、受信回路109の電圧源を有効／無効にすることがある

50

。

#### 【0074】

$t_0$  の前では、スイッチング回路 908 は受信モードで動作するように構成されることがある。この期間中は、制御信号 1002 は制御信号 1004 よりも大きいことがある。実施形態によっては、制御信号 1002 及び 1004 は両方とも、ゼロより大きいことがある。このようにして、両方のトランジスタとも、ゼロより大きなゲート - ソース電圧を有することがあり、従って、電流を伝導するように構成されることがある。制御信号 1006 は、トランジスタ 915 を遮断状態に保つために、ゼロであるか又はトランジスタ 915 の閾値電圧未満であることがある。実施形態によっては、制御信号 1008 は、受信回路 109 を有効にする値に設定されることがある。

10

#### 【0075】

$t_0 \sim t_1$  の間では、制御信号 1008 は、受信回路 109 を無効にする値に設定されることがある。

#### 【0076】

$t_1 \sim t_2$  の間では、制御信号 1002 は、制御信号 1004 と等しい値に設定されることがある。その結果、トランジスタ 910 及び 912 は、遮断モードになることがある。実施形態によっては、制御信号 1006 は、トランジスタ 915 の閾値電圧よりも高い値に設定されることがある。その結果、受信回路 109 の入力端子は、ゼロに等しい電圧に強制的になることがある。

20

#### 【0077】

$t_2 \sim t_3$  の間では、制御信号 1002 及び 1004 は、負の電圧に設定されることがある。実施形態によっては、制御信号 1002 及び 1004 は、負の電圧に同時に設定されることがある。実施形態によっては、この負の電圧は、図 3 に示した  $V_N$  に等しいことがある。

#### 【0078】

$t_3 \sim t_4$  の間では、制御信号 1002 及び 1004 は、ゼロか、又はパルス化回路 103 のバイアス電圧に設定されることがある。実施形態によっては、制御信号 1002 及び 1004 は、ゼロか、又はパルス化回路 103 のバイアス電圧に、同時に設定されることがある。

#### 【0079】

30

$t_4 \sim t_5$  の間では、制御信号 1002 は、トランジスタ 910 及び 912 のゲート - ソース電圧が閾値を上回るような電圧に設定されることがある。実施形態によっては、制御信号 1006 は、受信回路 109 の入力端子に関連した電圧が自由に増減することができるよう、トランジスタ 915 の閾値電圧未満の値に設定されることがある。

#### 【0080】

$t_5$  の後では、制御信号 1008 は、受信回路 109 を有効にする値に設定されることがある。

#### 【0081】

実施形態によっては、受信モードは  $t_0$  の前及び  $t_5$  の後の期間によって規定されることがある、送信モードは  $t_0 \sim t_5$  の間の期間によって規定されることがある。他の実施形態では、受信モードは  $t_1$  の前及び  $t_4$  の後の期間によって規定されることがある、送信モードは  $t_1 \sim t_4$  の間の期間によって規定されることがある。実施形態によっては、 $t_0$  は  $t_1$  と等しいことがある。実施形態によっては、 $t_1$  は  $t_2$  と等しいことがある。実施形態によっては、 $t_3$  は  $t_4$  と等しいことがある。実施形態によっては、 $t_4$  は  $t_5$  と等しいことがある。

40

#### 【0082】

本出願の態様は、1つ又は複数の利点を提供することがあり、それらの利点のうちの幾つかについては前述している。今から説明するのは、そのような利点の幾つかの非限定的な例である。全ての態様及び実施形態が必ずしも今から説明する利点の全てを提供するわけではないことを、理解されたい。更に、本出願の態様は、今から説明する利点に追加の

50

利点を提供することがあることを、理解されたい。

【0083】

本出願の態様は、受信回路の飽和をもたらすことなく受信することができる両極性パルスを生成するように構成されたパルス化回路を提供する。しかしながら、受信回路は、両極性パルスに関連した大きな正及び負の電圧スパイクに耐えるように設計されていない構成要素を含むことがある。

【0084】

本出願の態様は、送信モード中は送信回路から受信回路を切り離し、従って、両極性パルスによって引き起こされる受信回路に対する損傷を防止するように構成された対称スイッチを提供する。

10

【0085】

時間領域及び空間領域でアポダイズされたパルスを生成するには、マルチレベルパルスを制御する能力が必要である。本出願の態様は、追加の供給電圧を頼ることなく、時間領域及び空間領域のアポダイゼーションを提供するように構成されたフィードバック回路を提供する。従って、超音波機器に追加の供給電圧を組み込むと、相当に大きな手持ち式の超音波プローブがもたらされることがある。

【0086】

本出願の技術の幾つかの態様及び実施形態についてこのように説明してきたが、当業者であれば様々な変形例、修正例、及び改善例を容易に思い付くであろうことを理解されたい。そのような変形例、修正例、及び改善例は、本出願で説明される技術の趣旨及び範囲内であることが意図されている。従って、前述の実施形態は例としてのみ提示されたものであり、添付の特許請求の範囲及びその均等物の範囲内で、本発明の実施形態は具体的に説明されたものとは別の態様で実施されることがあることを、理解されたい。加えて、本明細書で説明した2つ以上の特徴、システム、物品、材料、及び／又は方法の任意の組み合わせは、そのような特徴、システム、物品、材料、及び／又は方法が互いに矛盾しない場合には、本開示の範囲内に含まれる。

20

【0087】

また、説明したように、幾つかの態様は、1つ又は複数の方法として具現化されることがある。方法の一部として行われる動作は、任意の適切な方法で順序付けられることがある。従って、例示的な実施形態では順次的動作として示されたとしても、幾つかの動作を同時にを行うことがある、例示された順序とは異なる順序で動作が行われる実施形態を、構築することができる。

30

【0088】

本明細書で定義し使用する全ての定義は、辞書の定義、参照により組み込まれる文献での定義、及び／又は定義された用語の一般的な意味を制御するものと理解されるべきである。

【0089】

本明細書及び特許請求の範囲で使用される不定冠詞「a」及び「an」は、特に断りの無い限り、「少なくとも1つ(at least one)」を意味するものと理解されるべきである。

【0090】

40

本明細書及び特許請求の範囲で使用される「及び／又は(and/or)」という語句は、そのように結合された要素の「一方又は両方(either of both)」、即ち、ある場合では連言的に存在し、他の場合では選言的に存在する要素を意味するものと理解されるべきである。

【0091】

本明細書及び特許請求の範囲で使用される場合、1つ又は複数の要素のリストに関する「少なくとも1つ(at least one)」という語句は、その要素リスト中の任意の1つ又は複数の要素から選択された少なくとも1つの要素を意味するものと理解されるべきであるが、その要素リスト内に具体的に列挙された全ての要素の少なくとも1つを必ずしも含むわけではなく、また、要素リスト内の要素の任意の組み合わせを排除するものではない。

50

この定義は、「少なくとも 1 つ (at least one)」という語句が言及する要素リスト内の具体的に特定された要素以外の要素が、具体的に特定された要素に関係していると、任意選択的に存在することがあることを許す。

#### 【0092】

「約 (approximately)」及び「約 (about)」という用語は、実施形態によっては目標値の  $\pm 20\%$  以内、実施形態によっては目標値の  $\pm 10\%$  以内、実施形態によっては目標値の  $\pm 5\%$  以内、実施形態によっては目標値の更に  $\pm 2\%$  以内を意味するものとして使用されることがある。「約 (approximately)」及び「約 (about)」という用語は、目標値を含むことがある。

#### 【0093】

10

特許請求の範囲では、上記の明細書と同様に、「備える (comprising)」、「含む (including)」、「運ぶ (carrying)」、「有する (having)」、「含む (containing)」、「含む (involving)」、「保持する (holding)」、「から構成される (composed of )」などの全ての移行句は、オープンエンドである、即ち、「～を含むがこれらには限定されない」ということを意味するものとして理解されるべきである。「からなる (consisting of )」及び「から本質的になる (consisting essentially of )」という移行句は、それぞれクローズド、又はセミクローズドの移行句であるものとする。

【図 1】

【図 2】

【図3】

【図4】

【図5A】

FIG. 5A

【図5B】

FIG. 5B

【図 6 A】

FIG. 6A

【図 6 B】

FIG. 6B

【図 7】

FIG. 7

【図 8 A】

【図 8 B】

【図 9】

【図 10】

FIG. 10

【図 11】

---

フロントページの続き

(72)発明者 チェン , カイリヤン

アメリカ合衆国 , コネチカット州 06437 , ギルフォード , リバー コロニー 7

(72)発明者 ラルストン , タイラー , エス .

アメリカ合衆国 , コネチカット州 06413 , クリントン , ビーチ パーク ロード 56

(72)発明者 ファイフ , キース , ジー .

アメリカ合衆国 , カリフォルニア州 94306 , パロ アルト , マタデロ アベニュー 635

審査官 西村 純

(56)参考文献 特開昭62-240032(JP,A)

特開昭61-069212(JP,A)

特開平09-074345(JP,A)

Chen et al., Ultrasonic Imaging Transceiver Design for CMUT: A Three-Level 30-Vpp Pulse-Shaping Pulser With Improved Efficiency and a Noise-Optimized Receiver , IEEE JOURNAL OF SOLID-STATE CIRCUITS , VOL. 48, NO. 11, 2013年11月

(58)調査した分野(Int.Cl. , DB名)

H04R 1/00 - 31/00

A61B 8/00 - 8/15

H03K 17/00 - 17/98