(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4217506号

(P4217506)

(45) 発行日 平成21年2月4日(2009.2.4)

(24) 登録日 平成20年11月14日(2008.11.14)

(51) Int.Cl.

F 1

**A61B 6/00 (2006.01)**

**H01L 27/14 (2006.01)**

**H01L 27/146 (2006.01)**

**H04N 5/32 (2006.01)**

**H04N 5/335 (2006.01)**

A 6 1 B 6/00 300 S

H 01 L 27/14 K

H 01 L 27/146 C

H 04 N 5/32

H 04 N 5/335 Q

請求項の数 10 (全 24 頁) 最終頁に続く

(21) 出願番号 特願2003-54520 (P2003-54520)

(22) 出願日 平成15年2月28日 (2003.2.28)

(65) 公開番号 特開2004-130058 (P2004-130058A)

(43) 公開日 平成16年4月30日 (2004.4.30)

審査請求日 平成18年2月20日 (2006.2.20)

(31) 優先権主張番号 特願2002-56127 (P2002-56127)

(32) 優先日 平成14年3月1日 (2002.3.1)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2002-234911 (P2002-234911)

(32) 優先日 平成14年8月12日 (2002.8.12)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2002-234912 (P2002-234912)

(32) 優先日 平成14年8月12日 (2002.8.12)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090273

弁理士 國分 孝悦

(72) 発明者 小林 功

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

(72) 発明者 辻井 修

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

(72) 発明者 望月 千織

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

最終頁に続く

(54) 【発明の名称】放射線撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の変換素子を有する画素を複数備える変換部を基板の放射線が入射する側に有し、前記変換部に入射した放射線量に応じて画像情報を出力する放射線撮像装置であつて、

前記変換部内に入射した放射線の照射量、前記変換部内への放射線の入射及び放射線の停止のうち、少なくともいずれか1つを検出するための第2の変換素子を有し、

前記第2の変換素子は、前記基板の放射線が入射する側で、前記変換部内の隣接する画素の前記第1の変換素子の間に、一方の幅が前記画素のピッチよりも小さい形状で配置されていることを特徴とする放射線撮像装置。

## 【請求項 2】

10

前記変換部は、前記第1の変換素子及び当該第1の変換素子に接続されたスイッチ素子を有する前記画素が行方向及び列方向に複数配置され、列方向の複数の前記スイッチ素子に接続される信号線を行方向に複数有し、

前記第2の変換素子は、隣接する前記信号線の間に配置されていることを特徴とする請求項1に記載の放射線撮像装置。

## 【請求項 3】

前記第1の変換素子は、列方向及び行方向に前記ピッチ  $p$  で配設されており、前記第2の変換素子の受光面の面積  $S$  が、

$$S = w \times h \quad (w < p, h = k \times p, k \geq 1)$$

ただし、 $w$  は前記一方の幅である第2の変換素子の行方向の長さ

20

$h$  は第 2 の変換素子の列方向の長さ

$k$  は実数

であることを特徴とする請求項 1 又は 2 に記載の放射線撮像装置。

#### 【請求項 4】

前記第 2 の変換素子は、前記第 1 の変換素子と同時に形成されたものであることを特徴とする請求項 1 ~ 3 のいずれか 1 項に記載の放射線撮像装置。

#### 【請求項 5】

前記第 1 の変換素子が MIS 型半導体構造で形成され、前記第 2 の変換素子が MIS 型半導体構造又は TFT 型の構造で形成されていることを特徴とする請求項 1 ~ 4 のいずれか 1 項に記載の放射線撮像装置。 10

#### 【請求項 6】

前記第 2 の変換素子に隣接して配置された前記第 1 の変換素子は、その他の前記第 1 の変換素子より面積が小さいことを特徴とする請求項 1 ~ 5 のいずれか 1 項に記載の放射線撮像装置。

#### 【請求項 7】

前記画像情報を出力するための第 1 の処理回路部と、

前記第 2 の変換素子からの出力を処理するための第 2 の処理回路部と、

を更に有し、

前記第 2 の処理回路部は、

前記第 2 の変換素子の出力を加算する加算手段と、

前記加算手段で加算された出力を積分する積分手段と、

前記積分手段で積分された値と予め設定されている閾値とを比較する比較手段と、

前記比較手段において前記閾値よりも前記積分された値が大きいと判定されたときには、前記変換部への放射線の照射を停止する放射線遮断手段とを含むことを特徴とする請求項 1 ~ 6 のいずれか 1 項に記載の放射線撮像装置。 20

#### 【請求項 8】

前記第 2 の変換素子が前記変換部内の複数の個所に設けられており、前記第 2 の処理回路部は、複数の第 2 の変換素子の中から最適個所の第 2 の変換素子を選択して放射線照射量を検出することを特徴とする請求項 7 に記載の放射線撮像装置。

#### 【請求項 9】

前記第 2 の処理回路部は、前記第 2 の変換素子の出力をもとに、前記第 1 の変換素子からの出力電荷を蓄積するメモリの蓄積停止タイミングを決定する手段を有することを特徴とする請求項 7 又は 8 に記載の放射線撮像装置。 30

#### 【請求項 10】

前記画像情報を出力するタイミングでは、前記第 2 の変換素子をオフ状態にすることを特徴とする請求項 1 ~ 9 のいずれか 1 項に記載の放射線撮像装置。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、放射線撮像装置に関し、特に、放射線により像を形成するものや、入射した放射線に対応した画像情報を出力するものに関する。 40

##### 【0002】

##### 【従来の技術】

近年、医療業界において「X 線画像情報のデジタル化」の要求が高まりつつある。このデジタル化が達成されれば、医師が最適なアングルでの患者の X 線画像情報をリアルタイムに知ることができ、その得られた X 線画像情報を光磁気ディスクのような媒体を用いて記録及び管理をすることができる。また、ファクシミリや他の通信方式等を利用すれば、患者の X 線画像情報を世界中のどこの病院にも短時間で送ることが可能となる。

##### 【0003】

また、建物の躯体などの物体内部の検査に代表される非破壊検査などにおいても、X 線撮 50

影をするための各種機器の設置や必要とする部位の撮影を、何度もやり直せるものでもない。

#### 【0004】

したがって、このような分野においても、所望部位のX線画像情報をリアルタイムに提供することに対する要求は高い。そこで、最近ではフィルムの代わりにCCD固体撮像素子やアモルファスシリコンセンサを用いたX線撮像装置が提案されてきている。

#### 【0005】

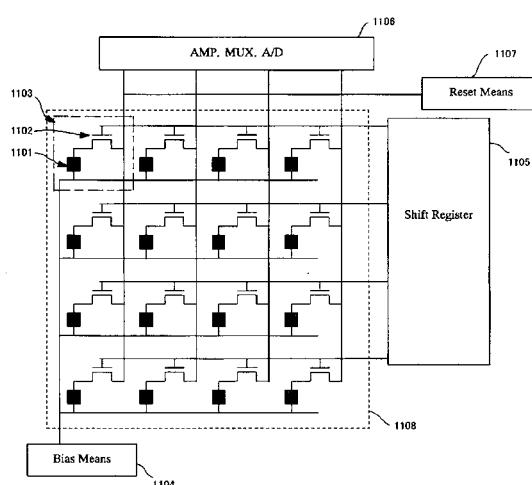

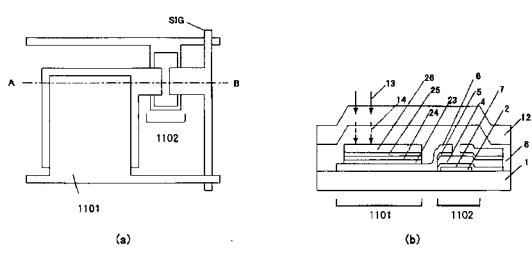

次に、本発明者らが以前提案した放射線撮像装置の一例を説明する。

図11は、二次元エリアセンサの構成を示す回路図である。また、図12は、二次元エリアセンサの1画素に相当する各構成素子の平面図及び断面図であり、図12(a)はその平面図、図12(b)はその断面図である。10

#### 【0006】

図11の放射線撮像装置においては、センサ素子1101と接続された転送用トランジスタ1102を1組として構成される画素1103が、2次元状に縦4セル、横4セルの合計16画素で構成されている。

#### 【0007】

そして、センサ素子1101はバイアス手段1104に接続され、転送用トランジスタ1102はそのゲートがゲート線を介してシフトレジスタ1105と接続されている。また、転送用トランジスタ1102の出力信号は信号出力線を介して増幅器・マルチプレクサ・A/D変換器1106に転送され、順次信号処理される。また、転送用トランジスタ1102の信号出力線には、リセット手段1107が接続されている。20

#### 【0008】

図11の破線で囲んだ部分は、大面積の同一絶縁基板1108上に形成されているが、このうち1画素に相当する部分の平面図を図12(a)に示す。

図12(a)に示すように、1画素には1つの光電変換素子1101と、1つの転送用トランジスタ(TFT)1102と、信号配線SIGが形成されている。

#### 【0009】

また、図12(a)中の破線A-B間で示した部分の断面図を図12(b)に示す。

図12(b)に示した層構成によれば、絶縁基板1上に、光電変換素子1101、TFT1102、及び信号配線SIGが同時に積層されて構成されている。これらは、絶縁基板1上に共通の下部メタル層2、窒化シリコン層(SiN)7、i層4、n層5、及び上部メタル層6の順に積層され、各層のエッチングのみで形成されている。その後、光電変換素子1101としてP層23、I層24、N層25を形成し、その上にITO等からなる上部電極層26を形成する。30

#### 【0010】

また、画素上部には、パッシベーション用窒化シリコン膜(SiN)8とCsI、Gd<sub>2</sub>O<sub>2</sub>S等の放射線を可視光に波長変換する蛍光体12が形成されている。放射線撮像装置に像情報の含まれるX線13が入射すると、蛍光体12で像情報光14に変換され、この光が光電変換素子S11に入射する。

#### 【0011】

次に、放射線撮像装置における、X線源から照射されるX線の露出を自動的に制御する、X線自動露出制御装置(AEC)について説明をする。40

#### 【0012】

一般に、2次元状に配設されたセンサを有する放射線撮像装置において、入力される光量を調整(AEC制御)することが必要である。これは以下に示す2つに分類することができる。

(1) AEC制御用のセンサを、放射線撮像装置とは別に別途設ける。

(2) 放射線撮像装置内の全部あるいは一部のセンサを高速で読み出して、AEC制御用信号とする。

#### 【0013】

10

30

40

50

従来は、入力するX線パターンを2次元画像化する2次元センサの前面に、X線の減衰が5%程度である薄型のAEC制御用センサを複数個配置して、これらのAEC制御用センサの出力によりX線の曝射をストップして、画像化に適切なX線量を得ようとするものであった。ここで使用されるAEC制御用センサとしては、イオンチャンバで直接的に電荷として取り出すものや、蛍光体光をファイバーで外部に取り出し、フォトマルで電荷に変換するものが使用されている。

## 【0014】

## 【発明が解決しようとする課題】

しかしながら、前述したように、2次元状に配設された放射線撮像装置において、別途AEC制御用のセンサを設けて入力される光量また放射線量を調整(AEC制御)する場合、AEC制御用センサの配置が問題となる。つまり、一般にAEC制御に必要な情報は被写体の中央部分にあり、画像撮像用センサによる撮像に支障無いようにAEC制御用センサを配置するには別途光学手段、あるいは光学的減衰の非常に小さいAEC制御用センサが必要となる。

10

## 【0015】

また、全画素を使用する場合には、画素数の比較的小ないセンサではAEC制御が可能であるが、画素数が2000個×2000個を超えるようなセンサでは高速駆動用回路が必要となり、装置全体のコスト上昇を引き起こすことになる。

## 【0016】

また、高速で駆動をする必要があるために、放射線撮像装置のセンサにおいて、電荷の蓄積時間及び電荷の転送時間、容量のリセット時間等の時間を十分にとることが困難となり、結果的に撮像画像の画質低下を引き起こしてしまうという問題がある。

20

## 【0017】

本発明は上述の問題点にかんがみてなされたもので、高速駆動を必要とせずに、入射する光量又は放射線量を調整(AEC制御)することができる放射線撮像装置及びその駆動方法を提供することを目的とする。

## 【0018】

## 【課題を解決するための手段】

本発明の放射線撮像装置は、第1の変換素子を有する画素を複数備える変換部を基板の放射線が入射する側に有し、前記変換部に入射した放射線量に応じて画像情報を出力する放射線撮像装置であつて、前記変換部内に入射した放射線の照射量、前記変換部内への放射線の入射及び放射線の停止のうち、少なくともいずれか1つを検出するための第2の変換素子を有し、前記第2の変換素子は、前記基板の放射線が入射する側で、前記変換部内の隣接する画素の前記第1の変換素子の間に、一方の幅が前記画素のピッチよりも小さい形態で配置されている。

30

## 【0031】

## 【発明の実施の形態】

次に、添付図面を参照しながら本発明の放射線撮像装置の実施の形態について説明する。

## 【0032】

40

## (第1の実施形態)

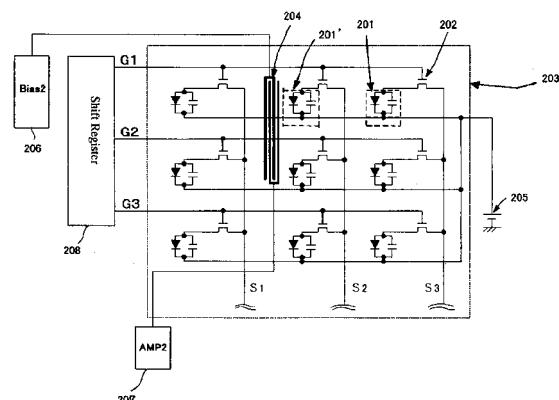

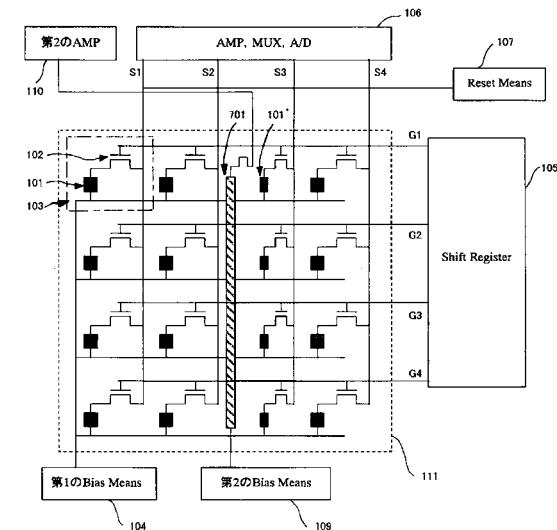

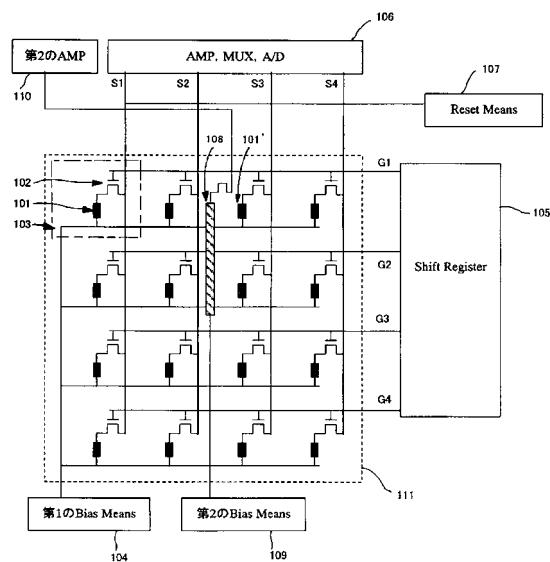

以下、本発明の第1の実施形態を図1に基づいて説明する。

図1は、本実施形態の放射線撮像装置の回路図である。図1に示すように、本実施形態の放射線撮像装置は、第1の光電変換素子101及びこれに接続された転送用スイッチ素子であるトランジスタ102からなる画素103が2次元(マトリクス)状に多数配置されてなる変換部を構成する光電変換基板111と、第2の光電変換素子108及びこれに接続され、変換部内に入射した放射線の総照射量を検出する処理回路部である第2の増幅器(AMP)110とを備えた総照射量検出手段とを有して構成されている。ここでは図示の便宜上、縦4セル、横4セルの合計16画素を示している。

## 【0033】

50

そして、第1の光電変換素子101は、第1のバイアス手段104に接続され、トランジスタ102はそのゲートが行毎にゲート線G1～G4を介してシフトレジスタ105と接続されている。また、トランジスタ102の出力信号は列毎に信号線S1～S4を介して増幅器・マルチプレクサ・A/D変換器106に転送され、順次信号処理される。また、トランジスタ102の列毎の信号線S1～S4には、リセット手段107が接続されている。

#### 【0034】

更に、通常の画像を撮像するための第1の光電変換素子101とは異なる形状をした、図1の斜線でハッキングをつけた細長い形状の第2の光電変換素子108が光電変換基板111に配置されている。

10

#### 【0035】

第1の光電変換素子101は、図1において灰色に着色された素子の部分であり、4個×4個の2次元状に等ピッチ間隔pで配置されており、第1のバイアス手段(Bias Means)104に接続されている。

#### 【0036】

シフトレジスタ105により選択された行に対応する第1の光電変換素子101で生成された電荷は、トランジスタ102を介して読み出され、増幅器・マルチプレクサ・A/D変換器106に転送され、選択的に増幅器(AMP)で増幅され、その後、A/D変換器で変換される。

20

#### 【0037】

その読み出した後に、リセット手段107により電荷のリセット動作が行われる。ただし、これは放射線撮像装置の構造により必要ない場合もある。

#### 【0038】

第2の光電変換素子108は、画素103間に、かつ列方向の信号線(S2とS3)間に細長く配置されている。ここで、第2の光電変換素子108は、第1の光電変換素子101と同一平面内で同層構成に配置されるため、第2の光電変換素子108に隣接して配置された第1の光電変換素子101'は、その他の第1の光電変換素子101よりもその面積を小さくして構成される。

#### 【0039】

第2の光電変換素子108は、第2のバイアス手段(Bias Means)109に接続されており、その電荷の読み出しの際には、シフトレジスタ105により選択されることなく、入射光量に応じて電荷を常に出力することができる。そのため、常に一定電位が印加されている。この第2の光電変換素子108で検出された電荷は、第2の増幅器(AMP)110で増幅され、この出力を加算することにより放射線の総照射量を検出している。

30

#### 【0040】

本実施形態によれば、AEC制御用センサ(第2の光電変換素子108)を光電変換基板111内に作り込むため、AEC制御用センサを別体で設ける必要が無くなり、放射線検出装置を小型化できるとともに、回路構成を簡易にすることが可能となる。また、AEC制御用センサと画像情報に使用するセンサ(第1の光電変換素子101)とを別構成とし、それぞれ別に処理回路部を設けることにより、電荷の読み出しを高速駆動で行う必要も無くなるため、撮像画像の画質低下を防止することができる。

40

#### 【0041】

また、AEC制御用センサ(第2の光電変換素子108)を行方向の駆動配線と交差して複数の画素にまたがるように配置し、列方向の信号線S1～S4に平行に配置させ、列方向の信号線S1～S4と交差する部分を設けないようにすることによって、信号線S1～S4に余分な容量が寄生するがないため、SN比の高い出力信号の読み出しを行うことが可能となる。また、信号線と平行な方向には複数の画素がまたがって配置されているために、放射線照射量も広い領域で平均化して検出できるため好ましい。

#### 【0042】

(第2の実施形態)

50

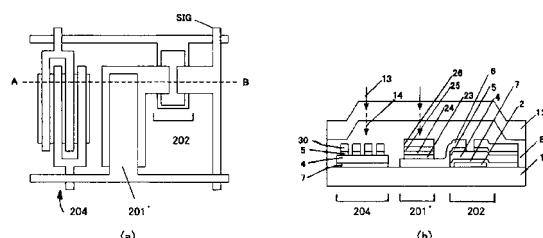

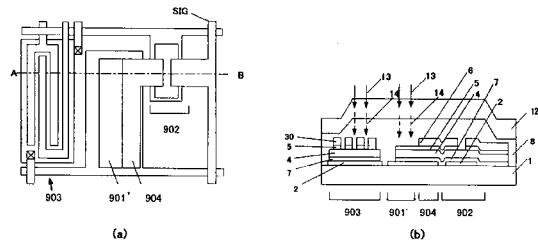

以下、本発明の第2の実施形態を図2及び図3に基づいて説明する。

図2は、本実施形態の放射線撮像装置の回路図である。また、図3は、放射線撮像装置の1画素に相当する各構成素子の平面図及び断面図であり、図3(a)はその平面図であり、図3(b)は図3(a)中の破線A-B間で示した部分の断面図である。

#### 【0043】

本実施形態において、第1の光電変換素子201はPIN構造をしている。スイッチ素子202はTFT(薄膜トランジスタ)で形成されている。また、スイッチ素子202のゲートはゲート線G1～G3を介してシフトレジスタ208に接続されている。また、スイッチ素子202からの出力信号は、信号線S1～S3を介して外部に出力される。

#### 【0044】

基板上に配設された光電変換回路部203内に、通常の画像を読み出すための第1の光電変換素子201に比べて細長く、通常の画素の信号線方向に複数の画素にまたがって第2の光電変換素子204が配置されている。特に、本実施形態においては、櫛歯状の形状で形成されている。

#### 【0045】

第2の光電変換素子204は、第1の光電変換素子201と同一平面内に配置されるため、これに隣接して配置された第1の光電変換素子201'は、他の第1の光電変換素子201よりも面積を小さくして形成されており、この面積の減少分は読み出した後の画像補正により補うことが可能である。

#### 【0046】

また、第2の光電変換素子204は、画像情報を得るための第1のバイアス電源205とは独立して第2のバイアス電源(Bias2)206に接続されており、入射光量に応じて電荷を常に出力する。従って、常にバイアスが印加された状態となっている。そして、その電荷は増幅器(AMP2)207により増幅される。

#### 【0047】

図3は、放射線撮像装置の1画素に相当する各構成素子及び第2の光電変換素子204の平面図及び断面であり、図3(a)はその平面図であり、図3(b)は図3(a)のその断面図である。

#### 【0048】

ここで、AEC制御用センサである第2の光電変換素子204の層構成は、TFT202の下部メタル層2を削除した構成となっている。以下にその形成方法を示す。

#### 【0049】

まず、絶縁材料であるガラス基板1上にスパッタ等により、下部メタル層2としてCrを約50nm程度堆積させ、その後フォトリソグラフィによりパターニングを行い、不要なエリアをエッチングする。これにより、TFT202のゲート電極が形成される。

#### 【0050】

次に、CVDにより同一真空中で窒化シリコン膜(SiN)7、i層4、n層5をそれぞれ約200nm、500nm、50nm堆積する。これら各層はTFT202においては、窒化シリコン膜(SiN)7がゲート絶縁膜、i層4が半導体層、n層5がオームикコンタクト層となる。また、第2の光電変換素子204においては、窒化シリコン膜(SiN)7が下部絶縁層、i層4が光電変換半導体層、n層5がオームикコンタクト層となる。

#### 【0051】

各層堆積後、Alをスパッタ等で約1000nm堆積させる。更に、フォトリソグラフィによりパターニングを行い、不要なエリアをエッチングにて除去する。これにより、TFT202の主電極であるソース電極並びにドレイン電極、信号線SIGとなる上部メタル層6が形成される。また、第2の光電変換素子204においては、上部電極30が形成される。

#### 【0052】

その後、第1の光電変換素子201'をしてP層23、I層24、N層25を形成し、そ

10

20

30

40

50

の上にITO等からなる上部電極層26を形成する。更に、TFT202のチャネル部のみn層5をRIEでエッティングし、その後不必要なSiN膜7、i層4、n層5に対してエッティングを行うことで各素子が分離される。

#### 【0053】

前述の作製プロセスにより、第1の光電変換素子201'、TFT202、第2の光電変換素子204が作製される。以上、1画素について説明を行ったが他の画素についても同時に形成されることとは言うまでもない。

#### 【0054】

また、耐久性を向上させるために、各素子の上部に窒化シリコン膜(SiN)等のパッシベーション膜8を形成して覆い、更に、CsI、Gd<sub>2</sub>O<sub>2</sub>S等の波長変換体となる蛍光体12を形成する。

10

#### 【0055】

本実施形態においては、AEC制御用センサである第2の光電変換素子204では、入射した放射線の総照射量のみが分かればよいため、その放射線照射中は常にバイアスを印加している。そのため第2の光電変換素子204は、TFT202の下部メタル層2を取り除いた構成で作製することができるため、作製プロセスを簡単にすることことができ、コスト低減を図ることができる。

#### 【0056】

##### (第3の実施形態)

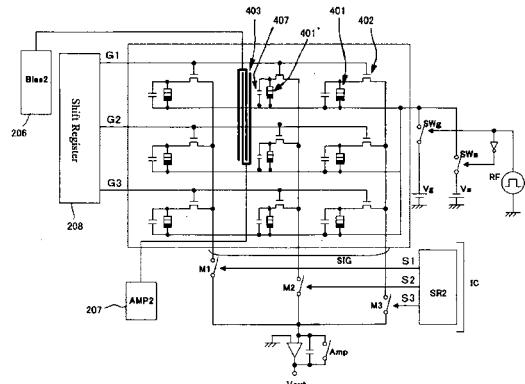

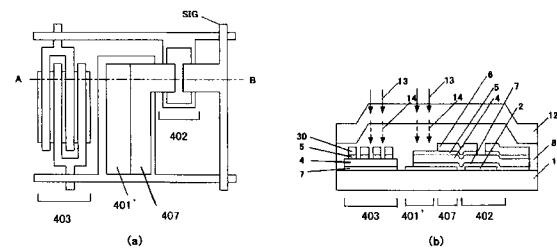

以下、本発明の第3の実施形態を図4及び図5に基づいて説明する。

20

図4は、本実施形態の放射線撮像装置の回路図である。また、図5は、放射線撮像装置の1画素に相当する各構成素子の平面図と断面図であり、図5(a)はその平面図、図5(b)にその断面図を示す。本実施例においては第1の光電変換素子401はMIS型構造からなり、スイッチ素子402はTFTからなる。

#### 【0057】

本実施例においても、第2の光電変換素子403に隣接して配置された第1の光電変換素子401'は、その他の第1の光電変換素子401よりも面積を小さくする。

#### 【0058】

第2の光電変換素子403は、第2のバイアス電源(Bias2)206に接続されており、読み出しの際にはシフトレジスタ208により選択される必要はなく、入射光量に応じて電荷が常に出力するようにバイアスが常に印加されている。また、第2の光電変換素子403で生成された電荷は、増幅器(AMP2)207により増幅される。

30

#### 【0059】

図5は、第2の光電変換素子403とそれに隣接する第1の光電変換素子401'を含む1画素の平面図及び断面図であり、図5(a)はその平面図であり、図5(b)は断面図である。以下にその形成方法を示す。

#### 【0060】

まず、絶縁材料であるガラス基板1上にスパッタ等により、Crを約50nm堆積させて下部電極層2を形成し、その後フォトリソグラフィによりパターニングを行い、不必要なエリアをエッティングする。この際に、第2の光電変換素子403が形成される領域の下部電極層2は取り除いておく。これにより光電変換素子401'の下部電極、TFT402のゲート電極、及びキャパシタ407の下部電極が形成される。

40

#### 【0061】

次に、CVDにより同一真空中で窒化シリコン層(SiN)7、i層4、n層5をそれぞれ約200nm、500nm、50nm堆積する。これら各層は光電変換素子401'においては、窒化シリコン膜(SiN)7が下部絶縁層、i層4が光電変換半導体層、n層5がホール注入阻止層となる。また、TFT402においては、窒化シリコン膜(SiN)7がゲート絶縁膜、i層4が半導体層、n層5がオーミックコンタクト層となる。更に、キャパシタ407においては、それら窒化シリコン膜(SiN)7、i層4、n層5が中間層となり、第2の光電変換素子403においては、窒化シリコン膜(SiN)7が下

50

部絶縁層、*i*層4が光電変換半導体層、*n*層5がオーミックコンタクト層となる。また、これらは信号配線S I Gのクロス部絶縁層としても使われる。

#### 【0062】

各層の厚さはこれに限らず二次元エリアセンサとして使用する電圧、電流、電荷、入射光量等により最適に設計するが、少なくとも窒化シリコン層(SiN)7は電子とホールが通過できず、また、TFT402のゲート絶縁膜として機能させるためには、50nm以上の厚さが必要である。

#### 【0063】

各層堆積後、上部メタル層6としてA1をスパッタ等で約1000nm堆積させる。更に、フォトリソグラフィによりパターニングを行い、不必要的エリアをエッチングにて除去する。これにより、光電変換素子401'の上部電極、TFT402の主電極であるソース電極並びにドレイン電極、キャパシタ407の上部電極、信号配線S I G、また、第2の光電変換素子403においては、上部電極30が形成される。ここで、素子の特性により第1及び第2の光電変換素子401'、403の上部電極上のみにITO等を設けてよい。

10

#### 【0064】

また、更に、TFT402のチャネル部のみ*n*層5をRIEでエッチングし、その後不必要的窒化シリコン層(SiN)7、*i*層4、*n*層5をエッチングし各素子が分離される。

#### 【0065】

前述の作製プロセスにより、第1の光電変換素子401'、TFT402、第2の光電変換素子403及びキャパシタ407が作成される。以上、1画素について説明を行ったが他の画素についても同時に形成されることは言うまでもない。

20

#### 【0066】

また、耐久性を向上させるために、各素子の上部を窒化シリコン(SiN)等のパッシベーション膜8を形成して覆い、更に、CsI、Gd<sub>2</sub>O<sub>2</sub>S等の波長変換体となる蛍光体12を形成する。

#### 【0067】

ここで、AEC制御用センサである第2の光電変換素子403での層構成は、前述したように第1の光電変換素子401'、TFT402及びキャパシタ407の下部メタル層2を削除した層構成である。

30

#### 【0068】

このように、AEC制御用センサ(第2の光電変換素子403)では、入射した放射線の総照射量のみが分かれればよいために、第1の光電変換素子401'及びスイッチ素子402などの層構成とともに作製することができるため、AEC制御用センサの作製プロセスを簡略化することができ、コスト低減を図ることができる。

#### 【0069】

##### (第4の実施形態)

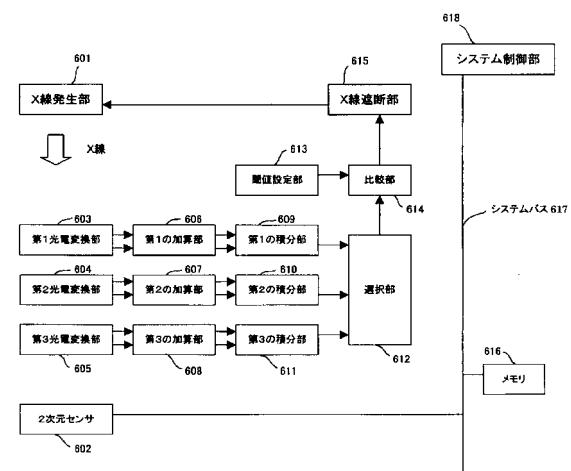

以下、本発明の第4の実施形態を図6に基づいて説明する。

図6は、本実施形態の放射線撮像装置のシステム構成図である。X線発生部601から曝射されたX線は、不図示の蛍光部により可視光に変換されて、像情報を有する放射線が2次元センサ602に入射する。

40

#### 【0070】

また、この2次元センサ602への入射と同時に、センサ基板上に作り込まれたAEC制御用センサである第2の光電変換素子の第1光電変換部603、第2光電変換部604、第3光電変換部605にも可視光に変換された光が照射する。

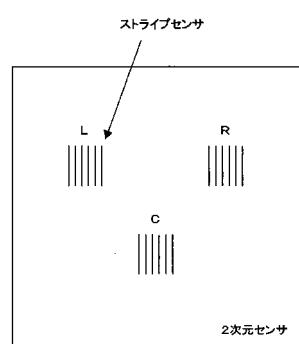

#### 【0071】

AEC制御用センサである第2の光電変換素子の各光電変換部603～605は、それぞれがセンサ基板内の異なる場所に配置されている。例えば、図13に示すようなストライプ状のAEC制御用センサ(第2の光電変換素子)のグループL、R、Cの集合が挙げられる。

50

**【 0 0 7 2 】**

第2の光電変換素子の各光電変換部 603～605で入射光から発生した電荷は、各光電変換部 603～605から取り出されて、各加算部 606～608でグループごとに加算される。ここでの加算方法は単純に加算する他に、図13に示すように6本のストライプに重み付けを行って加算をしてよい。これらの各加算部 606～608で加算された電荷は、それぞれ各積分部 609～611で積分され、各積分出力は選択部 612に入力される。

**【 0 0 7 3 】**

選択部 612では、各積分部 609～611である3チャンネルの積分出力を選択的に使用するか、加算して使用するかを制御する。この制御は、撮影される部位に依存しており、例えば、胸部正面の撮影であれば、グループLとグループRのいずれかの出力が大きい方を選択し、腹部や胸部側面の撮影であれば、グループCの出力を単独で採用するなどである。10

**【 0 0 7 4 】**

選択部 612で選択された出力は、比較部 614において閾値設定部 613で予め設定されている閾値と比較される。この閾値よりも当該出力が大きければ、X線遮断部 615を駆動して、X線発生部 601からのX線の曝射を停止させる。このX線曝射の停止が行われると、2次元センサ 602の積分が終了し、その2次元センサ 602からのデータは、A/D変換された後にメモリ 616に転送されて記憶される。このメモリ 616に記憶されたデータは、システムバス 617を介して接続されているシステム制御部 618で制御され、その読み出し等がなされる。20

**【 0 0 7 5 】**

このように第2の光電変換素子を用いてその出力を利用することにより、X線の曝射停止の制御を行うことができるとともに、これに起因して2次元センサ 602の積分を早期に終了して、その2次元センサ 602に蓄積される不必要なオフセット電荷を制限することができる。

**【 0 0 7 6 】**

また、データの取り込みをX線の曝射停止に合わせて行うようにすることによって、撮影画像の表示を早期に行うことができるようになる。

**【 0 0 7 7 】**

(第5の実施形態)30

以下、本発明の第5の実施形態を図7に基づいて説明する。

図7は、本実施形態の放射線撮像装置の回路図である。なお、前記第1の実施形態の図1で説明した構成要素には同一の符号を付し、以下では前記第1の実施形態との相違点について説明する。

**【 0 0 7 8 】**

本実施形態においては、AEC制御用センサである第2の光電変換素子 701が4画素分の大きさ(端の画素から端の画素まで)となっている。

**【 0 0 7 9 】**

このように信号線 S1～S4と平行な方向の幅は画素 103のピッチよりも小さく、もう一方の幅は4画素分にわたっているため画素 103のピッチの約4倍となっている。このように、信号線 S1～S4と交差しない方向に幅を大きくして、AEC制御用センサである第2の光電変換素子 701の受光面積を大きくすることにより、AEC制御用センサである第2の光電変換素子 701で発生する光電流を増加させることができとなり、AEC制御用センサ(第2の光電変換素子 701)の感度を向上させることが可能となる。40

**【 0 0 8 0 】**

(第6の実施形態)

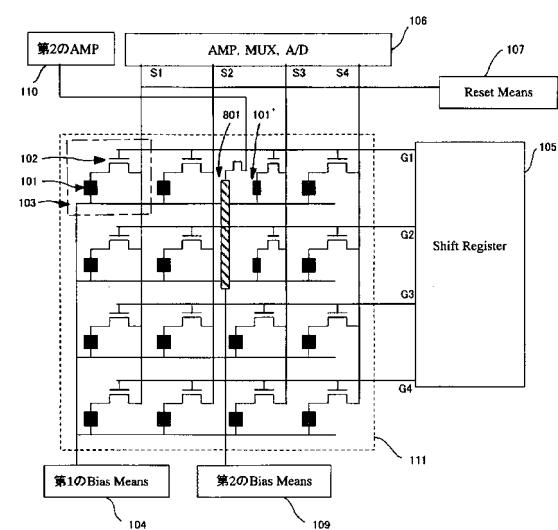

以下、本発明の第6の実施形態を図8に基づいて説明する。

図8は、本実施形態の放射線撮像装置の回路図である。なお、前記第1の実施形態の図1で説明した構成要素には同一の符号を付し、以下では前記第1の実施形態との相違点につ50

いて説明する。

【0081】

本実施形態においては、同一の列内に配された第1の光電変換素子でもAEC制御用センサである第2の光電変換素子801と隣接していない第1の光電変換素子においては、通常の画素の大きさにしている。

【0082】

このような構成とすることにより、第1の光電変換素子における出力を、光電変換素子が小さくなっていることにより補正する画素の数を少なくすることが可能となる。

【0083】

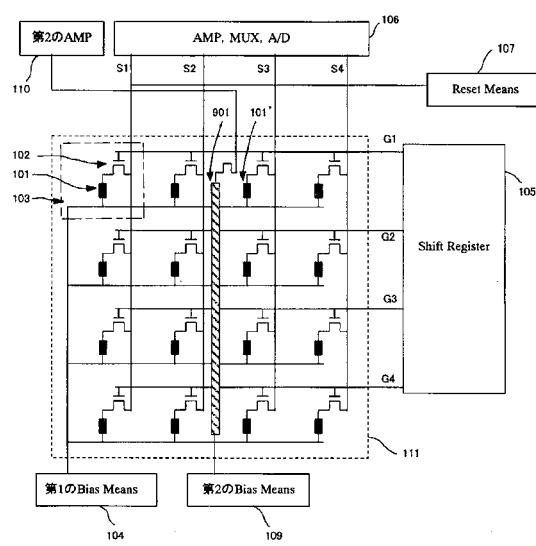

(第7の実施形態)

10

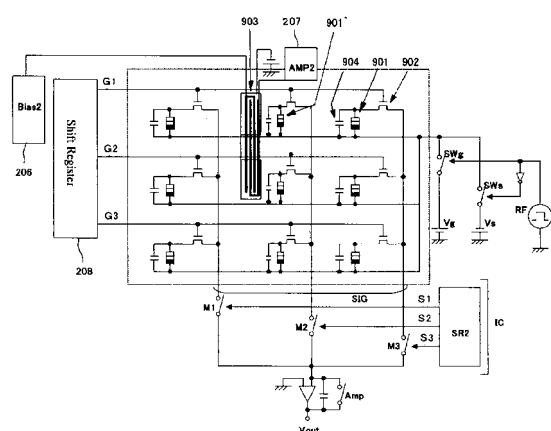

以下、本発明の第7の実施形態を図9に基づいて説明する。

図9は、本実施形態の放射線撮像装置の全体回路図である。なお、前記第1の実施形態の図1で説明した構成要素には同一の符号を付し、以下では前記第1の実施形態との相違点について説明する。

【0084】

本実施形態においては、第2の光電変換素子901が第1の光電変換素子形成領域同一の長さ、もしくは幅を有しており第1の光電変換素子の大きさを全ての画素で同じにしている。

【0085】

このように、第1の光電変換素子の大きさを全ての画素で同じにすることにより、第1の光電変換素子における光電変換素子の大きさが異なることによる、出力補正する必要性が無くすことができる。

20

【0086】

(第8の実施形態)

以下、本発明の第8の実施形態を図10に基づいて説明する。

図10は、本実施形態の放射線撮像装置の回路図である。なお、前記第1の実施形態の図1で説明した構成要素には同一の符号を付している。以下では前記第1の実施形態との相違点について説明する。

【0087】

本実施形態においては、AEC制御用の第2の光電変換素子108を第1の光電変換素子形成領域に局所的に設けながらも、かつ第1の光電変換素子101の大きさを全ての画素で同じにしている点である。

30

【0088】

このように、第1の光電変換素子の大きさを全ての画素で同じにすることにより、第1の光電変換素子における光電変換素子の大きさが異なることによる、出力補正する必要性が無くすことができる。

【0089】

(第9の実施形態)

以下、本発明の第9の実施形態を図14及び図15に基づいて説明する。

図14は、本実施形態の放射線撮像装置の回路図である。また、図15は、放射線撮像装置の1画素に相当する各構成素子の平面図と断面図であり、図15(a)にその平面図、図15(b)にその断面図を示す。

40

【0090】

本実施形態においては、第1の光電変換素子901はMIS型構造からなり、スイッチ素子902はTFTからなる。放射線撮像装置は、第1の光電変換素子901、スイッチ素子902、キャパシタ904を1画素として形成されている。また、第2の光電変換素子903は、TFT型の構造となっており、そのゲート(下メタル)が、一定電位になるようバイアスが印加されている構造となっている。

【0091】

本実施形態においても、第2の光電変換素子903に隣接して配置された第1の光電変換

50

素子 901' は、その他の第 1 の光電変換素子 901 よりもその面積を小さくして構成される。

#### 【0092】

第 2 の光電変換素子 903 のソースもしくはドレイン電極は、第 2 のバイアス電源 (Bias 2) 206 に接続されており、読み出しの際にはシフトレジスタ 208 により選択される必要はなく、入射光量に応じて電荷が常に出力するようにバイアスが常に印加されている。また、ゲート電極は一定電位、図 14 では負のバイアスが印加されている。第 2 の光電変換素子 903 で生成された電荷は、増幅器 (AMP 2) 207 により増幅される。

#### 【0093】

図 15 は、第 2 の光電変換素子 903 とそれに隣接する第 1 の光電変換素子 901' を含む 1 画素の平面図及び断面図であり、図 15 (a) はその平面図であり、図 15 (b) は断面図である。形成方法は、第 3 の実施形態で述べたのと同様の方法を用い、第 2 の光電変換素子のゲート (下電極) を残した構成とすればよい。

10

#### 【0094】

また、耐久性を向上させるために、各素子の上部を窒化シリコン (SiN) 等のパッシブーション膜 8 を形成して覆い、更に、CsI、Gd<sub>2</sub>O<sub>2</sub>S 等の波長変換体となる蛍光体 12 を形成する。

#### 【0095】

本実施形態においては、第 2 の光電変換素子 903 をスイッチ素子 902 である TFT 同様の層構成として、プロセスの簡易化を図り、更に、第 2 の光電変換素子 903 の特性も安定したものを得ることが可能となる。

20

#### 【0096】

また、第 2 の光電変換素子 903 にかかるソース・ドレインへのバイアス、ゲートへのバイアス、信号の増幅などの処理回路を、第 2 の光電変換素子 903 が配された領域から近い辺に集めることによって、配線の引き回しが容易になって好ましい。

#### 【0097】

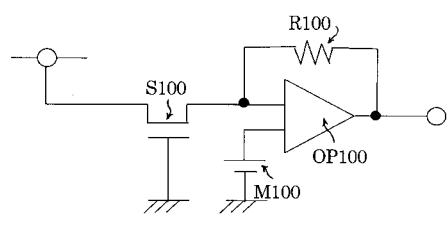

##### (第 10 の実施形態)

次に、第 2 の光電変換素子の駆動及び信号の処理について説明する。

以下、本発明の第 10 の実施形態を図 16 に基づいて説明する。

図 16 は、図 14 に示した第 2 の光電変換素子 903 が TFT 型センサである場合の処理回路部を示している。図 16 に示すように、本実施形態の放射線撮像装置は、TFT 型である第 2 の光電変換素子 S100 と、図 14 における第 2 の増幅器 (AMP 2) であるオペアンプ OP100 と、電源 M100 と、フィードバック抵抗 R100 とを備えている。

30

#### 【0098】

放射線撮像装置の駆動方法としては、まず、TFT 型である第 2 の光電変換素子 S100 のソース電極とドレイン電極との間にバイアスを印加し、ゲート電極を一定電位に固定する。

#### 【0099】

続いて、この状態で信号光が入射されると、光電流が発生し、正の信号電荷 (ホール) がフィードバック抵抗 R100 へ流れるため、この光電流をオペアンプ OP100 の出力端子で読み取ることが可能となる。この時、オペアンプ OP100 の正相入力端子に電源 M100 を接続することにより、TFT 型である第 2 の光電変換素子 S100 のソース電極の電位を電源 M100 の電位にすることができる。

40

#### 【0100】

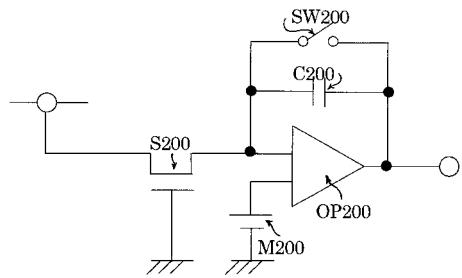

##### (第 11 の実施形態)

以下、本発明の第 11 の実施形態を図 17 に基づいて説明する。

図 17 は、図 14 に示した第 2 の光電変換素子 903 が TFT 型センサである場合の処理回路部を示し、また、第 10 の実施形態の他の形態を示したものである。図 16 に示すように、本実施形態の放射線撮像装置は、TFT 型である第 2 の光電変換素子 S200 と、図 14 における第 2 の増幅器 (AMP 2) であるオペアンプ OP200 と、電源 M200

50

と、スイッチ SW200 と、フィードバック容量 C200 とを備えている。

【0101】

放射線撮像装置の駆動方法としては、まず、TFT型である第2の光電変換素子 S200 のソース電極とドレイン電極との間にバイアスを印加し、ゲート電極を一定電位に固定する。

【0102】

続いて、この状態で信号光が入射されると、光電流が発生し、正の信号電荷（ホール）がフィードバック容量 C200 へ流れるため、オペアンプ OP200 の出力端子で蓄積された正の信号電荷（ホール）の総電荷量を読み取ることが可能となる。この時、スイッチ SW200 は開放されており、また、オペアンプ OP200 の正相入力端子に電源 M200 を接続する事により、TFT型である第2の光電変換素子 S200 のソース電極の電位を電源 M200 の電位にすることができる。10

【0103】

続いて、オペアンプ OP200 の出力端子で蓄積された正の信号電荷（ホール）の総電荷量を読み取った後、スイッチ SW200 を閉じて、蓄積された総電荷をリセットする。

【0104】

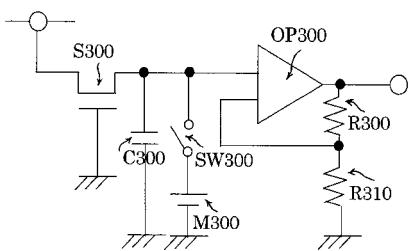

（第12の実施形態）

以下、本発明の第12の実施形態を図18に基づいて説明する。

図18は、図14に示した第2の光電変換素子 S903 が TFT型センサである場合の処理回路部を示し、また、第10の実施形態のその他の形態を示したものである。図18に示すように、本実施形態の放射線撮像装置は、TFT型である第2の光電変換素子 S300 と、図14における第2の増幅器（AMP2）であるオペアンプ OP300 と、電源 M300 と、スイッチ SW300 と、フィードバック抵抗 R300、R310 とを備えている。20

【0105】

放射線撮像装置の駆動方法としては、まず、TFT型である第2の光電変換素子 S300 のソース電極とドレイン電極との間にバイアスを印加し、ゲート電極を一定電位に固定する。

【0106】

続いて、この状態で信号光が入射されると、光電流が発生して、正の信号電荷（ホール）が蓄積容量 C300 へ蓄積されるため、蓄積された正の信号電荷（ホール）の総電荷量の電位をオペアンプ OP300 によって  $((R300 + R310) / R310)$  の増幅率で増幅できるため、オペアンプ OP300 の出力端子で増幅された電位を読み取ることが可能となる。この時、スイッチ SW300 は開放されている。30

【0107】

続いて、オペアンプ OP300 の出力端子で増幅された電位を読み取った後、スイッチ SW300 を閉じて蓄積された総電荷をリセットし、TFT型である第2の光電変換素子 S300 のソース電極を電源 M300 の一定電位に固定する。

【0108】

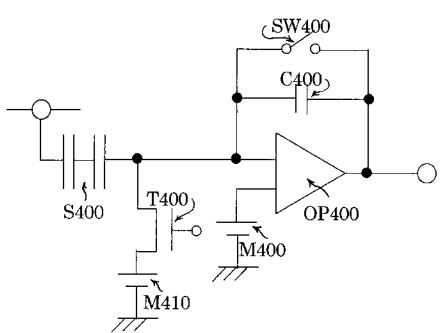

（第13の実施形態）

以下、本発明の第13の実施形態を図19に基づいて説明する。

図19は、図17に示した第2の光電変換素子 S200 が MIS型センサである場合の処理回路部を示したものである。図19に示すように、本実施形態の放射線撮像装置は、MIS型である第2の光電変換素子 S400 と、オペアンプ OP400 と、電源 M400、M410 と、トランジスタ T400 と、スイッチ SW400 と、フィードバック容量 C400 とを備えている。40

【0109】

放射線撮像装置の駆動方法としては、まず、MIS型である第2の光電変換素子 S400 の上下電極間にバイアスを印加する。

【0110】

10

20

30

40

50

続いて、この状態で信号光が入射されると、光電荷が発生し、正の信号電荷（ホール）がフィードバック容量C400へ流れるため、オペアンプOP400の出力端子で蓄積された正の信号電荷（ホール）の総電荷量を読み取ることが可能となる。この時、スイッチSW400は開放されており、また、オペアンプOP400の正相入力端子に電源M400を接続することにより、MIS型である第2の光電変換素子S400のオペアンプOP400の入力側電極の電位を電源M400の電位にすることができる。

#### 【0111】

続いて、オペアンプOP400の出力端子で蓄積された正の信号電荷（ホール）の総電荷量を読み取った後、スイッチSW400を閉じて、MIS型である第2の光電変換素子S400に蓄積された光電荷をリセット（リフレッシュ）する。

10

#### 【0112】

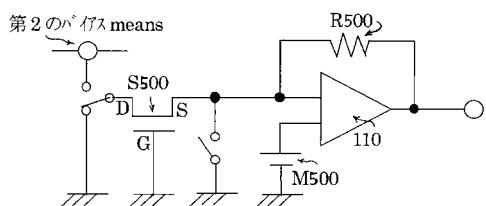

##### (第14の実施形態)

以下、本発明の第14の実施形態を図20に基づいて説明する。

図20は、図1に示す第2の光電変換素子108がTFT型センサである場合の処理回路部を示している。

S500がTFT型である第2の光電変換素子であり、Dがドレイン電極、Sがソース電極、Gがゲート電極を示している。また、110は図1における第2の増幅器（AMP：オペアンプ）、M500は電源、R500はフィードバック抵抗である。

#### 【0113】

実際の駆動方法としては、まず、TFT型である第2の光電変換素子S500のソース電極とドレイン電極との間にバイアスを印加し、ゲート電極を一定電位に固定する。

20

#### 【0114】

続いて、この状態で信号光が入射されると、光電流が発生し、正の信号電荷（ホール）がフィードバック抵抗R500へ流れ、第2の増幅器110の出力端子で光電流を読み取ることが可能となる。この時、第2の増幅器110の正相入力端子に電源M500を接続することにより、TFT型である第2の光電変換素子S500のソース電極の電位を電源M500の電位にすることができる。

#### 【0115】

また、第2の光電変換素子S500は、周りにある第1の光電変換素子101の信号に影響を及ぼさないように、第1の光電変換素子101が読み取った画像情報を出力するタイミングでは、第2の光電変換素子S500の各電極の電位を接地（GND）電位もしくは一定電位に固定し、オフ状態とする。

30

これにより、第1の光電変換素子101が読み取った信号を画像情報として出力する動作における影響をなくすことが可能となる。

#### 【0116】

また、AEC制御用センサ（第2の光電変換素子S500）の出力を第2の増幅器110を用いて電流として読み取ることにより、第2の光電変換素子S500の出力によりX線の曝射を停止して、画像化に適切なX線量を得るのみならず、曝射されているX線が停止したタイミングを得ることも可能になる。

#### 【0117】

40

##### (第15の実施形態)

以下、本発明の第15の実施形態を図21及び図22に基づいて説明する。

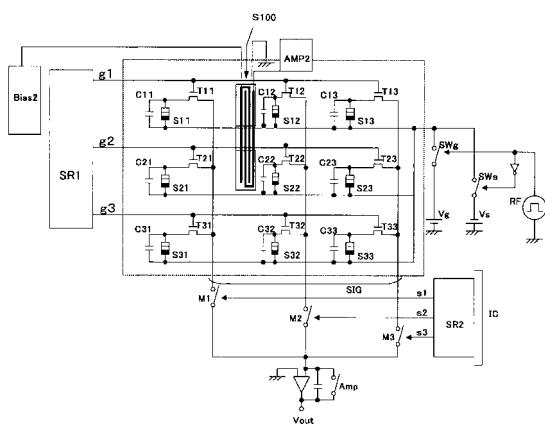

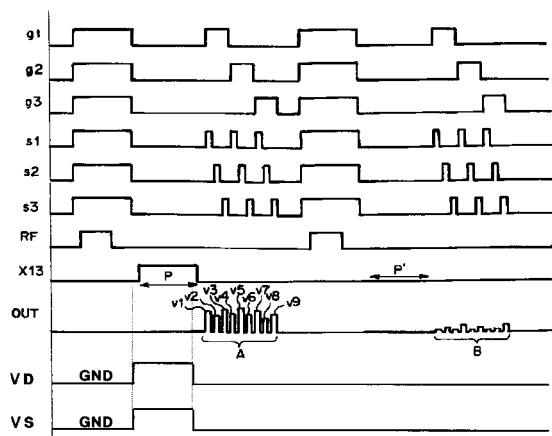

図21は、本実施形態の放射線撮像装置の回路図である。また、図22は、本実施形態の放射線撮像装置のタイミングチャートである。また、図15は、放射線撮像装置の1画素に相当する各構成素子の平面図及び断面図であり、図15(a)はその平面図であり、図15(b)は図15(a)中の破線A-B間で示した部分の断面図である。

#### 【0118】

図21において、S11～S33は光電変換素子、C11～C33は蓄積用キャパシタ、T11～T33は転送用TFTである。図中破線で囲んだ部分は、大面積の同一絶縁基板上に形成されている。また、Vsは読み出し用電源、Vgはリフレッシュ用電源であり、

50

それぞれスイッチ SWs、SWg を介して全光電変換素子 S11～S33 に接続されている。スイッチ SWs はインバータを介して、スイッチ SWg は直接にリフレッシュ制御回路 RF に接続されており、リフレッシュ期間は SWg がオン、その他の期間は SWs がオンするよう制御されている。

#### 【0119】

1画素は、1個の光電変換素子とキャパシタ、及び TFT で構成され、その信号出力は信号配線 SIG により検出用集積回路 IC に接続されている。本実施例の二次元エリアセンサは計 9 個の画素を 3 つのブロックに分け、1 ブロックあたり 3 画素の出力を同時に転送し、この信号配線を通して検出用集積回路によって順次出力に変換され出力される。また、1 ブロック内の 3 画素を横方向に配置し、3 ブロックを順に縦に配置することにより各画素を二次元的に配置している。10

#### 【0120】

更に、通常の画像を撮像するための第 1 の光電変換素子 S11～S33 とは異なる形状をした、櫛歯状の細長い形状の第 2 の光電変換素子が、光電変換素子 S11, S21 と光電変換素子 S12, S22 の間に配置されている。

#### 【0121】

ここで、図 21 における第 2 の光電変換素子は TFT 型のセンサである。

図 21 の第 2 の光電変換素子は、ドレイン電極がバイアス電源 (Bias 2) に接続されており、ソース電極は、增幅器 (AMP 2) と接続されており、放射線の入射光量に従って発生する電荷が増幅され、出力される。20

#### 【0122】

この時、ゲート電極電位がソース電極電位に対して、負に固定されている為、ゲート電極がない場合に比較して、より大きな光電流と暗電流の比が得られる。この大きな光電流と暗電流の比により、第 2 の光電変換素子の性能を向上させることが可能となる。

#### 【0123】

図 15 は、S12 及び S22 の平面図 (a) 及び断面図 (b) である。

ここで、AEC センサ用の第 2 の光電変換素子は 903 で示してあり、層構成は光電変換素子 901'、キャパシタ 904 及び TFT 902 と同様の構成である。

#### 【0124】

このように、第 2 の光電変換素子を AEC センサに用いることにより、AEC センサを低コストで構成することが可能となり、コストの低い撮像装置を提供することが可能となる。30

#### 【0125】

S11 は光電変換素子、T11 は TFT、C11 はキャパシタ、及び SIG は信号配線である。本実施例においては、キャパシタ C11 と光電変換素子 S11 とは特別に素子を分離しておらず、光電変換素子 S11 の電極の面積を大きくすることによりキャパシタ C11 を形成している。

#### 【0126】

画素上部には、パッシベーション用窒化シリコン膜 SiN8 と CsI、Gd<sub>2</sub>O<sub>2</sub>S 等の蛍光体 12 が形成されている。上方より像情報の含まれる X 線 13 が入射すると蛍光体 12 により像情報光 14 に変換され、この光が光電変換素子に入射される。40

#### 【0127】

ここで、図 15 を用いて各素子の形成方法について順に説明する。

まず、絶縁材料であるガラス基板 1 上にスパッタ等により、下部メタル層 2 として Cr を約 50 nm 程度堆積させ、その後フォトリソグラフィによりパターニングを行い、不要なエリアをエッチングする。これにより、光電変換素子 S11 の下部電極、TFT・T11 のゲート電極、及びキャパシタ C11 の下部電極が形成される。

#### 【0128】

次に、CVD により同一真空中で SiN 膜 7、i 層 4、n 層 5 をそれぞれ約 200 nm、500 nm、50 nm 堆積する。これら各層は光電変換素子 S11 においては、SiN 膜50

7が下部絶縁層、i層4が光電変換半導体層、n層5がホール注入阻止層となり、TFT・T11においては、SiN膜7がゲート絶縁膜、i層4が半導体層、n層5がオーミックコンタクト層となる。また、上述の3層はキャパシタC11の中間層となり、また、信号配線のクロス部絶縁層としても使われる。各層の厚さはこれに限らず二次元エリアセンサとして使用する電圧、電流、電荷、入射光量等により最適に設計するが、少なくともSiN膜7の厚さは電子とホールが通過できず、また、TFTのゲート絶縁膜として機能ができる厚さ50nm以上が必要である。

#### 【0129】

各層堆積後、上部メタル層6としてA1をスパッタ等で約1000nm堆積させる。更に、フォトリソグラフィによりパターニングを行い、不必要的エリアをエッチングにて除去する。これにより、光電変換素子S11の上部電極、TFT・T11の主電極であるソース電極並びにドレイン電極、キャパシタC11の上部電極、及び信号配線SIGが形成される。

10

#### 【0130】

また更に、TFT・T11のチャネル部のみn層5をRIEでエッチングし、その後不要なSiN膜7、i層4、n層5に対してエッチングを行うことで各素子が分離される。これにより、光電変換素子S11、TFT・T11及びキャパシタC11が完成する。以上、1画素について説明を行ったが他の画素についても同時に形成されることは言うまでもない。

#### 【0131】

また、耐久性を向上させるために、各素子の上部にSiN等のパッシベーション膜8を形成して覆い、更に、CsI、Gd<sub>2</sub>O<sub>3</sub>S等の波長変換体となる蛍光体12を形成する。

20

#### 【0132】

以上説明したように、本実施形態では、光電変換素子、TFT、キャパシタ及び信号配線SIGとが同時に堆積された共通の下部メタル層2、SiN膜7、i層4、n層5及び上部メタル層6と各層のエッチングのみで形成することができる。また、光電変換素子S11内に注入素子層が1カ所しかなく、かつ、同一真空中で形成できる。更に、TFTの特性上重要なゲート絶縁膜とi層との界面も同一真空中で形成できる。また更に、キャパシタC11の中間層が熱によるリークの少ない絶縁層を含んでいるために、良好な特性のキャパシタを形成できる。

30

#### 【0133】

次に、図22のタイミングチャートを用いて本実施形態の放射線撮像装置の動作について説明する。

まず、医師又は技師は診断対象である患者、つまり被写体（不図示）をX線源（不図示）と二次元エリアセンサ（不図示）の間に置き診断したい部位が観察できるように被写体にポーズさせる。同時に前もって問診等で得た患者の症状、体格、年齢や得たい情報を考慮し最適な撮影出力が得られるように条件を制御パネル（不図示）に入力する。この信号は電気信号でAEコントローラ（不図示）に電送される。同時に条件メモリ回路（不図示）にこれら条件が記憶される。

40

#### 【0134】

この状態で、医師又は技師が撮影露光開始ボタン（不図示）を押すと撮影モードが開始される。まず、システム制御回路（不図示）は二次元エリアセンサ（不図示）をリフレッシュ動作させる。ここでこのリフレッシュ動作を説明する。

まず、図21において、シフトレジスタSR1及びSR2により制御配線g1～g3、s1～s2にHiが印可される。これにより、転送用TFT・T11～T33とスイッチM1～M3がオンとなって導通し、全光電変換素子S11～S33のD電極は、GND電位になる（積分検出器AMPの入力端子はGND電位に設計されているためである）。

#### 【0135】

同時に、リフレッシュ制御回路RFからHiが出力されて、スイッチSWGがオンし、全光電変換素子S11～S33のG電極は、リフレッシュ用電源Vgにより正電位になる。

50

これにより、全光電変換素子 S 1 1 ~ S 3 3 は、リフレッシュモードとなってリフレッシュされる。

**【 0 1 3 6 】**

続いて、リフレッシュ制御回路 R F から L o が出力されて、スイッチ S W s がオンし、全光電変換素子 S 1 1 ~ S 3 3 の G 電極は、読み取り用電源 V s により負電位になる。これにより、全光電変換素子 S 1 1 ~ S 3 3 が光電変換モードになると同時に、キャパシタ C 1 1 ~ C 3 3 は初期化される。

**【 0 1 3 7 】**

続いて、この状態でシフトレジスタ S R 1 及び S R 2 から制御配線 g 1 ~ g 3, s 1 ~ s 2 に L o が印可される。これにより、転送用 T F T · T 1 1 ~ T 3 3 とスイッチ M 1 ~ M 3 がオフし、全光電変換素子 S 1 1 ~ S 3 3 の電極は D C 的にはオープンになるが、キャパシタ C 1 1 ~ C 1 3 によって電位は保持される。しかし、この時点で X 線は入射されていないため、全光電変換素子 S 1 1 ~ S 3 3 に光は入射されず光電流は流れない。これでリフレッシュ動作は終了する。

**【 0 1 3 8 】**

この第 1 の光電変換素子のリフレッシュ動作の間は、図 2 0 及び図 2 1 で示す第 2 の光電変換素子 S 1 0 0 の各電極（ソース、ドレイン、ゲート）の電位は G N D もしくは一定電位に固定される。これによって、第 1 の光電変換素子のリフレッシュ動作は、全ての画素が均一にリフレッシュされる。

**【 0 1 3 9 】**

ここで、図 2 0 及び図 2 1 で示す第 2 の光電変換素子 S 1 0 0 の各電極（ソース、ドレイン、ゲート）の電位が光電変換可能な電位に設定される。具体的には、ソース電極電位が約 3 V、ドレイン電極電位が約 1 0 V、ゲート電極電位が約 0 V である。

**【 0 1 4 0 】**

この状態で X 線が出射され、被写体を通過して蛍光体に入射すると光に変換され、その光がそれぞれの第 1 の光電変換素子 S 1 1 ~ S 3 3 及び第 2 の光電変換素子 S 1 0 0 に入射する。

**【 0 1 4 1 】**

そして、第 2 の光電変換素子 S 1 0 0 に入射した総光量がある閾値に達した時、X 線照射を止める信号が出され、X 線照射が終了する。これにより、第 2 の光電変換素子 S 1 0 0 の役割は終了するため、この時点で、図 2 0 及び図 2 1 で示す第 2 の光電変換素子 S 1 0 0 の各電極（ソース、ドレイン、ゲート）の電位は、G N D もしくは一定電位に固定される。これによって、この後、第 1 の光電変換素子 S 1 0 1 が読み取った信号を画像情報として出力する動作における影響をなくすことが可能となる。

**【 0 1 4 2 】**

実際の動作を図 2 2 のタイミングチャートに基いて説明する。

第 1 の光電変換素子 S 1 0 1 に対して、ある一定量この光により流れた光電流は、電荷としてそれぞれのキャパシタ C 1 1 ~ C 3 3 に蓄積され、X 線の入射終了後も保持される。

**【 0 1 4 3 】**

次に、二次元エリアセンサは、読み出し動作を行う。シフトレジスタ S R 1 により制御配線 g 1 に H i の制御パルスが印可され、シフトレジスタ S R 2 の制御配線 s 1 ~ s 3 への制御パルス印可によって、転送用 T F T · T 1 1 ~ T 1 3 、スイッチ M 1 ~ M 3 を通して v 1 ~ v 3 が順次出力される。同様にシフトレジスタ S R 1 、 S R 2 の制御により他の光信号も出力される。これにより、人体等の内部構造の二次元情報が v 1 ~ v 9 として得られる。ここで、制御配線 s 2 によりスイッチ M 2 を通して出力された V 2 , V 5 , V 8 は、第 1 の光電変換素子 S 1 2 , S 2 2 , S 3 2 の面積が小さいため、出力は小さくなるが、その分を最終的には信号補正される。

**【 0 1 4 4 】**

また、第 1 の光電変換素子の駆動は、図 1 1 の従来例と同じ駆動が可能となるため、高速駆動を必要とせず、結果的に撮像画像の画質低下を引き起こすことがない、高性能な撮像

10

20

30

40

50

装置を提供することが可能となる。

【0145】

また、市販されている別のAEC制御用センサを使用することなく、AEC制御用センサを小さくすることが可能となり、小型の撮像装置を提供することが可能となる。また、第1の光電変換素子と第2の光電変換素子は同じ薄膜を用いて同層として形成することが可能となり、更に、コストの低い撮像装置を提供することができる。

【0146】

(第16の実施形態)

本実施形態においては、画像読取用に用いる信号を検出する第1の光電変換素子とは別に設けられた第2の光電変換素子を、放射線発生部からの放射線の入射及び停止のうち、少なくともいずれか一方を検出するためのセンサ(以下、X線モニターとする)として利用する。その場合には、読み出し用回路において微分回路を第2の光電変換素子に接続して、検出した信号を微分して前述した放射線の入射及び停止のうち、少なくともいずれか一方の検出を行う。ここで、この微分回路は、通常知られているものを用いればよい。もしくは、図18の回路を用いることもできる。また、第2の光電変換素子の構成はTFT型であってもよいしMIS型であってもよい。ここでいうMIS型とは、絶縁層においてキャリアを溜める容量タイプであり、例えば、USP6075256に開示されているセンサである。

10

【0147】

また、第15の実施形態まで述べられてきた放射線の総照射量を検出するための光電変換素子と、X線モニタの光電変換素子を両方とも基板上に設けることもできるし、別個に設けず両方の機能を併せ持つものとして利用することもできる。その際の読み出し回路の構成としては、図18の電流読み出し型を用いることができる。

20

【0148】

(本発明の他の実施形態)

本発明は複数の機器から構成されるシステムに適用しても1つの機器からなる装置に適用しても良い。

【0149】

また、前述した実施形態の機能を実現するように各種のデバイスを動作させ、前記各種デバイスと接続された装置あるいはシステム内のコンピュータに対し、記憶媒体から、又はインターネット等の伝送媒体を介して前記実施形態の機能を実現するためのソフトウェアのプログラムコードを供給し、そのシステムあるいは装置のコンピュータ(CPUあるいはMPU)に格納されたプログラムに従って前記各種デバイスを動作させることによって実施したものも、本発明の範疇に含まれる。

30

【0150】

また、この場合、前記ソフトウェアのプログラムコード自体が前述した実施形態の機能を実現することになり、そのプログラムコード自体、及びそのプログラムコードをコンピュータに供給するための手段、例えばかかるプログラムコードを格納した記憶媒体は本発明を構成する。かかるプログラムコードを記憶する記憶媒体としては、例えばフレキシブルディスク、ハードディスク、光ディスク、光磁気ディスク、CD-ROM、磁気テープ、不揮発性のメモリカード、ROM等を用いることができる。

40

【0151】

また、コンピュータが供給されたプログラムコードを実行することにより、前述の実施形態で説明した機能が実現されるだけでなく、そのプログラムコードがコンピュータにおいて稼働しているOS(オペレーティングシステム)あるいは他のアプリケーションソフト等の共同して前述の実施形態で示した機能が実現される場合にもかかるプログラムコードは本発明の実施形態に含まれる。

【0152】

更に、供給されたプログラムコードがコンピュータの機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに格納された後、そのプログラムコードの指示

50

に基づいてその機能拡張ボードや機能拡張ユニットに備わるC P U等が実際の処理の一部又は全部を行い、その処理によって前述した実施形態の機能が実現される場合にも本発明に含まれる。

### 【0153】

#### 【発明の効果】

本発明によれば、同一基板上に画像情報を出力する変換部内に配設された第1の変換素子を有する画素とは独立して、変換部に入射する放射線の総照射量を検出するための第2の変換素子を配設するようにしたので、入力される放射線量を調整するために第1の変換素子からの出力を高速で読み出すことが不要になるとともに、放射線量を調整するためのセンサを別途設ける必要がなくなるため、放射線撮像装置の構成を簡易にすることができる

10

### 【0154】

更に、第2の変換素子をT F T型に形成し、第1の変換素子の変換部に入射した放射線量に応じて第1の変換素子が画像情報を出力するタイミングでは、第2の変換素子の放射線検出をオフ状態にする、具体的には、第2の光電変換素子の各電極（ソース、ドレイン、ゲート）の電位をG N Dもしくは一定電位に固定することにより、この後の第1の光電変換素子が読み取った信号を画像情報として出力する動作における影響をなくすことが可能となる。

### 【0155】

更に、第2の変換素子の出力を処理回路部（オペアンプ）を用いて電流として読み取ることにより、第2の変換素子の出力によりX線の曝射をストップして、画像化に適切なX線量を得るだけでなく、曝射されているX線がストップしたタイミングを得ることも可能になる。

20

#### 【図面の簡単な説明】

【図1】第1の実施形態における放射線撮像装置の回路図である。

【図2】第2の実施形態における放射線撮像装置の回路図である。

【図3】第2の実施形態における放射線撮像装置の1画素に相当する各構成素子の平面図及び断面図である。

【図4】第3の実施形態における放射線撮像装置の回路図である。

【図5】第3の実施形態における放射線撮像装置の1画素に相当する各構成素子の平面図及び断面図である。

30

【図6】第4の実施形態における放射線撮像装置のシステム構成図である。

【図7】第5の実施形態における放射線撮像装置の回路図である。

【図8】第6の実施形態における放射線撮像装置の回路図である。

【図9】第7の実施形態における放射線撮像装置の回路図である。

【図10】第8の実施形態における放射線撮像装置の回路図である。

【図11】従来例を示し、二次元エリアセンサの構成を示す回路図である。

【図12】従来例を示し、図11の二次元エリアセンサの1画素に相当する各構成素子の平面図及び断面図である。

【図13】本実施形態における第2の光電変換素子の配置イメージ図である。

40

【図14】第9の実施形態における放射線撮像装置の回路図である。

【図15】第9の実施形態における放射線撮像装置の1画素に相当する各構成素子の平面図及び断面図である。

【図16】第10の実施形態における放射線撮像装置の回路図である。

【図17】第11の実施形態における放射線撮像装置の回路図である。

【図18】第12の実施形態における放射線撮像装置の回路図である。

【図19】第13の実施形態における放射線撮像装置の回路図である。

【図20】第14の実施形態における放射線撮像装置の回路図である。

【図21】第15の実施形態における放射線撮像装置の回路図である。

【図22】第15の実施形態における放射線撮像装置のタイミングチャートである。

50

## 【符号の説明】

- 101、101' 第1の光電変換素子

102 トランジスタ

103 画素

104 第1のバイアス手段

105 シフトレジスタ

106 増幅器・マルチプレクサ・A/D変換器

107 リセット手段

108 第2の光電変換素子

109 第2のバイアス手段

110 第2の増幅器

111 光電変換基板

G1～G4 ゲート線

S1～S4 信号線

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【 図 1 0 】

【 図 1 1 】

【 図 1 3 】

【 义 1 2 】

〔 図 1-4 〕

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

---

フロントページの続き

(51)Int.Cl. F I

H 0 5 G 1/44 (2006.01) H 0 4 N 5/335 U

H 0 5 G 1/44 A

(72)発明者 森下 正和

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 松谷 洋平

(56)参考文献 米国特許第06198800(US, B1)

特開平05-130990(JP, A)

特表平11-513122(JP, A)

特開平11-188021(JP, A)

特表2003-529425(JP, A)

(58)調査した分野(Int.Cl., DB名)

A61B6/00-6/14

H04N5/30-5/335

G01T1/00-7/12

H05G1/00-2/00