(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7561663号**

**(P7561663)**

(45)発行日 令和6年10月4日(2024.10.4)

(24)登録日 令和6年9月26日(2024.9.26)

## (51)国際特許分類

|        |                  |     |        |        |   |

|--------|------------------|-----|--------|--------|---|

| H 02 M | 1/08 (2006.01)   | F I | H 02 M | 1/08   | A |

| H 03 K | 17/04 (2006.01)  |     | H 03 K | 17/04  | E |

| H 03 K | 17/042 (2006.01) |     | H 03 K | 17/042 |   |

| H 03 K | 17/16 (2006.01)  |     | H 03 K | 17/16  | L |

| H 03 K | 17/687 (2006.01) |     | H 03 K | 17/687 | F |

請求項の数 5 (全12頁)

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2021-41380(P2021-41380)   |

| (22)出願日  | 令和3年3月15日(2021.3.15)        |

| (65)公開番号 | 特開2022-141181(P2022-141181) |

|          | A)                          |

| (43)公開日  | 令和4年9月29日(2022.9.29)        |

| 審査請求日    | 令和5年12月11日(2023.12.11)      |

|          |                    |

|----------|--------------------|

| (73)特許権者 | 000004260          |

|          | 株式会社デンソー           |

|          | 愛知県刈谷市昭和町1丁目1番地    |

| (73)特許権者 | 000003207          |

|          | トヨタ自動車株式会社         |

|          | 愛知県豊田市トヨタ町1番地      |

| (73)特許権者 | 520124752          |

|          | 株式会社ミライズテクノロジーズ    |

|          | 愛知県日進市米野木町南山500番地1 |

| (74)代理人  | 110000567          |

|          | 弁理士法人サトー           |

| (72)発明者  | 杉浦 秀和              |

|          | 愛知県日進市米野木町南山500-1  |

|          | 株式会社ミライズテクノロジーズ内   |

| 審査官      | 今井 貞雄              |

最終頁に続く

(54)【発明の名称】 ゲート駆動装置

## (57)【特許請求の範囲】

## 【請求項1】

上アームおよび下アームにそれぞれ配置され整流素子を備えたゲート駆動型の半導体スイッチング素子のゲート駆動を行うゲート駆動装置であって、

前記上下アームのそれぞれの半導体スイッチング素子を交互に駆動するための駆動信号を送信する制御回路(20)と、

前記制御回路からの駆動信号に応じて前記上下アームのそれぞれの半導体スイッチング素子のゲートを駆動する駆動回路(40a、40b)と、

前記上下アームのそれぞれの半導体スイッチング素子についてゲート電圧が参照電圧と一致するタイミングを検出するゲート変動検出回路(60)と、

前記半導体スイッチング素子の電流値に応じて前記ゲート変動検出回路の前記参照電圧を調整する参照電圧調整回路(50a、50b)とを備え、

前記制御回路は、前記ゲート変動検出回路により検出される前記上下アームの前記半導体スイッチング素子のゲート電圧変動のタイミングからデッドタイムを算出し、次に駆動する側の駆動タイミングを調整するタイミング調整機能を備えるゲート駆動装置。

## 【請求項2】

前記参照電圧調整回路は、前記参照電圧を、対応する前記半導体スイッチング素子の電流値の平方根に比例して変動させて設定する請求項1に記載のゲート駆動装置。

## 【請求項3】

前記参照電圧は、前記半導体スイッチング素子のしきい値電圧に相当する定数項と、前

記半導体スイッチング素子の電流値の平方根に比例して変動させて設定する変動項とを加算した電圧値に設定される請求項 2 に記載のゲート駆動装置。

**【請求項 4】**

前記参照電圧は、前記半導体スイッチング素子が同期整流時に対応し電流値が負である場合には前記変動項をゼロとして設定する請求項 3 に記載のゲート駆動装置。

**【請求項 5】**

前記参照電圧は、前記半導体スイッチング素子のしきい値電圧に相当する定数項についても、前記半導体スイッチング素子の素子温度に応じて変更設定される請求項 3 または 4 に記載のゲート駆動装置。

**【発明の詳細な説明】**

10

**【技術分野】**

**【0001】**

本発明は、ゲート駆動装置に関する。

**【背景技術】**

**【0002】**

ゲート駆動型の半導体スイッチング素子として、例えばMOSトランジスタを上下アームに配置して構成し、それぞれのMOSトランジスタを交互に駆動することで負荷に給電するインバータや、直流電源の電圧変換をするコンバータなどがある。これらの構成では、上下アームのMOSトランジスタが同時にオンする状態を防止するために、2つのMOSトランジスタが共にオフ状態となるデッドタイムを設けている。

20

**【0003】**

しかしながら、デッドタイムを長くすることは、その期間中にボディダイオードに電流が流れ発生する損失が増加することとなるので、できるだけ短く設定することが求められる。デッドタイムを短縮するためには、正確にデッドタイムを検出することが必要となる。

**【0004】**

デッドタイム検出の方法として、上下アームのMOSトランジスタのゲート・ソース間電圧  $V_{gs}$  の変動を見てデッドタイムを検出する場合、従来ではしきい値電圧  $V_{th}$  をリファレンス値としてオンオフのタイミングを検出し、上下アームのMOSトランジスタの  $V_{gs}$  変動タイミング差をデッドタイムとして検出していた。

30

**【0005】**

しかしながら、実際には制御対象としているMOSトランジスタのオンオフの切り替わりタイミングが、ゲート・ソース間電圧  $V_{gs}$  がしきい値電圧  $V_{th}$  と一致するタイミングとずれており、正確なデッドタイムを検出できなかった。このため、検出タイミングがずれる分、検出誤差として予めマージンを持ったデッドタイムの設定をすることとなり、検出誤差分のデッドタイムが短縮できないという課題があった。

**【先行技術文献】**

**【特許文献】**

**【0006】**

**【文献】特開2020-127145号公報**

40

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0007】**

本発明は、上記事情を考慮してなされたもので、その目的は、ゲート駆動型の半導体スイッチング素子のオンオフのタイミングを正確に検出することでデッドタイムの設定のマージンを短くすることができるようにしたゲート駆動装置を提供することにある。

**【課題を解決するための手段】**

**【0008】**

請求項 1 に記載のゲート駆動装置は、上アームおよび下アームにそれぞれ配置され整流素子を備えたゲート駆動型の半導体スイッチング素子のゲート駆動を行うゲート駆動装置

50

であって、前記上下アームのそれぞれの半導体スイッチング素子を交互に駆動するための駆動信号を送信する制御回路(20)と、前記制御回路からの駆動信号に応じて前記上下アームのそれぞれの半導体スイッチング素子のゲートを駆動する駆動回路(40a、40b)と、前記上下アームのそれぞれの半導体スイッチング素子についてゲート電圧が参照電圧と一致するタイミングを検出するゲート変動検出回路(60)と、前記半導体スイッチング素子の電流値に応じて前記ゲート変動検出回路の前記参照電圧を調整する参照電圧調整回路(50a、50b)とを備え、前記制御回路は、前記ゲート変動検出回路により検出される前記上下アームの前記半導体スイッチング素子のゲート電圧変動のタイミングからデッドタイムを算出し、次に駆動する側の駆動タイミングを調整するタイミング調整機能を備える。

10

#### 【0009】

上記構成を採用することにより、参照電圧調整回路が、半導体スイッチング素子の電流値に応じて参照電圧を調整してゲート変動検出回路に設定するので、ゲート変動検出回路において、半導体スイッチング素子のゲート電圧が参照電圧と一致するタイミングを検出することで実際のオンあるいはオフのタイミングを検出することができる。

#### 【0010】

これにより、制御回路においては、ゲート変動検出回路により検出される上下アームの半導体スイッチング素子のゲート電圧変動のタイミングから実際のデッドタイムに相当する時間を正確に検出することができるので、電流値に依存した変動を含めたマージンを設定する必要がなくなり、半導体スイッチング素子に並列に接続された整流素子に電流が流れる時間を極力低減することができる。

20

#### 【図面の簡単な説明】

#### 【0011】

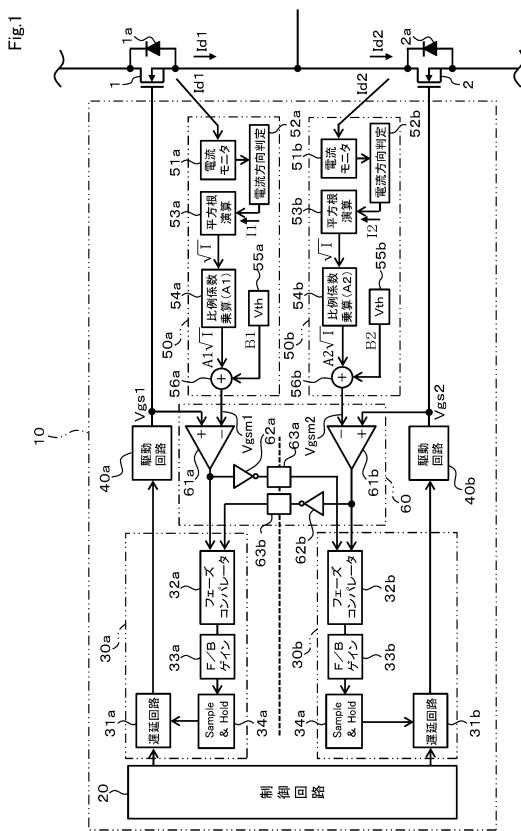

【図1】第1実施形態を示す電気的構成図

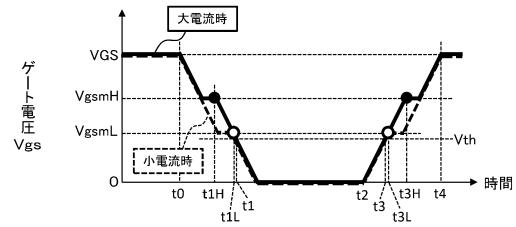

【図2】第1実施形態を示すゲート電圧の検出タイミングの作用説明図

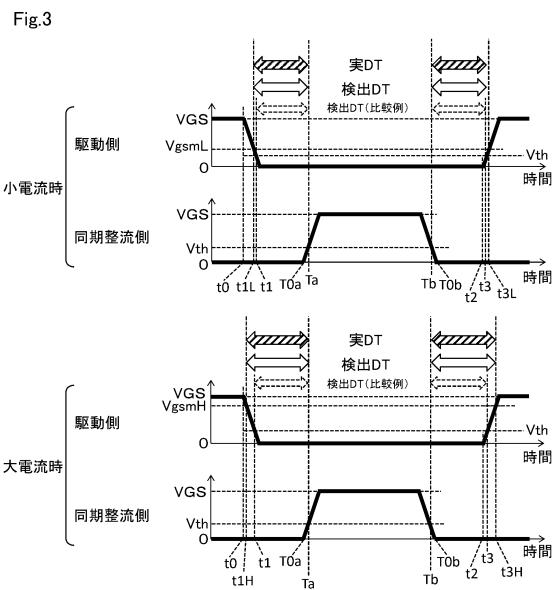

【図3】第1実施形態を示すタイミングチャート

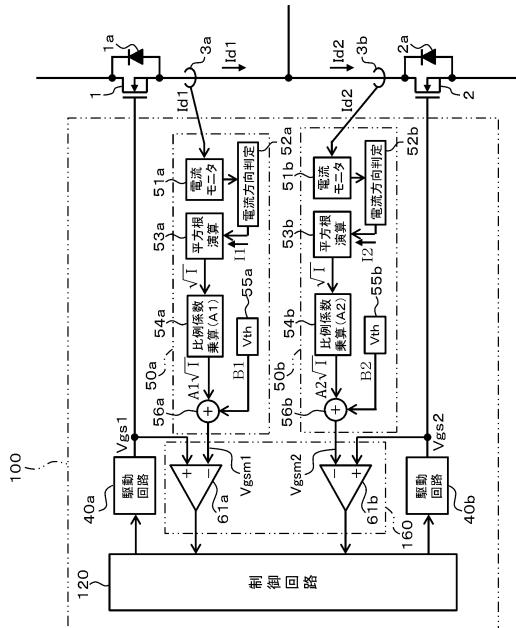

【図4】第2実施形態を示す電気的構成図

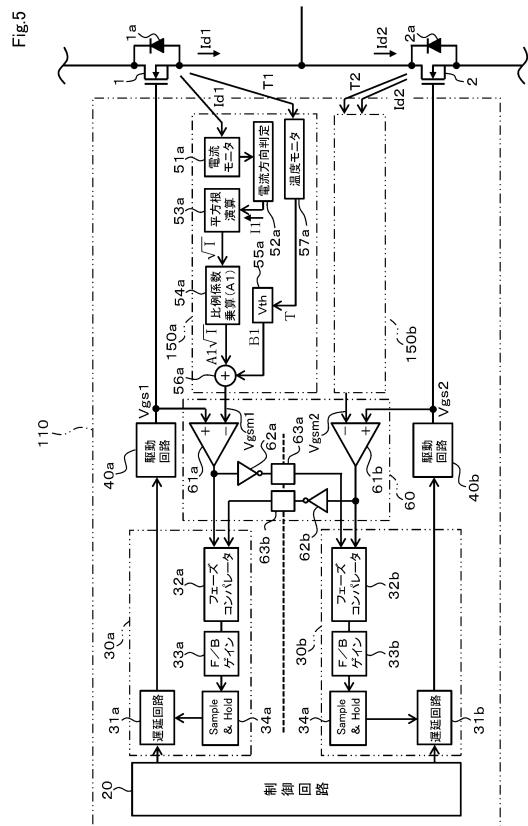

【図5】第3実施形態を示す電気的構成図

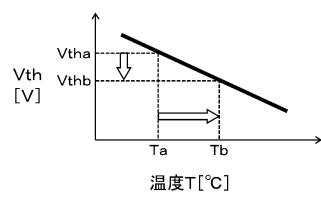

【図6】第3実施形態を示す作用説明図

#### 【発明を実施するための形態】

30

#### 【0012】

##### (第1実施形態)

以下、本発明の第1実施形態について、図1～図3を参照して説明する。

電気的構成を示す図1において、上下アームを構成する2つの半導体スイッチング素子であるNチャンネル型のMOSトランジスタ1、2は、直列接続された状態として電源端子間に接続されている。MOSトランジスタ1および2の共通接続点は負荷への出力端子となっている。また、MOSトランジスタ1はボディダイオード1aを有し、MOSトランジスタ2はボディダイオード2aを有する。

#### 【0013】

2個のMOSトランジスタ1、2は、ゲート駆動装置10によりオンオフの駆動制御が行われる。また、2個のMOSトランジスタ1、2には、それぞれ負荷電流であるドレン電流Id1、Id2をモニタする電流センス機能が備えられている。この場合、電流センス素子を別途設ける構成としても良いし、通電経路に別途電流検出部を設けて検出する構成とすることもできる。

40

#### 【0014】

ゲート駆動装置10は、制御回路20、デッドタイム設定回路30a、30b、駆動回路40a、40b、参照電圧調整回路50a、50b、ゲート変動検出回路60を備える。なお、ゲート駆動装置10の構成中、添字a、bを付したデッドタイム設定回路30a、30b、駆動回路40a、40b、参照電圧調整回路50a、50bは、それぞれMOSトランジスタ1、2に対応して個別に設けられたもので、それぞれが同等の内部構成を

50

有している。以下の構成説明では、MOSトランジスタ1に対応する添字aを付した回路について説明し、添字bを付した回路についての説明を省略する。

#### 【0015】

制御回路20は、外部から与えられるオンオフの指示信号に応じて上下アームのMOSトランジスタ1、2に対して駆動信号を作成してオンオフの駆動制御を行う。この場合、制御回路20は、MOSトランジスタ1に対してデッドタイム設定回路30aを介して駆動回路40aに駆動信号を与える、MOSトランジスタ2に対してデッドタイム設定回路30bを介して駆動回路40bに駆動信号を与える。

#### 【0016】

デッドタイム設定回路30aは、検出されたデッドタイムの信号に基づいて指示信号に対して回路構成上で発生する誤差を考慮した所定のマージンを加えてデッドタイムを設定する。デッドタイム設定回路30aは、遅延回路31a、フェーズコンパレータ32a、F/Bゲイン回路33aおよびサンプルアンドホールド回路34aを備えている。

10

#### 【0017】

参照電圧調整回路50aは、MOSトランジスタ1のオンオフのタイミングを判定するための参照電圧V<sub>gsm1</sub>を設定してゲート変動検出回路60を構成するコンパレータ61aの反転入力端子に出力する。参照電圧V<sub>gsm1</sub>は、MOSトランジスタ1がオンまたはオフ動作中に、ゲート電圧V<sub>gs</sub>がミラー期間に入ったときのミラー電圧を示しており、この電圧を超えて変化したときがオンオフのタイミングとなる。

#### 【0018】

このため、参照電圧調整回路50aは、次式(1)に基づいてドレン電流I<sub>d1</sub>およびしきい値電圧V<sub>th</sub>から参照電圧V<sub>gsm1</sub>を算出するように回路が構成されている。

20

#### 【0019】

#### 【数1】

$$V_{gsm} = \sqrt{\frac{2L}{\mu_n C_{ox} W}} \sqrt{I_d} + V_{th} = A \sqrt{I_d} + B \quad \cdots (1)$$

30

#### 【0020】

なお、式(1)中、ドレン電流I<sub>d</sub>はミラー期間中の飽和電流を示しており、そのドレン電流I<sub>d</sub>の平方根の前にかかる係数は、MOSトランジスタ1、2のそれぞれのゲート長をL、ゲート幅をW、電子移動度をμ<sub>n</sub>、単位面積あたりのゲート酸化膜容量をC<sub>ox</sub>としており、これらは素子によって決まる一定の数値である。また、しきい値電圧V<sub>th</sub>についても素子によって決まる一定の数値である。

#### 【0021】

この結果、しきい値電圧V<sub>th</sub>にドレン電流I<sub>d</sub>の平方根の値に比例した値を加算した値がミラー電圧V<sub>gsm</sub>となり、これがMOSトランジスタ1、2のオンオフのタイミングを決める参照電圧となる。したがって、負荷電流としてのドレン電流I<sub>d</sub>が流れているレベルに応じて参照電圧V<sub>gsm</sub>が変化する。

40

#### 【0022】

参照電圧調整回路50aは、電流モニタ部51a、電流方向判定部52a、平方根演算部53a、比例係数乗算部54a、しきい値設定部55a、加算部56aを有する。電流モニタ部51aは、MOSトランジスタ1のドレン電流I<sub>d1</sub>の検出信号を取り込み、電流方向判定部52aによりドレン電流I<sub>d1</sub>が正の場合すなわちドレン側からソース側に電流が流れている場合には、ドレン電流I<sub>d1</sub>をそのまま出力し、ドレン電流が負の場合にはゼロとして平方根演算部53aに出力する。

#### 【0023】

50

続いて、平方根演算部 53a でドレイン電流  $I_d$  1 の値の平方根の値を演算し、比例係数演算部 54a にて比例係数  $A_1$  を乗じる。加算部 56a では、比例係数演算部 54a からの出力と、しきい値設定部 55a からのしきい値  $V_{th}$  とを加算して得た参照電圧  $V_{gsm}$  1 をゲート変動検出回路 60 に出力する。

#### 【0024】

ゲート変動検出回路 60 は、MOSトランジスタ 1、2 のそれぞれに対応するコンパレータ 61a、61b を備えるとともに、それぞれの判定結果を対抗アームに反転して伝えるインバータ 62a、62b および絶縁通信部 63a、63b を備える。

#### 【0025】

コンパレータ 61a は、MOSトランジスタ 1 のゲート電圧  $V_{gss}$  1 と参照電圧調整回路 50a により設定された参照電圧  $V_{gsm}$  1 とを比較し、ゲート電圧  $V_{gss}$  1 が参照電圧  $V_{gsm}$  1 を超えるとハイレベルの検出信号を出力する。この検出信号は、デッドタイム設定回路 30a のフェーズコンパレータ 32a に出力されるとともに、インバータ 62a および絶縁通信部 63a を通じて反転した信号がデッドタイム設定回路 30b のフェーズコンパレータ 32b に出力される。

10

#### 【0026】

コンパレータ 61b についても、同様にして、MOSトランジスタ 2 のゲート電圧  $V_{gss}$  2 と参照電圧調整回路 50b により設定された参照電圧  $V_{gsm}$  2 とを比較し、ゲート電圧  $V_{gss}$  2 が参照電圧  $V_{gsm}$  2 を超えるとハイレベルの検出信号を出力する。この検出信号は、デッドタイム設定回路 30b のフェーズコンパレータ 32b に出力されるとともに、インバータ 62b および絶縁通信部 63b を通じて反転した信号がデッドタイム設定回路 30a のフェーズコンパレータ 32a に出力される。

20

#### 【0027】

次に、上記構成の作用について図 2 および図 3 も参照して説明する。なお、ゲート駆動装置 10 の基本的な動作としては、制御回路 20 から MOSトランジスタ 1、2 を交互にオンオフ駆動する信号がそれぞれデッドタイム設定回路 30a、30b に出力されると、遅延回路 31a、31b に設定されているデッドタイム DT に従ったタイミングで駆動信号が生成され、駆動回路 40a、40b に出力される。駆動回路 40a、40b は、MOSトランジスタ 1、2 のゲートにゲート駆動信号を与えてオンオフの駆動を行う。

30

#### 【0028】

MOSトランジスタ 1、2 に流れる負荷電流であるドレイン電流  $I_d$  1、 $I_d$  2 はそれぞれ計測されており、参照電圧調整回路 50a、50b に入力されている。参照電圧調整回路 50a、50b においては、前述の式(1)に相当する演算処理を実行して参照電圧  $V_{gsm}$  1、 $V_{gsm}$  2 を算出し、それぞれコンパレータ 61a、61b に設定する。

#### 【0029】

この場合、電流方向判定部 52a、52b においては、ドレイン電流  $I_d$  1、 $I_d$  2 が正の場合には、その大きさに対応する信号を生成し、負の場合には、電流値はゼロとして生成する。これにより、参照電圧  $V_{gsm}$  1、 $V_{gsm}$  2 は、通常の駆動時にはドレイン電流  $I_d$  に基づいた値が設定され、同期整流時にはしきい値  $V_{th}$  1、 $V_{th}$  2 がそれぞれ設定される。

40

#### 【0030】

前述のように、MOSトランジスタ 1、2 のオンオフ切り替わり時のゲート電圧  $V_{gss}$  1、 $V_{gss}$  2 の大きさは素子がオンオフ動作する過渡期に中間的な電圧が保持されるミラー電圧により決まっている。このため、ミラー電圧は、前述した式(1)に示すように、ドレイン電流  $I_d$  としきい値電圧  $V_{th}$  とにより表されている。

#### 【0031】

したがって、あらかじめ MOSトランジスタ 1、2 の特性に対応した定数を求めておくことで、参照電圧調整回路 50a、50b の比例係数乗算部 54a およびしきい値設定部 55a のそれぞれに設定しておけば、ドレイン電流  $I_d$  に対応したミラー電圧を得ることができる。そして、コンパレータ 61a、61b において、ドレイン電流  $I_d$  に対応して

50

設定したミラー電圧と比較することでオンオフのタイミングを正確に判定することができる。

#### 【0032】

また、ドレイン電流  $I_d$  が負の場合、すなわち同期整流側となっている場合には、オンオフの切り替わりタイミングとなるゲート電圧  $V_{gs}$  は、ドレイン電流  $I_d$  に依存せず、しきい値電圧  $V_{th}$  となる。そこで、この場合に対応できるように、参照電圧調整回路 50a、50bにおいて、ドレイン電流  $I_d$  が負となる場合には、電流方向判定部 52a、52b が、ドレイン電流  $I_d$  をゼロとして設定する。これにより、参照電圧はしきい値電圧  $V_{th}$  と等しくなる。

#### 【0033】

図2はゲート変動検出回路60のコンパレータ61a、61bにてMOSトランジスタ1、2のオンオフタイミングを検出する場合について、負荷電流すなわちドレイン電流  $I_d$  が大きいレベルと小さいレベルとでゲート電圧  $V_{gs}$  のミラー電圧が異なり、これによって判定タイミングが異なることを示している。

#### 【0034】

例えばドレイン電流  $I_d$  が大きいレベル  $I_dH$  のときに、実線で示すミラー電圧  $V_{gs}$   $mH$  となり、小さいレベル  $I_dL$  のときに破線で示すミラー電圧  $V_{gsmL}$  となるものとする。コンパレータ61a、61bは、それぞれ、参照電圧  $V_{gsm1}$ 、 $V_{gsm2}$  としてドレイン電流  $I_d$  が大きい場合、小さい場合に応じて、電流値に応じた  $V_{gsmH}$ 、 $V_{gsmL}$  が設定されている。なお、これらの参照電圧  $V_{gsm}$  は、式(1)に基づいて参照電圧調整回路50a、50bにより演算して設定されるものである。

#### 【0035】

MOSトランジスタ1、2がオン状態でゲート電圧  $V_{gs}$  が所定電圧  $V_{GS}$  のレベルから時刻  $t_0$  で下降し始めるとすると、途中のミラー電圧  $V_{gsmH}$ 、 $V_{gsmL}$  で一定レベルとなり、この後、再び下降し始める時刻  $t_{1H}$ 、 $t_{1L}$  で、コンパレータ61a、61bは参照電圧よりも低下したとして出力信号をハイレベルからローレベルに変化させる。MOSトランジスタ1、2は、それぞれ時刻  $t_{1H}$ 、 $t_{1L}$  でオフ状態に変化している。

#### 【0036】

したがって、従来相当の参照電圧  $V_{th}$  で判定したタイミングが時刻  $t_1$  あるとすると、小電流時には時刻  $t_1$  に比べて若干早いタイミング  $t_{1L}$  (図中白丸で示す) で出力信号が変化し、大電流時には時刻  $t_{1L}$  よりもさらに早いタイミング  $t_{1H}$  (図中黒丸で示す) で出力が変化する。

#### 【0037】

一方、MOSトランジスタ1、2がオフ状態でゲート電圧  $V_{gs}$  がゼロのレベルから時刻  $t_2$  で上昇し始めるとすると、途中のミラー電圧  $V_{gsmL}$ 、 $V_{gsmH}$  で一定レベルとなり、この後、再び上昇し始める時刻  $t_{3H}$ 、 $t_{3L}$  で、コンパレータ61a、61bは参照電圧に達したとして出力信号をローレベルからハイレベルに変化させる。MOSトランジスタ1、2は、それぞれ時刻  $t_{3L}$ 、 $t_{3H}$  でオン状態に変化している。

#### 【0038】

したがって、従来相当の参照電圧  $V_{th}$  で判定したタイミングが時刻  $t_3$  あるとすると、小電流時には時刻  $t_3$  に比べて若干遅いタイミング  $t_{3L}$  (図中白丸で示す) で出力信号が変化し、大電流時には時刻  $t_{3L}$  よりもさらに遅いタイミング  $t_{3H}$  (図中黒丸で示す) で出力が変化する。

#### 【0039】

この結果、ドレイン電流  $I_d$  の大小に応じてオンオフのタイミングがずれるとともに、ドレイン電流  $I_d$  が大きいほど、しきい値電圧  $V_{th}$  での検出タイミングからの時間差が長くなっていることがわかる。

#### 【0040】

図3は、上記したゲート変動検出回路60のコンパレータ61a、61bにてMOSトランジスタ1、2のオンオフタイミングを検出する動作に基づいて、上下アームのMOS

10

20

30

40

50

トランジスタ 1、2 が、一方が駆動側（上段に表示）、他方が同期整流側（下段に表示）となる場合のオンオフの動作について、ドレイン電流  $I_d$  が大電流時と小電流時とで示している。

#### 【0041】

前述したように、小電流時は、参照電圧  $V_{gsm}$  が低いレベルである  $V_{gsmL}$  となり、しきい値電圧  $V_{th}$  よりも少し大きい値となっている。また、大電流時には高いレベルである  $V_{gsmH}$  となっている。

#### 【0042】

まず、ドレイン電流  $I_d$  が小電流時には、MOSトランジスタ 1、2 のうちの駆動側のものが時刻  $t_0$  でオフ駆動されると、ゲート電圧  $V_{gs}$  が印加されていた  $V_{GS}$  から下降していく。時刻  $t_{1L}$  で参照電圧  $V_{gsmL}$  に達し、オフ状態に移行する。そして、この後時刻  $t_1$  でしきい値電圧  $V_{th}$  に達する。

10

#### 【0043】

ここで、デッドタイム  $DT$  の開始時点は、オフ状態に移行した時刻  $t_{1L}$  であり、実デッドタイムと検出デッドタイム  $DT$  の開始時刻はほぼ同じである。一方、しきい値電圧  $V_{th}$  で判定する従来方式の比較例では、少し遅れてオフタイミングが検出される。

#### 【0044】

この後、デッドタイム  $DT$  が経過して MOSトランジスタ 1、2 のうちの同期整流側のものが時刻  $T_{0a}$  でオン駆動されると、ゲート電圧  $V_{gs}$  が上昇し、時刻  $T_a$  でしきい値電圧  $V_{th}$  に達してオン状態となり、この時刻  $T_a$  が検出される。

20

#### 【0045】

これにより、このときの実デッドタイムは時刻  $t_{1L}$  から時刻  $T_a$  までとなり、検出デッドタイム  $DT$  とほぼ同じである。これに対して、比較例では、駆動側のオフ時刻が  $t_{1L}$  よりも遅れた時刻  $t_1$  で検出されることで、少し短い検出デッドタイムとなるため、実デッドタイムとの差が発生している。

#### 【0046】

次に、ドレイン電流  $I_d$  が大電流時には、MOSトランジスタ 1、2 のうちの駆動側のものが時刻  $t_0$  でオフ駆動されると、ゲート電圧  $V_{gs}$  が印加されていた  $V_{GS}$  から下降し始めて、時刻  $t_{1H}$  で参照電圧  $V_{gsmH}$  に達し、オフ状態に移行する。そして、この後時刻  $t_1$  でしきい値電圧  $V_{th}$  に達する。

30

#### 【0047】

ここでのデッドタイム  $DT$  の開始時点は、オフ状態に移行した時刻  $t_{1H}$  であり、実デッドタイムと検出デッドタイム  $DT$  の開始時刻はほぼ同じである。一方、しきい値電圧  $V_{th}$  で判定する従来方式の比較例では、遅れてオフタイミングが検出される。

#### 【0048】

この後、デッドタイム  $DT$  が経過して MOSトランジスタ 1、2 のうちの同期整流側のものが時刻  $T_{0a}$  でオン駆動されると、ゲート電圧  $V_{gs}$  が上昇し、時刻  $T_a$  でしきい値電圧  $V_{th}$  に達してオン状態となり、この時刻  $T_a$  が検出される。

#### 【0049】

これにより、このときの実デッドタイムは時刻  $t_{1H}$  から時刻  $T_a$  までとなり、この場合においても検出デッドタイム  $DT$  とほぼ同じである。これに対して、比較例では、駆動側のオフ時刻が  $t_{1H}$  よりも遅れた時刻  $t_1$  で検出されることで、少し短い検出デッドタイムとなるため、実デッドタイムとの差が大きく発生している。

40

#### 【0050】

上記の検出誤差は、ドレイン電流  $I_d$  が大きくなるほど大きくなる。このため、従来においては、このような検出誤差を考慮したマージンを加算してデッドタイムを設定していた。このため、ドレイン電流  $I_d$  が小さい場合でも必要以上にデッドタイムが大きく設定されることとなっていた。

#### 【0051】

このような本実施形態においては、参照電圧調整回路 50a、50b により、MOSト

50

ランジスタ1、2のオンオフのタイミングを負荷電流であるドレイン電流 $I_{d1}$ 、 $I_{d2}$ の大きさに応じて参照電圧 $V_{gsm1}$ 、 $V_{gsm2}$ として設定するようにした。これにより、ドレイン電流 $I_{d1}$ 、 $I_{d2}$ が変動しても、実際にMOSトランジスタ1、2がオンオフするタイミングと、ゲート電圧 $V_{gs}$ の変動を検出するタイミングが一致させることができ、検出デッドタイムと実デッドタイムの長さを一致させることができる。

#### 【0052】

この結果、ドレイン電流 $I_{d1}$ 、 $I_{d2}$ の大きさに起因して変動する検出デッドタイムDTの変動分含めた状態で検出することができるようになり、このような変動分を考慮してデッドタイムにマージンを設定する必要が無くなり、その分、設定するデッドタイムの短縮を図ることができる。

10

#### 【0053】

##### (第2実施形態)

図4は第2実施形態を示すもので、以下、第1実施形態と異なる部分について説明する。この実施形態では、ゲート駆動装置100は、デッドタイム設定回路30a、30bの機能を制御回路120において実行する構成とされ、また、これによって、ゲート変動検出回路160はコンパレータ61a、61bを設ける構成としている。

#### 【0054】

また、この実施形態においては、MOSトランジスタ1、2の電流検出機能を用いるのではなく、それぞれの通電経路にドレイン電流 $I_{d1}$ 、 $I_{d2}$ を検出するように、電流検出センサ3a、3bを設ける構成としている。参照電圧調整回路50a、50bの電流モニタ部51a、51bは、それぞれの電流検出センサ3a、3bから電流検出信号が入力されるように構成されている。

20

#### 【0055】

制御回路120は、ゲート変動検出回路160から出力されるMOSトランジスタ1、2のゲート電圧の変動の検出信号により実デッドタイムを算出し、マージンを加えてデッドタイムを設定した値に基づいて、駆動回路40a、40bに駆動信号を与える構成である。

したがって、このような第3実施形態においても第1実施形態と同様の作用効果を得ることができる。

#### 【0056】

30

##### (第3実施形態)

図5および図6は第3実施形態を示すもので、以下、第1実施形態と異なる部分について説明する。この実施形態では、ゲート駆動装置110は、参照電圧調整回路150a、150bとして、それぞれのMOSトランジスタ1、2の温度をモニタする機能を備えた構成としている。温度モニタの構成としては、例えば、検出部位にダイオードを配置し、これに一定電流を流す構成が設けられる。ダイオードに一定電流が流れたときの順方向電圧を検出することで温度を算出することができる。

#### 【0057】

以下、参照電圧調整回路150a、150bは、同等の構成となっており、以下の説明では参照電圧調整回路150aについて説明する。温度モニタ部57aは、MOSトランジスタ1からの温度に対応した信号が入力されると、温度信号をしきい値設定部55aに出力する。しきい値設定部55aは、温度Tに対応したしきい値 $V_{th}$ の値を加算器56aに出力する。

40

#### 【0058】

第1実施形態においては、前述した式(1)に示したしきい値電圧 $V_{th}$ の値は、MOSトランジスタ1、2のそれぞれの固有の値として扱っていたが、実際には使用環境温度やドレイン電流 $I_d$ が流れることにより素子温度が変化すると、これに応じてしきい値電圧 $V_{th}$ についての変化する特性を有している。

#### 【0059】

このしきい値電圧 $V_{th}$ の温度特性は、図6に示すように、温度Tが上昇するとこれに

50

応じて例えば図示のように直線的に減少する関係にある。図6に示しているように、温度TがT<sub>a</sub>からT<sub>b</sub>に上昇すると、しきい値電圧V<sub>th</sub>は、V<sub>tha</sub>からV<sub>thb</sub>に低下する。

#### 【0060】

温度モニタ部57a、57bは、MOSトランジスタ1、2の温度Tの検出信号を入力して検出温度に対応した信号をしきい値設定部55a、55bに出力する。しきい値設定部55aは、あらかじめMOSトランジスタ1の温度特性に対応するデータが記憶されており、温度信号Tが入力されると、これに対応したしきい値V<sub>th</sub>(T)を読み出して出力する。なお、図6に示す温度としきい値電圧との関係を数式として記憶し、算出して出力するようにしても良い。

10

#### 【0061】

これにより、参照電圧調整回路150aは、MOSトランジスタ1のドレイン電流I<sub>d</sub>1の大きさと温度Tとに応じて参照電圧V<sub>gsm1</sub>をコンパレータ61aに設定することができる。

#### 【0062】

この結果、MOSトランジスタ1、2がオンオフするタイミングをより正確に検出することができ、マージンの設定を回路中の誤差に起因するわずかな分だけ設定することができ、デッドタイムの検出を精度良く行うことができる。特に、同期整流時には、参照電圧としてしきい値電圧V<sub>th</sub>が温度に対応して設定されるので、オンオフのタイミングを正確に検出することができるようになる。

20

#### 【0063】

このような本実施形態によれば、MOSトランジスタ1、2のドレイン電流I<sub>d1</sub>、I<sub>d2</sub>の大きさだけでなく、素子温度T<sub>1</sub>、T<sub>2</sub>にも対応して、オンオフのタイミングを検出するための参照電圧V<sub>gsm1</sub>、V<sub>gsm2</sub>を設定することができるようになる。

#### 【0064】

なお、装置の使用環境や使用形態によっては、温度変化が少なくしきい値電圧V<sub>th</sub>の変動も少ない場合には、一定値として設定する第1実施形態の構成を用いることでも支障はない。そして、この実施形態で扱うように、素子温度の変動に伴うしきい値電圧V<sub>th</sub>の変化が大きくなる場合には、本実施形態を適用することでデッドタイムを精度良く検出することができる。

30

#### 【0065】

##### (他の実施形態)

なお、本発明は、上述した実施形態のみに限定されるものではなく、その要旨を逸脱しない範囲で種々の実施形態に適用可能であり、例えば、以下のように変形または拡張することができる。

#### 【0066】

半導体スイッチング素子として、MOSトランジスタは、一般的なシリコン(Si)製のもの以外に、炭化シリコン(SiC)のものを用いることもできるし、また、IGBT(Insulated Gate Bipolar Transistor)などのゲート駆動型のスイッチング素子に適用することができる。

40

#### 【0067】

本開示は、実施例に準拠して記述されたが、本開示は当該実施例や構造に限定されるものではないと理解される。本開示は、様々な変形例や均等範囲内の変形をも包含する。加えて、様々な組み合わせや形態、さらには、それらに一要素のみ、それ以上、あるいはそれ以下、を含む他の組み合わせや形態をも、本開示の範疇や思想範囲に入るものである。

#### 【符号の説明】

#### 【0068】

図面中、1、2はMOSトランジスタ(ゲート駆動型の半導体スイッチング素子)、3a、3bは電流検出素子、10、100、110はゲート駆動装置、20は制御回路、30a、30bはデッドタイム設定回路、40a、40bは駆動回路、50a、50bは参

50

照電圧調整回路、60はゲート変動検出回路、61a、61bはコンパレータである。

【図面】

【図1】

【図2】

Fig.2

10

20

30

【図3】

【図4】

Fig.4

40

50

【図 5】

【図 6】

Fig.6

10

20

30

40

50

---

フロントページの続き

(56)参考文献      特開2002-272131(JP,A)

特開2015-216818(JP,A)

特開2010-016937(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H02M 1/08