(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3906067号

(P3906067)

(45) 発行日 平成19年4月18日(2007.4.18)

(24) 登録日 平成19年1月19日(2007.1.19)

(51) Int.C1.

F 1

|                               |                             |

|-------------------------------|-----------------------------|

| <b>H01L 21/8246 (2006.01)</b> | <b>H01L 27/10 27/10 447</b> |

| <b>H01L 27/105 (2006.01)</b>  | <b>G11C 11/15 100</b>       |

| <b>G11C 11/15 (2006.01)</b>   | <b>H01L 43/08 Z</b>         |

| <b>H01L 43/08 (2006.01)</b>   |                             |

請求項の数 3 (全 12 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2001-367753 (P2001-367753)  |

| (22) 出願日  | 平成13年11月30日 (2001.11.30)      |

| (65) 公開番号 | 特開2003-168784 (P2003-168784A) |

| (43) 公開日  | 平成15年6月13日 (2003.6.13)        |

| 審査請求日     | 平成15年10月1日 (2003.10.1)        |

|           |                                       |

|-----------|---------------------------------------|

| (73) 特許権者 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号 |

| (74) 代理人  | 100058479<br>弁理士 鈴江 武彦                |

| (74) 代理人  | 100084618<br>弁理士 村松 貞男                |

| (74) 代理人  | 100092196<br>弁理士 橋本 良郎                |

| (74) 代理人  | 100091351<br>弁理士 河野 哲                 |

| (74) 代理人  | 100088683<br>弁理士 中村 誠                 |

| (74) 代理人  | 100070437<br>弁理士 河井 将次                |

最終頁に続く

(54) 【発明の名称】磁気ランダムアクセスメモリ

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の第1TMR素子を有する第1アレイと、前記第1アレイ上に配置され、複数の第2TMR素子を有する第2アレイと、前記第1アレイ内に配置され、前記複数の第1TMR素子に接続される第1配線と、前記第1配線の一端に接続される第1スイッチング素子と、前記第2アレイ内に配置され、前記複数の第2TMR素子に接続され、前記第1配線と同一方向に延びる第2配線と、前記第2配線の一端に接続される第2スイッチング素子とを具備し、前記第2TMR素子の数は、前記第1TMR素子の数よりも多く、前記第1及び第2スイッチング素子は、前記第1及び第2配線が延びる方向に一列に配置され、前記第1スイッチング素子は、前記第2スイッチング素子よりも前記第1アレイの中心に近い位置に配置されることを特徴とする磁気ランダムアクセスメモリ。

## 【請求項 2】

複数の第1TMR素子を有する第1アレイと、前記第1アレイ上に配置され、複数の第2TMR素子を有する第2アレイと、前記第1アレイ内に配置され、前記複数の第1TMR素子に接続される第1配線と、前記第1配線の一端に接続される第1センスアンプと、前記第2アレイ内に配置され、前記複数の第2TMR素子に接続され、前記第1配線と同一方向に延びる第2配線と、前記第2配線の一端に接続される第2センスアンプとを具備し、前記第2TMR素子の数は、前記第1TMR素子の数よりも多く、前記第1及び第2センスアンプは、前記第1及び第2配線が延びる方向に一列に配置され、前記第1センスアンプは、前記第2センスアンプよりも前記第1アレイの中心に近い位置に配置されるこ

10

20

とを特徴とする磁気ランダムアクセスメモリ。

**【請求項 3】**

複数の第1TMR素子を有する第1アレイと、前記第1アレイ上に配置され、複数の第2TMR素子を有する第2アレイと、前記第1アレイ内に配置され、前記複数の第1TMR素子の各々に対する書き込みに使用する第1書き込み線と、前記第1書き込み線の一端に接続される第1スイッチング素子と、前記第2アレイ内に配置され、前記複数の第2TMR素子の各々に対する書き込みに使用し、前記第1書き込み線と同一方向に延びる第2書き込み線と、前記第2書き込み線の一端に接続される第2スイッチング素子とを具備し、前記第2TMR素子の数は、前記第1TMR素子の数よりも多く、前記第1及び第2スイッチング素子は、前記第1及び第2書き込み線が延びる方向に一列に配置され、前記第1スイッチング素子は、前記第2スイッチング素子よりも前記第1アレイの中心に近い位置に配置されることを特徴とする磁気ランダムアクセスメモリ。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、トンネル磁気抵抗（Tunneling Magneto Resistive）効果により“1”，“0”-情報を記憶するTMR素子を利用してメモリセルを構成した磁気ランダムアクセスメモリ（MRAM: Magnetic Random Access Memory）に関する。

**【0002】**

**【従来の技術】**

近年、新たな原理により情報を記憶するメモリが数多く提案されているが、そのうちの一つに、Roy Scheuerlein et.al.によって提案されたトンネル磁気抵抗（Tunneling Magneto Resistive: 以後、TMRと表記する。）効果を利用したメモリがある（例えば、ISSCC2000 Technical Digest p.128「A 10ns Read and Write Non-Volatile Memory Array Using a Magnetic Tunnel Junction and FET Switch in each Cell」を参照）。

**【0003】**

磁気ランダムアクセスメモリは、TMR素子により“1”，“0”-情報を記憶する。TMR素子は、2つの磁性層（強磁性層）により絶縁層（トンネルバリア）を挟んだ構造を有する。TMR素子に記憶される情報は、2つの磁性層のスピノの向きが平行か又は反平行かによって判断される。

**【0004】**

ここで、平行とは、2つの磁性層のスピノの向きが同じであることを意味し、反平行とは、2つの磁性層のスピノの向きが逆向きであることを意味する。

**【0005】**

通常、TMR素子を構成する2つの磁性層のうちの一つは、スピノの向きが固定される固定層となるため、“1”，“0”-情報をTMR素子に記憶させる場合には、書き込み情報に応じて、これら2つの磁性層のうちの他の一つ（自由層）のスピノの向きを変えてやればよい。

**【0006】**

ところで、近年では、種々のデバイス構造又は回路構造のMRAMが提案されており、そのうちの一つに、一つのスイッチング素子（選択トランジスタ）に複数のTMR素子を接続したデバイス構造が知られている。この構造は、セルの高密度化や読み出しマージンの向上を図るうえで有利である。

**【0007】**

例えば、特願2000-296082（平成12年9月28日出願）は、上部配線と下部配線の間に複数のTMR素子を並列に接続したセル構造を提案する。このセル構造では、図9及び図10に示すように、複数のTMR素子10が基板上に複数段（本例では、3段）に積み上げられる。また、各段においては、上部配線11と下部配線12の間に複数のTMR素子10が並列に接続される。

**【0008】**

10

20

30

40

50

上部配線 11 は、X 方向に延び、その一端は、選択トランジスタ 14 に接続される。下部配線 12 も、X 方向に延び、その一端は、センスアンプ (S/A) 15 などの周辺回路に接続される。本例では、読み出し電流は、上部配線 11、TMR 素子 10、下部配線 12 という経路、即ち、X 方向に沿って流れる。書き込み配線 13 は、TMR 素子 10 に隣接して配置され、Y 方向に延びている。

#### 【0009】

なお、図 9において、積み重ねられた TMR 素子と X 方向に延びる配線は、各段において互いにずれているように記載されているが、これは、説明を分かり易くするためであり、実際は、互いにずれっていても、又は、完全にオーバーラップしていても、どちらでもよい。

10

#### 【0010】

##### 【発明が解決しようとする課題】

磁気ランダムアクセスメモリのセルの基本構造は、1つの TMR 素子に1つのスイッチング素子（選択トランジスタ）を対応させた1セル-1トランジスタ構造である。しかし、TMR 素子を複数段に積み重ねたデバイス構造では、1つの TMR 素子に1つのスイッチング素子を対応させると、スイッチング素子数が多くなり、セルの高密度化に不利となる。

#### 【0011】

そこで、TMR 素子 10 を複数段に積み重ねたデバイス構造の場合、1つの TMR 素子に1つのスイッチング素子を対応させなくとも、読み出し動作や書き込み動作を行うことができるようなデバイス構造が採用される。

20

#### 【0012】

例えば、図 9 及び図 10 に示すデバイス構造では、TMR 素子 10 のアレイの各段において、上部配線 10 と下部配線 12との間に複数の TMR 素子 10 を接続する。そして、例えば、上部配線 11 の一端に選択トランジスタ 14 を接続し、下部配線 12 の一端にセンスアンプ (S/A) 15 を接続する。

#### 【0013】

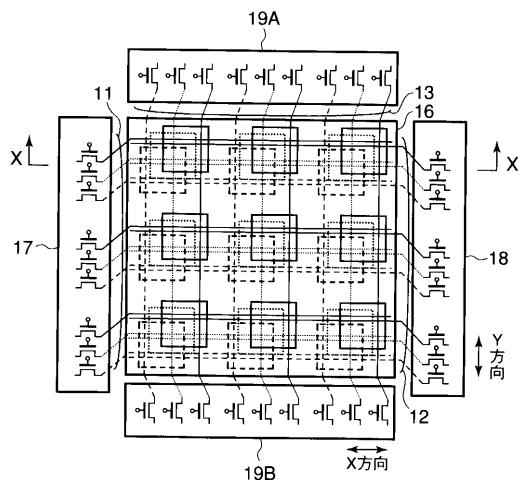

しかし、この場合、TMR 素子 10 のアレイの各段に配置される上部配線 11 のそれぞれに対して選択トランジスタが必要になる。また、上部配線 11 は、TMR 素子 10 のアレイ 16 上において X 方向に延びている。このため、上部配線 11 に接続される選択トランジスタは、アレイ 16 の端部のエリア 17 に集中して配置される。

30

#### 【0014】

同様に、TMR 素子 10 のアレイの各段に配置される下部配線（読み出し配線）12 のそれぞれに対しては、センスアンプ（トランジスタ）が必要になる。また、下部配線 12 は、TMR 素子 10 のアレイ 16 上において X 方向に延びている。このため、下部配線 12 に接続されるトランジスタは、アレイ 16 の端部のエリア 18 に集中して配置される。

#### 【0015】

同様に、TMR 素子 10 のアレイの各段に配置される書き込み配線 13 のそれぞれに対しても、選択トランジスタが必要になる。また、書き込み配線 13 は、TMR 素子 10 のアレイ 16 上において Y 方向に延びている。このため、書き込み配線 13 に接続される選択トランジスタは、アレイ 16 の端部のエリア 19A, 19B に集中して配置される。

40

#### 【0016】

ところで、TMR 素子に対するデータ書き込み / 読み出し動作においては、TMR 素子の特性に起因し、大電流が必要になることが知られている。このため、上部配線 11、下部配線 12 及び書き込み配線 13 に接続されるトランジスタのサイズ（又はピッチ）は、必然的に大きくなることが予想される。

#### 【0017】

また、X 方向に配置される TMR 素子のグループを 1 カラムとし、Y 方向に配置される TMR 素子のグループを 1 ロウとした場合、TMR 素子の積み重ね段数が増加すると、これに比例して、1 ロウ又は 1 カラム内に設けなければならないトランジスタ数も増加する。

50

**【0018】**

TMR素子のピッチは、TMR素子の積み重ね段数に影響を受けないため、TMR素子の積み重ね段数が非常に多くなると、1ロウ又は1カラム内のトランジスタ数のみが増大し、アレイ16周辺のエリア17，18，19A，19B内に、全てのトランジスタを配置できなくなる。

**【0019】**

逆に、アレイ16周辺のエリア17，18，19A，19B内に、全てのトランジスタを配置しようとすると、トランジスタのピッチが大きいために、これに合わせて、TMR素子10のピッチも大きくなり、結局、TMR素子の高集積化を図ることができない。

**【0020】**

なお、トランジスタのサイズを小さくし、そのピッチを小さくすると、大電流を扱うことができなくなるため、メモリの動作に支障をきたす。

**【0021】**

本発明の目的は、TMR素子の積み重ね段数が増加し、TMR素子のアレイ内に配置される配線に接続されるトランジスタ数が多くなっても、そのトランジスタ数に左右されずには、TMR素子のピッチを決定することができるような新規なデバイス構造を提案することにより、TMR素子の微細化や、高集積化などを図ることにある。

**【0022】****【課題を解決するための手段】**

本発明の磁気ランダムアクセスメモリは、複数段に積み重ねられた複数のTMR素子を有するアレイと、前記アレイ内に配置される第1配線と、前記第1配線に接続される第1素子と、前記アレイ内に配置され、前記第1配線と同一機能を有し、前記第1配線よりも上に形成される第2配線と、前記第2配線に接続される第2素子とを備え、各段に配置されるTMR素子の数は、下段から上段に向かって次第に多くなり、前記第1及び第2素子は、前記アレイの直下に配置される。

**【0023】**

本発明の磁気ランダムアクセスメモリは、複数段に積み重ねられた複数のTMR素子を有するアレイと、前記アレイ内に配置される第1配線と、前記第1配線に接続される第1素子と、前記アレイ内に配置され、前記第1配線と同一機能を有し、前記第1配線よりも上に形成される第2配線と、前記第2配線に接続される第2素子とを備え、前記第1及び第2素子は、共に、前記アレイの直下を除く周辺部に配置され、前記第1素子は、前記第2素子よりも前記アレイの近くに配置される。

**【0024】**

前記第1及び第2配線は、共に、同一方向に延びている。前記第1及び第2素子は、前記第1及び第2配線が延びる方向に一列に並んでいる。前記第1素子は、前記第2素子よりも前記アレイの中心に近い位置に配置される。

**【0025】**

前記第1及び第2配線が延びる方向に存在するTMR素子に関して、TMR素子の数は、下段から上段に向かって次第に多くなる。

**【0026】**

前記第1及び第2配線が延びる方向は、ロウ方向又はカラム方向である。前記第1及び第2配線は、データ書き込み動作又はデータ読み出し動作に使用する配線である。

**【0027】**

前記第1及び第2素子は、スイッチング素子である。前記第1及び第2素子は、センスアンプを構成している。前記第1配線は、前記第2配線よりも短い。

**【0028】**

本発明の磁気ランダムアクセスメモリは、一列に並んだ複数のTMR素子と、前記複数のTMR素子に共通に接続され、かつ、前記複数のTMR素子を挟み込む第1及び第2配線と、前記第1配線の一端に接続されるスイッチング素子と、前記第2配線の一端に接続されるセンスアンプとから構成されるユニットを備え、前記ユニットは、複数段に積み重ね

10

20

30

40

50

られ、かつ、前記ユニット内の前記TMR素子の数は、下段のユニットから上段のユニットに向かって次第に多くなっていく。

#### 【0029】

本発明の磁気ランダムアクセスメモリは、一列に並んだ複数のTMR素子と、前記複数のTMR素子に共通に接続され、かつ、前記複数のTMR素子を挟み込む第1及び第2配線と、前記第1配線の一端に接続されるスイッチング素子と、前記第2配線の一端に接続されるセンスアンプとから構成されるユニットを備え、前記ユニットは、複数段に積み重ねられ、かつ、前記ユニット内の前記第1及び第2配線の長さは、下段のユニットから上段のユニットに向かって次第に長くなっていく。

#### 【0030】

本発明の磁気ランダムアクセスメモリは、一列に並んだ複数のTMR素子と、前記複数のTMR素子に共通に接続される配線と、前記配線の一端に接続されるスイッチング素子と、前記配線の他端に接続されるスイッチング素子とから構成されるユニットを備え、前記ユニットは、複数段に積み重ねられ、かつ、前記ユニット内のTMR素子の数は、下段のユニットから上段のユニットに向かって次第に多くなっていく。

#### 【0031】

##### 【発明の実施の形態】

以下、図面を参照しながら、本発明の磁気ランダムアクセスメモリについて詳細に説明する。

#### 【0032】

本発明は、TMR素子が複数段に積み重ねられたアレイ構造を有する磁気ランダムアクセスメモリに適用される。

#### 【0033】

本発明の磁気ランダムアクセスメモリの第一の特徴は、各段に配置されるTMR素子の数を、下段から上段に向かって次第に多くする点にある。このようなアレイ構造にすることで、TMR素子のアレイの直下にトランジスタを配置することができるため、TMR素子の積み重ね段数が増大し、1口ウ又は1カラム内の配線に接続されるトランジスタ数が増大しても、トランジスタのピッチによらず、TMR素子のピッチを決定することができる。

#### 【0034】

本発明の磁気ランダムアクセスメモリの第二の特徴は、TMR素子のアレイ内に配置される同一機能を有する配線に関して、下段に位置する配線は、TMR素子のアレイの近くに存在するトランジスタに接続され、上段に位置する配線は、TMR素子のアレイから遠く離れたトランジスタに接続される点にある。このようなデバイス構造にすれば、1口ウ又は1カラム内の配線に接続されるトランジスタ数が増大した場合でも、それらのトランジスタは、アレイの近傍から遠くへ向かって一列に配置されることになるため、トランジスタのピッチによらず、TMR素子のピッチを決定することができる。

#### 【0035】

##### 【第1実施の形態】

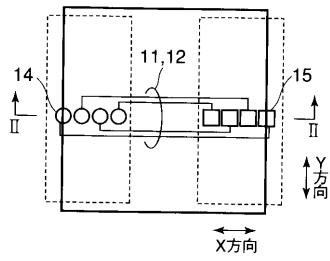

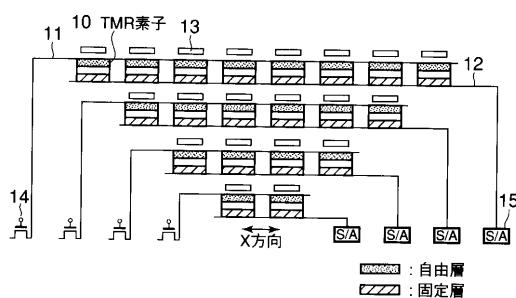

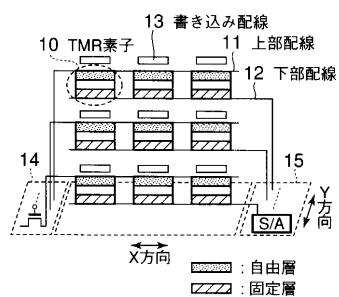

図1は、本発明の第1実施の形態に関する磁気ランダムアクセスメモリのセルアレイ部のレイアウトの概要を示している。図2は、図1のセルアレイ部のX方向(1カラム)に沿った断面、即ち、図1のII-II線に沿う断面を示している。

#### 【0036】

半導体基板上には、複数のTMR素子10が複数段(本例では、4段)に積み重ねられている。また、各段においては、TMR素子10は、X-Y平面内においてアレイを構成している。

#### 【0037】

上部配線11及び下部配線12は、共に、X方向に延び、両配線11, 12の間には、X方向に配置される複数のTMR素子10が配置されている。上部配線11の一端には、選択トランジスタ14が接続される。また、下部配線12の一端には、センスアンプ(S/

10

20

30

40

50

A ) 15などの周辺回路が接続される。

**【0038】**

上部配線11及び下部配線12は、読み出し配線として機能する。即ち、データ読み出し時、読み出し電流は、上部配線11、TMR素子10、下部配線12という経路、即ち、X方向に沿って流れる。

**【0039】**

書き込み配線13は、TMR素子10のアレイの各段において、TMR素子10上に配置され、Y方向に延びている。また、書き込み配線13は、TMR素子10の自由層に近接して配置される。

**【0040】**

TMR素子10の数は、下段から上段に向かって次第に多くなっている。本実施の形態では、1カラム内のTMR素子10に関して、TMR素子10の数を、下段から上段に向かって次第に多くなるようにしている。

**【0041】**

このようなアレイ構造にすることで、TMR素子10のアレイの直下にトランジスタを配置することができるため、TMR素子10の積み重ね段数が増大し、1カラム内の配線に接続されるトランジスタ数が増大しても、トランジスタを形成するための十分な領域を確保できる。

**【0042】**

また、TMR素子10のアレイ内に配置される同一機能を有する配線、例えば、X方向に延びる上部配線11に関して、下段に位置する上部配線11は、TMR素子10のアレイの近くに存在するトランジスタに接続され、上段に位置する上部配線11は、TMR素子10のアレイから遠く離れたトランジスタに接続される。

**【0043】**

同様に、X方向に延びる下部配線12に関しても、下段に位置する下部配線12は、TMR素子10のアレイの近くに存在するセンスアンプ(トランジスタ)15に接続され、上段に位置する下部配線12は、TMR素子10のアレイから遠く離れたセンスアンプ(トランジスタ)15に接続される。

**【0044】**

このようなデバイス構造にすれば、TMR素子10の積み重ね段数が増大し、1カラム内の配線に接続されるトランジスタ数が増大した場合でも、それらのトランジスタは、アレイの近傍から遠くへ向かって一列に配置されることになるため、トランジスタのピッチに影響されずに、TMR素子のピッチを決定することができる。

**【0045】**

このように、本実施の形態では、TMR素子10の数は、TMR素子10のアレイの下段から上段に向かって次第に多くなり、さらに、TMR素子10のアレイ内に配置される同一機能を有する配線に関しては、上段の配線は、下段の配線に比べて、TMR素子10のアレイから遠く離れたトランジスタに接続される。

**【0046】**

これにより、TMR素子のアレイ内に配置される配線に接続されるトランジスタ数が多くなっても、そのトランジスタ数に左右されずに、TMR素子のピッチを決定することができ、TMR素子の微細化や、高集積化などを図ることができる。

**【0047】**

[第2実施の形態]

上述の第1実施の形態では、複数段に積み重ねられたTMR素子のアレイに関して、下段から上段に向かうにつれてTMR素子の数を増やしている。しかし、TMR素子の抵抗、配線抵抗、配線容量などを考慮した場合、各段において、TMR素子の数が異なると、読み出し/書き込み動作などに悪影響を与える場合がある。

**【0048】**

そこで、本実施の形態では、このような点を考慮し、複数段に積み重ねられたTMR素子

10

20

30

40

50

のアレイに関して、各段のTMR素子の数は、変えずに、一定とすることを前提とし、この前提条件の下で、TMR素子のピッチの増大を防止し、TMR素子の微細化や、高集積化などを図る技術を提案する。

#### 【0049】

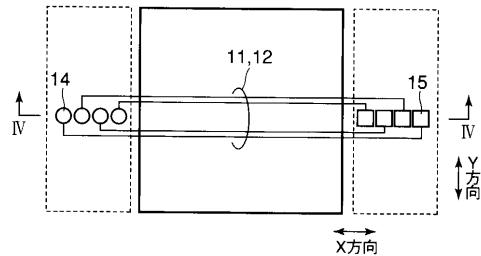

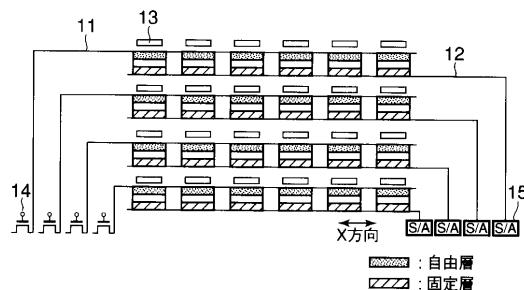

図3は、本発明の第2実施の形態に関する磁気ランダムアクセスメモリのセルアレイ部のレイアウトの概要を示している。図4は、図3のセルアレイ部のX方向(1カラム)に沿った断面、即ち、図3のIV-IV線に沿う断面を示している。

#### 【0050】

半導体基板上には、複数のTMR素子10が複数段(本例では、4段)に積み重ねられている。また、各段においては、TMR素子10は、X-Y平面内においてアレイを構成している。

10

#### 【0051】

上部配線11及び下部配線12は、共に、X方向に延び、両配線11, 12の間には、X方向に配置される複数のTMR素子10が配置されている。上部配線11の一端には、選択トランジスタ14が接続される。また、下部配線12の一端には、センスアンプ(S/A)15などの周辺回路が接続される。

#### 【0052】

上部配線11及び下部配線12は、読み出し配線として機能する。即ち、データ読み出し時、読み出し電流は、上部配線11、TMR素子10、下部配線12という経路、即ち、X方向に沿って流れる。

20

#### 【0053】

書き込み配線13は、TMR素子10のアレイの各段において、TMR素子10上に配置され、Y方向に延びている。また、書き込み配線13は、TMR素子10の自由層に近接して配置される。

#### 【0054】

TMR素子10のアレイ内に配置される同一機能を有する配線、例えば、X方向に延びる上部配線11について、下段に位置する上部配線11は、TMR素子10のアレイの近くに存在するトランジスタに接続され、上段に位置する上部配線11は、TMR素子10のアレイから遠く離れたトランジスタに接続される。

#### 【0055】

30

また、X方向に延びる下部配線12についても、下段に位置する下部配線12は、TMR素子10のアレイの近くに存在するセンスアンプ(トランジスタ)15に接続され、上段に位置する下部配線12は、TMR素子10のアレイから遠く離れたセンスアンプ(トランジスタ)15に接続される。

#### 【0056】

このようなデバイス構造にすれば、TMR素子10の積み重ね段数が増大し、1カラム内の配線に接続されるトランジスタ数が増大した場合でも、それらのトランジスタは、アレイの近傍から遠くへ向かって一列に配置されることになるため、トランジスタのピッチに影響されずに、TMR素子のピッチを決定することができる。

#### 【0057】

40

このように、本実施の形態では、TMR素子10のアレイ内に配置される同一機能を有する配線については、上段の配線は、下段の配線に比べて、TMR素子10のアレイから遠く離れたトランジスタに接続される。

#### 【0058】

これにより、TMR素子のアレイ内に配置される配線に接続されるトランジスタ数が多くなっても、そのトランジスタ数に左右されずに、TMR素子のピッチを決定することができ、TMR素子の微細化や、高集積化などを図ることができる。

#### 【0059】

#### [第3実施の形態]

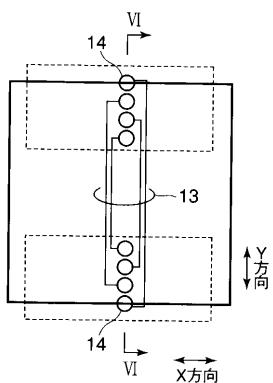

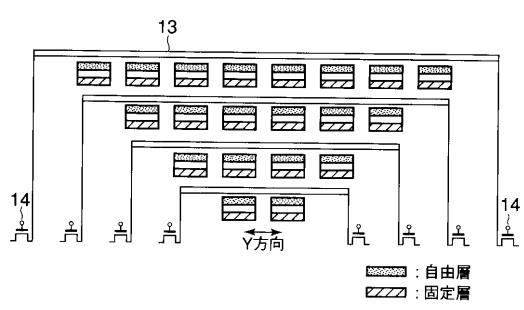

図5は、本発明の第3実施の形態に関する磁気ランダムアクセスメモリのセルアレイ部の

50

レイアウトの概要を示している。図6は、図5のセルアレイ部のY方向(1口ウ)に沿った断面、即ち、図5のVI-VI線に沿う断面を示している。

#### 【0060】

半導体基板上には、複数のTMR素子10が複数段(本例では、4段)に積み重ねられている。また、各段においては、TMR素子10は、X-Y平面内においてアレイを構成している。

#### 【0061】

上部配線は、TMR素子10の自由層に接続され、下部配線は、TMR素子の固定層に接続され、両配線は、共に、X方向に延びている。本実施の形態では、説明を簡略化するため、上部配線及び下部配線については、省略している。

10

#### 【0062】

書き込み配線13は、TMR素子10のアレイの各段において、TMR素子10上に配置され、Y方向に延びている。また、書き込み配線13は、TMR素子10の自由層に近接して配置される。

#### 【0063】

TMR素子10の数は、下段から上段に向かって次第に多くなっている。本実施の形態では、1口ウ内のTMR素子10に関して、TMR素子10の数を、下段から上段に向かって次第に多くなるようにしている。

#### 【0064】

このようなアレイ構造にすることで、TMR素子10のアレイの直下にトランジスタを配置することができるため、TMR素子10の積み重ね段数が増大し、1カラム内の配線に接続されるトランジスタ数が増大しても、トランジスタを形成するための十分な領域を確保できる。

20

#### 【0065】

また、TMR素子10のアレイ内に配置される同一機能を有する配線、例えば、Y方向に延びる書き込み配線13に関して、下段に位置する書き込み配線13は、TMR素子10のアレイの近くに存在するトランジスタに接続され、上段に位置する書き込み配線13は、TMR素子10のアレイから遠く離れたトランジスタに接続される。

#### 【0066】

このようなデバイス構造にすれば、TMR素子10の積み重ね段数が増大し、1口ウ内の配線に接続されるトランジスタ数が増大した場合でも、それらのトランジスタは、アレイの近傍から遠くへ向かって一列に配置されることになるため、トランジスタのピッチに影響されずに、TMR素子のピッチを決定することができる。

30

#### 【0067】

このように、本実施の形態では、TMR素子10の数は、TMR素子10のアレイの下段から上段に向かって次第に多くなり、さらに、TMR素子10のアレイ内に配置される同一機能を有する配線に関しては、上段の配線は、下段の配線に比べて、TMR素子10のアレイから遠く離れたトランジスタに接続される。

#### 【0068】

これにより、TMR素子のアレイ内に配置される配線に接続されるトランジスタ数が多くなっても、そのトランジスタ数に左右されずに、TMR素子のピッチを決定することができ、TMR素子の微細化や、高集積化などを図ることができる。

40

#### 【0069】

##### [第4実施の形態]

第4実施の形態では、第2実施の形態と同様の理由により、複数段に積み重ねられたTMR素子のアレイに関して、各段のトランジスタ数は、変えずに、一定とすることを前提とし、この前提条件の下で、TMR素子のピッチの増大を防止し、TMR素子の微細化や、高集積化などを図る技術を提案する。

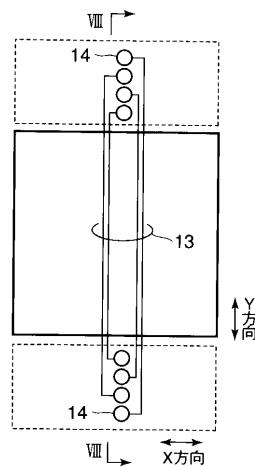

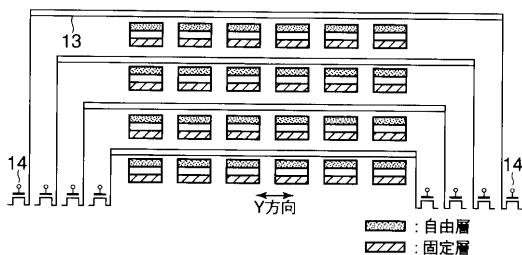

#### 【0070】

図7は、本発明の第4実施の形態に関わる磁気ランダムアクセスメモリのセルアレイ部の

50

レイアウトの概要を示している。図8は、図7のセルアレイ部のY方向(1口ウ)に沿った断面、即ち、図7のVII - VII線に沿う断面を示している。

#### 【0071】

半導体基板上には、複数のTMR素子10が複数段(本例では、4段)に積み重ねられている。また、各段においては、TMR素子10は、X-Y平面内においてアレイを構成している。

#### 【0072】

上部配線は、TMR素子10の自由層に接続され、下部配線は、TMR素子の固定層に接続され、両配線は、共に、X方向に延びている。本実施の形態では、説明を簡略化するため、上部配線及び下部配線については、省略している。

10

#### 【0073】

書き込み配線13は、TMR素子10のアレイの各段において、TMR素子10上に配置され、Y方向に延びている。また、書き込み配線13は、TMR素子10の自由層に近接して配置される。

#### 【0074】

TMR素子10のアレイ内に配置される同一機能を有する配線、例えば、Y方向に延びる書き込み配線13に関して、下段に位置する書き込み配線13は、TMR素子10のアレイの近くに存在するトランジスタに接続され、上段に位置する書き込み配線13は、TMR素子10のアレイから遠く離れたトランジスタに接続される。

#### 【0075】

このようなデバイス構造にすれば、TMR素子10の積み重ね段数が増大し、1カラム内の配線に接続されるトランジスタ数が増大した場合でも、それらのトランジスタは、アレイの近傍から遠くへ向かって一列に配置されることになるため、トランジスタのピッチに影響されずに、TMR素子のピッチを決定することができる。

20

#### 【0076】

このように、本実施の形態では、TMR素子10のアレイ内に配置される同一機能を有する配線に関しては、上段の配線は、下段の配線に比べて、TMR素子10のアレイから遠く離れたトランジスタに接続される。

#### 【0077】

これにより、TMR素子のアレイ内に配置される配線に接続されるトランジスタ数が多くなっても、そのトランジスタ数に左右されずに、TMR素子のピッチを決定することができ、TMR素子の微細化や、高集積化などを図ることができる。

30

#### 【0078】

##### [その他]

本発明は、TMR素子が複数段に積み重ねられたセルアレイ構造を有する磁気ランダムアクセスメモリであれば、如何なる構造のものにも適用可能である。

#### 【0079】

上述の第1乃至第4実施の形態において、TMR素子のアレイ内の配線に接続されるトランジスタは、MOSトランジスタが一般的であるが、バイポーラトランジスタやダイオードなどであってもよい。

40

#### 【0080】

また、上述の第1乃至第4実施の形態では、複数段に積み重ねられたTMR素子の各段に配置された配線を例に説明したが、例えば、上下のTMR素子で配線を共有化する場合などにおいては、同一機能を有する配線は、各段に配置されず、1段おきに配置される。このような場合でも、それら1段おきに配置された配線に関して、本発明を適用することができる。

#### 【0081】

##### 【発明の効果】

以上、説明したように、本発明の磁気ランダムアクセスメモリによれば、TMR素子が複数段に積み重ねられたアレイ構造において、TMR素子の積み重ね段数が増加し、TMR

50

素子のアレイ内に配置される配線に接続されるトランジスタ数が多くなっても、そのトランジスタ数に左右されずに、TMR素子のサイズやピッチを決定することができ、TMR素子の微細化や、高集積化などを図ることができる。

【図面の簡単な説明】

【図1】本発明の第1実施の形態に關わるメモリのアレイ部を示す平面図。

【図2】図1のII-II - II-II線に沿う断面図。

【図3】本発明の第2実施の形態に關わるメモリのアレイ部を示す平面図。

【図4】図3のIV-IV - IV-IV線に沿う断面図。

【図5】本発明の第3実施の形態に關わるメモリのアレイ部を示す平面図。

【図6】図5のVI-VI - VI-VI線に沿う断面図。

【図7】本発明の第4実施の形態に關わるメモリのアレイ部を示す平面図。

【図8】図7のVII-VII - VII-VII線に沿う断面図。

【図9】従来のメモリのアレイ部を示す平面図。

【図10】図9のIX-IX - IX-IX線に沿う断面図。

【符号の説明】

|                           |                     |    |

|---------------------------|---------------------|----|

| 1 0                       | : TMR素子、            |    |

| 1 1                       | : 上部配線、             |    |

| 1 2                       | : 下部配線、             |    |

| 1 3                       | : 書き込み配線、           |    |

| 1 4                       | : スイッチング素子、         | 20 |

| 1 5                       | : センスアンプ、           |    |

| 1 6                       | : TMR素子のアレイ、        |    |

| 1 7 , 1 8 , 1 9 A , 1 9 B | : TMR素子のアレイの端部のエリア。 |    |

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

実線(—)：上段

点線(---)：中段

破線(- - -)：下段

【図10】

---

フロントページの続き

(72)発明者 梶山 健

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

審査官 柴山 将隆

(56)参考文献 特開2000-187976(JP,A)

特開2000-163950(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8246

G11C 11/15

H01L 27/105

H01L 43/08