(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6495291号

(P6495291)

(45) 発行日 平成31年4月3日(2019.4.3)

(24) 登録日 平成31年3月15日(2019.3.15)

(51) Int.Cl.

H01L 21/822 (2006.01)

H01L 27/04 (2006.01)

F 1

H01L 27/04

H

請求項の数 14 (全 19 頁)

(21) 出願番号 特願2016-542015 (P2016-542015)

(86) (22) 出願日 平成26年9月4日 (2014.9.4)

(65) 公表番号 特表2016-534577 (P2016-534577A)

(43) 公表日 平成28年11月4日 (2016.11.4)

(86) 國際出願番号 PCT/US2014/054104

(87) 國際公開番号 WO2015/038402

(87) 國際公開日 平成27年3月19日 (2015.3.19)

審査請求日 平成29年8月8日 (2017.8.8)

(31) 優先権主張番号 14/024,833

(32) 優先日 平成25年9月12日 (2013.9.12)

(33) 優先権主張国 米国(US)

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】集積回路の静電放電保護

## (57) 【特許請求の範囲】

## 【請求項 1】

入力トランジスタを備える増幅器と、

前記入力トランジスタのドレインにゲートを結合するダイオードであって、

前記ダイオードは、前記ドレインに対する前記ゲートの電圧が正であるとき、順方向バ

イアスされるように構成されるダイオード、

を備え、

前記入力トランジスタの前記ドレインを接地端子に直接結合する第2および第3のダイ

オードをさらに備える装置。

## 【請求項 2】

第1の集積回路パッドと第2の集積回路パッドとをさらに備え、ここにおいて、前記第

1の集積回路パッドが前記入力トランジスタの前記ゲートに結合され、前記第2の集積回

路パッドが前記入力トランジスタのソースに結合された、請求項1に記載の装置。

## 【請求項 3】

前記入力トランジスタの前記ドレインに前記ゲートを結合する第4のダイオードをさ

らに備え、前記ダイオードは、前記ドレインに対する前記ゲートの前記電圧が正であるとき

、順方向バリアスされるように構成される、請求項1に記載の装置。

## 【請求項 4】

前記ダイオードと直列に結合された抵抗器をさらに備える、請求項3に記載の装置。

## 【請求項 5】

10

20

前記入力トランジスタの前記ドレインに前記ゲートを結合する第5のダイオードをさらに備え、前記ダイオードは、前記ゲートに対する前記ドレインの電圧が正であるとき、順方向バイアスされるように構成されるよう記載の装置。

**【請求項6】**

前記第5のダイオードと直列に結合された第6のダイオードをさらに備える、請求項5に記載の装置。

**【請求項7】**

前記入力トランジスタのソースに前記ゲートを結合する第7のダイオードをさらに備え、前記ダイオードは、前記ゲートに対する前記ドレインの前記電圧が正であるとき、順方向バイアスされるように構成されるよう記載の装置。 10

**【請求項8】**

前記入力トランジスタの前記ドレインに結合されたカスコードトランジスタをさらに備える、請求項1に記載の装置。

**【請求項9】**

ゲートとドレインとを有する入力トランジスタを備えるカスコード増幅器を使用して入力信号を増幅することと、

前記ドレインに対する前記ゲートの電圧が正であるとき、順方向バイアスされるように構成されるダイオードを使用して、前記入力信号を前記入力トランジスタの前記ドレインに結合することと、

さらに、第2および第3のダイオードを使用して前記入力トランジスタの前記ドレインを接地端子に直接結合することと 20

を備える方法。

**【請求項10】**

第4のダイオードを使用して前記入力信号を前記入力トランジスタの前記ドレインに結合することをさらに備え、前記ダイオードは、前記ドレインに対する前記ゲートの前記電圧が正であるとき、順方向バイアスされるように構成された、請求項9に記載の方法。

**【請求項11】**

前記ダイオードと直列に抵抗器を結合することをさらに備える、請求項10に記載の方法。

**【請求項12】**

第5のダイオードを使用して前記入力信号を前記入力トランジスタの前記ドレインに結合することをさらに備え、前記ダイオードは、前記ゲートに対する前記ドレインの電圧が正であるとき、順方向バイアスされるように構成された、請求項9に記載の方法。 30

**【請求項13】**

前記第5のダイオードと直列に第6のダイオードを結合することをさらに備える、請求項12に記載の方法。

**【請求項14】**

第7のダイオードを使用して前記入力トランジスタのソースを前記入力信号に結合すること

をさらに備える、請求項9に記載の方法。 40

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

関連出願の相互参照

[0001]本出願は、その内容全体が参照により本明細書に明確に組み込まれる、2013年9月12日に出願された、同一出願人が所有する米国非仮特許出願第14/024,833号の優先権を主張する。

**【0002】**

[0002]本開示は集積回路の静電放電(ESD: electro-static discharge)保護に関する。 50

**【背景技術】****【0003】**

[0003]最先端の集積回路（I C）は、継続的な技術スケーリングにより、ますます高密度の回路およびより小さいデバイスフィーチャサイズを採用する。この傾向は、静電放電（ESD）からの損傷に対する現代のI Cの脆弱性を高め、現代のI Cの十分でロバストなESD保護を与えることが重要になる。

**【0004】**

[0004]I CがESD要件を満たすことを保証するために、製造およびテスト中に、所定のテスト電圧がI Cの入力／出力（I / O）ピンの両端間に外部から印加され得る。これらのテスト電圧は、ESD準拠を決定するための、当技術分野で知られている様々なモデル、たとえば、帯電デバイスマodel（CDM：charged-device model）、人体モデル（HBM：human body model）、機械モデル（MM：machine model）などに従って生成され得る。大きいテスト電圧が印加されたとき、寄生インダクタンスまたは抵抗の存在により、大きい電圧降下がI Cのクリティカル端子の両端間で望ましくなく持続し、敏感回路に潜在的に損傷を与える。

10

**【0005】**

[0005]したがって、最先端のI CにおけるESD保護機構のロバストネスを改善するための新規の技法を提供することが望ましいであろう。

**【図面の簡単な説明】****【0006】**

20

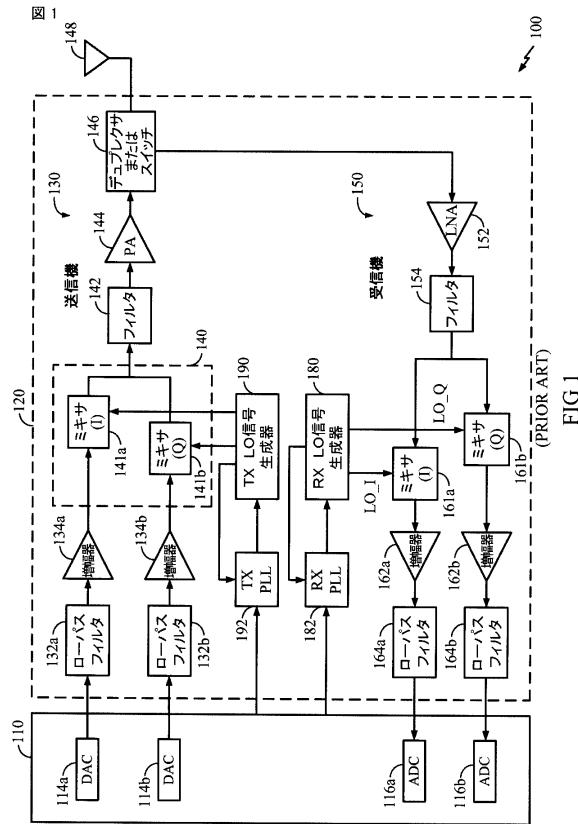

【図1】[0006]本開示の技法が実装され得る従来技術のワイヤレス通信デバイスの設計のプロック図。

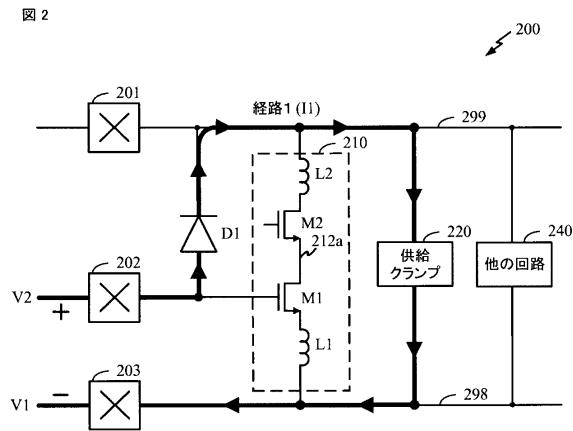

【図2】[0007]I / Oパッドおよび回路を組み込んだ集積回路（I C）の従来技術の実装形態を示す図。

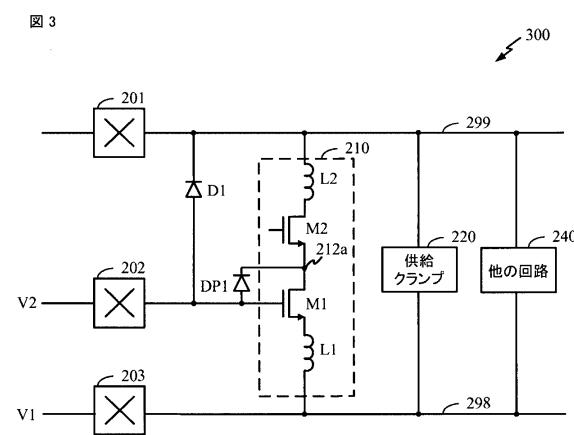

【図3】[0008]上述の問題に対処するために保護ダイオードが設けられた、本開示によるI Cの例示的な実施形態を示す図。

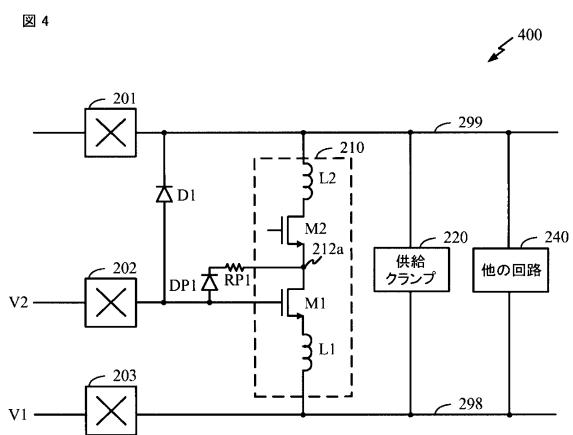

【図4】[0009]追加の抵抗器を組み込んだ、本開示によるI Cの代替の例示的な実施形態を示す図。

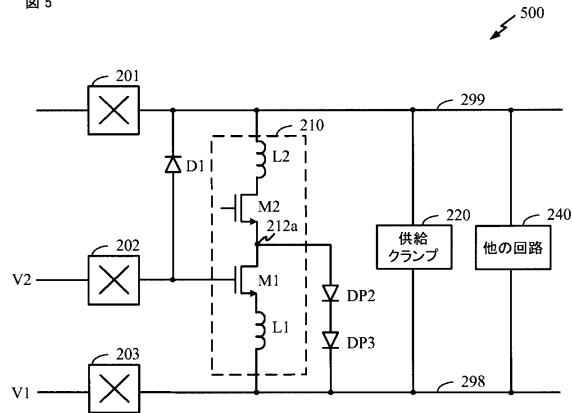

【図5】[0010]複数の保護ダイオードを組み込んだ、本開示によるI Cの代替の例示的な実施形態を示す図。

30

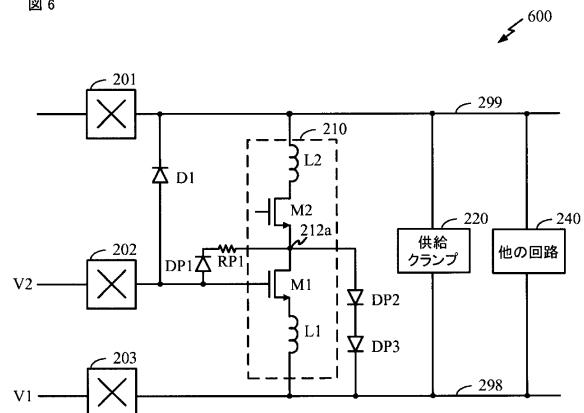

【図6】[0011]本開示の複数の技法を組み込んだ、本開示によるI Cの代替の例示的な実施形態を示す図。

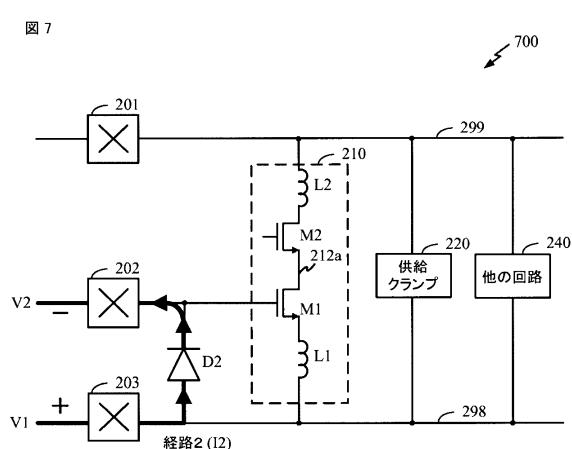

【図7】[0012]I / Oパッドおよび回路を組み込んだ集積回路（I C）の代替の従来技術の実装形態を示す図。

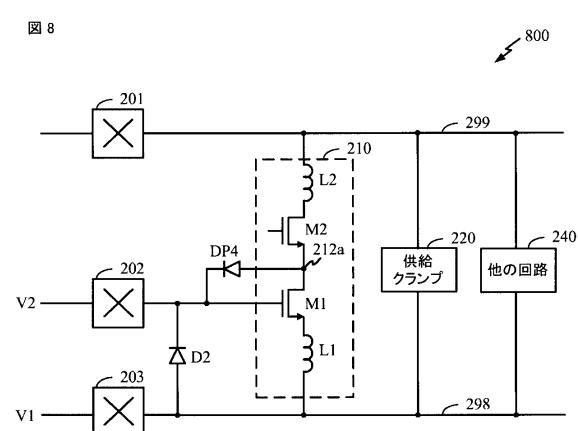

【図8】[0013]追加の保護ダイオードが設けられた、本開示によるI Cの例示的な実施形態を示す図。

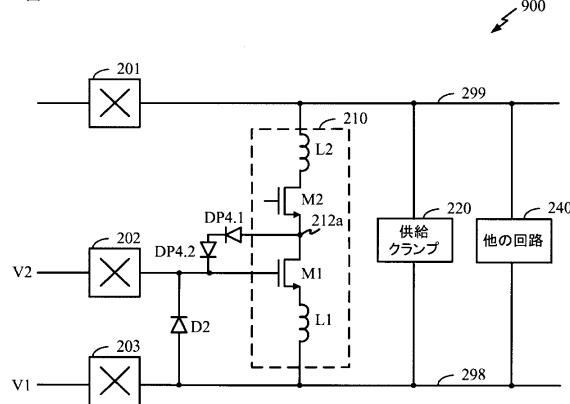

【図9】[0014]2つの直列結合されたダイオードが設けられた、本開示によるI Cの代替の例示的な実施形態を示す図。

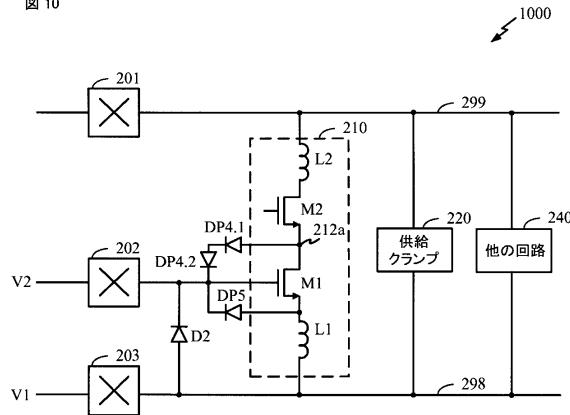

【図10】[0015]本開示のさらなる技法を組み込んだI Cの代替の例示的な実施形態を示す図。

40

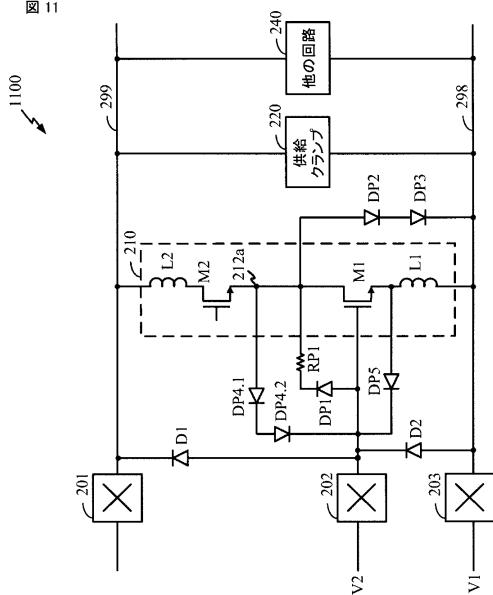

【図11】[0016]本開示の複数の技法を組み込んだ、本開示によるI Cの代替の例示的な実施形態を示す図。

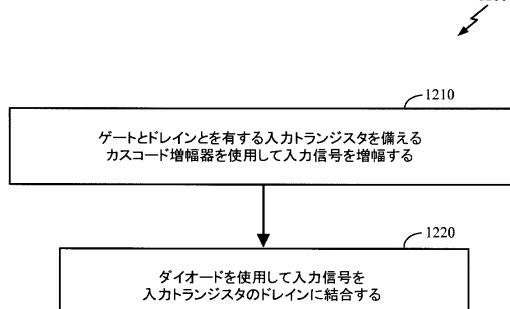

【図12】[0017]本開示による方法の例示的な実施形態を示す図。

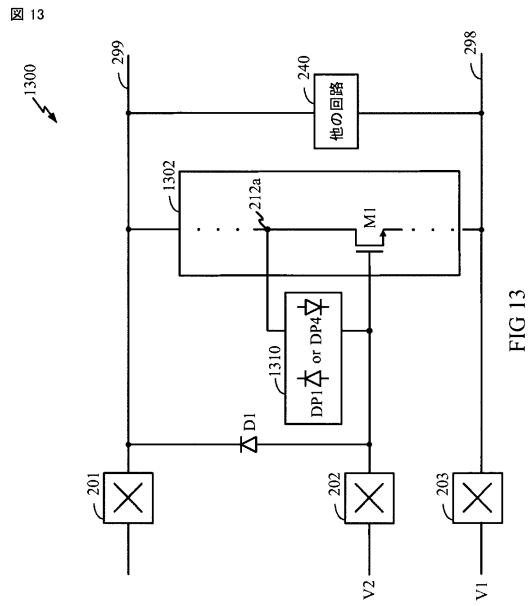

【図13】[0018]本開示による装置の例示的な実施形態を示す図。

**【発明を実施するための形態】****【0007】**

[0019]添付の図面を参照しながら本開示の様々な態様について以下でより十分に説明する。ただし、本開示は、多くの異なる形態で実施され得、本開示全体にわたって提示する任意の特定の構造または機能に限定されるものと解釈されるべきではない。むしろ、これらの態様は、本開示が周到で完全になり、本開示の範囲を当業者に十分に伝えるために与

50

えるものである。本明細書の教示に基づいて、本開示の範囲は、本開示の他の態様とは無関係に実装されるにせよ、本開示の他の態様と組み合わされるにせよ、本明細書で開示する本開示のいかなる態様をもカバーするものであることを、当業者は諒解されたい。たとえば、本明細書に記載する態様をいくつ使用しても、装置は実装され得、または方法は実施され得る。さらに、本開示の範囲は、本明細書に記載する本開示の様々な態様に加えてまたはそれらの態様以外に、他の構造、機能、または構造および機能を使用して実施されるそのような装置または方法をカバーするものとする。本明細書で開示する本開示のいずれの態様も、請求項の1つまたは複数の要素によって実施され得ることを理解されたい。

#### 【0008】

[0020]添付の図面に関して以下に記載する発明を実施するための形態は、本発明の例示的な態様を説明するものであり、本発明が実施され得る例示的な様態のみを表すものではない。この明細書全体にわたって使用する「例示的」という用語は、「例、事例、または例示の働きをすること」を意味し、必ずしも他の例示的な態様よりも好ましいまたは有利であると解釈されるべきではない。発明を実施するための形態は、本発明の例示的な態様の完全な理解を与える目的で具体的な詳細を含む。本発明の例示的な態様はこれらの具体的な詳細なしに実施され得ることが当業者には明らかであろう。いくつかの例では、本明細書で提示する例示的な態様の新規性を不明瞭にしないように、よく知られている構造およびデバイスをブロック図の形式で示す。本明細書および特許請求の範囲において、「モジュール」および「ブロック」という用語は、説明する動作を実行するように構成されたエンティティを示すために互換的に使用され得る。10

#### 【0009】

[0021]図1に、本開示の技法が実装され得る従来技術のワイヤレス通信デバイス100の設計のブロック図を示す。図1は、例示的なトランシーバ設計を示す。概して、送信機および受信機における信号の調整は、増幅器、フィルタ、アップコンバータ、ダウンコンバータなどの1つまたは複数の段によって実行され得る。これらの回路ブロックは、図1に示す構成とは異なって構成され得る。さらに、図1に示されていない他の回路ブロックも送信機および受信機において信号を調整するために使用され得る。別段に記載されていない限り、図1、または図面中の他の図中のいかなる信号もシングルエンドまたは差動のいずれかであり得る。また、図1中のいくつかの回路ブロックが省略され得る。20

#### 【0010】

[0022]図1に示された設計では、ワイヤレスデバイス100はトランシーバ120とデータプロセッサ110とを含む。データプロセッサ110は、データとプログラムコードとを記憶するためのメモリ(図示せず)を含み得る。トランシーバ120は、双方向通信をサポートする送信機130と受信機150とを含む。概して、ワイヤレスデバイス100は、任意の数の通信システムと周波数帯域とのための任意の数の送信機および/または受信機を含み得る。トランシーバ120の全部または一部分が、1つまたは複数のアナログ集積回路( I C )、無線周波数( R F ) I C、混合信号 I Cなどの上に実装され得る。30

#### 【0011】

[0023]送信機または受信機は、スーパーへテロダインアーキテクチャまたは直接変換アーキテクチャを用いて実装され得る。スーパーへテロダインアーキテクチャでは、信号が、受信機のために、複数の段において R F とベースバンドとの間で、たとえば、1つの段において R F から中間周波数( I F )に、次いで別の段において I F からベースバンドに周波数変換される。直接変換アーキテクチャでは、信号が1つの段において R F とベースバンドとの間で周波数変換される。スーパーへテロダインアーキテクチャおよび直接変換アーキテクチャは、異なる回路ブロックを使用し、および/または異なる要件を有し得る。図1に示された設計では、送信機130および受信機150は、直接変換アーキテクチャを用いて実装される。40

#### 【0012】

[0024]送信経路では、データプロセッサ110は、送信されるべきデータを処理し、送信機130に I および Q アナログ出力信号を与える。図示の例示的な実施形態では、デー50

タブロセッサ 110 は、データプロセッサ 110 によって生成されたデジタル信号をさらなる処理のために I および Q アナログ出力信号、たとえば、I および Q 出力電流に変換するためのデジタルアナログ変換器 (D A C) 114a および 114b を含む。

#### 【0013】

[0025] 送信機 130 内で、ローパスフィルタ 132a および 132b は、前のデジタルアナログ変換によって生じた望ましくないイメージを除去するために、それぞれ、I および Q アナログ出力信号をフィルタ処理する。増幅器 (Amp) 134a および 134b は、それぞれ、ローパスフィルタ 132a および 132b からの信号を増幅し、I および Q ベースバンド信号を与える。ミキサ 141a および 141b を含むアップコンバータ 140 が、送信 (T X) 局部発振 (L O) 信号生成器 190 からの I および Q T X L O 信号を用いて I および Q ベースバンド信号をアップコンバートし、アップコンバートされた信号を与える。フィルタ 142 は、周波数アップコンバージョンによって生じた望ましくないイメージならびに受信周波数帯域中の雑音を除去するために、アップコンバートされた信号をフィルタ処理する。電力増幅器 (P A) 144 は、所望の出力電力レベルを取得するためにフィルタ 142 からの信号を増幅し、送信 R F 信号を与える。送信 R F 信号は、デュプレクサまたはスイッチ 146 を通してルーティングされ、アンテナ 148 を介して送信される。

10

#### 【0014】

[0026] 受信経路では、アンテナ 148 は、基地局によって送信された信号を受信し、受信 R F 信号を与え、受信 R F 信号は、デュプレクサまたはスイッチ 146 を通してルーティングされ、低雑音増幅器 (L N A) 152 に与えられる。デュプレクサ 146 は、R X 信号が T X 信号から分離されるように、特定の R X - T X デュプレクサ周波数分離を用いて動作するように設計される。受信 R F 信号は、L N A 152 によって増幅され、所望の R F 入力信号を取得するためにフィルタ 154 によってフィルタ処理される。ダウンコンバージョンミキサ 161a および 161b は、I および Q ベースバンド信号を生成するために、フィルタ 154 の出力を、受信 (R X) L O 信号生成器 180 からの I および Q R X L O 信号 (すなわち、L O\_I および L O\_Q) と混合する。I および Q ベースバンド信号は、データプロセッサ 110 に与えられる I および Q アナログ入力信号を取得するために、増幅器 162a および 162b によって増幅され、ローパスフィルタ 164a および 164b によってさらにフィルタ処理される。図示の例示的な実施形態では、データプロセッサ 110 は、I および Q アナログ入力信号を、データプロセッサ 110 によってさらに処理されるべきデジタル信号に変換するためのアナログデジタル変換器 (A D C) 116a および 116b を含む。

20

30

#### 【0015】

[0027] 図 1 では、T X L O 信号生成器 190 は、周波数アップコンバージョンのために使用される I および Q T X L O 信号を生成し、R X L O 信号生成器 180 は、周波数ダウンコンバージョンのために使用される I および Q R X L O 信号を生成する。各 L O 信号は、特定の基本周波数をもつ周期信号である。P L L 192 は、データプロセッサ 110 からタイミング情報を受信し、L O 信号生成器 190 からの T X L O 信号の周波数および / または位相を調整するために使用される制御信号を生成する。同様に、P L L 182 は、データプロセッサ 110 からタイミング情報を受信し、L O 信号生成器 180 からの R X L O 信号の周波数および / または位相を調整するために使用される制御信号を生成する。

40

#### 【0016】

[0028] L N A 152 および P A 144 は、I C の外部のノードにインターフェースする入力 / 出力 (I / O) 端子を組み込み得るので、そのような回路ブロックは、外部環境からの、場合によっては大きい電位にさらされ、損傷を受けやすくなり得る。たとえば、製造またはテスト中などの、たとえば、取扱者または工業機器との接触により、かなりの量の静電荷が、たとえば、摩擦、誘導などにより、電子デバイス中に堆積することがある。そのような帶電電子デバイスが放電経路に接触するとき、電子デバイスを通して電流

50

のサージが生成され、デバイスの突発故障 (catastrophic failure) が潜在的に生じ得る。電流サージ現象はまた、帯電体が電子デバイスの近傍に入れられたときに発生し得、その場合、帯電体は電子デバイスを通して放電し、それにより、電子デバイスの構成要素に損傷を与える。

#### 【0017】

[0029]上記で説明したようなデバイス故障は、半導体製造およびテストのすべての段階において、ならびに電子デバイスがエンドユーザによって操作されているときのフィールドにおいてさえ発生し得る。したがって、最先端のRFおよびアナログIC製品を開発する際に、ESDに対する十分な保護ストラテジーが有用である。

#### 【0018】

[0030]図2に、入力／出力(I/O)パッドおよび回路を組み込んだ集積回路(IC)200の従来技術の実装形態を示す。図2は、説明の目的で示したものにすぎず、本開示の範囲を本明細書で開示する技法の特定の適用例に限定するものではないことに留意されたい。たとえば、ICは、概して、必ずしもIC200中に示されているとは限らない、追加のパッド、回路、リード線などを含み得る。

#### 【0019】

[0031]図2では、IC200はI/Oパッド201、202、および203を含む。パッド201は、外部から与えられた電源電圧(たとえば、VDD、図2に図示せず)をIC200の供給レール299に結合する。パッド202は、外部電圧V2を、IC200の入力、たとえば、IC200の増幅器入力端子に結合する。パッド203は外部電圧V1をIC200の接地端子に結合する。IC200は、増幅器210と、供給クランプ220と、他の回路240とをさらに含み、それらの機能については以下でさらに説明する。

#### 【0020】

[0032]図2では、増幅器210は、カスコードトポロジーを使用して実装される。特に、増幅器210は、ノード212aにおいて結合された入力トランジスタM1とカスコードトランジスタM2とを内蔵し、M1のゲートがパッド202に結合される。増幅器210は、M2のドレインに結合された負荷インダクタンスL2と、入力トランジスタM1のソースに結合されたソースインダクタンスL1とをさらに含む。図示されていない他の回路要素が増幅器210中にさらに存在し得ることに留意されたい。たとえば、直列インダクタンスおよび／または抵抗(図示せず)が入力トランジスタM1のゲートなどにさらに結合され得る。

#### 【0021】

[0033]さらに、増幅器210の上述の説明は、本開示の範囲をカスコード増幅器実装形態に限定するものではないことに留意されたい。たとえば、(たとえば、必ずしもカスコードトランジスタM2を含むとは限らない)任意の負荷に結合された入力トランジスタM1を有する共通ソース増幅器設計が本開示の技法を容易に利用し得る。さらに、いくつかの実装形態では、負荷インダクタンスL2は、差動ミキサ(図示せず)の入力を供給するためにトランスフォーマ構成の一部として別のインダクタ(図示せず)に相互結合され得る。代替実装形態では、増幅器210は、当技術分野で知られているLディジェネレートトポロジー(L-degenerated topology)を利用し得、その場合、ソースインダクタンスL1は削除され得、および／または整合のために1つまたは複数のシャント抵抗が追加され得る。さらなる代替実装形態では、ソースインダクタンスL1はトランスフォーマなどによって置き換えられ得る。本明細書で説明する技法は、そのような他の増幅器トポロジーにも適応するように容易に適合され得ることが諒解されよう。

#### 【0022】

[0034]IC200がESDに関係する仕様を満たすことを保証するために、テスト段階中に、いくつかのESDイベントに対するIC200の応答を決定するために、所定のテスト電圧がI/Oパッドの両端間に外部から印加され得る。特に、これらのテスト電圧は、ESD準拠を決定するための、当技術分野で知られている様々なモデル、たとえば、帯

電デバイスモデル（ C D M ）、人体モデル（ H B M ）、機械モデル（ M M ）などに従って生成され、印加され得る。たとえば、 C D M は、電子デバイスが（たとえば、摩擦帯電または誘導機構により）高い D C 電圧まで充電され、その後、場合によっては電子デバイスのピンのうちの 1 つに接触する接地導体の近傍に入るシナリオをエミュレートし得る。そのようなシナリオにより、電子デバイス内に（およびそのピンのすべてに）蓄積された電荷が、低インピーダンス経路を通って接地に至るピンを通して放電することがある。本開示の技法はまた、 C D M イベントのほかに（明示的に言及されていない）他のタイプの E S D イベントの保護を与え得ることが諒解されることに留意されたい。

#### 【 0 0 2 3 】

[0035] E S D イベントから I C 2 0 0 のクリティカル回路（たとえば、増幅器 2 1 0 、他の回路 2 4 0 など）を保護するために、クリティカル回路から離れて E S D 電流を分流するためにいくつかの保護要素が設けられ得る。たとえば、（たとえば、負の C D M イベントなど、 E S D テストイベント中に）かなりの過渡正電圧がデバイス M 1 および M 2 の両端間に生じた場合、それにより誘起された電流の大部分は、図 2 に経路 1 と標示された電流経路を通って分流され得る。たとえば、パッド 2 0 3 は、（たとえば、負の C D M テストイベントの場合）負電圧までまたは（たとえば、正の C D M テストの場合）正電圧まで充電され得、パッド 2 0 2 は接地に結合され得る。得られた過渡電流は、デバイス M 1 および M 2 の両端間で大きい過渡電圧を生成し得る。特に、電流 I 1 は、経路 1 を流れ、 V 2 からパッド 2 0 2 を通って、ダイオード D 1 、供給レール 2 9 9 、供給レール 2 9 9 を接地 2 9 8 に結合する（場合によっては双方向）供給クランプ 2 2 0 、接地レール 2 9 8 を通って、パッド 2 0 3 を介して V 1 に戻り得る。経路 1 は低インピーダンスを有するように設計されているので、 E S D イベントに関連する電流の大部分は経路 1 を通って分流され、それにより、 I C 2 0 0 のクリティカル回路をある程度まで保護することになる。

#### 【 0 0 2 4 】

[0036] しかしながら、実際には、たとえば、導電経路の残差直列インピーダンス、供給レールおよび / または接地レール、供給クランプおよび / または他の直列保護回路などにより、大きい寄生インダクタンスおよび / または抵抗が経路 1 の両端間に存在し得る。そのような大きい直列インダクタンスにより、たとえば、オーミック電圧降下に起因する、かなりの電圧が M 1 および M 2 の端子の両端間に生じ得ることが諒解されよう。この大きい電圧降下は、特に、最先端のトランジスタプロセスを特徴づける低い破壊電圧を仮定すれば、ダイオード D 1 および供給クランプ 2 2 0 が設けられたときでも、 I C 2 0 0 のクリティカル回路に望ましくなく損傷を与える。たとえば、 6 5 n m プロセスを使用して作製された一般的なトランジスタは 7 V の破壊電圧をサポートし得るが、 2 8 n m プロセスを使用して作製されたトランジスタは 5 V のみの破壊電圧をサポートすることが可能であり得る。）例示的な実施形態では、破壊電圧は、デバイスのゲートソース接合またはドレインソース接合が、損傷されることなしに維持し得る、電圧に対応し得る。

#### 【 0 0 2 5 】

[0037] さらに、いくつかのトランシーバ実装形態では、トランシーバ入力（たとえば、受信部分の増幅器 2 1 0 への入力）は、トランシーバの送信部分から発生する強い信号にさらされ得ることが諒解されよう。たとえば、いくつかの例示的な実施形態では、デバイスは、 G S M （登録商標）ネットワークのための送信（ T X ）と C D M A ネットワークのための受信（ R X ）とを同時にサポートし得る。この例示的な実施形態では、 G S M 送信機から C D M A 受信機への T X 電力漏れも C D M A 受信機への損傷を望ましく引き起こし得る。

#### 【 0 0 2 6 】

[0038] したがって、 I C 中のクリティカル回路に損傷を与える E S D イベントならびにいくつかの他の高電力イベントに効果的に対処するための新規でロバストな技法を提供することが望ましいであろう。

#### 【 0 0 2 7 】

10

20

30

40

50

[0039]図3に、上述の問題に対処するために（本明細書では「保護ダイオード」としても示される）ダイオードD P 1が設けられた、本開示によるICの例示的な実施形態300を示す。図3は、説明の目的で示したものにすぎず、本開示の範囲を図示の特定の例示的な実施形態に限定するものではないことに留意されたい。

#### 【0028】

[0040]図3では、ダイオードD P 1はM 1のゲートをそのドレインに結合する。図示の例示的な実施形態では、D P 1は、正電圧がM 1のゲートとドレインとの間に存在するとき、順方向バイアスされるようにさらに構成される。パッド202とパッド203との間に大きい正電圧V 2 - V 1 > > 0が生じたとき、図2の経路1を通って最初に分流された電流I 1の一部分が、代わりに、D P 1を通ってM 1のドレイン、またはノード212aに分流される。ノード212aから、分流された電流は、さらに、いくつかの経路を通って、たとえば、M 1のドレインソースチャネルを通して、M 1の基板を通ってなど、接地レール298にリダイレクトされ得る。このようにして、経路1を通る電流が相応して低減されるので、V 2とV 1との間のオーミック電圧降下も低減されることが予想され、したがってデバイスM 1およびM 2に対する電圧応力が低下する。10

#### 【0029】

[0041]1つの保護ダイオードD P 1が図3に示されているが、代替の例示的な実施形態は、M 1のゲートとそのドレインとの間で直列に任意の別の数のダイオードを組み込み得ることに留意されたい。複数の直列結合されたダイオードは、有利には、ESD保護機構の関連するターンオン電圧を増加させ、それにより、デバイスの通常動作中に保護ダイオードの偶発的順方向バイアスを防ぎ（またはその可能性を低減し）得ることが諒解されよう。20

#### 【0030】

[0042]ダイオードD P 1、および／または以下で説明する他のダイオードの機能を実装するための様々な技法が当技術分野で知られていることを当業者は諒解されよう。たとえば、接合ダイオード、ゲート型ダイオード、シリコン制御整流器、およびショットキーダイオードなどのうちのいずれかが使用され得る。そのような代替の例示的な実施形態は本開示の範囲内に入ることが企図される。

#### 【0031】

[0043]M 1のドレインを通ってそのソースに至る分流経路を与えることのさらなる利点は、追加の電流がM 1のソースを流れることにより、M 1のソース電圧が増加することが予想され、したがってM 1のゲートソース間電圧が減少することが諒解されよう。この影響は、有利には、M 1のゲートソース接合にかけられる応力を低減し得る。30

#### 【0032】

[0044]図4に、追加の抵抗器R P 1を組み込んだ、本開示によるIC400の代替の例示的な実施形態を示す。図4は、説明の目的で示したものにすぎず、本開示の範囲を図示の特定の例示的な実施形態に限定するものではないことに留意されたい。図4では、抵抗器R P 1はD P 1と直列に設けられる。いくつかの例示的な実施形態では、R P 1をD P 1と直列に設けることは、D P 1を通過する電流を低減し、したがって、D P 1のサイズが低減されることが可能になり得ることが諒解されよう。したがって、これは、有利には、たとえば、M 1への入力において、そのようなダイオードに関連する寄生要素（たとえば、キャパシタンスまたは抵抗）のサイズを低減し得る。40

#### 【0033】

[0045]いくつかの例示的な実施形態では、R P 1は、D P 1と直列の明示的に設けられた抵抗要素に対応する必要がないことが諒解されよう。代わりに、R P 1は、図示の様式でD P 1が設けられたときに存在する固有の直列抵抗を単にモデル化することが理解され得る。さらに、R P 1などの明示的または暗黙的抵抗が、概して、本開示で説明および／または図示するダイオードのうちのいずれかと直列に配置され得ることが諒解されよう。そのような例示的な実施形態は本開示の範囲内に入ることが企図される。

#### 【0034】

50

20

30

40

50

[0046]図5に、複数の保護ダイオードを組み込んだ、本開示によるICの代替の例示的な実施形態500を示す。図5は、説明の目的で示したものにすぎず、本開示の範囲を図示の特定の例示的な実施形態に限定するものではないことに留意されたい。

#### 【0035】

[0047]図5では、ダイオードDP2がダイオードDP3と直列に設けられ、共同でM1のドレインまたはノード212aを接地に結合する。DP2およびDP3は、かなりの正電圧がM1のドレインと接地との間に存在するとき、順方向バイアスされるように構成される。特に、大きい正電圧V2-V1がパッド202とパッド203との間に存在するとき、経路1に関連する電流の一部が、ノード212aに分流され、DP2およびDP3、接地レール298を通って、パッド203を介してV1に戻る。このようにして、パッド202とパッド203との間の持続するオーミック電圧降下が低減されることが予想される。10

#### 【0036】

[0048]図5では、直列に結合された2つの保護ダイオードDP2およびDP3が示されているが、代替の例示的な実施形態は、概して、図、たとえば、図5ならびに他の図において、本明細書で示すダイオードの代用として直列に任意の複数のダイオードを組み込み得ることに留意されたい。複数の直列結合されたダイオードは、有利には、ESD保護機構の関連するターンオン電圧を増加させ、それにより、デバイスの通常動作中に保護ダイオードの偶発的順方向バイアスを防ぎ（またはその可能性を低減し）得ることが諒解されよう。20

#### 【0037】

[0049]図6に、本開示の複数の技法を組み込んだ、本開示によるICの代替の例示的な実施形態600を示す。例示的な実施形態600は、説明の目的で示したものにすぎず、本開示の範囲を限定するものではないことに留意されたい。代替の例示的な実施形態は、図6に示されている技法の任意のサブセットまたは組合せを組み込み得、そのような代替の例示的な実施形態は本開示の範囲内に入ることが企図される。20

#### 【0038】

[0050]図6では、DP1およびRP1はM1のゲートをそのドレインに結合し、DP2およびDP3は共同でM1のドレインを接地に結合する。例示的な実施形態600に適用される技法の動作原理は、図4～図5に関する上記での説明に照らして明らかになり、したがって、それらの説明は以下で省略されることが諒解されよう。30

#### 【0039】

[0051]図7に、入力／出力（I/O）パッドおよび回路を組み込んだ集積回路（IC）700の代替の従来技術の実装形態を示す。図2および図7中の同様に標示された要素は、同様の機能を有する要素に対応し、したがって、それらの説明は以下で省略されることに留意されたい。

#### 【0040】

[0052]図7では、IC700は、前に図2のIC200に関して上記で説明した、I/Oパッド201、202、203と、カスコード増幅器210と、供給クランプ220と、他の回路240とを含む。IC700は、M1のゲートを接地レール298に結合するダイオードD2をさらに含む。大きい負電圧（たとえば、V2-V1<<0）がM1のゲートと接地レール298（または、それぞれパッド202とパット203）との間に存在するとき、D2は、順方向バイアスされるように構成される。（たとえば、正のCDMイベントなど、ESDテストイベント中に）かなりの過渡負電圧がパッド202および203の両端間に印加された場合、それにより誘起された電流の大部分は、図7に経路2と標示された電流経路を通って分流される。特に、電流は、経路2を流れ、V1からパッド203を通って、D2を通って、パッド202を介してV2に戻る。経路2は低インピーダンスを有するように設計されているので、ESDイベントに関連する電流の大部分は経路2を通って分流され、それにより、IC700のクリティカル回路（たとえば、増幅器210および他の回路240）をある程度まで保護することになる。4050

**【 0 0 4 1 】**

[0053]しかしながら、実際には、経路 2 における大きい寄生直列インダクタンス（図 7 に図示せず）により、大きい電圧が M 1 の両端間に生じ得、それにより、V 2 と V 1 との間で相応して大きい（負の）オーミック電圧降下が生じ得る。この大きい負の電圧降下は、D 2 が設けられたときでも、I C 7 0 0 のクリティカル回路に望ましくなく損傷を与える。たとえば、M 1 のゲートソース接合は、そのような大きい負の電圧降下の存在下で故障し得る。さらに、かなりの負電圧が存在するとき、それにより生成された電流の一部がインダクタンス L 2 を通って分流され、それにより、M 2 および / または M 1 のドレインに潜在的に損傷を与えることがある L 2 の両端間の電圧応答におけるかなりのリンクギングが生じ得る。

10

**【 0 0 4 2 】**

[0054]図 8 に、保護ダイオード D P 4 が設けられた、本開示による I C の例示的な実施形態 8 0 0 を示す。図 8 は、説明の目的で示したものにすぎず、本開示の範囲を図示の特定の例示的な実施形態に限定するものではないことに留意されたい。

**【 0 0 4 3 】**

[0055]図 8 では、保護ダイオード D P 4 は M 1 のドレインをそのゲートに結合する。図示の例示的な実施形態では、D P 4 は、正電圧が M 1 のドレインとゲートとの間に存在するとき、順方向バイアスされるように構成される。D P 4 は、有利には、M 1 のドレインにおける電圧スイングを制限し、したがって M 1 に対する電圧応力が低減することが諒解されよう。

20

**【 0 0 4 4 】**

[0056]1 つの保護ダイオード D P 4 が図 8 に示されているが、代替の例示的な実施形態は、M 1 のドレインとそのゲートとの間で直列に任意の数のダイオードを組み込み得ることに留意されたい。複数の直列結合されたダイオードは、有利には、E S D 保護機構の関連するターンオン電圧を増加させ、それにより、デバイスの通常動作中に保護ダイオードの偶発的順方向バイアスを防ぎ（またはその可能性を低減し）得ることが諒解されよう。たとえば、図 9 に、2 つの直列結合されたダイオード D P 4 . 1 および D P 4 . 2 が設けられた、本開示による I C 9 0 0 の代替の例示的な実施形態を示す。そのような代替の例示的な実施形態は本開示の範囲内に入ることが企図される。

**【 0 0 4 5 】**

30

[0057]図 1 0 に、本開示のさらなる技法を組み込んだ I C 1 0 0 0 の代替の例示的な実施形態を示す。図 1 0 では、直列結合された保護ダイオード D P 4 . 1 および D P 4 . 2 は M 1 のドレインをそのゲートに結合し、保護ダイオード D P 5 は M 1 のソースをそのゲートにさらに結合する。D P 5 は、パッド 2 0 2 とパッド 2 0 3 との間の可能な負電圧のための代替の分流経路を与え、したがって、I C 1 0 0 0 のクリティカル回路の追加の保護を与えることに留意されたい。

**【 0 0 4 6 】**

[0058]特に、D P 5 は、正電圧が M 1 のソースとゲートとの間に存在するとき、順方向バイアスされるように構成される。大きい負電圧 V 2 - V 1 << 0 がパッド 2 0 2 とパッド 2 0 3 との間に印加されたとき、最初に D 2 を通って分流された電流 I 2 の一部は、代わりに、D P 5 を通って、たとえば、接地レール 2 9 8 から、D P 5 を通って分流され、パッド 2 0 2 を介して V 2 に戻る。このようにして、D 2 を通る電流が低減されるので、V 2 と V 1 との間のオーミック電圧降下も低減され得る。

40

**【 0 0 4 7 】**

[0059]I C 1 0 0 0 中の D P 4 . 1 と D P 4 . 2 と D P 5 との組合せは、有利には、2 つの並列分流経路（たとえば、M 1 のソースを通じてそのゲートに至る 1 つの分流経路、および M 1 のドレインを通じてそのゲートに至る 1 つの分流経路）を与えることが諒解されよう。したがって、たとえば、正の C D M イベントに対処するとき、I C 1 0 0 0 のために、より大きい E S D 保護が与えられる。

**【 0 0 4 8 】**

50

[0060]図11に、本開示の複数の技法を組み込んだ、本開示によるICの代替の例示的な実施形態1100を示す。例示的な実施形態1100は、説明の目的で示したものにすぎず、本開示の範囲を限定するものではないことに留意されたい。代替の例示的な実施形態は、図11に示されている技法の任意のサブセットを組み込み得、そのような代替の例示的な実施形態は本開示の範囲内に入ることが企図される。

#### 【0049】

[0061]図11では、DP1およびRP1はM1のゲートをそのドレインに結合し、DP2およびDP3は共同でM1のドレインを接地に結合する。図11にさらに示されているように、DP4.1およびDP4.2は共同でM1のドレインをそのゲートに結合し、DP5はM1のソースをそのゲートに結合する。例示的な実施形態1100に適用される上述の技法のいくつかの動作原理は、本開示の他の図に関する上記での説明に照らして明らかになり、したがって、それらの説明は以下で省略されることが諒解されよう。

10

#### 【0050】

[0062]図12に、本開示による方法の例示的な実施形態を示す。図12は、説明の目的で示したものにすぎず、本開示の範囲を図示の特定の方法に限定するものではないことに留意されたい。

#### 【0051】

[0063]図12では、ブロック1210において、ゲートとドレインとを有する入力トランジスタを備えるカスコード増幅器を使用して入力信号を増幅する。

20

#### 【0052】

[0064]ブロック1220において、ダイオードを使用して入力信号を入力トランジスタのドレインに結合する。

#### 【0053】

[0065]図13に、本開示による装置1300の例示的な実施形態を示す。本明細書の図13および他の図中の同様に標示された要素は、概して、別段に記載されていない限り、同様の機能を実行する要素に対応し得ることに留意されたい。

#### 【0054】

[0066]図13では、増幅器1302は入力トランジスタM1を含む。M1のドレインに潜在的に結合された要素は図13に明示的に示されていないが、そのような要素が、たとえば、1つまたは複数のカスコードトランジスタ、負荷などを含み得ることを当業者は諒解することに留意されたい。同様に、M1のソースに潜在的に結合された要素は図13に明示的に示されていないが、そのような要素が、たとえば、1つまたは複数のソースディジェネレーションインダクタなどを含み得ることを当業者は諒解されよう。そのような例示的な実施形態は本開示の範囲内に入ることが企図される。

30

#### 【0055】

[0067]図13では、ダイオードブロック1310は入力トランジスタM1のゲートをドレインに結合する。例示的な実施形態では、ダイオードブロック1310は、図3に示されたダイオードDP1、たとえば、ゲートドレイン間電圧が正であるとき、順方向バイアスされるように構成されたダイオードに対応し得る。代替の例示的な実施形態では、ダイオードブロック1310は、図8に示されたダイオードDP4、たとえば、ドレインゲート間電圧が正であるとき、順方向バイアスされるように構成されたダイオードに対応し得る。ダイオードブロック1310は、前に上記で説明したように、示されたダイオードDP1またはDP4のほかに他の要素、たとえば、直列結合された抵抗器または複数のダイオードを含み得ることに留意されたい。

40

#### 【0056】

[0068]本明細書および特許請求の範囲において、ある要素が別の要素に「接続」または「結合」されていると言及されるとき、その要素はその別の要素に直接接続または結合され得るか、あるいは介在要素が存在し得ることを理解されよう。対照的に、ある要素が別の要素に「直接接続」または「直接結合」されていると言及されるとき、介在要素は存在しない。さらに、ある要素が別の要素に「電気的に結合」されていると言及されるとき、

50

それは、そのような要素間に低抵抗の経路が存在することを示し、ある要素が別の要素に単に「結合」されていると言及されるとき、そのような要素間に低抵抗の経路があることもないこともある。

#### 【0057】

[0069]情報および信号は多種多様な技術および技法のいずれかを使用して表され得ることを、当業者は理解されよう。たとえば、上記の説明全体にわたって言及され得るデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁界または磁性粒子、光場または光学粒子、あるいはそれらの任意の組合せによって表され得る。

#### 【0058】

[0070]さらに、本明細書で開示した例示的な態様に関して説明した様々な例示的な論理ブロック、モジュール、回路、およびアルゴリズムステップは、電子ハードウェア、コンピュータソフトウェア、または両方の組合せとして実装され得ることを、当業者は諒解されよう。ハードウェアとソフトウェアのこの互換性を明確に示すために、様々な例示的な構成要素、ブロック、モジュール、回路、およびステップについて、上記では概してこれらの機能に関して説明した。そのような機能をハードウェアとして実装するか、ソフトウェアとして実装するかは、特定の適用例および全体的なシステムに課される設計制約に依存する。当業者は、説明した機能を特定の適用例ごとに様々な方法で実装し得るが、そのような実装の決定は、本発明の例示的な態様の範囲からの逸脱を生じるものと解釈されるべきではない。

10

#### 【0059】

[0071]本明細書で開示した例示的な態様に関して説明した様々な例示的な論理ブロック、モジュール、および回路は、汎用プロセッサ、デジタル信号プロセッサ（DSP）、特定用途向け集積回路（ASIC）、フィールドプログラマブルゲートアレイ（FPGA）または他のプログラマブル論理デバイス、個別ゲートまたはトランジスタ論理、個別ハードウェア構成要素、あるいは本明細書で説明する機能を実行するように設計されたこれらの任意の組合せを用いて実装または実行され得る。汎用プロセッサはマイクロプロセッサであり得るが、代替として、プロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、または状態機械であり得る。プロセッサはまた、コンピューティングデバイスの組合せ、たとえば、DSPとマイクロプロセッサとの組合せ、複数のマイクロプロセッサ、DSPコアと連携する1つまたは複数のマイクロプロセッサ、あるいは任意の他のそのような構成として実装され得る。

20

#### 【0060】

[0072]本明細書で開示した例示的な態様に関して説明した方法またはアルゴリズムのステップは、ハードウェアで直接実施されるか、プロセッサによって実行されるソフトウェアモジュールで実施されるか、またはその2つの組合せで実施され得る。ソフトウェアモジュールは、ランダムアクセスメモリ（RAM）、フラッシュメモリ、読み取り専用メモリ（ROM）、電気的プログラマブルROM（EPROM）、電気的消去可能プログラマブルROM（EEPROM（登録商標））、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野で知られている任意の他の形態の記憶媒体中に常駐し得る。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取り、記憶媒体に情報を書き込むことができるよう、プロセッサに結合される。代替として、記憶媒体はプロセッサと一緒に得る。プロセッサおよび記憶媒体はASIC中に常駐し得る。ASICはユーザ端末中に常駐し得る。代替として、プロセッサおよび記憶媒体は、ユーザ端末中に個別構成要素として常駐し得る。

30

#### 【0061】

[0073]1つまたは複数の例示的な態様では、説明した機能は、ハードウェア、ソフトウェア、ファームウェア、またはそれらの任意の組合せで実装され得る。ソフトウェアで実装される場合、機能は、1つまたは複数の命令またはコードとしてコンピュータ可読媒体上に記憶されるか、あるいはコンピュータ可読媒体を介して送信され得る。コンピュータ

40

50

可読媒体は、ある場所から別の場所へのコンピュータプログラムの転送を可能にする任意の媒体を含む、コンピュータ記憶媒体とコンピュータ通信媒体の両方を含む。記憶媒体は、コンピュータによってアクセスされ得る任意の利用可能な媒体であり得る。限定ではなく例として、そのようなコンピュータ可読媒体は、RAM、ROM、EEPROM、CD-ROMまたは他の光ディスクストレージ、磁気ディスクストレージまたは他の磁気ストレージデバイス、あるいは命令またはデータ構造の形態の所望のプログラムコードを搬送または記憶するために使用され得、コンピュータによってアクセスされ得る、任意の他の媒体を備えることができる。また、いかなる接続もコンピュータ可読媒体と適切に呼ばれる。たとえば、ソフトウェアが、同軸ケーブル、光ファイバーケーブル、ツイストペア、デジタル加入者回線(DSL)、または赤外線、無線、およびマイクロ波などのワイヤレス技術を使用して、ウェブサイト、サーバ、または他のリモートソースから送信される場合、同軸ケーブル、光ファイバーケーブル、ツイストペア、DSL、または赤外線、無線、およびマイクロ波などのワイヤレス技術は、媒体の定義に含まれる。本明細書で使用するディスク(disk)およびディスク(disc)は、コンパクトディスク(disc)(CD)、レーザーディスク(登録商標)(disc)、光ディスク(disc)、デジタル多用途ディスク(disc)(DVD)、フロッピー(登録商標)ディスク(disk)、およびBlu-Ray(登録商標)ディスク(disc)を含み、ディスク(disk)は、通常、データを磁気的に再生し、ディスク(disc)は、データをレーザーで光学的に再生する。上記の組合せもコンピュータ可読媒体の範囲内に含まれるべきである。

## 【0062】

[0074]開示した例示的な態様の前述の説明は、当業者が本発明を実施または使用することができるように与えたものである。これらの例示的な態様への様々な修正は当業者には容易に明らかであり、本明細書で定義した一般原理は、本発明の趣旨または範囲から逸脱することなく他の例示的な態様に適用され得る。したがって、本開示は、本明細書で示した例示的な態様に限定されるものではなく、本明細書で開示した原理および新規の特徴に一致する最も広い範囲を与えられるべきである。

以下に本願の出願当初の特許請求の範囲に記載された発明を付記する。

[C1] 入力トランジスタを備える増幅器と、

前記入力トランジスタのドレインにゲートを結合するダイオードとを備える装置。

[C2] 前記ダイオードは、ゲートドレイン間電圧が正であるとき、順方向バイアスされるように構成された、C1に記載の装置。

[C3] 第1の集積回路パッドと第2の集積回路パッドとをさらに備え、ここにおいて、前記第1の集積回路パッドが前記入力トランジスタの前記ゲートに結合され、前記第2の集積回路パッドが前記入力トランジスタのソースに結合された、C1に記載の装置。

[C4] 前記ダイオードと直列に結合された抵抗器をさらに備える、C1に記載の装置。

[C5] 前記入力トランジスタの前記ドレインに結合されたカスコードトランジスタをさらに備える、C1に記載の装置。

[C6] 前記入力トランジスタの前記ドレインを接地端子に結合する2つのダイオードをさらに備える、C1に記載の装置。

[C7] 前記ダイオードは、ドレンゲート間電圧が正であるとき、順方向バイアスされるように構成された、C1に記載の装置。

[C8] 前記ゲートドレイン間電圧が正であるとき、順方向バイアスされるように構成された、第2のダイオードをさらに備える、C7に記載の装置。

[C9] 前記ダイオードと直列に結合された第2のダイオードをさらに備える、C1に記載の装置。

[C10] 前記ドレインを前記ゲートに結合する第2のダイオードをさらに備え、前記第2のダイオードは、前記ドレンゲート間電圧が正であるとき、順方向バイアスされるように構成された、C2に記載の装置。

10

20

30

40

50

[ C 1 1 ] 入力信号を増幅するための手段を備える集積回路と、

前記集積回路の帶電デバイスモデル( C D M )性能を改善するための手段と

を備える装置。

[ C 1 2 ] C D M性能を改善するための前記手段が、正のC D M性能を改善するための

手段を備える、C 1 1に記載の装置。

[ C 1 3 ] 正のC D M性能を改善するための前記手段が、増幅するための前記手段のド

レインにゲートを結合するダイオードを備える、C 1 2に記載の装置。

[ C 1 4 ] C D M性能を改善するための前記手段が、負のC D M性能を改善するための

手段を備える、C 1 1に記載の装置。

[ C 1 5 ] 負のC D M性能を改善するための前記手段が、増幅するための前記手段のド

レインを接地端子に結合する少なくとも1つのダイオードを備える、C 1 1に記載の装置

。

[ C 1 6 ] ゲートとドレインとを有する入力トランジスタを備えるカスコード増幅器を

使用して入力信号を増幅することと、

ダイオードを使用して前記入力信号を前記入力トランジスタの前記ドレインに結合する

ことと

を備える方法。

[ C 1 7 ] 前記ダイオードは、ゲートドレイン間電圧が正であるとき、順方向バイアス

されるように構成された、C 1 6に記載の方法。

[ C 1 8 ] 前記ダイオードは、ドレンゲート間電圧が正であるとき、順方向バイアス

されるように構成された、C 1 6に記載の方法。

[ C 1 9 ] 前記入力トランジスタの前記ドレインを接地端子に結合すること

をさらに備える、C 1 6に記載の方法。

[ C 2 0 ] 第2のダイオードを使用して前記入力トランジスタのソースを前記入力信号

に結合すること

をさらに備える、C 1 6に記載の方法。

10

20

【図1】

【図2】

FIG 2

【図3】

【図4】

FIG 4

FIG 3

【図5】

図5

FIG 5

【図6】

図6

FIG 6

【図7】

図7

FIG 7

【図8】

図8

FIG 8

【図9】

図9

FIG 9

【図10】

図10

FIG 10

【図11】

図11

FIG 11

【図12】

図12

FIG 12

【図 1 3】

---

フロントページの続き

- (72)発明者 ユーセフ、アーメド・アブデル・モネン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

- (72)発明者 グデム、プラサド・スリニバサ・シバ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

- (72)発明者 チヤン、リ-チュン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

- (72)発明者 アブデル・ガーニー、エハブ・アーメド・ソビー<sup>1</sup>

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライ브 5775

審査官 棚田 一也

- (56)参考文献 特表2005-512377(JP,A)

米国特許出願公開第2011/0102081(US,A1)

特開2001-358297(JP,A)

米国特許出願公開第2007/0058308(US,A1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/822

H01L 27/04