(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4836985号

(P4836985)

(45) 発行日 平成23年12月14日(2011.12.14)

(24) 登録日 平成23年10月7日(2011.10.7)

(51) Int.Cl.

G O 1 C 19/56 (2006.01)

G O 1 P 15/125 (2006.01)

F 1

G O 1 C 19/56 276

G O 1 P 15/125 V

請求項の数 12 (全 19 頁)

(21) 出願番号 特願2008-98694 (P2008-98694)

(22) 出願日 平成20年4月4日 (2008.4.4)

(65) 公開番号 特開2009-250774 (P2009-250774A)

(43) 公開日 平成21年10月29日 (2009.10.29)

審査請求日 平成22年12月8日 (2010.12.8)

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100077931

弁理士 前田 弘

(74) 代理人 100110939

弁理士 竹内 宏

(74) 代理人 100110940

弁理士 嶋田 高久

(74) 代理人 100113262

弁理士 竹内 祐二

(74) 代理人 100115059

弁理士 今江 克実

(74) 代理人 100115691

弁理士 藤田 篤史

最終頁に続く

(54) 【発明の名称】物理量検出回路

## (57) 【特許請求の範囲】

## 【請求項 1】

外部から与えられた物理量に応じてセンサ信号を出力する物理量センサに用いられる物理量検出回路であって、

所定のサンプリング周波数を有するサンプリングクロックの位相を調整するサンプリング位相調整回路と、

前記サンプリング位相調整回路によって位相調整されたサンプリングクロックに同期して前記センサ信号をデジタルセンサ信号に変換するアナログ / デジタル変換回路と、

前記アナログ / デジタル変換回路によって得られたデジタルセンサ信号に基づいて前記物理量を検出する検出回路とを備え、

前記検出回路は、

前記センサ信号の周波数に対応する周波数を有する基準クロックの遷移に応答して正弦波信号に対応するデジタル検波信号を生成する検波信号生成回路と、

前記アナログ / デジタル変換回路によって得られたデジタルセンサ信号に前記検波信号生成回路によって生成されたデジタル検波信号を乗算することによって前記物理量に対応する物理量信号を検波する乗算回路とを含む

ことを特徴とする物理量検出回路。

## 【請求項 2】

請求項 1において、

前記サンプリング位相調整回路は、前記サンプリング周波数よりも高い周波数を有する

10

20

遅倍クロックに同期して動作し、前記サンプリングクロックを前記遅倍クロックの所定のパルス数だけ遅延させる

ことを特徴とする物理量検出回路。

**【請求項 3】**

請求項 2において、

前記サンプリング位相調整回路は、

前記遅倍クロックに同期して前記サンプリングクロックを順次シフトさせることにより複数の遅延クロックを生成するシフトレジスタと、

前記シフトレジスタによって生成された複数の遅延クロックのいずれか 1 つを選択するセレクタとを含み、

前記アナログ / デジタル変換回路は、前記セレクタによって選択された遅延クロックに同期してアナログ / デジタル変換を行う

ことを特徴とする物理量検出回路。

**【請求項 4】**

請求項 2において、

前記サンプリング位相調整回路は、

前記遅倍クロックの発生パルス数を計数し、発生パルス数が所定値に到達するとタイミング信号を生成するサンプリング位相調整カウンタと、

前記サンプリング位相調整カウンタからのタイミング信号の遷移エッジに応答して前記サンプリングクロックを生成するクロック生成回路とを含む

ことを特徴とする物理量検出回路。

**【請求項 5】**

請求項 4において、

前記クロック生成回路は、前記サンプリング位相調整カウンタからのタイミング信号の遷移エッジに応答して前記遅倍クロックを分周することによって前記サンプリングクロックを生成する分周回路である

ことを特徴とする物理量検出回路。

**【請求項 6】**

請求項 1において、

前記デジタル検波信号の位相を調整する第 1 の位相調整回路をさらに備える

ことを特徴とする物理量検出回路。

**【請求項 7】**

請求項 6において、

前記第 1 の位相調整回路は、前記基準クロックが供給されるとともに前記基準クロックの周波数よりも高い周波数を有する第 1 の動作クロックに同期して動作し、前記基準クロックの遷移エッジを前記第 1 の動作クロックの所定のパルス数だけ遅延させ、

前記検波信号生成回路は、前記第 1 の位相調整回路によって遅延された基準クロックの遷移エッジに応答して前記デジタル検波信号を生成する

ことを特徴とする物理量検出回路。

**【請求項 8】**

外部から与えられた物理量に応じてセンサ信号を出力する物理量センサに用いられる物理量検出回路であって、

所定のサンプリング周波数を有するサンプリングクロックの位相を調整するサンプリング位相調整回路と、

前記サンプリング位相調整回路によって位相調整されたサンプリングクロックに同期して前記センサ信号をデジタルセンサ信号に変換するアナログ / デジタル変換回路と、

前記デジタルセンサ信号の位相を調整するセンサ位相調整回路と、

前記センサ位相調整回路によって位相調整されたデジタルセンサ信号に基づいて前記物理量を検出する検出回路とを備え、

前記センサ位相調整回路は、前記アナログ / デジタル変換回路によって得られたデジタ

10

20

30

40

50

ルセンサ信号が供給されるとともに前記センサ信号の周波数よりも高い周波数を有する動作クロックに同期して動作し、前記デジタルセンサ信号を前記動作クロックの所定のパルス数だけ遅延させる

ことを特徴とする物理量検出回路。

**【請求項 9】**

外部から与えられた物理量に応じてセンサ信号を出力する物理量センサに用いられる物理量検出回路であって、

所定のサンプリング周波数を有するサンプリングクロックの位相を調整するサンプリング位相調整回路と、

前記サンプリング位相調整回路によって位相調整されたサンプリングクロックに同期して前記センサ信号をデジタルセンサ信号に変換するアナログ／デジタル変換回路と、

前記デジタルセンサ信号の位相を調整するセンサ位相調整回路と、

前記センサ位相調整回路によって位相調整されたデジタルセンサ信号に基づいて前記物理量を検出する検出回路とを備え、

前記サンプリング位相調整回路は、前記サンプリング周波数よりも高い周波数を有する遅倍クロックに同期して動作し、前記サンプリングクロックを前記遅倍クロックの所定のパルス数だけ遅延させる

ことを特徴とする物理量検出回路。

**【請求項 10】**

請求項9において、

20

前記サンプリング位相調整回路は、

前記遅倍クロックに同期して前記サンプリングクロックを順次シフトさせることにより複数の遅延クロックを生成するシフトレジスタと、

前記シフトレジスタによって生成された複数の遅延クロックのいずれか1つを選択するセレクタとを含み、

前記アナログ／デジタル変換回路は、前記セレクタによって選択された遅延クロックに同期してアナログ／デジタル変換を行う

ことを特徴とする物理量検出回路。

**【請求項 11】**

請求項9において、

30

前記サンプリング位相調整回路は、

前記遅倍クロックの発生パルス数を計数し、発生パルス数が所定値に到達するとタイミング信号を生成するサンプリング位相調整カウンタと、

前記サンプリング位相調整カウンタからのタイミング信号の遷移エッジに応答して前記サンプリングクロックを生成するクロック生成回路とを含む

ことを特徴とする物理量検出回路。

**【請求項 12】**

請求項11において、

前記クロック生成回路は、前記サンプリング位相調整カウンタからのタイミング信号の遷移エッジに応答して前記遅倍クロックを分周することによって前記サンプリングクロックを生成する分周回路である

ことを特徴とする物理量検出回路。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

この発明は、外部から与えられた物理量を検知する物理量センサに用いられる物理量検出回路およびそれを備える物理量センサ装置に関し、さらに詳しくは、センサ信号と検波信号との位相関係を調整する技術に関する。

**【背景技術】**

**【0002】**

40

50

従来より、物理量（例えば、角速度や加速度など）を検出可能な物理量センサ装置は、デジタルカメラの手ぶれ検出、移動体（航空機、自動車、ロボット、船舶など）の姿勢制御、ミサイルや宇宙船の誘導などの多種多様な技術分野において利用されている。

#### 【0003】

一般的に、物理量センサ装置は、外部から与えられた物理量に応じてセンサ信号を出力する物理量センサと、検波信号（センサ信号の周波数に対応する周波数を有する信号）を用いてセンサ信号から物理量信号（物理量に対応する信号）を検波する物理量検出回路とを備える。

#### 【0004】

近年、回路の微細化技術の発展により、物理量検出回路のデジタル化が進みつつある。

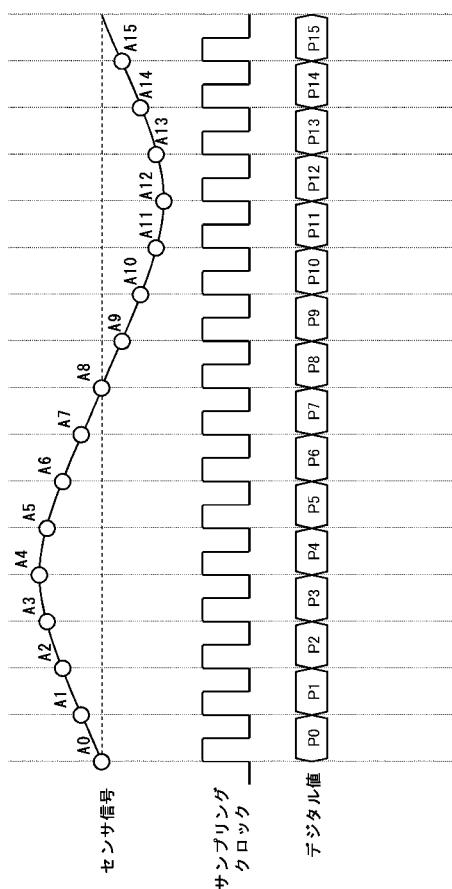

特許第2728300号公報（特許文献1）には、デジタル回路によって構成された2軸角速度・加速度センサの信号処理回路が開示されている。この信号処理回路では、アナログ／デジタル変換回路がセンサからセンサ信号をデジタルセンサ信号に変換する一方で、正弦波信号発生回路がデジタル正弦波信号を生成し、デジタル乗算回路がデジタルセンサ信号とデジタル正弦波信号とを乗算する。例えば、図17のように、アナログ／デジタル変換回路は、サンプリングクロックに同期して（すなわち、サンプリング周期毎に）センサ信号をサンプリングし、サンプリングしたセンサ信号のアナログ値（振幅値）A0, A1, A2, …をデジタル値P0, P1, P2, …に変換する。

#### 【0005】

また、物理量検出回路では、アナログ回路であってもデジタル回路であっても、センサ信号と検波信号とが互いに同期するようにセンサ信号と検波信号との位相関係を調整することが重要である。そのような位相調整技術は、特開平8-14916号公報（特許文献2）などに開示されている。特許文献2に開示された振動ジャイロは、感温素子（所定の温度特性を有する素子）を含む位相補正回路を備えることで、温度変化に起因する検波信号の位相ずれを補正する。

【特許文献1】特許2728300号公報

【特許文献2】特開平8-14916号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0006】

しかしながら、特許文献1に開示された信号処理回路では、アナログ／デジタル変換回路によって得られたデータ（デジタル値）を正確に処理するためには、デジタルセンサ信号のデータ単位でデジタルセンサ信号とデジタル正弦波信号との位相関係を調整する必要がある。すなわち、位相調整の分解能（最小単位）をアナログ／デジタル変換回路のサンプリング周期よりも小さくすることができない。そのため、位相調整の精度を向上させるためにはアナログ／デジタル変換回路のサンプリング周波数を高くしなければならないが、サンプリング周波数を高くする程、回路規模および消費電力が増大してしまう。

#### 【0007】

そこで、この発明は、サンプリング周波数の増加を抑制しつつ位相調整の精度を向上させることを目的とする。

#### 【課題を解決するための手段】

#### 【0008】

この発明の1つの局面に従うと、物理量検出回路は、外部から与えられた物理量に応じてセンサ信号を出力する物理量センサに用いられる物理量検出回路であって、所定のサンプリング周波数を有するサンプリングクロックの位相を調整するサンプリング位相調整回路と、上記サンプリング位相調整回路によって位相調整されたサンプリングクロックに同期して上記センサ信号をデジタルセンサ信号に変換するアナログ／デジタル変換回路と、上記アナログ／デジタル変換回路によって得られたデジタルセンサ信号に基づいて上記物理量を検出する検出回路とを備える。

#### 【0009】

10

20

30

40

50

上記物理量検出回路では、サンプリングクロックの位相を調整することにより、サンプリングポイント（サンプリングクロックの遷移エッジの位置）を移動させることができる。その結果、デジタルセンサ信号の位相を変更することができる。これにより、サンプリング周波数の増大を抑制しつつ位相調整の精度を向上させることができる。

#### 【0010】

好ましくは、上記サンプリング位相調整回路は、上記サンプリング周波数よりも高い周波数を有する遅倍クロックに同期して動作し、上記サンプリングクロックを上記遅倍クロックの所定のパルス数だけ遅延させる。

#### 【0011】

上記物理量検出回路では、遅倍クロックの周期を単位としてサンプリングクロックの位相を設定することができる。遅倍クロックの周波数が高い程、サンプリングクロックの位相を精密に設定することができる。これにより、デジタルセンサ信号の位相を精密に調整することができる。10

#### 【0012】

上記サンプリング位相調整回路は、上記遅倍クロックに同期して上記サンプリングクロックを順次シフトさせることにより複数の遅延クロックを生成するシフトレジスタと、上記シフトレジスタによって生成された複数の遅延クロックのいずれか1つを選択するセレクタとを含んでいても良い。上記アナログ／デジタル変換回路は、上記セレクタによって選択された遅延クロックに同期してアナログ／デジタル変換を行っても良い。このように構成することにより、サンプリングクロックを遅倍クロックの所定のパルス数だけ遅延させることができます。20

#### 【0013】

また、上記サンプリング位相調整回路は、上記遅倍クロックの発生パルス数を計数し、発生パルス数が所定値に到達するとタイミング信号を生成するサンプリング位相調整カウンタと、上記サンプリング位相調整カウンタからのタイミング信号の遷移エッジに応答して上記サンプリングクロックを生成するクロック生成回路とを含んでいても良い。このように構成することにより、サンプリングクロックを遅倍クロックの所定のパルス数だけ遅延させることができます。

#### 【0014】

この発明の別の局面に従うと、物理量検出方法は、外部から与えられた物理量検知する物理量センサからのセンサ信号に基づいて物理量を検出する方法であって、所定のサンプリング周波数を有するサンプリングクロックの位相を調整し、上記位相調整されたサンプリングクロックに同期して上記センサ信号をデジタルセンサ信号に変換し、上記デジタルセンサ信号に基づいて上記物理量を検出する。30

#### 【0015】

上記物理量検出回路では、サンプリングクロックの位相を調整することにより、サンプリングポイントを移動させることができる。その結果、デジタルセンサ信号の位相を変更することができる。これにより、サンプリング周波数の増大を抑制しつつ位相調整の精度を向上させることができる。

#### 【発明の効果】

#### 【0016】

以上のように、サンプリング周波数の増加を抑制しつつ位相調整の精度を向上させることができる。

#### 【発明を実施するための最良の形態】

#### 【0017】

以下、この発明の実施の形態を図面を参照して詳しく説明する。なお、図中同一または相当部分には同一の符号を付しその説明は繰り返さない。

#### 【0018】

(実施形態1)

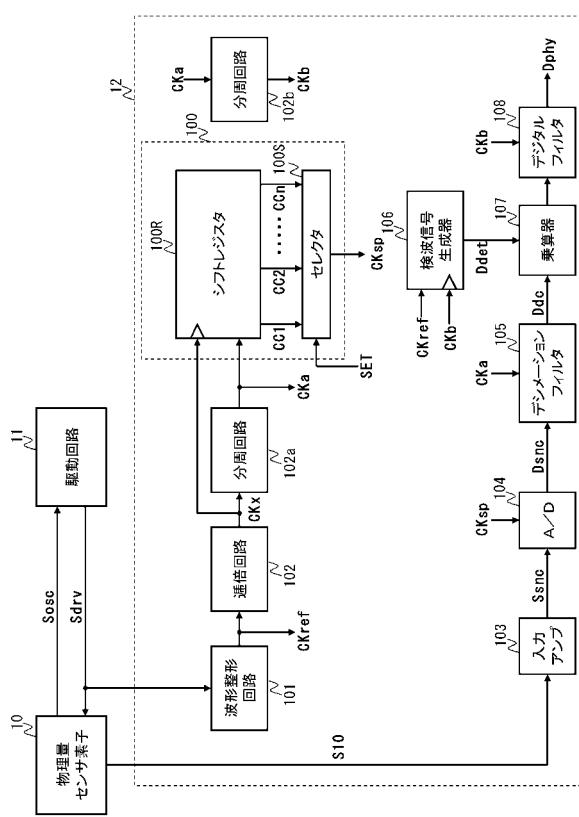

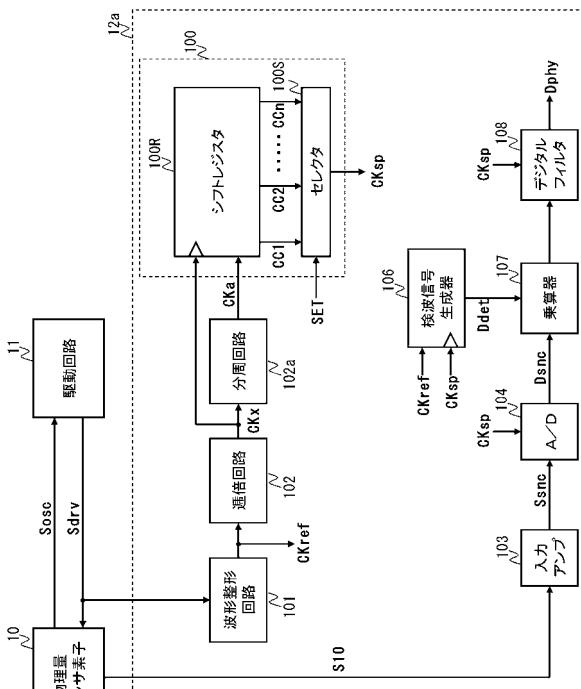

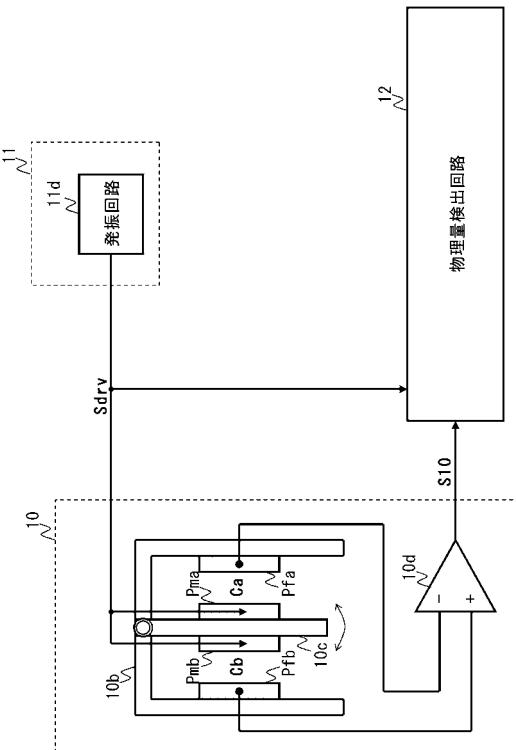

図1は、この発明の実施形態1による物理量センサ装置の構成を示す。物理量センサ装40

50

置は、物理量センサ 10 と、駆動回路 11 と、物理量検出回路 12 とを備える。

#### 【0019】

物理量センサ 10 は、所定周波数を有する駆動信号 S<sub>d r v</sub> が駆動回路 11 から供給されるとともに、外部から与えられた物理量（例えば、角速度、加速度など）に応じてセンサ信号 S<sub>10</sub> を出力する。センサ信号 S<sub>10</sub> の周波数は、駆動信号 S<sub>d r v</sub> の周波数に対応する。例えば、センサ信号 S<sub>10</sub> の中心周波数は、駆動信号 S<sub>d r v</sub> の周波数に相当する。なお、ここでは、物理量センサ 10 は、音叉型角速度センサであるものとする。駆動回路 11 は、駆動信号 S<sub>d r v</sub> を物理量センサ 10 に供給する。また、駆動回路 11 は、物理量センサ 10 からの振動信号 S<sub>o s c</sub> に応じて駆動信号 S<sub>d r v</sub> の周波数および振幅を調整する。物理量検出回路 12 は、物理量センサ 10 からのセンサ信号 S<sub>10</sub> に基づいて物理量を検出する。10

#### 【0020】

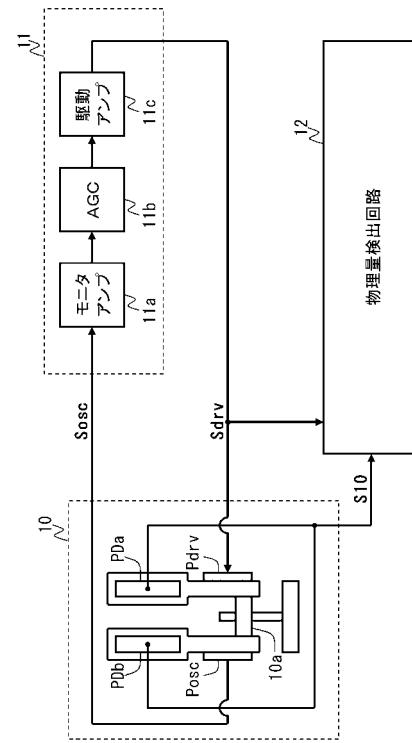

##### 〔物理量センサ〕

図 2 のように、物理量センサ 10 は、音叉本体 10a と、駆動用圧電素子 P<sub>d r v</sub> と、振動検出用圧電素子 P<sub>o s c</sub> と、角速度検出用圧電素子 P<sub>D a</sub>, P<sub>D b</sub> を有する。音叉本体 10a は、それぞれが中央部で直角にねじられた一対の音叉片（駆動用・検出用）と、音叉片の各々の一端を連結する連結部と、回転軸となるように連結部に設けられた支持ピンとを有する。駆動用圧電素子 P<sub>d r v</sub> は、駆動回路 11 からの駆動信号 S<sub>d r v</sub> の周波数および振幅に応じて駆動用の音叉片を振動させる。これにより、駆動用の音叉片と検出用の音叉片とが互いに共振する。この音叉振動によって、振動検出用圧電素子 P<sub>o s c</sub> には、電荷が発生する（すなわち、振動信号 S<sub>o s c</sub> が発生する）。また、回転角速度が発生すると、角速度検出用圧電素子 P<sub>D a</sub>, P<sub>D b</sub> には、回転角速度（コリオリ力）に応じた電荷が発生する（すなわち、センサ信号 S<sub>10</sub> が発生する）。20

#### 【0021】

##### 〔駆動回路〕

駆動回路 11 では、モニタアンプ 11a は、物理量センサ 10 からの振動信号 S<sub>o s c</sub> を電圧に変換し、自動利得制御増幅器（A G C）11b は、駆動アンプ 11c に供給される電圧が一定値になるように、自己の増幅利得を変化させる。駆動アンプ 11c は、自動利得制御増幅器 11b の出力に応じて駆動信号 S<sub>d r v</sub> の周波数および振幅を制御する。このように、振動信号 S<sub>o s c</sub> に応じて駆動信号 S<sub>d r v</sub> が調整されることにより、物理量センサ 10 の最大振動振幅および振動周波数が一定に保たれる。30

#### 【0022】

##### 〔物理量検出回路〕

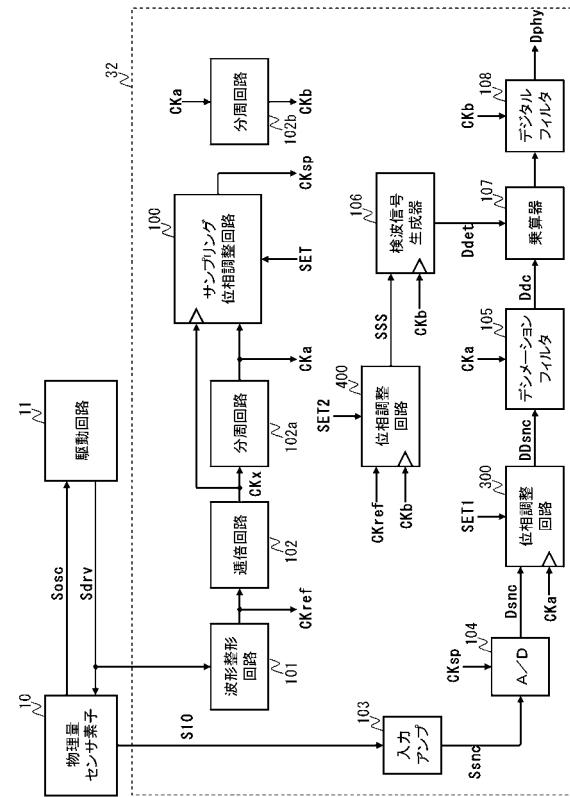

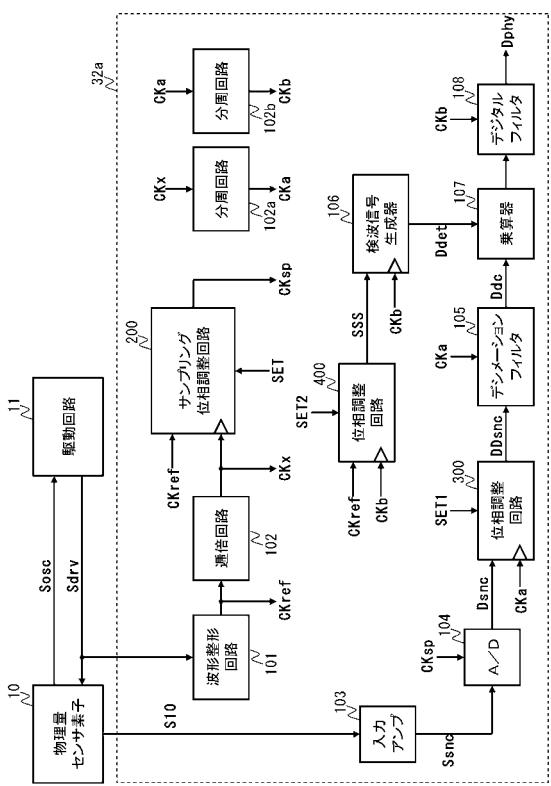

図 1 に戻って、物理量検出回路 12 は、波形整形回路 101 と、遅倍回路 102 と、分周回路 102a と、サンプリング位相調整回路 100 と、分周回路 102b と、入力アンプ 103 と、アナログ／デジタル変換器（A / D）104 と、デシメーションフィルタ 105 と、検波信号生成器 106 と、乗算器 107 と、デジタルフィルタ 108 とを含む。

#### 【0023】

波形整形回路 101 は、駆動信号 S<sub>d r v</sub> を方形波に変換し、基準クロック C<sub>K r e f</sub> として出力する。例えば、波形整形回路 101 は、コンパレータやインバータによって構成される。基準クロック C<sub>K r e f</sub> の周波数は、駆動信号 S<sub>d r v</sub> の周波数（すなわち、センサ信号 S<sub>10</sub> の周波数）と実質的に同一である。40

#### 【0024】

遅倍回路 102 は、波形整形回路 101 からの基準クロック C<sub>K r e f</sub> を遅倍し、基準クロック C<sub>K r e f</sub> の周波数よりも高い周波数を有する遅倍クロック C<sub>K x</sub> を生成する。例えば、遅倍回路 102 は PLL（Phase Locked Loop）によって構成される。

#### 【0025】

分周回路 102a は、遅倍回路 102 からの遅倍クロック C<sub>K x</sub> を分周し、所定のサンプリング周波数（アナログ／デジタル変換器 104 に要求されるサンプリング周波数）と同一の周波数を有する動作クロック C<sub>K a</sub>（サンプリングクロック）を生成する。すなわ50

ち、遅倍クロック CKx は、サンプリング周波数よりも高い周波数を有する。

#### 【0026】

サンプリング位相調整回路 100 は、シフトレジスタ 100R と、セレクタ 100S を含む。シフトレジスタ 100R は、遅倍回路 102 からの遅倍クロック CKx に同期して分周回路 102a からの動作クロック CKa を順次シフトさせることにより、位相が所定量ずつずれた n 個 (n は 2 以上の整数) の遅延クロック CCl, CCl2, … CCln を生成する。例えば、シフトレジスタ 100R は、縦続接続された複数のフリップフロップによって構成される。セレクタ 100S は、外部制御により設定された設定値 SET に応じて、遅延クロック CCl, CCl2, …, CCln のいずれか 1 つを選択し、選択した遅延クロックをサンプリングクロック CKsp (位相調整されたサンプリングクロック) として出力する。設定値 SET は、サンプリング位相調整回路 100 の遅延時間を設定するための値であり、遅倍クロック CKx のパルス数を示す。例えば、設定値 SET が “3” に設定されると、セレクタ 100S は、第 3 番目の遅延クロック CCl3 を選択する。これにより、サンプリング位相調整回路 100 の遅延時間は、遅倍クロック CKx の 3 パルスに対応する時間に設定される。10

#### 【0027】

分周回路 102b は、分周回路 102a からの動作クロック CKa を分周し、動作クロック CKb の周波数よりも低い周波数を有する動作クロック CKb を生成する。

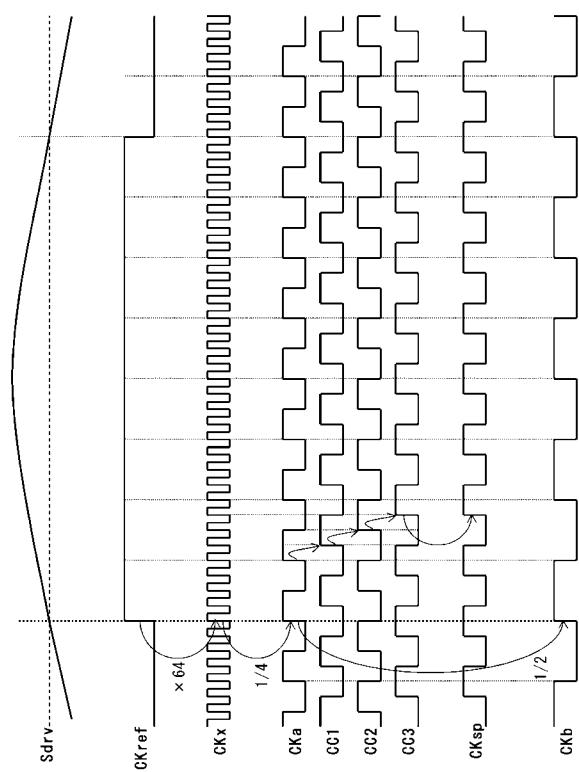

#### 【0028】

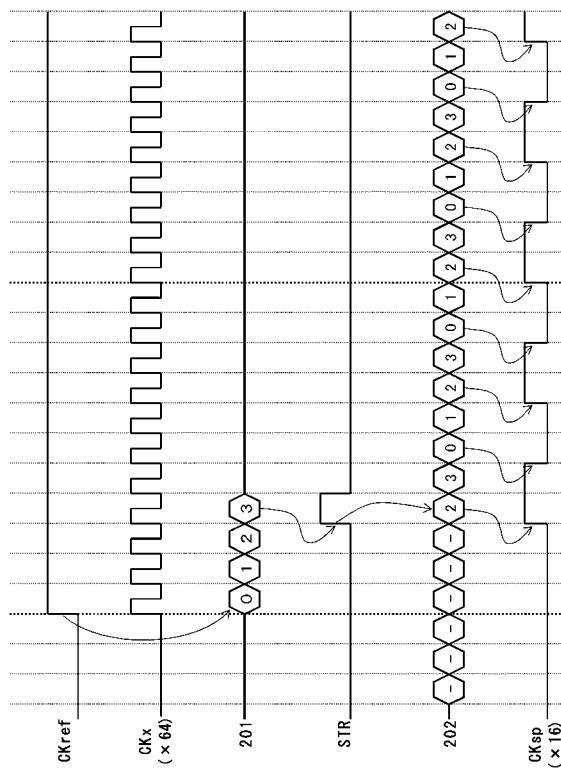

例えば、図 3 のように、基準クロック CKref が遅倍 (64 倍) されて遅倍クロック CKx が生成され、遅倍クロック CKx が分周 (1/4) されて動作クロック CKa が生成され、動作クロック CKa が分周 (1/2) されて動作クロック CKb が生成される。また、サンプリング位相調整回路 100 は、複数の遅延クロック (CCl, CCl2, CCl3) のいずれか 1 つ (遅延クロック CCl3) をサンプリングクロック CKsp として出力する。20

#### 【0029】

入力アンプ 103 は、物理量センサ 10 からのセンサ信号 S10 を電圧に変換し、アナログセンサ信号 Ssnc として出力する。

#### 【0030】

アナログ / デジタル変換器 104 は、サンプリング位相調整回路 100 からのサンプリングクロック CKsp に同期してアナログセンサ信号 Ssnc をサンプリングし、サンプリングしたアナログ値 (振幅値) をデジタル値に変換する。これにより、アナログセンサ信号 Ssnc は、複数のデジタル値によって構成されたデジタルセンサ信号 Dsnc に変換される。30

#### 【0031】

デシメーションフィルタ 105 は、分周回路 102a からの動作クロック CKa に同期して動作し、アナログ / デジタル変換器 104 によって得られたデジタルセンサ信号 Dsnc にデシメーション処理 (サンプリング周波数の変換やデジタル値の間引き等) を実行することにより、サンプリングクロック CKsp (動作クロック CKa) に対応するデジタルセンサ信号 Dsnc を動作クロック CKb に対応するデジタルセンサ信号 Ddc に変換する。40

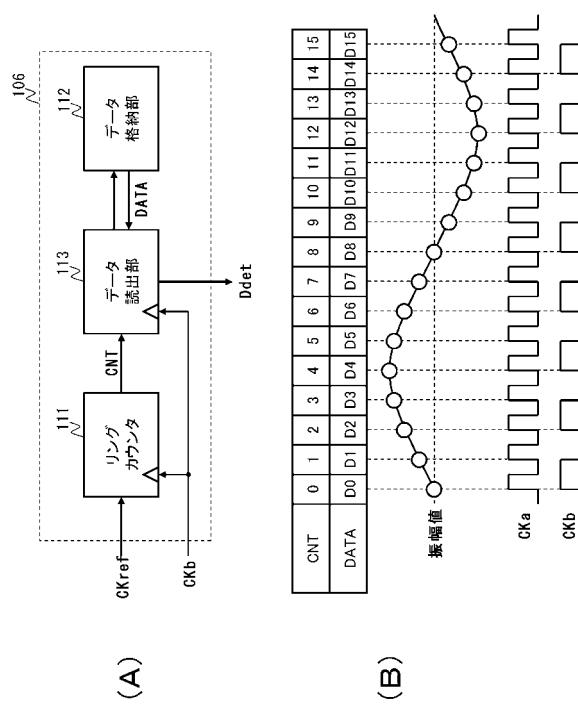

#### 【0032】

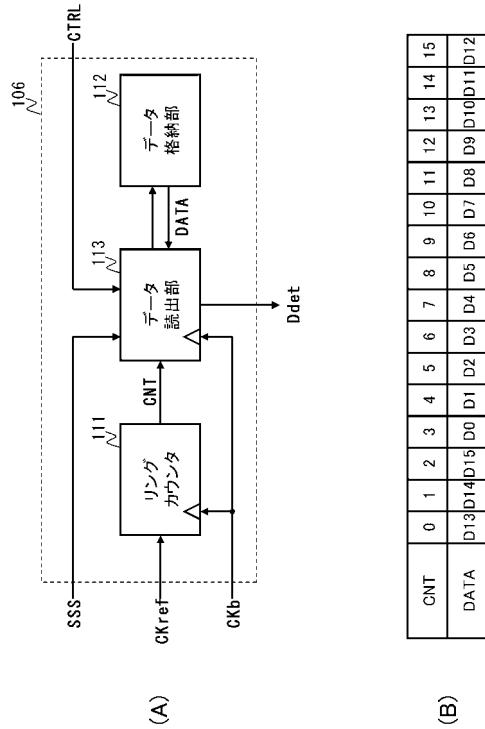

検波信号生成器 106 は、分周回路 102b からの動作クロック CKb に同期して動作し、波形整形回路 101 からの基準クロック CKref の遷移エッジ (ここでは、立ち上がりエッジ) に応答して正弦波信号に対応するデジタル検波信号 Ddet を生成する。デジタル検波信号 Ddet は、複数の正弦波データによって構成される。複数の正弦波データは、それぞれ、所定クロック (例えば、動作クロック CKa) に同期して所定周波数の正弦波信号 (例えば、駆動信号 Sdrv) をサンプリングすることによって得られる複数のアナログ値 (振幅値) に対応する (図 4B 参照)。例えば、複数の正弦波データは、正弦関数で表現される理想的な振幅値を示す。50

## 【0033】

乗算器107は、デシメーションフィルタ105からのデジタルセンサ信号Ddcに検波信号生成器106によって生成されたデジタル検波信号Ddetを乗算する。これにより、物理量信号（物理量センサ10によって検知された物理量に対応する信号）が検波される。

## 【0034】

デジタルフィルタ108は、動作クロックCKbに同期して動作し、ノイズ除去等のために乗算器107によって検波された物理量信号のうち低周波数成分のみをデジタル検出信号Dphyとして通過させる。

## 【0035】

## 〔検波信号生成器〕

図4Aのように、検波信号生成器106は、リングカウンタ111と、データ格納部112と、データ読出部113とを含む。リングカウンタ111、データ読出部113は、動作クロックCKbに同期して動作する。リングカウンタ111は、基準クロックCKrefの遷移エッジに応答してカウント値CNTのインクリメントを開始し、カウント値CNTが所定の最大値に到達するとカウント値CNTを“0”にリセットする。データ格納部112は、デジタル検波信号Ddetの元となる複数の正弦波データDATAを格納する。データ読出部113は、予め設定されたカウント値CNTと正弦波データDATAとの対応関係（図4B）に基づいて、リングカウンタ111のカウント値CNTに対応する正弦波データDATAを読み出して出力する。このようにして、正弦波データD0, D1, D2, ..., D15を順番に出力するによって、正弦波信号に対応するデジタル検波信号Ddetが生成される。

## 【0036】

## 〔動作〕

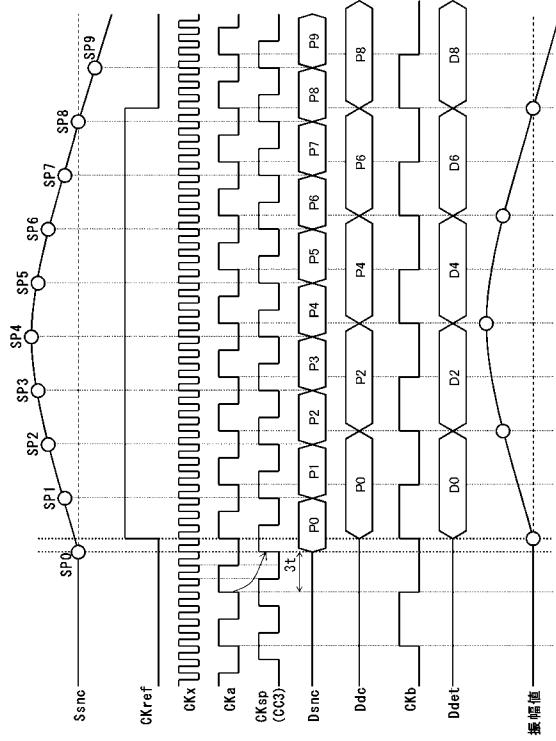

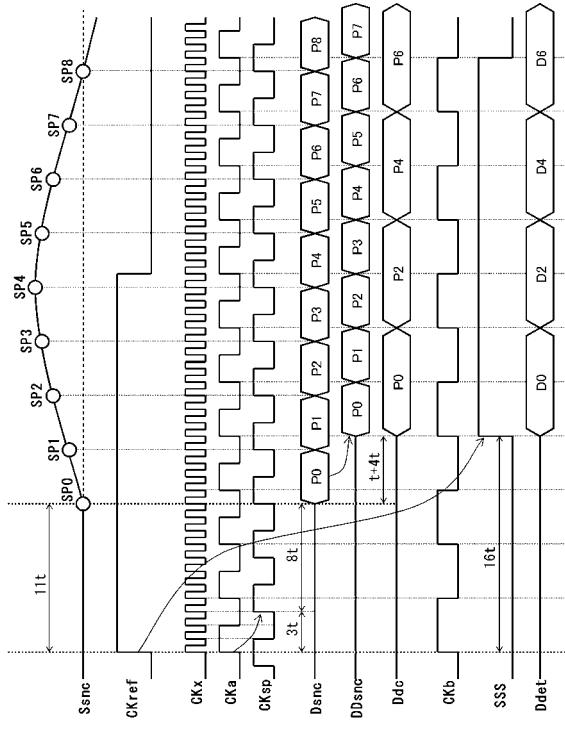

次に、図5を参照しつつ、図1に示した物理量検出回路12による動作について説明する。なお、ここでは、動作クロックCKxの周期を“t”とし、アナログセンサ信号SSncの位相は基準クロックCKrefの位相よりも“t”だけ進んでいるものとする。また、デシメーションフィルタ105は、デジタルセンサ信号Dssncを動作クロックCKbの周波数（動作クロックCKaの周波数の1/2）に対応させるために、デジタルセンサ信号Dssncからデジタル値を1つおきに間引くものとする。

## 【0037】

動作クロックCKa（位相調整される前のサンプリングクロック）の遷移エッジは、アナログセンサ信号SSncの所望サンプリングポイントSPO, S P1, S P2, ...（例えば、正弦波データD0, D1, D2, ...に対応するポイント）に一致していない。ここで、設定値SETが“3”に設定されると、セレクタ100Sは、3番目の遅延クロックCC3をサンプリングクロックCKspとして選択する。これにより、サンプリングクロックCKspの遷移エッジを所望サンプリングポイントSPO, S P1, S P2, ...にそれぞれ一致させることができる。

## 【0038】

アナログ/デジタル変換器104は、サンプリングクロックCKspに同期してアナログセンサ信号SSncをデジタル値P0, P1, P2, P3, P4...に変換する。デシメーションフィルタ105は、デジタルセンサ信号Dssncからデジタル値P1, P3, ...を間引いてデジタルセンサ信号Ddcとして出力する。一方、検波信号生成器106は、基準クロックCKrefの遷移エッジに応答して、動作クロックCKbに同期した正弦波データD0, D2, ...の出力を開始する。乗算器107は、デシメーションフィルタ105からのデジタル値P0, P2, ...に検波信号生成器106からの正弦波データD0, D2, ...をそれぞれ乗算する。

## 【0039】

以上のように、サンプリングクロックCKspの位相を調整することにより、サンプリングポイント（サンプリングクロックCKspの遷移エッジの位置）を移動させることができ

10

20

30

40

50

できる。その結果、デジタルセンサ信号 D<sub>s n c</sub> の位相を変更することができる。このように、サンプリング周波数を高くすることなくデジタルセンサ信号 D<sub>s n c</sub> の位相調整の精度を向上させることができる。また、サンプリングクロック C<sub>K s p</sub> の遷移エッジの位置を所望サンプリングポイント S<sub>P 0</sub>, S<sub>P 1</sub>, S<sub>P 2</sub>, … に一致させる（または近づける）ことができるので、アナログ／デジタル変換の精度を向上させることができ。10

#### 【0040】

また、遙倍クロック C<sub>K x</sub> の周期を単位としてサンプリングクロック C<sub>K s p</sub> の位相を設定することができる。遙倍クロック C<sub>K x</sub> の周波数が高い程、サンプリングクロック C<sub>K s p</sub> の位相を精密に設定することができる。これにより、従来よりもデジタルセンサ信号 D<sub>s n c</sub> の位相を精密に調整することができる。

#### 【0041】

なお、分周回路 102b は、サンプリング位相調整回路 100 からのサンプリングクロック C<sub>K s p</sub> を分周して動作クロック C<sub>K b</sub> を生成しても良い。

#### 【0042】

##### （実施形態 1 の変形例）

また、図 6 のように、検波信号生成器 106 およびデジタルフィルタ 108 は、アナログ／デジタル変換器 104 に供給されるサンプリングクロック C<sub>K s p</sub> に同期して動作しても良い。図 6 に示した物理量検出回路 12a では、図 1 に示した分周回路 102b, デシメーションフィルタ 105 が省略されている。

#### 【0043】

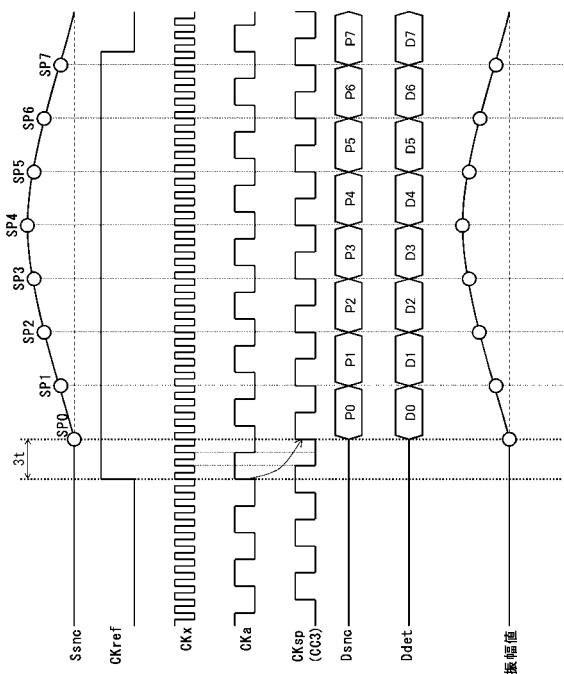

図 7 のように、検波信号生成器 106 は、基準クロック C<sub>K ref</sub> の遷移に応答して、サンプリングクロック C<sub>K s p</sub> に同期した正弦波データ D<sub>0</sub>, D<sub>1</sub>, D<sub>2</sub>, … の出力を開始する。乗算器 107 は、アナログ／デジタル変換器 104 によって得られたデジタル値 P<sub>0</sub>, P<sub>1</sub>, P<sub>2</sub>, … に検波信号生成器 106 からの正弦波データ D<sub>0</sub>, D<sub>1</sub>, D<sub>2</sub>, … をそれぞれ乗算する。このようにサンプリングクロック C<sub>K s p</sub> を物理量検出回路 12a の動作クロックとして利用した場合も図 1 と同様の効果を得ることができる。

#### 【0044】

##### （実施形態 2）

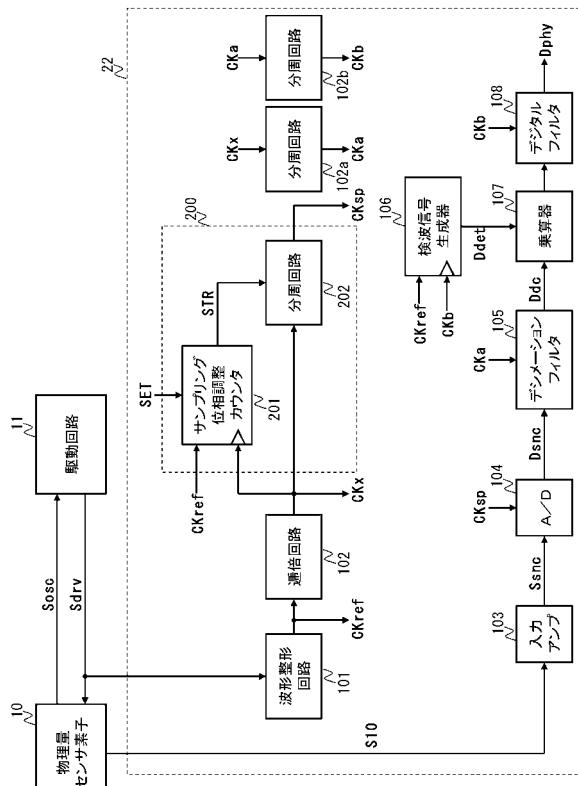

図 8 は、この発明の実施形態 2 による物理量センサ装置の構成を示す。この物理量センサ装置は、図 1 に示した物理量検出回路 12 に代えて、物理量検出回路 22 を備える。物理量検出回路 22 は、図 1 に示したサンプリング位相調整回路 100 に代えて、サンプリング位相調整回路 200 を含む。その他の構成は図 1 と同様である。

#### 【0045】

サンプリング位相調整回路 200 は、サンプリング位相調整カウンタ 201 と、分周回路 202 (クロック生成回路) とを含む。サンプリング位相調整カウンタ 201 は、基準クロック C<sub>K ref</sub> の遷移エッジに応答して遙倍クロック C<sub>K x</sub> の発生パルス数の計数を開始し、発生パルス数が外部制御により設定された所定値 S<sub>ET</sub> に到達するとタイミング信号 S<sub>TR</sub> を生成する。分周回路 202 は、サンプリング位相調整カウンタ 201 からのタイミング信号 S<sub>TR</sub> の遷移エッジに応答して分周処理を開始する（例えば、分周回路 202 の出力が初期状態にリセットされる。）。そして、分周回路 202 は、遙倍クロック C<sub>K x</sub> を分周し、所定のサンプリング周波数を有するサンプリングクロック C<sub>K s p</sub> を生成する。

#### 【0046】

##### 〔動作〕

次に、図 9 を参照しつつ、図 8 に示したサンプリング位相調整回路 200 による処理について説明する。なお、ここでは、動作クロック C<sub>K x</sub> の周波数を 1 / 4 に分周するために、分周回路 202 を 2 ビットカウンタによって構成し、その 2 ビットカウンタの 2 出力のうち M<sub>S B</sub> (Most Significant Bit) に対応する出力をサンプリングクロック C<sub>K s p</sub> として供給するものとする。

## 【0047】

サンプリング位相調整カウンタ201は、基準クロックCKrefの遷移エッジに応答して遅倍クロックCKxの発生パルス数の計数を開始する。ここで、設定値SETが“3”に設定されると、サンプリング位相調整カウンタ201は、カウント値が“3”に到達するとタイミング信号STRを出力する。分周回路202は、サンプリング位相調整カウンタ201からのタイミング信号STRの遷移エッジに応答して、予め設定された初期値（ここでは、2）からカウントを開始し、カウント値が最大値（ここでは、3）に到達するとカウント値を“0”にリセットする。分周回路202のMSB出力は、分周回路202のカウント値が2または3である場合には“1”になり、分周回路202のカウント値が0または1である場合には“0”になる。

10

## 【0048】

以上のように、遅倍クロックCKxの周期を単位としてサンプリングクロックCKspの位相を設定することができる。また、遅倍クロックCKxの周波数が高い程、サンプリングクロックCKspの位相を精密に設定することができる。これにより、従来よりもデジタルセンサ信号Dsnecの位相を精密に調整することができる。

## 【0049】

なお、分周回路202を、サンプリング位相調整カウンタ201からのタイミング信号STRに応答して遅倍処理を開始する遅倍回路に置き換えても良い。このような遅倍回路は、所定周波数のクロックを遅倍し、サンプリングクロックCKspを生成する。

## 【0050】

20

## （実施形態3）

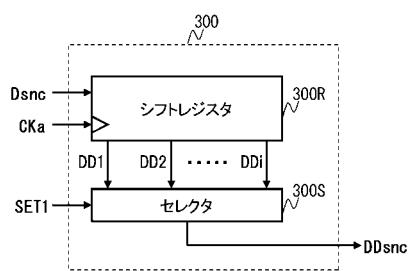

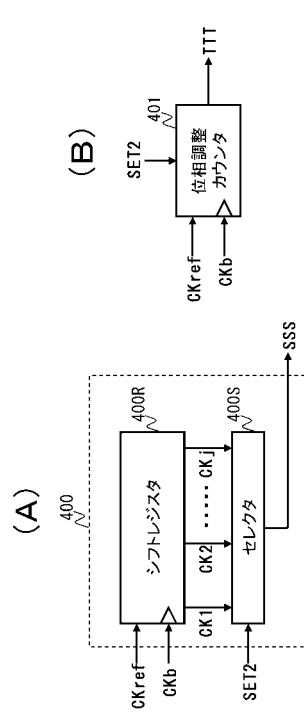

図10は、この発明の実施形態3による物理量センサ装置の構成を示す。この物理量センサ装置は、図1に示した物理量検出回路12に代えて、物理量検出回路32を備える。物理量検出回路32は、図1に示した構成に加えて、デジタルセンサ信号Dsnecの位相を調整する位相調整回路300と、デジタル検波信号Ddetの位相を調整する位相調整回路400とを含む。その他の構成は、図1と同様である。

## 【0051】

図11のように、位相調整回路300は、シフトレジスタ300Rと、セレクタ300Sとを含む。シフトレジスタ300Rは、分周回路102aからの動作クロックCKaに同期してデジタルセンサ信号Dsnecを順次シフトさせることにより、位相が所定量ずつずれたi個（iは、2以上の整数）の遅延信号DD1, DD2, …, DDiを生成する。例えば、シフトレジスタ300Rは、縦続接続された複数のフリップフロップによって構成される。セレクタ300Sは、外部制御により設定された設定値SET1に応じて遅延信号DD1, DD2, …, DDiのいずれか1つを選択し、選択した遅延信号を遅延デジタルセンサ信号DDsnecとして出力する。設定値SET1は、位相調整回路300の遅延時間を設定するための値であり、動作クロックCKaのパルス数を示す。

30

## 【0052】

図12Aのように、位相調整回路400は、シフトレジスタ400Rと、セレクタ400Sとを含む。シフトレジスタ400Rは、分周回路102bからの動作クロックCKbに同期して基準クロックCKrefを順次シフトさせることにより、位相が所定量ずつずれたj個（jは、2以上の整数）の遅延クロックCK1, CK2, …, CKjを生成する。例えば、シフトレジスタ400Rは、縦続接続された複数のフリップフロップによって構成される。セレクタ400Sは、外部制御により設定された設定値SET2に応じて遅延クロックCK1, CK2, …, CKjのいずれか1つを選択し、選択した遅延クロックを選択クロックSSSとして出力する。設定値SET2は、位相調整回路400の遅延時間を設定するための値であり、動作クロックCKbのパルス数を示す。

40

## 【0053】

なお、図10に示した位相調整回路400を図12Bに示した位相調整カウンタ401に置き換えても良い。位相調整カウンタ401は、基準クロックCKrefの遷移エッジに応答して分周回路102bからの動作クロックCKbの発生パルス数の計数を開始し、

50

発生パルス数が設定値 S E T 2 に到達するとタイミング信号 T T T を出力する。

#### 【 0 0 5 4 】

##### 〔 動作 〕

次に、図 13 を参照しつつ、図 10 に示した物理量検出回路 3 2 による動作について説明する。なお、ここでは、遅倍クロック C K x の周期を “ t ” とし、アナログセンサ信号 S s n c の位相は、基準クロック C K r e f の位相よりも “ 1 1 t ” だけ遅れているものとする。また、動作クロック C K a (サンプリングクロック C K s p ) の周波数、動作クロック C K b の周波数は、それぞれ、遅倍クロック C K x の周波数の “ 1 / 4 ” , “ 1 / 8 ” であるものとする。

#### 【 0 0 5 5 】

10

ここで、サンプリング位相調整回路 1 0 0 の設定値 S E T が “ 3 ” に設定されると、サンプリング位相調整回路 1 0 0 は、動作クロック C K a を遅倍クロック C K x の 3 パルスに対応する時間 “ 3 t ” だけ遅延させてサンプリングクロック C K s p として出力する。これにより、サンプリングクロック C K s p の遷移エッジを所望サンプリングポイント S P 0 , S P 1 , S P 2 , . . . にそれぞれ一致させることができる。

#### 【 0 0 5 6 】

20

また、位相調整回路 3 0 0 の設定値 S E T 1 を “ 1 ” に設定すると、位相調整回路 3 0 0 は、デジタルセンサ信号 D s n c を動作クロック C K a の 1 パルスに対応する時間 “ 4 t ” だけ遅延させ、遅延デジタルセンサ信号 D D s n c として出力する。ここでは、動作クロック C K a はサンプリングクロック C K s p に対して位相が “ t ” だけずれているので、基準クロック C K r e f と遅延デジタルセンサ信号 D D s n c との位相差は “ 1 6 t ( = 3 t + 8 t + t + 4 t ) ” になる。また、基準クロック C K r e f とデシメーションフィルタ 1 0 5 によって得られたデジタルセンサ信号 D d c との位相差も “ 1 6 t ” になる。

#### 【 0 0 5 7 】

30

さらに、位相調整回路 4 0 0 の設定値 S E T 2 を “ 2 ” に設定すると、位相調整回路 4 0 0 は、基準クロック C K r e f を動作クロック C K b の 2 パルスに対応する時間 “ 1 6 t ” だけ遅延させ、選択クロック S S S として出力する。検波信号生成器 1 0 6 は、選択クロック S S S の遷移エッジに応答して正弦波データ D 0 , D 2 , . . . を出力する。これにより、基準クロック C K r e f とデジタル検波信号 D d e t との位相差は “ 1 6 t ” になるので、デジタルセンサ信号 D s n c の位相とデジタル検波信号 D d e t の位相とを互いに一致させることができる。

#### 【 0 0 5 8 】

以上のように、位相調整回路 3 0 0 によって、動作クロック C K a の周期を単位としてデジタルセンサ信号 D s n c の位相を設定することができる。また、位相調整回路 4 0 0 (または、位相調整カウンタ 4 0 1) によって、動作クロック C K b の周期を単位としてデジタル検波信号 D d e t の位相を設定することができる。このように、デジタルセンサ信号 D s n c の位相およびデジタル検波信号 D d e t の位相を精密に設定することができる。

#### 【 0 0 5 9 】

40

また、動作クロック C K b は動作クロック C K a よりも周波数が低いので、位相調整回路 4 0 0 の位相調整の精度は、位相調整回路 3 0 0 の位相調整の精度よりも低い。このように、位相調整の精度がそれぞれ異なる位相調整回路 3 0 0 , 4 0 0 に位相調整処理を分担させることにより、位相調整処理に要する回路規模および消費電力を低減することができる。例えば、動作クロック C K a の周期 “ t ” を単位として最大遅延時間を “ 1 6 t ” に設定するために、位相調整回路 4 0 0 のみを使用する場合では 1 6 個のフリップフロップを設ける必要があるが、図 10 の場合では位相調整回路 3 0 0 , 4 0 0 にフリップフロップを 4 個ずつ設ければ良い。

#### 【 0 0 6 0 】

なお、位相調整回路 3 0 0 , 4 0 0 は、それぞれ、基準クロック C K r e f の周波数よ

50

りも高い周波数を有する別の動作クロック（動作クロックCKaとは異なる周波数を有する動作クロック）に同期して動作しても良い。

#### 【0061】

##### 〔検波信号生成器の変形例〕

また、図14Aのように、リングカウンタ111が基準クロックCKrefの遷移エッジに応答してカウント値CNTのインクリメントを開始するように構成しても良い。この場合、データ読出部113におけるカウント値CNTと正弦波データDATAとの対応関係は、外部制御CTR1によって設定可能である。データ読出部113は、選択クロックSSSの遷移エッジに応答して、カウント値CNTに対応する正弦波データDATAの読み出しを開始する。例えば、位相調整回路300の設定値SETが“3”に設定されると、カウント値CNTと正弦波データDATAとの対応関係は、図14Bのように設定される。このように設定することにより、検波信号生成器106は、選択クロックSSSの遷移エッジに応答して正弦波データD0, D1, D2, …を順番に出力することができる。

10

#### 【0062】

##### 〔実施形態3の変形例1〕

また、図15に示した物理量検出回路32aのように、図10に示したサンプリング位相調整回路100を図8に示したサンプリング位相調整回路200に置き換えた場合も、図10の場合と同様の効果を得ることができる。

#### 【0063】

20

##### 〔その他の実施形態〕

なお、以上の各実施形態における物理量センサ10は、音叉型に限らず、円柱型、正三角柱型、正四角柱型、リング型や、その他の形状であっても良い。また、図16のように、物理量センサ10は、静電容量式加速度センサであっても良い。物理量センサ10は、固定部10bと、可動部10cと、可動電極Pma, Pmbと、検出電極Pfa, Pfbと、差動增幅器10dとを有する。可動部10cは、加速度に応じて変位するように固定部10bに連結される。可動電極Pma, Pmbは、可動部10cに配置される。検出電極Pfa, Pfbは、それぞれ、可動電極Pma, Pmbに対向するように、固定部10bに配置される。すなわち、可動電極Pma, 検出電極Pfaによって容量素子Caが構成され、可動電極Pmb, 検出電極Pfbによって容量素子Cbが構成される。また、容量素子Ca, Cbには、それぞれ、発振回路11dからの駆動信号Sdrvが供給される。差動增幅器10dは、検出電極Pfa, Pfbのそれぞれに発生する電荷量の差に対応するセンサ信号S10を出力する。加速度が発生すると、可動部10cの変位に起因して容量素子Caの静電容量および容量素子Cbの静電容量のうち一方が増加し他方が減少する。これにより、検出電極Pfa, Pfbのそれぞれにおける電荷量に差が生じ、この差に対応するセンサ信号S10が出力される。

30

#### 【0064】

また、以上の各実施形態において設定値SET, SET1, SET2は変更可能な値として説明したが、設定値SET, SET1, SET2は固定値であっても良い。

#### 【産業上の利用可能性】

40

#### 【0065】

この発明は、サンプリング周波数の増大を抑制しつつ位相調整の精度を向上させることができるので、移動体、携帯電話、デジタルカメラ、ゲーム機などに用いられる物理量センサ（例えば、音叉型角速度センサや静電容量式加速度センサなど）に好適である。

#### 【図面の簡単な説明】

#### 【0066】

【図1】この発明の実施形態1による物理量センサ装置の構成を示すブロック図。

【図2】図1に示した物理量センサおよび駆動回路の構成を示すブロック図。

【図3】図1に示したサンプリング位相調整回路による処理について説明するためのタイミングチャート。

50

【図4】(A)図1に示した検波信号生成器の構成例を示すブロック図。(B)図4Aの検波信号生成器におけるカウント値と正弦波データとの対応関係を示す図。

【図5】図1に示した物理量検出回路による動作について説明するためのタイミングチャート。

【図6】図1に示した物理量検出回路を変形例を示すブロック図。

【図7】図6に示した物理量検出回路による動作について説明するためのタイミングチャート。

【図8】この発明の実施形態2による物理量センサ装置の構成を示すブロック図。

【図9】図8に示したサンプリング位相調整回路による処理について説明するためのタイミングチャート。 10

【図10】この発明の実施形態3による物理量センサ装置の構成を示すブロック図。

【図11】図10に示した位相調整回路の構成を示す図。

【図12】(A)図10に示した位相調整回路の構成を示す図。(B)位相調整カウンタの構成を示すブロック図。 15

【図13】図10に示した物理量検出回路による動作について説明するためのタイミングチャート。

【図14】(A)図10に示した検波信号生成器の構成例を示すブロック図。(B)図1 4Aの検波信号生成器におけるカウント値と正弦波データとの対応関係を示す図。 20

【図15】図10に示した物理量検出回路の変形例を示すブロック図。

【図16】物理量センサの変形例について説明するためのブロック図。 25

【図17】アナログ/デジタル変換回路における処理について説明するための図。

#### 【符号の説明】

##### 【0067】

10 物理量センサ

11 駆動回路

12, 12a, 22, 22a, 32, 32a 物理量検出回路

101 波形整形回路

102 通倍回路

102a, 102b, 202 分周回路

103 入力アンプ

30

104 アナログ/デジタル変換器

105 デシメーションフィルタ

106 検波信号生成器

107 乗算器

108 デジタルフィルタ

100, 200 サンプリング位相調整回路

300, 400 位相調整回路

100R, 300R, 400R シフトレジスタ

100S, 300S, 400S セレクタ

201 サンプリング位相調整カウンタ

40

401 位相調整カウンタ

111 リングカウンタ

112 データ格納部

113 データ読出部

【 四 1 】

【図2】

【 义 3 】

【 図 4 】

【図5】

【図6】

【図8】

【図9】

【 図 1 0 】

【 図 1 1 】

【 図 1 2 】

【 図 1 3 】

【図14】

【図15】

【図16】

(B) DATA D13 D14 D15 D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12

【図17】

---

フロントページの続き

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 関 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(72)発明者 犬飼 文人

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 室屋 清一

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 貝野 陽一

大阪府門真市大字門真1006番地 パナソニック半導体システムテクノ株式会社内

審査官 小野寺 麻美子

(56)参考文献 特開2007-292660 (JP, A)

特開2004-239907 (JP, A)

特開2004-212111 (JP, A)

特開2006-329637 (JP, A)

特開2003-042768 (JP, A)

特開平07-146151 (JP, A)

特開平08-014916 (JP, A)

特開2008-052175 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 01 C 19 / 56

G 01 P 15 / 125