(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4819325号

(P4819325)

(45) 発行日 平成23年11月24日(2011.11.24)

(24) 登録日 平成23年9月9日(2011.9.9)

(51) Int.Cl.

F 1

G 11 C 11/407 (2006.01)

G 11 C 11/4093 (2006.01)G 11 C 11/34 362 S

G 11 C 11/34 354 P

請求項の数 8 (全 25 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2004-161460 (P2004-161460)  |

| (22) 出願日     | 平成16年5月31日 (2004.5.31)        |

| (65) 公開番号    | 特開2004-362756 (P2004-362756A) |

| (43) 公開日     | 平成16年12月24日 (2004.12.24)      |

| 審査請求日        | 平成19年1月31日 (2007.1.31)        |

| (31) 優先権主張番号 | 2003-035604                   |

| (32) 優先日     | 平成15年6月3日 (2003.6.3)          |

| (33) 優先権主張国  | 韓国 (KR)                       |

| (31) 優先権主張番号 | 2003-042840                   |

| (32) 優先日     | 平成15年6月27日 (2003.6.27)        |

| (33) 優先権主張国  | 韓国 (KR)                       |

| (31) 優先権主張番号 | 10/792425                     |

| (32) 優先日     | 平成16年3月3日 (2004.3.3)          |

| (33) 優先権主張国  | 米国 (US)                       |

|           |                                                                                                                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区梅灘洞416<br>416, Maetan-dong, Yeongtong-gu, Suwon-si,<br>Gyeonggi-do, Republic<br>of Korea |

| (74) 代理人  | 100064908<br>弁理士 志賀 正武                                                                                                                                             |

| (74) 代理人  | 100089037<br>弁理士 渡邊 隆                                                                                                                                              |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                                                                                             |

最終頁に続く

(54) 【発明の名称】集積回路装置及びその動作方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のメモリセルを含むメモリセルアレイと、

外部ターミナルから  $2^N$  個のデータビットを直列に受信する書込みデータ経路と、を具備し、

前記書込みデータ経路は、

$2^N$  個の書込みデータバッファと、

$2^N$  個のスイッチと、

$N$  個のデータビットを並列に前記メモリセルアレイに書き込むために前記  $2^N$  個のスイッチのうち少なくとも  $N$  個のスイッチと連結される  $N$  個のデータラインと、を具備し、

前記書込みデータ経路は、

前記外部ターミナルと連結される第 1 及び第 2 直列 - 並列変換部と、

$N$  個の第 1 グローバルデータラインと  $N$  個の第 2 グローバルデータラインとを具備し、

前記  $2^N$  個の書込みデータバッファは、 $N$  個の第 1 書込みデータバッファと  $N$  個の第 2 書込みデータバッファとを含んで構成され、

前記  $2^N$  個のスイッチは、 $N$  個の第 1 スイッチと  $N$  個の第 2 スイッチとを含んで構成され、

前記  $N$  個の第 1 書込みデータバッファは、第 1 直列 - 並列変換部に連結され、前記  $N$  個の第 1 グローバルデータラインのそれぞれは、前記  $N$  個の第 1 スイッチのそれぞれと前記  $N$  個の第 1 書込みデータバッファのそれぞれとの間に連結され、

10

20

前記 N 個の第 2 書込みデータバッファは、第 2 直列 - 並列変換部に連結され、前記 N 個の第 2 グローバルデータラインのそれぞれは、前記 N 個の第 2 スイッチのそれぞれと前記 N 個の第 2 書込みデータバッファのそれぞれとの間に連結され、

前記 N 個のデータラインは、N 個のローカルデータラインであり、

前記 N 個のローカルデータラインのそれぞれは、前記 N 個の第 1 スイッチ及び前記 N 個の第 2 スイッチと前記メモリセルアレイとの間にそれぞれ連結され、

前記書込みデータ経路は、

前記第 1 及び第 2 直列 - 並列変換部のうち何れか 1 つと前記 N 個の第 1 書込みデータバッファ及び前記 N 個の第 2 書込みデータバッファのうち何れか 1 つの間にそれぞれ連結される第 1 及び第 2 データオーダリング回路をさらに具備し、

10

前記 N 個の第 1 スイッチは、第 1 制御信号に応答し、

前記 N 個の第 2 スイッチは、前記第 1 制御信号から遅延された第 2 制御信号に応答し、前記第 1 及び第 2 制御信号は、

書込み活性化信号から異なる遅延時間をもって遅延されて生成される

ことを特徴とする集積回路装置。

#### 【請求項 2】

前記集積回路装置は、

チップ選択命令及びファンクション命令に応答して前記書込み活性化信号を発生する命令デコーダと、

前記書込み活性化信号に応答して前記第 1 及び第 2 制御信号を発生する制御信号発生部と、をさらに具備する

20

ことを特徴とする請求項 1 に記載の集積回路装置。

#### 【請求項 3】

前記命令デコーダは、

前記チップ選択命令及び前記ファンクション命令に応答してアクティブ命令及び読出命令をさらに発生する

ことを特徴とする請求項 2 に記載の集積回路装置。

#### 【請求項 4】

前記命令デコーダは、

前記チップ選択命令及び前記ファンクション命令に応答して読出命令、リフレッシュ命令及びモードレジスタ命令をさらに発生する

30

ことを特徴とする請求項 2 に記載の集積回路メモリ装置。

#### 【請求項 5】

複数のメモリセルを含むメモリセルアレイと、

外部ターミナルから 2 N 個のデータビットを直列に受信する書込みデータ経路と、を具備し、

前記書込みデータ経路は、

2 N 個の書込みデータバッファと、

2 N 個のスイッチと、

N 個のデータビットを並列に前記メモリセルアレイに書き込むために前記 2 N 個のスイッチのうち少なくとも N 個のスイッチと連結される N 個のデータラインと、を具備し、

40

前記書込みデータ経路は、

前記外部ターミナルと連結される第 1 及び第 2 直列 - 並列変換部と、

N 個の第 1 グローバルデータラインと N 個の第 2 グローバルデータラインとを具備し、

前記 2 N 個の書込みデータバッファは、N 個の第 1 書込みデータバッファと N 個の第 2 書込みデータバッファとを含んで構成され、

前記 2 N 個のスイッチは、N 個の第 1 スイッチと N 個の第 2 スイッチとを含んで構成され、

前記 N 個の第 1 書込みデータバッファは、第 1 直列 - 並列変換部に連結され、前記 N 個の第 1 グローバルデータラインのそれぞれは、前記 N 個の第 1 スイッチのそれぞれと前記

50

N個の第1書き込みデータバッファのそれぞれとの間に連結され、

前記N個の第2書き込みデータバッファは、第2直列・並列変換部に連結され、前記N個の第2グローバルデータラインのそれぞれは、前記N個の第2スイッチのそれぞれと前記N個の第2書き込みデータバッファのそれぞれとの間に連結され、

前記N個のデータラインは、N個のローカルデータラインであり、

前記N個のローカルデータラインのそれぞれは、前記N個の第1スイッチ及び前記N個の第2スイッチと前記メモリセルアレイとの間にそれぞれ連結され、

前記書き込みデータ経路は、

前記第1及び第2直列・並列変換部のうち何れか1つと前記N個の第1書き込みデータバッファ及び前記N個の第2書き込みデータバッファのうち何れか1つとの間にそれぞれ連結される第1及び第2データオーダリング回路をさらに具備し、

10

前記N個の第1スイッチは、第1制御信号に応答し、

前記N個の第2スイッチは、前記第1制御信号から遅延された第2制御信号に応答し、前記集積回路装置は、

N個の第3スイッチとN個の第4スイッチとをさらに具備し、

前記N個の第3スイッチのそれぞれは、前記第1直列・並列変換部と前記N個の第1書き込みデータバッファのそれぞれとの間に連結され、

前記N個の第4スイッチは、前記第2直列・並列変換部と前記N個の第2書き込みデータバッファのそれぞれとの間に連結される

ことを特徴とする集積回路装置。

20

#### 【請求項6】

前記N個の第3スイッチは、第3制御信号に応答し、

前記N個の第4スイッチは、前記第3制御信号から遅延された第4制御信号に応答することを特徴とする請求項5に記載の集積回路装置。

#### 【請求項7】

前記第3及び第4制御信号は、

データストローブ信号のオフセット立下りエッジに応答して発生されることを特徴とする請求項6に記載の集積回路装置。

#### 【請求項8】

前記集積回路装置は、

30

前記データストローブ信号に応答して前記データストローブ信号の立下りエッジをカウントして、前記データストローブ信号のオフセット立下りエッジにしたがって前記第3及び第4制御信号を発生するデータストローブカウンタをさらに具備する

ことを特徴とする請求項7に記載の集積回路装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、集積回路装置及びその動作方法に係り、例えば、集積回路メモリ装置の書き込みデータ経路及びその動作方法に関する。

##### 【背景技術】

##### 【0002】

集積回路メモリ装置は、多くの消費財及び商業上の応用に広く使われている。集積回路メモリ装置の集積度が高まることによって、集積回路メモリ装置内のメモリセルの数も増加する。その上、集積回路メモリ装置のプリフェッチスキームもさらに増加する。当業者に周知のように、プリフェッチは、集積回路メモリ装置において、どれだけのビットを同時に書き込みまたは読み出しえできるかを意味する。プリフェッチスキームはまた、一度に外部ターミナルへ/から直列に出力または入力されるビット数を意味するバースト長で表される。多くの集積回路装置は、例えば4ビットバースト長の4ビットプリフェッチスキームを使用する。しかし、高いデータレートのために8ビットバースト長または8ビットプリフェッチスキームに増加することが要求される。将来は、さらに高いプリフェッチスキーム

40

50

ムやバースト長が使われる。

#### 【0003】

高いプリフェッチャスキームに増加するほど、集積回路メモリ装置の書き込みデータ経路はそのサイズ及び複雑性がさらに大きくなる。当業者に周知のように、書き込みデータ経路は、外部ターミナルから多数のデータビットを直列に受信し、メモリセルアレイに多数のデータビットを並列に書き込むために提供される。これによりデータ書き込み経路はチップ面積の相当部分を占める。

#### 【0004】

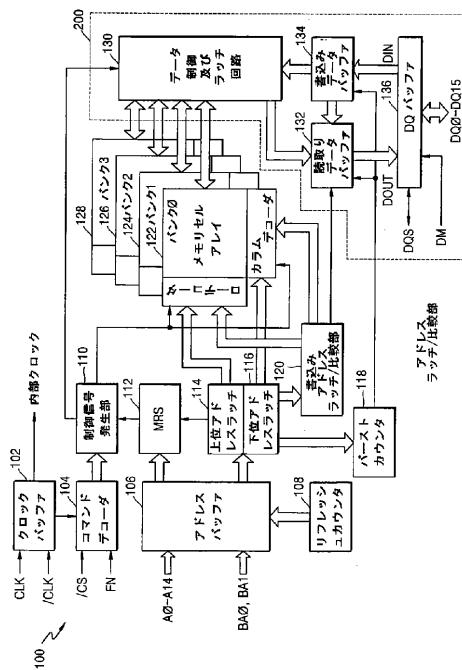

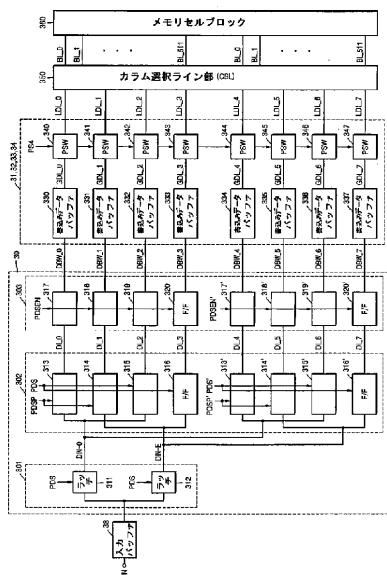

図1は、典型的なDRAMのブロックダイアグラムである。図1のDRAMは、ファストサイクルDRAM(FCDRAM)とも称する。これを参照すれば、FCRAM100は、クロック信号を受信して内部クロック信号を発生させるクロックバッファ102、外部入力にしたがって命令を発生するコマンドデコーダ104、アドレスデータA0～A14とバンク選択信号BA0、BA1にしたがってアドレス信号を発生するアドレスバッファ106、及び、リフレッシュカウンタ108を含む。制御信号発生部110は、コマンドデコーダ104から提供される信号にしたがって制御信号を発生する。モードレジスタMRS112は、適切なモード信号を発生する。上位アドレスラッチ114と下位アドレスラッチ116とは、ローデコーダとカラムデコーダとにそれぞれ提供されるアドレス信号を発生する。バーストカウンタ118は、読み出し及び書き込みデータのバースト長を制御するために使われる。書き込みアドレスラッチ/比較部120は、以前の書き込みアドレスと現在の書き込みアドレスとを比較するために使われる。

10

20

#### 【0005】

メモリセルアレイとして、例えば4個のバンク122～128が提供される。しかし、これより少数または多数のバンクが提供されてもよい。入出力データ経路200は、データ制御及びラッチ回路130、読み出しデータバッファ132、書き込みデータバッファ134、及び、入出力DQバッファ136を含む。DQバッファ136は、所定の入力をマスキングするデータマスク信号DMに応答する。図1に記載されたFCDRAMは、当業者に周知の技術であるので、これ以上の説明は省略する。

#### 【0006】

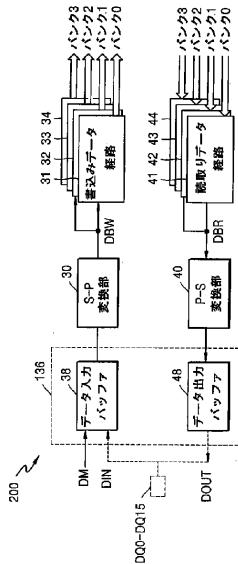

図2は、図1のデータ入出力経路200のさらに具体的なブロックダイアグラムである。図2に示されたように、図1のモードレジスタ112がバースト長4を選択する時、各入出力ターミナルDQ0～DQ15は、外部ターミナルから伝えられる4データビットを順次に受信する。この後、各入力データビットは、DQバッファ136内のデータ入力バッファ38によって直列-並列(S-P)変換部30に伝えられる。直列-並列S-P変換部30により直列から並列に変換された書き込みデータバスDBW上の入力データは、バンクアドレスビットBA0、BA1により選択される適切な書き込みデータ経路31、32、33、34に伝えられる。

30

#### 【0007】

図2において、データの読み出しを説明すると、多数のバンクBANK0～BANK3のうち何れか1つのバンクからデータが出力され、バンクアドレスビットBA0、BA1により選択される読み出しデータ経路41、42、43、44を通じて読み出しデータバスラインDBRに伝えられる。読み出しデータバスラインDBR上の並列データは、並列-直列変換部40により直列データに変換される。この後、直列データは、データ出力バッファ48とデータ入出力ターミナルDQ0～DQ15を通じて外部に出力される。したがって、データ入出力ターミナルDQ0～DQ15を通じて、64(4×16)ビットの入力データが選択されたバンクのメモリセルアレイに同時に書き込まれ、64ビットのデータが同時に読み出される。

40

#### 【0008】

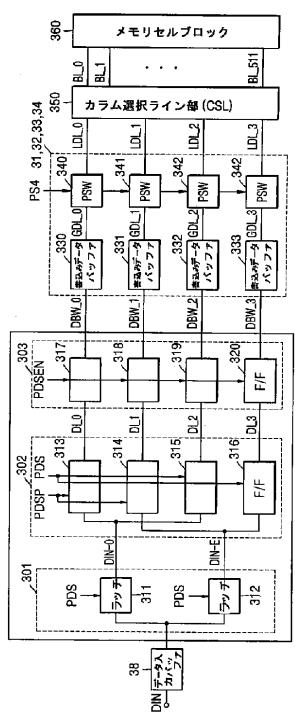

図3は、図1及び図2と連結する従来のFCDRAMにおいて、4ビットプリフェッチャスキームを説明するブロックダイアグラムである。図3を参照すれば、バースト長4が図1のMRS112により選択される時、入力バッファ38を通じてバッファされた第1

50

入力データビットは、第1内部データストローブ信号PDSの立上がりエッジに応答して直列・並列変換部30の入力データラッチ301の第1ラッチ311に保存される。直列に受信された第2入力データビットは、第1内部データストローブ信号PDSの立下りエッジに応答して直列・並列変換部30の入力データラッチ301の第2ラッチ312に保存される。

#### 【0009】

この時、第1ラッチ311に保存された第1入力データビットと第2ラッチ312に保存された第2入力データビットは、第2内部データストローブ信号PDSPに応答して並列変換部302の第1レジスタ313と第2レジスタ314とにそれぞれ伝えられる。第3入力データビットは、第1内部データストローブ信号PDSの次の立上がりエッジに応答して第1ラッチ311に保存され、第4入力データビットは、第1内部データストローブ信号PDSの次の立下りエッジに応答して第2ラッチ312に保存される。

10

#### 【0010】

また、第3入力データビット及び第4入力データビットは、第1内部データストローブ信号PDSの立上がり及び立下りエッジに応答して、並列変換部302の第3レジスタ315と第4レジスタ316とにそれぞれ伝えられる。したがって、図3に示されたように、第1及び第3入力データビットのような奇数入力データDIN-Oは、連続的に第1及び第3レジスタ313、315に伝えられ、第2及び第4入力データビットのような偶数入力データDIN-Eは、第2及び第4レジスタ314、316に伝えられる。全ての入力データD0、D1、D2、D3が並列変換部302に伝えられた後、全ての入力データは、第3内部データストローブ信号PDSENに応答して並列に並列データ出力回路303に伝えられて保存される。

20

#### 【0011】

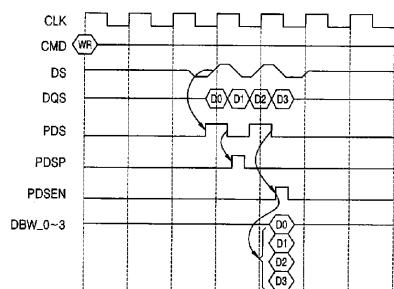

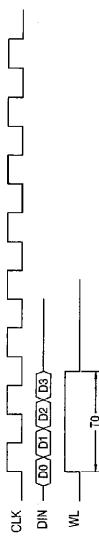

図4は、入力DQパッド上の4つのデータビットD0～D3の直列入力とデータラインDBW\_0～DBW\_3上の4つのデータビットの並列出力を含む前述した動作を説明するタイミングダイアグラムである。

#### 【0012】

また、図3を参照すれば、直列・並列変換部30に保存された入力データは、図2の書き込みデータ経路31、32、33、34の部分を形成する書き込みデータバッファ330、331、332、333に保存される。書き込みデータバッファ330、331、332、333から、入力データは、並列ビットスイッチPSW、340～343に印加される制御信号PS4に応答してカラム選択ラインCSL、350に伝えられる。4ビットの入力データは、メモリセルブロック360に同時に書き込まれる。図3及び4では、4ビットデータがメモリセルブロックに同時に書き込まれるので、4ビットプリフェッチスキームを説明する。図3において、書き込みデータバッファ330～333と並列ビットスイッチPSW340～343を連結させるラインをグローバルデータラインGDL\_0～GDL\_3と呼ぶ。並列ビットスイッチPSWとカラム選択ラインCSLとを連結させるラインをローカルデータラインLDL\_0～LDL\_3と呼ぶ。最後に、メモリセルアレイのビットラインは、図3でBL\_0～BL\_511と表示される。

30

#### 【0013】

図5は、8ビットプリフェッチスキームを含む従来のFCDRAMのブロックダイアグラムである。当業者に周知のように、8ビットプリフェッチスキームでは、FCDRAMがさらに高いデータレートで動作する。図5において、図3の参照符号と同一に使われた参照符号は、同様の構成要素を示す。8ビットプリフェッチスキームに適合するために、図3の構成要素は、図5においてその個数が2倍となる。したがって、レジスタの第2セット313'～316'は並列変換部302に、そして、レジスタの第2セット317'～320'が並列データ出力回路303に提供される。また、書き込みデータバッファの第2セット334～337と並列ビットスイッチ344～347も提供される。

40

#### 【0014】

図5に示されたように、ローカルデータラインLDLとグローバルデータラインGDL

50

とは、図3と比較して2倍である。言い換えれば、図5の8ビットプリフェッチスキームにおいて、グローバルデータラインGDLとローカルデータラインLDLとの数は、図3の4ビットプリフェッチスキームと比較して2倍に増加する。さらに具体的には、図5において、8個のグローバルデータラインGDL\_0～GDL\_7は、それぞれの書き込みデータバッファ330～337をそれぞれの並列ビットスイッチ340～347に連結させるために使われる。また、8個のローカルデータラインLDL\_0～LDL\_7は、それぞれの並列ビットスイッチ340～347をカラム選択ライン350に連結させるために使われる。これにより、多数のローカル及び/又はグローバルデータラインが集積回路メモリ装置の面積を過度に占める。

## 【0015】

10

他の高速メモリ装置における読み出し及び/又は書き込みデータ経路は、特許文献1(Suzukiなどによる“半導体メモリ装置”)と特許文献2(Seigoなどによる“高速データ読み出し及びデータ書き込み動作のためにクロック信号に同期されて動作する半導体メモリ装置”)に、そして特許文献3(Ochumaなどによる“向上されたデータ書き込み動作を有するファストサイクルRAM”)に記載されている。

【特許文献1】米国特許第6,144,616号公報

【特許文献2】米国特許第6,427,197号公報

【特許文献3】米国特許出願第2001/0005012号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

20

## 【0016】

本発明の目的は、nビットプリフェッチ構造を利用して2nビットプリフェッチスキームを具現するメモリ装置を提供するところにある。

## 【0017】

本発明の他の目的は、バースト長の変化により自動プリチャージ時点を調節するメモリ装置を提供するところにある。

## 【0018】

本発明のさらに他の目的は、nビットプリフェッチ構造のメモリ装置を利用して2nビットプリフェッチスキームを具現する方法を提供するところにある。

## 【0019】

30

本発明のさらに他の目的は、バースト長の変化による自動プリチャージ制御方法を提供するところにある。

## 【課題を解決するための手段】

## 【0020】

本発明の1つの側面の集積回路メモリ装置は、N個のデータビットを並列に書き込むメモリセルアレイと外部ターミナルから2N個のデータビットを直列に受信する書き込みデータ経路とを含む。書き込みデータ経路は、2N個のデータビットを保存する2N個の書き込みデータバッファと、2N個のスイッチと、並列にN個のデータビットをメモリセルアレイに書き込むために2N個のスイッチのうち少なくともN個とメモリセルアレイを連結させるN個のデータラインとを含む。これによりローカルデータライン及びグローバルデータラインの数が減る。

40

## 【0021】

本発明の実施形態において、書き込みデータ経路は、外部ターミナルと連結される第1及び第2直列-並列変換部、N個の第1グローバルデータライン及びN個の第2グローバルデータラインを含む。本発明の実施形態において、第1直列-並列変換部は、第1内部データストローブ信号に応答し、第2直列-並列変換部は、第2内部データストローブ信号に応答する。他の実施形態において、第1及び第2直列-並列変換部は、同じ内部データストローブ信号に応答する。2N個の書き込みデータバッファは、N個の第1書き込みデータバッファとN個の第2書き込みデータバッファで構成され、2N個のスイッチは、N個の第1スイッチとN個の第2スイッチとで構成される。これら実施形態において、N個の第1

50

書き込みデータバッファは、第1直列 - 並列変換部に連結され、N個の第1グローバルデータラインのそれぞれは、N個の第1スイッチのそれぞれとN個の第1書き込みデータバッファのそれぞれとの間に連結される。これら実施形態において、N個の第2書き込みデータバッファは、第2直列 - 並列変換部に連結され、N個の第2グローバルデータラインのそれぞれは、N個の第2スイッチのそれぞれとN個の第2書き込みデータバッファのそれぞれとの間に連結される。これらの実施形態において、N個のデータラインは、N個のローカルデータラインであり、N個のローカルデータラインのそれぞれは、N個の第1スイッチ及びN個の第2スイッチとメモリセルアレイとの間にそれぞれ連結される。

#### 【0022】

これら実施形態において、書き込みデータ経路は、第1及び第2直列 - 並列変換部のうち何れか1つとN個の第1書き込みデータバッファ及びN個の第2書き込みデータバッファのうち何れか1つとの間にそれぞれ連結される第1及び第2データオーダリング回路をさらに含む。さらに、これら実施形態において、N個の第1スイッチは第1制御信号に応答し、N個の第2スイッチは第1制御信号から遅延された第2制御信号に応答する。第1及び第2制御信号は、書き込み活性化信号から異なる遅延時間をもって遅延されて生成されうる。

10

#### 【0023】

これら実施形態は、チップ選択命令及びファンクション命令に応答して書き込み活性化信号を発生させる命令デコーダと、書き込み活性化信号に応答して第1及び第2制御信号を発生させる制御信号発生部をさらに含む。命令デコーダは、チップ選択命令及び前記ファンクション命令に応答してアクティブ命令及び読出命令をさらに発生させ、命令デコーダは、チップ選択命令及びファンクション命令に応答して読出命令、リフレッシュ命令及びモードレジスタ命令をさらに発生せうる。

20

#### 【0024】

これら実施形態は、N個の第3スイッチとN個の第4スイッチをさらに含む。N個の第3スイッチのそれぞれは、第1直列 - 並列変換部とN個の第1書き込みデータバッファのそれぞれとの間に連結され、N個の第4スイッチは、第2直列 - 並列変換部とN個の第2書き込みデータバッファのそれぞれとの間に連結される。実施形態において、N個の第3スイッチは第3制御信号に応答し、N個の第4スイッチは第3制御信号から遅延された第4制御信号に応答する。第3及び第4制御信号は、データストローブ信号のオフセット立下りエッジに応答して発生する。最後に、データストローブカウンタは、データストローブ信号に応答してデータストローブ信号の立下りエッジをカウントしてデータストローブ信号のオフセット立下りエッジから第3及び第4制御信号を発生しうる。

30

#### 【0025】

本発明の他の実施形態において、書き込みデータ経路は、外部ターミナルと連結される直列 - 並列変換部とN個のグローバルデータラインとを含む。これらの実施形態において、2N個の書き込みデータバッファは、N個の第1書き込みデータバッファとN個の第2データバッファとで構成され、2N個のスイッチは、N個の第1スイッチとN個の第2スイッチとで構成される。N個の第1書き込みデータバッファは、第1直列 - 並列変換部に連結され、N個の第1書き込みデータバッファのそれぞれは、N個の第1スイッチに連結される。N個の第2書き込みデータバッファのそれぞれは、N個の第1スイッチそれぞれと連結され、N個のグローバルデータラインのそれぞれは、N個の第2スイッチのそれぞれとN個の第2書き込みデータバッファのそれぞれとの間に連結される。最後に、N個のローカルデータラインのそれぞれは、N個の第2スイッチとメモリセルアレイとの間にそれぞれ連結される。

40

#### 【0026】

これらの他の実施形態において、書き込みデータ経路は、直列 - 並列変換部とN個の第1書き込みデータバッファとの間に連結されるデータオーダリング回路をさらに含む。また、これらの実施形態は、直列 - 並列変換部とN個の第1書き込みデータバッファのそれぞれとの間に連結されるN個の第3スイッチをさらに含む。さらに、N個の第3スイッチは、第1制御信号に応答し、N個の第1スイッチは、前記第1制御信号から遅延された第2制御

50

信号に応答する。第1及び第2制御信号は、データストローブ信号のオフセット立下りエッジに応答して発生されうる。

#### 【0027】

本発明のさらに他の実施形態は、2グループのN並列ビットである2N個のデータビットをメモリセルアレイに保存するのに十分な時間にメモリセルアレイのワードラインをイネーブルさせるプリチャージ制御回路を含む。これら実施形態において、プリチャージ制御回路は、集積回路装置の第1プリチャージモードの間、2グループのN並列ビットである2N個のデータビットをメモリセルアレイに保存するのに十分な時間の間、メモリセルアレイのワードラインをイネーブルさせる。プリチャージ制御回路は、集積回路装置の第2プリチャージモードの間、1グループのN並列ビットであるN個のデータビットをメモリセルアレイに書き込むのに十分な時間の間、メモリセルアレイのワードラインを活性化させる。モードレジスタは、第1または第2プリチャージモードを選択するように設定され、プリチャージ制御回路はモードレジスタに応答する。

10

#### 【0028】

これらの実施形態において、プリチャージ制御回路は、第1及び第2遅延部で構成される。第1遅延部は、第1プリチャージモードに応答し、2グループのN並列ビットである2N個のデータビットをメモリセルアレイに保存するのに十分な時間の間、メモリセルアレイのワードラインを活性化させる。第2遅延部は、第2プリチャージモードに応答し、第1グループのN並列ビットのN個のデータビットをメモリセルアレイに書き込むのに十分な時間の間、メモリセルアレイのワードラインを活性化させる。

20

#### 【0029】

本発明の他の実施形態によれば、書き込みデータバッファの少なくとも1つは、書き込みアドレスをラッチするアドレスラッチと、アドレスラッチにラッチされた書き込みアドレスと現在のアドレスとを比較するアドレス比較部と、書き込みアドレスに対応する書き込みデータをラッチするデータラッチを含む。これらの実施形態において、現在のアドレスが読出しあドレスであり、アドレス比較部が、読出しあドレスとアドレスラッチにラッチされた書き込みアドレスとが一致していると判断する場合、メモリセルアレイではなくデータラッチから外部ターミナルに読出しデータを出力する。他の実施形態において、集積回路メモリ装置は、現在のアドレスが読出しあドレスであり、アドレス比較部が、読出しあドレスとアドレスラッチにラッチされた書き込みアドレスとが一致していないと判断する場合、メモリセルアレイから外部ターミナルに読出しデータを出力する。

30

#### 【0030】

したがって、本発明の多様な実施例による集積回路メモリ装置は多数のデータビットを並列に書き込むメモリセルアレイを含む。書き込みデータ経路は外部ターミナルから多数のデータビットを2回直列に受信し、データビットの最初の半分を並列にメモリセルアレイに書き込み、データビットの最後の2番目の半分を並列にメモリセルアレイに書き込む。

#### 【0031】

本発明の実施形態による多数のデータビットを並列に保存するメモリセルアレイを持つ集積回路装置は、外部ターミナルから複数のデータビットを直列に2回にわたって受信しながら動作する。受信されたデータビットは、複数の書き込みデータバッファに保存される。複数のデータビットの最初の半分（第1の半分）が書き込みデータバッファからメモリセルアレイに並列に書き込まれる。その後、複数のデータビットの残りの半分（第2の半分）が書き込みデータバッファからメモリセルアレイに並列に書き込まれる。

40

#### 【0032】

これら実施形態では、2回にわたるデータビットの受信において、複数のデータビットの最初の半分（第1の半分）を直列に受信してから前記複数のデータビットの残りの半分（第2の半分）を直列に受信する。複数のデータビットの最初の半分（第1の半分）が書き込みデータバッファの第1セットに保存されてから、前記複数のデータビットの残りの半分（第2の半分）が書き込みデータバッファの第2セットに保存される。最後に、第1及び第2セットの書き込みデータバッファのそれぞれから前記複数のデータビットの最初の半分

50

(第1の半分)及び残りの半分(第2の半分)が共通にローカルデータラインを通じてメモリセルアレイに書き込まれる。

#### 【0033】

本発明の他の実施形態によれば、複数のデータビットの最初の半分(第1の半分)が直列に受信されてから前記複数のデータビットの残りの半分(第2の半分)が直列に受信される。複数のデータビットの最初の半分(第1の半分)が第1書込みデータバッファに保存され、第1書込みデータバッファの前記複数のデータビットの最初の半分(第1の半分)が第2書込みデータバッファにシフトされ、第1書込みデータバッファに複数のデータビットの残りの半分(第2の半分)が保存される。第2書込みデータバッファから複数のビットデータの最初の半分(第1の半分)がメモリセルアレイに書き込まれる。第1書込みデータバッファの複数のデータビットの残りの半分(第2の半分)が第2書込みデータバッファにシフトされ、第2書込みデータバッファから複数のデータビットの残りの半分(第2の半分)がメモリセルアレイに書き込まれる。10

#### 【0034】

また、本発明の実施形態によれば、グローバルデータラインとローカルデータラインとの数を増加させずに、例えば4ビットプリフェッチ構造で8ビットプリフェッチスキームを具現することによって、チップサイズを増加させずに超高速動作が可能な集積回路メモリ装置を提供することができる。

#### 【0035】

また、本発明の実施形態によれば、例えば、4ビットプリフェッチ構造を有するメモリ装置でバースト長によってビットラインの自動プリチャージ時点を調節して、例えば、バースト長が8に対応するデータをメモリセルに書き込めるようにワードラインイネーブル時間が伸びた集積回路メモリ装置を提供することができる。20

#### 【発明の効果】

#### 【0036】

本発明によれば、 $n$ ビットプリフェッチ構造を利用して $2n$ ビットプリフェッチスキームを具現することができる。

#### 【0037】

或いは、本発明によれば、バースト長の変化により自動プリチャージ時点を調節することができる。30

#### 【0038】

或いは、本発明によれば、 $n$ ビットプリフェッチ構造のメモリ装置を利用して $2n$ ビットプリフェッチスキームを具現することができる。

#### 【0039】

或いは、本発明によれば、バースト長の変化による自動プリチャージ制御方法を提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0040】

本発明とその動作上の利点及び本発明の実施によって達成される目的を十分に理解するためには本発明の望ましい実施形態を例示する添付図面及び添付図面に記載された内容を参照すべきである。40

#### 【0041】

以下、図面を参照して本発明の望ましい実施形態を説明することによって、本発明を詳細に説明する。各図面に提示された同じ参照符号は、同様の構成要素を示す。

#### 【0042】

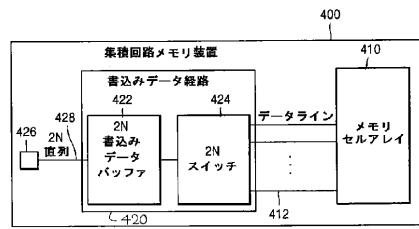

図6は、本発明の1つの実施形態の集積回路メモリ装置のブロックダイアグラムである。図6に示されたように、集積回路メモリ装置400は、N個のデータビットが並列に書き込まれるメモリセルアレイ410を含む。書き込みデータ経路420は、外部ターミナル426から直列ライン428に直列に2N個のデータビットを受信する。図6に示されたように、書き込みデータ経路420は、直列ライン428上に受信される2N個のデータビ50

ットを保存するための $2N$ 個の書込みデータバッファ422と $2N$ 個のスイッチ424とで構成される。 $N$ 個のデータライン412はまた、メモリセルアレイ410に並列に $N$ データビットを書き込むために、 $2N$ 個のスイッチ424のうち少なくとも $N$ 個をメモリセルアレイ410にする連結。

#### 【0043】

図6は、複数データビットを並列に保存するためのメモリセルアレイ410を含む集積回路メモリ装置400として具体化された本発明の1つの実施形態を示している。書込みデータ経路420は、外部ターミナル426から $2N$ 個のデータビットを並列に受信し、 $2N$ 個のデータビットをそれぞれ $N$ 個に2分したうちの一方である第1グループ（最初の半分、或いは、第1の半分）を並列にメモリセルアレイ410に保存してから、 $2N$ 個のデータビットをそれぞれ $N$ 個に2分したうちの残りである第2グループ（残りの半分、或いは、第2の半分）を並列にメモリセルアレイ410に保存する。図6は、本発明の1つの実施形態の集積回路メモリ装置400の動作方法を示している。この動作方法は、外部ターミナル426から $2N$ 個のデータビットを直列に受信し、これらを $2N$ 個の書込みデータバッファ422に保存し、書込みデータバッファ422から $2N$ 個のデータビットをそれぞれ $N$ 個に2分したうちの第1グループを並列にメモリセルアレイ410に保存してから、書込みデータバッファ422から2個のデータビットをそれぞれ $N$ 個に2分したうちの残りの第2グループを並列にメモリセルアレイ410に保存する。

#### 【0044】

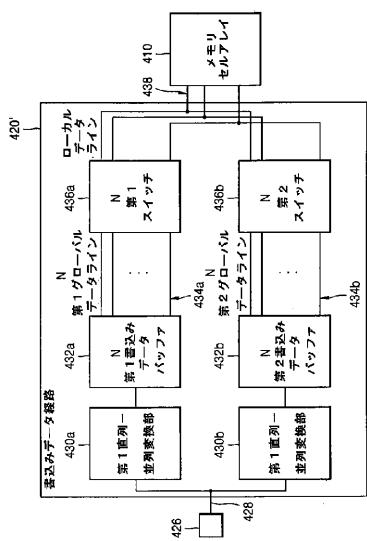

図7及び図8は、本発明の実施形態の書込みデータ経路のブロックダイアグラムである。図7に示す実施形態は、本発明の第1実施形態であり、図9乃至図12と関連して具体的に説明される。図8に示す実施形態は、本発明の第2実施形態であり、図15と21と関連して具体的に説明される。

#### 【0045】

図7を参照すれば、書込みデータ経路420'は、直列ライン428を通じて外部ターミナル426と連結される第1及び第2直列-並列変換部430a、430bで構成される。書込みデータ経路420'には、 $N$ 個の第1グローバルデータライン434aと $N$ 個の第2グローバルデータライン434bとがさらに設けられている。図6の $2N$ 個の書込みデータバッファ422は、 $N$ 個の第1書込みデータバッファ432aと $N$ 個の第2書込みデータバッファ432bとで構成される。また、図6の $2N$ 個のスイッチ424は、 $N$ 個の第1スイッチ436aと $N$ 個の第2スイッチ436bとで構成される。図7に示されたように、 $N$ 個の第1書込みデータバッファ432aは、第1直列-並列変換部430aと連結され、 $N$ 個の第1グローバルデータラインのそれぞれは、 $N$ 個の第1スイッチ436aそれぞれと $N$ 個の第1書込みデータバッファ432aのそれぞれの間に連結される。これと同様に、図7に示されたように、 $N$ 個の書込みデータバッファ432bは、第2直列-並列変換部430bと連結され、 $N$ 個の第2グローバルデータラインのそれぞれは、 $N$ 個の第2スイッチ436bのそれぞれと $N$ 個の第2書込みデータバッファ432bのそれぞれの間に連結される。最後に、図7においては、図6の $N$ 個のデータラインは、 $N$ 個のローカルデータライン438である。 $N$ 個のローカルデータライン438のそれぞれは、 $N$ 個の第1スイッチ436a及び $N$ 個の第2スイッチ436bのそれぞれとメモリセルのアレイ410との間に連結される。

#### 【0046】

外部ターミナル426を通じて直列に受信される $2N$ 個のデータビットをそれぞれ $N$ 個に2分したうちの第1グループが第1直列-並列変換部430aに保存され、外部ターミナル426を通じて直列に受信される $2N$ 個のデータビットをそれぞれ $N$ 個に2分したうちの残りの第2グループが第2直列-並列変換部430bに受信される。 $2N$ 個のデータビットのうちの $N$ 個の第1グループは、第1書込みデータバッファ432aに保存され、 $2N$ 個のデータビットのうちの残りの $N$ 個の第2グループは、第2書込みデータバッファ432bに保存される。 $2N$ 個のデータビットのうちの $N$ 個の第1グループは、第1書込みデータバッファ432aからメモリセルアレイ410に、そして、 $2N$ 個のデータビット

10

20

30

40

50

トのうちの残りの N 個の第 2 グループは、第 2 書込みデータバッファ 432b からメモリセルアレイ 410 に、ローカルデータライン 438 を通じて書き込まれる。

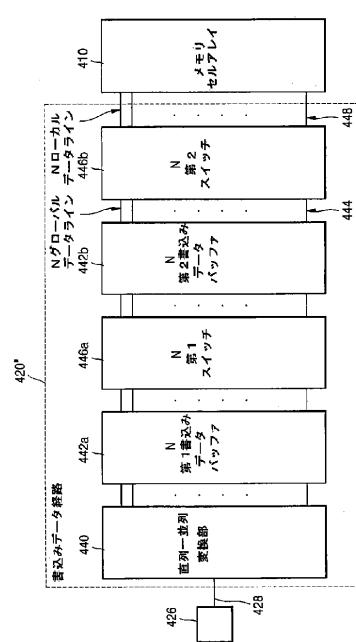

#### 【 0047 】

図 8 は、本発明の第 2 実施形態の書込みデータ経路のブロックダイアグラムである。図 8 に示されたように、書込みデータ経路 420' は、外部ターミナル 426 と連結される直列 - 並列変換部 440 を含む。書込みデータ経路 420' には、N 個の第 1 書込みデータバッファ 442a と N 個の第 2 書込みデータバッファ 442b、及び、N 個の第 1 スイッチ 446a と N 個の第 2 スイッチ 446b も提供される。N 個の第 1 書込みデータバッファ 442a のそれぞれは N 個の第 1 スイッチ 446a のそれぞれと連結される。また、N 個の第 2 書込みデータバッファ 442b は、N 個の第 2 スイッチ 446b のそれぞれと連結される。N 個のグローバルデータライン 444 のそれぞれは、N 個の第 2 スイッチ 446b のそれと N 個の第 2 書込みデータバッファ 442b のそれとの間に連結される。最後に、N 個のローカルデータライン 448 のそれぞれは、N 個の第 2 スイッチ 446b のそれとメモリセルアレイ 410 との間に連結される。

10

#### 【 0048 】

図 8 は、本発明の第 2 実施形態の動作方法を示している。この動作方法は、2N 個のデータビットをそれぞれ N 個に 2 分したうちの N 個の第 1 グループが外部ターミナル 426 から直列に受信されてから、2N 個のデータビットをそれぞれ N 個に 2 分したうちの残りの N 個の第 2 グループが外部ターミナル 426 から直列に受信される動作を示している。

20 2N 個のデータビットのうちの N 個の第 1 グループは、第 1 書込みデータバッファ 442a に保存された後、2N 個のデータビットのうちの残りの N 個の第 2 グループが第 1 書込みデータバッファ 442a に保存される際に、N 個の第 1 スイッチ 446a を通じて第 1 書込みデータバッファ 442a から第 2 書込みデータバッファ 442b にシフトされる。2N 個のデータビットのうちの N 個の第 1 グループは、N 個の第 2 スイッチ 446b を通じて第 2 書込みデータバッファ 442b からメモリセルアレイ 410 に書き込まれる。2N 個のデータビットのうちの残りの N 個の第 2 グループは、N 個の第 1 スイッチ 446a を通じて第 1 書込みデータバッファ 442a から第 2 書込みデータバッファ 442b にシフトされた後、第 2 スイッチ 446b を通じてメモリセルアレイ 410 に書き込まれる。すなわち、図 8 は、2N 個のデータビットが書込みデータ経路 420' に保存され、N 個のデータビットが並列にメモリセルアレイ 410 に書き込まれる書込みデータのパイプライン方式を示している。

30

#### 【 0049 】

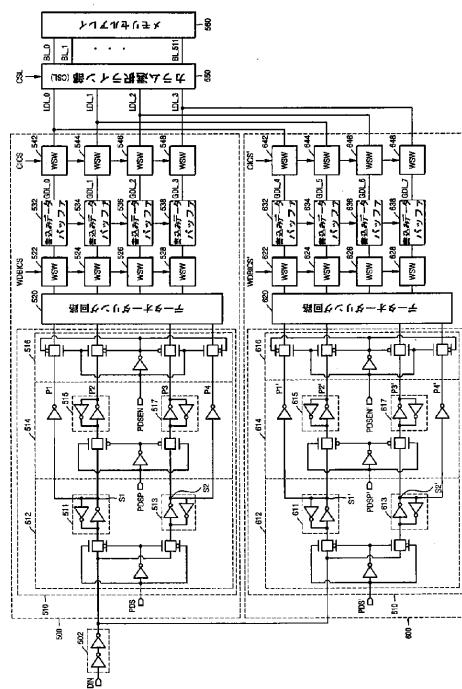

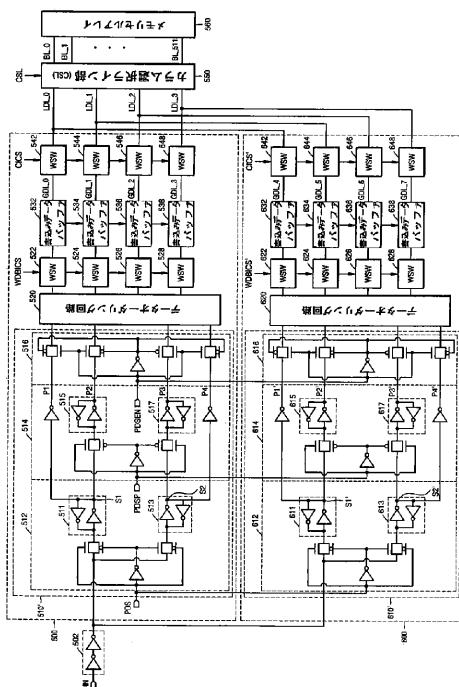

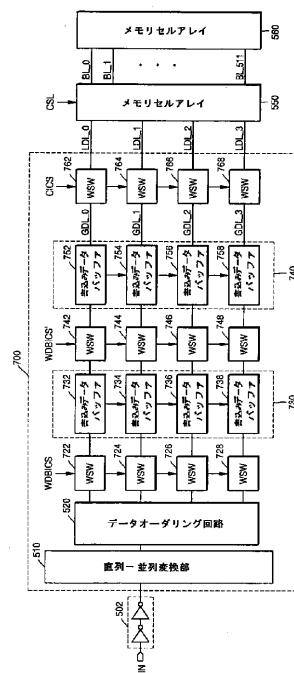

図 9A 及び図 9B は、図 7 に示す第 1 実施形態の集積回路メモリ装置の具体的なブロックダイアグラムである。図 9A 及び図 9B に示された実施形態では、バースト長が 4 (BL = 4) のスキームで 8 ビットプリフェッチ動作を行う。しかし、他の実施形態において、それより小さいかまたは大きいプリフェッチスキームとして使われうることは当業者に自明である。図 9A 及び図 9B に示されたように、8 ビットプリフェッチ動作にもかかわらず、8 個のグローバルデータライン GDL\_0 ~ GDL\_7 が使われる一方で 4 個のローカルデータライン LDL\_0 ~ LDL\_3 のみが使われる。したがって、メモリ装置のレイアウト面積は、8 ビットプリフェッチ動作を行っても、図 5 のメモリ装置に比べて減る。

40

#### 【 0050 】

図 9A を参照すれば、モードレジスタ MRS によりバースト長 = 8 (BL = 8) が選択され、BL = 8 に相当する 8 ビットの入力データが直列にバッファ 502 に受信される。バッファ 502 から出力される第 1 入力データビットは、第 1 内部データストローブ信号 PDS の立上がりエッジに応答して第 1 入力データラッチ回路 512 の第 1 ラッチ 511 に保存される。第 2 入力データビットは、第 1 内部データストローブ信号 PDS の立下りエッジに応答して第 1 入力データラッチ回路 512 の第 2 ラッチ 513 に保存される。2 つの入力データビットが第 1 入力データラッチ回路 512 に保存された後に、第 1 ラッチ

50

511の第1入力データビットと第2ラッチ513の第2入力データビットとがPDS信号の最初の立下りエッジに発生する第2内部データストローブ信号PDSPに応答して同時に並列変換部514の第3ラッチ515と第4ラッチ517とにそれぞれ伝えられる。

#### 【0051】

次いで、図9Aにおいて、第3入力データビットは、第1内部データストローブ信号PDSの第2の立上がりエッジに応答して第1入力データラッチ回路512の第1ラッチ511に保存され、第4入力データビットは、第1内部データストローブ信号PDSの第2の立下りエッジに応答して第1入力データラッチ回路512の第2ラッチ513に保存される。同時に、第3及び第4入力データビットは、PDS信号の第2の立上がりエッジ及び立下りエッジに応答して並列変換部514のP1及びP4ノードにそれぞれ伝えられる。これにより、直列入力データの4ビットが並列変換部514内のP1ないしP4として示されたように、4ビットの並列入力データに変換される。並列データ出力516は、4ビット入力データをデータオーダリング回路520に出力する。データオーダリング回路520は、4ビット並列入力データの出力順序を決定する。しかし、本発明の他の実施形態では、データオーダリング回路520を使用しない場合もある。4ビット並列データP1～P4は、複数の書き込みスイッチ(WSW)522～528に提供される第1書き込み制御信号WDBITSに応答してそれぞれの書き込みデータバッファ532、534、536、538に保存される。第1書き込み制御信号WDBITSは、図10を参照して説明されるデータストローブカウンタから発生する。

#### 【0052】

更に、バッファ502から出力される第5入力データビットは、第4内部データストローブ信号PDS'の立上がりエッジに応答して第2入力データラッチ回路612の第5ラッチ611に保存される。第6入力データビットは、第4内部データストローブ信号PDS'の立下りエッジに応答して第2入力データラッチ回路612の第6ラッチ613に保存される。第5及び第6入力データビットが第2入力データラッチ回路610に保存された後、第5及び第6ラッチ611、613内の第5及び第6入力データビットは、PDS'信号の最初の立下りエッジから発生する第5内部データストローブ信号PDSP'に応答して並列変換部614の第7及び第8ラッチ615、617にそれぞれ同時に伝えられる。

#### 【0053】

その後、第7入力データビットは、第4内部データストローブ信号PDS'の第2の立上がりエッジに応答して第5ラッチ611に保存され、第8入力データビットは、第4内部データストローブ信号PDS'の第2の立下りエッジに応答して第6ラッチ613に保存される。これと同時に、第7及び第8入力データビットは、PDS'信号の第2の立上がりエッジ及び立下りエッジにそれぞれ応答して並列変換部614のノードP1'、P4'とにそれぞれ伝えられる。これにより直列に受信される第5ないし第8入力データビットは、第5ないし第8並列データビットP1'～P4'に変換される。並列データ出力616は、4ビット並列入力データを、4ビット並列入力データの順序を決定するデータオーダリング回路620に出力する。前述したように、他の実施形態では、データオーダリング回路620を使用しない場合もある。

#### 【0054】

次いで、4ビット並列データは、第2書き込み制御信号WDBITS'に応答して複数の書き込みデータバッファ632～638に保存される。第2書き込み制御信号WDBITS'は、図10で説明されるデータストローブカウンタにより生成される。したがって、直列に受信されたデータの8ビットは、8ビットの並列データに変換され、8個の書き込みデータバッファ532～538、632～638に保存される。

#### 【0055】

したがって、図9Aに記載された本発明の実施形態では、第1直列-並列変換部510は、第1内部データストローブ信号、例えばPDS、PDSP及びPDSNに応答し、第2直列-並列変換部610は、第2内部データストローブ信号、例えばPDS'、PD

10

20

30

40

50

S P ' 及び P D S E N ' に応答する。一方、図 9 B を参照すれば、第 1 直列 - 並列変換部 510' と第 2 直列 - 並列変換部 610' は、両方とも同時に内部データストローブ信号、例えば P D S 、 P D S P 及び P D S E N に応答する。

#### 【 0 0 5 6 】

次いで、図 9 A 及び 9 B に示す集積回路メモリ装置の動作を説明する。この集積回路メモリ装置では、8 ビットの直列入力データが 8 個の書き込みデータバッファに保存された後、第 1 書込みデータバッファ 532 ~ 538 に保存された並列入力データである第 1 グループの 4 ビットは、複数の制御スイッチ ( C S W ) 542 ~ 548 に提供される第 1 スイッチング信号 C I C S に応答してそれぞれのローカルデータライン L D L \_ 0 ~ L D L \_ 3 に伝えられ、カラム選択ライン部 550 に提供されるカラム選択信号 C S L に応答して選択されるビットライン B L を通してメモリセルアレイ 560 の選択されたメモリセルに書き込まれる。次いで、第 2 書込みデータバッファ 632 ~ 638 に保存された第 2 グループの 4 ビット並列入力データは、第 2 制御スイッチ ( C S W ) 642 ~ 648 に提供される第 2 スイッチング信号 C I C S ' に応答してそれぞれのローカルデータライン L D L \_ 0 ~ L D L \_ 3 に伝えられる。10

#### 【 0 0 5 7 】

ここで、 C S W 542 ~ 548 を第 1 制御スイッチと呼び、 C S W 642 ~ 648 を第 2 制御スイッチと呼ぶ。また、 W S W 522 ~ 528 を第 3 スイッチと呼び、 W S W 622 ~ 628 を第 4 スイッチと呼ぶ。20

#### 【 0 0 5 8 】

したがって、図 9 A 及び図 9 B に示されたように、本発明の実施形態では、8 個のグローバルデータライン G D L \_ 0 ~ G D L \_ 7 と共に 4 個のローカルデータライン L D L \_ 0 ~ L D L \_ 3 のみが使われる。したがって、集積回路レイアウト面積は、従来の 8 個のグローバルデータラインと 8 個のローカルデータラインとで 8 ビットプリフェッчを行なう書き込みデータ経路に比べて減る。20

#### 【 0 0 5 9 】

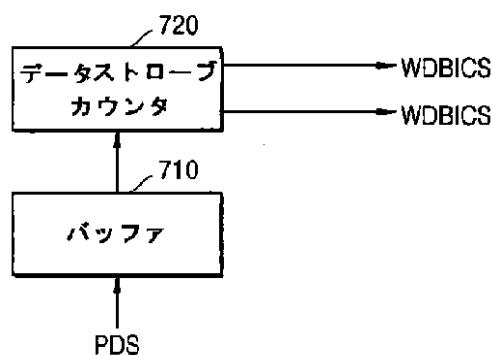

図 10 は、本発明の 1 つの実施形態における第 1 書込み制御信号 W D B I C S 及び第 2 書込み制御信号 W D B I C S ' の発生回路を説明するブロックダイアグラムである。図 10 に示されたように、書き込み制御信号は、第 1 データストローブ信号 P D S に応答するバッファ 710 と、バッファ 710 の出力に応答して第 1 データストローブ信号 P D S の立上がり及び立下りエッジ数をカウントするデータストローブカウンタ 720 とにより発生する。第 1 書込み制御信号 W D B I C S は、データストローブ信号 P D S の第 2 の立下りエッジに応答して発生し、第 2 書込み制御信号 W D B I C S ' は、データストローブ信号 P D S の第 4 の立下りエッジに応答して発生する。この実施形態により P D S E N 及び P D S E N ' 信号も生成されうる。30

#### 【 0 0 6 0 】

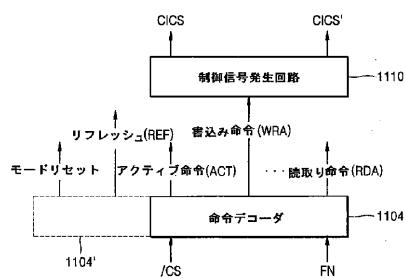

図 11 は、図 9 で説明された実施形態のためのスイッチング信号の発生回路の実施形態を説明するブロックダイアグラムである。図 11 に示されたように、スイッチング信号は、チップ選択信号 / C S とファンクション信号 F N に応答してアクティブ命令信号 A C T 、読み命令信号 R D A 及び書き込み命令信号 W R A を発生させるコマンダーデコーダ 104 を使用して発生する。制御信号発生回路 1110 は、書き込み命令信号 W R A に応答して所定の時間間隔で第 1 及び第 2 スイッチング信号 C I C S 、 C I C S ' を発生する。40

#### 【 0 0 6 1 】

次いで、本発明の他の実施形態では、図 11 の命令デコーダ 1104 は、 1104' として示され、命令デコーダ 1104 に提供されるチップ選択信号 / C S とファンクション信号と F N に応答してモードリセット命令とリフレッシュ命令 R E F をも発生する。

#### 【 0 0 6 2 】

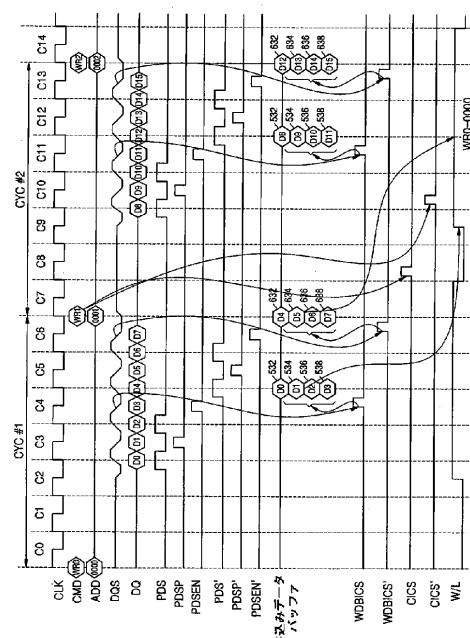

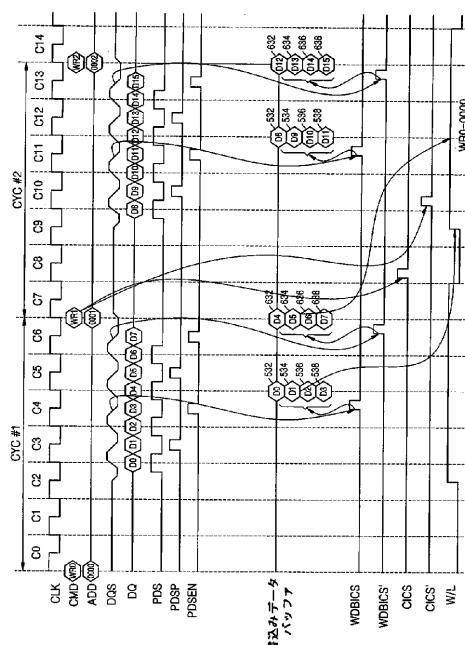

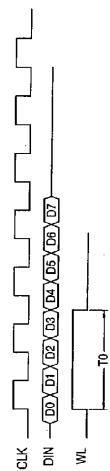

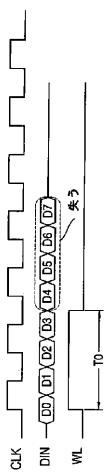

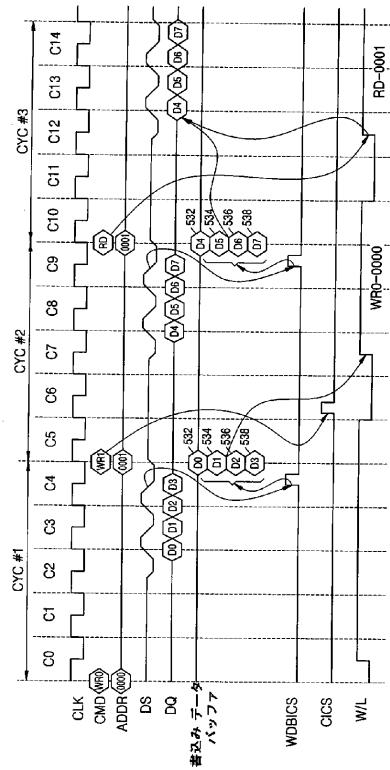

図 12 A 及び 12 B は、図 7 及び 9 A 乃至図 11 に記載された本発明の実施形態によって 8 ビットプリフェッч動作を行うタイミングダイアグラムである。さらに具体的には、図 12 A は、図 9 A のタイミングダイアグラムであり、図 12 B は図 9 B のタイミングダ50

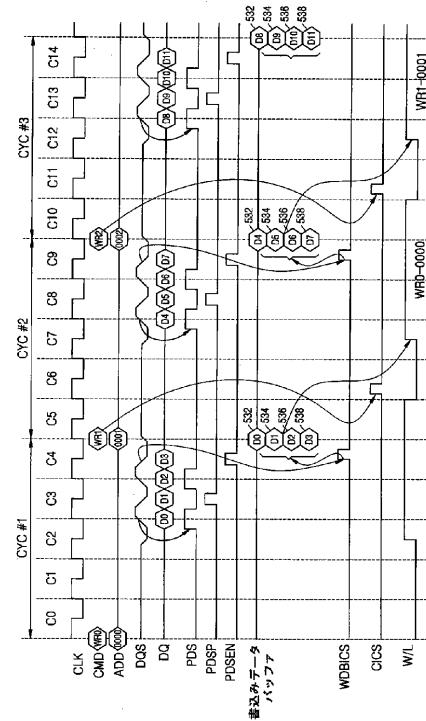

イアグラムである。これらのタイミングダイアグラムは、前述した書込みデータバッファ 532～538、632～638の動作だけでなく、多様な制御信号を説明する。これに対する比較のために、図13及び14は、図3を参照して前述したF C R A Mの4ビットプリフェッチ動作とD D R S D R A Mでの4ビットプリフェッチ動作を説明するタイミングダイアグラムである。

#### 【0063】

図13において、"0000"番地に書き込むための4ビット入力データは、以前の書き込み命令W R 0に応答して書き込まれるのではなく、次の書き込み命令W R 1を受信した後に書き込まれる。したがって、入力データは、以前のサイクルC Y C # 1で書き込みデータバッファに保存された後にサイクルC Y C # 2において次の書き込み命令W R 1に応答してメモリセルに書き込まれる。10

#### 【0064】

図14において、D D R S D R A Mでは、"0000"番地に書き込むための4ビット入力データは、図13に示されたように、次の書き込み命令W R 1に応答するのではなく、書き込み命令W R 0に応答して該当メモリセルに書き込まれる。このD D R S D R A Mは、入力データを書き込みデータバッファに保存せずに直ちにメモリセルに書き込むため、書き込みデータバッファを含まない。

#### 【0065】

図15は、図8に記載された本発明の第2実施形態のさらに具体的なブロックダイアグラムである。図8に示されたように、単にN個のグローバルデータラインとN個のローカルデータラインとを2N個の書き込みデータ経路に使用するために、書き込みデータ経路にパイプライン構成が使われる。これにより、グローバルデータラインとローカルデータラインの数は従来の書き込みデータ経路と比較して減る。20

#### 【0066】

さらに具体的には、図15を参照すれば、書き込みデータ経路700は、例えば既に図9で説明されたような直列・並列変換部510、オプションであるデータオーダリング回路520、第1スイッチ722～728、第1書き込みデータバッファ732～738、第2スイッチ742～748、第2書き込みデータバッファ752～758及び第3スイッチ762～768を含むパイプラインステージで構成される。図15に示されたように、このような実施形態は、例えば図9の実施形態よりデータラインが少数である。なぜなら、グローバルデータラインG D L \_ 0～G D L \_ 3の数は、4ビットプリフェッチスキームと同じであり、ローカルデータラインL D L \_ 0～L D L \_ 3の数は、4ビットプリフェッチスキームと同じであるためである。それゆえに、メモリ装置のレイアウト面積は減る。30

#### 【0067】

次いで、図15において、B L = 8に対応する8ビット入力データは、バッファ502を通じて直列に受信される。直列入力データの第1の4ビットは、並列入力データ回路510において4ビット並列入力データに変換され、並列入力データの第1の4ビットはオプションであるデータオーダリング回路520に提供される。データオーダリング回路520は、4ビット並列入力データの出力順序を決定する。その後、並列入力データの最初の4ビットは、書き込みスイッチ(W S W)722～728に提供される第1書き込み制御信号W D B I C Sに応答して第1書き込みデータバッファ732～738に保存される。これと同時に、直列入力データの第2の4ビットは、並列データ出力回路510から4ビットの並列入力データに変換され、もし存在するならば、データオーダリング回路520に提供される。40

#### 【0068】

次いで、第1書き込みデータバッファ732～738に保存された並列入力データの第1の4ビットは、書き込みスイッチW S W、742～748に提供される第2書き込み制御信号W D B I C S'に応答して第2書き込みデータバッファ752～758に保存される。これと同時に、データオーダリング回路520から並列ビットデータの第2の4ビットはまた、第1書き込み制御信号W D B I C Sの第2の活性化に応答して第1書き込みデータバッファ50

732～738に保存される。これにより、並列入力データの第1の4ビットと第2の4ビットとは、順次にメモリセルアレイ560に伝えられ、多数のWDBICS、WDBI<sub>C S'</sub>、CICS、CSL信号に応答して選択されたメモリセルに書き込まれる。図15に示されたように、これらのWDBICS、WDBI<sub>C S'</sub>、CICS、CSL信号は、パイプライン動作のために第1の4ビットのために、そして、第2の4ビットのために2回イネーブルされる。

#### 【0069】

次いで、本発明の実施形態のプリチャージ制御回路について説明する。このプリチャージ制御回路は、各N個の並列ビットを2グループとして、メモリセルアレイに2N個のデータビットを書き込むために十分な時間にわたってメモリセルアレイのワードラインを活性化させるために図6乃至図12及び図15の実施形態と関連して使われる。本発明の実施形態のプリチャージ制御回路を説明するために、図16を参照して従来のプリチャージ制御回路を説明する。

10

#### 【0070】

図16は、図13と共に使われる従来のプリチャージ制御回路に対するタイミングダイアグラムである。図16に示されたように、4ビットプリフェッチスキームを使用してあらゆる入力データD0、D1、D2、D3を該当メモリセルに書き込むためにワードラインを活性化させるために、ワードラインはT0時間にわたってイネーブルされる。

#### 【0071】

図17は、図5を参照して説明した8ビットプリフェッチスキームにおいてワードラインをイネーブルさせる従来の技術を示している。図17において、図5に示す8ビットプリフェッチスキームでは、8ビットが並列に書き込まれるために、図16に示す4ビットプリフェッチスキームで使われたT0時間は、メモリセルに8ビットの入力データを書き込むのに十分な時間である。なぜなら、図5において、8ビット入力データは、並列入力データに変換された後、同時に該当メモリセルに書き込まれるためである。

20

#### 【0072】

図18は、図16及び図17に示すプリチャージスキームが本発明の実施形態に適用されない理由を説明する。特に、図18に示されたように、同じプリフェッチ時間T0が本発明の実施形態に使われれば、2N個のデータビットをそれぞれN個に2分したうちのN個の第2グループは、メモリセルアレイに書き込むことができない。言い換えると、入力データD4～D7が失われる。本発明の実施形態によって、プリチャージ制御回路は、N個の並列データの2グループ分である2N個のデータビットをメモリセルアレイに書き込むのに十分な時間の間、メモリセルのワードラインを活性化させる。

30

#### 【0073】

さらに具体的には、図18に示されたように、4ビットプリフェッチスキームに使われたT0時間は、本発明の実施形態による8ビット入力データをメモリセルアレイに書き込むのに十分ではない。なぜなら、前述されたように、本発明の実施形態によれば、8ビット入力データは、同時にメモリセルに書き込まれないためである。言い換えると、8ビットの直列入力データは、第1及び第2グループに分けられるためである。4ビット直列入力データの第1グループが4ビット並列データに変換される。その後、4ビット直列入力データの第2グループが4ビット並列入力データに変換される。それにより、第1の4ビット入力データがメモリセルに並列に書き込まれた後、第2の4ビット入力データがメモリセルに並列に書き込まれる。したがって、本発明の実施形態において、ワードラインイネーブル時間は、バースト長(BL) = 4、BL = 8によって調整されねばならない。

40

#### 【0074】

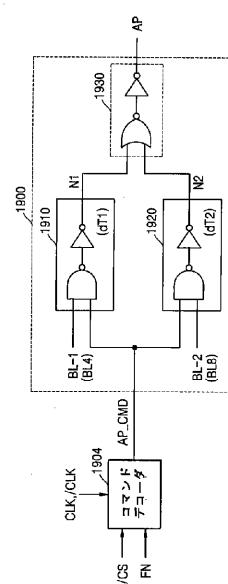

図19は、集積回路メモリ装置の第1プリチャージモードの間ににおいて、N並列ビットの2グループ分である2N個のデータビットをメモリセルアレイに書き込むのに十分な時間のためにメモリセルアレイのワードラインをイネーブルさせるプリチャージ制御回路の回路ダイアグラムである。プリチャージ制御回路1900は、集積回路メモリ装置の第2プリチャージモードの間ににおいて、N並列ビットの1つの形式であるNデータビットのグ

50

ループをメモリセルアレイに書き込むのに十分な時間にわたってメモリセルアレイのワードラインを活性化させる。

#### 【0075】

さらに具体的には、図19に示されたように、プリチャージ制御回路1900は、バースト長信号BL-1、BL-2と命令デコーダ1904が発生するプリチャージ命令信号AP\_CMDを受信した後に、プリチャージ制御信号APを出力する。命令デコーダ1904は、外部命令信号/CS、FNと外部クロック信号CLK、/CLKに応答することができる。例えば、メモリ装置が4ビットプリフェッチ(BL=4が選択された時)で動作する時は、BL-1がイネーブルされる。また、本発明の実施形態において、メモリ装置が8ビットプリフェッチ(BL=8が選択された時)で動作する時は、BL-2がイネーブルされる。10

#### 【0076】

図19に示されたように、BL=4のための遅延時間DT1は、BL=8のための遅延時間DT2より短い。したがって、第1遅延回路1910は相対的に短い第1遅延時間DT1を提供し、第2遅延回路1920は相対的に長い第2遅延時間DT2を提供する。1つの実施形態において、DT1は3.5クロックサイクルであり、一方、DT2は5.5クロックサイクルである。結合回路1930は、第1遅延回路1910及び第2遅延回路1920からプリチャージ制御信号APを提供する。したがって、BL=4のためのプリチャージ制御信号APは、BL=8のためのプリチャージ制御信号APより速く活性化されてワードラインを非活性化させる。したがって、BL=8のためのワードラインイネーブル時間は、図18に示されたT0時間と比較して長くなる。20

#### 【0077】

図13に示されたように、BL=4のためのワードラインイネーブル時間は、ほぼ3.5クロックサイクルである。一方、図12に示されたように、BL=8のためのワードラインイネーブル時間は、ほぼ5.5クロックサイクルである。1つの実施形態において、モードレジスタは、第1及び第2プリチャージモードを選択するように設定されて、プリチャージ制御回路1910は、モードレジストに応答する。

#### 【0078】

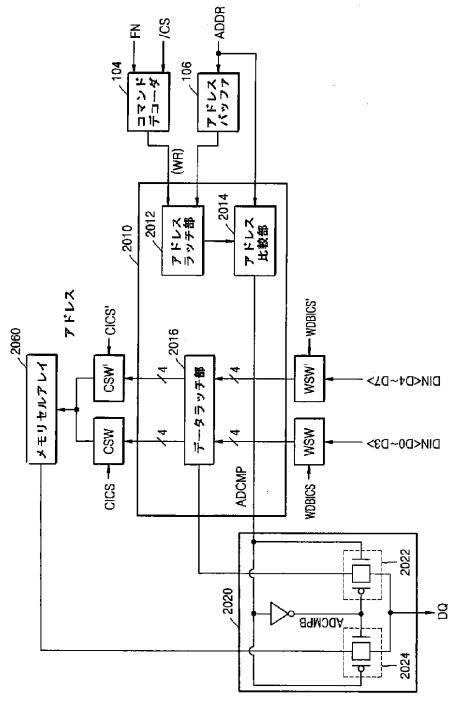

次いで、本発明の実施形態の書き込みデータバッファの追加的な事項について説明する。図20には、図6乃至9及び図15の書き込みデータバッファの1つが例示的に示されている。書き込みデータバッファ2010は、書き込みアドレスをラッチするアドレスラッチ2012を含む。アドレス比較部2014は、アドレスラッチ2012にラッチされた書き込みアドレスと現在の書き込みアドレスとを比較する。データラッチ2016は、書き込みアドレスに対応する書き込みデータをラッチする。1つの実施形態において、現在のアドレスが読み出しアドレスであり、アドレス比較部2014が読み出しアドレスとアドレスラッチ2012にラッチされた書き込みアドレスとが一致すると判断する場合、集積回路メモリ装置は、メモリセルアレイからではなく、データラッチ2016から外部ターミナルに読み出しだデータを出力する。他の実施形態において、現在のアドレスが読み出しアドレスであり、アドレス比較部2014が読み出しアドレスとアドレスラッチ2012にラッチされた書き込みアドレスとが一致していないと判断する場合、集積回路メモリ装置は、メモリセルアレイから外部ターミナルに読み出しだデータを出力する。3040

#### 【0079】

図20は、本発明の実施形態のデータ書き込み構造及び過程だけでなく、データ読み出構造及び過程も示している。書き込みデータバッファ2010は、アドレスラッチ2012、アドレス比較部2014及びデータラッチ2016を含む。アドレスラッチ2012は、命令デコーダ104のような命令デコーダから提供される書き込み命令信号WRにより制御され、アドレスバッファ106から受信される入力アドレスを保存する。これと同時に、入力アドレスに対応する入力データがデータラッチ2016に保存される。アドレス比較部2014は、アドレスラッチ2012に保存された入力アドレスと現在の入力アドレスとを比較してアドレス比較信号ADCMをDQバッファ2020に出力する。現在の入力50

アドレスが保存された入力アドレスと一致する場合、A D C M P 信号は、例えばハイレベルに活性化される。これにより、データラッチ 2 0 1 6 に保存された読出しデータが第 1 伝送ゲート 2 0 2 2 を通じて D Q パッドに出力される。しかし、現在の入力アドレスが保存された入力アドレスと異なる場合、A D C M P 信号は非活性化される。このような状況下で、メモリセルアレイに保存された読出しデータが第 2 伝送ゲート 2 0 2 4 を通じて D Q パッドに出力される。

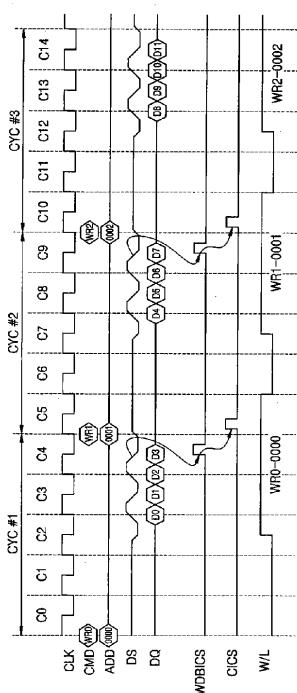

#### 【 0 0 8 0 】

図 2 1 は、図 1 5 及び図 1 8 乃至図 2 0 と連係して本発明の実施形態のデータ読出し / 書込み過程を説明するタイミングダイアグラムである。図 2 1 に示されたように、データビットのパイプライン書込みは、拡張されたワードラインイネーブル信号を含む 2 つのサイクル C Y C # 1、C Y C # 2 の間に起る。その上、図 2 1 に示されたように、メモリ装置が命令デコーダ 1 0 4 から読出命令 R D を受信すれば、図 2 0 のアドレス比較部 2 0 1 4 は、現在の入力アドレス ( 0 0 0 1 ; R D 命令入力 ) とアドレスラッチに保存された入力アドレス ( 0 0 0 1 ; W R 1 命令入力 ) とを比較する。ここでは、両者が同じアドレスであるために、読出しデータは、メモリセルアレイではなく書込みデータバッファ 5 3 2 ~ 5 3 8 から直ちに出力される。

10

#### 【 0 0 8 1 】

本発明は実施形態を通じて説明されたが、これは例示的なものに過ぎず、本技術分野の当業者であれば、これより多様な変形及び均等な他の実施形態が可能である点が理解できるであろう。したがって、本発明の真の技数的保護範囲は、特許請求の範囲の技数的思想により定められねばならない。

20

#### 【 産業上の利用可能性 】

#### 【 0 0 8 2 】

本発明による集積回路メモリ装置は、消費材及び商業上の応用に広く使われている。

#### 【 図面の簡単な説明 】

#### 【 0 0 8 3 】

【 図 1 】 従来の D R A M のブロックダイアグラムである。

【 図 2 】 図 1 のデータ入力 / 出力バスの具体的なブロックダイアグラムである。

【 図 3 】 従来のファストサイクル D R A M における 4 ビットプリフェッチスキームを説明するブロックダイアグラムである。

30

【 図 4 】 図 3 の装置の動作を説明するタイミングダイアグラムである。

【 図 5 】 8 ビットプリフェッチスキームを含む従来のファストサイクル D R A M のブロックダイアグラムである。

【 図 6 】 本発明の実施形態の集積回路メモリ装置のブロックダイアグラムである。

【 図 7 】 本発明の実施形態の書込みデータ経路のブロックダイアグラムである。

【 図 8 】 本発明の実施形態の書込みデータ経路のブロックダイアグラムである。

【 図 9 A 】 図 7 に一般的に記載された集積回路メモリ装置の具体的なブロックダイアグラムである。

【 図 9 B 】 図 7 に一般的に記載された集積回路メモリ装置の具体的なブロックダイアグラムである。

40

【 図 1 0 】 本発明の実施形態による書込み制御信号の発生を説明するブロックダイアグラムである。

【 図 1 1 】 図 9 で説明された本発明の実施形態によるスイッチング信号の発生を説明するブロックダイアグラムである。

【 図 1 2 A 】 図 7 及び図 9 A 乃至図 1 1 に記載された本発明の実施形態による 8 ビットプリフェッチ動作を説明するタイミングダイアグラムである。

【 図 1 2 B 】 図 7 及び図 9 A 乃至図 1 1 に記載された本発明の実施形態による 8 ビットプリフェッチ動作を説明するタイミングダイアグラムである。

【 図 1 3 】 ファストサイクル D R A M とデュアルデータレート D R A M とにおける従来の 4 ビットプリフェッチ動作を説明するタイミングダイアグラムである。

50

【図14】ファストサイクルDRAMとデュアルデータレートDRAMにおける従来の4ビットプリフェッチ動作を説明するタイミングダイアグラムである。

【図15】図8に一般的に記載された本発明の実施形態の具体的なロックダイアグラムである。

【図16】従来のプリチャージ制御回路のタイミングダイアグラムである。

【図17】8ビットプリフェッチスキームでワードラインをイネーブルする従来技術を説明する図である。

【図18】本発明の実施形態のフリーチャージングタイミングダイアグラムを説明する。

【図19】本発明の実施形態のプリチャージ制御回路の回路ダイアグラムである。

【図20】本発明の実施形態の読み出し/書き込みデータバッファのロックダイアグラムである。 10

【図21】本発明の実施形態のデータ読み出し/書き込みプロセスを説明するタイミングダイアグラムである。

【符号の説明】

【0084】

510 第1直列 - 並列変換部

511 BL\_0 - BL\_

512 第1入力データラッチ回路

513 第2ラッチ

514 並列変換部

20

515 第3ラッチ

516 並列データ出力

517 第4ラッチ

520 データオーダリング回路

522、524、526、528 書込みスイッチ

532、534、536、538 書込みデータバッファ

542、544、546、548 制御スイッチ

550 カラム選択ライン部

560 メモリセルアレイ

610 第2入力データラッチ回路

30

611 第5ラッチ

612 第2入力データラッチ回路

613 第6ラッチ

614 並列変換部

615、617 第7及び第8ラッチ

616 並列データ出力

620 データオーダリング回路

622、624、626、628 書込みスイッチ

632、634、636、638 書込みデータバッファ

642、644、646、648 第2制御スイッチ

40

【図1】

【図2】

【図3】

【図4】

【 四 5 】

【 四 6 】

【四七】

【 四 8 】

【図9A】

【図9B】

【 図 1 0 】

【 図 1 1 】

【図12A】

【図12B】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(74)代理人 100110364

弁理士 実広 信哉

(72)発明者 李潤相

大韓民国京畿道龍仁市駒城面麻北里526-3番地淵源マウルエルジーアパート107棟502号

(72)発明者 李禎培

大韓民国京畿道龍仁市水枝邑豊徳川里1167番地鎮山マウル三星5次アパート523棟302号

(72)発明者 羅元均

大韓民国京畿道華城郡台安邑半月里865-1番地新靈通現代タウン110棟901号

(72)発明者 金成律

大韓民国京畿道水原市長安区華西2洞674-1番地豊林アパート211棟1802号

審査官 堀江 義隆

(56)参考文献 特開平11-195296(JP,A)

特開2000-163959(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11/407

G 11 C 11/4093