(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년12월06일

(11) 등록번호 10-1683357

(24) 등록일자 2016년11월30일

(51) 국제특허분류(Int. Cl.)

*G11C 16/26* (2006.01) *G11C 16/34* (2006.01)*G11C 29/42* (2015.01)

(21) 출원번호 10-2014-7026539

(22) 출원일자(국제) 2012년03월29일

심사청구일자 2014년09월23일

(85) 번역문제출일자 2014년09월23일

(65) 공개번호 10-2014-0130192

(43) 공개일자 2014년11월07일

(86) 국제출원번호 PCT/US2012/031297

(87) 국제공개번호 WO 2013/147811

국제공개일자 2013년10월03일

(56) 선행기술조사문헌

US20110058430 A1

US20110197015 A1

US20110305099 A1

KR1020100029192 A

(73) 특허권자

인텔 코포레이션

미합중국 캘리포니아 95054 산타클라라 미션 칼리지 블러바드 2200

(72) 발명자

골드만, 매튜

미국 95630 캘리포니아주 풀솜 저랑 코트 1627

파렛, 크리쉬나 케이.

미국 94306 캘리포니아주 팔로 알토 허브바트 드 라이브 4177

(뒷면에 계속)

(74) 대리인

양영준, 백만기

전체 청구항 수 : 총 13 항

심사관 : 한선경

(54) 발명의 명칭 비휘발성 메모리의 멀티스트로브 판독을 이용하여 상태 신뢰 데이터를 획득하는 방법 및 시스템

**(57) 요 약**

장치가 비휘발성 메모리로부터 데이터를 검색하는 프로세서 회로, 및

다수의 감지 동작들에 걸쳐 메모리

셀을 판독하는 판독 동작을 설정하도록 프로세서 회로에서 작동되는 멀티스트로브 판독 모듈을 포함할 수 있고,

각 감지 동작은 상이한 감지 조건 하에 수행된다. 멀티스트로브 판독 모듈은 추가로 하나 이상의 판독 조건의

값이 미리 정해진 범위 내에 있을 때 워드라인의 재충전 없이 다수의 감지 동작들 중 이전 감지 동작의 뒤를 잇

도록 새로운 감지 동작을 스케줄링하도록 작동될 수 있다. 다른 실시예들이 개시되고 청구된다.

**대 표 도 - 도1**

(72) 발명자

칼라바드, 프라나브

미국 95129 캘리포니아주 산 호세 슬리다 드라이브

6385

프랑클린, 나단 알.

미국 94403 캘리포니아주 산 마테오 마리나 씨티

에이피티 이 1715

---

헬름, 마크

미국 95134 캘리포니아주 산 호세 노쓰 1번 스트리

트 3060

## 명세서

### 청구범위

#### 청구항 1

장치로서,

비휘발성 메모리로부터 데이터를 검색하는 프로세서 회로; 및

다수의 감지 동작들 - 각 감지 동작은 상이한 감지 조건 하에 수행됨 - 에 걸쳐 메모리 셀을 판독하는 판독 동작을 설정하고,

하나 이상의 판독 조건의 값이 미리 정해진 범위 내에 있을 때 워드라인의 재충전 없이 상기 다수의 감지 동작들 중 이전 감지 동작의 뒤를 있도록 새로운 감지 동작을 스케줄링하도록

상기 프로세서 회로에서 작동가능한 멀티스트로브 판독 모듈

을 포함하고,

상기 멀티스트로브 판독 모듈은 연속되는 감지 동작들 사이의 상기 워드라인의 램핑의 기간이 제1 문턱치를 초과하는 경우에 비트라인 방전 경로를 디스에이블시키도록 상기 프로세서 회로에서 작동가능한 것인 장치.

#### 청구항 2

제1항에 있어서, 상기 멀티스트로브 판독 모듈은 다수의 판독 동작들을 수행함으로써 판독된 데이터의 오류율에 기초하여 상기 메모리로부터 데이터를 판독하기 위해 적용될 하나 이상의 판독 파라미터를 선택적으로 조정하도록 작동가능하고, 상기 하나 이상의 판독 파라미터는 상기 비휘발성 메모리의 비트라인 방전 경로의 상태, 상기 비휘발성 메모리의 메모리 셀을 판독하기 위한 워드라인의 워드라인 전압 레벨, 및 비트라인의 프리차지 레벨을 포함하는 것인 장치.

#### 청구항 3

제1항에 있어서, 상기 멀티스트로브 판독 모듈은

상기 다수의 감지 동작들의 결과들을 인코딩된 상태 신뢰 데이터로서 저장하기 위해 전송하고,

상기 다수의 감지 동작들의 완료 후에만 상기 저장된 인코딩된 상태 신뢰 데이터가 외부 장치로 전송되게 스케줄링하도록

상기 프로세서 회로에서 작동가능한 것인 장치.

#### 청구항 4

삭제

#### 청구항 5

제1항에 있어서, 상기 멀티스트로브 판독 모듈은 상기 메모리 셀의 논리 상태를 검증할 때 존재한 상기 워드라인의 전압과 후속 판독 동작을 위한 상기 워드라인의 예상 전압 간의 차이가 제2 문턱치를 초과하는 경우에 워드라인 전압을 조정하도록 상기 프로세서 회로에서 작동가능한 것인 장치.

#### 청구항 6

제1항에 있어서, 상기 멀티스트로브 판독 모듈은 제1 감지 동작과 다음 감지 동작 사이에 워드라인 전압을 조정하기 위해 할당된 시간이 제3 문턱치를 초과하는 경우에 비트라인의 프리차지 레벨이 조정되고 상기 비트라인이 재충전되도록 지시하도록 상기 프로세서 회로에서 작동가능한 것인 장치.

#### 청구항 7

제1항에 있어서, 상기 멀티스트로브 판독 모듈은 상기 판독 동작 중의 비트라인 전압의 변화가 제5 문턱치를 초과하는 경우에, 감지 동작의 감지 펄스 중에 이용될 기준 전압의 값과, 상기 감지 펄스의 기간 중 하나 이상을 조정하도록 상기 프로세서 회로에서 작동가능한 것인 장치.

#### 청구항 8

제1항에 있어서, 상기 멀티스트로브 판독 모듈은 상기 판독 동작 중의 워드라인 전압의 변화가 제6 문턱치를 초과하는 경우에, 감지 동작의 감지 펄스 중에 이용될 기준 전압의 값과, 상기 감지 펄스의 기간 중 하나 이상을 조정하도록 상기 프로세서 회로에서 작동가능한 것인 장치.

#### 청구항 9

컴퓨터에 의해 구현되는 방법으로서, 상기 방법은,

다수의 감지 동작들 - 각 감지 동작은 상이한 감지 조건 하에 수행됨 - 에 걸쳐 비휘발성 메모리의 메모리 셀을 판독하는 판독 동작을 설정하는 것,

하나 이상의 판독 조건의 값이 미리 정해진 범위 내에 있을 때 워드라인의 재충전 없이 상기 다수의 감지 동작들 중 이전 감지 동작의 뒤를 잇도록 새로운 감지 동작을 스케줄링하는 것, 및

연속되는 감지 동작들 사이의 상기 워드라인의 램핑의 기간이 제1 문턱치를 초과하는 경우에 비트라인 방전 경로를 디스에이블시키는 것

을 포함하는 멀티스트로브 판독 동작을 수행하는 단계

를 포함하는, 컴퓨터에 의해 구현되는 방법.

#### 청구항 10

제9항에 있어서, 다수의 판독 동작들을 수행함으로써 판독된 데이터의 오류율에 기초하여 상기 비휘발성 메모리로부터 데이터를 판독하기 위해 적용될 하나 이상의 판독 파라미터를 선택적으로 조정하는 단계를 포함하고, 상기 하나 이상의 판독 파라미터는 상기 비휘발성 메모리의 비트라인 방전 경로의 상태, 상기 비휘발성 메모리의 메모리 셀을 판독하기 위한 워드라인의 워드라인 전압 레벨, 및 비트라인의 프리차지 레벨을 포함하는 것인, 컴퓨터에 의해 구현되는 방법.

#### 청구항 11

제9항에 있어서,

상기 다수의 감지 동작들의 결과들을 인코딩된 상태 신뢰 데이터로서 저장하기 위해 전송하는 단계 - 각 감지 조건은 감지 전압과 감지 펄스 기간의 조합을 포함함 -; 및

상기 다수의 감지 동작들의 완료 후에만 상기 저장된 인코딩된 상태 신뢰 데이터가 외부 장치로 전송되게 스케줄링하는 단계

를 포함하는, 컴퓨터에 의해 구현되는 방법.

#### 청구항 12

삭제

#### 청구항 13

제9항에 있어서, 상기 메모리 셀의 논리 상태를 검증할 때 존재한 상기 워드라인의 전압과 후속 판독 동작을 위한 상기 워드라인의 예상 전압 간의 차이가 제2 문턱치를 초과하는 경우에 워드라인 전압을 조정하는 단계를 포함하는, 컴퓨터에 의해 구현되는 방법.

#### 청구항 14

제9항에 있어서, 판독 동작 중의 워드라인 전압의 변화가 제5 문턱치를 초과하는 경우에, 감지 동작의 감지 펄스 중에 이용될 기준 전압의 값과, 상기 감지 펄스의 기간 중 하나 이상을 조정하는 단계를 포함하는, 컴퓨터에

의해 구현되는 방법.

### 청구항 15

제9항 내지 제11항, 제13항 및 제14항 중 어느 한 항의 방법을 수행하기 위한 수단을 포함하는 장치.

### 청구항 16

삭제

### 청구항 17

삭제

### 청구항 18

삭제

### 청구항 19

삭제

### 청구항 20

삭제

## 발명의 설명

### 배경 기술

[0001]

메모리 장치들의 셀 치수들이 더 작은 치수들로 스케일링됨에 따라, 데이터 저장의 무결성(integrity)이 도전받고 있다. 특히, NAND 플래시 메모리 등의 비휘발성 메모리 장치들에서의 RBER(raw bit error rate)은 셀 사이즈가 감소함에 따라 증가하는 것으로 관찰되었다. NAND 기술은 정상적인 장치 동작 중에 자연적으로 고장날 수 있는 비트들을 보상하기 위해 오류 정정 코드(ECC) 프로세스에 의지한다.

[0002]

허용 가능한 비트 오류율을 달성하기 위하여, 보통 시스템 레벨에서 오류 정정 엔진이 사용된다. 최근 세대의 NAND 제품들에서 사용되고 있는 가장 흔한 ECC는 소위 BCH 코드(이 두문자어는 발명자의 이름 Bose, Ray-Chaudhuri, 및 Hocquenghem에서 유래한 것임)를 사용한다. 그러나, BCH 코드는 셀 사이즈가 더 작은 차세대 NAND 제품들에서 요구될 수 있는 오류 정정 능력을 발휘하지 못할 수 있다.

[0003]

다른 한편으로, 저밀도 패리티 체크(low density parity check, LDPC) 등의 오류 코드들은 더 큰 능력을 제공하지만 NAND 메모리가 종래의 사용자 데이터와는 다른 방식으로 데이터를 제공할 것을 요구한다. BCH 모델과 다르게, LDPC 코드는 각각의 비트 값에 대하여, 비트의 신뢰도의 추정을 제공하는 데이터인 소위 상태 신뢰 데이터를 제공하는 것을 수반한다. LDPC는 BCH에 비하여 상당한 정정 능력 이득들을 낼 수 있는데, 그 이유는 디코더가 어느 비트들이 플립될 가능성이 더 많은지를 결정할 수 있고 이 정보를 그것의 정정 알고리즘들에서 이용할 수 있기 때문이다. 그러나, 성능에 과도하게 영향을 주지 않고 메모리로부터 상태 신뢰 데이터를 생성하는 효율적인 방법들은 없다.

[0004]

따라서, 이러한 문제들 및 기타 문제들을 해결하는 개선된 기법들 및 장치가 필요할 수 있다.

### 도면의 간단한 설명

[0005]

도 1은 시스템 실시예의 블록도를 도시한다.

도 2는 또 다른 시스템 실시예의 블록도를 도시한다.

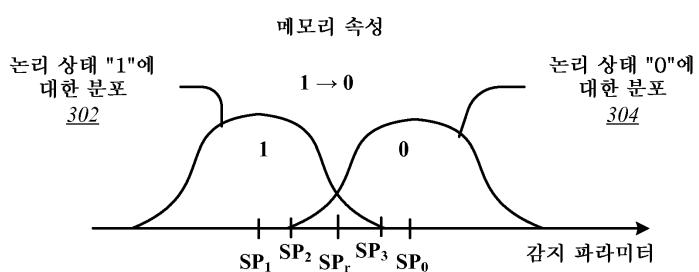

도 3은 메모리 속성들의 예를 도시한다.

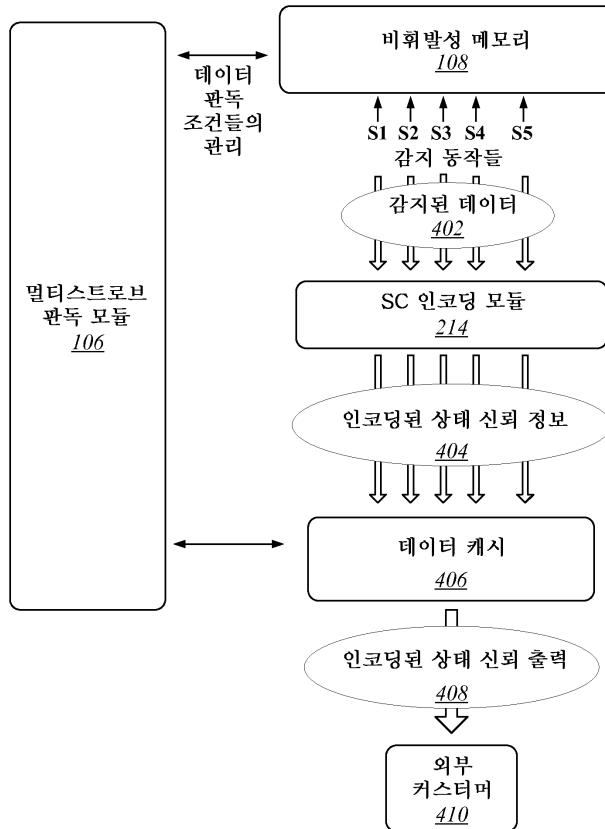

도 4는 예시적인 시스템 배열의 동작을 도시한다.

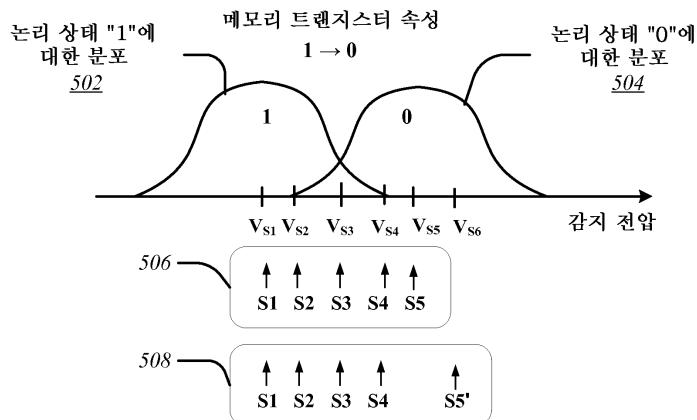

도 5는 메모리 속성들의 또 다른 예를 도시한다.

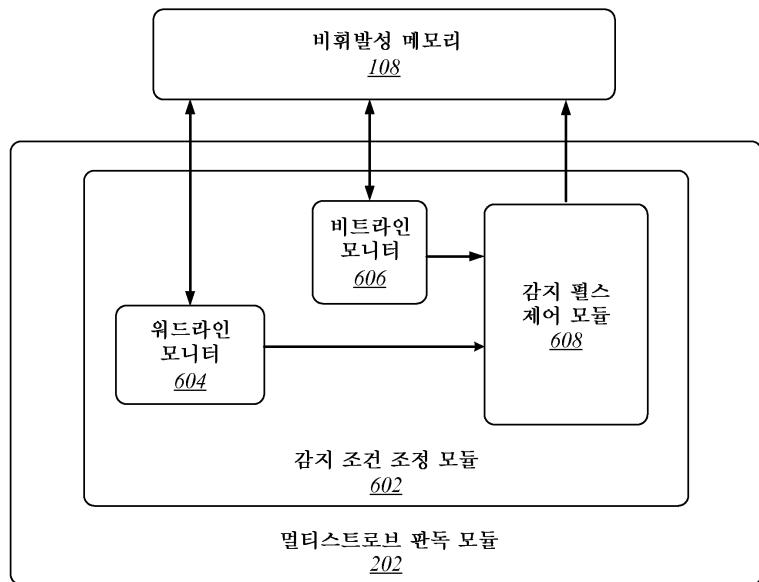

도 6은 도 5의 메모리를 판독하기 위한 예시적인 시스템을 도시한다.

도 7a는 멀티레벨 메모리 내의 데이터 저장에 대한 예를 도시한다.

도 7b는 도 7a의 멀티레벨 메모리를 판독하기 위한 시나리오를 도시한다.

도 8은 메모리를 판독하기 위한 예시적인 시스템의 동작을 도시한다.

도 9는 예시적인 제1 논리 흐름을 나타낸다.

도 10은 예시적인 제2 논리 흐름을 나타낸다.

도 11은 예시적인 시스템 실시예에 대한 도면이다.

### 발명을 실시하기 위한 구체적인 내용

[0006]

다양한 실시예들은 데이터를 판독하는 새로운 시스템, 장치, 및 방법들을 수반한다. 특히, 본 실시예들의 방법들 및 장치는 저장된 데이터를 처리하여 데이터 오류의 가능성을 결정할 수 있다. 다양한 실시예들은 더 정확하고 효율적인 오류 정정이 적용될 수 있도록 상태 신뢰 데이터의 생성 및 해당 데이터의 처리에 관련된다. 특히, 실시예들은 효율적이고 시기적절한 방식으로 상태 신뢰 데이터를 생성하기 위해 메모리의 다중 감지를 수반하는 판독 동작들을 수행하는 방법들에 관련된다. 달리 지적하지 않는 한, "상태 신뢰 데이터"와 "상태 신뢰 정보"라는 용어들은 호환 가능하고, "신뢰"와 "상태 신뢰"라는 용어들도 호환 가능하게 사용될 수 있다.

[0007]

다양한 실시예들에서, 정정될 데이터는 NAND 플래시 메모리, 상 변화 메모리(PCM), 스핀 메모리, 스위치를 가진 상 변화 메모리(phase change memory with switch, PCMS), 자기저항 랜덤 액세스 메모리(MRAM), 스핀 메모리, 나노와이어 메모리, 강유전성 트랜지스터 랜덤 액세스 메모리(FeTRAM), 또는 메모리에 저장된 정보에 관한 상태 신뢰 데이터를 추출하는 것이 바람직할 수 있는 다른 메모리 등의 비휘발성 메모리 어레이에 저장될 수 있다.

[0008]

NAND 플래시 메모리 등의 비휘발성 메모리에서, 플로팅-케이트 트랜지스터들은 소정의 메모리 셀을 제어하는 플로팅-케이트 트랜지스터를 온시키기 위해 필요한 문턱 전압( $V_T$ )을 제어하는 전하를 저장하는 데 이용된다. 소정의 메모리 셀에 대한  $V_T$  레벨은 차례로 해당 메모리 셀의 논리 상태를 결정하는 데 이용된다. NAND 플래시 아키텍처에서는, 메모리 어레이가 몇몇 트랜지스터가 직렬로 연결되어 있는 워드 라인들 및 비트 라인들에 연결된다. 모든 워드 라인들이 (트랜지스터의  $V_T$ 보다 높은) 하이로 풀링되는(pulled high) 경우에만 비트 라인이 로우로 풀링된다(pulled low). 판독 동작을 수행하기 위해, 워드 라인들의 대부분이 프로그램된 비트의  $V_T$  위로 풀업되는 반면, 하나는 소거된 비트의  $V_T$  바로 위로 풀업된다. 선택된 비트가 프로그램되지 않은 경우에는 직렬 그룹이 도통(그리고 비트 라인을 로우로 풀링)할 것이다.

[0009]

NAND 플래시의 메모리 사이즈가 증가함에 따라, 인접 셀들 간의 분리는 감소하고, 위에 언급한 바와 같이, 오류 생성의 가능성이 증가한다. 이러한 문제를 해결하기 위해, 다양한 실시예들은 메모리 셀의 논리 상태가 더 정확하고 효율적으로 결정될 수 있도록 NAND 장치들을 판독하는 개선된 방법들을 제공한다. 특히, 아래에 상세 기술되는 바와 같이, 본 실시예들은 LDPC와 같은 진보된 기법들에 따라 오류 정정을 수행하는 데 이용될 수 있는 상태 신뢰 정보를 생성하기 위해 메모리 셀에 대해 다중 감지 동작들을 수행하는 것을 수반하는 데이터 판독 동작들을 효율적으로 관리하기 위한 새로운 절차들을 제공한다.

[0010]

다양한 실시예들에서, 메모리 셀에 데이터 감지 동작들의 반복 적용을 통해 LDPC 엔진에 의한 처리를 위한 데이터가 생성될 수 있는데 각 감지 동작 사이에 감지 조건들은 변경되어야 한다. 각 감지 동작과 함께, 해당 감지 동작에 앞서 하나 이상의 다른 판독 파라미터가 조정될 수 있다. 데이터 감지 동작들이 완료된 후에, 외부 제어기와 같은 외부 장치(본 명세서에서 "커스터머"라고도 함)에 파싱하기 위해 다중 감지 동작들의 결과들로부터의 상태 신뢰 정보가 인코딩되어 저장될 수 있다.

[0011]

뒤에 나올 도면들에 관하여 상세 설명된 바와 같이, 다양한 실시예들에서, 상태 신뢰 정보는 다중 감지 동작 판독 절차의 모든 감지 동작들이 수행될 때까지 외부 장치에 데이터를 파싱하지 않고 각 감지 동작 후에 데이터를 감지하고 인코딩하는 멀티스트로브 판독 프로세스에 의해 제공될 수 있다. 게다가, 감지 동작들 사이에 필요에 따라 다양한 판독 파라미터들이 조정될 수 있다. 이것은 필요하다고 판단되는 경우를 제외하고, 워드라인 전압의 조정 및 비트라인의 제충전을 방지하는 능력을 포함한 몇 가지 이점을 제공할 수 있다. 이런 식으로, 각 감지 조건 하에 판독 동작들이 최적화되면서 각 감지 동작이 효율적인 방식으로 순환될 수 있다. 이러한 멀티스

트로브 판독 프로세스는, 다수의 감지 동작들 각각 이후에 상태 신뢰 데이터가 생성되고 외부 장치에 파싱 출력될 수 있는, 순차적 감지 절차와 대비된다. 후자의 프로세스에서는, 각 감지 동작 후에 워드라인 전압도 조정되고, 이어서 다음 감지 절차에 대비하여 비트라인 및 워드라인이 충전될 수 있어, 결과적으로 다수의 감지 동작들을 순환하는 데 비교적 더 긴 기간이 걸릴 수 있다.

[0012] 더욱이, 본 실시예들은 감지 동작들 사이에 다수의 판독 파라미터들 중 하나 이상을 모니터링하고 조정하는 용통성을 가진 시스템을 제공한다. 그러한 판독 파라미터들은 비트라인 프리차지 상태, 감지 전압, 감지 시간, 워드라인 전압, 비트라인 전압을 포함할 수 있다. 일부 실시예들에서, 시스템은 메모리의 셀의 다중 감지의 프로세스 동안에 비트라인 재충전이 일어나야 하는지를 판정하고, 만일 그렇다면, 어느 감지 동작들 사이에 비트라인 재충전이 수행되어야 하는지를 판정하는 능력을 제공한다. 다른 실시예들은 비트라인 방전 경로가 인에이블된 상태로 있어야 하는지를 판정하고, 상태 신뢰 정보를 포함하는 데이터를 외부 장치에 파싱 출력하기 전에 몇 개의 감지 동작이 일어나야 하는지를 판정하는 능력을 제공한다.

[0013] 본 실시예들에 따른 방법들은 오류 정정 성능을 최적화시키기 위해 외부 장치에 의해 이용될 수 있는 설계 기준들을 제공한다. 일부 실시예들에서, 방법들은 오류 정정을 포함하는 데이터 판독 프로세스에 의해 생성되는 오류율과 같은 속성을 개선하거나 최소화시키기 위하여 멀티스트로브 판독 프로세스 동안에 하나 이상의 판독 파라미터를 최적화시키기 위해 멀티스트로브 판독 프로세스를 이용할 수 있다. 설계 기준들은 커스터머의 필요에 따라 성능이 조정될 수 있도록 판독 파라미터들에 대한 상이한 조정 조합들을 제공할 수 있다.

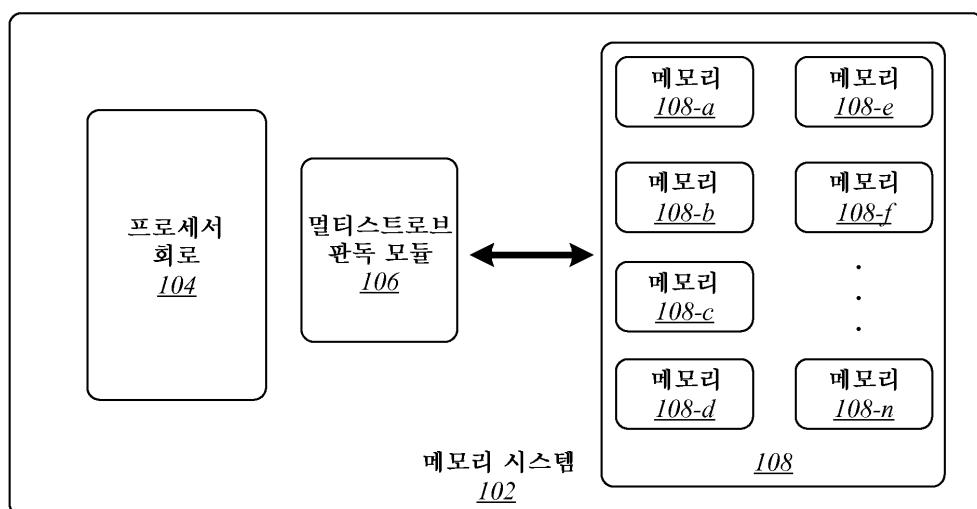

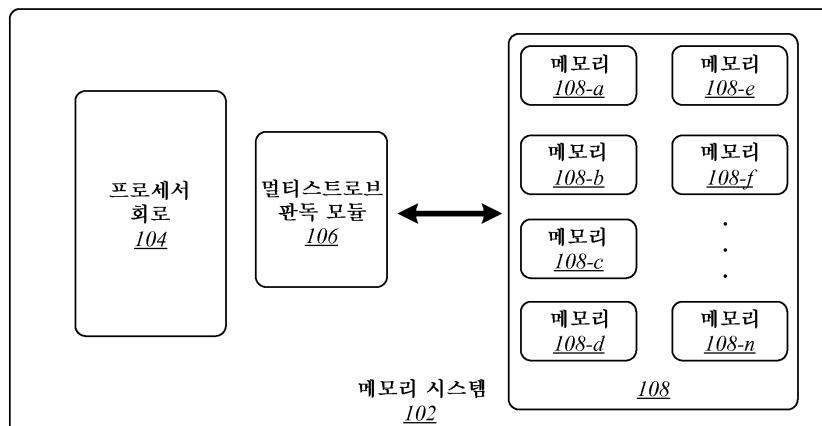

[0014] 도 1은 메모리의 멀티스트로브 판독을 수행하기 위해 이용될 수 있는 메모리 시스템(102)의 실시예를 나타낸다. 멀티스트로브 판독 절차에서는, 메모리 셀과 같은 비휘발성 메모리 요소의 판독이, 메모리 셀의 다중 감지 동작들을 수행하고, 감지 동작들 사이에 감지 조건들을 변경하고, 각 감지 동작 후에 인코딩된 데이터를 저장하고, 모든 감지 동작이 완료된 후에만 인코딩되어 저장된 데이터를 파싱 출력함으로써 수행될 수 있다. 메모리 시스템(100)은 프로세서 회로(104), 멀티스트로브 판독 모듈(106), 및 비휘발성 메모리(108)를 포함하며, 비휘발성 메모리(108)는 다수의 메모리 유닛(108-a 내지 108-n)을 포함할 수 있고, 여기서 a, b, c, d, e, f, 및 n은 임의의 양의 정수를 나타내고 동일한 또는 상이한 정수들을 나타낼 수 있다.

[0015] 메모리 시스템(102)은 비휘발성 메모리(108)로부터 판독될 데이터를 요청하는 외부 장치(미도시)에 연결될 수 있다. 비휘발성 메모리(108)로부터 판독될 데이터가 상태 신뢰 정보를 포함한다면, 멀티스트로브 판독 모듈(106)은 데이터와 함께 상태 신뢰 정보를 외부 장치에 제공하기 위하여 비휘발성 메모리(108)에 대해 멀티스트로브 판독 프로세스가 수행되어야 한다고 결정할 수 있다.

[0016] 특히, 멀티스트로브 판독 모듈은 각 감지 동작 동안 약간 상이한 감지 조건들 하에 요청된 데이터를 감지하는 일련의 감지 동작들을 관리할 수 있다. 더욱이, 후술하는 바와 같이, 멀티스트로브 판독 모듈(106)은, 일련의 감지 동작들 전부가 완료될 때까지 데이터/상태 신뢰 정보가 외부 장치에 파싱되게 하지 않고, 캐시와 같은 로컬 저장소에 인코딩 및 저장을 위해 메모리 판독으로부터의 데이터 및 상태 신뢰 정보를 제공할 수 있다.

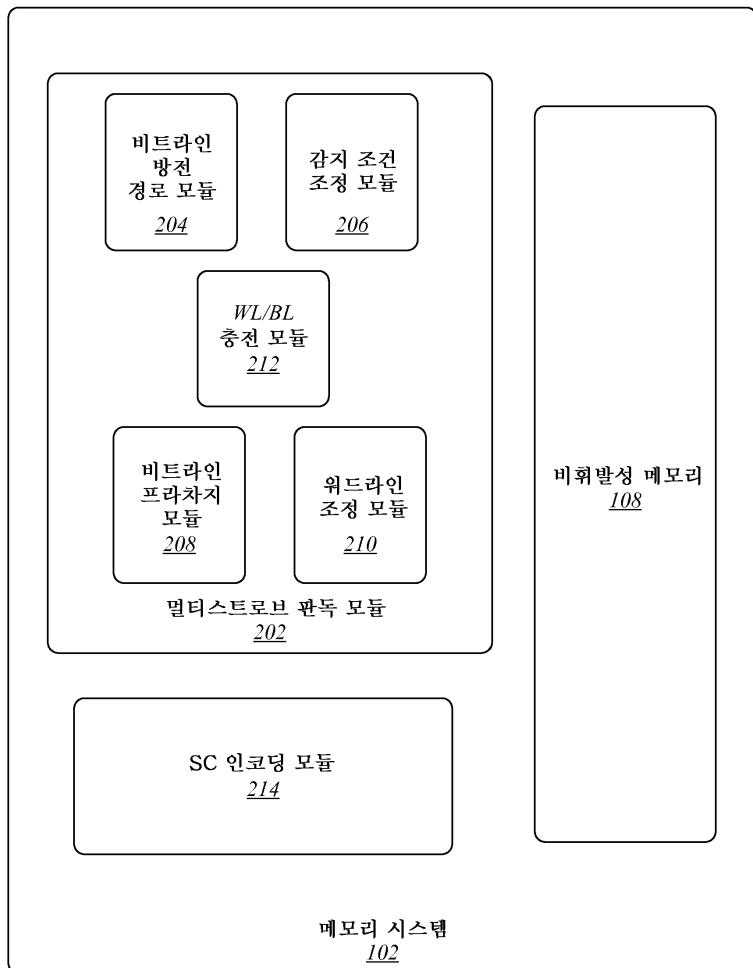

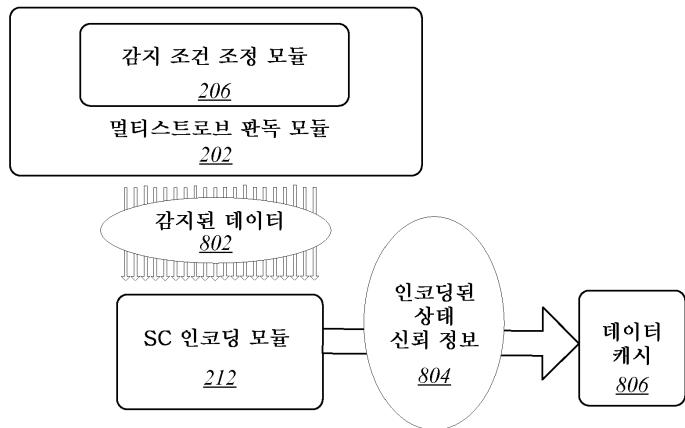

[0017] 도 2는 멀티스트로브 판독 모듈(202)의 세부 사항들을 포함하는 메모리 시스템(102)의 실시예의 블록도를 나타낸다. 도시된 바와 같이, 멀티스트로브 판독 모듈(202)은 비트라인 방전 경로 모듈(204), 감지 조건 조정 모듈(206), 비트라인 프리차지 모듈(208), 워드라인 조정 모듈(210), 워드라인/비트라인(WL/BL) 충전 모듈(212) 등의 다수의 구성요소를 포함할 수 있다. 본 실시예들에 따라, 멀티스트로브 판독 모듈(202)뿐만 아니라 그것의 구성요소들은 하드웨어, 소프트웨어, 또는 하드웨어와 소프트웨어의 조합을 포함할 수 있다. 그 구성요소들 각각은 멀티스트로브 판독 동작을 수행하기 위한 판독 조건들을 조정하기 위해, 그리고 특히, 멀티스트로브 판독 동작의 각 감지 동작 사이에 판독 조건들을 조정하기 위해 이용될 수 있다. 따라서, 상태 신뢰 데이터를 포함하는 데이터가 메모리 주소로부터 판독되어야 하는 경우, 멀티스트로브 판독 모듈은 비트라인 방전 경로 모듈(204), 감지 조건 조정 모듈(206), 비트라인 프리차지 모듈(208), WL/BL 충전 모듈(212), 및 워드라인 조정 모듈(210) 중 하나 이상을 이용하여 멀티스트로브 판독 동작의 모든 감지 동작이 완료될 때까지 판독 조건들을 제어할 수 있다.

[0018] 도 2에 추가로 도시된 바와 같이, 메모리 시스템(102)은 일련의 감지 동작들의 각 감지 동작의 결과들을 수신하고, 그 결과들을 다중 비트 인코딩된 출력으로서 인코딩하도록 배열된 상태 신뢰(SC) 인코딩 모듈(214)을 포함할 수 있다. 인코딩된 출력은 그 후 일련의 감지 동작들이 완료된 후에 외부 장치에 파싱될 수 있다.

[0019] 상태 신뢰 인코딩 모듈(214)은 위에 언급한 LPDC 절차와 같은 ECC 동작을 수행하기 위하여 오류 정정 코드(ECC) 엔진(미도시)에 의해 처리될 상태 신뢰 데이터를 제공하도록 동작할 수 있다. 이것은 오류율이 상당할 정도로

셀 사이즈가 작은 고밀도 메모리들을 관독하는 데 유용할 수 있는데, BCH 등의 전통적인 코드들은 그러한 메모리들로부터 관독된 데이터를 정정하기 위해 적용될 때 무효하게 된다.

[0020] 플래시 NAND 등의 메모리 어레이들의 스케일링 증가의 하나의 결과는 하나의 논리 상태와 또 하나의 논리 상태를 구별하기가 어렵다는 것이다. 플래시 NAND 메모리에서, 각 메모리 셀은 논리 "0"과 논리 "1"을 구별하는 방식으로 전하를 저장하는 데 이용되는 플로팅 게이트 트랜지스터에 의해 제어된다. 메모리 셀의 논리 상태는 플로팅 게이트 트랜지스터를 온시키기 위해 필요한 문턱 전압으로 특징지어질 수 있고, 그것은 차례로 플로팅 게이트에 존재하는 전하의 양에 의해 제어된다. 메모리 어레이에서, 제1 논리 상태의 메모리 셀들은 제1 공칭 문턱 전압으로 설정될 수 있는 반면, 제2 논리 상태의 메모리 셀들은 제2 공칭 문턱 전압으로 설정된다. 관독 프로세스 동안에, 감지 전압은 제1 논리 상태로 설정된 플로팅 게이트 트랜지스터들을 온시키기에는 충분하지만 제2 논리 상태로 설정된 플로팅 게이트 트랜지스터들을 온시키기에는 충분하지 않은 문턱 전압에 대응하는 기준 전압으로 설정될 수 있다. 따라서, 감지 전압을 기준 전압에 둘으로써 NAND 메모리의 블록이 관독될 때, 해당 블록에서 제2 논리 상태로 설정되어 있는 페이지들 내의 모든 메모리 셀들의 트랜지스터들은 오프 상태로 있어야 한다.

[0021] 그러나, 전형적인 메모리 어레이들에서, 상이한 메모리 셀들은 문턱 전압들의 범위(분포)에 걸쳐 있는 상이한 문턱 전압을 나타낸다. 더욱이, 현세대 및 차세대 플래시 NAND 메모리에서, 제1 논리 상태에 대한 문턱 전압의 분포는 제2 논리 상태에 대한 문턱 전압의 분포와 의도치 않게 겹칠 수 있다. 그러한 상황에서는, 감지 기준 전압을 그 2개의 분포의 평균 값들 사이의 중간점에 두는 감지 동작에 기초하여 메모리 셀의 실제 논리 상태를 결정하는 것은 가능하지 않거나 어려울 수 있다. 그러한 경우에, 소정의 메모리 셀의 일련의 감지 측정을 수행하고 그러한 감지 측정의 결과들을, 데이터를 올바르게 평가하고 필요에 따라 정정하기 위하여, LDPC 엔진 등의 ECC 엔진에 의해 처리될 수 있는 상태 신뢰 데이터의 형태로 제공하는 것이 바람직할 수 있다.

[0022] 그렇게 함으로써 메모리 시스템(102)은 플래시 NAND 메모리 장치 등의 장치들에서의 관독 성능이 최적화될 수 있고, 특히, 데이터 관독 동작들에서의 오류 정정이 개선될 수 있도록 멀티스트로브 관독 프로세스에서 하나 이상의 관독 파라미터를 변경하는 것의 효과를 결정하는 것을 가능하게 한다.

[0023] 도 3은 본 실시예들에 따라 관독될 수 있는 비휘발성 메모리의 메모리 속성들의 예를 나타낸다. 특히, 도 3은 메모리 어레이의 각각의 논리 상태 "1" 및 "0"과 연관된 2개의 상이한 분포를 나타낸다. 도시된 바와 같이, 제1 감지 파라미터 분포(302)는 논리 상태 "1"을 나타내고 제2 감지 파라미터 분포(304)는 논리 상태 "0"을 나타낸다. 용어 "감지 파라미터"는 메모리 셀의 논리 상태를 측정하기 위해 감지 필스가 적용되는 때의 감지 전압 또는 지속 시간과 같은 파라미터들을 나타낸다. 분명한 바와 같이, 최고점이 SP<sub>1</sub>에 있는 것으로 특징지어지는 감지 파라미터 분포(302)는 최고점이 SP<sub>0</sub>에 있는 것으로 특징지어지는 감지 파라미터 분포(304)와 겹친다. 감지 파라미터가 문턱 전압을 나타내는 경우에, 논리 상태들 "1"과 "0"의 특성을 사이의 중간에 있는, 즉, 점들 SP<sub>1</sub>과 SP<sub>0</sub> 사이의 중간에 있는 문턱 전압을 나타내는 기준 전압을 나타낼 수 있는 SP<sub>r</sub>에서 수행되는 것과 같은 감지 측정의 결과들에 대하여 불확실성을 야기하는 분포들에서의 충분한 겹침이 있다.

[0024] 도 3에서 제시된 상황을 해결하기 위하여, 약간 상이한 감지 조건들에서 다중 감지 동작들이 수행될 수 있고, 그 결과들이 처리를 위해 외부 장치(커스터머)에 전송될 수 있다. 그러한 다중 감지 동작들은 관독된 데이터를 필요에 따라 정정하기 위해 외부 장치에 의해 이용될 수 있는 상태 신뢰 정보의 형태로 정보를 제공할 수 있다. 예를 들어, 감지 파라미터가 관독될 메모리의 메모리 셀들의 문턱 전압인 도 3에 도시된 경우에, 관독될 메모리 요소들의 논리 상태에 관한 상태 신뢰 정보를 제공하기 위하여 SP<sub>r</sub>을 포함하는 분포에 걸쳐 있는 상이한 문턱 전압들에서 다중 감지 측정들이 수행될 수 있다. 문턱 전압들의 범위에 걸쳐 있음으로써, 다중 감지 측정들로부터의 출력은 더 신뢰할 수 있는 정보를 외부 장치에 제공할 수 있는데, 그 이유는 다중 감지 측정들은 메모리 셀을 온시키고, 그렇게 함으로써 하나의 논리 상태에서 또 하나의 논리 상태로의 전이를 야기하는 확률이 변화하는 전압 범위에 걸쳐 있을 수 있기 때문이다. 예를 들어, 점 SP<sub>2</sub>에 대응하는 문턱 전압에서 수행된 감지 동작의 결과들이 감지되는 메모리 셀(들)이 온 되는 것이라면, 감지된 메모리 셀의 실제 논리 상태는 "1"에 대응한다는 것이 높은 신뢰도로 결정될 수 있다. 이러한 결론이 나오는 이유는 감지 파라미터 분포(304)는 논리 상태 "0"으로 설정된 소수의(있더라도) 메모리 셀들이 SP<sub>2</sub>에 대응하는 것만큼 낮은 문턱 전압을 나타낸다는 것을 보여주기 때문이다. 그에 따라, 감지 동작이 SP<sub>2</sub>에 대응하는 전압을 적용할 때 상태를 변화시키는 임의의 메모리 셀은 실제로는 논리 상태 "1"로 기입되었어야 한다. 마찬가지로, 점 SP<sub>3</sub>에 대응하는 문턱 전압에서 수행된 감지 동작의 결과들이 메모리 셀이 온 되는 것을 야기하지 않는다면, 감지된 메모리 셀의 실제 논리 상태는 "

0"에 대응한다는 것이 높은 신뢰도로 결정될 수 있다. 이러한 결론이 나오는 이유는 감지 파라미터 분포(302)는 논리 상태 "1"로 설정된 소수의(있더라도) 메모리 셀들이  $SP_3$ 에 대응하는 것만큼 높은 문턱 전압을 나타낼 것임을 보여주기 때문이다. 그에 따라, 감지 동작이  $SP_3$ 에 대응하는 전압을 적용할 때 상태를 변화시키지 않는 임의의 메모리 셀은 실제로는 논리 상태 "0"으로 기입되었어야 한다. 한편,  $SP_r$ 에 대응하는 문턱 전압에서 수행된 감지 측정이 메모리 셀 트랜지스터가 온 되는 것을 야기한다면, 그 결과들은 분명히 해석될 수 있는데, 그 이유는, 이 영역에서 감지 파라미터 분포들(302 및 304)의 겹침이 보여주는 바와 같이, 논리 "1"로 설정된 어떤 메모리 셀들 및 논리 "0"으로 설정된 어떤 메모리 셀들은  $SP_r$ 에 대응하는 감지 전압을 받을 때 온 될 수 있기 때문이다. 따라서,  $SP_2$ 와  $SP_3$  사이의 범위에 걸쳐 수행된 일련의 감지 동작들의 결과들은 판독되고 있는 메모리 셀이 소정의 논리 상태에 있는 확률을 더 정확하게 반영하는 상태 신뢰 정보를 생성하는 데 이용될 수 있다.

[0025] 본 실시예들의 동작을 명확히 하기 위하여, 데이터의 멀티스트로브 판독을 수반하지 않는 절차들이 상태 신뢰 데이터를 생성할 가능성이 있다는 점에 유의해야 한다. 예를 들어, 그러한 상태 신뢰 데이터를 외부 장치에 제공하기 위하여, 원칙적으로, "순차적" 감지 프로세스에서는, 다중 감지 동작들의 각 감지 동작 후에 상태 신뢰 정보의 비트가 생성되고 외부 장치에 과성될 수 있다. 따라서, 예를 들어, 5개의 감지 동작들의 세트를 포함하는 데이터 판독 절차의 경우, 5개의 상이한 감지 사이클들에서 상태 신뢰 데이터의 별개의 비트가 생성되고 외부 장치에 과성될 수 있다. 그러한 판독 절차의 각 감지 사이클은 비트라인 및 워드라인을 충전하는 것, 감지 펄스를 인가하는 것, 문제의 메모리 셀들의 데이터를 감지하는 것, 상태 신뢰 정보의 비트를 생성하는 것, 그 비트를 로컬 캐시에 저장하는 것, 및 그 후 그 비트를 처리를 위해 외부 장치로 보내는 것과 같은 동작들을 포함할 수 있다. 각각의 후속 감지 동작을 위해, 비트라인 및 워드라인은 각각의 적절한 레벨들로 재충전될 수 있고, 다음 감지 펄스는 상이한 감지 전압으로 적용되어, 상태 신뢰 데이터의 추가 비트가 생성되고, 이는 그 후 외부 장치로 과성되고, 그렇게 계속된다.

[0026] 그러나, 상기 순차적 감지 절차는 감지 동작을 수행하는 각 사이클이 새로운 감지 동작으로부터의 비트들이 과성되기 전에 제1 감지 동작에서 판독된 메모리 셀들로부터의 모든 비트들이 수신될 것을 요구한다는 사실로 인해 성가심을 겪는다. 예를 들어, 간단히 NAND 어레이 페이지가 제1 감지 동작에서 판독되는 1000개의 비트를 포함하고 있다고 가정할 수 있다. 버스 폭은, 예를 들어, 8 비트이므로, 1000개 비트를 로컬 캐시로부터 외부 장치로 보내기 위해서는, 상당한 양의 시간이 소비될 수 있다. 더욱이, 각 감지 동작 사이에 워드라인 및/또는 비트라인을 충전하는 프로세스는 보통 상당한 양의 시간을 소비하여, 상태 신뢰 정보를 제공하기 위해 순차적 감지 절차가 이용된다면 판독 시간이 비교적 길어진다.

[0027] 본 실시예들에 따라, 이러한 단점들은 메모리 셀에 대해 다중 감지 동작들이 수행될 때 상태 신뢰 정보의 신규하고 효율적인 수집 및 과성을 제공하는 멀티스트로브 절차들 및 장치들에서 해결된다. 이제 도 4를 보면 다중 감지 절차들을 이용한 메모리 어레이의 판독에 기초하여 상태 신뢰 정보를 제공하는 멀티스트로브 배열이 도시되어 있다. 도 3의 예에 따라, 도 4의 배열은 상이한 논리 상태들의 분포가 문턱 전압 겹침을 나타낼 수 있는 메모리 어레이를 판독하기 위해 이용될 수 있다. 도 4의 배열의 동작의 일례에서, 멀티스트로브 판독 모듈(106)은, 도 3에 도시된 감지 파라미터 분포(302) 및 감지 파라미터 분포(304)로 특징지어질 수 있는, 비휘발성 메모리(108)로부터 감지된 데이터에 대한 판독 조건들을 관리할 수 있다. 도 4에 도시된 시나리오에서는, 데이터 판독 동작에서 판독되고 있는 메모리 주소들(메모리 셀들)에 관한 상태 신뢰 정보를 제공하기 위하여 비휘발성 메모리(108)에 5개의 상이한 감지 동작들(S1, S2, S3, S4, 및 S5)의 세트가 적용될 수 있다. 5개의 상이한 감지 동작들(S1, S2, S3, S4, 및 S5)의 각 감지 동작 후에, 해당 감지 동작의 결과가 상태 신뢰 인코딩 모듈(214)에 개별적으로 제공될 수 있다. 그러한 감지된 데이터의 합은 감지된 데이터(402)로서 도시되어 있다. 상태 신뢰 인코딩 모듈(214)은, 차례로, 인코딩된 상태 신뢰 정보(404)를 데이터 캐시(406)에 출력할 수 있다. 모든 감지 동작들(S1-S5)이 완료될 때, 멀티스트로브 판독 모듈(106)은 인코딩된 상태 신뢰 출력(408)을 외부 장치(410)에 과성되도록 스케줄링할 수 있다.

[0028] 도 4의 멀티스트로브 데이터 판독 배열의 이점은 상이한 감지 조건들에서 여려 차례 데이터가 감지되고 인코딩될 수 있는 반면 상이한 감지 조건들의 인코딩된 결과들은 단 하나의 경우에만 외부 장치에 과성된다는 것이다. 이것은 메모리의 각 페이지로부터의 모든 비트들 각각이 다중 감지 동작들 각각의 후에 캐시에 저장되고 외부 장치에 과성될 때 생길 수 있는 데이터 병목 현상의 문제들을 크게 방지한다.

[0029] 상기 이점들에 더하여, 그리고 다양한 실시예들에 따라, 멀티스트로브 판독 모듈(106)은 다중 감지 동작들을 포함하는 멀티스트로브 판독 동작 중에 데이터 판독 조건들을 관리할 수 있으며, 이에 따라 다중 감지 동작들이

보다 효율적인 방식으로 수행된다. 일부 실시예들에서, 그리고 후술하는 바와 같이, 데이터 판독 조건들의 관리는 다중 감지 동작들에 기초하여 더 정확하게 상태 신뢰 비트들을 생성하고 판독 시간을 감소시키는 방식으로 다중 감지 동작들이 수행되도록 상이한 감지 동작들 사이에 판독 조건들을 모니터링하고 조정하는 것을 포함할 수 있다.

[0030] 도 4의 예를 계속하여, 일 실시예에서, SC 인코딩 모듈(214)은 5개의 감지 동작들(S1-S5)을 수반하는 멀티스트로브 판독 동작의 결과들을 다중-비트 인코딩된 출력으로서 인코딩할 수 있다. 일례로, 다중-비트 인코딩된 출력은 각 감지 동작 후에 업데이트되고 최종 감지 동작 후에 최종 다중-비트 인코딩된 출력이 외부 장치에 파싱될 수 있다. 이런 식으로, 외부 장치에 파싱된 다중-비트 인코딩된 출력의 사이즈는 제1 감지 동작 후에 생성된 최초 인코딩된 출력의 사이즈와 동일할 수 있다.

[0031] 다양한 실시예들에 따라, 멀티스트로브 판독 모듈(106)은 둘 이상의 감지 동작이 수행되는 멀티스트로브 판독 동작 중에 하나 이상의 경우에 하나 이상의 판독 파라미터를 조정할 수 있다. 이것은 하나 이상의 판독 조건을 모니터링하고 연속되는 감지 동작들 사이에 적절하게 하나 이상의 판독 조건을 조정함으로써 달성될 수 있다. 용어 "판독 조건들"은 워드라인 전압, 비트라인 전압, 비트라인 방전 경로의 상태, 워드라인/비트라인의 충전 상태, 감지 전압 및 감지 펄스 기간, 및 기타 등의 파라미터를 나타낸다.

[0032] 일 실시예에서, 멀티스트로브 판독 모듈(106)은 비트라인 방전 경로가 연속되는 감지 동작들 사이에 인에이블된 상태로 있어야 하는지를 판정할 수 있다. 예를 들어, 약간 상이한 감지 조건 하에서 5개의 연속되는 감지 동작들을 각각 수행해야 하는 판독 동작에서, 비트라인 방전 경로 모듈(204)은 비트라인 방전 경로가 제1 감지 동작과 제2 감지 동작 사이의 시간 내내 인에이블되어야 한다고 판정할 수 있고, 그 후 비트라인 방전 경로가 제2 감지 동작과 제3 감지 동작 사이의 시간의 일부 동안 디스에이블되어야 한다고 판정할 수 있다. 비트라인 방전 경로를 선택적으로 인에이블/디스에이블시키는 이러한 능력은, 예를 들어, 연속되는 감지 동작들 사이의 시간이 증가할 때 감지 동작들의 정확도를 증가시키는 융통성을 제공한다. 상기 예에서, 제1 감지 동작과 제2 감지 동작 사이에, 판독 조건들은 제1 감지 동작과 제2 감지 동작을 수행하는 것 사이의 시간이 상대적으로 더 짧아야 하는 것일 수 있고, 따라서 멀티스트로브 판독 모듈은 비트라인 방전 경로가 인에이블되어야/인에이블된 상태로 있어야 한다고 판정한다. 대조적으로, 후속의 판독 조건들은 제2 감지 동작과 제3 감지 동작 사이의 시간이 상대적으로 더 길어야 하도록 전개될 수 있다. 예를 들어, 연속되는 제2 감지 동작과 제3 감지 동작 사이에 워드라인을 램프하기 위해 추가 시간이 요구될 수 있고, 따라서 비트라인 방전 경로 모듈(204)은 비트라인 방전 경로 특징이 제2 감지 동작이 수행된 후에 디스에이블되어야 하고 그 후 제3 감지 동작을 시작할 준비가 되어 있을 때 다시 인에이블되어야 한다고 결정한다.

[0033] 또 다른 실시예에서, 멀티스트로브 판독 모듈(106)은 워드라인 조정 모듈(210)을 이용하여 연속되는 감지 동작들 사이에 워드라인 전압이 조정되어야 하는지 판정하고 조정된다면 새로운 워드라인 전압의 값을 결정할 수 있다. 워드라인 전압을 선택적으로 조정하는 이러한 능력은, 판독 및 검증을 위한 워드라인 조건들 사이의 오프셋을 감소시킴으로써, 필요에 따라 감지 동작의 정확도를 증가시키는 융통성을 제공한다. 예를 들어, 5개의 감지 동작을 포함하는 판독 동작에서, 3개의 감지 동작이 수행된 후에, 워드라인의 상태는 메모리 셀의 배치를 검증할 때 존재한 워드라인의 상태 사이의 차이가 후속의 감지 동작에 대한 워드라인의 예상 상태로부터 허용 가능한 양을 넘어 벗어나는 정도까지 변할 수 있다. 그렇게 함으로써 워드라인 조정 모듈(210)은 워드라인 전압이 다음 감지 동작 전에 조정되어야 한다고 결정하고 그렇게 함으로써 이 특징을 인에이블시킬 수 있다. 그렇게 하면서, 워드라인 전압은 다음 감지 동작(들)을 위해 원하는 레벨로 재설정될 수 있다.

[0034] 추가의 실시예에서, 비트라인 프리차지 모듈(208)은 연속되는 감지 동작들 사이에 비트라인 프리차지를 선택적으로 인에이블시킬 뿐만 아니라, 조정된다면 새로운 비트라인 프리차지 전압의 값을 결정할 수 있다. 프리차지가 인에이블되는지를 선택적으로 설정하고 비트라인 프리차지 전압을 조정하는 능력은 조건들이 재충전을 정당화시키는 경우에만 비트라인을 재충전(프리차지)함으로써 다중의 연속되는 감지 동작들을 포함하는 멀티스트로브 시퀀스의 성능을 최적화시키는 융통성을 제공한다. 일례로, 멀티스트로브 판독 모듈(106)은 판독 조건들을 모니터링하고 2개의 연속되는 감지 동작들 사이에 워드라인 전압이 조정되어야 한다고 결정할 수 있다. 워드라인 전압을 이동시키기 위해 시간이 할당되어야 하므로, 비트라인 프리차지 모듈(208)은 프리차지 프로세스를 수행하기 위한 임의의 추가적인 시간 페널티를 초래하지 않고 워드라인 전압 조정 프로세스 중에 연속되는 감지 동작들 사이에 원하는 프리차지 레벨로 설정될 수 있다는 것을 확인할 수 있다. 그에 따라, 연속되는 감지 동작들의 하나 이상의 쌍 사이에 하나 이상의 경우에, 비트라인 프리차지 모듈(208)은 비트라인 프리차지를 인에이블시킬 수 있다. 비트라인 프리차지의 선택적 인에이블을 제공하는 것의 추가 이익은 "판독" 및 "검증"을 위한 비트라인 조건들 사이에 오프셋이 감소될 수 있고, 그렇게 함으로써 감지 동작의 정확도가 증가된다는 것이

다.

[0035] 또 다른 실시예에서, 감지 조건 조정 모듈(206)은 멀티스트로브 판독 동작에서 수행되는 하나 이상의 감지 동작에 대한 감지 조건들을 선택적으로 조정할 수 있다. 감지 전압 및 감지 펄스의 기간 등의 감지 파라미터들을 선택적으로 설정하는 이러한 능력은 비트라인 및/또는 워드라인 전압의 변동에 따라 수행될 임의의 소정의 감지 동작을 최적화시키는 융통성을 제공한다. 결과적으로, 다양한 실시예들에서, 플래시 NAND 장치 등의 소정의 유형의 비휘발성 메모리 장치를 판독하기 위해 적용될 감지 파라미터들을 조정하기 위하여 멀티스트로브 판독 프로세스에 의해 생성된 데이터의 정확도가 평가될 수 있다.

[0036] 이 특징을 설명하기 위하여, 도 5 및 도 6은 멀티스트로브 판독 동작의 감지 조건들이 조정되는 하나의 시나리오를 보여준다. 도 5는, 특히, 비휘발성 메모리(108)에 포함될 수 있는, 메모리 어레이의 각각의 논리 상태 "1" 및 "0"으로 설정된 메모리 셀들의 트랜지스터들과 연관된 2개의 상이한 문턱 전압 분포들을 나타낸다. 도시된 바와 같이, 제1 문턱 전압 분포(502)는 논리 상태 "1"을 나타내고 제2 문턱 전압 분포(504)는 논리 상태 "0"을 나타낸다. 분명한 바와 같이, 문턱 전압 분포(502)는 문턱 전압 분포(504)와 겹친다. 도 5에 도시된 시나리오에서는, 상태 신뢰 정보를 제공하기 위하여, 5개의 감지 동작들(S1, S2, S3, S4, 및 S5)의 세트(506)를 각각의 감지 전압들(V<sub>S1</sub>, V<sub>S2</sub>, V<sub>S3</sub>, V<sub>S4</sub>, 및 V<sub>S5</sub>)에서 수행하기 위해 멀티스트로브 데이터 판독 동작이 설정될 수 있다.

[0037] 이제 도 6을 보면, 비휘발성 메모리(108)에 대해 수행되는 멀티스트로브 데이터 판독에서 이용되는 감지 조건들을 선택적으로 변경하기 위해 이용될 수 있는, 감지 조건 조정 모듈(602)의 예시적인 블록도가 도시되어 있다. 감지 조건 조정 모듈은 데이터 판독 중에 비트라인/워드라인 조건들을 모니터링하고 모니터링된 조건들에 기초하여 적절한 감지 조건을 설정함으로써 하나 이상의 감지 동작에서 감지 조건들을 조정할 수 있다.

[0038] 감지 조건 조정 모듈(602)은 워드라인 모니터(604), 비트라인 모니터(606), 및 감지 펄스 제어 모듈(608)을 포함할 수 있다. 워드라인 모니터(604)는, 예를 들어, 데이터 판독 동작 중의 다양한 경우에, 비휘발성 메모리(108)의 선택 워드라인(들)에서 워드라인 조건들을 모니터링할 수 있다. 유사하게, 비트라인 모니터(606)는 데이터 판독 동작 중에 비휘발성 메모리(108)의 선택 비트라인들에서 비트라인 조건들을 모니터링할 수 있다. 워드라인 모니터(604) 및 비트라인 모니터(606)는 각각의 워드라인 및/또는 비트라인 전압을 나타내는 신호를 감지 펄스 제어 모듈(608)에 전송할 수 있고, 감지 펄스 제어 모듈(608)은 그 후 비휘발성 메모리(108)에서 수행될 하나 이상의 후속 감지 동작들에 대한 감지 조건들을 변경할 수 있다.

[0039] 도 5에 도시된 시나리오에서는, 하나 이상의 감지 동작(S1-S4)이 각각의 감지 전압들(V<sub>S1</sub>, V<sub>S2</sub>, V<sub>S3</sub>, V<sub>S4</sub>)에서 수행된 후에, 판독되고 있는 메모리 요소들의 워드라인 및/또는 비트라인 전압이 변화할 수 있고, 제2 감지 동작 또는 나중의 감지 동작 후의 감지 동작들의 누적된 잘못들로 인해 결과적으로 감지 전압이 미리 정해진 값에서 사실상 이동할 수 있다. 도시된 바와 같이, 도 5에서, 예를 들어, 감지 동작(S5)의 감지 전압은 워드라인 전압의 이동에 응하여 V<sub>S6</sub>에 대응하는 더 높은 레벨로 이동하여, 조정된 감지 동작들의 세트(508)를 야기할 수 있고, 이는 초기 감지 동작 후에 수행되는 하나 이상의 감지 동작 중에 수행되는 감지 동작들의 실제 조건들을 나타낼 수 있다. 결과적으로, 감지 펄스 제어 모듈(608)은 V<sub>S6</sub>로의 관찰된 이동을 보상하기 위해 워드라인 전압, 감지 펄스의 기간(감지 시간) 또는 또 다른 판독 파라미터를 조정하고 그렇게 함으로써 실제 감지 전압이 목표 전압, 즉 V<sub>S5</sub>와 일치하도록 후속의 감지 동작을 조정할 수 있다. 이 프로세스의 결과는 NAND 장치의 멀티스트로브 판독을 위한 판독 파라미터들의 세트의 적용을 위한 절차가 다중 감지 동작들 중에 적용되는 실제 감지 전압의 오차를 최소화시키도록 조정되는 것일 수 있다.

[0040] 다른 실시예들에서, 멀티스트로브 판독 동작에서 하나 이상의 감지 펄스의 기간이 워드라인 및/또는 비트라인 전압 조건들에 따라 조정될 수 있다. 도 5의 예에 따라, 워드라인 및/또는 비트라인 전압의 이동을 보상하기 위해 감지 동작(S5)에서 전압을 조정하는 대신에, 동작(S5)에 대한 감지 펄스의 기간은 최초의 워드라인/비트라인 전압 조건들 하에 최초 기간의 감지 펄스가 적용될 경우의 판독 조건들과 비슷할 것으로 예상되는 방식으로 최초 기간에서 조정된 기간으로 변경될 수 있다. 예를 들어, 전형적인 동작에서, 논리 "1"로 설정된 메모리 셀과 논리 "0"으로 설정된 메모리 셀에 의해 생성된 것 사이에 감지 증폭기에 의해 감지될 수 있는 비트라인 전압 레벨의 차이는 감지 시간에 따라 증가한다. 그에 따라, 감지 동작(S5)의 감지 펄스의 기간은 소정의 경우에 변경된 워드라인/비트라인 전압 조건들을 보상하기 위해 증가될 수 있다.

[0041] 또 다른 실시예들에서, 워드라인/비트라인(WL/BL) 충전 모듈(212)은 멀티스트로브 판독 동작 중에 워드라인 및/또는 비트라인 충전 상태를 모니터링하고, 그 모니터링의 결과에 기초하여 연속되는 감지 동작들 사이에 워드라

인 및/또는 비트라인을 충전할지를 판정할 수 있다. 예를 들어, WL/BL 충전 모듈(212)은 워드라인 전압 및/또는 비트라인 전압의 값이 미리 정해진 범위들 내에 있는 한 워드라인의 재충전 없이 다수의 감지 동작들 중 이전 감지 동작의 뒤를 잇도록 새로운 감지 동작을 스케줄링할 수 있다. 따라서, 5개-감지-동작 멀티스트로브 팬독 프로세스에서, 워드라인 및/또는 비트라인은 각각의 계속되는 감지 동작 후에 그들 각각의 상태에 따라 각각 겨우 1회밖에 충전되지 않을지도 모른다.

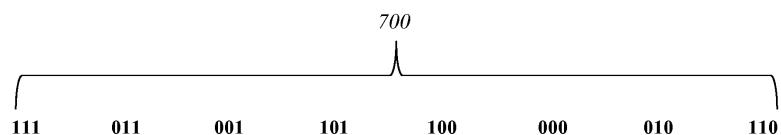

[0042] 다양한 추가 실시예들에서, 멀티스트로브 팬독 동작들은 각 셀에 다중 비트들이 저장되어 있는 다중 레벨 셀 (multiple level cell, MLC) 메모리 셀들을 포함하는 메모리들로부터 상태 신뢰 정보를 생성하기 위해 수행될 수 있다. 공지된 MLC 기술에서, 각각의 상이한 논리 상태에 대해 상이한 문턱 전압이 설정될 수 있다. 위에 논의한 바와 같이, 다수의 메모리 셀을 가진 메모리 어레이에서 소정의 논리 상태와 연관된 문턱 전압은 전압들의 분포로 특징지어질 수 있는데, 그 이유는 개개의 메모리 셀들의 문턱 전압은 공칭 문턱 전압에서 벗어날 수 있기 때문이다. 이는 MLC 기반 어레이들의 경우에도 마찬가지인데, 이 경우 소정의 논리 상태를 나타내는 문턱 전압이 전압의 분포로 특징지어진다. 도 7a는 8개의 3-비트 조합들의 하나의 가능한 배열의 세트(700)가 예시되어 있는 3-비트 MLC에의 데이터 저장의 일례를 도시하고 있다. 그러나, 다른 배열들도 가능하다. 특히, 최저 문턱 전압에서 최고 문턱 전압까지 순서대로, 상이한 시퀀스들은 (1,1,1); (0,1,1); (0,0,1); (1,0,1); (1,0,0); (0,0,0); (0,1,0); (1,1,0)이다.

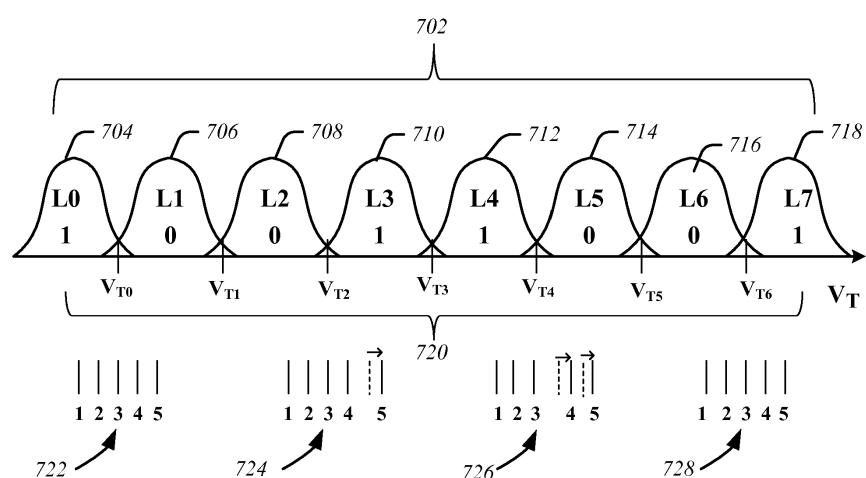

[0043] 이제 도 7b를 보면, 3-비트 MLC에 저장될 수 있는 8개의 상이한 3-비트 논리 상태 시퀀스들을 나타내기 위해 사용될 수 있는 문턱 전압 분포들의 세트(702)가 도시되어 있다. 특히, 시퀀스들 (1,1,1); (0,1,1); (0,0,1); (1,0,1); (1,0,0); (0,0,0); (0,1,0); (1,1,0)은, 도시된 바와 같이, 레벨들(L0, L1, L2, L3, L4, L5, L6, 및 L7)에 대응하는 각각의 문턱 전압 분포들(704, 706, 708, 710, 712, 714, 716, 718)로 저장될 수 있다. 일반적으로, 도 7b의 분포들(704-718)로 표현되는 메모리 셀 내의 데이터의 비트의 논리 상태를 결정하기 위하여, 도시된 바와 같이  $V_{T0}$  내지  $V_{T6}$ 로 표현되는 감지 전압에서 감지가 적용될 수 있다. 이 점을 설명하기 위하여, 도 7b의 각각의 문턱 전압 분포는 해당 전압 분포에 대응하는 3-비트 논리 상태 시퀀스의 제1 비트의 논리 상태도 도시한다. 증가하는 문턱 전압의 순서대로, 제1 비트들은 "1", "0", "0", "1", "1", "0", "0", "1"로 판독된다. 이 예시적인 시퀀스는 판독되고 있는 비트의 논리 상태를 결정하기 위해 필요한 데이터 감지 동작들의 양을 최소화시키는 데 유용하다. 예를 들어, 상태 신뢰 정보 없이 제1 비트의 논리 상태만을 판독하는 것이 요구된다면, 문턱 전압들  $V_{T0}$ ,  $V_{T2}$ ,  $V_{T4}$ , 및  $V_{T6}$ 에서 일련의 4개의 감지 동작이 적용될 수 있다. 이들 문턱 전압은, 도 7b에 도시된 바와 같이, 제1 비트에서 논리 "0"과 논리 "1" 또는 논리 "1"과 논리 "0" 사이의 전이를 표시한다. 그에 따라, 문턱 전압들  $V_{T0}$ ,  $V_{T2}$ ,  $V_{T4}$ , 및  $V_{T6}$  중 하나에 응하여 메모리 셀의 트랜지스터가 온 될 때 해당 셀의 비트 상태가 알려진다.

[0044] 유사한 방식으로, 제2 및 제3 비트의 비트 상태들이 조사(probe)될 수 있다. 예를 들어, 증가하는 문턱 전압의 순서대로, 제2 비트들은 "1", "1", "0", "0", "0", "0", "1", "1"로 판독된다. 이 경우 상태 신뢰 정보 없이 제2 비트의 논리 상태만을 판독하는 것이 또한 요구된다면, 문턱 전압들  $V_{T1}$  및  $V_{T5}$ 에서 일련의 2개의 감지 동작만이 적용될 필요가 있는데, 그 이유는 이를 문턱 전압이 제2 비트들의 시퀀스에 대하여 논리 "0"과 논리 "1" 또는 논리 "1"과 논리 "0" 사이의 유일한 전이를 표시하기 때문이다. 그 패턴이 "1", "1", "1", "1", "0", "0", "0", "0"으로 판독되는 제3 비트의 경우는, 문턱 전압  $V_{T3}$ 에서 하나의 감지 동작만이 적용될 필요가 있는데, 그 이유는 이 문턱 전압이 제3 비트 시퀀스에 대하여 논리 "0"과 논리 "1" 또는 논리 "1"과 논리 "0" 사이의 유일한 전이를 표시하기 때문이다.

[0045] 또한 도 8을 참조하면, 멀티스트로브 팬독 프로세스에서 다중 감지 동작들을 관리하는 것에 대한 일례가 도시되어 있다. 도시된 바와 같이 멀티스트로브 팬독 모듈(202)은 도 7b의 문턱 전압 분포들로 특징지어지는 3-비트 MLC로부터 상태 신뢰 정보를 판독하고, 인코딩하고, 저장하기 위해 이용된다. 특히, 멀티스트로브 팬독 모듈(202)은 판독될 3-비트 MLC 메모리의 적절한 비트를 감지하기 위해 선택되는 목표 문턱 전압들의 세트에 관하여 일련의 감지 동작들이 수행되도록 지시할 수 있다. 도 7b에 도시된 특정한 예에서, 제1 비트로부터의 상태 신뢰 정보는 문턱 전압들  $V_{T0}$ ,  $V_{T2}$ ,  $V_{T4}$ , 및  $V_{T6}$  각각에 관하여 5개 감지 동작들의 세트를 수행함으로써 조사된다. 이런 식으로, 4개의 감지 동작 세트(722, 724, 726, 및 728)를 수행함으로써, 3-비트 MLC의 제1 비트의 논리 상태는 상태 신뢰 데이터와 함께 결정될 수 있고 상태 신뢰 데이터는 해당 결정의 신뢰도를 나타낸다. 도 7b에 추가로 도시된 바와 같이, 예를 들어, 감지 동작(726-2)에 응하여 3-비트 메모리 셀의 트랜지스터가 온 된다면, 제1 비트의 논리 상태는 "1"이라고 결정될 수 있는데, 그 이유는 문턱 전압 분포(712)에 따르면, 감지 동작(726-2)에 대응하는 문턱 전압의 적용에 응하여 3-비트 논리 상태 "1,0,0"을 나타내는 메모리 셀의 대부분의 트

랜지스터들이 온 될 것이지만, 문턱 전압 분포(714)에 따르면, 감지 동작(726-2)에 대응하는 문턱 전압의 적용에 응하여 3-비트 논리 상태 "0,0,0"을 나타내는 메모리 셀의 대부분의 트랜지스터들이 온 되지 않을 것이 때문이다.

[0046] 다양한 실시예들에 따라, 멀티스트로브 판독 모듈(202)은, 도 7b가 시사하는 바와 같이, 다중 감지 동작들 중에 판독 조건들을 조정할 수 있다. 일례로, 감지 동작들의 세트는 722, 724, 726, 및 728의 순서대로 수행될 수 있다. 도 7b는 감지 조건 조정 모듈(206)이 멀티스트로브 판독 동작 중에 연속되는 감지 동작들 사이에 감지 조건들을 조정할 수 있는 예들을 나타낸다. 예를 들어, 다수의 감지 동작 세트(722-728)를 효율적으로 수행하기 위해, 멀티스트로브 판독 모듈(202)은 필요한 경우에만 워드라인 재충전을 할당할 수 있다. 일례로, 5개 감지 동작들의 세트(722)가 수행된 후에 제1 워드라인 재충전이 일어날 수 있다. 다음 감지 동작 세트 중에 감지 동작들(724)의 전압은, 일련의 감지 동작 후에, 감지 동작(724-5)에서, 워드라인 전압은, 도 7b에 도시된 바와 같이, 최초에 설정된 값(파선)에서 더 높은 전압(실선)으로 벗어나는 것으로 판찰될 수 있다. 그에 따라, 감지 전압은 전체적인 감지 조건들을 원하는 감지 조건들에 부합되게 가져오는 방식으로 후속 감지 동작들을 위해 감지 조건 조정 모듈(206)에 의해 조정될 수 있다. 워드라인은 그 후 재충전되고 새로운 감지 동작 세트(726)가 수행될 수 있다. 다시 말하지만, 감지 동작들(726)의 수행 중에, 워드라인 전압은 전체적인 감지 조건들을 원하는 감지 조건들에 부합되게 가져오는 방식으로 후속 감지 동작들을 위해 감지 조건 조정 모듈(206)에 의해 감지 전압이 다시 조정되는 정도까지 이동할 수 있다.

[0047] 도 8에 추가로 도시된 바와 같이, 감지된 데이터(802)는 상태 신뢰 인코딩 모듈(214)에 의해 인코딩되고, 데이터 캐시(806)에 인코딩된 상태 신뢰 정보(804)로서 제공될 수 있다. 일부 실시예들에서, 인코딩된 상태 신뢰 정보는 각각의 감지 동작 후에 업데이트될 수 있는 비트들의 세트를 포함할 수 있다. 업데이트된 비트들의 세트는 모든 감지 동작들(722-728)이 완료된 후에 멀티스트로브 판독 모듈이 외부 장치에 데이터의 파싱을 스케줄링할 때까지 데이터 캐시(734)에 유지될 수 있다. MLC 플래시 NAND 메모리에 적용되는 멀티스트로브 판독 프로세스에서, 도 7a-7c에 도시된 프로세스는 판독되고 있는 페이지의 각 비트에 대해 수행될 수 있는데, 이것은 일부 실시예들에서 수천 개의 비트까지 확장될 수 있다. 이런 식으로, MLC 메모리에 대한 상태 신뢰 정보는 메모리 어레이 내의 각 비트를 더 정확하게 감지하고, 감지된 데이터를 더 효율적으로 인코딩하고, 인코딩된 정보를 저장하고, 인코딩된 정보를 외부 장치로 더 효율적으로 전달하는 용통성 있는 방식으로 얻어질 수 있다.

[0048] 본 명세서에는 개시된 아키텍처의 신규한 양태들을 수행하기 위한 예시적인 방법들을 대표하는 순서도들의 세트가 포함되어 있다. 설명을 간소화하기 위하여, 본 명세서에, 예를 들어, 순서도 또는 흐름도의 형태로 도시된 하나 이상의 방법들은 일련의 단계들로서 도시되고 설명되어 있지만, 일부 단계들은, 그에 따라서, 본 명세서에 도시되고 설명된 것과는 다른 순서로 및/또는 다른 단계들과 동시에 발생할 수 있으므로, 이 방법들은 단계들의 순서에 의해 제한되지 않는다는 것을 이해하고 인정해야 한다. 예를 들어, 숙련된 당업자들은 방법이 대안으로 상태도에서와 같이 일련의 서로 관계있는 상태들 또는 이벤트들로서 표현될 수도 있다는 것을 이해하고 인정할 것이다. 더욱이, 신규한 구현을 위해 방법에 예시된 단계들 모두가 요구되지 않을 수도 있다.

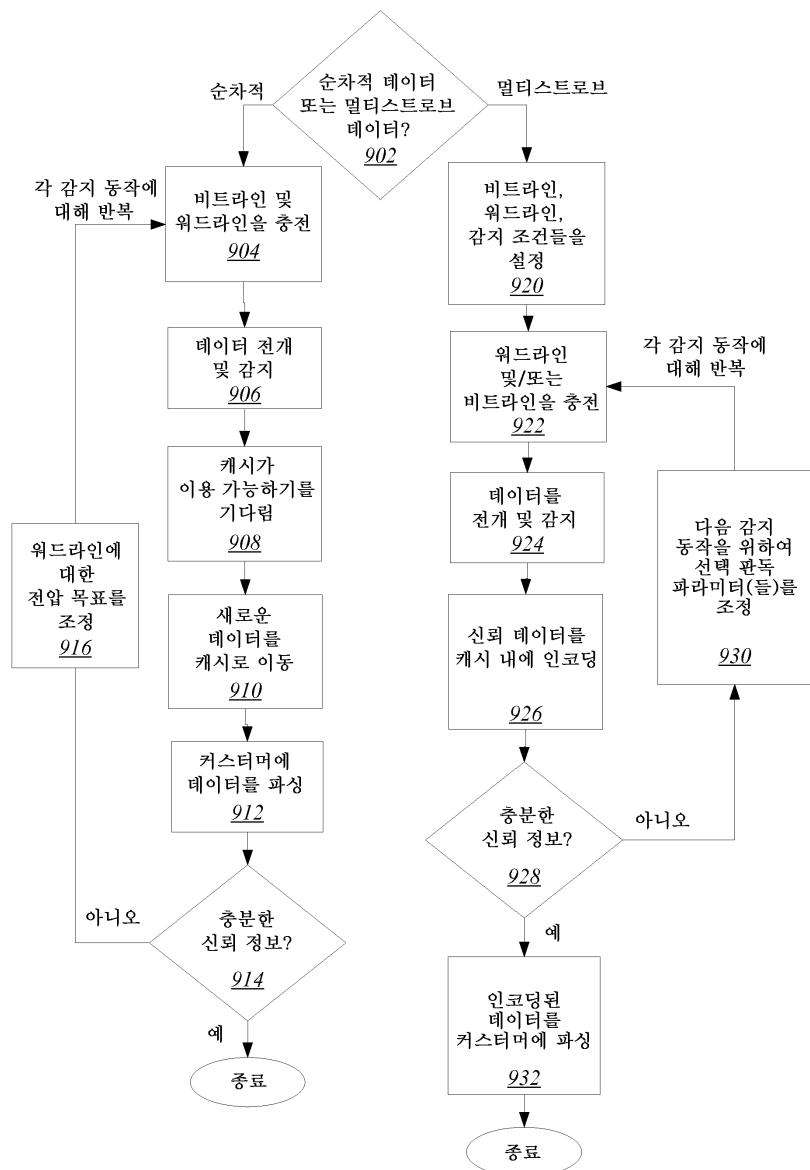

[0049] 도 9는 예시적인 제1 논리 흐름(900)을 도시한다. 블록 902에서는, 순차적 데이터 판독이 수행되어야 하는지 멀티스트로브 데이터 판독이 수행되어야 하는지에 대한 판정이 이루어진다. 예를 들어, 메모리의 상이한 부분들의 판독을 위해, 일부 데이터에 대해서는 LDPC 엔진에 의한 처리를 위해 데이터를 인코딩하는 것이 바람직할 수 있는 반면, 다른 데이터는 그러한 오류 정정을 필요로 하지 않을 수 있다. 상태 신뢰 데이터가 생성되어야 하고 순차적 판독 프로세스가 선택된다면, 흐름은 블록 904로 이동한다. 블록 906에서는 소정의 감지 동작을 위한 메모리 판독을 위한 데이터가 전개되고 감지된다. 블록 908에서는, 캐시가 이용 가능하게 되기를 기다리면서 데이터가 유지된다. 블록 910에서는, 새로운 데이터가 캐시로 이동되는 반면, 블록 912에서는 데이터가 외부 장치에 파싱된다.

[0050] 블록 914에서, 더 이상의 신뢰 정보가 요구되지 않는다면, 흐름이 종료한다. 그렇지 않다면, 흐름은 블록 916으로 이동하고, 여기서 워드라인에 대한 전압 목표가 조정된다. 그 후, 흐름은 블록 904로 되돌아가고 여기서 워드라인 및 비트라인이 충전된다. 블록 904와 블록 916 사이의 루프는 각 데이터 감지 동작에 대하여 반복될 수 있다.

[0051] 블록 902에서, 멀티스트로브 판독이 선택된다면, 흐름은 블록 920으로 이동하고, 여기서 초기 감지 조건들, 워드라인 및 비트라인 조건들이 설정될 수 있다. 그 후 흐름은 블록 922로 이동하고 여기서 워드라인 및 비트라인이 충전된다. 그 후 흐름은 블록 924로 이동하고, 여기서 데이터가 전개되고 감지된다. 블록 926에서는 감지된 데이터에 기초하여 신뢰 데이터가 캐시 내에 인코딩된다. 일부 실시예들에서, 이 인코딩된 신뢰 데이터는

다중 비트들의 형태를 가질 수 있다. 블록 928에서, 충분한 신뢰 정보가 얻어졌다면, 흐름은 블록 932로 이동하고 여기서 인코딩된 신뢰 데이터는 외부 장치(커스터머)에 파싱 출력된다.

[0052] 블록 928에서, 더 많은 신뢰 정보가 생성되어야 한다면, 흐름은 블록 930으로 이동하고, 여기서 다음 판독 동작을 위하여 선택 판독 파라미터들이 조정될 수 있다. 그 후 흐름은 블록 922로 되돌아가고, 여기서 필요할 경우 워드라인 및 비트라인이 충전된다. 이런 식으로, 블록 922-930의 시퀀스로 기술된 루프는 각 데이터 감지 동작에 대하여, 각 감지 동작 사이에 워드라인 또는 비트라인의 충전을 반드시 야기하는 일 없이, 그리고 수행될 모든 감지 동작들이 완료될 때까지 외부 장치에 데이터를 파싱하는 일 없이, 수행될 수 있다. 논리 흐름(900)에 따른 일례에서, 멀티스트로브 판독 프로세스는 겨우 하나의 워드라인 충전 동작이 수행되는 7개의 판독 동작들을 수반할 수 있다. 더욱이, 멀티스트로브 판독 프로세스는 각 감지 동작 후에 업데이트되는 간결한 인코딩된 출력을 생성할 수 있고, 그렇게 함으로써 순차적 감지 절차에서보다 상태 신뢰 정보를 캡처하는 더 효율적인 방식을 제공할 수 있다.

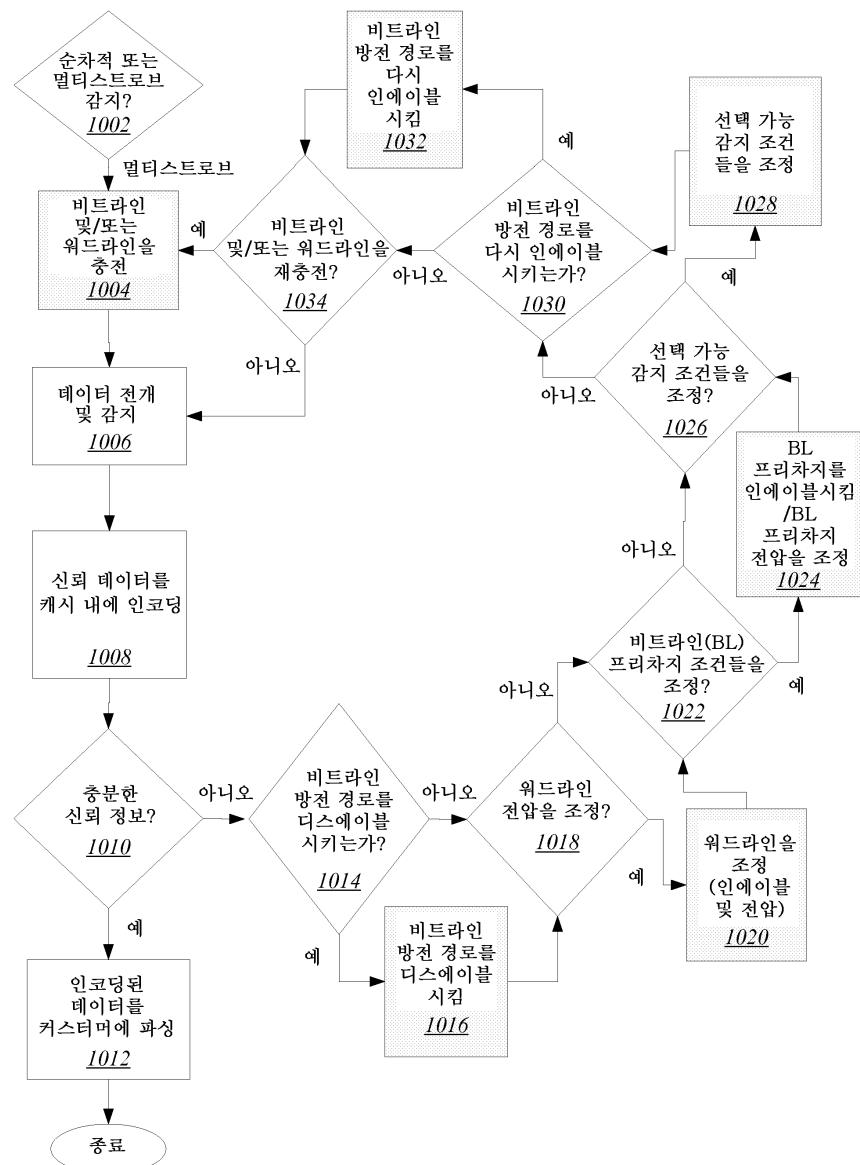

[0053] 도 10은 예시적인 제2 논리 흐름(1000)을 도시한다. 논리 흐름(1000)은 논리 흐름(900)의 일부분을 나타낼 수 있다. 블록 1002에서는, 비휘발성 메모리로부터 데이터를 판독하기 위해 멀티스트로브 판독 프로세스가 이용되어야 한다는 판정이 이루어진다. 블록 1004에서는, 비트라인 및 워드라인이 충전된다. 블록 1006에서는, 제1 감지 동작을 위하여 데이터가 전개되고 감지된다. 블록 1008에서는, 감지된 데이터에 기초하여 신뢰 데이터가 캐시 내에 인코딩된다. 블록 1010에서, 충분한 신뢰 정보가 얻어졌다면, 흐름은 블록 1012로 이동하고, 여기서 데이터가 외부 장치에 파싱된다.

[0054] 블록 1010에서, 더 많은 신뢰 정보가 제공되어야 한다고 판정된다면, 흐름은 블록 1014로 이동한다. 블록 1014, 및 계속되는 블록들에서는, 데이터 판독과 연관된 하나 이상의 파라미터가 조정되어야 하는지에 대한 일련의 결정들이 이루어진다. 전술한 바와 같이, 본 실시예들은 예시적인 것에 불과한 도 10에 도시된 특정 시퀀스로 제한되지 않는다. 블록 1014에서는, 비트라인 방전 경로가 디스에이블되어야 하는지에 대한 결정이 이루어진다. 만약 그렇다면, 흐름은 블록 1016으로 이동하고, 여기서 비트라인 방전 경로가 디스에이블되고, 이후 블록 1018로 이동한다. 방전 경로를 디스에이블시킬지에 대한 결정은, 워드라인 상의 전압이 다음 감지 동작 전에 램핑되어야 하는지 여부, 및 방전 경로의 현재 상태, 즉, 방전 경로가 현재 인에이블되어 있는지 여부와 같은, 하나 이상의 요인에 기초할 수 있다. 그렇지 않다면, 흐름은 바로 블록 1018로 이동한다.

[0055] 블록 1018에서는, 워드라인 전압이 조정되어야 하는지에 대한 결정이 이루어진다. 만약 그렇다면, 흐름은 블록 1020로 이동하고, 여기서 워드라인 상의 전압이 현재 레벨로부터 변경되고, 이후 블록 1022로 이동한다. 워드라인 전압을 조정하는 결정은 후속 감지 동작을 위한 예상 워드라인 전압과 셀의 배치를 검증할 때 존재하는 워드라인 전압 간의 차이가 문턱치를 초과하는지 여부에 기초할 수 있다. 워드라인 전압이 조정되지 않는다면, 흐름은 바로 블록 1022로 이동한다.

[0056] 블록 1022에서는, 비트라인 방전 조건들이 조정되어야 하는지에 대한 결정이 이루어진다. 만약 그렇다면, 흐름은 블록 1024로 이동하고, 여기서 비트라인 프리차지가 인에이블되고 비트라인 프리차지에 대한 적절한 조정이 수행되고, 이후 블록 1026으로 이동한다. 비트라인 프리차지를 수행하는 결정은 다음 감지 동작 전에 워드라인 전압이 조정되어야 하는지 여부를 포함하는 하나 이상의 요인에 기초할 수 있다. 비트라인 프리차지가 인에이블되지 않는다면, 흐름은 바로 블록 1026으로 이동한다.

[0057] 블록 1026에서는, 선택 가능 감지 조건들이 조정되어야 하는지에 대한 결정이 이루어진다. 선택 가능 감지 조건들은 다음 감지 동작에서 적용될 감지 전압 및 감지 펄스의 기간을 포함할 수 있다. 만약 그렇다면, 흐름은 블록 1028로 이동하고, 여기서 하나 이상의 감지 조건들이 그것들의 현재 상태로부터 조정되고, 이후 블록 1030으로 이동한다. 선택 가능 감지 조건들을 조정하는 결정은 현재 비트라인 전압, 현재 워드라인 전압, 및 기타 요인들을 포함하는 요인들에 기초할 수 있다. 예를 들어, 멀티스트로브 판독 동작 중에 비트라인 전압의 변화 또는 워드라인 전압의 변화에 대해 조정하기 위해 다음 감지 동작을 위한 감지 전압 및/또는 감지 펄스 기간은 이전 감지 동작에서 적용된 이전 값으로부터 증가될 수 있다. 선택 감지 조건들이 변경되지 않는다면, 흐름은 바로 블록 1030으로 이동한다.

[0058] 블록 1030에서는, 비트라인 방전 경로가 다시 인에이블되어야 하는지에 대한 결정이 이루어진다. 예를 들어, 이전 감지 동작 후에 비트라인 방전 경로가 일시적으로 디스에이블되었다면, 비트라인 방전 경로는 블록 1032에서 다시 인에이블되고, 흐름은 그 후 블록 1034로 이동한다. 비트라인 방전 경로가 디스에이블되지 않았다면, 후속 감지 동작을 위해 다시 인에이블시키는 것이 필요하지 않고, 흐름은 바로 블록 1034로 이동한다.

- [0059] 블록 1034에서는, 비트라인 및/또는 워드라인이 재충전되어야 하는지에 대한 결정이 이루어진다. 만약 그렇다면, 흐름은 블록 1004로 되돌아가고, 여기서 비트라인 및/또는 워드라인이 (재)충전된다. 비트라인/워드라인을 재충전하는 결정은 비트라인 전압 및 워드라인 전압의 현재 상태와 같은 하나 이상의 판독 조건의 상태에 기초할 수 있다. 이들 판독 조건들은, 차례로, 논리 흐름(1000)에서 이전 흐름 시퀀스에 좌우될 수 있다. 예를 들어, 블록 1020에서와 같이, 워드라인 전압이 이전에 조정된다면, 그것은 블록 1004에서 재충전될 필요가 있을 것이다. 유사하게, 블록 1024에서와 같이, 비트라인이 프리차지되고 및/또는 비트라인 프리차지 전압이 조정된다면, 블록 1034에서의 비트라인 재충전 동작이 스케줄링되어야 한다.

- [0060] 그러나, 워드라인을 재충전하는 것이 필요하지 않은 경우, 멀티스트로브 판독 동작의 처음에 설정된 최초 값으로부터 현재 워드 라인 전압의 편차가 문턱치를 초과할 때까지는 워드라인을 재충전하지 않는 것이 바람직할 수 있다. 문턱치는 감지 전압 및 감지 폴스 기간을 포함하여, 다른 파라미터들에 대한 이용 가능한 조정들을 고려하더라도 다음 감지 동작의 정확도를 손상시킬 것으로 예상되는 워드라인 전압을 나타낸다. 따라서, 워드라인 전압이 해당 문턱치를 초과하지 않는 미리 정해진 범위 내에 있는 동안은, 워드라인의 충전으로 초래되는 시간 폐널티를 피하기 위하여 워드라인 전압을 조정하는 일 없이 다른 판독 파라미터들을 조정하는 것이 더 나을 수 있다.

- [0061] 블록 1034에서 결정이 워드라인/비트라인을 변경하지 않는 것이라면, 흐름은 블록 1006으로 되돌아가고, 여기서 다음 감지 동작이 수행되는데, 즉, WL 또는 BL 전압의 조정 없이, 판독되고 있는 메모리 셀에 대하여 데이터가 전개되고 감지된다.

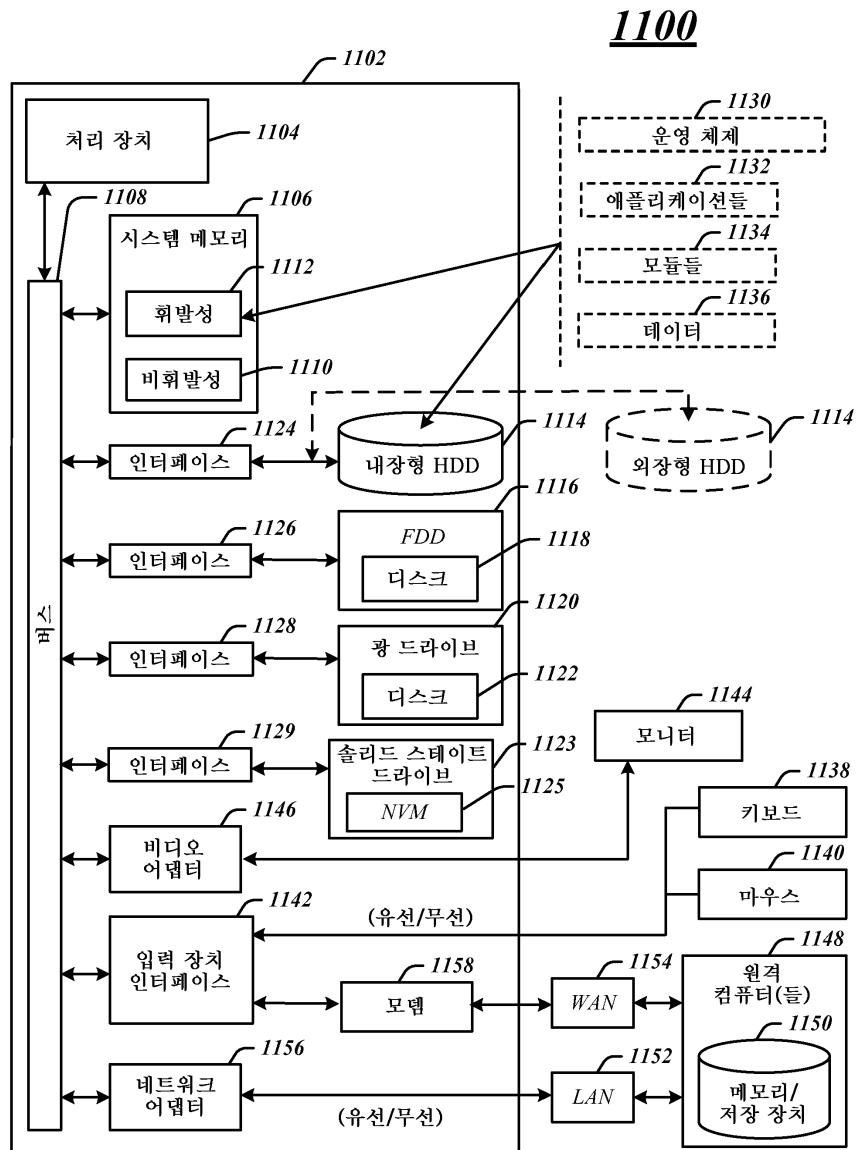

- [0062] 도 11은 전술한 바와 같은 다양한 실시예들을 구현하기에 적합한 예시적인 컴퓨팅 아키텍처(1100)의 일 실시예를 나타낸다. 본원에서 사용될 때, 용어 "시스템" 및 "컴포넌트"는, 하드웨어이든, 하드웨어와 소프트웨어의 조합이든, 소프트웨어이든, 또는 실행 중인 소프트웨어이든 간에, 컴퓨터 관련 엔티티를 지칭하기 위한 것이고, 그 예들이 예시적인 컴퓨팅 아키텍처(1100)에 의해 제공된다. 예를 들어, 컴포넌트는 프로세서에서 실행되는 프로세스, 프로세서, 하드 디스크 드라이브, (광학 및/또는 자기 저장 매체의) 다중 저장 드라이브들, 객체, 실행 파일, 실행 스크립트, 프로그램, 및/또는 컴퓨터일 수 있지만, 이에 제한되지는 않는다. 예시로서, 서버에서 실행되는 애플리케이션과 서버는 둘 다 컴포넌트일 수 있다. 하나 이상의 컴포넌트가 프로세스 및/또는 실행 스크립트 내에 상주할 수 있고, 컴포넌트가 하나의 컴퓨터에 국한되고/되거나 둘 이상의 컴퓨터 사이에 분산될 수 있다. 또한, 컴포넌트들이 동작들을 조정(coordinate)하기 위해 다양한 유형의 통신 매체들에 의해 서로 통신 결합되어 있을 수 있다. 조정은 단방향 또는 양방향 정보 교환을 수반할 수 있다. 예를 들어, 컴포넌트들은 통신 매체들을 통하여 전달되는 신호들의 형태로 정보를 전달할 수 있다. 정보는 다양한 신호 라인들에 할당된 신호들로서 구현될 수 있다. 그러한 할당들에서, 각 메시지는 신호이다. 그러나, 추가의 실시예들은 대안으로 데이터 메시지들을 이용할 수 있다. 그러한 데이터 메시지들은 다양한 연결들을 가로질러 전송될 수 있다. 예시적인 연결들은 병렬 인터페이스, 직렬 인터페이스, 및 버스 인터페이스를 포함한다.

- [0063] 일 실시예에서, 컴퓨팅 아키텍처(1100)는 전자 장치를 포함하거나 전자 장치의 일부로서 구현될 수 있다. 전자 장치의 예들은 제한 없이 모바일 장치, PDA(personal digital assistant), 모바일 컴퓨팅 장치, 스마트폰, 휴대 전화, 핸드셋, 일방 호출기, 양방 호출기, 메시징 장치, 컴퓨터, 퍼스널 컴퓨터(PC), 데스크톱 컴퓨터, 랩톱 컴퓨터, 노트북 컴퓨터, 핸드헬드 컴퓨터, 태블릿 컴퓨터, 서버, 서버 어레이 또는 서버 패, 웹 서버, 네트워크 서버, 인터넷 서버, 워크스테이션, 미니-컴퓨터, 메인 프레임 컴퓨터, 슈퍼컴퓨터, 네트워크 가전 기기, 웹 가전 기기, 분산형 컴퓨팅 시스템, 멀티프로세서 시스템, 프로세서 기반 시스템, 소비자 전자 기기, 프로그래머블 소비자 전자 기기, 텔레비전, 디지털 텔레비전, 셋톱 박스, 무선 액세스 포인트, 기지국, 가입자국, 모바일 가입자 센터, 무선 네트워크 컨트롤러, 라우터, 허브, 게이트웨이, 브리지, 스위치, 머신, 또는 이들의 조합을 포함할 수 있다. 실시예들은 이에 관련하여 제한되지 않는다.

- [0064] 컴퓨팅 아키텍처(1100)는 다양한 공통 컴퓨팅 요소들, 예를 들어, 하나 이상의 프로세서, 코-프로세서, 메모리 유닛, 칩셋, 컨트롤러, 주변 장치, 인터페이스, 발진기, 타이밍 장치, 비디오 카드, 오디오 카드, 멀티미디어 입력/출력(I/O) 컴포넌트, 및 기타 등등을 포함한다. 그러나, 실시예들은 컴퓨팅 아키텍처(1100)에 의한 구현으로 제한되지 않는다.

- [0065] 도 11에 도시된 바와 같이, 컴퓨팅 아키텍처(1100)는 처리 장치(1104), 시스템 메모리(1106) 및 시스템 버스(1108)를 포함한다. 처리 장치(1104)는 다양한 상업적으로 입수할 수 있는 프로세서들 중 임의의 것일 수 있다. 듀얼 멀티프로세서 및 기타 멀티-프로세서 아키텍처들도 처리 장치(1104)로서 이용될 수 있다. 시스템 버스(1108)는 처리 장치(1104)와의 시스템 메모리(1106)(이에 제한되지 않음)를 포함하는 시스템 컴포넌트들에

대한 인터페이스를 제공한다. 시스템 버스(1108)는 상업적으로 입수할 수 있는 각종 버스 아키텍처들 중 임의의 것을 이용한 메모리 버스(메모리 컨트롤러가 있는 또는 없는), 주변 버스, 및 로컬 버스에 추가로 상호 연결될 수 있는 여러 버스 구조 유형들 중 임의의 것일 수 있다.

[0066] 컴퓨팅 아키텍처(1100)는 다양한 제조물을 포함하거나 구현할 수 있다. 제조물은 로직을 저장하는 컴퓨터 판독 가능 저장 매체를 포함할 수 있다. 실시예들은 적어도 부분적으로 비일시적 컴퓨터 판독 가능 매체에 포함된 명령어들로서 구현될 수도 있고, 이 명령어들은 본 명세서에 기술된 동작들의 수행을 가능하게 하기 위해 하나 이상의 프로세서에 의해 판독되어 실행될 수 있다. 컴퓨터 판독 가능 매체의 예들은 휘발성 메모리 또는 비휘발성 메모리, 이동식 또는 비이동식 메모리, 소거 가능 또는 소거 불가 메모리, 기입 가능 또는 재기입 가능 메모리 등을 포함하여, 전자 데이터를 저장할 수 있는 임의의 유형(有形)의 메모리를 포함할 수 있다. 로직의 예들은 소스 코드, 컴파일러형 코드, 해석형 코드, 실행 가능 코드, 정적 코드, 동적 코드, 객체 지향 코드, 비주얼 코드 등과 같은 임의의 적합한 유형의 코드를 이용하여 구현된 실행 가능 컴퓨터 프로그램 명령어들을 포함할 수 있다.

[0067] 시스템 메모리(1106)는 판독 전용 메모리(ROM), 랜덤-액세스 메모리(RAM), 다이내믹 RAM(DRAM), 더블-데이터-레이트 DRAM(DDRDRAM), 동기식 DRAM(SDRAM), 스테틱 RAM(SRAM), 프로그램 가능 ROM(PROM), 소거 가능 프로그램 가능 ROM(EPROM), 전기적으로 소거 가능 프로그램 가능 ROM(EEPROM), 플래시 메모리, 강유전성 폴리머 메모리, 오보닉 메모리, 상변화 또는 강유전성 메모리, 실리콘-산화물-질화물-산화물-실리콘(SONOS) 메모리, 자기 또는 광학 카드, 또는 정보를 저장하기에 적합한 임의의 다른 유형의 매체 등의 하나 이상의 고속 메모리 유닛의 형태로 다양한 유형의 컴퓨터 판독 가능 저장 매체를 포함할 수 있다. 도 11에 도시된 예시된 실시예에서, 시스템 메모리(1106)는 비휘발성 메모리(1110) 및/또는 휘발성 메모리(1112)를 포함할 수 있다. 기본 입력/출력 시스템(BIOS)이 비휘발성 메모리(1110)에 저장될 수 있다.

[0068] 컴퓨터(1102)는 내장형 하드 디스크 드라이브(HDD)(1114), 이동식 자기 디스크(1118)에 기입하거나 그로부터 판독하는 자기 플로피 디스크 드라이브(FDD)(1116), 이동식 광 디스크(1122)(예컨대, CD-ROM 또는 DVD)에 기입하거나 그로부터 판독하는 광 디스크 드라이브(1120), 및 본 명세서에 기술된 바와 같은 NAND 플래시 메모리 및 NAND 컨트롤러를 포함할 수 있는, 비휘발성 메모리(NVM)(1125)에 데이터를 기입하거나 그로부터 데이터를 판독하는 솔리드 스테이트 드라이브(SSD)(1123)를 포함하여, 하나 이상의 저속 메모리 유닛의 형태로 다양한 유형의 컴퓨터 판독 가능 저장 매체를 포함할 수 있다. NVM(1125)은 상변화 메모리(PCM), 스핀 메모리, 스위치를 갖춘 상변화 메모리(phase change memory with switch, PCMS), 자기저항 랜덤 액세스 메모리(MRAM), 스핀 메모리, 나노와이어 메모리, 강유전성 트랜지스터 랜덤 액세스 메모리(FeTRAM)를 포함할 수 있다. HDD(1114), FDD(1116), 광 디스크 드라이브(1120), 및 솔리드 스테이트 드라이브(1123)는 각각 HDD 인터페이스(1124), FDD 인터페이스(1126), 광 드라이브 인터페이스(1128), 및 솔리드 스테이트 드라이브 인터페이스(1129)에 의해 시스템 버스(1108)에 연결될 수 있다. 외장형 드라이브 구현을 위한 HDD 인터페이스(1124)는 범용 직렬 버스(USB) 및 IEEE 1394 인터페이스 기술들 중 적어도 하나 또는 둘 다를 포함할 수 있다. 솔리드 스테이트 드라이브 인터페이스(1129)는 호스트 장치에 결합하기 위한 임의의 적합한 인터페이스를 포함할 수 있는데, 예를 들어, SATA(serial advanced technology attachment) 인터페이스, SAS(serial attached SCSI) 인터페이스, 범용 직렬 버스(USB) 인터페이스, PCI(peripheral control interface), 또는 다른 적합한 장치 인터페이스가 있지만, 이들에 제한되지는 않는다.

[0069] 드라이브들 및 연관된 컴퓨터 판독 가능 매체들은 데이터, 데이터 구조, 컴퓨터 판독 가능 명령어 등의 휘발성 및/또는 비휘발성 저장을 제공한다. 예를 들어, 운영 체제(1130), 하나 이상의 애플리케이션 프로그램(1132), 기타 프로그램 모듈(1134), 및 프로그램 데이터(1136)를 포함하는, 다수의 프로그램 모듈들이 드라이브들 및 메모리 유닛들(1110, 1112)에 저장될 수 있다.

[0070] 사용자는 하나 이상의 유선/무선 입력 장치, 예를 들어, 키보드(1138) 및 마우스(1140) 등의 포인팅 장치를 통하여 명령들 및 정보를 컴퓨터(1102)에 입력할 수 있다. 다른 입력 장치들로는 마이크, 적외선(IR) 리모컨, 조이스틱, 게임 패드, 스타일러스 펜, 터치 스크린, 또는 기타 등등이 있을 수 있다. 이를 및 다른 입력 장치들은 흔히 시스템 버스(1108)에 결합되어 있는 입력 장치 인터페이스(1142)를 통하여 처리 장치(1104)에 연결되지만, 병렬 포트, IEEE 1394 직렬 포트, 게임 포트, USB 포트, IR 인터페이스 등과 같은 다른 인터페이스들에 의해 연결될 수 있다.

[0071] 모니터(1144) 또는 다른 유형의 디스플레이 장치가 또한 비디오 어댑터(1146) 등의 인터페이스를 통해 시스템 버스(1108)에 연결된다. 모니터(1144) 외에도, 컴퓨터는 보통 스피커, 프린터 등과 같은 다른 주변 출력 장치

들을 포함한다.

[0072] 컴퓨터(1102)는 원격 컴퓨터(1148)와 같은 하나 이상의 원격 컴퓨터와의 유선 및/또는 무선 통신을 통한 논리적 연결을 이용하여 네트워킹 환경에서 동작할 수 있다. 원격 컴퓨터(1148)는 워크스테이션, 서버 컴퓨터, 라우터, 퍼스널 컴퓨터, 휴대용 컴퓨터, 마이크로프로세서 기반 오락 기기, 피어 장치 또는 다른 일반적인 네트워크 노드일 수 있고, 보통 컴퓨터(1102)에 관하여 기술된 요소들 중 다수 또는 전부를 포함하지만, 간결성을 위해, 메모리/저장 장치(1150)만이 도시되어 있다. 도시된 논리적 연결들은 근거리 통신망(LAN)(1152) 및/또는 더 대규모의 네트워크, 예를 들어, 광역 통신망(WAN)(1154)과의 유선/무선 연결을 포함한다. 그러한 LAN 및 WAN 네트워킹 환경들은 사무실과 회사에서 아주 흔하고, 인트라넷 등의 전사적 컴퓨터 네트워크들을 가능하게 하고, 이들 모두는 글로벌 통신 네트워크, 예를 들어, 인터넷에 연결될 수 있다.

[0073] LAN 네트워킹 환경에서 이용될 때, 컴퓨터(1102)는 유선 및/또는 무선 통신 네트워크 인터페이스 또는 어댑터(1156)를 통하여 LAN(1152)에 연결된다. 어댑터(1156)는 LAN(1152)과의 유선 및/또는 무선 통신을 가능하게 할 수 있고, LAN(1152)은 어댑터(1156)의 무선 기능과 통신하기 위해 배치된 무선 액세스 포인트를 또한 포함할 수 있다.

[0074] WAN 네트워킹 환경에서 이용될 때, 컴퓨터(1102)는 모뎀(1158)을 포함할 수 있거나, WAN(1154) 상의 통신 서버에 연결되거나, WAN(1154)을 통하여, 예를 들어 인터넷을 경유하여 통신을 설정하기 위한 다른 수단을 가지고 있다. 내장형 또는 외장형이고 유선 및/또는 무선 장치일 수 있는 모뎀(1158)은 입력 장치 인터페이스(1142)를 통해 시스템 버스(1108)에 연결된다. 네트워킹 환경에서, 컴퓨터(1102), 또는 그의 부분들에 관하여 묘사된 프로그램 모듈들이 원격 메모리/저장 장치(1150)에 저장될 수 있다. 도시된 네트워크 연결들은 예시적인 것이고 컴퓨터들 간에 통신 연결을 설정하는 다른 수단이 이용될 수 있다는 것을 알 것이다.

[0075] 컴퓨터(1102)는, 예를 들어, 프린터, 스캐너, 데스크톱 및/또는 휴대용 컴퓨터, PDA(personal digital assistant), 통신 위성, 무선으로 탐지 가능한 태그와 연관된 임의의 장비 또는 장소(예컨대, 키오스크, 신문판매대, 화장실), 및 전화와 무선 통신(예컨대, IEEE 802.11 OTA(over-the-air) 변조 기법)으로 동작적으로 배치된 무선 장치들과 같이, IEEE 802 계열의 표준들을 이용하여 유선 및 무선 장치들 또는 엔티티들과 통신하도록 작동된다. 이것은 적어도 Wi-Fi(또는 Wireless Fidelity), WiMax, 및 Bluetooth™ 무선 기술들을 포함한다. 따라서, 통신은 종래의 네트워크와 같이 미리 정의된 구조일 수 있거나 단순히 적어도 2개의 장치 간의 애드혹 통신일 수 있다. Wi-Fi 네트워크들은 안전하고, 신뢰할 수 있는, 고속 무선 연결을 제공하기 위해 IEEE 802.11x(a, b, g, n 등)라 불리는 무선 기술들을 이용한다. Wi-Fi 네트워크는 컴퓨터들을 서로, 인터넷에, 그리고 (IEEE 802.3 관련 미디어 또는 기능들을 이용하는) 무선 네트워크들에 연결시키기 위해 이용될 수 있다.

[0076] 일부 실시예들은 "일 실시예" 또는 "실시예"라는 표현과 함께 이들의 과생어들을 이용하여 기술될 수 있다. 이 용어들은 실시예와 관련하여 기술된 특정한 특징, 구조, 또는 특성이 적어도 하나의 실시예에 포함된다는 것을 의미한다. 명세서의 여러 곳에서 "일 실시예에서"라는 구절의 출현들은 반드시 모두가 동일한 실시예를 나타내는 것은 아니다. 또한, 일부 실시예들은 "결합된" 및 "연결된"이라는 표현과 함께 이들의 과생어들을 이용하여 기술될 수 있다. 이 용어들은 반드시 서로 동의어로 의도된 것은 아니다. 예를 들어, 일부 실시예들은 둘 이상의 요소가 서로 직접 물리적으로 또는 전기적으로 접촉하고 있는 것을 나타내기 위해 "연결된" 및/또는 "결합된"이라는 용어들을 이용하여 기술될 수 있다. 그러나, "결합된"이라는 용어는 둘 이상의 요소가 서로 직접 접촉하고 있지 않으면서도, 서로 협력하거나 상호 작용함을 의미할 수도 있다.

[0077] 일 실시예에서, 장치는 비휘발성 메모리로부터 데이터를 검색하는 프로세서 회로 및 다수의 감지 동작들 - 각 감지 동작은 상이한 감지 조건 하에 수행됨 - 에 걸쳐 메모리 셀을 판독하는 판독 동작을 설정하도록 프로세서 회로에서 작동되는 멀티스트로브 판독 모듈을 포함할 수 있다. 멀티스트로브 판독 모듈은 추가로 하나 이상의 판독 조건의 값이 미리 정해진 범위 내에 있을 때 워드라인의 재충전 없이 다수의 감지 동작들 중 이전 감지 동작의 뒤를 잇도록 새로운 감지 동작을 스케줄링하도록 작동될 수 있다.

[0078] 또 다른 실시예에서, 멀티스트로브 판독 모듈은 다수의 판독 동작들을 수행함으로써 판독된 데이터의 오류율에 기초하여 비휘발성 메모리로부터 데이터를 판독하기 위해 적용될 하나 이상의 판독 파라미터를 선택적으로 조정하도록 작동될 수 있고, 하나 이상의 판독 파라미터는 비휘발성 메모리의 비트라인 방전 경로의 상태, 비휘발성 메모리의 메모리 셀을 판독하기 위한 워드라인의 워드라인 전압 레벨, 및 비트라인의 프리차지 레벨을 포함한다.

- [0079] 대안으로, 또는 추가로, 또 다른 실시예에서, 멀티스트로브 판독 모듈은 다수의 감지 동작들의 결과들을 인코딩된 상태 신뢰 데이터로서 저장하기 위해 전송하고; 다수의 감지 동작들의 완료 후에만 저장된 인코딩된 상태 신뢰 데이터를 외부 장치로 전송되도록 스케줄링하도록 프로세서 회로에서 작동될 수 있다.

- [0080] 대안으로, 또는 추가로, 또 다른 실시예에서, 멀티스트로브 판독 모듈은 연속되는 감지 동작들 사이의 워드라인의 램프의 기간이 제1 문턱치를 초과하는 경우에 비트라인 방전 경로를 디스에이블시키도록 프로세서 회로에서 작동될 수 있다.

- [0081] 대안으로, 또는 추가로, 또 다른 실시예에서, 멀티스트로브 판독 모듈은 메모리 셀의 배치를 검증할 때 존재한 워드 라인의 상태와 후속 판독 동작을 위한 워드 라인의 예상 상태 간의 차이가 제2 문턱치를 초과하는 경우에 워드라인 전압을 조정하도록 프로세서 회로에서 작동될 수 있다.

- [0082] 대안으로, 또는 추가로, 또 다른 실시예에서, 멀티스트로브 판독 모듈은 제1 감지 동작과 다음 감지 동작 사이에 워드라인 전압을 조정하기 위해 할당된 시간이 제3 문턱치를 초과하는 경우에 비트라인의 프리차지 레벨이 조정되고 비트라인이 재충전되도록 지시하도록 프로세서 회로에서 작동될 수 있다.

- [0083] 대안으로, 또는 추가로, 또 다른 실시예에서, 멀티스트로브 판독 모듈은 비트라인 판독과 비트라인 검증 조건들 간의 오프셋이 제4 문턱치를 초과하는 경우에 제1 감지 동작과 다음 감지 동작 사이에 비트라인의 프리차지 레벨이 조정되고 비트라인이 재충전되도록 지시하도록 컨트롤러에서 작동될 수 있다.

- [0084] 대안으로, 또는 추가로, 또 다른 실시예에서, 멀티스트로브 판독 모듈은 판독 동작 중의 비트라인 전압의 변화가 제5 문턱치를 초과하는 경우에 감지 동작의 감지 펄스 중에 이용될 기준 전압의 값과, 감지 펄스의 기간 중 하나 이상을 조정하도록 프로세서 회로에서 작동될 수 있다.

- [0085] 대안으로, 또는 추가로, 또 다른 실시예에서, 멀티스트로브 판독 모듈은 판독 동작 중의 워드라인 전압의 변화가 제6 문턱치를 초과하는 경우에 감지 동작의 감지 펄스 중에 이용될 기준 전압의 값과, 감지 펄스의 기간 중 하나 이상을 조정하도록 프로세서 회로에서 작동될 수 있다.

- [0086] 대안으로, 또는 추가로, 또 다른 실시예에서, 이 장치는 비휘발성 메모리로부터 판독된 데이터의 결과들을 표시하기 위한 디지털 디스플레이를 포함할 수 있다.

- [0087] 또 다른 실시예에서, 컴퓨터 구현 방법은 다수의 감지 동작들 - 각 감지 동작은 상이한 감지 조건 하에 수행됨 -에 걸쳐 메모리 셀을 판독하는 판독 동작을 설정하는 것을 포함하고, 하나 이상의 판독 조건의 값이 미리 정해진 범위 내에 있을 때 워드라인의 재충전 없이 다수의 감지 동작들 중 이전 감지 동작의 뒤를 있도록 새로운 감지 동작을 스케줄링하는 것을 포함하는 멀티스트로브 판독 동작을 수행하는 단계를 포함할 수 있다.

- [0088] 또 다른 실시예에서, 컴퓨터 구현 방법은 다수의 판독 동작들을 수행함으로써 판독된 데이터의 오류율에 기초하여 비휘발성 메모리로부터 데이터를 판독하기 위해 적용될 하나 이상의 판독 파라미터를 선택적으로 조정하는 단계를 포함할 수 있고, 하나 이상의 판독 파라미터는 비휘발성 메모리의 비트라인 방전 경로의 상태, 비휘발성 메모리의 메모리 셀을 판독하기 위한 워드라인의 워드라인 전압 레벨, 및 비트라인의 프리차지 레벨을 포함한다.

- [0089] 대안으로, 또는 추가로, 또 다른 실시예에서, 컴퓨터 구현 방법은 다수의 감지 동작들의 결과들을 인코딩된 상태 신뢰 데이터로서 저장하기 위해 전송하는 단계 - 각 감지 조건은 감지 전압과 감지 펄스 기간의 조합을 포함함 -; 및 다수의 감지 동작들의 완료 후에만 저장된 인코딩된 상태 신뢰 데이터를 외부 장치로 전송되도록 스케줄링하는 단계를 포함할 수 있다.

- [0090] 대안으로, 또는 추가로, 또 다른 실시예에서, 컴퓨터 구현 방법은 연속되는 감지 동작들 사이의 워드라인의 램프의 기간이 제1 문턱치를 초과하는 경우에 비트라인 방전 경로를 디스에이블시키는 단계를 포함할 수 있다.

- [0091] 대안으로, 또는 추가로, 또 다른 실시예에서, 컴퓨터 구현 방법은 메모리 셀의 배치를 검증할 때 존재한 워드라인의 상태와 후속 판독 동작을 위한 워드 라인의 예상 상태 간의 차이가 제2 문턱치를 초과하는 경우에 워드라인 전압을 조정하는 단계를 포함할 수 있다.

- [0092] 대안으로, 또는 추가로, 또 다른 실시예에서, 컴퓨터 구현 방법은 제1 감지 동작과 다음 감지 동작 사이에 워드라인 전압을 조정하기 위해 할당된 시간이 제3 문턱치를 초과하는 경우에 비트라인의 프리차지 레벨이 조정되고 비트라인이 재충전되도록 지시하는 단계를 포함할 수 있다.

- [0093] 대안으로, 또는 추가로, 또 다른 실시예에서, 컴퓨터 구현 방법은 비트라인 판독과 비트라인 검증 조건들 간의

오프셋이 제4 문턱치를 초과하는 경우에 제1 감지 동작과 다음 감지 동작 사이에 비트라인의 프라차지 레벨이 조정되고 비트라인이 재충전되도록 지시하는 단계를 포함할 수 있다.

[0094] 대안으로, 또는 추가로, 또 다른 실시예에서, 컴퓨터 구현 방법은 판독 동작 중의 워드라인 전압의 변화가 제5 문턱치를 초과하는 경우에 감지 동작의 감지 펄스 중에 이용될 기준 전압의 값과, 감지 펄스의 기간 중 하나 이상을 조정하는 단계를 포함할 수 있다.

[0095] 대안으로, 또는 추가로, 또 다른 실시예에서, 장치는 전술한 실시예들 중 어느 하나의 방법을 수행하기 위한 수단을 포함할 수 있다.

[0096] 대안으로, 또는 추가로, 또 다른 실시예에서, 적어도 하나의 기계 판독가능 매체는, 컴퓨팅 장치에서 실행되는 것에 응하여, 컴퓨팅 장치로 하여금 전술한 실시예들 중 어느 하나에 따른 방법을 수행하게 하는 복수의 명령어를 포함할 수 있다.

[0097] 요약서는 독자가 기술 명세서의 본질을 빠르게 확인하는 것을 가능하게 하기 위해 제공된다는 점을 강조한다. 요약서는 그것이 청구항들의 범위 또는 의미를 해석하거나 한정하는 데 사용되지 않을 것임을 전제로 하고 제시된다. 게다가, 위의 상세한 설명에서는, 개시의 간소화를 위해 다양한 특징들이 단일 실시예 내에 함께 그룹화되어 있다는 것을 알 수 있다. 이러한 개시 방법은 청구되는 실시예들이 각각의 청구항에 명확히 기재된 것보다 많은 특징을 필요로 한다는 의도를 반영하는 것으로 해석되지 않아야 한다. 오히려, 아래의 청구항들이 반영하는 바와 같이, 본 발명의 내용은 단일의 개시된 실시예의 모든 특징들보다 적은 특징에 존재한다. 따라서 아래의 청구항들은 이로써 상세한 설명 내에 포함되며, 각각의 청구항은 개별 실시예로서 독립한다. 첨부된 청구항들에서, 용어 "including" 및 "in which"는 각각의 용어 "comprising" 및 "wherein"의 평이한 영어 등가물들로서 사용된다. 더욱이, 용어 "제1", "제2", "제3" 등은 라벨들로서 사용될 뿐이며, 그들의 대상들에 대해 수치적 요구들을 부과하는 것을 의도하지 않는다.

[0098] 위에 설명한 것은 개시된 아키텍처의 예들을 포함한다. 물론, 상상할 수 있는 모든 컴포넌트들 및/또는 방법들의 조합을 기술하는 것은 불가능하지만, 통상의 기술을 가진 당업자는 많은 추가의 조합들 및 치환들이 가능하다는 것을 알 수 있다. 따라서, 신규한 아키텍처는 첨부된 청구항들의 사상 및 범위 안에 포함되는 모든 그러한 변경들, 수정들 및 변형들을 포괄하는 것을 의도한다.

[0099] 다양한 실시예들은 하드웨어 요소들, 소프트웨어 요소들, 또는 이 둘의 조합을 이용하여 구현될 수 있다. 하드웨어 요소들의 예들은 프로세서, 마이크로프로세서, 회로, 회로 요소(예컨대, 트랜지스터, 저항기, 커패시터, 인덕터 등), 집적 회로, ASIC(application specific integrated circuits), PLD(programmable logic devices), DSP(digital signal processors), FPGA(field programmable gate array), 논리 게이트, 레지스터, 반도체 장치, 칩, 마이크로칩, 칩셋 등을 포함할 수 있다. 소프트웨어의 예들은 소프트웨어 컴포넌트, 프로그램, 애플리케이션, 컴퓨터 프로그램, 애플리케이션 프로그램, 시스템 프로그램, 기계 프로그램, 운영 체제 소프트웨어, 미들웨어, 펌웨어, 소프트웨어 모듈, 루틴, 서브루틴, 함수, 메소드, 프로시저, 소프트웨어 인터페이스, API(application program interfaces), 명령어 세트, 컴퓨터 코드, 컴퓨터 코드, 코드 세그먼트, 컴퓨터 코드 세그먼트, 워드, 값, 심벌, 또는 이들의 임의 조합을 포함할 수 있다. 실시예를 하드웨어 요소들 및/또는 소프트웨어 요소들을 이용하여 구현할지에 대한 결정은 원하는 계산 레이트, 전력 레벨, 열 허용 오차, 처리 사이클 예산, 입력 데이터 레이트, 출력 데이터 레이트, 메모리 자원, 데이터 버스 속도 및 기타 설계 또는 성능 제약들과 같은 임의의 수의 요인에 따라 변할 수 있다.

[0100] 일부 실시예들은 "결합된" 및 "연결된"이라는 표현과 함께 이들의 파생어들을 이용하여 기술될 수 있다. 이러한 용어들은 서로에 대한 동의어로서 의도된 것은 아니다. 예를 들어, 일부 실시예들은 둘 이상의 요소가 서로 직접 물리적으로 또는 전기적으로 접촉한다는 것을 나타내기 위해 용어 "연결된" 및/또는 "결합된"을 이용하여 기술될 수 있다. 그러나, 용어 "결합된"은 둘 이상의 요소가 서로 직접 접촉하지 않지만, 그럼에도 서로 협력하거나 상호작용한다는 것을 의미할 수도 있다.

[0101] 일부 실시예들은, 예를 들어, 컴퓨터에 의해 실행될 경우, 컴퓨터로 하여금 실시예들에 따른 방법들 및/또는 동작들을 수행하게 할 수 있는 명령어 또는 명령어들의 세트를 저장할 수 있는 컴퓨터 판독가능 매체 또는 물품을 이용하여 구현될 수 있다. 그러한 컴퓨터는, 예를 들어, 임의의 적합한 처리 플랫폼, 컴퓨팅 플랫폼, 컴퓨팅 장치, 처리 장치, 컴퓨팅 시스템, 처리 시스템, 컴퓨터, 프로세서, 또는 기타 유사한 것을 포함할 수 있고, 하드웨어 및/또는 소프트웨어의 임의의 적합한 조합을 이용하여 구현될 수 있다. 컴퓨터 판독가능 매체 또는 물품은, 예를 들어, 임의의 적합한 유형의 메모리 유닛, 메모리 장치, 메모리 물품, 메모리 매체, 저장 장치, 저

장 물품, 저장 매체 및/또는 저장 유닛, 예를 들어, 메모리, 이동식 또는 비이동식 매체, 소거 가능 또는 소거 불가 매체, 기입 가능 또는 재기입 가능 매체, 디지털 또는 아날로그 매체, 하드 디스크, 플로피 디스크, CD-ROM(Compact Disk Read Only Memory), CD-R(Compact Disk Recordable), CD-RW(Compact Disk Rewriteable), 광디스크, 자기 매체, 광자기 매체, 이동식 메모리 카드 또는 디스크, 다양한 유형의 DVD(Digital Versatile Disk), 테이프, 카세트, 또는 기타 유사한 것을 포함할 수 있다. 명령어들은 임의의 적합한 고레벨, 저레벨, 객체 지향, 비주얼, 컴파일러형 및/또는 해석형 프로그래밍 언어를 이용하여 구현된, 임의의 적합한 유형의 코드, 예를 들어 소스 코드, 컴파일러형 코드, 해석형 코드, 실행 가능 코드, 정적 코드, 동적 코드, 암호화된 코드, 및 기타 유사한 것을 포함할 수 있다.

[0102]

구체적으로 다르게 진술되지 않는 한, "처리", "컴퓨팅", "계산", "결정", 또는 기타 유사한 것 등의 용어들은 컴퓨팅 시스템의 레지스터들 및/또는 메모리를 내의 물리적 양들(예컨대, 전자식)로서 표현된 데이터를 컴퓨팅 시스템의 메모리들, 레지스터들 또는 다른 그러한 정보 저장, 전송 또는 표시 장치들 내의 물리적 양들로서 유사하게 표현된 다른 데이터가 되도록 조작 및/또는 변형시키는 컴퓨터 또는 컴퓨팅 시스템, 또는 유사한 전자 컴퓨팅 장치의 액션 및/또는 프로세스를 지칭한다는 것을 알 수 있다. 실시예들은 이에 관련하여 제한되지 않는다.

[0103]

본 내용은 구조적 특징들 및/또는 방법 단계들에 특유한 언어로 설명되었지만, 첨부된 청구항들에서 정의되는 내용은 반드시 전술한 특정 특징들 또는 단계들로 제한되는 것은 아니라는 것을 이해해야 한다. 오히려, 전술한 특정 특징들 및 단계들은 청구항들을 구현하는 예시의 형태들로서 개시되어 있다.

## 도면

### 도면1

### 도면2

### 도면3

## 도면4

## 도면5

도면6

도면7a

도면7b

## 도면8

## 도면9

## 도면10

## 도면11