(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4879515号

(P4879515)

(45) 発行日 平成24年2月22日(2012.2.22)

(24) 登録日 平成23年12月9日(2011.12.9)

(51) Int.Cl.

F 1

**G09G 3/30 (2006.01)**

**G09G 3/20 (2006.01)**

**H01L 51/50 (2006.01)**

GO9G 3/30 J

GO9G 3/20 641A

GO9G 3/20 612F

GO9G 3/20 621A

GO9G 3/20 623D

請求項の数 2 (全 42 頁) 最終頁に続く

(21) 出願番号

特願2005-144874 (P2005-144874)

(22) 出願日

平成17年5月18日 (2005.5.18)

(65) 公開番号

特開2006-11401 (P2006-11401A)

(43) 公開日

平成18年1月12日 (2006.1.12)

審査請求日

平成20年3月20日 (2008.3.20)

(31) 優先権主張番号

特願2004-152628 (P2004-152628)

(32) 優先日

平成16年5月21日 (2004.5.21)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 木村 肇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 早川 昌彦

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山崎 優

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】表示装置及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のスイッチと、第2のスイッチと、第3のスイッチと、第1の容量素子と、第2の容量素子と、インバータと、発光素子と、電流源と、を有し、

前記インバータは、pチャネル型の薄膜トランジスタと、nチャネル型の薄膜トランジスタとを有し、

前記第1のスイッチの一方の電極は、ビデオ信号または基準信号が入力される第1の配線と電気的に接続され、

前記第1のスイッチの他方の電極は、前記第1の容量素子の一方の電極と電気的に接続され、

前記第1の容量素子の他方の電極は、固定電位が与えられる第2の配線と電気的に接続され、

前記第1のスイッチの他方の電極は、前記第2の容量素子の一方の電極と電気的に接続され、

前記第2の容量素子の他方の電極は、前記pチャネル型の薄膜トランジスタのゲートと電気的に接続され、

前記第2の容量素子の他方の電極は、前記nチャネル型の薄膜トランジスタのゲートと電気的に接続され、

前記pチャネル型の薄膜トランジスタのソースまたはドレインの一方は、第1の電源線と電気的に接続され、

10

20

前記 p チャネル型の薄膜トランジスタのソースまたはドレインの他方は、前記第 2 のスイッチの他方の電極と電気的に接続され、

前記 n チャネル型の薄膜トランジスタのソースまたはドレインの一方は、第 2 の電源線と電気的に接続され、

前記 n チャネル型の薄膜トランジスタのソースまたはドレインの他方は、前記第 2 のスイッチの他方の電極と電気的に接続され、

前記第 2 の容量素子の他方の電極は、前記第 2 のスイッチの一方の電極と電気的に接続され、

前記 n チャネル型の薄膜トランジスタのソースまたはドレインの他方、前記 p チャネル型の薄膜トランジスタのソースまたはドレインの他方、及び前記第 2 のスイッチの他方の電極の電位によって、前記第 3 のスイッチが制御され、

前記第 3 のスイッチの一方の電極は、前記電流源と電気的に接続され、

前記第 3 のスイッチの他方の電極は、前記発光素子と電気的に接続され

前記第 1 の電源線の電位は、前記第 2 の電源線の電位に比較して高く、

前記第 2 の配線として、前記第 1 の電源線または前記第 2 の電源線が用いられていることを特徴とする表示装置。

## 【請求項 2】

請求項 1 に記載の表示装置を用いた電子機器。

## 【発明の詳細な説明】

### 【技術分野】

20

### 【0001】

本発明は自発光素子を含む表示装置及びその駆動方法に関する。

### 【背景技術】

### 【0002】

従来の自発光素子を含む表示装置には、画素回路内でコンパレータ回路を用いて、ビデオ信号として入力された信号電圧と、1 フレーム期間かけて変化するような三角波である基準信号の電圧とを比較し、電圧関係が反転するまでの期間によって発光素子の発光する時間を制御することにより 1 フレーム時間内の発光時間をアナログ的に制御して、階調を表現する表示方法が提案されている（非特許文献 1 及び 2 参照。）。

【非特許文献 1】 "An Innovative Pixel-Driving Scheme for 64-Level Gray-Scale Full-Color Active Matrix OLED Displays" Hajime Akimoto et al SID'02DIGEST P972-975

30

【非特許文献 2】 "A 3.5-inch OLED Display using a 4-TFT Pixel Circuit with an Innovative Pixel Driving Scheme" Hiroshi Kageyama, Hajime Akimoto SID'03DIGEST P96-9

9

### 【発明の開示】

### 【発明が解決しようとする課題】

### 【0003】

上記非特許文献 1 では、1 フレーム期間で発光期間と、信号入力期間とを設けていないようにするため、スイープラインと、データラインとを設けている。これらを設けると、ビデオ信号と、基準信号とを同時に入力することができる。従って、1 フレーム期間は、すべて発光期間となっている。このような画素構成では、デューティ比を大きくすることができる。そのため、自発光素子の発光部に流れる電流の電流密度を小さくすることができる、発光素子の信頼性を高めることができる。しかし、基準信号を入力するスイープラインと、ビデオ信号を入力するデータラインとを設けるため、開口率が低くなってしまう。

40

### 【0004】

上記非特許文献 2 では、スイープラインを設けていない画素構成が開示されている。そのため、上記非特許文献 1 よりも開口率を大きくすることができる。しかし、このような画素構成では、デューティ比が小さくなってしまう。これは、同時に基準信号と、ビデオ信号とを入力できないため、1 フレーム期間を発光期間と、信号入力期間とに分けているからである。その結果、電流密度が大きくなり、発光素子の信頼性が低下してしまう。

50

**【0005】**

そこで本発明は、開口率が低下しない画素構成を有する表示装置を提供することを課題とする。さらに、本発明はデューティ比を高め、発光素子の信頼性を高める表示装置及びその駆動方法を提供することを課題とする。

**【課題を解決するための手段】****【0006】**

上記課題を鑑み本発明は、ビデオ信号が入力される信号線と、基準信号が入力される信号とを共用し、画素の開口率を向上させることを特徴とする。また信号線を共用するため、1ゲート選択期間において、ビデオ信号を入力する期間と、基準信号を入力する期間とを設けるよう駆動することを特徴とする。本発明の駆動方法により、1ゲート選択期間に、ビデオ信号と、基準信号とを入力することができるため、1フレーム期間を階調表示期間(点灯期間、発光期間とも表記する)と、信号入力期間とに分ける必要がない。

10

**【0007】**

本発明の表示装置の駆動方法の一例は、アナログ信号が入力される信号線と、第1の走査線により制御される第1のスイッチと、第2の走査線により制御される第2のスイッチと、第2のスイッチに接続される発光素子とを有し、1ゲート選択期間の第1の期間において、第1のスイッチ及び第2のスイッチが選択されて、アナログ信号が入力され、1ゲート選択期間の第2の期間において、第1のスイッチが選択されて、信号線から基準信号が入力され、アナログ信号と、基準信号とによって発光素子が点灯(発光)することを特徴とする。

20

**【0008】**

本発明の表示装置の駆動方法の一例は、アナログ信号が入力される信号線と、第1の走査線により制御される第1のスイッチと、第2の走査線により制御される第2のスイッチと、第2のスイッチが両端に設けられたインバータと、インバータの出力側に設けられた発光素子とを有し、1ゲート選択期間の第1の期間において、第1のスイッチ及び第2のスイッチが選択されて、アナログ信号が入力され、1ゲート選択期間の第2の期間において、第1のスイッチが選択されて、信号線から基準信号が入力され、アナログ信号と、基準信号とによってインバータから信号が出力され、当該信号に基づき発光素子が点灯することを特徴とする。

30

**【0009】**

本発明の表示装置の駆動方法の一例は、アナログ信号が入力される信号線と、第1の走査線により制御される第1のスイッチと、第2の走査線により制御される第2のスイッチと、第1のスイッチ及び第2のスイッチが入力側に設けられた差動增幅回路と、差動增幅回路の出力側に設けられた発光素子とを有し、1ゲート選択期間の第1の期間において、第1のスイッチ及び第2のスイッチが選択されて、アナログ信号が入力され、1ゲート選択期間の第2の期間において、第1のスイッチが選択されて、信号線から基準信号が入力され、アナログ信号と、基準信号とによって差動增幅回路から信号が出力され、当該信号に基づき発光素子が点灯することを特徴とする。

**【0010】**

本発明の駆動方法において、インバータ又は差動增幅回路は複数の薄膜トランジスタを有し、薄膜トランジスタのうち発光素子に接続される薄膜トランジスタを、線形領域で動作させることを特徴とする。

40

**【0011】**

本発明の表示装置の一例は、第1の走査線により制御される第1のスイッチと、第2の走査線により制御される第2のスイッチと、第2のスイッチが両端に設けられたインバータ回路と、インバータ回路の出力側に設けられた発光素子と、を有する画素領域と、第1の走査線及び第2の走査線へ入力する信号を生成するドライバとを有し、画素領域と、ドライバとの間に保護回路が設けられていることを特徴とする。

また画素領域と、ドライバとの間に温度補償機能を有する素子が設けられていてもよい。

**【0012】**

50

本発明の表示装置の一例は、第1の走査線により制御される第1のスイッチと、第2の走査線により制御される第2のスイッチと、第1のスイッチ及び第2のスイッチが入力側に設けられた差動增幅回路と、差動增幅回路の出力側に設けられた発光素子と、を有する画素領域と、第1の走査線及び第2の走査線へ入力する信号を生成するドライバとを有し、画素領域と、ドライバとの間に温度補償機能を有する素子が設けられていることを特徴とする。また画素領域と、ドライバとの間に温度補償機能を有する素子が設けられていてもよい。

【発明の効果】

【0013】

このような本発明の駆動方法により、画素の配線、具体的には信号線の本数を低減することができるため、開口率を向上させることができる。そのため、信号線が複数設けられたことによる製造プロセスの不良を低減させることができる。従って、製造歩留りが向上し、さらにコストを低減することができる。また本発明の駆動方法により、デューティ比(1フレーム期間における階調表示期間の割合)を高めることができる。その結果、発光素子に流れる電流密度を低くすることができるため、発光素子の信頼性を高めることができる。

10

【0014】

また本発明の保護回路を設けることにより、素子の静電破壊を防止することができる。さらに本発明の温度補償機能を設けることにより、温度変化に関わらず発光素子は所定の輝度で点灯することができる。

20

【発明を実施するための最良の形態】

【0015】

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

【0016】

(実施の形態1)

30

本実施の形態では、画素構成について説明する。

【0017】

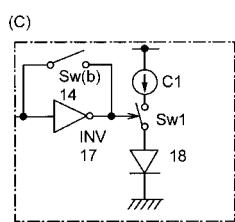

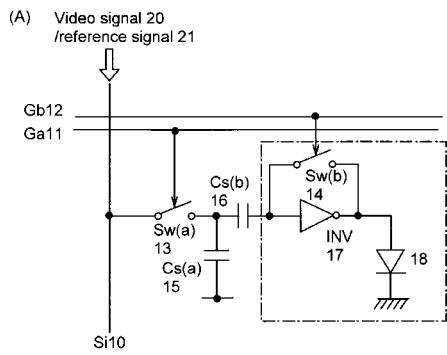

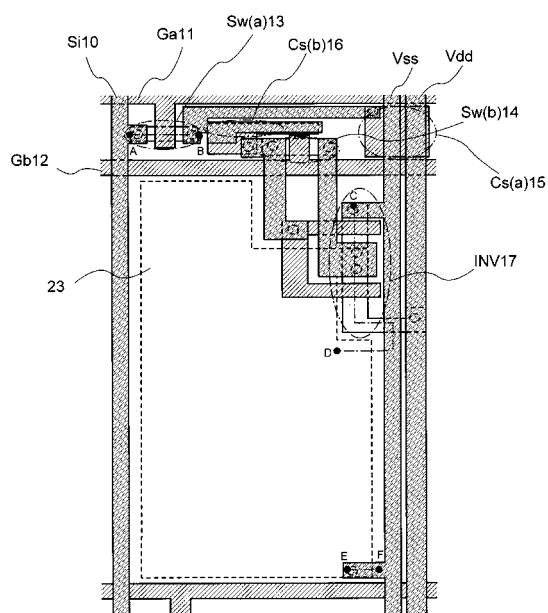

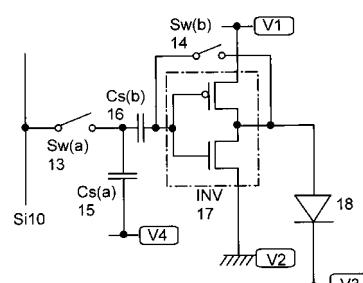

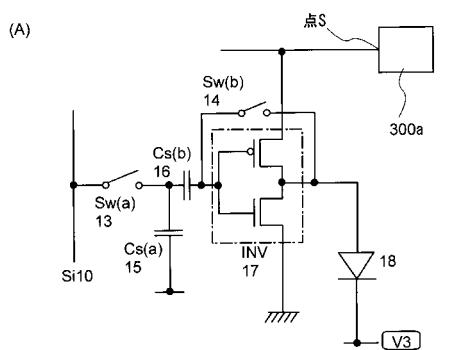

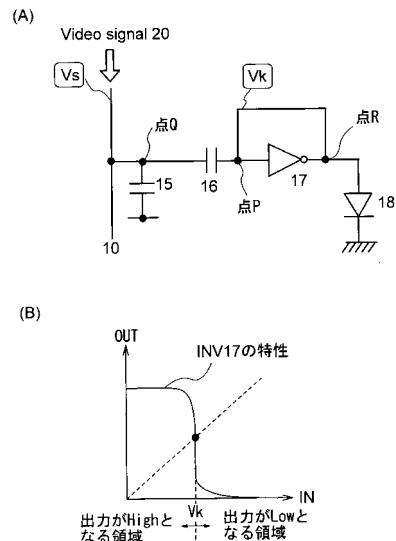

図1(A)に示すように、画素は、信号線(Si)10、第1の走査線(Ga)11、第2の走査線(Gb)12、第1のスイッチ(Sw(a))13、第2のスイッチ(Sw(b))14、第1の容量素子(Cs(a))15、第2の容量素子(Cs(b))16、インバータ17、発光素子18を有する。第1のスイッチ13及び第2のスイッチ14は、例えば薄膜トランジスタを用いて作製することができる。薄膜トランジスタは、ゲート電極、ソース電極、ドレイン電極の3つの端子を有するが、特にソース電極、ドレイン電極に関しては、薄膜トランジスタの構造上、明確に区別が出来ない。よって、素子間の接続について説明する際は、ソース電極、ドレイン電極のうち一方を第1の電極、他方を第2の電極と表記する。

40

【0018】

このような画素構成の接続関係等について説明する。なお、接続するとは、電気的に接続されていればよい。すなわち、各素子間にスイッチ等のその他の素子が設けられていても構わない。第1のスイッチ13の一方は、信号線10に接続され、第1の走査線11によつて制御される。第1のスイッチ13の他方には、第1の容量素子15の一方が接続される。第1の容量素子15の他方は、任意の配線に接続されている。任意の配線は、固定電位を有すると好ましいため、インバータが有するアノード線(Vdd線)やVss線を用いることよい。また、前段の画素が有する第2の走査線を用いることもできる。また第1の容量素子15は、信号線10から入力される電荷を保持する機能を有していればよい。具

50

体的には、第1の容量素子15は、信号線10から入力される基準信号21を保持すればよい。以下に説明するが、本発明は1ゲート選択期間という非常に短い時間にビデオ信号と、基準信号との入力を行い、基準信号は、1ゲート選択期間の周期で入力し直すので、第1の容量素子15は小さくてすむ。すなわち、短時間で基準信号21を入力するため、電荷を保持する期間が短くて済むため、第1の容量素子15は小さくてすむ。

【0019】

第2のスイッチ14は、インバータ17の両端に接続され、第2の走査線12によって制御される。第2の容量素子16は、第1のスイッチ13と、第2のスイッチ14の一方の間に接続されている。第2の容量素子16は、信号線10から入力される電荷を保持する機能を有していればよい。具体的には、第2の容量素子16は、信号線10から入力されるビデオ信号20（正確には、インバータのしきい値電圧とビデオ信号の差分の電圧）を保持すればよい。

10

【0020】

発光素子18は、インバータ17の出力側に接続される。なお発光素子18と、インバータ17との間には、その他の素子、例えばスイッチ等が設けられていても構わない。このようなスイッチを設けることにより、第2のスイッチ14がオンとなるとき、発光素子18が点灯してしまうことを防止できる。

【0021】

このような画素構成によって、1つの信号線からビデオ信号20、及び基準信号21を入力することができる。その結果、画素の開口率を高めることができる。さらに本発明の動作を用いると、デューティ比を高くすることができます。これは、1フレーム期間で、階調表示期間と、信号入力期間とを分けなくともすむからである。その結果、1フレーム期間中、階調表示期間とすることができる、デューティ比を高めることができる。以下に、図1(A)に示した画素構成を有する表示装置の動作について説明する。

20

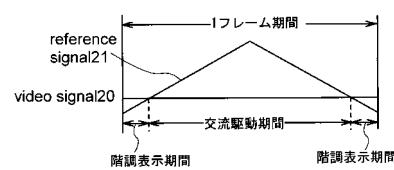

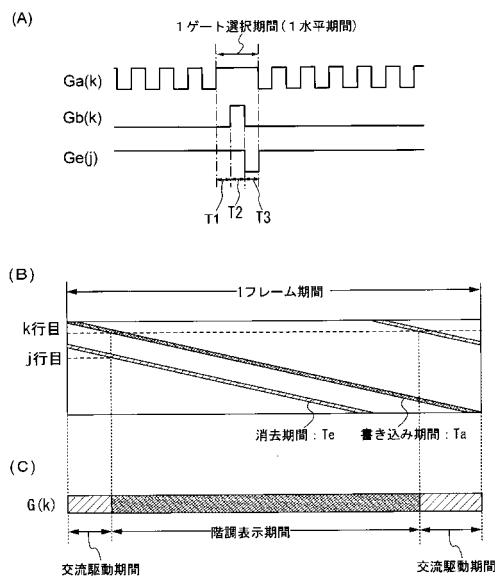

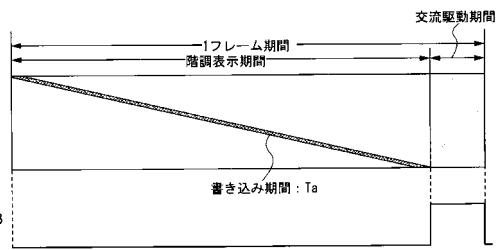

【0022】

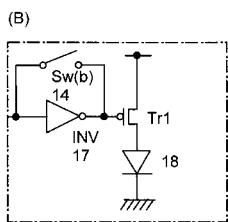

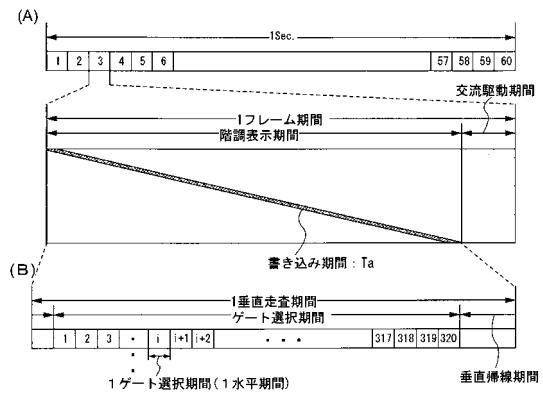

図2(A)には、例えば1秒間に60フレームの画像の書き換えが行われる、1フレーム期間のタイミングチャートであって、縦軸が走査線G（1行目から最終行目）、横軸が時間を示す。また本実施の形態では、図2(A)に示すように、1フレーム期間は階調表示期間と、交流駆動期間とが設けられている場合で説明する。しかし本発明は、交流駆動期間を設けなくともよい。

30

【0023】

なお本実施の形態において、インバータ17が有する薄膜トランジスタ、特にpチャネル型の薄膜トランジスタを飽和領域で動作させる必要がないことを特徴とする。すなわち、薄膜トランジスタを線形領域で動作させることができるので、薄膜トランジスタのソース・ドレイン間電圧が小さくなるので、駆動電圧を高くする必要がなく、消費電力を削減することができる。

【0024】

また交流駆動期間では、発光素子に対して逆方向の電圧（逆方向電圧）、つまり発光素子が点灯しない電圧を印加することができる。例えば、発光素子の対向電極と、インバータが有する高電位側電源（Vdd）の電位を変えればよい。なお、発光素子18に逆方向電圧の電圧を印加するタイミング、つまり交流駆動期間は、図2(A)に限定されない。すなわち、1フレーム毎に交流駆動期間を設ける必要はない。また1フレームの後半に交流駆動期間を設ける必要もない。交流駆動期間の動作は、以下の実施の形態で説明する。加えてその他の逆方向電圧の構成、及びその動作等については、以下の実施の形態で説明する。

40

【0025】

逆方向電圧を印加する結果、発光素子の状態を改善し、信頼性を向上させることができるため好ましい。また、発光素子は、異物の付着や、陽極又は陰極にある微細な突起によるピンホール、電界発光層の不均一性を起因として、陽極と陰極が短絡する初期不良が生じることがある。このような初期不良が発生すると、信号に応じた点灯及び非点灯が行われ

50

ず、電流のほとんどが短絡部を流れてしまい、画素が消光する現象が生じることがある。その結果、画像の表示が良好に行われないとという問題が発生する。また、この短絡は任意の画素に生じる恐れがある。そこで本実施の形態のように、発光素子に逆方向電圧を印加する。すると、短絡部のみに局所的な電流が流れ、該短絡部が発熱し、短絡部を酸化又は炭化させることができる。その結果、短絡部を絶縁化させることができるために、短絡部外の領域に電流が流れ、信号に応じた輝度を得ることができる。このように逆方向電圧を印加することにより、初期不良が生じても、その不良を解消し、画像の表示を良好に行うことができる。なお、このような短絡部の絶縁化は、出荷前に行うとよい。

#### 【0026】

また、初期不良だけでなく、時間の経過に伴い、新たに陽極と陰極の短絡が発生することがある。このような不良は、進行性不良とも呼ばれる。そこで、定期的に発光素子に逆方向電圧を印加することができるので、進行性不良が生じても、その不良を解消し、画像の表示を良好に行うことができる。

10

#### 【0027】

また逆方向電圧を印加することによって、画像の焼き付きを防止することができる。画像の焼き付きとは、発光素子18の劣化状態により生じるが、逆方向電圧を印加することにより、劣化状態を低減することができる。その結果、画像の焼き付きが防止できる。

#### 【0028】

また一般に発光素子の劣化は、初期に大きく進み、時間と共に劣化の進行度合いが少なくなってくる。すなわち画素において、一度劣化した発光素子は、さらなる劣化が生じにくくなる。そのため、出荷前、又は画像を表示しないとき等に、全画素を点灯し、劣化していない画素に劣化を生じさせることによって、全画素の劣化状態を平均化することができる。このように、表示しないときに全画素を点灯してもよい。

20

#### 【0029】

次に図2(B)に示すように、書き込み期間には、1垂直走査期間が設けられ、1垂直走査期間は垂直帰線期間、及びゲート選択期間が設けられている。垂直帰線期間では、書き込み方向を変えたり、予備的な画素に信号を書き込んだりすることができる。ゲート選択期間は、走査線の本数分の選択期間が設けられており、これを1ゲート選択期間(1水平期間)と呼ぶ。

#### 【0030】

30

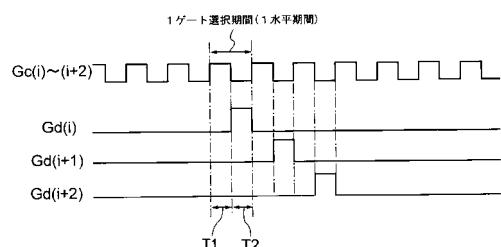

図2(C)には、 $i$ 行目～( $i + 2$ )行目における第1の走査線G<sub>a</sub>及び第2の走査線G<sub>b</sub>へ入力される信号の波形を示す。本実施の形態において、1ゲート選択期間は、基準信号入力期間T<sub>1</sub>と、ビデオ信号入力期間T<sub>2</sub>が設けられている。またこれらの期間を、図2(C)に示すようにそれぞれT( $i$ )～T( $i + 6$ )と表記し、これらT( $i$ )～T( $i + 6$ )期間の画素の動作について説明する。

#### 【0031】

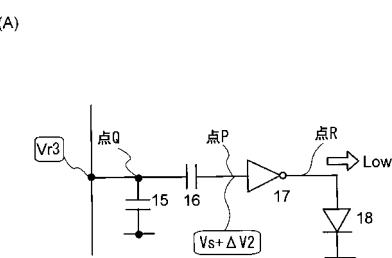

T( $i$ )期間において、図35(A)に示すように第1のスイッチ13及び第2のスイッチ14がオンとなる。なお図面では、スイッチがオンとなるときは直線でつなぐように記載し、オフとなるときは切断されるように記載する。すると、信号線10からビデオ信号20が入力される。このときのビデオ信号20の電位をV<sub>s</sub>とする。また第2のスイッチ14がオンとなっているため、インバータ17の入力側と出力側が接続される。このとき、点Pの電位がV<sub>k</sub>となる。よって、第2の容量素子16には、(V<sub>k</sub> - V<sub>s</sub>)分の電荷が蓄積される。このようにして、T( $i$ )期間では、ビデオ信号が入力される。

40

#### 【0032】

なお、V<sub>k</sub>とは、図35(B)に示すように、インバータ17の入力側と出力側が接続された状態の電位、つまりインバータ17の入力と出力が等しくなるとき電位である。また図35(B)に示すように、インバータ17の入力側である点Pの電位がV<sub>k</sub>より上がると、インバータ17の出力、つまり点Rの電位がL<sub>ow</sub>となる。このとき、発光素子18は非点灯となる。逆に点Pの電位がV<sub>k</sub>より下がると、点Rの電位がH<sub>igh</sub>となる。このとき、発光素子18に電圧が印加され点灯する。

50

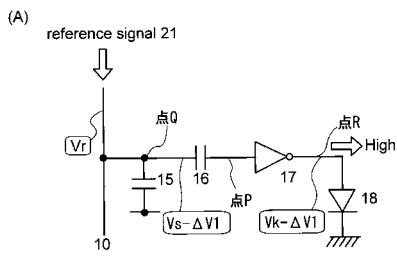

## 【0033】

次に  $T(i+1)$  期間において、図36(A)に示すように、第1のスイッチ13がオン、第2のスイッチ14がオフとなる。すると、信号線10から基準信号21が入力される。なお基準信号21は、図36(B)に示すように、1フレーム期間で三角波を有する。この  $T(i+1)$  期間では、基準信号21の電位は  $V_r1$  であるとする。図36(B)に示すように、ビデオ信号の電位である  $V_s$  は、  $V_r1$  より大きいものとする。ここで  $V_s - V_r1 = V1$  とすると、点Qの電位は  $V_r1 (= V_s - V1)$  となり、  $V_s$  よりも  $V1$  だけ低くある。従って、点Pの電位は、  $(V_k - V1)$  となる。このとき、点Pの電位は  $V_k$  より小さいため、点Rの電位が  $HIGH$  となる。このとき、発光素子18に電圧が印加され点灯する。

10

## 【0034】

次に、  $T(i+2)$  期間において、図37に示すように、第1のスイッチ13及び第2のスイッチ14がオフとなる。そのため点Qの電位となる  $V_r1$  の電位は、第1の容量素子15に保持される。また第2の容量素子16には、  $(V_k - V_s)$  分の電荷が保持されたままである。そのため、点Pの電位は、  $(V_k - V1)$  に保持され、点Rの電位は  $HIGH$  に維持し、発光素子18に電圧が印加され点灯する。

20

## 【0035】

このとき、次の行である  $(i+1)$  行目の画素の第1のスイッチ13、及び第2のスイッチ14はオンとなる。そして信号線10から、  $(i+1)$  行目の画素用のビデオ信号20が入力されている。

20

## 【0036】

次いで、  $T(i+3)$  期間において、第1のスイッチ13がオン、第2のスイッチ14がオフとなる。すると信号線10から基準信号21が入力される。この基準信号21の電位を  $V_r2$  とする。基準信号21の電位  $V_r2$  はビデオ信号の電位  $V_s$  より低いままなので、点Pの電位は  $V_k$  より低いままである。そのため、点Rは  $HIGH$  を維持し、発光素子18に電圧が印加され点灯する。

## 【0037】

次いで、  $T(i+4)$  期間において、図37に示す状態と同様に、第1のスイッチ13、及び第2のスイッチ14がオフとなる。ただし  $T(i+4)$  期間では、第1の容量素子15に  $V_r2$  分の電荷が保持されるため、点Qの電位は  $V_r2$  である。また第2の容量素子16には、  $(V_k - V_s)$  分の電荷が保持されたままである。そのため、点Pの電位は、  $V_k - V2$  (ここで  $V2 = V_s - V_r2$ ) に保持されている。よって、点Pは  $V_k$  より低いので、点Rの電位は  $HIGH$  に維持されている。

30

## 【0038】

このとき、さらに次の行である  $(i+2)$  行目の画素の第1のスイッチ13、及び第2のスイッチ14はオンとなる。そして、信号線10から  $(i+2)$  行目の画素用のビデオ信号20が入力されている。

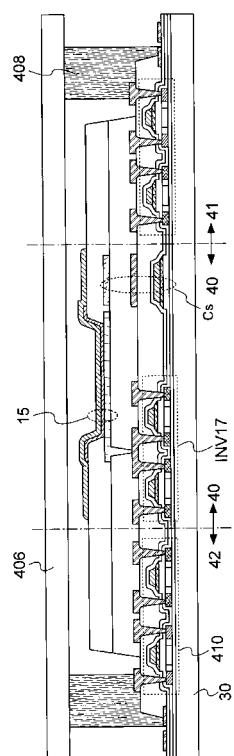

## 【0039】

次いで、  $T(i+5)$  期間において、図38(A)に示すように、第1のスイッチ13がオン、第2のスイッチ14がオフとなる。すると信号線10から基準信号21が入力される。この基準信号21の電位を  $V_r3$  とする。図38(B)に示すように、  $V_s - V_r3 = V3$  を満たす。このとき、  $V3$  は負の値であり、  $V_r3$  は  $V_s$  より高くなる。従って、点Pの電位は  $V_k$  より高くなる。点そのため、点Rは  $LOW$  となる。このとき、発光素子18は、非点灯となる。

40

## 【0040】

次いで、  $T(i+6)$  期間において、第1のスイッチ13、及び第2のスイッチ14がオフとなる。すると第1の容量素子15に  $V_r3$  が保持されるため、点Qの電位は  $V_r3$  となる。また第2の容量素子16には、  $(V_k - V_s)$  分の電荷が保持されたままである。そのため、点Pの電位は、  $V_k - V3$  (  $V3 = V_s - V_r3$  ) に保持されている。そのため、点Rの電位は  $LOW$  に維持され、発光素子18は非点灯となる。

50

## 【0041】

このとき、さらに次の行である( $i + 3$ )行目の画素の第1のスイッチ13、及び第2のスイッチ14はオンとなる。そして信号線10から、( $i + 3$ )行目の画素用のビデオ信号20が入力されている。

## 【0042】

このようにビデオ信号20及び基準信号21の書き込みと、基準信号21の保存を交互に行えばよい。そして、基準信号21の電位がビデオ信号20の電位より高い又は低いかにより、発光素子18の点灯、非点灯が制御される。

## 【0043】

なお上述したように本実施の形態において、インバータ17が有する薄膜トランジスタ、特にpチャネル型の薄膜トランジスタを飽和領域で動作させる必要がない。そのため、駆動電圧を高くする必要がなく、消費電力を削減することができる。 10

## 【0044】

また本実施の形態は、1ゲート選択期間に基準信号入力期間T1と、ビデオ信号入力期間T2が設けられていることを特徴とする。その結果、1つの信号線10を共用でき、開口率を高めることができる。さらにデューティ比を高めることができる。また1ゲート選択期間に、基準信号入力期間T1と、ビデオ信号入力期間T2を設けるため、走査線駆動回路の動作周波数を高めるとよい。なお、ある画素に着目したとき、基準信号入力期間T1と、ビデオ信号入力期間T2とが現れる順序は、どちらが先でもよい。

## 【0045】

また図1(A)とは異なる画素構成について説明する。図1(B)には、図1(A)に示す画素において、インバータ17と、発光素子18との間にトランジスタTr1を設けた画素を示す。その他の構成は、図1(A)と同様であるため、説明は省略する。 20

## 【0046】

また図1(C)には、図1(A)に示す画素において、インバータ17と、発光素子18との間にスイッチSw1を設け、Sw1には電流源C1が設けられた画素を示す。電流源C1が一定の電流を流すことにより、発光素子18には、一定の電流を流すことができる。その他の構成は、図1(A)と同様であるため、説明は省略する。

## 【0047】

なお本実施の形態は、その他の実施の形態と自由に組み合わせることができる。 30

## 【0048】

## (実施の形態2)

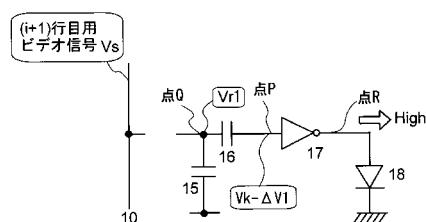

本実施の形態では、通常のCMOS構成のインバータと異なるインバータの構成について説明する。インバータ17は1つの極性のトランジスタを有するように構成することができる。その場合、トランジスタと抵抗素子を設けたり、1つの極性を有するトランジスタを2つ設けてもよい。具体的なインバータを有する画素回路は、図39、図40に示す。

## 【0049】

図39(A)には、抵抗素子Rと、nチャネル型のトランジスタTr6とが設けられている。抵抗素子Rと、トランジスタTr6とは接続し、その間に第2のスイッチ14の一端が接続されている。また当該第2のスイッチ14の一端には、発光素子18の画素電極が接続されている。この抵抗素子Rと、トランジスタTr6がインバータとしての機能を奏する。その他の構成は、図1(A)と同様であるため説明を省略する。 40

## 【0050】

図39(B)には、第1のnチャネル型のトランジスタTr7と、第2のnチャネル型のトランジスタTr8とが設けられている。第1のnチャネル型トランジスタTr7と、第2のnチャネル型のトランジスタTr8とは接続し、その間に第2のスイッチ14の一端が接続されている。また当該第2のスイッチ14の一端には、発光素子18の画素電極が接続されている。第1のnチャネル型トランジスタTr7はダイオード接続となっている。その他の構成は、図1(A)と同様であるため説明を省略する。

## 【0051】

10

20

30

40

50

図40(A)には、抵抗素子Rと、pチャネル型のトランジスタTr9とが設けられている。抵抗素子Rと、トランジスタTr9とは接続し、その間に第2のスイッチ14の一端が接続されている。また当該第2のスイッチ14の一端には、発光素子18の画素電極が接続されている。この抵抗素子Rと、トランジスタTr9がインバータとしての機能を奏する。その他の構成は、図1(A)と同様であるため説明を省略する。

【0052】

図40(B)には、第1のpチャネル型のトランジスタTr10と、第2のpチャネル型のトランジスタTr11とが設けられている。第1のpチャネル型トランジスタTr10と、第2のpチャネル型のトランジスタTr11とは接続し、その間に第2のスイッチ14の一端が接続されている。また当該第2のスイッチ14の一端には、発光素子18の画素電極が接続されている。第2のnチャネル型トランジスタTr11はダイオード接続となっている。その他の構成は、図1(A)と同様であるため説明を省略する。

10

【0053】

図39に示した構成と、図40に示した構成とを比較すると、発光素子18のアノード電圧が各素子の影響を受けにくい。そのため、図40に示す構成は好ましい。

【0054】

(実施の形態3)

本実施の形態では、図1に示した等価回路を有する画素の画素部のレイアウトの一例について説明する。

【0055】

20

図3には、第1のスイッチ13、第2のスイッチ14、及びインバータ17として薄膜トランジスタを用いる場合を示す。なおインバータ17は極性の異なる2以上の薄膜トランジスタを用いて形成する場合で説明する。

【0056】

上記薄膜トランジスタのため、所定の形状にパターニングされた半導体膜を形成する。当該半導体膜を覆うようにゲート絶縁膜を形成する。

【0057】

その後、第1の導電膜を形成し、当該第1の導電膜を第1の走査線(Ga)11、第2の走査線(Gb)12、薄膜トランジスタのゲート電極となるようにパターニングする。

【0058】

30

第1の導電膜を覆って、絶縁膜を形成する。その後、第2の導電膜を形成し、当該第2の導電膜を信号線(Si)10、電源線Vss、Vdd、薄膜トランジスタのソース電極又はドレイン電極となるようにパターニングする。

【0059】

このとき第1の容量素子(Cs(a))15を、第1の導電膜、ゲート絶縁膜又は絶縁膜、第2の導電膜により形成する。そのため、第1の導電膜を、第1の電源線Vss、第2の電源線Vddの下方に形成し、第2の導電膜により、第1のスイッチとしての薄膜トランジスタのソース電極又はドレイン電極と当該第1の導電膜とを接続させる。また、第2の容量素子(Cs(b))16を、第1の導電膜、ゲート絶縁膜又は絶縁膜、第2の導電膜により形成する。そのため、第1の導電膜を第1のスイッチとしての薄膜トランジスタのソース電極又はドレイン電極の下方に形成する。このとき、当該第1の導電膜と、第2のスイッチとしての薄膜トランジスタのソース電極又はドレイン電極とを接続させる。

40

【0060】

発光素子18の画素電極23は、インバータを構成する薄膜トランジスタのソース電極又はドレイン電極に接続するように形成される。

【0061】

このように画素電極まで形成した後、隔壁として機能する絶縁膜を形成し、電界発光層を形成する。隔壁や電界発光層の詳細は、以下の実施の形態において説明する。

【0062】

なお本実施の形態は、その他の実施の形態と自由に組み合わせることができる。

50

## 【0063】

## (実施の形態4)

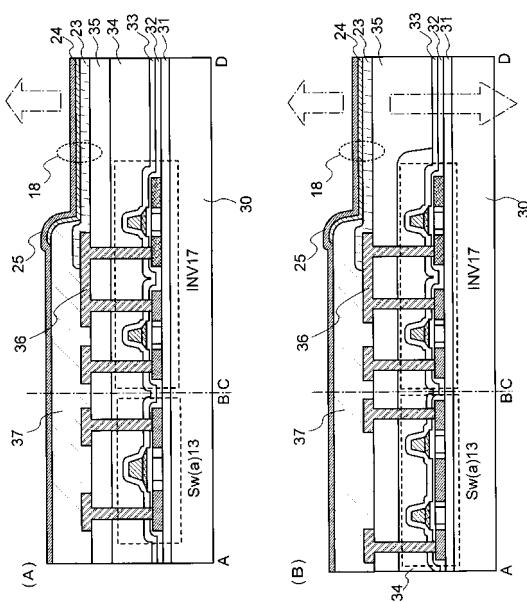

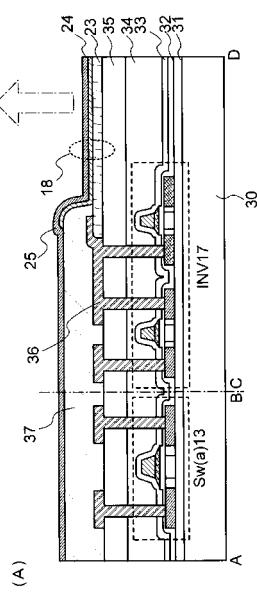

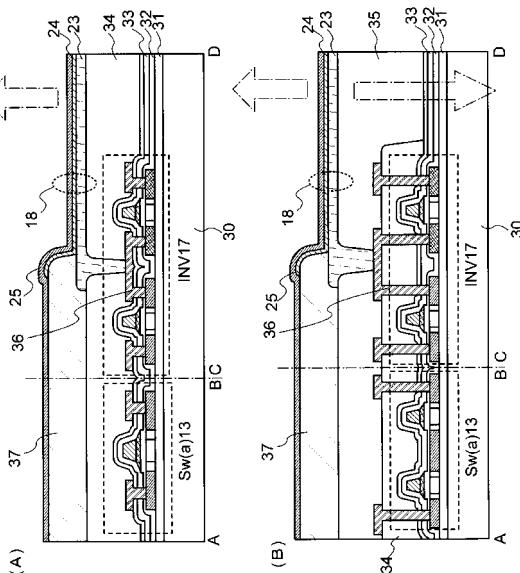

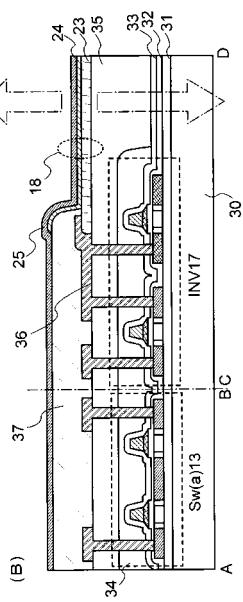

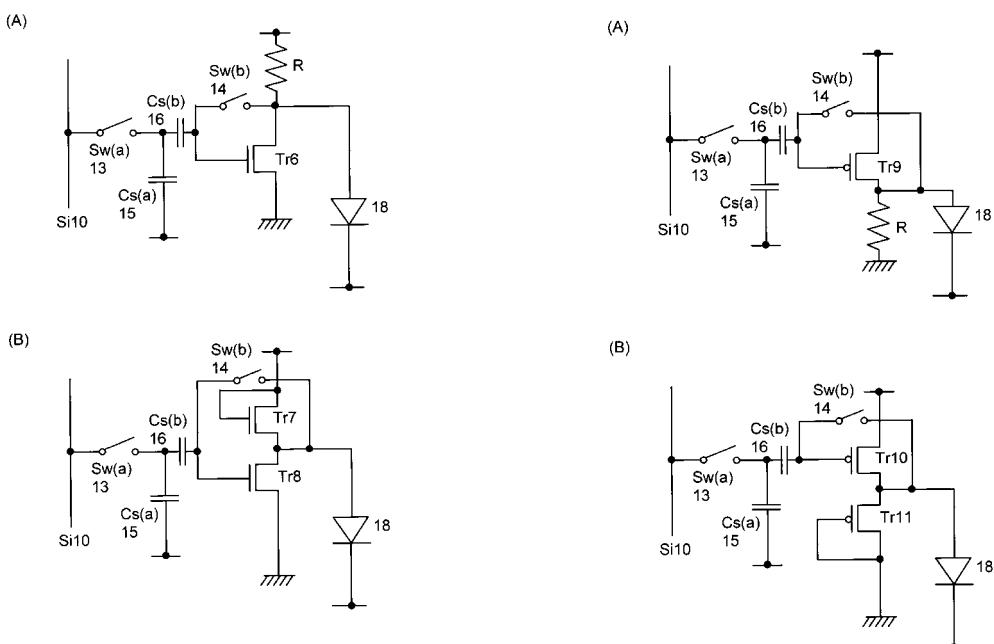

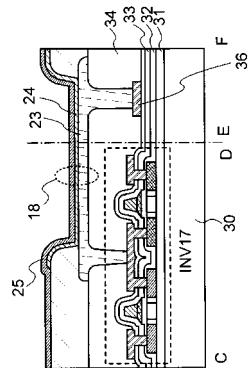

本実施の形態では、図3に一例を示した画素部の断面について説明する。

## 【0064】

図4には、第1のスイッチ13、インバータ17、及び発光素子18の断面図を示す。絶縁基板30上に設けられた下地絶縁膜上には、第1のスイッチ13として薄膜トランジスタTr1、インバータを構成する第1の薄膜トランジスタTr2、第2の薄膜トランジスタTr3が設けられている。本実施の形態では、薄膜トランジスタTr1及びTr2をnチャネル型とし、Tr3をpチャネル型とする。

## 【0065】

10

絶縁基板としては、バリウムホウケイ酸ガラスや、アルミノホウケイ酸ガラスなどのガラス基板、石英基板等が挙げられる。またその他の絶縁表面を有する基板としては、ポリエチレン-テレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルファン(PES)に代表されるプラスチックや、アクリル等の可撓性を有する合成樹脂からなる基板がある。

## 【0066】

薄膜トランジスタTr1～Tr3は、活性層となる半導体膜、半導体膜上に設けられたゲート絶縁膜32、ゲート電極を有する。

## 【0067】

20

半導体膜は、非晶質半導体、非晶質状態と結晶状態とが混在したSAS、非晶質半導体中に0.5nm～20nmの結晶粒を観察することができる微結晶半導体、及び結晶性半導体から選ばれたいずれの状態を有してもよい。

## 【0068】

本実施の形態では、非晶質半導体膜を形成し、加熱処理により結晶化された結晶性半導体膜を用いる。加熱処理とは、加熱炉、レーザ照射、若しくはレーザ光の代わりにランプから発する光の照射(以下、ランプアニールと表記する)、又はそれらを組み合わせて用いることができる。

## 【0069】

レーザ照射を用いる場合、連続発振型のレーザビーム(CWレーザビーム)やパルス発振型のレーザビーム(パルスレーザビーム)を用いることができる。レーザビームとしては、Arレーザ、Krレーザ、エキシマレーザ、YAGレーザ、Y<sub>2</sub>O<sub>3</sub>レーザ、YVO<sub>4</sub>レーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、ガラスレーザ、ルビーレーザ、アレキサンドライトレーザ、Ti:サファイアレーザ、銅蒸気レーザまたは金蒸気レーザのうち一種または複数種から発振されるものを用いることができる。このようなレーザビームの基本波、及び当該基本波の第2高調波、第3高調波、又は第4高調波のレーザビームを照射することで、大粒径の結晶を得ることができる。例えば、Nd:YVO<sub>4</sub>レーザ(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を用いることができる。このときレーザのエネルギー密度は0.01～100MW/cm<sup>2</sup>程度(好ましくは0.1～10MW/cm<sup>2</sup>)が必要である。そして、走査速度を10～2000cm/sec程度として照射する。

30

## 【0070】

40

なお連続発振の基本波のレーザビームと連続発振の高調波のレーザビームとを照射するようにしてもよいし、連続発振の基本波のレーザビームとパルス発振の高調波のレーザビームとを照射するようにしてもよい。複数のレーザビームを照射することにより、エネルギーを補うことができる。

## 【0071】

またパルス発振型のレーザビームであって、半導体膜がレーザ光によって溶融してから固化するまでに、次のパルスのレーザ光を照射できるような発振周波数でレーザを発振させるレーザビームを用いることもできる。このような周波数でレーザビームを発振することで、走査方向に向かって連続的に成長した結晶粒を得ることができる。具体的なレーザ

50

ビームの発振周波数は 10 MHz 以上であって、通常用いられている数十 Hz ~ 数百 Hz の周波数帯よりも著しく高い周波数帯を使用する。

【0072】

また、希ガスや窒素などの不活性ガス雰囲気中でレーザビームを照射するようにしてもよい。これにより、レーザビームの照射による半導体表面の荒れを抑えたり、平坦性を高めることができ、界面準位密度のばらつきによって生じる閾値のばらつきを抑えることができる。

【0073】

また SiH<sub>4</sub> と F<sub>2</sub>、又は SiH<sub>4</sub> と H<sub>2</sub> を用いて微結晶半導体膜を形成し、その後上記のようなレーザ照射を行って結晶化してもよい。

10

【0074】

その他の加熱処理として、加熱炉を用いる場合、非晶質半導体膜を 500 ~ 550 で 2 ~ 20 時間かけて加熱する。このとき、徐々に高温となるように温度を 500 ~ 550 の範囲で多段階に設定するとよい。最初の低温加熱工程により、非晶質半導体膜の水素等が出てくるため、結晶化の際の膜荒れを低減する、所謂水素出しを行なうことができる。さらに、結晶化を促進させる金属元素、例えばニッケル (Ni) を非晶質半導体膜上に形成すると、加熱温度を低減することができ好ましい。このような金属元素を用いた結晶化であっても、600 ~ 950 に加熱しても構わない。

【0075】

但し、金属元素を形成する場合、半導体素子の電気特性に悪影響を及ぼすことが懸念されるので、該金属元素を低減又は除去するためのゲッタリング工程を施す必要が生じる。例えばゲッタリング工程として、非晶質半導体膜をゲッタリングシンクとして金属元素を捕獲するよう工程を行なえばよい。

20

【0076】

また直接下地絶縁膜上に、結晶性半導体膜を形成してもよい。この場合、GeF<sub>4</sub>、又は F<sub>2</sub> 等のフッ素系ガスと、SiH<sub>4</sub>、又は Si<sub>2</sub>H<sub>6</sub> 等のシラン系ガスとを用い、熱又はプラズマを利用して直接、結晶性半導体膜を形成することができる。

【0077】

このような半導体膜の作製方法であって、高温処理が必要となるときは、耐熱性の高い石英基板を用いるとよい。

30

【0078】

このように形成される半導体膜上にゲート絶縁膜、ゲート電極を順に形成する。ゲート絶縁膜は、珪素を有する酸化膜、又は珪素を有する窒化膜を用いることができる。

【0079】

その後ゲート電極をマスクとして自己整合的に不純物元素を添加する。すると、不純物元素が添加されたソース領域及びドレイン領域、並びにゲート電極下方にチャネル形成領域が形成される。このとき、ゲート電極の端面をテーパ形状とすることにより、低濃度不純物領域 (LDD 領域) を形成することができる。低濃度不純物領域を有する構造を、LDD (lightly doped drain) 構造と呼ぶ。LDD 構造は、ホットキャリア劣化耐性を強くでき、またオフリーケ電流も低減できるといった特徴を有している。低濃度不純物領域のうち、ゲート電極と重なっている領域を有する場合、ゲートオーバーラップ LDD 構造 (GOLD 構造) と呼ぶ。GOLD 構造は高電流駆動力で、かつホットキャリア劣化耐性に非常に優れた特徴を有している。例えばゲート電極を積層構造とし、第 1 のゲート電極のテーパ形状と、第 2 のゲート電極のテーパ形状を異ならすことにより LDD 構造や GOLD 構造を形成することができる。このようなゲート電極は、第 1 の導電膜を窒化タンタル (TaN) で形成し、第 2 の導電膜をタンゲステン (W) とする組み合わせ、第 1 の導電膜を窒化タンタル (TaN) で形成し、第 2 の導電膜をチタン (Ti) とする組み合わせ、第 1 の導電膜を窒化タンタル (TaN) で形成し、第 2 の導電膜をアルミニウム (Al) とする組み合わせ、第 1 の導電膜を窒化タンタル (TaN) で形成し、第 2 の導電膜を銅 (Cu) とする組み合わせで形成することが好ましい。また、第 1 の導電膜及び第 2

40

50

の導電膜としてリン( P )等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜や、 A g P d C u 合金を用いてもよい。またチャネル形成領域が微細化するにつれ短チャネル効果を防止するためには、ゲート電極の側面に絶縁物を形成し、当該絶縁物下方に低濃度不純物領域が形成される、所謂サイドウォール構造とすると好ましい。

【 0 0 8 0 】

その後、ゲート絶縁膜を開口して、ソース領域及びドレイン領域に接続する配線(それぞれソース配線及びドレイン配線と表記する)を形成し、薄膜トランジスタとして完成することができる。

【 0 0 8 1 】

しかし本実施の形態では、さらにゲート電極、及び半導体膜を覆ってパッシベーション膜 3 3 を形成する。当該パッシベーション膜 3 3 により、ゲート電極表面の酸化を防止することができる。加えて、パッシベーション膜が有する水素により、半導体膜の欠陥(ダングリングボンド)の終端を行うことができる。パッシベーション膜 3 3 として、珪素を有する酸化膜、又は珪素を有する窒化膜、具体的には酸化珪素( S i O x )、窒化珪素( S i N x )、酸化窒化珪素( S i O x N y )( x > y )、窒化酸化珪素( S i N x O y )( x > y )( x 、 y = 1 、 2 、 3 、 4 、 5 、 6 、 7 、 8 、 9 、 10 )等を用いることができる。さらに本実施の形態では、層間絶縁膜を設け、平坦性を高めることを特徴とする。層間絶縁膜は、有機材料や無機材料を用いることができる。有機材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト、ベンゾシクロブテン、シロキサン、又はポリシラザンを用いることができる。シロキサンとは、シリコン( S i )と酸素( O )との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基( 例えはアルキル基、芳香族炭化水素 )が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。またポリシラザンとは、珪素( S i )と窒素( N )の結合を有するポリマー材料を含む液体材料を出発原料として形成される。無機材料としては、酸化珪素( S i O x )、窒化珪素( S i N x )、酸化窒化珪素( S i O x N y )( x > y )、窒化酸化珪素( S i N x O y )( x > y )( x 、 y = 1 、 2 、 3 、 4 、 5 、 6 、 7 、 8 、 9 、 10 )等の酸素、又は窒素を有する絶縁膜を用いることができる。また、層間絶縁膜として、これら絶縁膜の積層構造を用いてもよい。例えは有機材料を用いて層間絶縁膜を形成すると、平坦性は高まるが、水分や酸素が吸収されやすい状態となってしまう。これを防止するため、有機材料上に、無機材料を有する絶縁膜を形成するとよい。無機材料に、窒素を有する絶縁膜を用いると、水分に加えて N a 等のアルカリイオンの侵入を防ぐことができる。本実施の形態では、第 1 の層間絶縁膜 3 4 に有色性有機材料、第 2 の層間絶縁膜 3 5 に透光性を有する有機材料を用いる。なおカーボンブラック等の粒子を有機材料へ分散させることにより、有色性を得ることができる。有色性有機材料により、配線等による光の回り込みを抑えることができる。所謂ブラックマトリクスとしての機能を奏することができる。

【 0 0 8 2 】

その後、第 1 及び第 2 の層間絶縁膜 3 4 、 3 5 、パッシベーション膜 3 3 及びゲート絶縁膜 3 2 に開口部を設け、ソース配線及びドレイン配線 3 6 を形成する。ソース配線及びドレイン配線は、導電性材料により単層又は積層で形成する。例えは、チタン( T i )と、アルミニウムシリコン( A l - S i )と T i との積層、 M o と、 A l - S i と、 M o との積層、 M o N と、 A l - S i と、 M o N との積層構造を用いることができる。また導電性材料として、炭素及びニッケル( 1 ~ 2 0 w t % )を含むアルミニウム合金( A l ( C + N i ) )膜を用いてもよい。( A l ( C + N i ) )膜は、通電又は熱処理後も耐熱性が高く以下に示す画素電極( I T O や I T S O )と酸化還元電位が近いため、電池効果による電食反応が生じにくく、コンタクト抵抗値に大きな変動がない材料である。

【 0 0 8 3 】

その後、薄膜トランジスタ T r 2 及び T r 3 を接続するソース配線及びドレイン配線 3 6 に、画素電極 2 3 を接続する。画素電極は透光性又は非透光性を有する材料を用いて形成する。例えは、透光性を有する場合、インジウム錫酸化物( I T O 、 Indium Tin Oxide )

10

20

30

40

50

、酸化インジウムに2～20%の酸化亜鉛(  $ZnO$  )を混合したIZO( indium zinc oxide )、酸化インジウムに2～20%の酸化珪素(  $SiO_2$  )を混合したITO-SiO<sub>x</sub>( 便宜上ITSO又はNITOと表記する )、有機インジウム、有機スズ等を用いることもできる。また非透光性を有する材料として、銀( Ag )以外にタンタル、タングステン、チタン、モリブデン、アルミニウム、銅から選ばれた元素、又は前記元素を主成分とする合金材料もしくは化合物材料を用いることができる。

【0084】

画素電極23の端を覆うように、絶縁膜37を形成する。絶縁膜37は、電界発光層を形成するときの隔壁(土手)として機能する。絶縁膜37は、層間絶縁膜と同様に無機材料と有機材料のどちらの材料を用いて形成してもよい。

10

【0085】

次いで絶縁膜37に開口部を形成し、当該開口部に電界発光層24を形成する。このとき絶縁膜37に接するように電界発光層を形成するため、当該電界発光層にピンホールなどが生じないように、曲率半径が連続的に変化する形状を有するとよい。また絶縁膜37の加熱処理から電界発光層24の形成までを、大気に曝すことなく連続して行うとよい。

【0086】

電界発光層の材料は、有機材料(低分子又は高分子を含む)、又は有機材料と無機材料の複合材料として用いることができる。また電界発光層は、液滴吐出法、塗布法又は蒸着法により形成することができる。高分子材料は、液滴吐出法又は塗布法が好ましく、低分子材料は蒸着法、特に真空蒸着法が好ましい。本実施の形態では、電界発光層として、低分子材料を真空蒸着法により形成する。

20

【0087】

なお電界発光層が形成する分子励起子の種類としては一重項励起状態と三重項励起状態が可能である。基底状態は通常一重項状態であり、一重項励起状態からの発光は蛍光と呼ばれる。また、三重項励起状態からの発光は燐光と呼ばれる。電界発光層からの発光とは、どちらの励起状態が寄与する場合も含まれる。さらに、蛍光と燐光を組み合わせて用いてもよく、各RGBの発光特性(発光輝度や寿命等)により蛍光及び燐光のいずれかを選択することができる。例えばR用の電界発光層には、三重項励起状態となる材料を使用し、G、B用には、一重項励起状態となる材料を使用するとよい。

【0088】

詳細な電界発光層は、画素電極23側から順に、HIL(ホール注入層)、HTL(ホール輸送層)、EML(発光層)、ETL(電子輸送層)、EIL(電子注入層)の順に積層されている。なお電界発光層は、積層構造以外に単層構造、又は混合構造をとることができる。

30

【0089】

具体的には、HILとしてCuPcやPEDOT、HTLとして-NPD、ETLとしてBCPやAlq<sub>3</sub>、EILとしてBCP:LiやCaF<sub>2</sub>をそれぞれ用いる。また例えばEMLは、R、G、Bのそれぞれの発光色に対応したドーパント( Rの場合DCM等、Gの場合DMQD等 )をドープしたAlq<sub>3</sub>を用いればよい。

【0090】

なお、電界発光層は上記材料に限定されない。例えば、CuPcやPEDOTの代わりに酸化モリブデン(  $MoO_x$  :  $x = 2 \sim 3$  )等の酸化物と-NPDやルブレンを共蒸着して形成し、ホール注入性を向上させることもできる。また電子注入層にベンゾオキサゾール誘導体( BzOSと示す )を用いてもよい。

40

【0091】

さらに各RGBの電界発光層を形成する場合、カラーフィルターを用いて、高精細な表示を行うこともできる。カラーフィルターにより、各RGBの発光スペクトルにおけるブロードなピークを鋭くなるように補正できるからである。

【0092】

以上、各RGBの電界発光層を形成する場合を説明したが、単色の発光を示す電界発光層

50

を形成してもよい。この場合、カラーフィルターや色変換層を組み合わせることによりフルカラー表示を行うこともできる。例えば、白色又は橙色の発光を示す電界発光層を形成する場合、カラーフィルターやカラーフィルターと色変換層とを組み合わせたものを設けることによりフルカラー表示を行うことができる。

【0093】

もちろん単色の発光を示す電界発光層を形成して単色表示を行ってもよい。例えば、単色発光を用いてエリアカラータイプの表示を行うことができる。エリアカラータイプは、主に文字や記号を表示する場合に適している。

【0094】

その後、電界発光層24及び絶縁膜37を覆うように発光素子18の第2の電極25を形成する。 10

【0095】

なお、画素電極（便宜上第1の電極と表記する）23及び第2の電極25の材料は、仕事関数を考慮して選択する必要がある。そして第1の電極23及び第2の電極25は、画素構造により、いずれも陽極、陰極となりうる。以下に、陽極及び陰極に用いる電極材料について説明する。

【0096】

陽極として用いる電極材料としては、仕事関数の大きい（仕事関数4.0eV以上）金属、合金、電気伝導性化合物、及びこれらの混合物などを用いることが好ましい。具体的な材料としては、ITO、ZnO、IZO、ITSO、金、白金、ニッケル、タンゲステン、クロム、モリブデン、鉄、コバルト、銅、パラジウム、又は金属材料の窒化物（例えば、窒化チタン等）を用いることができる。 20

【0097】

また、陰極として用いる電極材料としては、仕事関数の小さい（仕事関数3.8eV以下）金属、合金、電気伝導性化合物、及びこれらの混合物などを用いることが好ましい。具体的な材料としては、元素周期律の1族又は2族に属する元素、すなわちリチウムやセシウム等のアルカリ金属、及びマグネシウム、カルシウム、ストロンチウム等、及びこれらを含む合金（Mg:Ag、Al:Li）や化合物（LiF、CsF、CaF<sub>2</sub>）の他、希土類金属を含む遷移金属を用いて形成することができる。

【0098】

このような第1の電極又は第2の電極を、透光性又は非透光性とすることにより、電界発光層からの光の射出方向を選択することができる。例えば、第1の電極及び第2の電極を、透光性を有する材料で形成する場合、電界発光層からの光が基板側30及び封止基板側へ射出する両面発光型の表示を行うことができる。 30

【0099】

電界発光層からの光を基板30へ射出する場合、第1の電極を透光性とし、第2の電極を非透光性とすればよい。その結果、下面発光型の表示装置を提供することができる。また電界発光層からの光を封止基板側へ射出する場合、第1の電極と非透光性とし、第2の電極を透光性とすればよい。その結果、上面発光型の表示装置を提供することができる。このような光の出射方向とならない側に設けられた非透光性の電極には、反射性の高い導電膜を用いることにより光を有効利用することができる。 40

【0100】

本実施の形態では、第1の層間絶縁膜34に有色性有機材料を使用するため、第1の電極に非透光性材料を用い、第2の電極に透光性材料を用いることにより、上面発光型とする。また層間絶縁膜に有色性有機材料を用いず、第1の電極にITO等の透光性材料を用いることにより、下面発光型とすることができる。

【0101】

また、本実施の形態において第1の電極及び第2の電極のうち、透光性とする必要がある場合、金属、又はこれら金属を含む合金を非常に薄く形成し、ITO、IZO、ITSO又はその他の透明導電膜（合金を含む）との積層により形成することができる。 50

## 【0102】

以上のようにして画素部を形成することができる。

## 【0103】

また信号線と、走査線との間に生じるクロストークを防止するため、層間絶縁膜を積層すると好ましい。このとき、クロストークが生じないような膜厚を確保するため、層間絶縁膜の一部には有機材料を用いるとよい。また層間絶縁膜に無機材料を用いる場合、低誘電率材料（low-k材料）を使用すると好ましい。

## 【0104】

また層間絶縁膜を積層した場合であって、発光素子からの光を下方へ出射するとき、異種材料の界面での光の屈折を防止するとよい。例えば、第1の層間絶縁膜に開口部を形成し、当該開口部を埋めるように第2の層間絶縁膜を形成する。その結果、第1の層間絶縁膜及び第2の層間絶縁膜の界面での光の屈折を防止することができ、光の取り出し効率を高めることができる。10

## 【0105】

このような層間絶縁膜を積層する場合であって、層間絶縁膜に開口部を形成する構成例を以下に示す。

## 【0106】

図4（B）は、図4（A）と異なり層間絶縁膜を積層し、第1の層間絶縁膜に開口部を設けることを特徴とする。また当該開口部は、電界発光層が設けられる領域に形成することを特徴とする。また第1のスイッチ13として半導体膜上に複数のゲート電極が形成されたマルチゲート構造を有する薄膜トランジスタを用いることを特徴とする。その他の構成は図4（A）と同様であるため説明を省略する。その結果、第1の層間絶縁膜に有色性有機材料を用いる場合であっても、下面発光を行うことができる。また有色性有機材料を用いない場合であっても、第1の層間絶縁膜に開口部を設けることにより、層間絶縁膜等の界面での光の屈折を低減させることができる。また第1の電極及び第2の電極を透光性材料とすることにより、両面発光型とすることができる。もちろん、第1の電極を非透光性材料とし、第2の電極を透光性材料とすることにより上面発光を行うことができる。20

## 【0107】

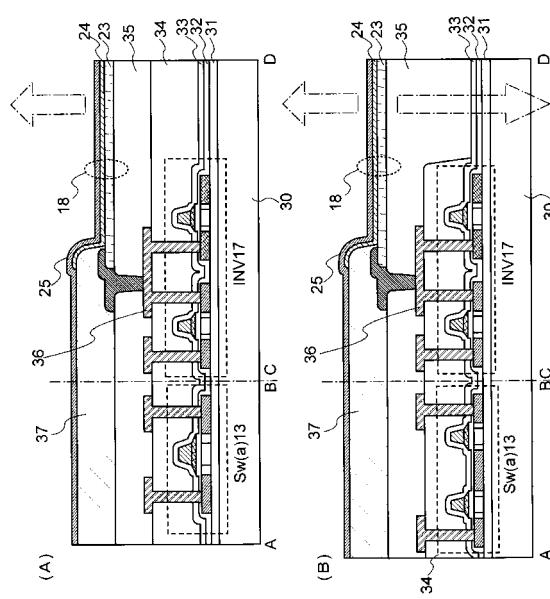

図5（A）は、図4（A）と異なり、画素電極23を形成した後、配線36を形成することを特徴とする。その他の構成は図4（A）と同様であるため説明を省略する。30

## 【0108】

図5（B）は、図5（A）と異なり第1の層間絶縁膜に開口部を設けることを特徴とする。また電界発光層が設けられる領域において、第1の層間絶縁膜に開口部を設けることを特徴とする。また第1のスイッチ13として半導体膜上に複数のゲート電極が形成されたマルチゲート構造を有する薄膜トランジスタを用いることを特徴とする。他の構成は図5（A）と同様であるため、図4（A）を参照することができる。その結果、第1の層間絶縁膜に有色性有機材料を用いる場合であっても、下面発光を行うことができる。また有色性有機材料を用いない場合であっても、第1の層間絶縁膜に開口部を設けることにより、層間絶縁膜等の界面での光の屈折を低減させることができる。またさらに第1の電極及び第2の電極を透光性材料とすることにより、図5（B）に示すように両面発光型とすることができる。もちろん、第1の電極を非透光性材料とし、第2の電極を透光性材料とすることにより上面発光を行うことができる。40

## 【0109】

図6（A）は、図4（A）と異なり、パッシベーション膜を積層構造とし、層間絶縁膜形成前に、配線36を形成し、層間絶縁膜34に開口部を形成し、配線36と接続する要に画素電極23を形成することを特徴とする。パッシベーション膜には、第1層目に酸化窒化珪素（SiNO）膜を用い、第2層目に窒化酸化珪素（SiON）膜を用いることができる。図6（A）に示す画素において、第1の層間絶縁膜34及び第2の層間絶縁膜35を積層した構造を用いてもよい。その他の構成は図4（A）と同様であるため説明を省略する。50

## 【0110】

図6(B)は、図6(A)と異なり第1の層間絶縁膜に開口部を設けることを特徴とする。また電界発光層が設けられる領域において、第1の層間絶縁膜に開口部を設けることを特徴とする。また第1のスイッチ13として半導体膜上に複数のゲート電極が形成されたマルチゲート構造を有する薄膜トランジスタを用いることを特徴とする。その他の構成は図6(A)と同様であるため、図4(A)を参照することができる。その結果、第1の層間絶縁膜に有色性有機材料を用いる場合であっても、下面発光を行うことができる。また有色性有機材料を用いない場合であっても、第1の層間絶縁膜に開口部を設けることにより、層間絶縁膜等の界面での光の屈折を低減させることができる。またさらに第1の電極及び第2の電極を透光性材料とすることにより、図6(B)に示すように両面発光型とすることができる。もちろん、第1の電極を非透光性材料とし、第2の電極を透光性材料とすることにより上面発光を行うことができる。

10

## 【0111】

図43には、図3におけるC-D、E-Fの断面図を示す。本発明の画素構成において、発光素子の電極として用いる画素電極23と、配線36とを画素毎に接続させる構造を適用してもよい。図43では直接、画素電極23と配線36とを接続しているが、画素電極23と同一層として形成される導電膜(代表的にはITO)を介して接続させても構わない。このように画素電極23と、配線36とを接続する場合、画素電極23と配線36とを同じ電位とすることにより、配線36を画素電極23の補助配線として用いることができる。補助配線により、画素電極23を薄く形成するために高抵抗となってしまう場合であっても、電圧降下を抑えることができる。

20

なお、補助配線を保持容量用の配線やインバータ用の電源線と共に用することもできる。その結果、配線数を増やすことなく、補助配線を設けることができる。このような構成によつて、製造歩留まりを向上させることができる。図43に示す補助配線の構成は、本発明の画素構成のいずれにも適用することができる。

## 【0112】

図7(A)は、図6(A)と異なり、配線36を2層にして設けることを特徴とする。すなわち、第1の層間絶縁膜34に開口部を設けて配線36aを形成し、次いで第2の層間絶縁膜35を形成し、当該第2の層間絶縁膜35に開口部を設けて配線36bを形成する。例えば配線36aとして、炭素及びニッケル(1~20wt%)を含むアルミニウム合金(A1(C+Ni))を用い、配線36bとしてTiと、AlとSiの合金と、Tiとの積層構造を用いることができる。その他の構成は図6(A)と同様であるため、図4(A)の説明を参照することができる。

30

## 【0113】

図7(B)は、図7(A)と異なり第1の層間絶縁膜に開口部を設けることを特徴とする。また電界発光層が設けられる領域において、第1の層間絶縁膜に開口部を設けることを特徴とする。また第1のスイッチ13として半導体膜上に複数のゲート電極が形成されたマルチゲート構造を有する薄膜トランジスタを用いることを特徴とする。その他の構成は図7(A)と同様であるため、図4(A)を参照することができる。その結果、第1の層間絶縁膜に有色性有機材料を用いる場合であっても、下面発光を行うことができる。また有色性有機材料を用いない場合であっても、第1の層間絶縁膜に開口部を設けることにより、層間絶縁膜等の界面での光の屈折を低減させることができる。またさらに第1の電極及び第2の電極を透光性材料とすることにより、図7(B)に示すように両面発光型とすることができる。もちろん、第1の電極を非透光性材料とし、第2の電極を透光性材料とすることにより上面発光を行うことができる。

40

## 【0114】

このように画素電極23を層間絶縁膜等の平坦面上に形成すると、均一に電圧を印加することができる。その結果、良好な画像表示を行うことができる。

## 【0115】

またこのように形成された表示装置には、コントラストの向上を図るために、偏光板、円

50

偏光板を設けてもよい。この場合、発光素子の光の出射側に、その発光波長帯を中心波長とし、当該波長領域を偏光するフィルム（偏光フィルム）を設けた構成とすると、コントラストの向上や、配線等による鏡面化（映り込み）の防止を図ることができる。

【0116】

また図41には、図6で示した画素部の一部、及び第1のゲートドライバ41、第2のゲートドライバ42の領域の断面図を示す。図6では図示しなかったが、第1又は第2の容量素子は、ゲート電極材料と、層間絶縁膜34等、配線36とにより形成することができる。第1及び第2のゲートドライバ領域には封止材408が設けられている。封止材により、対向基板406を張り合わせることができる。対向基板406を張り合わせるときに形成される空間には、窒素等の不活性ガス、樹脂材料を充填させたり、乾燥剤を設けるとよい。水分や酸素による発光素子15の劣化を防止することができる。

10

【0117】

また図41に示すように、封止材をゲートドライバ上に設けることにより、表示装置の狭額縁化を達成することができる。またソースドライバ上に封止材を設けてもよい。ただし、引き出し配線等が多く設けられているため、注意が必要である。

【0118】

このような封止構造は、図4、図5、図7で示したいずれの画素構成にも適用することができる。

【0119】

なお本実施の形態は、その他の実施の形態と自由に組み合わせることができる。

20

【0120】

（実施の形態5）

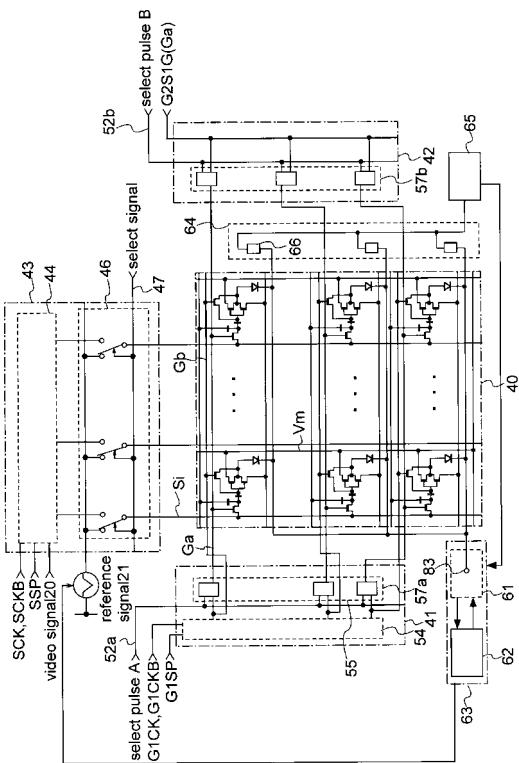

本実施の形態では、上記実施の形態で示した画素部を有する表示パネルの構造を説明する。

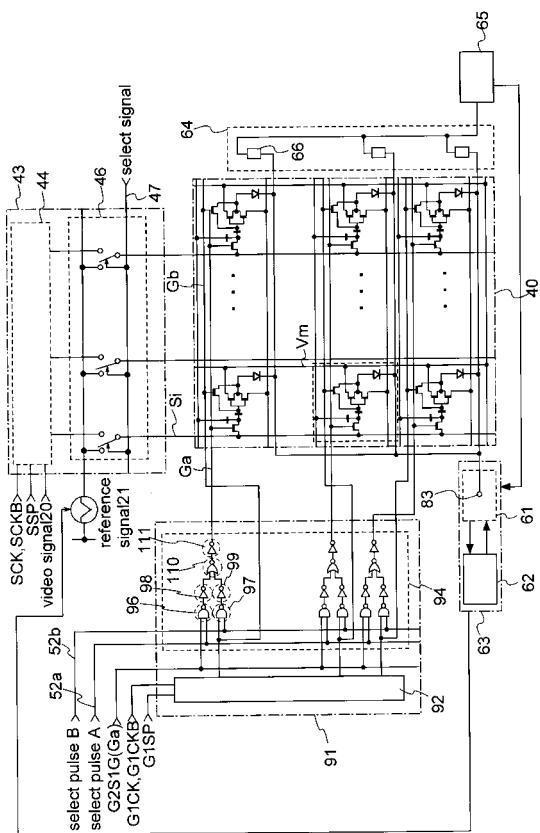

【0121】

図8に示すように、表示パネルは、上述した画素がマトリクス状に複数配置された画素領域40と、第1のゲートドライバ41と、第2のゲートドライバ42と、ソースドライバ43とを有する。第1のゲートドライバ41と第2のゲートドライバ42は、画素領域40を挟んで対向するように配置するか、画素領域40の上下左右の四方のうち一方に配置するとよい。

30

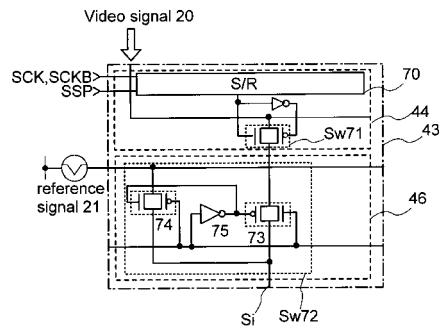

【0122】

ソースドライバ43は、パルス出力回路44、及び選択回路46を有する。選択回路46は、スイッチを有し、当該スイッチは配線（選択配線）47からの選択信号（select signal）により、制御される。そしてスイッチにより、ビデオ信号20又は基準信号21が信号線（Si）10へ入力される。

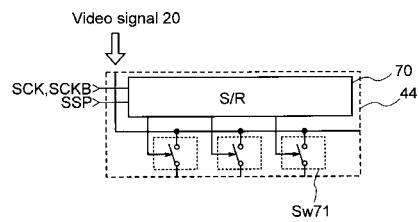

【0123】

以下に、ソースドライバの具体例を説明する。

【0124】

図9に示すように、パルス出力回路44は、シフトレジスタ（S/R）70を有し、当該シフトレジスタへスタートクロックパルス（SCK）、反転されたスタートクロックパルス（SCKB）が入力される。またパルス出力回路は第1のスイッチSw71を有し、上記スタートクロックパルスに基づきスイッチが選択されると、ビデオ信号20が出力される状態となる。なお第1のアナログスイッチ71は、薄膜トランジスタを有する。

40

【0125】

図10に示すように、選択回路46は、第2のスイッチSw72を有し、第2のスイッチ72は第1のアナログスイッチ73、第2のアナログスイッチ74、及びインバータ75を有する。第1及び第2のアナログスイッチ73、74、及びインバータ回路75は、極性の異なる薄膜トランジスタを有する。第1のアナログスイッチ73は、その入力側にパルス選択回路44が有する第1のスイッチ71に接続され、その出力側には、信号線（Si）10が接続される。第2のアナログスイッチ74は、その入力側に基準信号21が入

50

力され、その出力側には信号線 ( S i ) 1 0 が接続される。インバータ 7 5 は、第 1 のアナログスイッチ 7 3 と、第 2 のアナログスイッチ 7 4 が交互に選択されるように設ける。

【 0 1 2 6 】

このようなソースドライバ 4 3 により、第 1 のアナログスイッチ 7 3 が選択されるとき、ビデオ信号 2 0 が信号線 1 0 へ入力され、第 2 のアナログスイッチ 7 4 が選択されるとき、基準信号 2 1 が信号線 1 0 へ入力される。この第 1 のアナログスイッチ 7 3 が選択される期間が、ビデオ信号入力期間 T 2 であり、第 2 のアナログスイッチ 7 4 が選択される期間が、基準信号入力期間 T 1 である。

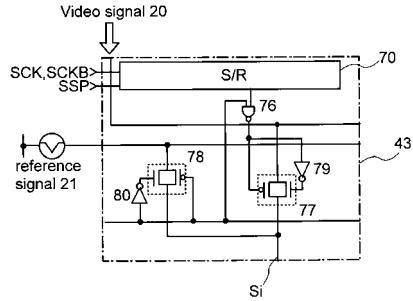

【 0 1 2 7 】

また図 1 1 に示すように、パルス出力回路 4 4 が有する機能と、選択回路 4 6 が有する機能とを共用することができる。図 1 1 に示すソースドライバ 4 3 は、シフトレジスタ 7 0 に接続された N A N D 7 6 を有する。また、第 1 のアナログスイッチ 7 7 と、当該第 1 のアナログスイッチ 7 7 が選択されるように設けられたインバータ 7 9 を有する。また基準信号 2 1 が入力される第 2 のアナログスイッチ 7 8 と、当該第 2 のアナログスイッチ 7 8 が選択されるように設けられたインバータ 8 0 を有する。第 1 及び第 2 のアナログスイッチ 7 7 、 7 8 はその出力側に信号線 1 0 が接続されている。なお N A N D 7 6 により、第 1 のアナログスイッチ 7 7 、及び第 2 のアナログスイッチ 7 8 のいずれかが選択される。この第 1 のアナログスイッチ 7 7 が選択される期間が、ビデオ信号入力期間 T 2 であり、第 2 のアナログスイッチ 7 8 が選択される期間が、基準信号入力期間 T 1 である。

【 0 1 2 8 】

なおソースドライバは、図 9 ~ 図 1 1 に示した構成に限定されるものではなく、ビデオ信号 2 0 と、基準信号 2 1 が交互に信号線 1 0 に入力されるような回路であればよい。

【 0 1 2 9 】

第 1 のゲートドライバ 4 1 はパルス出力回路 5 4 と選択回路 5 5 を有する。第 2 のゲートドライバ 4 2 は選択回路 5 7 を有する。選択回路 5 5 、 5 7 は、それぞれ第 1 の選択配線 5 2 a 、第 2 の選択配線 5 2 b が接続される。第 1 の選択配線 5 2 a から入力されるパルス信号 A ( s e l e c t p u l s e A ) と、第 2 の選択配線 5 2 b から入力されるパルス信号 B ( s e l e c t p u l s e B ) は反転した関係を有する。そしてパルス信号 A は、第 1 の選択回路 5 7 a からの信号に基づき、第 1 の走査線 G a へ入力される。またパルス信号 B は、第 2 の選択回路 5 7 b からの信号に基づき、第 1 の走査線 G a へ入力される。パルス信号 A 及びパルス信号 B により、図 2 ( C ) に示すような第 1 の走査線 G a へ入力されるパルス信号が作成される。当該パルス信号に基づき、第 1 のスイッチ 1 3 が選択される。

【 0 1 3 0 】

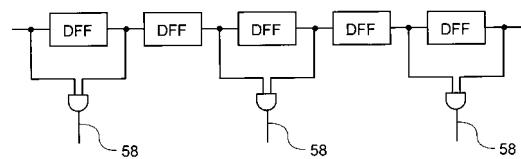

また第 2 の走査線 G b には、パルス出力回路 5 4 から、図 2 ( C ) に示すようなパルス信号が入力される。当該パルス信号を作成するため、パルス出力回路 5 4 は、図 3 3 に示すようなディレイ型フリップフロップ回路 ( D F F ) を有する。各 D F F からパルス信号が出力されるが、図 2 ( C ) に示すようなパルス信号を作成するため、出力配線 5 8 を一つおきに設けている。当該パルス信号に基づき、第 2 のスイッチ 1 4 が選択される。

【 0 1 3 1 】

第 1 の選択回路 5 7 a から、図 2 ( C ) に示したような、第 1 の走査線 ( G a ) 1 1 へ入力されるパルス信号 ( s e l e c t p u l s e A ) が入力される。このとき、画素が有する第 1 のスイッチ 1 3 に相当する薄膜トランジスタが選択され、信号線 1 0 からビデオ信号 2 0 が入力される。

【 0 1 3 2 】

第 1 のゲートドライバ 4 1 が有するパルス出力回路 5 4 は、複数のフリップフロップ回路からなるシフトレジスタやデコーダ回路を用いて形成してもよい。またソースドライバ 4 3 が含むパルス出力回路 4 4 を複数のフリップフロップ回路からなるシフトレジスタやデコーダ回路を用いて形成してもよい。パルス出力回路 4 4 、 5 4 、 5 6 として、デコーダ回路を適用すれば、ソース線 S x 又は走査線 G y をランダムに選択することができる。

10

20

30

40

50

## 【0133】

なおソースドライバ43の構成は上記の記載に制約されず、レベルシフタ、又はバッファ等のその他の回路を設けてもよい。また、第1のゲートドライバ41と第2のゲートドライバ42の構成も上記の記載に制約されず、レベルシフタ、又はバッファ等のその他の回路を設けてもよい。

## 【0134】

また、ソースドライバ43、第1のゲートドライバ41、第2のゲートドライバ42は、保護回路を有してもよい。保護回路は、抵抗素子、容量素子及び整流素子から選択された1個又は複数個であることを特徴とする。また、整流素子はゲート電極とドレイン電極が接続されたトランジスタ又はダイオードであることを特徴とする。このような保護回路により、静電気等の大電流による静電破壊を防止することができる。保護回路の詳細は、以下の実施の形態で説明する。

10

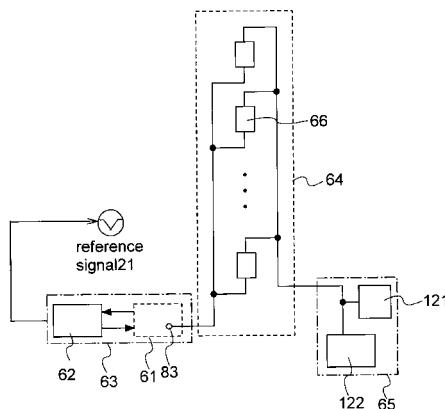

## 【0135】

また本発明の表示装置は、電源制御回路63を有することを特徴とする。電源制御回路63は、発光素子18に電源を供給する電源回路61とコントローラ62を有する。電源回路61は、電源83を有し、当該電源83は発光素子18の対向電極に接続する。

## 【0136】

発光素子18に順方向の電圧（順方向電圧）を印加して、発光素子18に電流を流して発光させるときは、電源83の電位は、発光素子18の画素電極の電位より低くなるように設定する。一方、交流駆動期間において、逆方向電圧を印加する場合、電源83の電位は、発光素子18の画素電極の電位より高くなるように設定する。このような電源83の設定は、コントローラ62から電源回路61に所定の信号を入力することによって行うことができる。

20

## 【0137】

電源制御回路63を用いて、発光素子18に逆方向電圧を印加することで、上述したように発光素子18の状態を改善し、信頼性を向上させることができるため好ましい。

## 【0138】

さらに表示パネルが、周囲の温度（以下環境温度と表記）に基づき動作するモニター回路64と制御回路65を有すると好ましい。モニター回路64は、モニター用発光素子66（以下発光素子66と表記）を有する。モニター用発光素子とは、画素に設けられた発光素子18と同様に形成されるが、画像表示に用いることは要しない。モニター用発光素子66により、環境温度によって、素子の変化情報を得ることができる。

30

## 【0139】

また定電流源等により、モニター用発光素子66へ電流が供給される。このとき画素に設けられた発光素子18と同様な電流が供給されると好ましい。このようにして、発光素子の劣化情報を得ることもできる。

## 【0140】

制御回路65は定電流源とバッファを有する。このような制御回路65は、モニター回路64の出力に基づき、電源電位を変更する信号を、電源制御回路63に供給する。電源制御回路63は、制御回路65から供給される信号に基づき、画素領域40に供給する電源電位を変更する。上記構成を有する本発明は、環境温度の変化に起因した電流値の変動を抑制して、信頼性を向上させることができる。

40

## 【0141】

このようにモニター回路64により、発光素子の状態に応じて駆動電圧を補正することができる。なおモニター回路64等の詳細な構成については、以下の実施の形態で説明する。

## 【0142】

また駆動電圧が限界値を超えるようになると、表示面にその旨を表示させてもよい。または表示面の輝度を徐々に低下させたり、表示面を点灯させてもよい。

## 【0143】

50

なお、本実施の形態における薄膜トランジスタは、薄膜トランジスタ以外のどのようなタイプのトランジスタでもよい。またこれらトランジスタは、どのような基板上に形成されてもよい。すなわち、図8で示したような回路が、全てガラス基板上に形成されてもよいし、プラスチック基板に形成されてもよいし、単結晶基板に形成されてもよいし、SOI基板上に形成されてもよい。または、図8における回路の一部が、ある基板に形成されており、図8における回路の別の一部が、別の基板に形成されてもよい。すなわち、図8に示したように、全ての回路が同じ基板上に形成される必要はない。例えば、図8において、画素領域40とゲートドライバ41とは、ガラス基板上にTFTを用いて形成し、ソースドライバ43（もしくはその一部）は、単結晶基板上に形成し、そのICチップをCOG(Chip On Glass)で接続してガラス基板上に配置してもよい。または、そのICチップをTAB(Tape Auto Bonding)やプリント基板を用いてガラス基板と接続してもよい。10

#### 【0144】

なお本実施の形態は、その他の実施の形態と自由に組み合わせることができる。

#### 【0145】

##### （実施の形態6）

本実施の形態では、上記実施の形態で示した画素部を有する表示パネルであって、第1及び第2のゲートドライバを共用する構造を、図12を用いて説明する。

#### 【0146】

ソースドライバ43は、パルス出力回路44、及び選択回路46を有し、図8と同様の構成である。20

#### 【0147】

ゲートドライバ91はパルス出力回路92及び選択回路94を有する。選択回路94は、各走査線に対応して、NAND96、97、インバータ98、99、111及びNOR110を有する。第1の選択配線52aはNANDゲート96の一方の端子に接続される。また、NAND96の他方の端子はパルス信号が入力される配線（G2S1G）に接続されている。第2の選択配線52bはNANDゲート97の一方の端子に接続される。また、NANDゲート97の他方の端子はパルス出力回路92に接続されている。NAND96の出力側はインバータ98の入力側に接続される。また、NAND97の出力側はインバータ99の入力側に接続されている。インバータ98及び99の出力側はNOR110の入力側に接続され、NOR110の出力側はインバータ111の入力側に接続されている。30

#### 【0148】

上記実施の形態と同様に、ソースドライバ43が含むパルス出力回路44、ゲートドライバ91が含む第1のパルス出力回路94及び第2のパルス出力回路92は、複数のフリップフロップ回路からなるシフトレジスタやデコーダ回路を用いることができる。パルス出力回路44、92、93として、デコーダ回路を適用すれば、ソース線Sx又は走査線Gyをランダムに選択することができる。

#### 【0149】

なおソースドライバ43の構成は上記の記載に制約されず、レベルシフタ、又はバッファ等のその他の回路を設けてもよい。また、ゲートドライバ91の構成も上記の記載に制約されず、レベルシフタ、又はバッファ等のその他の回路を設けてもよい。また、上記実施の形態と同様にソースドライバ43、ゲートドライバ91は、保護回路を有することを特徴とする。保護回路の詳細は、以下の実施の形態で説明する。40

#### 【0150】

このようにゲートドライバを共用することにより、画素領域40の占有面積を大きくすることができる。その結果、表示パネルの狭額縁化を図ることができる。

#### 【0151】

なお本実施の形態は、その他の実施の形態と自由に組み合わせることができる。

#### 【0152】

10

20

30

40

50

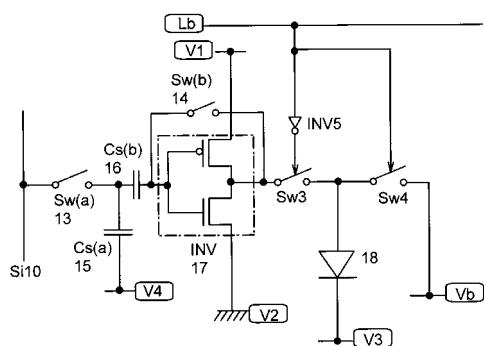

## (実施の形態 7)

本実施の形態では、逆方向電圧を印加する動作、及びそのための画素構成について説明する。

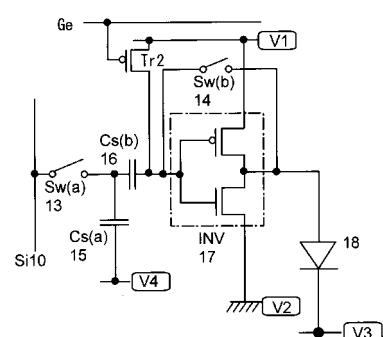

## 【0153】

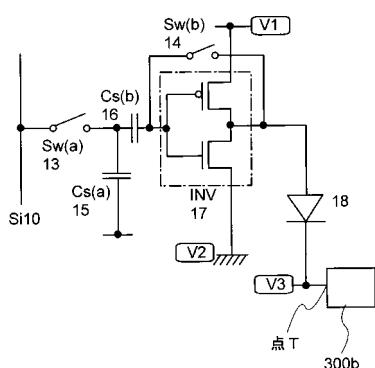

図18に示すように、インバータ17として、pチャネル型の薄膜トランジスタ、及びnチャネル型の薄膜トランジスタを設けた画素に基づき説明する。また図18において、インバータ17の一方の電圧をV1、インバータ17の他方の電圧をV2、発光素子18の対向電極の電位をV3、第1の容量素子15の低電位をV4と表記する。

## 【0154】

図18に示した画素構成において、交流駆動期間に、逆方向電圧を印加するには、発光素子18の対向電極と、画素電極との電位差を反転させるように設定すればよい。 10

## 【0155】

そのため、例えば図23に示すように、交流駆動期間において、対向電極の電位V3を画素電極の電位より高める。すなわち、発光素子18の対向電極の電位をふる場合について説明する。なお、図18に示す画素構成では、発光素子18の画素電極の電位が、対向電極の電位V3より高くなるとき点灯するようになっている。また発光素子18の対向電極の電位をふった結果、対向電極の電位V3が、インバータ17が有するV1の電位と等しい場合、交流駆動期間において、インバータ17が有するnチャネル型トランジスタがオンとなる。その結果、当該インバータ17に接続される発光素子に逆方向電圧が印加される。また対向電極の電位V3が、インバータ17が有するV1より大きい場合、交流駆動期間において、全画素に逆方向電圧を印加することができる。 20

## 【0156】

なお交流駆動期間において、図23に示すように、対向電極の電位V3を高め、インバータ17の一方の電圧V1を低めても構わない。

## 【0157】

また逆方向電圧を印加する方法、回路の構成、又はタイミングは、図23又は図18に限定されない。例えば対向電極の電位を固定した別の構成がある。この場合の画素構成や動作を以下に説明する。

## 【0158】

図18に示す画素に対して、図19に示すように1フレーム期間において、ビデオ信号20より、基準信号21の電位が小さいとき、階調表示期間、つまり階調表示期間となる。一方、ビデオ信号20より、基準信号21の電位が大きいとき、非階調表示期間となる。このとき、逆方向電圧を印加し、交流駆動期間とする。 30

## 【0159】

但し、上述したように、発光素子18の対向電極の電位V3を固定し、インバータ17のV2より大きくする。その結果、発光素子18へ逆方向電圧を印加することができる。すなわち、上記電位を満たすことにより、非点灯の時、常時発光素子18へ逆方向電圧を印加することができる。

## 【0160】

また、消去期間T<sub>e</sub>を設け、当該消去期間に逆方向電圧を印加する場合について説明する。この場合、図1とは異なる画素構成によって、達成することができる。例えば、図20に示すように、図1に示す画素構成において、トランジスタTr2を追加した画素構成を用いる。トランジスタTr2は、第2の容量素子16の電荷を放電するように設けられており、トランジスタTr2がオンとなると発光素子18が非点灯となる。また本実施の形態では、トランジスタTr2は、pチャネル型の薄膜トランジスタで形成する場合を示したため、図21に示すように、消去用走査線GeにLowが入力されるとトランジスタTr2はオンとなる。そして、トランジスタTr2は、消去用走査線Geにより制御される。この発光素子18が非点灯となる期間を消去期間と呼ぶ。 40

なお1フレーム期間中、発光素子18の対向電極の電位はV3に固定し、インバータ17のV2より大きくなるように設定する。その結果、消去期間において、発光素子18へ逆

方向電圧を印加することができる。つまり、消去用走査線を順に選択し、トランジスタTr2がオンとなるとき、画素へ逆方向電圧を印加することができる。また図20に示す画素では、トランジスタTr2がオンとなるときに加え、ビデオ信号によって発光素子18が非点灯となるときにも逆方向電圧を印加することができる。

【0161】

このような画素構成におけるタイミングチャートは、図22(B)(C)と同様なものとなるため、説明は省略する。

【0162】

このように、発光素子18を非点灯とすることにより、残像防止の効果を奏することもできる。

10

【0163】

また、図22(A)に示すように、1ゲート選択期間において、基準信号入力期間T1と、ビデオ信号入力期間T2に加えて、消去信号入力期間T3を設け、この消去信号入力期間に逆方向電圧を印加することができる。

【0164】

消去信号入力期間T3では、信号線10から消去用のビデオ信号が入力され、非点灯となる。一方、発光素子18の対向電極の電位はV3に固定し、インバータ17のV2より大きくなっている。その結果、発光素子18へ逆方向電圧を印加することができる。この場合、画素へ順に逆方向電圧を印加することができる。

20

【0165】

この場合のタイミングチャートは、図22(B)に示すように、1フレーム期間において、書き込み期間Taが終了後、消去期間Teが開始するものとなる。例えばk行目の画素に着目すると、図22(C)に示すように、1フレーム期間において、階調表示期間と、消去期間つまり交流駆動期間とが現れることになる。

【0166】

また上記と異なる画素構成により、逆方向電圧を印加することができる。その例を、図24を用いて説明する。

【0167】

図24には、図18に示す画素構成に、第3のスイッチSw3と、第4のスイッチSw4を設けた画素構成を示す。また、第4のスイッチSw4において発光素子と接続されていない一端(単に第4のスイッチの一端という)の電圧をVbと表記する。第3のスイッチSw3及び第4のスイッチSw4は、走査線Gbにより制御される。また第3のスイッチSw3及び第4のスイッチSw4は、インバータINV5を介して接続されているため、反転動作をする。

30

【0168】

このような画素構成において、発光素子18の対向電極の電位V3は、第4のスイッチの一端の電位Vbよりも大きくなるように設定する。このような構成において、第4のスイッチSw4が選択されると、発光素子18へ逆方向電圧が印加される。なお第4のスイッチの一端の電位Lbは、各行ずつ変化させてもよいし、全行同時に変化させてもよい。またさらに、発光素子18の対向電極の電位V3は、第4のスイッチSw4が選択されるときのみ、第4のスイッチの一端の電位Vbよりも大きくなるように制御してもよい。同様に、第4のスイッチSw4が選択されるときのみ、第4のスイッチの一端の電位VbVbが対向電極の電位V3より低くなるように設定してもよい。さらに上記電圧を満たすように、第4のスイッチの一端の電位Vbと、発光素子18の対向電極の電位V3とを固定してもよい。

40

【0169】

本実施の形態で示したような画素構成に対して逆方向電圧を印加することにより、上述したように初期不良等による影響を低減することができ好ましい。

【0170】

また本実施の形態では、発光素子18に逆方向電圧を印加する場合について説明したが、

50

同様にモニター用の発光素子66に逆方向電圧を印加することができる。その結果、発光素子66の初期劣化等を低減できる。また、発光素子18へ逆方向電圧を印加すると同時に、発光素子66へ逆方向電圧を印加すると好ましい。発光素子66の状態と、発光素子18の状態が同程度となるため、発光素子66に基づき補正される電圧の精度を高めることができるからである。

【0171】

なお本実施の形態は、その他の実施の形態と自由に組み合わせることができる。

【0172】

(実施の形態8)

本実施の形態では温度補償機能について説明する。

10

【0173】

本実施の形態において、温度補償機能を有する素子は、図15に示すような周囲の温度に基づき動作するモニター回路64を有し、モニター回路64はモニター用発光素子66を有する。発光素子66の一方の電極は一定の電位の保たれた電源に接続し(図示する構成では接地している)、他方の電極は制御回路65に接続する。制御回路65は、定電流源121とアンプ122を有する。電源制御回路63は、上述したように電源回路61とコントローラ62とを有する。なお、電源回路61は、供給する電源電位を変えることができる可変電源であることが好ましい。このようなモニター回路64、制御回路65及び電源制御回路63により温度補償が実行される。

【0174】

20

次に、発光素子66が環境温度を検出する仕組みについて説明する。発光素子66の両電極間には、定電流源121から一定の電流が供給される。すなわち、発光素子6には常に一定の電流が供給される。このような発光素子66は、環境温度が変化すると、発光素子66自体の抵抗値が変化する。発光素子66の抵抗値が変化すると、当該発光素子66の電流値は常に一定であることから、発光素子66の両電極間の電位差が変化する。この温度変化による発光素子66の電位差の変化を検出することで、環境温度の変化を検出する。このとき、発光素子66の一定の電位に保たれている側の電極の電位は変わらないので、定電流源121に接続する側の電極の電位の変化を検出する。このような発光素子の電位の変化の情報を含む信号は、アンプ122に供給され、当該アンプ122で増幅された後、電源制御回路63に出力される。電源制御回路63は、アンプ122を介して、モニター回路64の出力に基づき、基準信号21を変える。具体的には、基準信号21の電位を制御する。その結果、温度変化に合わせて、発光素子18の輝度を補正することができる。

30

【0175】

なお図15では、発光素子66を複数有するが、これに制約されない。すなわちモニター回路64に設ける発光素子66の個数は制約されない。例えば、各RGB用のモニター用発光素子を設けてもよい。各RGBによって、温度特性が異なるからである。この場合、上記のように画素電極の電位を制御するとよい。

【0176】

40

また、発光素子66にトランジスタを直列に接続した構成をモニター用素子として適用してもよい。その場合、例えば常時、当該トランジスタをオンとなるようにする。そして、当該トランジスタをリミッターとして使用することができる。当該トランジスタは、画素が有するトランジスタと同様に作製することができる。なおリミッターとして使用する場合は、当該トランジスタのチャネル幅やチャネル長を大きくすると好ましい。

【0177】

以上、基準信号を補正する場合について説明したが、発光素子18の画素電極の電位や、対向電極の電位を制御してもよい。

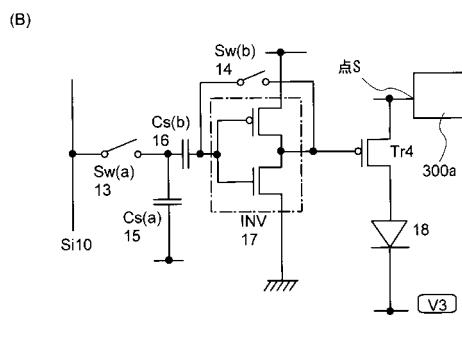

【0178】

図25(A)(B)を用いて、画素電極の電位を制御する場合について説明する。図25(A)に示す画素構成では、画素電極に、インバータ17を介して補償回路300aが設

50

けられている。この補償回路 300a により、発光素子 18 の画素電極の電位を制御することができる。

【0179】

また図 25 (B) に示す画素構成では、画素電極に、トランジスタ Tr 4 を介して補償回路 300a が設けられている。この補償回路 300a により、発光素子 18 の画素電極の電位を制御することができる。

【0180】

このように、画素電極の電位を制御する場合、当該画素電極は、各画素に設けられているため、各 RGB による温度変化の差異を考慮することができ、好ましい。

【0181】

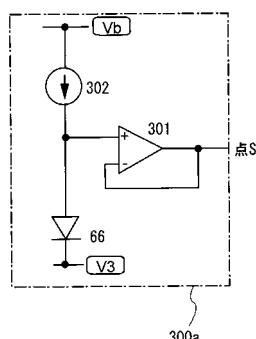

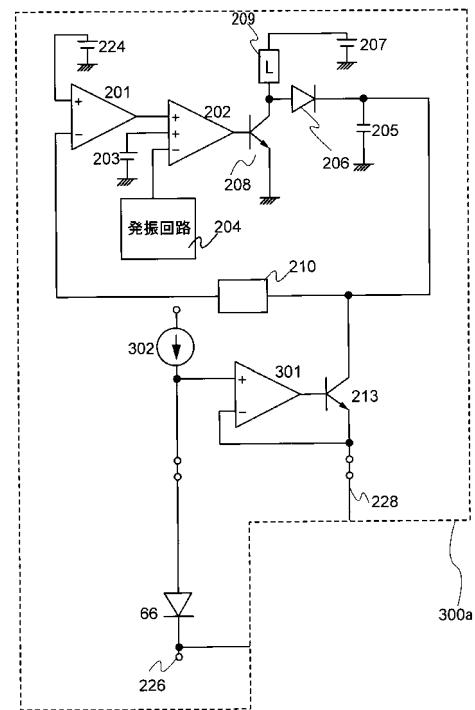

図 26 には、補償回路 300a の具体的な構成を示す。補償回路 300a は、発光素子 66 を有し、当該発光素子 66 の画素電極に接続されたアンプ 301、及び定電流源 302 を有する。オペアンプのマイナス側は、当該オペアンプの出力側に接続されている。またオペアンプのプラス側は、定電流源 302 に接続されている。

【0182】

このような補償回路により、温度変化による発光素子 66 の電位差の変化を検出することができる。より詳しくは、発光素子 66 の一定の電位に保たれている側の電極の電位は変わらないので、定電流源 302 に接続する側の電極の電位の変化を検出する。このような発光素子の画素電位の変化の情報を含む信号は、アンプ 301 に供給され、当該アンプ 301 で増幅される。増幅された信号が、発光素子 18 の画素電極に入力され、温度変化に応じた電位となるように制御される。

【0183】

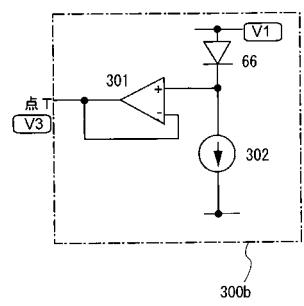

図 27 を用いて、対向電極の電位を制御する場合について説明する。図 27 に示す画素構成では、対向電極に、補償回路 300b が設けられている。この補償回路 300b により、発光素子 18 の対向電極の電位を制御することができる。

【0184】

図 28 には、補償回路 300b の具体的な構成を示す。補償回路 300b は、発光素子 66 を有し、当該発光素子 66 の画素電極に接続された定電流源 302 を有し、画素電極が接続されていない定電流源 302 の一端にアンプ 301 が接続されている。オペアンプのマイナス側は、当該オペアンプの出力側に接続されている。またオペアンプのプラス側は、定電流源 302 に接続されている。

【0185】

このような補償回路により、温度変化による発光素子 66 の電位差の変化を検出することができる。より詳しくは、発光素子 66 の一定の電位に保たれている側の電極の電位は変わらないので、定電流源 302 に接続する側の電極の電位の変化を検出する。このような発光素子の対向電位の変化の情報を含む信号は、アンプ 301 に供給され、当該アンプ 301 で増幅される。増幅された信号が、発光素子 18 の対向電極に入力され、温度変化に応じた電位となるように制御される。

【0186】

以上のように、温度変化に応じて、発光素子 18 の画素電極又は対向電極の電位を制御することができる。その結果、温度変化によらず所定の輝度で発光することができる。

【0187】

また補償回路 300a のより詳細な例を図 29 ~ 図 32 に示す。図 29 に示す画素部は、図 1 等で示すように少なくともインバータ 17、及び発光素子 18 を有している。またモニター用の発光素子 66 は、電源線 226 を介して発光素子 18 の対向電極に接続される。

【0188】

発光素子 18 が温度に対して電流・電圧特性が変化してしまうと、一定の電圧を印加した場合であっても、高温で高輝度となり、低温で低輝度となる。これを補正するため、定電流を定電流源 302 より発光素子 66 に流し、そこで発生する電圧をアンプ 301、トランジ

10

20

30

40

50

ンジスタ 213 を介して、電源線 228 に印加している。当該電源線 228 は、インバータ 17 を介して、発光素子 18 の画素電極に接続されている。このような補償回路を用いる場合、発光素子 66 と発光素子 18 が同一材料で形成されていれば、温度特性はキャンセルされ、温度に対して輝度を一定に保つことが可能となる。

【0189】

アンプ 301 以外に、スイッチングレギュレータを有し、スイッチングレギュレータは、第1のコンパレータ 201、第2のコンパレータ 202、発振回路 204、平滑容量 205、ダイオード 206、スイッチトランジスタ 208、インダクタ 209、基準電源 203、207、224、アッテネータ 210 を有する。基準電源 207 は電流容量の大きな電源、たとえばバッテリーなどを用いる。

10

【0190】

スイッチングレギュレータの構成は上記には限定されず他の構成を用いても良い。また、図 29 ではスイッチトランジスタを NPN 型バイポーラトランジスタとしているがこれには限定されない。

【0191】

発振回路 204 の出力信号と基準電圧 203、第1のコンパレータ 201 の出力信号を第2のコンパレータ 202 で比較し、第2のコンパレータ 202 の出力信号でスイッチングトランジスタ 208 を制御する。スイッチトランジスタ 208 がオンとなるとインダクタ 209 に電流がながれ、磁界エネルギーがインダクタ 209 に保持される。トランジスタ 208 がオフとなると、磁界エネルギーは電圧に変わり、ダイオード 206 を介して平滑容量 205 を充電する。スイッチングトランジスタ 208 のオンオフデューティ比によって、平滑容量 205 に発生する直流電圧は変化する。

20

【0192】

平滑容量 205 の直流電圧はアッテネータ 210 でアッテネートされ、第1のコンパレータ 201 に入力される。第1のコンパレータ 201 は基準電圧 224 とアッテネータ 210 の電圧を比較し、その出力を第2のコンパレータ 202 に入力する。このようにして帰還がかかり、必要な電圧を平滑容量 205 に発生させることができる。図 29 に示す構成では定電流源 302、アンプ 301、発光素子 66 を直接接続しているが間に抵抗やスイッチなど他の素子を介して接続しても良い。

30

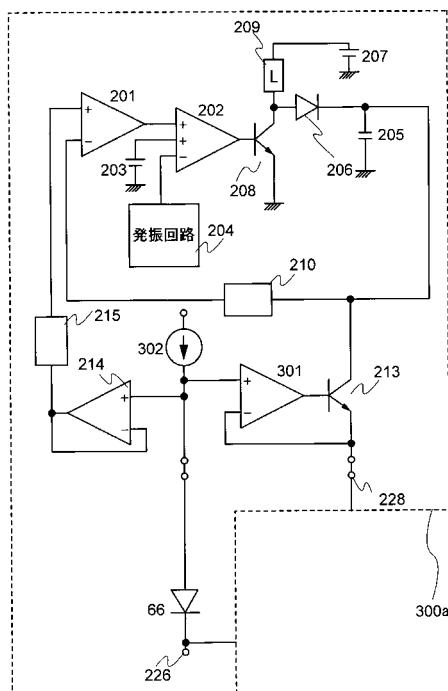

【0193】

図 29 とは異なる補償回路の構成について、図 30 を用いて説明する。図 29 に示す構成では平滑容量 205 の電圧が温度に依存せず一定の値をとるが、発光素子は温度特性をもつている。一般に発光素子の電圧は低温で大きく、高温で小さくなる。高温においては発光素子電圧と平滑容量電圧の差が大きくなりこの分は無駄な電力を消費することになる。その場合、高温でスイッチングレギュレータ電圧が発光素子電圧に連動して低下すれば無駄な電力を削減できる。

【0194】

図 30 はこのような問題を解決するために考えられた補償回路の構成であって、発光素子 66 の電圧をスイッチングレギュレータにも入力し、スイッチングレギュレータ電圧と、発光素子 18 の駆動電圧とを連動させる。

40

【0195】

具体的な補償回路の構成は、図 29 に示す補償回路に加え、アンプ 214、アッテネータ 215 を有する。発光素子 18 の駆動電圧はアンプ 214、アッテネータ 215 を介して第1のコンパレータ 201 に入力される。平滑容量 205 の直流電圧はアッテネータ 210 でアッテネートされ、第1のコンパレータ 201 に入力される。第1のコンパレータ 201 はアッテネータ 215 とアッテネータ 210 の電圧を比較し、その出力を第2のコンパレータ 202 に入力する。このようにして帰還がかかり、必要な電圧を平滑容量 205 に発生させることができる。図 30 に示す構成では定電流源 302、アンプ 301、214、発光素子 66 を直接接続しているが間に抵抗やスイッチなど他の素子を介して接続してもよい。

50

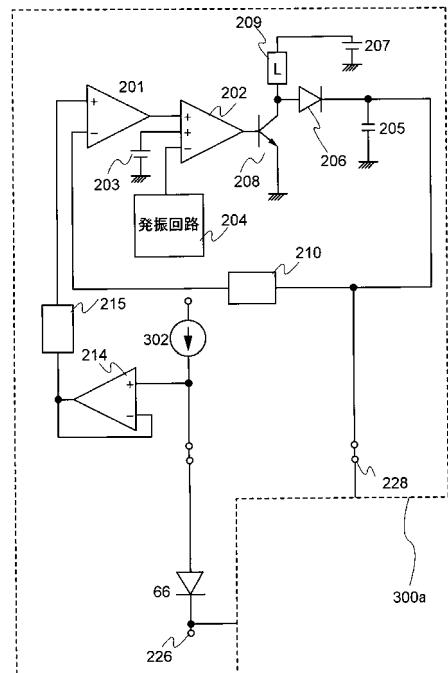

## 【0196】

またさらに、上記補償回路と異なる構成について図31を用いて説明する。図31に示す構成はスイッチングレギュレータの出力を直接表示パネルの第2の電源端子に接続したことを特徴とする。発光素子66の駆動電圧をスイッチングレギュレータにも入力し、スイッチングレギュレータ電圧と、発光素子18の駆動電圧とを連動させる。

## 【0197】

具体的な補償回路の構成は、図30に示す補償回路から、アンプ301、トランジスタ213を削除し、スイッチングレギュレータの出力が直接電源線228に接続される。図30に示した補償回路に比べて、安定度は落ちるがアンプとトランジスタを削減できるという長所がある。図31に示す構成では定電流源302、アンプ214、モニター素子66を直接接続しているが間に抵抗やスイッチなど他の素子を介して接続してもよい。

10

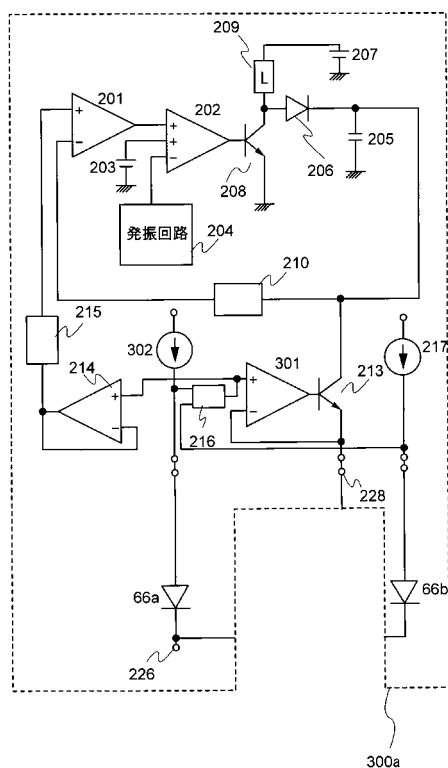

## 【0198】

またさらに、上記補償回路と異なり、発光素子66を複数設けた場合の構成について図32を用いて説明する。図32に示す構成は、複数の発光素子66a、66bの電圧をスイッチングレギュレータにも入力し、スイッチングレギュレータ電圧と、発光素子18の駆動電圧とを連動させる。またモニター素子を2個(66a、66b)画素部の両側に設け、加算回路216で平均化したのちアンプ214、301に接続すれば、より正確なモニターが可能になる。さらに、本発明では発光素子66の数を更に増やすことも可能である。発光素子66の数を増やすことにより、発光素子66と発光素子18の特性差を少なくすることができる。

20

## 【0199】

モニター素子66a、66bの電圧は加算回路216、アンプ214、アッテネータ215を介して第1のコンパレータ201に入力される。平滑容量205の直流電圧はアッテネータ210でアッテネートされ、第1のコンパレータ201に入力される。第1のコンパレータ201はアッテネータ215とアッテネータ210の電圧を比較し、その出力を第2のコンパレータ202に入力する。このようにして帰還がかかり、必要な電圧を平滑容量205に発生させることができる。ここでは定電流源302、217、アンプ301、発光素子66a、66bを直接接続しているが、それらの間に抵抗やスイッチなど他の素子を介して接続してもよい。

## 【0200】

30

図29～図32に示す構成において、表示パネルの第1の電源線226、第2の電源線228は固定電圧としているが、第1の電源線226、第2の電源線228それぞれに加わる電圧を、切換スイッチなどを挟むことにより定期的に入れ替え、発光素子18や発光素子66を交流駆動しても構わない。また、図29～図32を用いて温度補償について述べたが、発光素子66と発光素子18とが同様に劣化することを利用して、発光素子18の劣化に対しても補償を行っても構わない。

## 【0201】

本実施の形態において、モニター回路64として、発光素子66を用いる場合を説明したが、これに制約されず、公知の温度センサを用いてもよい。公知の温度センサを用いる場合は、画素領域40と同じ基板上に設けてもよいし、ICを用いて外付けにしてもよい。

40

## 【0202】

なお温度補償機能は、ユーザによる操作を必要としないため、ユーザに表示装置が渡った後も、継続して補正することができる。そのため、製品として、長寿命化を図ることができる。

## 【0203】

なお本実施の形態は、その他の実施の形態と自由に組み合わせができる。

## 【0204】

(実施の形態9)

本実施の形態では、モニター用発光素子66から得られる劣化情報について説明する。

## 【0205】

50

発光素子に電圧を印加して点灯させる駆動方法（電圧駆動）では、発光素子に電流を加えて点灯させる駆動方法（電流駆動）と比較すると、輝度劣化の進行が早くなる場合がある。これは電圧駆動の場合、発光素子材料の劣化に加え、陰極と陽極間の抵抗が上昇することによると考えられる。そのため、電圧駆動を用いる場合、モニター用発光素子から得られる劣化情報に、このような劣化を考慮するとよい。

#### 【0206】

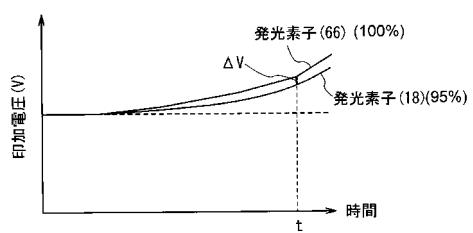

またモニター用発光素子66は、定電流源が接続されており、常時点灯する。すなわち、モニター用発光素子66の点灯のデューティ比は100%となる。一方、画素に設けられた発光素子18は、100%より低くなる。これは、黒表示を行う場合、発光素子18は非点灯となっているからである。また階調表示に応じて、印加する電圧がふれているからである。そのため、図42に示すように、ある時間tでは、モニター用発光素子66から得られる電圧と、発光素子18へ印加すべき電圧とに差（V）が生じてしまう。その結果、発光素子18において、所定の輝度が得られなくなることがある。そのため、電圧駆動を用いる場合、モニター用発光素子から得られる劣化情報に、このような情報を考慮するとよい。

10

#### 【0207】

また以下に、理論式を用いて、説明する。

#### 【0208】

まず、初期輝度 $L_0$ 、電流密度 $J_0$ で電流駆動を行った時、電流効率（t）は時間と共に低下していくが、この電流効率（t）は、以下ののような時間tの関数で表される。

20

$$(t) = L_0 / J_0 \times f(t) \quad \dots (1)$$

ここで、f(t)は、以下ののような指数関数で表せることが知られている。

$$f(t) = \exp\{- (t / \tau)\} \quad \dots (2)$$

なお、 $\tau$ は中期的、又は長期的な劣化を表すパラメータであり、 $\tau_0$ は初期劣化を表すパラメータであり、これらは実験的に求めることができる。

#### 【0209】

一方、電流密度Jが時間tによって変化する（すなわち $J = J(t)$ ）場合、輝度Lは以下の式で表すことができる。

$$L = (t) \times J(t) \quad \dots (3)$$

したがって、電圧駆動を行う場合、式(3)で $L = L_0$ （=一定）とすることにより、下記式(4)が成り立たなければならない。

30

$$L_0 = (t) \times J(t) \quad \dots (4)$$

#### 【0210】

式(4)を式(1)に代入することにより、以下の式を導くことができる。

$$J(t) = J_0 / f(t) \quad \dots (5)$$

式(5)は現象的には、「輝度を一定に保つためには、電流効率が低下していくことを考慮し、徐々に電流密度を $J_0$ よりも上げていかなければならない」ことを表している。なぜならば、式(2)より、f(t)は単調減少の関数だからである。

#### 【0211】

ところで、一般に、電流密度は電圧のべき乗（ $\times$ 乗）に比例するため、

40

$$J(t) = C \times V^x(t) \quad \dots (6)$$

である。 $\times$ は素子で決まるべき乗であり、Cは定数である。

したがって、式(6)を式(5)に代入し、式(2)を考慮すると、以下の式が成り立つ。

$$V(t) = \text{Const.} \times [\exp(t/\tau)]^{1/x} \quad \dots (7)$$

この式(7)が、「電圧駆動するためには電圧がどのように変化すればよいか」を表す式である。Const.は初期の電流密度 $J_0$ およびxによって決まる定数（Const. =  $(J_0 / C)^{1/x}$ ）である。

#### 【0212】

モニター用発光素子66の情報に上記電圧上昇を考慮して、発光素子18の駆動電圧を補

50

正するとよい。

【0213】

これらを踏まえ、発光素子の材料劣化の情報を蓄積し、メモリ等に保存しておくとよい。さらに発光素子の点灯のデューティ比に応じた劣化情報を蓄積し、メモリ等に保存しておくとよい。これら保存された劣化情報と、モニター用発光素子66からの劣化情報に基づき、発光素子18へ印加する電圧を補正する。その結果、温度変化に合わせて、発光素子18の輝度を補正することができる。

【0214】

さらに、RGBごとの発光素子の材料劣化の情報を蓄積するとよい。またRGBごとの発光素子の点灯のデューティ比に応じた劣化情報を蓄積するとよい。この場合、モニター用発光素子66をRGBごとに設けておく。

10

【0215】

本実施の形態のように、発光素子の材料劣化、点灯デューティ比を考慮することにより、モニター用発光素子66から得られる劣化情報を修正するとよい。その結果、発光素子18へ印加する、補正された電圧の精度を高めることができる。

【0216】

(実施の形態10)

本実施の形態では、保護回路について説明する。

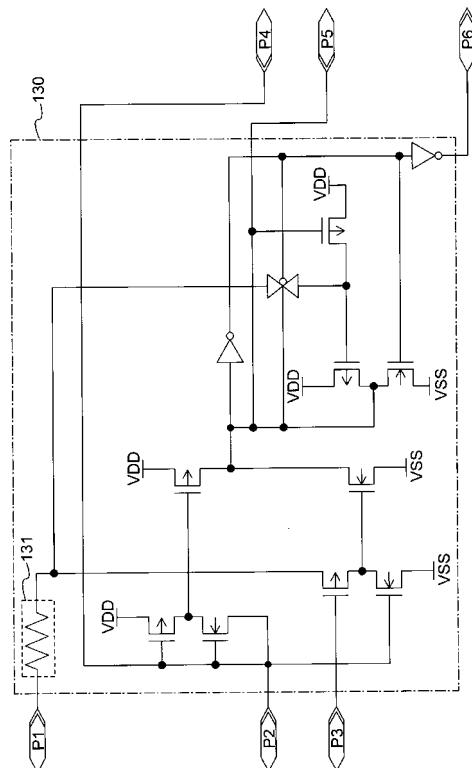

【0217】

ソースドライバが有するシフトレジスタ70は、単位回路130を有する。単位回路130は、図16に示すように、複数のトランジスタと論理回路を有する。単位回路130は、スタートクロックパルス(SCK)、又は反転されたスタートクロックパルス(SCKB)が入力される電源線に、保護回路として抵抗素子131が設けられている。また単位回路130内のいずれに保護回路を設けてもよい。またビデオ信号20が供給される電源線に、保護回路として抵抗素子を設けてもよい。また、選択回路46と信号線Siとの間に保護回路を設けてもよい。このように保護回路を設ける結果、静電気に起因した素子の劣化や破壊を抑制することができる。より具体的には、入力ノード側に入力されるクロック信号やデータ信号には雑音が含まれている場合があり、この雑音により、瞬間的に高い電圧又は低い電圧が素子に与えられることがある。しかしながら、保護回路を有する本発明は、素子の誤作動、素子の劣化や破壊を抑制することができる。

20

【0218】

このような保護回路は、抵抗素子、容量素子及び整流素子から選択された1個又は複数個を用いて形成することができる。

【0219】

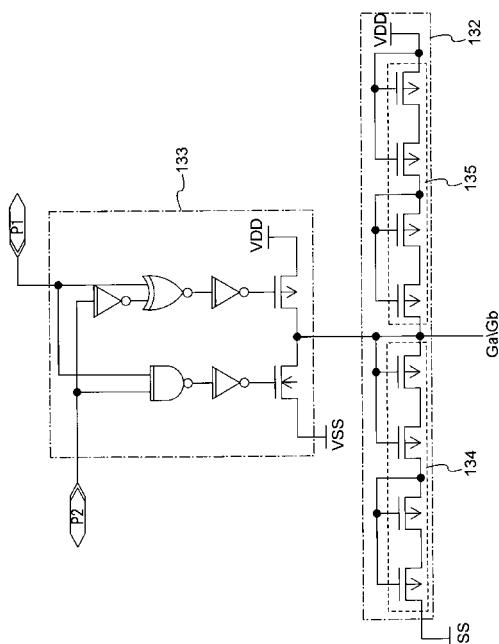

次に、ゲートドライバ41、42、91が有するパルス出力回路に設けられた保護回路について説明する。図17に示すように、当該パルス出力回路は、複数の単位回路(GSR)が継続接続した構成を有し、単位回路(GSR)は、トライステートバッファ133と、保護回路132を有する。トライステートバッファ133は、第1のゲートドライバ41及び第2のゲートドライバ42の一方が走査線Ga又はGbへ、信号を入力する際に、他方のドライバからの出力がそれを阻害しないようにするために設ける。従って、上記のような機能を有するものであれば、トライステートバッファだけでなく、アナログスイッチやクロックドインバータ等を用いてもよい。また保護回路132は、素子群134、135を有する。なお保護回路が有する素子群は、抵抗素子やトランジスタだけでなく、抵抗素子、容量素子及び整流素子から選択された1個又は複数個から構成される。整流素子とはゲート電極とドレイン電極が接続されたトランジスタ又はダイオードである。

30

【0220】

次に、ゲートドライバが有する保護回路88の動作について説明する。まず、雑音等の影響により、トライステートバッファ133の出力線から、VDDよりも高い電圧の信号が供給されたとする。そうすると、そのゲート・ソース間電圧の関係から、素子群134はオフ、素子群135はオンとなる。そうすると、トライステートバッファ133にチャ-

40

50

ジした電荷は、VDDを伝達する電源線に放電して、走査線Ga又はGbの電位は、VDD、又はVDD+の電位となる。一方、トライステートバッファ87の出力線から、VSSよりも低い電圧の信号が供給されたとする。そうすると、そのゲート・ソース間電圧の関係から、素子群134がオン、素子群135はオフとなる。そうすると、走査線Ga又はGbの電位は、VSS、又はVSS-の電位となる。このように、雑音等により、トライステートバッファ133の出力線から供給される電圧が、瞬間に、VDDよりも高くなったり、VSSよりも低くなったりしても、走査線Ga又はGbに与えられる電圧は、VDDよりも高くならず、またVSSよりも低くならない。従って、雑音や静電気等に起因した素子の誤作動、損傷、破壊を抑制することができる。

## 【0221】

10

また本実施の形態の保護回路は、FPC(flexible print circuit)等の接続フィルムと、ゲートドライバ41、42又はソースドライバ43との間に設けてもよい。

## 【0222】

なお本実施の形態は、その他の実施の形態と自由に組み合わせることができる。

## 【0223】

## (実施の形態11)

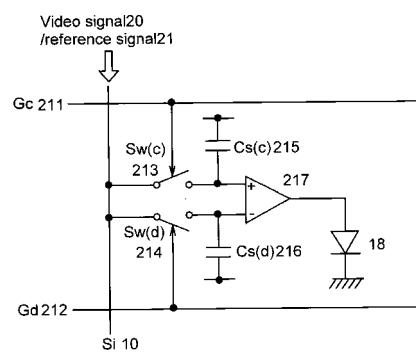

本実施の形態では、上記実施の形態とは異なる画素構成について説明する。

## 【0224】

20

図13に示す画素は、信号線(Si)10、第1の走査線(Gc)211、第2の走査線(Gb)212、第1のスイッチ(Sw(c))213、第2のスイッチ(Sw(d))214、第1の容量素子(Cs(c))215、第2の容量素子(Cs(d))216、差動增幅回路217、発光素子18を有する。第1のスイッチ213及び第2のスイッチ214は、例えば薄膜トランジスタを用いて作製することができる。差動增幅回路217は、例えばオペアンプを用いることができる。

## 【0225】

30

このような画素構成の接続関係等について説明する。第1のスイッチ213の一方は、信号線10に接続され、第1の走査線211によって制御される。第1のスイッチの他方には、第1の容量素子215の一方が接続される。第1の容量素子の他方は、任意の配線に接続されている。任意の配線は、固定電位を有すると好ましい。また第1の容量素子215は、信号線10から入力される電荷を保持する機能を有していればよい。具体的には、第1の容量素子215は、信号線10から入力される基準信号21を保持すればよい。以下に説明するが、本発明は1ゲート選択期間という非常に短い時間にビデオ信号20と、基準信号21との入力を行うため、第1の容量素子15は小さくてすむ。

## 【0226】

第2のスイッチ214の一方は、信号線10に接続され、第2の走査線212によって制御される。第1のスイッチの他方には、第2の容量素子216の一方が接続される。第2の容量素子の他方は、任意の配線に接続されている。任意の配線は、固定電位を有すると好ましい。また第2の容量素子216は、信号線10から入力される電荷を保持する機能を有していればよい。具体的には、第2の容量素子216は、信号線10から入力されるビデオ信号20を保持すればよい。

40

## 【0227】

差動增幅回路217の入力側において、高電位側は、第1のスイッチ214に接続され、低電位側は、第2のスイッチ215に接続される。

## 【0228】

発光素子18は、差動增幅回路217の出力側に接続される。なお発光素子18と、差動增幅回路217との間には、その他の素子、例えばスイッチ、スイッチとしてトランジスタ、又はインバータが設けられていても構わない。

## 【0229】

50

このような画素構成によって、1つの信号線からビデオ信号20、及び基準信号21を入力することができる。その結果、画素の開口率を高めることができる。

## 【0230】

次に、図13に示した画素構成を有する表示装置の動作について説明する。図13に示す画素構成の動作は、図2と同様に、1フレーム期間は階調表示期間と、交流駆動期間とが設けられている。しかし本発明は交流駆動期間を設けなくともよい。

## 【0231】

階調表示期間では、走査線が順に選択される書き込み期間が設けられている。書き込み期間では、信号線10からビデオ信号20が入力される。また書き込み期間において、信号線10から基準信号21が入力される。これらの信号は、図13に示した信号線10から入力される。どちらの信号が入力されるかは、第1のスイッチ213又は第2のスイッチ214により制御される。そしてビデオ信号の電圧と、基準信号21の電圧との大小関係に基づき、差動增幅回路217から信号が出力され、発光素子18へ電流が供給され、点灯する。差動增幅回路217からの信号により、発光素子の点灯時間が制御され、結果として階調表示を行うことができる。10

## 【0232】

なお本実施の形態において、差動增幅回路217が有する薄膜トランジスタ、特にpチャネル型の薄膜トランジスタを飽和領域で動作させる必要がないことを特徴とする。すなわち、薄膜トランジスタを線形領域で動作させることができるのであるため、駆動電圧を高くする必要がなく、消費電力を削減することができる。

## 【0233】

また交流駆動期間では、発光素子に対して逆方向の電圧（逆方向電圧）を印加する。例えば、発光素子の対向電極と、差動增幅回路217が有する低電位側電源（Vss）の電位を変えればよい。逆方向電圧を印加する結果、発光素子の状態を改善し、信頼性を向上させることができるので好ましい。20

## 【0234】

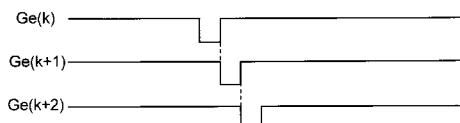

図14には、全行の第1の走査線Gcへ入力される波形、及びi行目～(i+2)行目における第2の走査線Gdへ入力される信号の波形を示す。本実施の形態において、1ゲート選択期間は、基準信号入力期間T1と、ビデオ信号入力期間T2が設けられている。

## 【0235】

i行目において、1ゲート選択期間にGc(i)にHighの信号が入力される。このとき、第1のスイッチ213が選択され、信号線10からビデオ信号20が入力され、第1の容量素子215へ電荷は保持される。また該1ゲート選択期間において、Gd(i)には、基準信号入力期間T1にLowの信号が入力され、ビデオ信号入力期間T2にHighの信号が入力される。Highの信号が入力されるとき、第2のスイッチ214が選択され、信号線10からビデオ信号20が入力され、第2の容量素子215へ電荷は保持される。30

## 【0236】

同様に(i+1)行目において、1ゲート選択期間にGc(i+1)にHighの信号が入力される。このとき、第1のスイッチ213が選択され、信号線10から基準信号21が入力され、第1の容量素子215へ電荷は保持される。また該1ゲート選択期間において、Gd(i+1)には、基準信号入力期間T1にLowの信号が入力され、ビデオ信号入力期間T2にHighの信号が入力される。Highの信号が入力されるとき、第2のスイッチ214が選択され、信号線10からビデオ信号20が入力され、第2の容量素子216へ電荷は保持される。40

## 【0237】

さらに同様に、(i+2)行目において、1ゲート選択期間にGc(i+2)にHighの信号が入力される。このとき、第1のスイッチ213が選択され、信号線10から基準信号21が入力され、第1の容量素子215へ電荷は保持される。また該1ゲート選択期間において、Gd(i+2)には、基準信号入力期間T1にLowの信号が入力され、ビデオ信号入力期間T2にHighの信号が入力される。Highの信号が入力されるとき、第2のスイッチ214が選択され、信号線10からビデオ信号20が入力され、第2の50

容量素子 216 へ電荷は保持される。

【0238】

以上のように、ビデオ信号の入力及び基準信号の入力が行われる。このビデオ信号の電位と、基準信号の電位の大小関係に基づき、差動増幅回路 217 から信号が出力され、発光素子 18 へ電流が供給され、点灯する。差動増幅回路 217 からの信号により、発光素子の点灯時間が制御され、結果として階調表示を行うことができる。なお上述したように本実施の形態において、差動増幅回路 217 が有する薄膜トランジスタを飽和領域で動作させる必要がない。そのため、駆動電圧を高くする必要がなく、消費電力を削減することができる。

【0239】

10

このように本実施の形態は、1 ゲート選択期間に基準信号入力期間 T1 と、ビデオ信号入力期間 T2 が設けられていることを特徴とする。その結果、1 つの信号線 10 を共用でき、開口率を高めることができる。また 1 ゲート選択期間に、基準信号入力期間 T1 と、ビデオ信号入力期間 T2 を設けるため、走査線駆動回路の動作周波数を高めるとよい。

【0240】

本実施の形態で示した画素構成であっても、上記実施の形態で示した作製方法により作製することができる。

【0241】

本実施の形態で示した画素構成であっても、上記実施の形態で示した、逆方向電圧を印加するための構成、温度補償機能を有する素子や、保護回路を設けてもよい。

20

【0242】

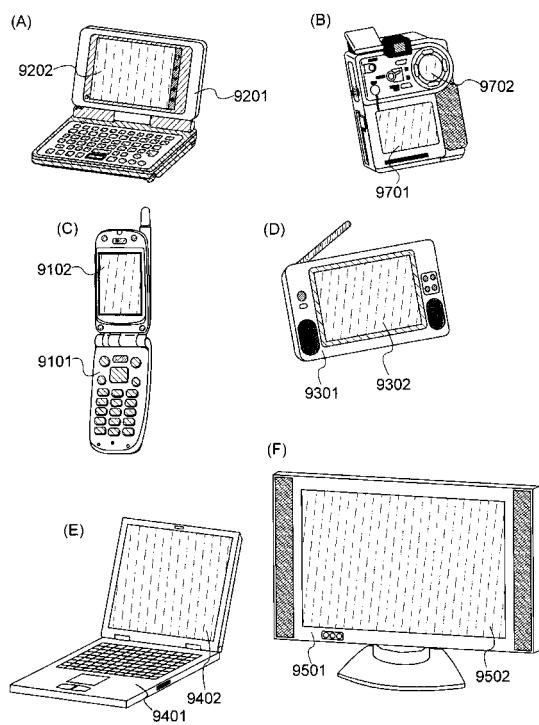

(実施の形態 12)

発光素子を含む画素領域を備えた表示装置を用いた電子機器として、テレビジョン装置（テレビ、テレビジョン受信機）、デジタルカメラ、デジタルビデオカメラ、携帯電話装置（携帯電話機）、PDA 等の携帯情報端末、携帯型ゲーム機、モニター、コンピュータ、カーオーディオ等の音響再生装置、家庭用ゲーム機等の記録媒体を備えた画像再生装置等が挙げられる。その具体例について、図 34 を参照して説明する。

【0243】

図 34 (A) に示す本発明の表示装置を用いた携帯情報端末は、本体 9201、表示部 9202 等を含み、本発明により消費電力を削減することができる。図 34 (B) に示す本発明の表示装置を用いたデジタルビデオカメラは、表示部 9701、9702 等を含み、本発明により消費電力を削減することができる。図 34 (C) に示す本発明の表示装置を用いた携帯端末は、本体 9101、表示部 9102 等を含み、本発明により消費電力を削減することができる。図 34 (D) に示す本発明の表示装置を用いた携帯型のテレビジョン装置は、本体 9301、表示部 9302 等を含み、本発明により消費電力を削減することができる。図 34 (E) に示す本発明の表示装置を用いた携帯型のコンピュータは、本体 9401、表示部 9402 等を含み、本発明により消費電力を削減することができる。図 34 (F) に示す本発明の表示装置を用いたテレビジョン装置は、本体 9501、表示部 9502 等を含み、本発明により消費電力を削減することができる。上記に挙げた電子機器において、バッテリーを用いているものは、消費電力を削減した分、電子機器の使用時間を長持ちさせることができ、バッテリーを充電する手間を省くことができる。

30

【図面の簡単な説明】

【0244】

【図 1】本発明の画素を示した回路図である

【図 2】本発明の画素の駆動方法を示した図である

【図 3】本発明の画素を示した上面図である

【図 4】本発明の画素を示した断面図である

【図 5】本発明の画素を示した断面図である

【図 6】本発明の画素を示した断面図である

【図 7】本発明の画素を示した断面図である

40

50

- 【図 8】本発明の画素を有するパネル全体図である

- 【図 9】本発明の駆動回路を示す図である

- 【図 10】本発明の駆動回路を示す図である

- 【図 11】本発明の駆動回路を示す図である

- 【図 12】本発明の画素を有するパネル全体図である

- 【図 13】本発明の画素を示した回路図である

- 【図 14】本発明の画素の駆動方法を示した図である

- 【図 15】本発明の温度補償機能を示した図である

- 【図 16】本発明の保護回路を示した図である

- 【図 17】本発明の保護回路を示した図である

- 【図 18】本発明の逆方向電圧を印加する画素を示した図である

- 【図 19】本発明の逆方向電圧を印加する動作を示した図である

- 【図 20】本発明の逆方向電圧を印加する画素を示した図である

- 【図 21】本発明の逆方向電圧を印加する動作を示した図である

- 【図 22】本発明の逆方向電圧を印加する動作を示した図である

- 【図 23】本発明の逆方向電圧を印加する動作を示した図である

- 【図 24】本発明の逆方向電圧を印加する画素を示した図である

- 【図 25】本発明の温度補償機能を有する画素を示した図である

- 【図 26】本発明の補償回路を示した図である

- 【図 27】本発明の温度補償機能を有する画素を示した図である

- 【図 28】本発明の補償回路を示した図である

- 【図 29】本発明の補償回路を示した図である

- 【図 30】本発明の補償回路を示した図である

- 【図 31】本発明の補償回路を示した図である

- 【図 32】本発明の補償回路を示した図である

- 【図 33】本発明のシフトレジスタの構成を示した図である

- 【図 34】本発明の電子機器を示した図である

- 【図 35】本発明の画素を示した回路図である

- 【図 36】本発明の画素を示した回路図である

- 【図 37】本発明の画素を示した回路図である

- 【図 38】本発明の画素を示した回路図である

- 【図 39】本発明の画素を示した回路図である

- 【図 40】本発明の画素を示した回路図である

- 【図 41】本発明の表示装置を示した断面図である

- 【図 42】本発明の温度補償機能を説明した図である

- 【図 43】本発明の画素を示した断面図である

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【 図 1 1 】

【図 1 2】

【 図 1 3 】

【 図 1 4 】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図 2 1】

【図 2 2】

【図 2 3】

【図 2 4】

【図 2 5】

【図 2 6】

【図 2 7】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図38】

【図37】

【図40】

【図41】

【図42】

【図43】

---

フロントページの続き

(51)Int.Cl.

F I

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 2 4 B |

| G 0 9 G | 3/20  | 6 4 2 P |

| G 0 9 G | 3/20  | 6 7 0 M |

| G 0 9 G | 3/20  | 6 7 0 Z |

| H 0 5 B | 33/14 | A       |

(72)発明者 安藤 由香里

神奈川県厚木市長谷3 9 8番地 株式会社半導体エネルギー研究所内

(72)発明者 宮川 恵介

神奈川県厚木市長谷3 9 8番地 株式会社半導体エネルギー研究所内

審査官 堀部 修平

(56)参考文献 特開2 0 0 3 - 0 0 5 7 0 9 ( J P , A )

特開2 0 0 4 - 1 3 3 2 4 0 ( J P , A )

特開2 0 0 3 - 2 0 8 1 2 4 ( J P , A )

特開2 0 0 2 - 3 3 3 8 7 0 ( J P , A )

特開2 0 0 3 - 2 2 3 1 3 7 ( J P , A )

特開2 0 0 4 - 0 4 5 6 4 7 ( J P , A )

(58)調査した分野(Int.Cl. , DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8