(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-141204

(P2010-141204A)

(43) 公開日 平成22年6月24日(2010.6.24)

(51) Int.Cl.

H01L 23/12 (2006.01)

F 1

H01L 23/12

テーマコード(参考)

N

審査請求 未請求 請求項の数 5 O L (全 18 頁)

(21) 出願番号

特願2008-317410 (P2008-317410)

(22) 出願日

平成20年12月12日 (2008.12.12)

(71) 出願人 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100091672

弁理士 岡本 啓三

(72) 発明者

金子 健太郎

長野県長野市小島田町80番地 新光電気

工業株式会社内

(54) 【発明の名称】配線基板及びその製造方法

## (57) 【要約】

【課題】低コストでPOP(パッケージ・オン・パッケージ)接続を容易に行えるようにし、その接続信頼性の向上を図ると共に、小型・薄型化に寄与すること。

【解決手段】配線基板(パッケージ)10は、その一方の面側の最外層の絶縁層12の、チップ搭載エリアに対応する箇所にキャビティCVが形成され、このキャビティCV内の絶縁層12の表面に露出するパッドP1と、キャビティCVの周囲の絶縁層12の表面に露出するパッドP2とを備えている。そして、このパッケージ10のキャビティCV内のパッドP1にチップ31がフリップチップ接続され、キャビティCVの周囲のパッドP2に他のパッケージ40が接続されて、POP構造の半導体装置30を構成している。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

支持基材上に、形成すべきキャビティの位置に対応する部分のみが残存するようパターン形成された第1のレジスト層を形成する工程と、

前記第1のレジスト層をマスクにして前記支持基材を所要量だけ除去し、段差部を有した支持基材を形成する工程と、

前記第1のレジスト層を除去後、前記支持基材の段差部が形成されている側の面に、該段差部の上の部分及び下の部分に対応する箇所にそれぞれ第1の開口部及び第2の開口部を有するようパターン形成された第2のレジスト層を形成する工程と、

前記第2のレジスト層の第1、第2の各開口部から露出している前記支持基材上に、それぞれ第1のパッド及び第2のパッドを形成する工程と、

前記第2のレジスト層を除去後、前記支持基材上に、前記第1、第2の各パッドを覆う絶縁層を形成する工程と、

前記絶縁層の上面から前記各パッドの一部を露出させる開口を形成する工程と、

前記絶縁層上に、前記各パッドにそれぞれ接続されるビアを含む配線層を形成する工程と、

以降、所要の層数となるまで絶縁層と配線層を交互に積層した後、前記支持基材を除去する工程とを含むことを特徴とする配線基板の製造方法。

**【請求項 2】**

前記第1のパッド及び第2のパッドを形成する工程の前に、前記第2のレジスト層から露出する第1の開口部及び第2の開口部の少なくとも一方に、犠牲導体層を形成する工程を含むことを特徴とする請求項1に記載の配線基板の製造方法。

**【請求項 3】**

支持基材上に、形成すべきキャビティの位置に対応する箇所に開口部を有するようパターン形成された第1のレジスト層を形成する工程と、

前記第1のレジスト層の開口部から露出している前記支持基材上に、犠牲導体層を所要の厚さに形成して、段差部を有した支持基材を形成する工程と、

前記第1のレジスト層を除去後、前記支持基材の段差部が形成されている側の面に、該段差部の上の部分の犠牲導体層上及び該段差部の下の部分に対応する箇所にそれぞれ第1の開口部及び第2の開口部を有するようパターン形成された第2のレジスト層を形成する工程と、

前記第2のレジスト層の第1、第2の各開口部から露出している前記犠牲導体層及び前記支持基材上に、それぞれ第1のパッド及び第2のパッドを形成する工程と、

前記第2のレジスト層を除去後、前記犠牲導体層及び前記支持基材上に、前記第1、第2の各パッドを露出させて絶縁層を形成する工程と、

前記絶縁層の上面から前記各パッドの一部を露出させる開口を形成する工程と、

前記絶縁層上に、前記各パッドにそれぞれ接続されるビアを含む配線層を形成する工程と、

以降、所要の層数となるまで絶縁層と配線層を交互に積層した後、前記支持基材及び前記犠牲導体層を除去する工程とを含むことを特徴とする配線基板の製造方法。

**【請求項 4】**

一方の面側の最外層の絶縁層の、電子部品の搭載エリアに対応する箇所にキャビティが形成され、

前記キャビティ内の前記絶縁層の表面に露出する第1のパッドと、

前記キャビティの周囲の前記絶縁層の表面に露出する第2のパッドとを備えたことを特徴とする配線基板。

**【請求項 5】**

前記キャビティ内の前記絶縁層の表面に露出する第1のパッドに代えて、前記キャビティ内の前記絶縁層の表面から基板内側に後退した位置に露出する第1のパッドを備えたことを特徴とする請求項4に記載の配線基板。

10

20

30

40

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、配線基板及びその製造方法に関し、より詳細には、半導体素子（チップ）等の搭載用もしくは外部接続用の端子（パッド）が最外層の絶縁層から露出した構造を有した配線基板及びその製造方法に関する。

**【0002】**

かかる配線基板は、半導体チップ等を搭載するパッケージとしての機能を果たすという点で、以下の記述では便宜上、「半導体パッケージ」ともいう。

**【背景技術】**

10

**【0003】**

配線基板（半導体パッケージ）に半導体チップ等の電子部品を搭載して半導体装置を構成するにあたり、その小型・薄型化及び高性能（高機能）化の流れの中で、実装面積削減のため、半導体チップ等を搭載したパッケージ同士を上下方向（高さ方向）に積層するPOP（パッケージ・オン・パッケージ）接合の要求がある。

**【0004】**

20

かかるPOP接合を実現する方法の一つとして、上下のパッケージ間にインターポーラを介在させて接続する方法がある。これは、下側パッケージ（配線基板）に半導体チップをフリップチップ接続するとともに、この下側パッケージ上で当該チップの周辺領域に形成された端子（パッド）に、上側パッケージ（配線基板）の実装面側の対応する領域に形成された端子（パッド）を、当該チップの厚さ（その電極端子を含む）よりも厚いインターポーラの両面にそれぞれ形成された外部端子を介して接合した構造である。

**【0005】**

この接続方法では、インターポーラを製造するためのプロセスも別途必要となる。その典型的なプロセスは、コア材を用意 その所要箇所にスルーホールを形成 そのスルーホールに導体を充填後、両面にレジスト層を形成 導体に接続させて所要のパターンに配線層を形成 レジスト層を除去 配線層の外部端子形成部を露出させて絶縁層（ソルダレジスト層）を形成 外部端子形成部に所要のめっき（ニッケル／金めっきなど）を施す工程等を含む。

**【0006】**

30

また、上記のPOP接合を実現する他の方法として、はんだを用いて上下各パッケージの端子（パッド）同士を接続する方法がある。これは、下側パッケージ（配線基板）に半導体チップをフリップチップ接続するとともに、この下側パッケージ上で当該チップの周辺領域に形成された端子（パッド）に、上側パッケージ（配線基板）の実装面側の対応する領域に形成された端子（パッド）を、はんだバンプを介して接合した構造である。

**【0007】**

40

かかるPOP接合に関連する技術として、特許文献1に記載されたものがある。この文献には、ソルダボールによりトップ基板（配線基板）と電気的に繋がるパッケージ・オン・パッケージのボトム基板（配線基板）が開示されており、このボトム基板は、コア基板と、ソルダボールの位置に応じてコア基板の表面に形成されるパッドと、コア基板に積層される絶縁層と、上記パッドが露出されるように絶縁層の一部を除去して形成される貫通ホールと、この貫通ホールに充填されてソルダボールと電気的に繋がる金属層とを備えている。

**【特許文献1】特開2008-16819号公報****【発明の開示】****【発明が解決しようとする課題】****【0008】**

上述したように従来の技術では、POP接合（接続）を実現するために、インターポーラによる接続や、はんだによる接続などが行われている。しかしながら、インターポーラによる接続の場合、そのインターポーラを製造するためのプロセス（相当の製造工程）を

50

別途必要とし、またそのための材料も必要となるため、製造コストが増大するといった問題があった。

【0009】

一方、はんだによる接続の場合、上下パッケージ間に搭載チップが介在している分、パッケージ間の間隔が大きいため、パッケージ間を接続するはんだ（バンプ）の使用量も多くなり、リフローの際にそのバンプが分断されたり（はんだの泣き別れ）、隣接するバンプ間で橋絡（ブリッジ）が生じたりするなどの不都合があった。その結果、上下パッケージ間の接続信頼性が低下するといった問題があった。

【0010】

また、いずれの方法による接続の場合も、上下パッケージ間に搭載チップが介在している分、POP構造全体として見た場合に、そのチップの厚さにも依るが、必ずしも所望の小型・薄型化を達成することができないといった課題もあった。

【0011】

本発明は、かかる従来技術における課題に鑑み創作されたもので、低コストでPOP接続を容易に行えるようにし、その接続信頼性の向上を図ると共に、小型・薄型化に寄与することができる配線基板及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

上述した従来技術の課題を解決するため、本発明の一形態によれば、支持基材上に、形成すべきキャビティの位置に対応する部分のみが残存するようパターン形成された第1のレジスト層を形成する工程と、前記第1のレジスト層をマスクにして前記支持基材を所要量だけ除去し、段差部を有した支持基材を形成する工程と、前記第1のレジスト層を除去後、前記支持基材の段差部が形成されている側の面に、該段差部の上の部分及び下の部分に対応する箇所にそれぞれ第1の開口部及び第2の開口部を有するようパターン形成された第2のレジスト層を形成する工程と、前記第2のレジスト層の第1、第2の各開口部から露出している前記支持基材上に、それぞれ第1のパッド及び第2のパッドを形成する工程と、前記第2のレジスト層を除去後、前記支持基材上に、前記第1、第2の各パッドを覆う絶縁層を形成する工程と、前記絶縁層の上面から前記各パッドの一部を露出させる開口を形成する工程と、前記絶縁層上に、前記各パッドにそれぞれ接続されるビアを含む配線層を形成する工程と、以降、所要の層数となるまで絶縁層と配線層を交互に積層した後、前記支持基材を除去する工程とを含むことを特徴とする配線基板の製造方法が提供される。

【0013】

この形態に係る配線基板の製造方法によれば、最終的に得られる配線基板において最外層の絶縁層（例えば、樹脂層）の電子部品搭載エリアに対応する箇所にキャビティが形成され、このキャビティ内の絶縁層の表面に第1のパッドが露出し、かつ、キャビティの周囲の絶縁層の表面に第2のパッドが露出している。つまり、第1のパッドが露出する絶縁層の表面の高さが、第2のパッドが露出する絶縁層の表面よりも低くなるように形成されている。従って、キャビティの周囲に配置された第2のパッドをPOP接合（接続）用の端子として利用することで、POP接続を容易に行うことができる。

【0014】

すなわち、本配線基板に搭載する電子部品（半導体チップなど）をキャビティ内に収容できるので、その周囲の第2のパッドに接続される他のパッケージとの間隔を相対的に狭くすることができる。このため、従来技術で使用されていたようなインターポーラを介在させなくても、その狭められた間隔に応じた少量のはんだ（はんだバンプなど）を介して上下パッケージ間の接続（POP接続）を容易に行うことが可能となる。つまり、POP接続を行うに際し、インターポーラが不要となることで、コストの低減化を図ることができる。

【0015】

また、POP接続を行う際、上下パッケージ間を接続するはんだ（バンプ）の使用量が

10

20

30

40

50

少なくて済むので、従来技術に見られたような不都合（はんだの泣き別れやブリッジ等）を解消することができる。これは、接続信頼性の向上に寄与する。

【0016】

さらに、搭載する電子部品をキャビティ内に収容できるので、本配線基板の高さを相対的に低くすることができ、小型・薄型化に寄与する。その結果、POP構造を実現するにあたり、所望の小型・薄型化を達成することが可能となる。

【0017】

また、本発明の他の形態によれば、支持基材上に、形成すべきキャビティの位置に対応する箇所に開口部を有するようパターン形成された第1のレジスト層を形成する工程と、前記第1のレジスト層の開口部から露出している前記支持基材上に、犠牲導体層を所要の厚さに形成して、段差部を有した支持基材を形成する工程と、前記第1のレジスト層を除去後、前記支持基材の段差部が形成されている側の面に、該段差部の上の部分の犠牲導体層上及び該段差部の下の部分に対応する箇所にそれぞれ第1の開口部及び第2の開口部を有するようパターン形成された第2のレジスト層を形成する工程と、前記第2のレジスト層の第1、第2の各開口部から露出している前記犠牲導体層及び前記支持基材上に、それぞれ第1のパッド及び第2のパッドを形成する工程と、前記第2のレジスト層を除去後、前記犠牲導体層及び前記支持基材上に、前記第1、第2の各パッドを露出させて絶縁層を形成する工程と、前記絶縁層の上面から前記各パッドの一部を露出させる開口を形成する工程と、前記絶縁層上に、前記各パッドにそれぞれ接続されるビアを含む配線層を形成する工程と、以降、所要の層数となるまで絶縁層と配線層を交互に積層した後、前記支持基材及び前記犠牲導体層を除去する工程とを含むことを特徴とする配線基板の製造方法が提供される。

10

20

30

【0018】

この形態に係る配線基板の製造方法においても、上記の形態に係る配線基板の製造方法と同様に、最終的に得られる配線基板は同じ構成を有しているので、同様の作用効果を奏すことができる。

【0019】

また、本発明の更に他の形態によれば、一方の面側の最外層の絶縁層の、電子部品の搭載エリアに対応する箇所にキャビティが形成され、前記キャビティ内の前記絶縁層の表面に露出する第1のパッドと、前記キャビティの周囲の前記絶縁層の表面に露出する第2のパッドとを備えたことを特徴とする配線基板が提供される。

【0020】

本発明に係る配線基板及びその製造方法の他の構成上の特徴及びそれに基づく有利な利点等については、以下に記述する発明の実施の形態を参照しながら説明する。

【発明を実施するための最良の形態】

【0021】

以下、本発明の好適な実施の形態について、添付の図面を参照しながら説明する。

【0022】

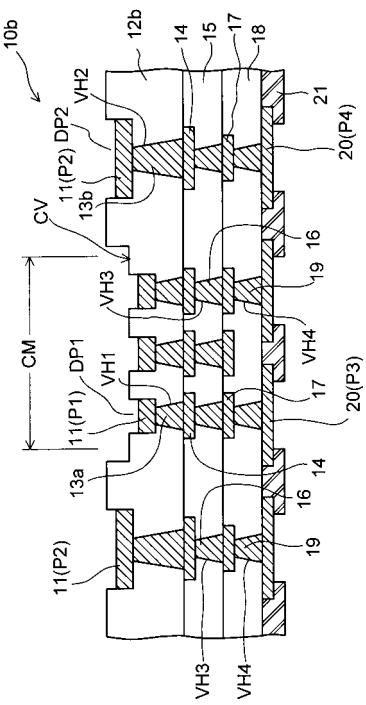

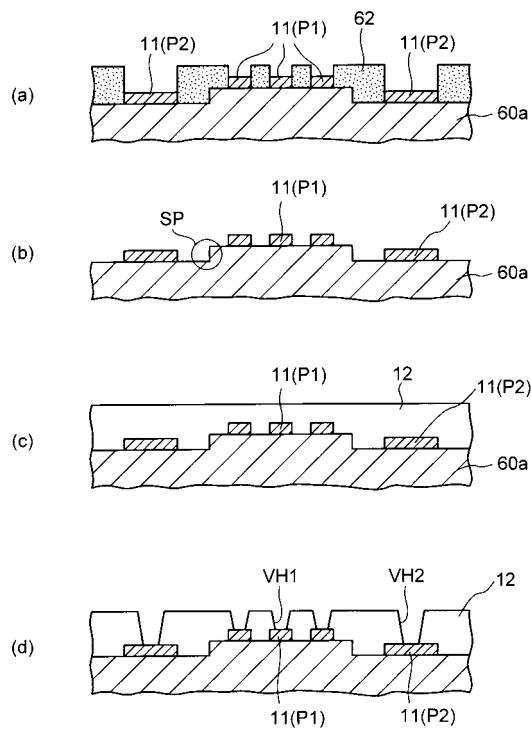

（第1の実施形態…図1～図6参照）

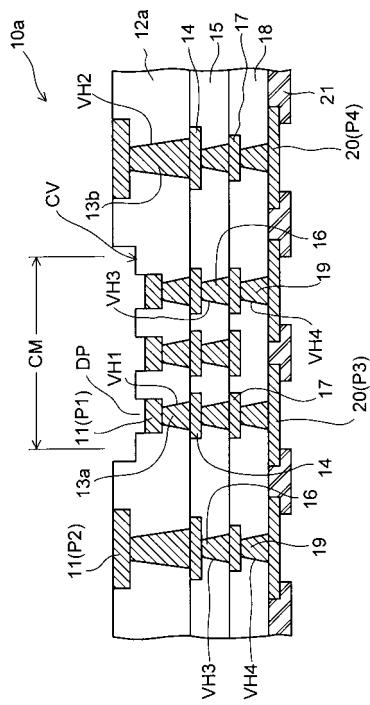

図1は本発明の第1の実施形態に係る配線基板（半導体パッケージ）の構成を断面図の形態で示したものである。

40

【0023】

本実施形態に係る配線基板（半導体パッケージ）10は、図示のように、複数の配線層11, 14, 17, 20が絶縁層（具体的には、樹脂層）12, 15, 18を介在させて積層され、各々の絶縁層12, 15, 18に形成されたビアホールVH1及びVH2, VH3, VH4にそれぞれ充填された導体（ビア13a及び13b、16, 19）を介して層間接続された構造を有している。つまり、本パッケージ10は、一般的なビルトアップ法を用いて作製される配線基板（支持基材としてのコア基板の両面／片面に所要数のビルトアップ層を順次形成して積み上げていくもの）とは違い、支持基材を含まない「コアレス基板」の形態を有している。

50

## 【0024】

このコアレス基板の一方の面側（図示の例では上側）の最外層の樹脂層12には、本発明を特徴付ける凹部（キャビティ）CVが形成されている。このキャビティCVには、本パッケージ10に搭載される半導体素子等の電子部品（チップ）が収容される。従って、このキャビティCVは、図示のように樹脂層12上のチップ搭載エリアCMに対応する箇所に、このエリアよりも若干大きいサイズで、所要の深さに形成されている。

## 【0025】

また、このキャビティCVは、チップを収容する役割の他に、後述するように本パッケージ10にチップを搭載してその間隙にアンダーフィル樹脂を充填したときに、その間隙から周囲に流れ出す樹脂を堰き止めるための「ダム」としての役割も果たす。

10

## 【0026】

キャビティCVが形成されている側の面には、2種類のパッドP1, P2（配線層11の所要の箇所に画定された部分）が露出しており、各パッドP1, P2は、図示のようにその表面が樹脂層12の表面と同一面となるように形成されている。ただし、パッドP1はキャビティCV内のチップ搭載エリアCMに配置され、パッドP2はキャビティCVの周囲の領域に配置されているので、パッドP1の表面は、図示のようにキャビティCVの深さに相当する分だけ、パッドP2の表面の位置から下側（基板内側）に後退した位置にある。

## 【0027】

一方、パッドP1, P2が形成されている側と反対側の面（図示の例では下側）には、保護膜として機能するソルダレジスト層（絶縁層）21が、最外層の配線層（図示の例では配線層20）の所要の箇所に画定されたパッドP3, P4の部分を除いてその表面を覆うように形成されている。このソルダレジスト層21から露出する各パッドP3, P4のうち、パッドP3は、ビア19、配線層17、ビア16、配線層14及びビア13aを介してチップ搭載エリアCM内のパッドP1に接続されている。また、パッドP4は、ビア19、配線層17、ビア16、配線層14及びビア13bを介してチップ搭載エリアCMの周囲のパッドP2に接続されている。

20

## 【0028】

本実施形態では、キャビティCVが形成されている側の樹脂層12から露出する各パッドP1, P2のうち、パッドP1には、本パッケージ10に搭載される半導体素子等の電子部品（チップ）の電極パッドがはんだバンプ等の導電性材料を用いてフリップチップ接続され、パッドP2には、本パッケージ10にPOP（パッケージ・オン・パッケージ）接合される他のパッケージの電極パッドがはんだバンプ等の導電性材料を用いて接続されるようになっている。一方、下側のソルダレジスト層21から露出する各パッドP3, P4には、本パッケージ10をマザーボード等に実装する際に使用されるはんだボール等の外部接続端子が接合されるようになっている。つまり、キャビティCVが形成されている側の面は「チップ搭載面（パッケージ接合面）」、ソルダレジスト層21が形成されている側の面は「外部接続端子接合面」として利用されるようになっている。

30

## 【0029】

ただし、本パッケージ10が使用される条件や使用環境、POP接合の際の配置態様等によっては、チップ搭載面（パッケージ接合面）と外部接続端子接合面を上下反対の使用形態としてもよい。

40

## 【0030】

なお、本パッケージ10の一方の面に形成されるソルダレジスト層21は、保護膜としての機能の他に、補強層としての役割も果たす。すなわち、本パッケージ10は剛性の小さいコアレス基板であってその厚さも薄いため、基板の強度が少なからず低下することは否めないが、図示のように基板の片面にソルダレジスト層21を形成することで基板の補強に寄与することができる。

## 【0031】

本実施形態に係る配線基板（半導体パッケージ）10を構成する各部材の具体的な材料

50

や大きさ、厚さ等については、以下に記述するプロセスに関連させて説明する。

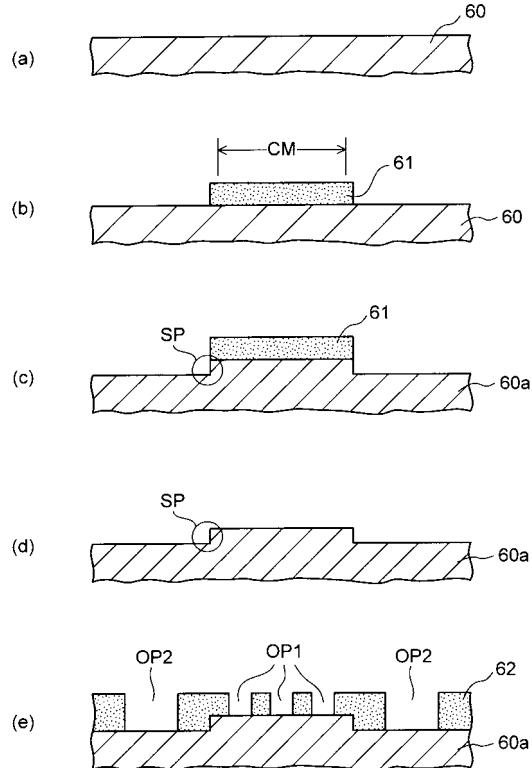

【0032】

次に、本実施形態に係る配線基板（半導体パッケージ）10を製造する方法について、その製造工程の一例を示す図2～図4を参照しながら説明する。

【0033】

先ず最初の工程では（図2（a）参照）、仮基板としての支持基材60を用意する。この支持基材60の材料としては、後述するように最終的にはエッチングされることを考慮して、エッチング液で溶解可能な金属（典型的には、銅（Cu））が用いられる。また、支持基材60の形態としては、基本的には金属板もしくは金属箔で十分である。具体的には、例えば、プリプレグ（補強材のガラス布にエポキシ系樹脂、ポリイミド系樹脂等の熱硬化性樹脂を含浸させ、半硬化のBステージ状態にした接着シート）上に下地層及び銅箔を配置して加熱・加圧することにより得られた構造体（例えば、特開2007-158174号公報に開示された支持基材）を、支持基材60として使用することができる。

10

【0034】

次の工程では（図2（b）参照）、支持基材60上に、パターニング材料を使用してエッチングレジストを形成し、所要の形状にパターニングしてレジスト層61を形成する。このレジスト層61は、最終的にチップ搭載面（パッケージ接合面）側の最外層の樹脂層12に形成されるキャビティCV（チップ搭載エリアCMよりも若干大きいサイズ）の位置に対応する部分のみが残存するようにパターニング形成される。

20

【0035】

パターニング材料としては、感光性のドライフィルム（レジスト材料をポリエステルのカバーシートとポリエチレンのセパレータシートの間に挟んだ構造のもの）、又は液状のフォトレジスト（ノボラック系樹脂、エポキシ系樹脂等の液状レジスト）を用いることができる。例えば、ドライフィルムを使用する場合には、支持基材60の表面を洗浄後、ドライフィルムを熱圧着により貼り付け、このドライフィルムを、所要の形状にパターニングされたマスク（図示せず）を用いて紫外線（UV）照射による露光を施して硬化させ、さらに所定の現像液を用いて当該部分以外の部分をエッチング除去し、所要のキャビティCVの形状に応じたレジスト層61を形成する。液状のフォトレジストを用いた場合も、同様の工程を経て、レジスト層61を形成することができる。

30

【0036】

次の工程では（図2（c）参照）、そのレジスト層（エッチングレジスト）61が形成された支持基材60に対し、そのエッチングレジスト61をマスクにして所要の深さにエッチングを施す。例えば、塩化第二鉄水溶液、塩化第二銅水溶液、過硫酸アンモニウム水溶液などを用いたウェットエッチングにより、支持基材（Cu）60を、レジスト層61に対して選択的に所要量だけ除去する。これにより、図示のようにそのエッチング量に応じた段差部SPを有する支持基材60aが形成される。

40

【0037】

この支持基材60aの段差部SP（すなわち、エッチング量）は、形成すべきキャビティCVの深さを規定するので、搭載すべきチップの大きさやチップ搭載時にアンダーフィル樹脂を充填したときにその間隙から周囲に流れ出す樹脂の量などを適宜考慮して、エッチングの条件やエッチング時間等を適宜選択する必要がある。

40

【0038】

次の工程では（図2（d）参照）、エッチングレジストとして用いたレジスト層61を除去する。例えば、エッチングレジストとしてドライフィルムを使用した場合には、水酸化ナトリウムやモノエタノールアミン系などのアルカリ性の薬液を用いて除去することができ、ノボラック系樹脂、エポキシ系樹脂等の液状レジストを使用した場合には、アセトンやアルコール等を用いて除去することができる。これにより、図示のように所要の段差部SPを有した支持基材60aが形成されたことになる。

【0039】

次の工程では（図2（e）参照）、支持基材60a上の段差部SP（図2（d））が形

50

成されている側の面に、パターニング材料を使用してめっきレジストを形成し、その段差部 S P の上の部分と下の部分にそれぞれ対応する部分において所要の箇所を開口する（開口部 O P 1 及び O P 2 を備えたレジスト層 6 2 の形成）。開口部 O P 1 及び O P 2 は、それぞれチップ搭載エリア C M 内及びその周囲に対応する部分において、それぞれ形成すべき所要のパッド P 1 及び P 2 の形状に従ってパターニング形成される。パターニング材料としては、図 2 ( b ) の工程で使用した材料と同様に、感光性のドライフィルム又は液状のフォトレジストを用いることができる。

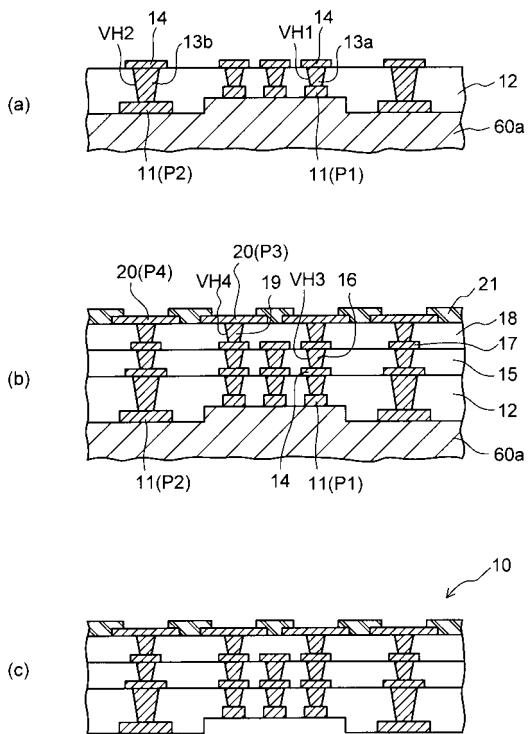

【 0 0 4 0 】

次の工程では（図 3 ( a ) 参照）、レジスト層 6 2 に開口された開口部 O P 1 及び O P 2（図 2 ( e )）から露出している支持基材（C u）6 0 a 上に、この支持基材 6 0 a を給電層として利用した電解めっきにより、配線層 1 1 を形成する。この配線層 1 1 の所定の複数箇所に画定された各部分は、チップを搭載するためのパッド P 1 及び他のパッケージを P O P 接合するためのパッド P 2 として機能する。

10

【 0 0 4 1 】

形成すべきパッド P 1 , P 2 は、特に図示はしないが、いずれも円形であり、それぞれの大きさ（直径）は、チップ搭載用のパッド P 1 については 50 ~ 150  $\mu\text{m}$  程度に選定され、他のパッケージ搭載用のパッド P 2 については 200 ~ 1000  $\mu\text{m}$  程度に選定される。また、各パッド P 1 , P 2 は、複数の金属層が積層された構造からなり、その最下層の金属層（最終的に露出する側の金属層）を構成する材料としては、これに接触する支持基材 6 0 a が最終的にエッチングされることを考慮して、そのエッチング液で溶解されない金属種を選定する。本実施形態では、支持基材 6 0 a の材料として銅（C u）を用いているので、これとは異なる金属として、良好なコンタクト性（はんだ付け性）を確保できるという点を考慮し、金（A u）を使用している。

20

【 0 0 4 2 】

具体的には、先ず支持基材（C u）6 0 a 上に A u フラッシュめっきを施して厚さ 40 nm 程度の A u 層を形成し、さらにパラジウム（P d）フラッシュめっきを施して厚さ 20 nm 程度の P d 層を形成して、A u / P d 層を形成する。次いで、この A u / P d 層上にニッケル（N i）めっきを施して厚さ 5  $\mu\text{m}$  程度の N i 層を形成し、さらに N i 層上に C u めっきを施して厚さ 15  $\mu\text{m}$  程度の C u 層を形成する。ここに、P d 層は、その下層部分である A u 層の酸化を防止するために形成され、N i 層は、その上層の金属層に含まれる C u が下層の A u / P d 層に拡散するのを防止するために形成されている。

30

【 0 0 4 3 】

つまり、この工程では、A u / P d 層と N i 層と C u 層の 3 層（厳密には 4 層）構造からなるパッド P 1 , P 2 を形成している。なお、本工程では最下層の金属層として A u / P d 層を形成しているが、P d 層については必ずしも形成する必要はなく、A u 層のみからなる金属層としてもよい。

30

【 0 0 4 4 】

次の工程では（図 3 ( b ) 参照）、めっきレジストとして用いたレジスト層 6 2 を除去する。除去方法については、図 2 ( d ) の工程で説明した方法と同じである。これによつて、図示のように支持基材 6 0 a 上の段差部 S P の上の部分及び下の部分にそれぞれパッド P 1（配線層 1 1）及びパッド P 2（配線層 1 1）が形成された構造体が作製されたことになる。

40

【 0 0 4 5 】

次の工程では（図 3 ( c ) 参照）、支持基材 6 0 a 上のパッド P 1 , P 2 が形成されている側の面に、エポキシ系樹脂やポリイミド系樹脂等からなる絶縁層 1 2 を形成する。例えば、エポキシ系樹脂フィルムを支持基材 6 0 a 及びパッド P 1 , P 2（配線層 1 1）上にラミネートし、この樹脂フィルムをプレスしながら 130 ~ 150 の温度で熱処理して硬化させることにより、樹脂層（絶縁層 1 2）を形成することができる。この場合、支持基材 6 0 a の段差部 S P と比べて樹脂フィルムの厚さは相対的に薄いため、1 回のラミネートでは絶縁層 1 2 の表面の平坦性を確保するのは難しく、2 回に分けて積層するのが

50

望ましい。

【0046】

次の工程では(図3(d)参照)、この絶縁層12の所定の箇所(パッドP1, P2に対応する部分)に、炭酸ガスレーザ、エキシマレーザ等による穴明け処理により、それぞれパッドP1, P2に達する開口部(ビアホールVH1, VH2)を形成する。なお、本工程ではレーザ等によりビアホールVH1, VH2を形成しているが、絶縁層12が感光性樹脂を用いて形成されている場合には、フォトリソグラフィにより所要のビアホールを形成することも可能である。

【0047】

次の工程では(図4(a)参照)、ビアホールVH1, VH2が形成された絶縁層12上に、各ビアホールVH1, VH2をそれぞれ充填して(ビア13a, 13bの形成)、各パッドP1, P2に接続される所要パターンの配線層14を形成する。この配線層14は、例えば、セミアディティブ法により形成される。

【0048】

具体的には、先ず、無電解めっきやスパッタリング等により、ビアホールVH1, VH2の内部を含めて絶縁層12上に銅(Cu)のシード層(図示せず)を形成した後、形成すべき配線層14の形状に応じた開口部を備えたレジスト膜(図示せず)を形成する。次に、このレジスト膜の開口部から露出しているシード層(Cu)上に、このシード層を給電層として利用した電解Cuめっきにより、導体(Cu)パターン(図示せず)を形成する。さらに、レジスト膜を除去した後に、導体(Cu)パターンをマスクにしてシード層をエッチングすることで、所要の配線層14が得られる。

【0049】

なお、セミアディティブ法以外に、サブトラクティブ法など各種の配線形成方法を用いてもよい。また、ビア13a, 13bの形成については、無電解めっき等に限らず、スクリーン印刷法を用いた導電性ペースト(銀ペースト、銅ペースト等)の充填によって形成することも可能である。

【0050】

次の工程では(図4(b)参照)、図3(c)~図4(a)の工程で行った処理と同様にして、絶縁層と配線層を交互に積層する。図示の例では、簡単化のため、2層の絶縁層と2層の配線層が積層されている。すなわち、絶縁層12及び配線層14上に樹脂層(絶縁層15)を形成し、この絶縁層15に、配線層14のパッド(図示せず)に達するビアホールVH3を形成した後、このビアホールVH3を充填して(ビア16の形成)当該パッドに接続される所要パターンの配線層17を形成する。さらに、絶縁層15及び配線層17上に樹脂層(絶縁層18)を形成し、この絶縁層18に、配線層17のパッド(図示せず)に達するビアホールVH4を形成した後、このビアホールVH4を充填して(ビア19の形成)当該パッドに接続される所要パターンの配線層20を形成する。この配線層20は、本実施形態では最外層の配線層を構成する。

【0051】

さらに、この配線層20の所定の箇所に画定されるパッドP3, P4の部分を除いて表面(絶縁層18及び配線層20)を覆うようにソルダレジスト層21を形成する。このソルダレジスト層21は、例えば、感光性のソルダレジストフィルムをラミネートし、又は液状のフォトレジストを塗布し、当該レジストを所要の形状にパターニングすることで形成することができる。これによって、ソルダレジスト層21の開口部からパッドP3, P4が露出する。

【0052】

これらパッドP3, P4には、本パッケージ10をマザーボード等に実装する際に使用されるはんだボールやピン等の外部接続端子が接合されるので、チップ搭載面(パッケージ接合面)側のパッドP1, P2と同様に、コンタクト性を良くするためにAuめっきを施しておくのが望ましい。その際、各パッド(Cu)P3, P4上にNiめっきを施してからAuめっきを施す。つまり、Ni層とAu層の2層構造からなる導体層(図示せず)

10

20

30

40

50

を各パッド P 3 , P 4 上に形成する。

【0053】

最後の工程では(図4(c)参照)、仮基板として用いた支持基材60aを、パッドP1,P2、樹脂層12、パッドP3,P4及びソルダレジスト層21に対して選択的に除去する。例えば、塩化第二鉄水溶液、塩化第二銅水溶液、過硫酸アンモニウム水溶液などを用いたウェットエッティングにより、パッドP1,P2(各々の表層部にAu層が形成されている)、樹脂層12、パッドP3,P4(各々の表層部にAu層が形成されている)及びソルダレジスト層21に対して、支持基材(Cu)60aを選択的にエッティングして除去することができる。

【0054】

以上の工程により、本実施形態の配線基板10(図1)が製造されたことになる。

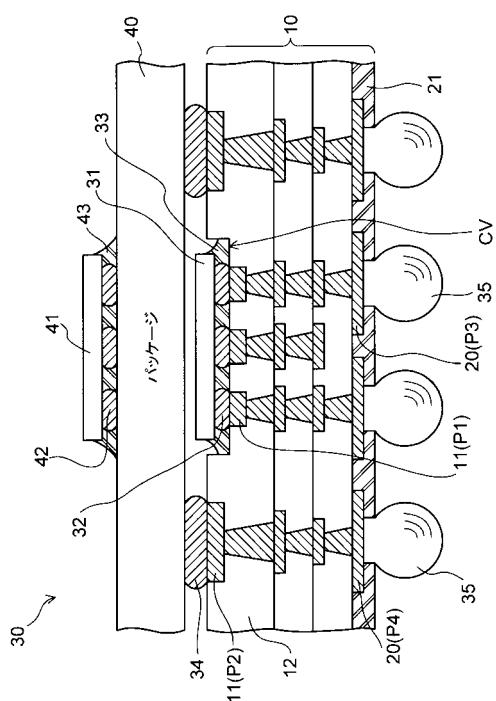

【0055】

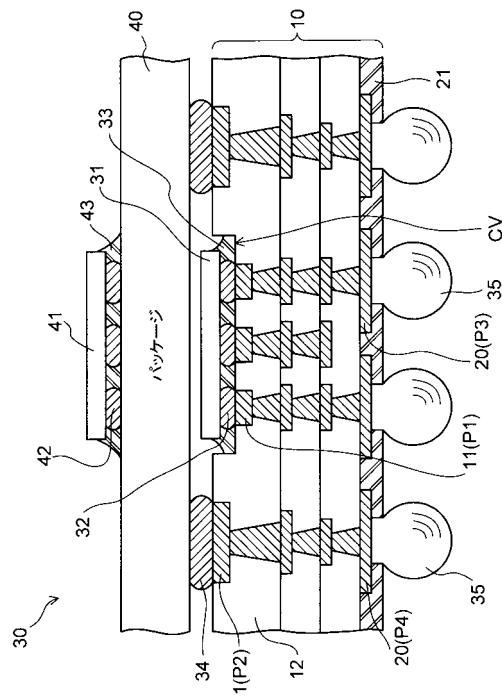

本実施形態の配線基板(半導体パッケージ)10には、上述したように一方の面から露出するパッドP1にチップの電極パッドがはんだバンプ等を介して接続されるとともに、パッドP2に他のパッケージの電極パッドがはんだバンプ等を介して接続され、他方の面から露出するパッドP3,P4にはんだボール等の外部接続端子が接合される。図5はその一構成例を示したものである。

【0056】

図5の例では、本パッケージ10に電子部品としての半導体素子(特定的には、CPU等の能動素子のチップ)31を搭載し、さらに他のパッケージ40を搭載した状態、すなわち、POP構造の半導体装置30を構成した場合の断面構造を示している。搭載されるチップ31は、その電極パッド(図示せず)がはんだバンプ32を介してキャビティCV内のパッドP1にフリップチップ接続されている。このようにキャビティCV内にチップ31を実質的に収容する形で搭載しているので、チップ31の表面は最外層の樹脂層12の表面から僅かに突出する程度である。

【0057】

さらに、その搭載されたチップ31と配線基板10(チップ31に対向する樹脂層12の面)との間隙にアンダーフィル樹脂33(熱硬化性のエポキシ系樹脂など)を充填し、熱硬化させて、チップ31と配線基板10との接続信頼性を高めている。樹脂充填後にチップ・基板間から溢れ出たアンダーフィル樹脂33は、図示のようにキャビティCV内で堰き止められている。つまり、チップ・基板間から周囲に流れ出したアンダーフィル樹脂33の「流れ出し」の範囲をキャビティCV内に止めておくことで、チップ周辺に配置されている回路素子や配線等(図示の例では、配線層11の一部に画定されたパッドP2)に悪影響が及ぼされるのを防いでいる。

【0058】

また、キャビティCVの周囲の樹脂層12上に露出するパッドP2には、他のパッケージ(配線基板)40の実装面側に形成された電極パッド(図示せず)がはんだバンプ34を介して接続されている(POP接続)。その接続の際、上述したようにチップ31の表面は樹脂層12の表面から僅かに突出する程度であるので、上下パッケージ40,10間の間隔は相対的に狭められ、その分だけはんだバンプ34の大きさを小さくすることができる。つまり、使用されるはんだ量を少なくできるので、従来技術に見られたような不都合(はんだの泣き別れやブリッジ等)が解消され、接続信頼性の向上に寄与する。

【0059】

また、他のパッケージ40の実装面側と反対側の面(図示の例では上側)には、本パッケージ10と同様に半導体素子(チップ)41が搭載されている。このチップ41は、その電極パッド(図示せず)がはんだバンプ42を介してパッケージ40上のパッド(図示せず)にフリップチップ接続されている。さらに、その搭載されたチップ41とパッケージ40との間隙にアンダーフィル樹脂43が充填され、熱硬化されて、チップ41がパッケージ40に固定化されている。

【0060】

10

20

30

40

50

一方、本パッケージ 10 のチップ搭載面（パッケージ接合面）と反対側の外部接続端子接合面の各パッド P3, P4 には、それぞれはんだボール 35 がリフローにより接合されている。図示の例では、パッド P3, P4 にはんだボール 35 を接合した BGA（ボール・グリッド・アレイ）の形態としているが、これの代わりに、当該パッドにピンを接合した PGA（ピン・グリッド・アレイ）の形態や、当該パッド自体を外部接続端子とした LGA（ランド・グリッド・アレイ）の形態としてもよい。

#### 【0061】

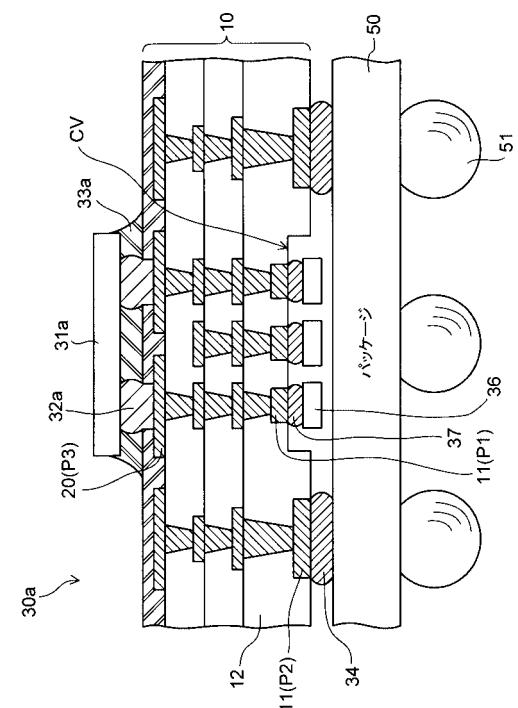

また、図 5 の設置態様とは逆に、チップ搭載面（パッケージ接合面）と外部接続端子接合面を上下反対に使用して POP 構造を実現することも可能である。図 6 はその一構成例を示したものである。

10

#### 【0062】

図 6 の例では、図 5 の場合とはパッケージの上下関係を逆にし、本パッケージ 10 を他のパッケージ 50 上に搭載してなる POP 構造の半導体装置 30a の構成（断面構造）を示している。図 6 の構成例では、上記の能動素子（チップ 31）の代わりに、受動素子としてのチップキャパシタ 36 がパッケージ 10 のキャビティ CV 内に搭載されている。このチップキャパシタ 36 は、その 1 対の電極端子（図示せず）がそれぞれはんだ 37 を用いて当該パッド P1 に接続されている。この構成例においても、キャビティ CV 内にチップキャパシタ 36 を実質的に収容する形で搭載しているので、チップキャパシタ 36 の表面は最外層の樹脂層 12 の表面から僅かに突出する程度である。

#### 【0063】

また、キャビティ CV の周囲の樹脂層 12 上に露出するパッド P2 には、他のパッケージ（配線基板）50 の実装面側と反対側の面（図示の例では上側）に形成された電極パッド（図示せず）がはんだバンプ 34 を介して接続されている（POP 接続）。その接続の際、上述したようにチップキャパシタ 36 の表面は樹脂層 12 の表面から僅かに突出する程度であり、上下パッケージ 10, 50 間の間隔は相対的に狭められるので、その分だけはんだバンプ 34 の大きさを小さくする（使用されるはんだ量を少なくする）ことができる。これにより、従来技術に見られたようなはんだの泣き別れ等の不都合が解消され、POP 接続の信頼性が高まる。

20

#### 【0064】

また、他のパッケージ 50 の実装面側には電極パッド（図示せず）が設けられており、この電極パッドに、当該パッケージ 50 をマザーボード等に実装する際に使用される外部接続端子としてのはんだボール 51 がリフローにより接合されている。

30

#### 【0065】

一方、本パッケージ 10 のチップ搭載面（パッケージ接合面）と反対側の外部接続端子接合面には、図 5 の構成におけるチップ 31 と同様の能動素子（チップ 31a）が搭載されている。このチップ 31a は、その電極パッド（図示せず）がはんだバンプ 32a を介してパッケージ 10 上のパッド P3 にフリップチップ接続されている。さらに、そのチップ 31a とパッケージ 10 との間隙にアンダーフィル樹脂 33a が充填され、熱硬化されて、チップ 31a がパッケージ 10 に固定化されている。なお、図 6 の例では、パッケージ 10 の外部接続端子接合面側のパッド P4（図 5）については図示を省略している。

40

#### 【0066】

以上説明したように、本実施形態に係る配線基板（半導体パッケージ）10 及びその製造方法（図 1～図 4）によれば、チップ搭載面（パッケージ接合面）側の最外層の樹脂層 12 上のチップ搭載エリア CM に対応する箇所に、所要の深さにキャビティ CV が形成され、このキャビティ CV 内の樹脂層 12 の表面と同一面にチップ搭載用のパッド P1 の表面が位置し、かつ、キャビティ CV の周囲の樹脂層 12 の表面と同一面に POP 接合用のパッド P2 の表面が位置するように形成されている。このようにパッド P1 が露出する樹脂層 12 の表面の高さを、パッド P2 が露出する樹脂層 12 の表面よりも低くなるように形成しているので、図 5、図 6 の構成例に示したように POP 接続を容易に行うことができる。

50

## 【0067】

すなわち、パッケージ10に搭載する電子部品（チップ31、チップキャパシタ36）をキャビティCV内に収容できるので、その周囲のパッドP2に接続される他のパッケージ40, 50との間隔を相対的に狭くすることができる。このため、従来技術で使用されていたようなインターポーラを介在させなくとも、その狭められた間隔に応じた少量のはんだ（はんだバンプ34）を介して上下パッケージ間の接続（POP接続）を容易に行うことが可能となる。つまり、POP接続を行うに際し、インターポーラが不要となることで、コストの低減化を図ることができる。

## 【0068】

また、POP接続を行う際、上下パッケージ間の間隔を小さくできるため、パッケージ間を接続するはんだ（バンプ）の使用量も少なくなる。その結果、従来技術に見られたようなはんだの泣き別れやブリッジ等の不都合が解消され、上下パッケージ間の接続信頼性が向上する。

10

## 【0069】

さらに、搭載するチップ31, 36をキャビティCV内に収容できるので、パッケージ10の高さを相対的に低くすることができ、小型・薄型化に寄与する。その結果、POP構造全体として見た場合に、所望の小型・薄型化を達成することが可能となる。

## 【0070】

なお、図5、図6に示した構成例では、パッケージ10のキャビティCV内に搭載するチップ31, 36の表面は樹脂層12の表面より僅かに突出しているが、キャビティCVの深さをさらに深く形成することにより、当該チップ全体をキャビティCV内に収容することができる。これにより、上下パッケージ間の間隔をさらに狭めることができ、更なる薄型化を図ることができる。また、それに応じて使用されるはんだ量も少なくなる。ただし、この場合、図2(c)の工程で行うエッティングの時間が長くなるため、このエッティング時間も考慮してキャビティCVの深さを適宜選定する必要がある。

20

## 【0071】

また、チップの搭載面（パッドP1が露出する樹脂層12の表面）がキャビティCV内に位置しているので、図5に示したように樹脂充填後にチップ・基板間から溢れ出たアンダーフィル樹脂33の「流れ出し」を抑制することができる。つまり、キャビティCVをダムとして機能させることで、チップ周辺に配置されている配線や回路素子等に悪影響が及ぼされるのを防ぐことができる。

30

## 【0072】

また、キャビティCVの深さを適宜変えることで、最外層の樹脂層12の使用量を調整できるので、この樹脂層12とパッドP1, P2を構成する導体層との熱膨張係数の違いに起因して起こり得るパッケージ10の反りを抑制することができる。

## 【0073】

つまり、本パッケージ10は支持基材を含まないコアレス基板であり、剛性が小さく、その厚さも薄いため、反りが発生することが想定される。特に、チップ実装の際に行うリフロー等の熱処理や、チップ実装後に充填されるアンダーフィル樹脂の熱硬化等の熱履歴に晒されると、導体層と樹脂層の熱膨張係数の違い、さらにアンダーフィル樹脂とチップ材料の熱膨張係数の違いに起因して、パッケージ10に反りが発生する可能性が高い。そこで、上記のようにキャビティCVの深さ（樹脂層12の使用量）を適宜変えることで、パッケージ10の反りを抑制することが可能となる。

40

## 【0074】

（第2の実施形態…図7参照）

図7は本発明の第2の実施形態に係る配線基板（半導体パッケージ）の構成を断面図の形態で示したものである。

## 【0075】

この第2の実施形態に係る配線基板（半導体パッケージ）10aは、第1の実施形態に係る配線基板10（図1）の構成と比べて、キャビティCV内のチップ搭載エリアCMに

50

配置されたパッド P 1 の表面が、そのキャビティ C V の底面（樹脂層 1 2 a の表面）から所定の深さだけ基板内側に後退した位置となるように形成されている点で相違している。つまり、キャビティ C V 内において樹脂層 1 2 a 上のパッド P 1 に対応する箇所に凹部 D P が形成されている。他の構成については、図 1 の配線基板 1 0 の構成と基本的に同じであるのでその説明は省略する。

#### 【 0 0 7 6 】

本実施形態に係る配線基板 1 0 a は、基本的には、上述した第 1 の実施形態に係る製造方法の各工程（図 2 ~ 図 4 ）で行った処理と同様にして製造することができる。ただし、キャビティ C V 内の凹部 D P を形成するための処理工程を必要とするため、これに関連する工程において行われる処理が若干異なる。特に図示はしないが、その製造方法の一例を説明すると、以下の通りである。

10

#### 【 0 0 7 7 】

先ず、図 2 ( a ) ~ ( d ) の工程を経て支持基材 6 0 a を形成した後、この支持基材 6 0 a 上の段差部 S P が形成されている側の面に、図 2 ( e ) の工程で行った処理と同様にして、パターニング材料を使用してめっきレジストを形成し、その段差部 S P の上の部分の所要の箇所（形成すべきパッド P 1 に対応する部分）のみを開口する。つまり、開口部 O P 1 のみを備えたレジスト層を形成する。

#### 【 0 0 7 8 】

次に、このレジスト層の開口部 O P 1 から露出している支持基材 6 0 a 上に、この支持基材 6 0 a を給電層として利用した電解めっきにより、犠牲導体層を所要の厚さ（形成すべき凹部 D P の深さに相当する厚さ）に形成する。この犠牲導体層を構成する材料としては、これに接触する支持基材 6 0 a と共に最終的にエッティングされることを考慮して、そのエッティング液で溶解され得る金属種を選定する。この場合、支持基材 6 0 a の材料として銅（C u）を用いているので、この支持基材 6 0 a 上に電解 C u めっきを施して犠牲導体層（C u）を形成する。このように同じ材料（C u）を選定することで、最終的に 1 回のエッティングで各部材（支持基材 6 0 a と犠牲導体層）を同時に除去することができ、工程の簡素化に寄与する。

20

#### 【 0 0 7 9 】

さらに、このめっきレジストを除去した後、支持基材 6 0 a 上の犠牲導体層（C u）が形成されている側の面に、図 2 ( e ) の工程で行った処理と同様にして、パターニング材料を使用してめっきレジストを形成し、その段差部 S P の上の部分と下の部分にそれぞれ対応する部分において所要の箇所（パッド P 1, P 2 に対応する部分）を開口する。つまり、図 2 ( e ) の工程におけるレジスト層 6 2 と同様のパターン形状を有したレジスト層を形成する。

30

#### 【 0 0 8 0 】

次に、図 3 ( a ) の工程で行った処理と同様にして、このレジスト層の開口部 O P 1 及び O P 2 から露出している犠牲導体層（C u）及び支持基材（C u）6 0 a 上に、この支持基材 6 0 a を給電層として利用した電解めっきにより、A u / P d 層（又は A u 層）、N i 層及び C u 層を順次積層してパッド P 1, P 2 を形成する。さらに、このめっきレジストを除去し、図 3 ( c ) ~ 図 4 ( b ) の各工程で行った処理と同様の処理を行った後、支持基材（C u）6 0 a と共に犠牲導体層（C u）も併せてエッティングする。

40

#### 【 0 0 8 1 】

以上の工程により、本実施形態の配線基板 1 0 a（図 7 ）が製造されたことになる。

#### 【 0 0 8 2 】

なお、上述した製造方法では、最終段階でエッティングされる支持基材 6 0 a と犠牲導体層を同じ金属材（C u）を用いて形成した場合を例にとって説明したが、両者は必ずしも同じ材料から形成される必要はない。要は、支持基材と犠牲導体層をそれぞれエッティングする際に、露出している他の構成部材に対して「選択的に」除去することができる材料で形成されれば十分である。この場合、支持基材と犠牲導体層は互いに異なる材料から形成されることになるので、エッティング工程は 2 段階で行われる。

50

## 【0083】

本実施形態(図7)によれば、上述した実施形態(図1～図6)で得られた効果に加えて、さらに以下の利点が得られる。すなわち、キャビティCV内において樹脂層12a上のパッドP1に対応する箇所に凹部DPが形成されているので、この凹部DPにプリソルダ(はんだ被着)を容易に施すことができ、POP接続(図5、図6)に先立って本パッケージ10aに電子部品(チップ)を接続する際に、チップの電極端子とその被着されたはんだとの位置合わせが行い易くなる。

## 【0084】

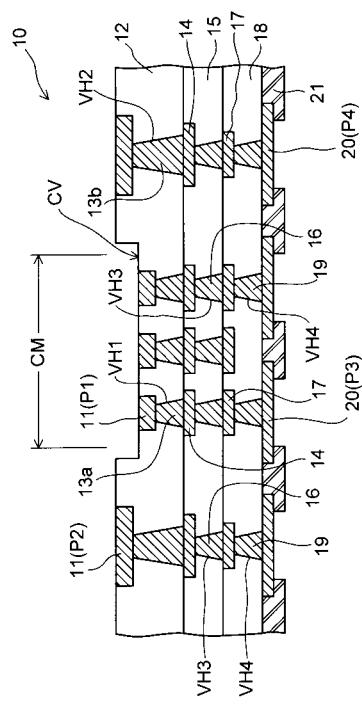

(第3の実施形態…図8参照)

図8は本発明の第3の実施形態に係る配線基板(半導体パッケージ)の構成を断面図の形態で示したものである。

10

## 【0085】

この第3の実施形態に係る配線基板(半導体パッケージ)10bは、第1の実施形態に係る配線基板10(図1)の構成と比べて、キャビティCV内のチップ搭載エリアCMに配置されたパッドP1の表面が、そのキャビティCVの底面(樹脂層12bの表面)から所定の深さだけ基板内側に後退した位置となるように形成されると共に、キャビティCVの周囲の領域に配置されたパッドP2の表面も、樹脂層12bの表面から所定の深さだけ基板内側に後退した位置となるように形成されている点で相違している。つまり、キャビティCV内において樹脂層12b上のパッドP1に対応する箇所に凹部DP1が形成されると共に、キャビティCVの周囲の領域において樹脂層12b上のパッドP2に対応する箇所に凹部DP2が形成されている。他の構成については、図1の配線基板10の構成と基本的に同じであるのでその説明は省略する。

20

## 【0086】

本実施形態に係る配線基板10bは、基本的には、上述した第1の実施形態に係る製造方法の各工程(図2～図4)で行った処理と同様にして製造することができる。ただし、キャビティCV内の凹部DP1及びキャビティCVの周囲の凹部DP2を形成するための処理工程を必要とするため、これに関連する工程において行われる処理が若干異なる。特に図示はしないが、その製造方法の一例を説明すると、以下の通りである。

30

## 【0087】

先ず、図2(a)～(e)の工程で行った処理と同様にして、支持基材60a上の段差部SPが形成されている側の面に、その段差部SPの上の部分と下の部分にそれぞれ対応する部分に所要の開口部OP1及びOP2を備えためっきレジスト(レジスト層62)を形成する。

## 【0088】

次に、このレジスト層62の開口部OP1, OP2から露出している支持基材(Cu)60a上に、この支持基材60aを給電層として利用した電解めっきにより、犠牲導体層を所要の厚さ(形成すべき凹部DP1, DP2の深さに相当する厚さ)に形成する。この犠牲導体層を構成する材料としては、これに接触する支持基材60aと共に最終的にエッティングされることを考慮して、そのエッティング液で溶解され得る金属種を選定する。この場合、支持基材60aの材料として銅(Cu)を用いているので、この支持基材60a上に電解Cuめっきを施して犠牲導体層(Cu)を形成する。このように同じ材料(Cu)を選定することで、最終的に1回のエッティングで各部材(支持基材60aと犠牲導体層)を同時に除去することができ、工程の簡素化に寄与する。

40

## 【0089】

次に、図3(a)の工程で行った処理と同様にして、このレジスト層62の開口部OP1, OP2から露出している犠牲導体層(Cu)上に、支持基材60aを給電層として利用した電解めっきにより、それぞれAu/Pd層(又はAu層)、Ni層及びCu層を順次積層してパッドP1, P2を形成する。さらに、このレジスト層を除去し、図3(c)～図4(b)の各工程で行った処理と同様の処理を行った後、支持基材(Cu)60aと共に犠牲導体層(Cu)も併せてエッティングする。

50

## 【0090】

以上の工程により、本実施形態の配線基板 10b (図8) が製造されたことになる。

## 【0091】

なお、本実施形態においても第2の実施形態の場合と同様に、最終段階でエッティングされる支持基材 60a と犠牲導体層は必ずしも同じ材料 (Cu) から形成されている必要はない。要は、支持基材と犠牲導体層をそれぞれエッティングする際に、露出している他の構成部材に対して「選択的に」除去することができる材料で形成されていれば十分であり、両者は互いに異なる材料から形成されていてもよい。

## 【0092】

この第3の実施形態 (図8) によれば、上述した第2の実施形態 (図7) で得られた効果と同様の効果を奏すことができる。すなわち、キャビティ CV 内の樹脂層 12b 上のパッド P1 に対応する箇所に凹部 DP1 が形成されると共に、キャビティ CV の周囲の領域において樹脂層 12b 上のパッド P2 に対応する箇所に凹部 DP2 が形成されているので、各凹部 DP1, DP2 にプリソルダ (はんだ被着) を容易に施すことができる。これにより、本パッケージ 10b に電子部品 (チップ) を接続する際に、チップの電極端子とその被着されたはんだとの位置合わせが行い易くなり、さらに POP 接続 (図5、図6) を行う際にも、他のパッケージの電極パッドとその被着されたはんだとの位置合わせが行い易くなる。

10

## 【0093】

## (他の実施形態)

20

上述した各実施形態では、パッケージ 10 (10a, 10b) に電子部品 (チップ) を収容するためのキャビティ CV を、所要の形状にパターニングされたエッティングレジスト 61 (図2(c)) をマスクにしてエッティングを施すことで形成した場合を例にとって説明したが、キャビティ CV を形成する方法がこれに限定されないことはもちろんである。例えば、図2(b) の工程において、支持基材 60 上に形成すべきレジスト層を、図示のパターンとは逆のパターン (ポジとネガの関係) としためっきレジストとし、このめっきレジストを利用して所要のキャビティ CV を形成することも可能である。

## 【0094】

30

この場合、そのめっきレジストは、キャビティ CV (チップ搭載エリア CM よりも若干大きいサイズ) の位置に対応する箇所に開口部を備えている。従って、このめっきレジストの開口部から露出している支持基材 (Cu) 60 上に、この支持基材 60 を給電層として利用した電解 Cu めっきにより、犠牲導体層 (Cu) を所要の厚さ (キャビティ CV の深さに相当する厚さ) に形成し、めっきレジストを除去後、図2(e) ~ 図4(b) の各工程で行った処理と同様の処理を経て、最終的に支持基材 (Cu) と犠牲導体層 (Cu) を同時にエッティングすることで、所望とするパッケージ 10 (10a, 10b) を得ることができる。

## 【図面の簡単な説明】

## 【0095】

40

【図1】本発明の第1の実施形態に係る配線基板 (半導体パッケージ) の構成を示す断面図である。

【図2】図1の配線基板の製造方法の工程 (その1) を示す断面図である。

【図3】図2の製造工程に続く工程 (その2) を示す断面図である。

【図4】図3の製造工程に続く工程 (その3) を示す断面図である。

【図5】図1の配線基板 (半導体パッケージ) を用いて POP 構造を実現した場合の一構成例 (半導体装置) を示す断面図である。

【図6】図1の配線基板 (半導体パッケージ) を用いて POP 構造を実現した場合の他の構成例 (半導体装置) を示す断面図である。

【図7】本発明の第2の実施形態に係る配線基板 (半導体パッケージ) の構成を示す断面図である。

【図8】本発明の第3の実施形態に係る配線基板 (半導体パッケージ) の構成を示す断面

50

図である。

【符号の説明】

【0096】

10, 10a, 10b ... 配線基板 (半導体パッケージ)、

11, 14, 17, 20 ... 配線層、

12, 12a, 12b, 15, 18 ... 樹脂層 (絶縁層)、

13a, 13b, 16, 19 ... ビア、

21 ... ソルダレジスト層 (絶縁層)、

30, 30a ... 半導体装置、

31, 31a, 36, 41 ... 半導体素子 (チップ / 電子部品)、

32, 32a, 34, 37, 42 ... はんだ (バンプ)、

33, 33a, 43 ... アンダーフィル樹脂、

60, 60a ... 支持基材、

61, 62 ... レジスト層、

CM ... チップ搭載エリア、

CV ... キャビティ、

DP, DP1, DP2 ... 凹部、

P1, P2, P3, P4 ... パッド、

VH1, VH2, VH3, VH4 ... ビアホール。

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】