**【特許請求の範囲】****【請求項 1】**

第1導電型の半導体基板と、

前記半導体基板内に形成された前記第1導電型のボディ領域と、

前記半導体基板内において、前記ボディ領域に対して前記半導体基板の基板面に平行な第1方向に離間して形成された第2導電型のドリフト領域と、

前記ドリフト領域内に形成された、当該ドリフト領域より高濃度の前記第2導電型のドレイン領域と、

前記ボディ領域内に形成された、前記ドリフト領域より高濃度の前記第2導電型のソース領域と、

前記ボディ領域の底面に連結すると共に、前記ボディ領域から前記第1方向に延伸する複数の突出部を有し、前記突出部の各先端が前記ドリフト領域内に達するように形成された前記第1導電型の埋め込み拡散領域と、

前記ボディ領域の一部及び前記ドリフト領域の一部に共通にオーバーラップして形成されたゲート酸化膜と、

前記ゲート酸化膜の上層に形成されたゲート電極と、を備えることを特徴とする半導体装置。

**【請求項 2】**

前記半導体基板内に前記第2導電型のウェル領域を有し、

前記ボディ領域、前記ドリフト領域、及び前記埋め込み拡散領域が、いずれも前記ウェル領域内に形成されていることを特徴とする請求項1に記載の半導体装置。

**【請求項 3】**

第1導電型の半導体基板と、

前記半導体基板内に形成された第2導電型のウェル領域と、

前記ウェル領域内に形成された前記第1導電型のボディ領域と、

前記ウェル領域内において、前記ボディ領域に対して前記半導体基板の基板面に平行な第1方向に離間して形成された第2導電型のドリフト領域と、

前記ドリフト領域内に形成された、当該ドリフト領域より高濃度の前記第2導電型のドレイン領域と、

前記ボディ領域内に形成された、前記ドリフト領域より高濃度の前記第2導電型のソース領域と、

前記ボディ領域の底面に連結すると共に、前記ボディ領域から前記第1方向に延伸する複数の突出部を有し、前記突出部の各先端が前記ドリフト領域の下方位置に達するように形成された前記第1導電型の埋め込み拡散領域と、

前記ボディ領域の一部及び前記ドリフト領域の一部に共通にオーバーラップして形成されたゲート酸化膜と、

前記ゲート酸化膜の上層に形成されたゲート電極と、を備えることを特徴とする半導体装置。

**【請求項 4】**

前記ウェル領域が、前記ドリフト領域よりも低濃度であることを特徴とする請求項2又は3に記載の半導体装置。

**【請求項 5】**

前記埋め込み拡散領域が、前記ボディ領域の一部底面に離散的に連結する複数の部分で構成され、前記各部分が前記第1方向に延伸することで前記複数の突出部を形成する短冊型形状を構成することを特徴とする請求項1～4のいずれか1項に記載の半導体装置。

**【請求項 6】**

前記埋め込み拡散領域が、前記ボディ領域の全底面に連結し、且つ前記ボディ領域から前記第1方向に延伸する複数の突出部を有する櫛型形状を構成することを特徴とする請求項1～5のいずれか1項に記載の半導体装置。

**【請求項 7】**

10

20

30

40

50

前記埋め込み拡散領域の前記複数の突出部が、前記半導体基板面に平行な方向であって前記第1方向と直交する第2方向に等間隔のスリット幅を有して形成されており、

前記スリット幅が、下層に前記ゲート酸化膜が形成された位置に存する前記ゲート電極と前記ドレイン領域との前記第1方向の離間距離の1/2倍以下に設定されていることを特徴とする請求項1～6のいずれか1項に記載の半導体装置。

【請求項8】

前記埋め込み拡散領域の前記複数の突出部が、前記半導体基板面に平行な方向であって前記第1方向と直交する第2方向に等間隔のスリット幅を有して離間された状態で形成されており、

前記スリット幅が、前記埋め込み拡散領域の前記複数の突出部の前記第2方向の幅以下に設定されていることを特徴とする請求項1～7のいずれか1項に記載の半導体装置。 10

【請求項9】

前記ドリフト領域が、下層に前記ゲート酸化膜が形成された位置に存する前記ゲート電極の前記ドレイン領域側の端部であるゲートエッジの下方位置から、前記ドレイン領域に向かって不純物濃度が高濃度となるような濃度勾配を有して形成されることを特徴とする請求項1～8のいずれか1項に記載の半導体装置。

【請求項10】

前記埋め込み拡散領域は、前記ボディ領域の底面から前記ドレイン領域に近付くほど、前記半導体基板面に平行な方向であって前記第1方向と直交する第2方向に拡がりを有して形成されていることを特徴とする請求項1～9のいずれか1項に記載の半導体装置。 20

【請求項11】

前記埋め込み拡散領域が、前記半導体基板の基板面から1.5μm以上の深さ位置に形成されていることを特徴とする請求項1～10のいずれか1項に記載の半導体装置。

【請求項12】

第1導電型の半導体基板上に前記第1導電型の不純物イオンを注入してボディ領域を形成する工程と、前記半導体基板上の前記ボディ領域と離間した位置に第2導電型の不純物イオンを注入してドリフト領域を形成する工程とを順不同に行い、

その後に、前記半導体基板面に平行な方向で、前記ドリフト領域と前記ボディ領域の離間方向と直交する方向に複数のスリットが設けられたマスクパターンを用いて、前記ボディ領域の形成時よりも高い注入エネルギーで前記第1導電型の不純物イオンを注入することで、前記ボディ領域の底面に連結すると共に、前記ボディ領域から前記第1方向に延伸する複数の突出部の各先端が前記ドリフト領域に達するように埋め込み拡散領域を形成し、 30

その後に、前記ドリフト領域よりも高濃度の前記第2導電型の不純物イオンを、前記ボディ領域内及び前記ドリフト領域内に注入して、前記ボディ領域内にソース領域を、前記ドリフト領域内にドレイン領域をそれぞれ形成し、

その後に、前記半導体基板面を酸化して、少なくとも前記ボディ領域の一部及び前記ドリフト領域の一部に共通にオーバーラップするように前記ゲート酸化膜を形成した後、前記ゲート酸化膜の上層にゲート電極を形成することを特徴とする半導体装置の製造方法。

【請求項13】

前記ボディ領域及び前記ドリフト領域を形成する前に、前記半導体基板内に前記第2導電型の不純物イオンを注入して、前記ドリフト領域よりも低濃度のウェル領域を形成する工程を有し、

前記ボディ領域及び前記ドリフト領域は、前記ウェル領域内に形成されることを特徴とする請求項12に記載の半導体装置の製造方法。

【請求項14】

第1導電型の半導体基板内に第2導電型の不純物イオンを注入してウェル領域を形成した後、

前記ウェル領域内に前記第1導電型の不純物イオンを注入してボディ領域を形成する工程と、前記ウェル領域内の前記ボディ領域と離間した位置に第2導電型の不純物イオンを 50

注入してドリフト領域を形成する工程とを順不同に行い、

その後に、前記半導体基板の基板面に平行な方向で、前記ドリフト領域と前記ボディ領域の離間方向と直交する方向に複数のスリットが設けられたマスクパターンを用いて、前記ボディ領域の形成時よりも高い注入エネルギーで前記第1導電型の不純物イオンを注入することで、前記ボディ領域の底面に連結すると共に、前記ボディ領域から前記第1方向に延伸する複数の突出部の各先端が前記ドリフト領域の下方に達するように埋め込み拡散領域を形成し、

その後に、前記ドリフト領域よりも高濃度の前記第2導電型の不純物イオンを、前記ボディ領域内及び前記ドリフト領域内に注入して、前記ボディ領域内にソース領域を、前記ドリフト領域内にドレイン領域をそれぞれ形成し、

その後に、前記半導体基板面を酸化して、少なくとも前記ボディ領域の一部及び前記ドリフト領域の一部に共通にオーバーラップするように前記ゲート酸化膜を形成した後、前記ゲート酸化膜の上層にゲート電極を形成することを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特にLDMOSトランジスタ（ラテラル二重拡散MOSトランジスタ）及びその製造方法に関する。

【背景技術】

【0002】

LDMOSトランジスタは、スイッチング速度が速い、電圧駆動系のため使いやすい等の特徴を有しており、この特徴を活かしてスイッチングレギュレータや各種ドライバ、DC-DCコンバータ等に用いられており、現在のパワー・高耐圧分野のキーデバイスとなっている。

【0003】

一般的にLDMOSトランジスタの性能は、そのオフ時の耐圧（降伏耐圧）とオン抵抗とで示される。しかし、これらは通常、トレードオフの関係にあり、高い耐圧と低いオン抵抗を両立させることは難しい。そのため、この両立をいかにして実現するかという点において、長年開発が行われている。

【0004】

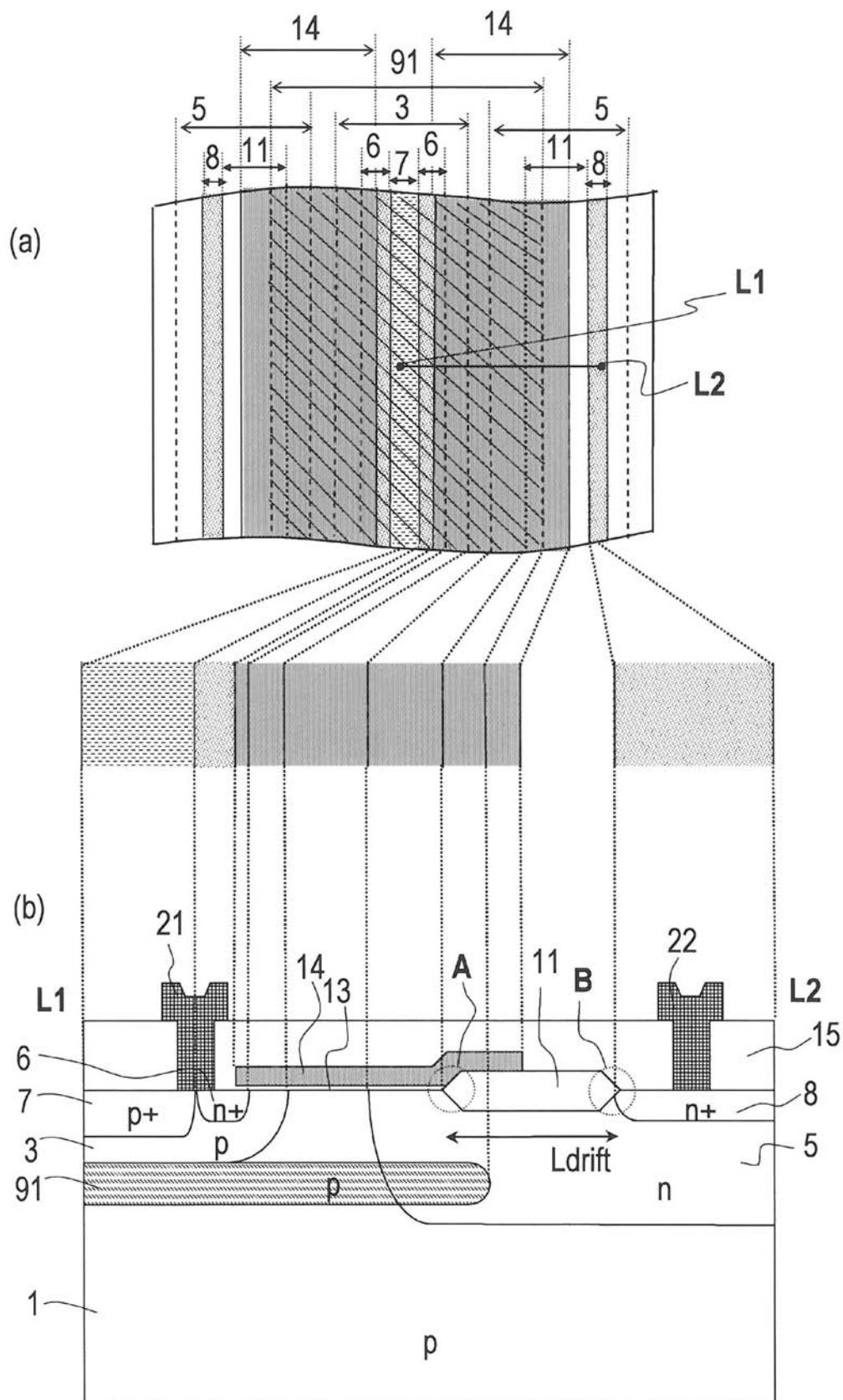

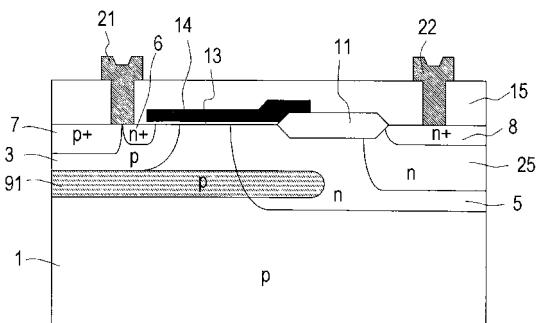

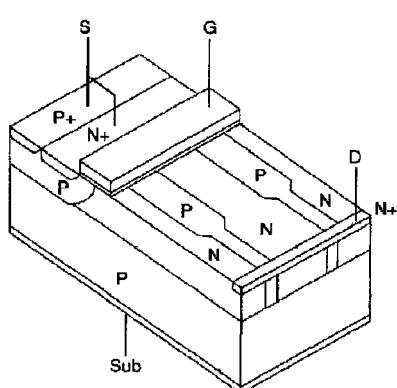

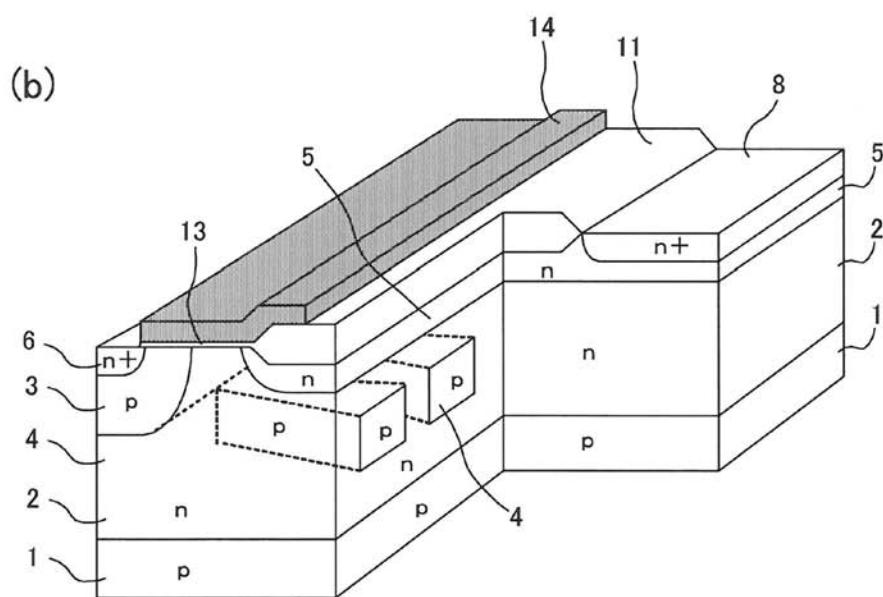

以下、図17を参照しながら、特許文献1に記載の従来のLDMOSトランジスタについて説明する。図17は、P型半導体基板上に形成されたNチャネルLDMOSトランジスタを示す概略構造図である。（a）が上面視概略図、（b）が断面概略図である。なお、（b）の断面概略図は、（a）の表示領域のうち線L1-L2で切断した部分の断面を示している。また（a）の上面視概略図では、（b）に図示されている要素のうち、層間絶縁膜15、ソース電極21、及びドレイン電極22の図示を省略している。

【0005】

図17に示すように、従来のNチャネルLDMOSトランジスタは、P型半導体基板1の表面に形成されたP型ボディ領域3の底面に連続するように、P型の埋め込み拡散領域91が高エネルギー注入によって形成されている。P型半導体基板1の表面には、P型ボディ領域3と離間して低濃度N型ドリフト領域5が形成されており、P型埋め込み拡散領域91は、先端がこのN型ドリフト領域5内に到達するように埋め込み形成されている。図17（a）では、このP型埋め込み拡散領域91が形成されている領域を右下がり斜線で表記している。

【0006】

P型ボディ領域3内の表面には、高濃度N型のソース領域6及び高濃度P型のボディコンタクト領域7が形成されている。N型ドリフト領域5内の表面の一部領域には高濃度N型のドレイン領域8が形成されている。なお、図17では、ドレイン領域8は、ドリフト領域5内において、当該ドリフト領域5上に形成されたフィールド酸化膜11を介してソース領域6とは反対側に形成されている。

10

20

30

40

50

## 【0007】

半導体基板1上には、ゲート酸化膜13を介してゲート電極14が形成されており、このゲート電極14は、P型ボディ領域3の一部及びN型ドリフト領域5の一部に共通にオーバーラップするように形成されている。ゲート電極14の一部は、フィールド酸化膜11上に乗り上げるように形成されている。そして、このゲート電極14を含む半導体基板1の全面を覆うように層間絶縁膜15が形成されている。

## 【0008】

そして、層間絶縁膜15を貫通し、N型ソース領域6とP型ボディコンタクト領域7に接触するようにソース電極21が形成されている。同様に、層間絶縁膜15を貫通し、N型ドレイン領域8に接触するようにドレイン電極22が形成されている。ソース電極21によって、N型ソース領域6とP型ボディ領域3は電気的に同電位となる。

10

## 【0009】

NチャネルLDMOSトランジスタにおいて、オフ時の耐圧を測定する際には、ソース電極21及びゲート電極14をGND電位に設定し、ドレイン電極22にプラス電位を印加する。このようにして、ドレイン-ソース間に逆バイアス電圧が印加されると、ある電圧において空乏層内の電界が臨界電界に達し、なだれ降伏が生じて急激にドレイン-ソース間に電流が流れ始める。このときの印加電圧がトランジスタの耐圧値である。

## 【0010】

一般的に、LDMOSトランジスタにおいては、ドレイン-ソース間に逆バイアスが印加されると、下層にゲート酸化膜が形成された位置に存するゲート電極のドレイン領域側の端部であるゲートエッジ(図17中の領域A)に電界が集中し、耐圧が低下する要因となる。従って、耐圧を上げるためにには、このゲートエッジの電界を緩和させることが重要となる。また、ゲートエッジ付近に電界が集中すると、多少の電荷をゲート酸化膜13に残すことによる信頼性上の問題を引き起こすことがあるため、ゲートエッジの電界を緩和させることは、LDMOSトランジスタの信頼性を向上させる点でも重要である。

20

## 【0011】

そこで、このゲートエッジの電界を緩和させるために、特許文献1に記載の従来のLDMOSトランジスタにおいては、上述したように、P型ボディ領域3の全ての底面に連続するようにP型埋め込み拡散領域91を設け、このP型埋め込み拡散領域91をN型ドリフト領域5内にまで埋め込まれるように、高エネルギー注入により形成する。この際、P型埋め込み拡散領域91はN型ドリフト領域5よりも高濃度で形成される。

30

## 【0012】

図17に示すような構造の下で、ドレイン-ソース間に逆バイアスを印加すると、空乏層はP型埋め込み拡散領域91とN型ドリフト領域5との接合界面から伸びるが、前述の通り、P型埋め込み拡散領域91はN型ドリフト領域5よりも高濃度で形成されているため、空乏層はN型ドリフト領域5の方に容易に伸び、これによってN型ドリフト領域5の全域が実質的に空乏化される。その結果、ゲートエッジ(領域A)を含む表面近傍の電界を十分に緩和できる。これにより、同一の耐圧を確保する場合、N型ドリフト領域5の濃度をより高濃度に設定することができるため、デバイスの耐圧とオン抵抗とのトレードオフ関係を大幅に改善できる。

40

## 【先行技術文献】

## 【特許文献】

## 【0013】

## 【特許文献1】特開2004-22769号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0014】

LDMOSトランジスタを設計するに際しては、一般的に、回路上の使用条件に合わせて、オフ耐圧を確保しつつ、且つオン抵抗を最小化するように、適切なN型ドリフト領域5の濃度並びにドリフト長(図17中のLdrift)が設定される。

50

## 【0015】

そして、回路上の使用条件により更なる高耐圧化が要望された場合、デバイスの基本的な構造は変更せず、N型ドリフト領域5の濃度を低減させたり、ドリフト長L<sub>drift</sub>を大きくする等、所望の特性を満たすように各パラメータを調整することで対応するのが通常である。

## 【0016】

しかしながら、上記特許文献1に記載のLDMOSトランジスタにおいて、更なる高耐圧化を図る場合、以下に示すような課題が生じる。

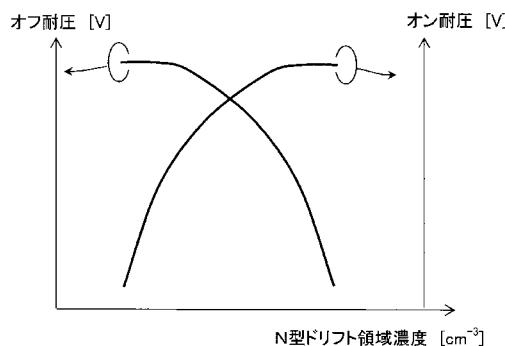

## 【0017】

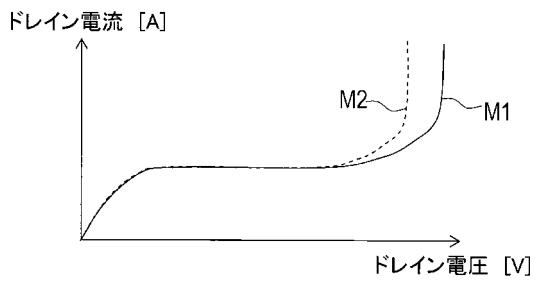

オン抵抗を低く維持しながら更なる高耐圧化を図るには、N型ドリフト領域5の濃度を低くして、ドリフト長L<sub>drift</sub>をできる限り小さく設定する必要がある。しかしながら、ドリフト長L<sub>drift</sub>を小さくすることにより、ゲートオン時の耐圧（以降、「オン耐圧」と表記する）は低下する。つまり、図18に示すようにオフ耐圧とオン耐圧は、N型ドリフト領域5の濃度に対してトレードオフの関係となる。つまり、オフ耐圧を増大させるためには、N型ドリフト濃度を小さくする必要があるが、一方でこれによりオン耐圧が低下してしまう。これは、オフ耐圧の降伏電圧時とオン耐圧の降伏電圧時で、両者の電界集中箇所が異なることに起因するが、以下、図面を用いて詳細に説明する。

10

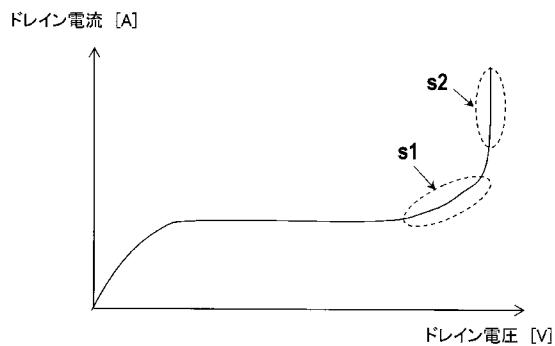

## 【0018】

まず、オン耐圧について図17と図19を参照して説明する。図19に、ゲートオン時にドレイン電圧を上昇させた場合のドレイン電圧に対するドレイン電流の関係を示す。ゲートオン時にドレイン電圧がある一定以上までに上昇させた場合、ある一定箇所に電界が集中するが、その電界が臨界電界を超えるとアバランシェブレークダウンを起こし、ドレイン電流が増加し始める（図19のs1）。このドレイン電流は、P型ボディ領域3を流れ、ソース電極21に回収される。

20

## 【0019】

そして、更にドレイン電圧を上昇させると、P型ボディ領域3内の抵抗とドレイン電流（アバランシェ電流）の積が約0.6Vを超えると、N型ドリフト領域5とP型ボディ領域3とN型ソース領域6から構成される寄生NPNトランジスタが動作する。この動作により、ドレイン電圧が寄生NPNトランジスタを介してN型ソース領域6に接続された接地線へと流れる電流経路が形成され、急激にドレイン電流が増大する（図19のs2）。このドレイン電流の急激な上昇により、LDMOSトランジスタ内に大きなジューク熱が発生し、結果的にデバイス破壊に至る場合がある。このデバイス破壊に至らない範囲内の印加ドレイン電圧の最大値がオン耐圧である。つまり、LDMOSトランジスタの耐圧を高めるためには、オフ耐圧だけではなくオン耐圧も向上させる必要がある。

30

## 【0020】

オン耐圧の降伏電圧時の電界集中箇所は、図17に示すように、オフ耐圧の降伏電圧時の電界集中箇所のゲートエッジ（図中の領域A）とは異なり、通常、N型ドレイン領域8のソース側エッジ（図中の領域B）となる。これは、ゲートオン時にはドレイン電流が流れているため、ゲートオフ時と比較してポテンシャル分布がドレイン領域8側にシフトし、その結果リーチスルーバイオードによる電界集中が起こるためである。

40

## 【0021】

上述したように、オフ耐圧を向上させるためにはN型ドリフト領域5の濃度を低下させる必要がある。しかしながら、N型ドリフト領域5の濃度を低下させると、図18に示すようにオン耐圧が低下してしまい、結果的に十分な高耐圧化が実現できない。これは、N型ドリフト領域5の濃度を低下させると、ゲートオン時のポテンシャル分布がドレイン領域8側にシフトし、リーチスルーバイオードによる電界集中が更に促進されるためである。この電界集中を緩和させるためには、N型ドリフト領域5の濃度を大きくする必要があるが、この場合には、図18に示すようにオフ耐圧が低下してしまう。

## 【0022】

また、N型ドリフト領域5の濃度を大きくする別の手段として、図20に示すように、

50

N型ドリフト領域5よりも高濃度かつN型ドレイン領域8よりも低濃度の追加N型ドリフト領域25を挿入することも考えられる。しかし、オフ耐圧を低下させずに追加N型ドリフト領域25を形成するためには、通常、ドリフト長の調整が必要となり、製造プロセスを複雑化させる。更に、マスク工程を1枚追加することを余儀なくされ、製造コストが増加するという問題もある。

【0023】

また、オン耐圧時のリーチスルーバイオードによる電界集中を緩和させる別の手段として、図17のドリフト長L<sub>drift</sub>を大きくする方法も考えられるが、この方法によればオン抵抗の増大を招いてしまう。

【0024】

本発明は、上記も問題を解決すべく、LDMOSトランジスタにおいて、オフ耐圧、オン耐圧、オン抵抗の相互のトレードオフ関係を改善させることにより、オン抵抗を増大させることなく、高耐圧化を実現させることができ半導体装置、及びその製造方法を提供することをその目的とする。

【課題を解決するための手段】

【0025】

上記目的を達成するため、本発明の半導体装置は、

第1導電型の半導体基板と、

前記半導体基板内に形成された前記第1導電型のボディ領域と、

前記半導体基板内において、前記ボディ領域に対して前記半導体基板の基板面に平行な第1方向に離間して形成された第2導電型のドリフト領域と、

前記ドリフト領域内に形成された、当該ドリフト領域より高濃度の前記第2導電型のドレイン領域と、

前記ボディ領域内に形成された、前記ドリフト領域より高濃度の前記第2導電型のソース領域と、

前記ボディ領域の底面に連結すると共に、前記ボディ領域から前記第1方向に延伸する複数の突出部を有し、前記突出部の各先端が前記ドリフト領域内に達するように形成された前記第1導電型の埋め込み拡散領域と、

前記ボディ領域の一部及び前記ドリフト領域の一部に共通にオーバーラップして形成されたゲート酸化膜と、

前記ゲート酸化膜の上層に形成されたゲート電極と、を備えることを特徴とする。

【0026】

このような構成としたとき、本発明の半導体装置をゲートオンさせ、ドレイン電圧を上昇させると、埋め込み拡散領域が形成されている外側位置におけるドレイン領域のソース領域側エッジ近傍に電界集中が生じる。ここで、本発明の半導体装置が備える埋め込み拡散領域は、ボディ領域からドリフト領域に向かう複数の突出部を有する構成であり、言い換えれば、ドリフト領域内並びにボディ領域とドリフト領域の間で離散的に形成されている。これにより、前記の電界集中箇所も離散的に形成されるため、ドレイン電流は、電界集中箇所を通る電流経路と、電界集中箇所を通らない電流経路に分かれて流れこととなる。これに対し、埋め込み拡散領域がボディ領域の全底面に連結し、且つその先端がドリフト領域内に到達するように、全面的に埋め込まれている従来構成の場合には、ドレイン電流は、全て電界集中箇所を通る電流経路を介して流れこととなる。従って、本発明の半導体装置によれば、従来構成よりも、ドレイン電流（アバランシェ電流）を少なくすることができ、オン耐圧を向上させることができとなる。

【0027】

そして、埋め込み拡散領域をボディ領域の底面に連結させ、その先端をドリフト領域内に達するように形成させていため、埋め込み拡散領域をボディ領域の全底面に連結し、且つその先端がドリフト領域内に到達するように全面的に埋め込んでいる従来構成と同様に、低オン抵抗や高オフ耐圧を確保できる。

【0028】

10

20

30

40

50

つまり、本発明の半導体装置によれば、低オン抵抗及び高オフ耐圧を維持しながらも、更にオン耐圧の向上を実現することができ、これら三者のトレードオフ関係が改善される。

【0029】

なお、上記構成において、前記半導体基板内に前記第2導電型のウェル領域を有し、前記ボディ領域、前記ドリフト領域、及び前記埋め込み拡散領域が、いずれも前記ウェル領域内に形成されるものとしても良い。

【0030】

また、本発明の半導体装置は、

第1導電型の半導体基板と、

10

前記半導体基板内に形成された第2導電型のウェル領域と、

前記ウェル領域内に形成された前記第1導電型のボディ領域と、

前記ウェル領域内において、前記ボディ領域に対して前記半導体基板の基板面に平行な第1方向に離間して形成された第2導電型のドリフト領域と、

前記ドリフト領域内に形成された、当該ドリフト領域より高濃度の前記第2導電型のドレイン領域と、

前記ボディ領域内に形成された、前記ドリフト領域より高濃度の前記第2導電型のソース領域と、

前記ボディ領域の底面に連結すると共に、前記ボディ領域から前記第1方向に延伸する複数の突出部を有し、前記突出部の各先端が前記ドリフト領域の下方位置に達するように形成された前記第1導電型の埋め込み拡散領域と、

前記ボディ領域の一部及び前記ドリフト領域の一部に共通にオーバーラップして形成されたゲート酸化膜と、

前記ゲート酸化膜の上層に形成されたゲート電極と、を備えることを別の特徴とする。

【0031】

このような構成とした場合でも、埋め込み拡散領域がドリフト領域内並びにボディ領域とドリフト領域の間で離散的に形成されることで、前記電界集中箇所も離散的に形成されるため、上記の構成と同様にオン耐圧を向上させることができが可能となる。更に、本構成の場合、第2導電型のウェル領域を設けることにより、第1導電型の半導体基板と第1導電型のボディ領域の間に第2導電型のウェル領域が位置するため、ソース領域が半導体基板に対して電気的に分離され、これによってソース電極が半導体基板に対して高い耐圧を要求される場合でも使用することができるという効果もある。

30

【0032】

なお、上記の構成では、前記ドリフト領域が前記埋め込み拡散領域よりも浅く形成されることとなる。これにより、ドリフト領域の不純物濃度の、埋め込み拡散領域の実効的濃度への影響を小さくすることができるため、所望の電気的特性を得るために必要な設計が簡素化される。更に、製造プロセス時においてドリフト領域の濃度にバラツキが生じた場合でも、安定した電気的特性を示す半導体装置の実現が可能となる。

【0033】

また、上記の構成において、埋め込み拡散領域は、ドリフト領域よりも高濃度とするのが好適である。

40

【0034】

また、上記の構成において、前記ウェル領域を前記ドリフト領域よりも低濃度とするのも好適である。

【0035】

このように構成することで、ドリフト領域については、濃度を高く設定してオン抵抗を低減させる一方、ウェルをドリフト領域よりも低濃度とすることでオフ耐圧を低下させないようにすることができる。

【0036】

更に、上記構成において、前記埋め込み拡散領域を、前記ボディ領域の全底面に連結し

50

、且つ前記ボディ領域から前記第1方向に延伸する複数の突出部を有する櫛型形状としても構わないし、前記ボディ領域の一部底面に離散的に連結する複数の部分で構成され、前記各部分が前記第1方向に延伸することで前記複数の突出部を形成する短冊型形状としても構わない。

【0037】

これらの構成であっても、埋め込み拡散領域がドリフト領域内並びにボディ領域とドリフト領域の間で離散的に形成されるため、オン耐圧を向上させる効果が得られる。

【0038】

また、上記の構成において、前記埋め込み拡散領域の前記複数の突出部を、前記半導体基板面に平行な方向であって前記第1方向と直交する第2方向に等間隔のスリット幅を有して形成し、前記スリット幅を、下層に前記ゲート酸化膜が形成された位置に存する前記ゲート電極と前記ドレイン領域との前記第1方向の離間距離の1/2倍以下とするのが好ましい。

10

【0039】

このような条件にすることで、埋め込み拡散領域をボディ領域の全底面に連結し、且つその先端がドリフト領域内に到達するように全面的に埋め込んでいる従来構成とほぼ同等のオフ耐圧を実現することができる。

【0040】

また、上記の構成において、前記スリット幅を前記埋め込み拡散領域の前記複数の突出部の前記第2方向の幅以下とするのも好ましい。このような条件にすることで、オン抵抗を十分小さくしながらも高いオフ耐圧を実現することができる。

20

【0041】

また、上記の構成において、前記ドリフト領域を、下層に前記ゲート酸化膜が形成された位置に存する前記ゲート電極の前記ドレイン領域側の端部であるゲートエッジの下方位置から、前記ドレイン領域に向かって不純物濃度が高濃度となるような濃度勾配を有して形成するのも好適である。

【0042】

このようにすることで、最も電界の集中しやすいゲートエッジ近傍のドリフト領域の濃度は低くなり、ゲートオフ時の電界緩和が促進される。更に、ゲートオン時では、最も電界の集中しやすいドレイン領域近傍の濃度が高いため、リーチスルーバイオードによる電界集中を回避することができる。これにより、オフ耐圧とオン耐圧のトレードオフ関係がより改善される。

30

【0043】

また、上記の構成において、前記埋め込み拡散領域を、前記ボディ領域の底面から前記ドレイン領域に近付くほど、前記半導体基板面に平行な方向であって前記第1方向と直交する第2方向に拡がりを有して形成するのも好適である。

【0044】

また、上記の構成において、前記埋め込み拡散領域を、前記半導体基板の基板面から1.5 μm以上の深さ位置に形成するのも好適である。

40

【0045】

このように構成することで、オン抵抗を更に低下させることが可能である。

【0046】

また、本発明の半導体装置の製造方法は、

第1導電型の半導体基板上に前記第1導電型の不純物イオンを注入してボディ領域を形成する工程と、前記半導体基板上の前記ボディ領域と離間した位置に第2導電型の不純物イオンを注入してドリフト領域を形成する工程とを順不同に行い、

その後に、前記半導体基板面に平行な方向で、前記ドリフト領域と前記ボディ領域の離間方向と直交する方向に複数のスリットが設けられたマスクパターンを用いて、前記ボディ領域の形成時よりも高い注入エネルギーで前記第1導電型の不純物イオンを注入することで、前記ボディ領域の底面に連結すると共に、前記ボディ領域から前記第1方向に延伸

50

する複数の突出部の各先端が前記ドリフト領域に達するように埋め込み拡散領域を形成し、

その後に、前記ドリフト領域よりも高濃度の前記第2導電型の不純物イオンを、前記ボディ領域内及び前記ドリフト領域内に注入して、前記ボディ領域内にソース領域を、前記ドリフト領域内にドレイン領域をそれぞれ形成し、

その後に、前記半導体基板面を酸化して、少なくとも前記ボディ領域の一部及び前記ドリフト領域の一部に共通にオーバーラップするように前記ゲート酸化膜を形成した後、前記ゲート酸化膜の上層にゲート電極を形成することを特徴とする。

#### 【0047】

なお、上記製法において、

前記ボディ領域及び前記ドリフト領域を形成する前に、前記半導体基板内に前記第2導電型の不純物イオンを注入して、前記ドリフト領域よりも低濃度のウェル領域を形成する工程を有し、

前記ボディ領域及び前記ドリフト領域を、前記ウェル領域内に形成するものとしても構わない。

#### 【0048】

また、本発明の半導体装置の製造方法は、

第1導電型の半導体基板内に第2導電型の不純物イオンを注入してウェル領域を形成した後、

前記ウェル領域内に前記第1導電型の不純物イオンを注入してボディ領域を形成する工程と、前記ウェル領域内の前記ボディ領域と離間した位置に第2導電型の不純物イオンを注入してドリフト領域を形成する工程とを順不同に行い、

その後に、前記半導体基板の基板面に平行な方向で、前記ドリフト領域と前記ボディ領域の離間方向と直交する方向に複数のスリットが設けられたマスクパターンを用いて、前記ボディ領域の形成時よりも高い注入エネルギーで前記第1導電型の不純物イオンを注入することで、前記ボディ領域の底面に連結すると共に、前記ボディ領域から前記第1方向に延伸する複数の突出部の各先端が前記ドリフト領域の下方に達するように埋め込み拡散領域を形成し、

その後に、前記ドリフト領域よりも高濃度の前記第2導電型の不純物イオンを、前記ボディ領域内及び前記ドリフト領域内に注入して、前記ボディ領域内にソース領域を、前記ドリフト領域内にドレイン領域をそれぞれ形成し、

その後に、前記半導体基板面を酸化して、少なくとも前記ボディ領域の一部及び前記ドリフト領域の一部に共通にオーバーラップするように前記ゲート酸化膜を形成した後、前記ゲート酸化膜の上層にゲート電極を形成することを別の特徴とする。

#### 【0049】

これらの製造方法によれば、オフ耐圧、オン耐圧、オン抵抗の相互のトレードオフ関係が改善され、低オン抵抗、高オフ耐圧、高オン耐圧の半導体装置を実現することができる。

#### 【発明の効果】

#### 【0050】

本発明の半導体装置によれば、オフ耐圧、オン耐圧、オン抵抗の相互のトレードオフ関係が改善され、オン抵抗を増大させることなく、高耐圧化を実現することができる。また、本発明の半導体装置の製造方法によれば、低オン抵抗、高耐圧の半導体装置を複雑な工程を有することなく製造することができる。

#### 【図面の簡単な説明】

#### 【0051】

【図1】本発明のNチャネル型LDMOSトランジスタの概略構造図

【図2】本発明のNチャネル型LDMOSトランジスタの概略構造図

【図3】本発明のNチャネル型LDMOSトランジスタの概略構造図に抵抗成分を模式的に付加したもの

10

20

30

40

50

- 【図4】埋め込み拡散領域の形成間隔とオフ耐圧の関係を説明するための図

- 【図5】埋め込み拡散領域の存在の有無とポテンシャル分布の関係を説明するための図

- 【図6】埋め込み拡散領域の存在の有無と空乏層の伸びの関係を説明するための図

- 【図7】埋め込み拡散領域の形成パターンと電界集中箇所の関係を説明するための図

- 【図8】埋め込み拡散領域の形成パターンとアバランシェ電流の関係を説明するためのグラフ

- 【図9】第1実施形態のNチャネル型LDMOSトランジスタの製造方法を示す工程断面図

- 【図10】第2実施形態のNチャネル型LDMOSトランジスタの概略構造図

- 【図11】埋め込み拡散領域幅とスリット幅との比と、オン抵抗比及びオフ耐圧比との関係を示すグラフ 10

- 【図12】埋め込み拡散領域の注入深さとオン抵抗の関係を示すグラフ

- 【図13】第2実施形態のNチャネル型LDMOSトランジスタの製造方法を示す工程断面図

- 【図14】別実施形態のNチャネル型LDMOSトランジスタの概略構造図

- 【図15】別実施形態のNチャネル型LDMOSトランジスタの概略構造図

- 【図16】別実施形態のNチャネル型LDMOSトランジスタの概略構造図

- 【図17】従来のNチャネル型LDMOSトランジスタの概略構造図

- 【図18】オフ耐圧とオン耐圧のトレードオフ関係を示す図

- 【図19】ゲートオン時のドレイン電圧とドレイン電流の関係を示す図。 20

- 【図20】オン耐圧を向上させた従来のNチャネル型LDMOSトランジスタの概略断面図

- 【図21】従来のマルチリサーフ構造のLDMOSトランジスタの概略構造図

- 【発明を実施するための形態】

- 【0052】

- 〔第1実施形態〕

- 本発明の半導体装置の第1実施形態につき、図1～図9の各図を参照しながら説明する。なお、以下の各図において、図17と同一の構成要素については同一の符号を付し、その説明を適宜省略する。 30

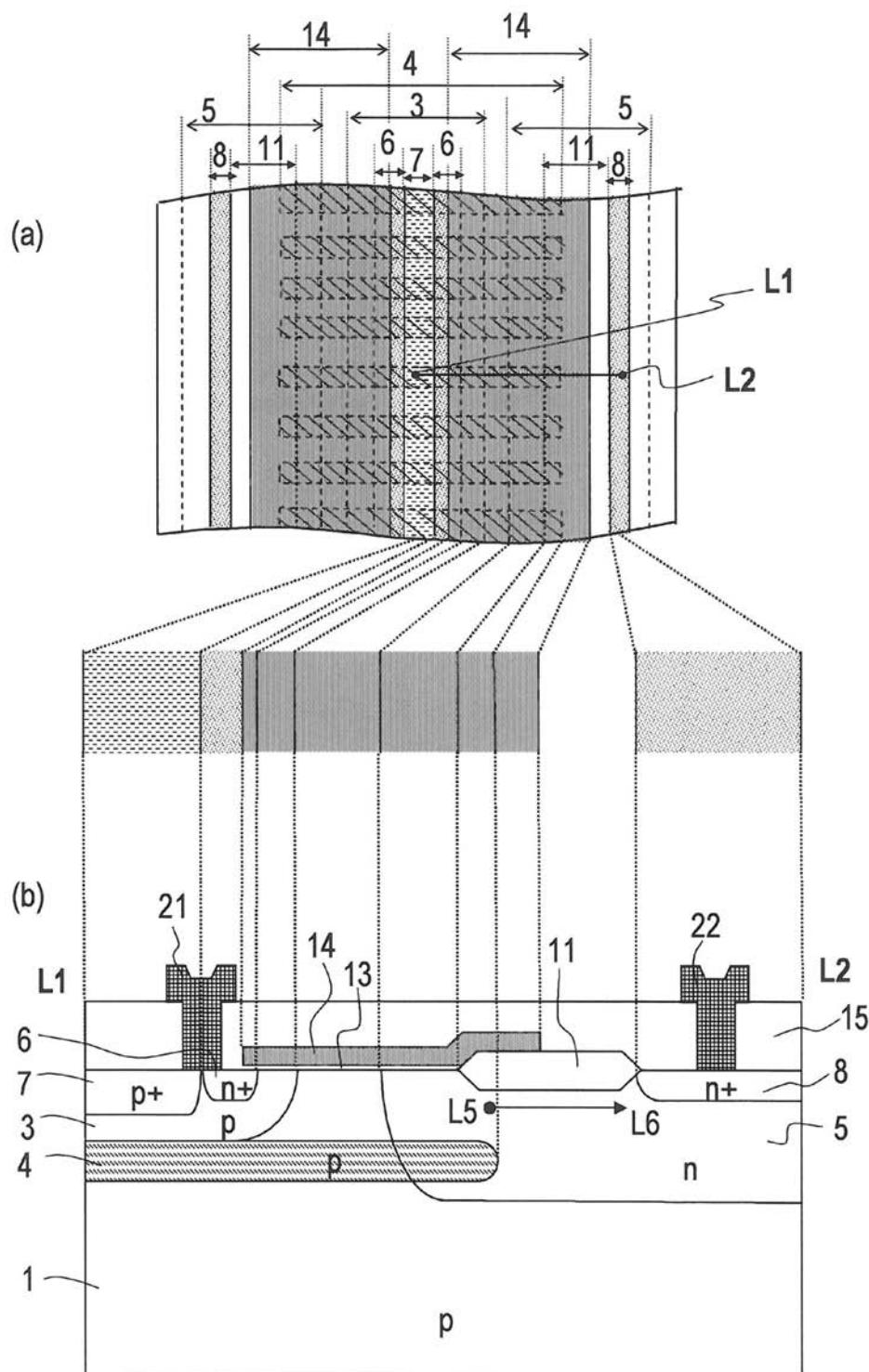

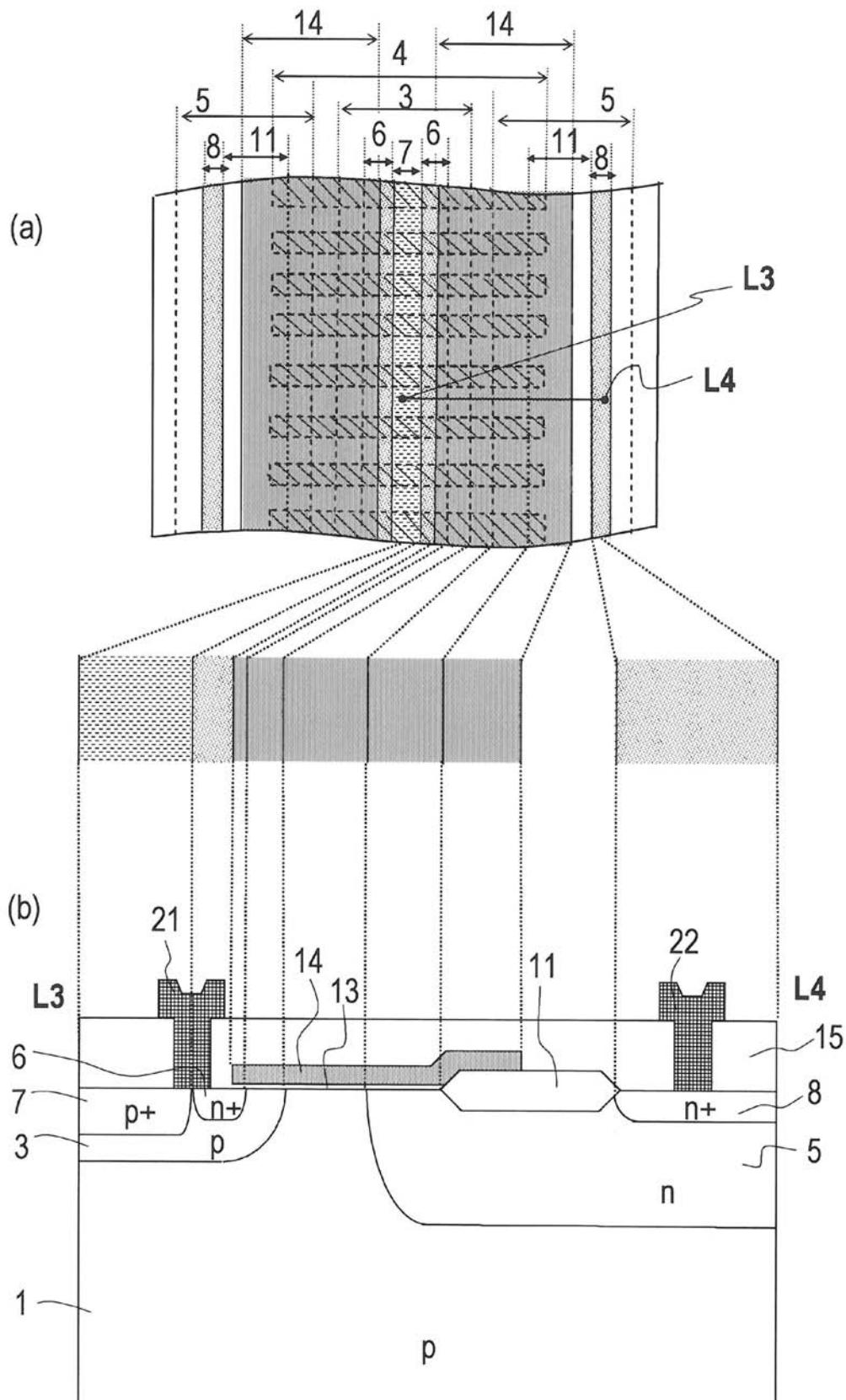

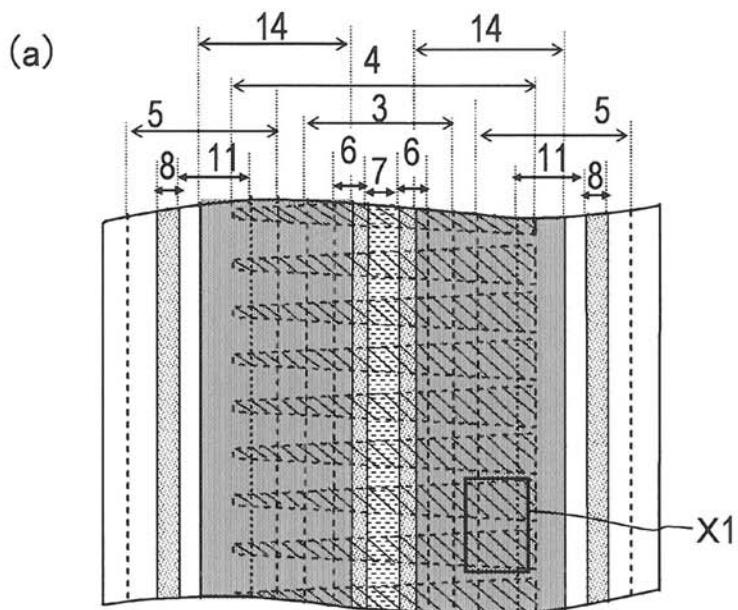

- 【0053】

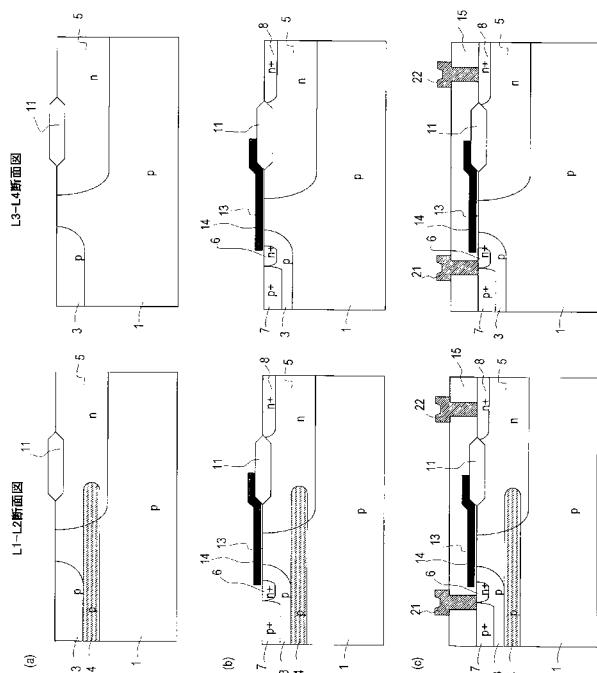

- 図1及び図2は、本実施形態の半導体装置であるNチャネルLDMOSトランジスタの概略構造図を示している。図1(a)及び図2(a)は上面視概略図であり、両者は全く同じ図である。図1(b)及び図2(b)は断面概略図であるが、それぞれは切断位置が異なっており、図1(b)は、線L1-L2で切断した部分の断面を、図2(b)は、線L3-L4で切断した部分の断面を示している。

- 【0054】

- なお、これらの図はあくまで模式的に示されたものであり、実際の寸法比と図面上の寸法比は必ずしも一致するものではない。以下の各図においても同様である。

- 【0055】

- 本実施形態のNチャネルLDMOSトランジスタは、図17に示す構造と比較して、P型埋め込み拡散領域91の代わりに、その埋め込み形状を異ならせたP型埋め込み拡散領域4を備えている点が異なる。なお、図1(a)、図2(a)では、P型埋め込み拡散領域4の形成領域を右下がりの斜線で示している。 40

- 【0056】

- 図17に示すP型埋め込み拡散領域91は、P型ボディ領域3の全ての底面に連続し、且つ、その先端がN型ドリフト領域5内に到達するように全面的に埋め込み形成されていた。すなわち、P型埋め込み拡散領域91は、その先端が到達するN型ドリフト領域5内の位置からP型ボディ領域3の底面にかけて、全面的に形成されていた。

- 【0057】

- これに対し、図1及び図2に示すP型埋め込み拡散領域4は、P型ボディ領域3の全て

の底面に連続するように設けるのではなく、P型ボディ領域3の一部領域の底面には連続して設けられる一方、他の領域の底面には設けられていない。つまり、P型埋め込み拡散領域4は、P型ボディ領域3の一部底面に離散的に連結する複数の部分で構成される。そして、これらの各部分がP型ボディ領域3からN型ドリフト領域5に向かう方向に延伸し、その先端部がN型ドリフト領域5内に到達している。すなわち、P型埋め込み拡散領域4は、P型ボディ領域3からN型ドリフト領域5に向かう方向に延伸する短冊型形状を構成している。図1及び図2は、その一例として、P型埋め込み拡散領域4を一定間隔で平面的に離間して形成した場合を示している。そして、図1に示すL1-L2線は、P型ボディ領域3の底面にP型埋め込み拡散領域4が形成されている箇所に対応し、図2に示すL3-L4線は、P型ボディ領域3の底面にP型埋め込み拡散領域4が形成されていない箇所に対応している。

10

## 【0058】

このような構造とすることで、図17に示す従来構造よりも、オフ耐圧、オン耐圧、オン抵抗の相互のトレードオフ関係を改善させることができ、これによってオン抵抗を増大させることなく、高耐圧化を実現させることが可能となる。この点につき、以下説明する。

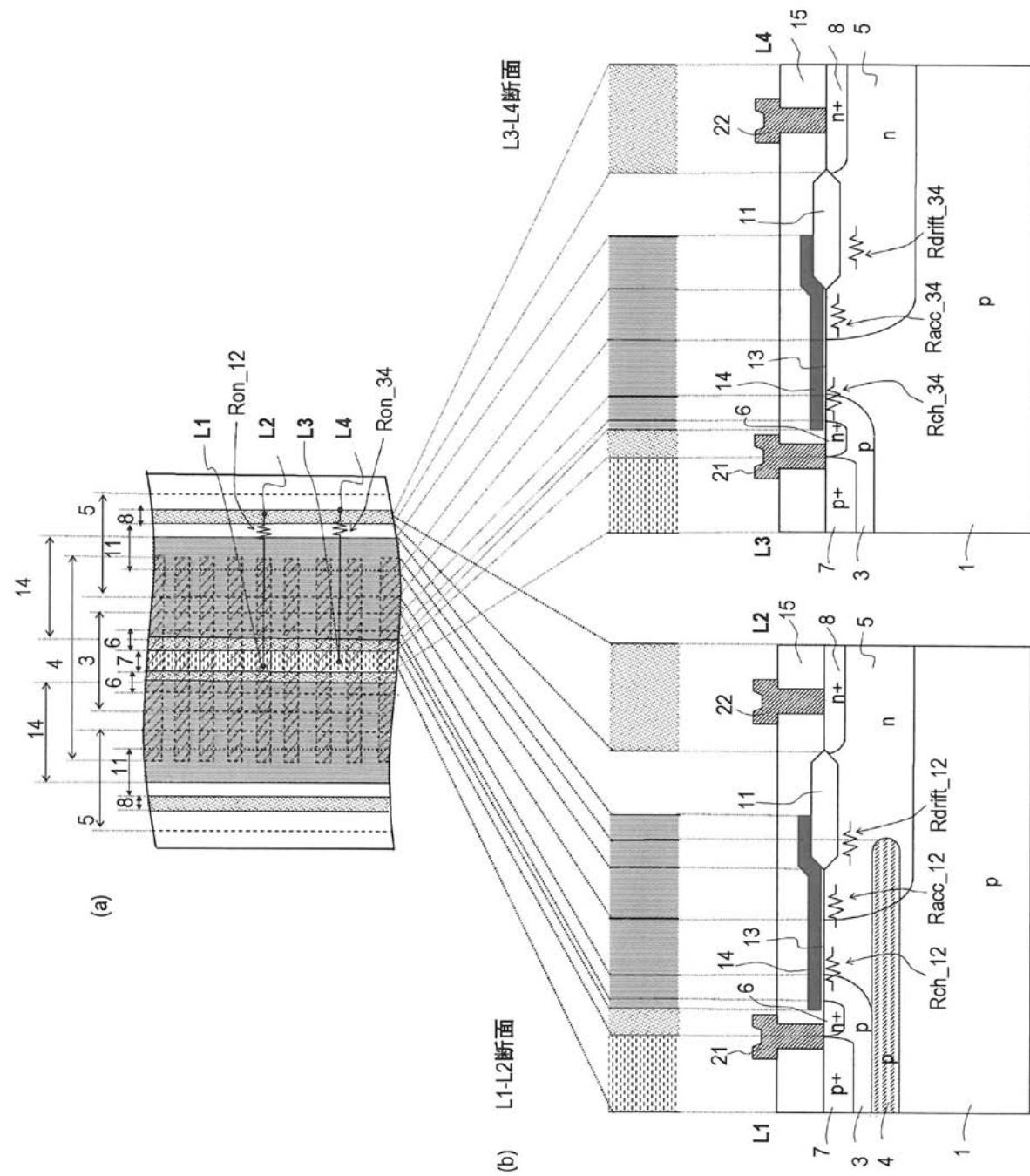

## 【0059】

図3は、図1及び図2を一つの図にまとめ、更に各図内に、オン抵抗、チャネル抵抗等の抵抗成分を付加したものである。本実施形態のNチャネルLD MOSトランジスタのオン抵抗Ronは、P型ボディ領域3の底面に連続してP型埋め込み拡散領域4が形成されているL1-L2線で切断された箇所におけるオン抵抗Ron\_12と、P型ボディ領域3の底面にP型埋め込み拡散領域4が形成されないL3-L4線で切断された箇所におけるオン抵抗Ron\_34との並列接続で表わされ、以下の数1によって示される。

20

(数1)

$$1/Ron = 1/Ron_{12} + 1/Ron_{34}$$

## 【0060】

また、オン抵抗Ronは、電子が誘起されたMOSFETのチャネル抵抗をRch、ゲートドレインオーバーラップ領域において電子が蓄積された領域の抵抗をRacc、薄くドープされたドリフト領域5内の抵抗をRdriftとすれば、以下の数2によって示される。

30

(数2)

$$Ron = Rch + Racc + Rdrift$$

である。

## 【0061】

つまり、図3に示すように、(L1-L2)の経路におけるオン抵抗Ron\_12と、(L3-L4)の経路におけるオン抵抗Ron\_34については、それぞれ、下記数3、数4によって表わすことができる。なお、Rch\_12, Racc\_12, Rdrift\_12は、(L1-L2)の経路におけるRch、Racc、Rdriftを表わし、Rch\_34, Racc\_34, Rdrift\_34は、(L3-L4)の経路におけるRch、Racc、Rdriftを表わす。

(数3)

$$Ron_{12} = Rch_{12} + Racc_{12} + Rdrift_{12}$$

40

(数4)

$$Ron_{34} = Rch_{34} + Racc_{34} + Rdrift_{34}$$

## 【0062】

ここで、(L1-L2)の断面構造、及び(L3-L4)の断面構造は、P型埋め込み拡散領域4の有無を除いては同一構造であるため、Rch及びRaccは両者で等しくなり、この結果、Rch\_12 = Rch\_34、及びRacc\_12 = Racc\_34の関係を満たす。

## 【0063】

一方、N型ドリフト領域5内の抵抗Rdriftに関しては、(L1-L2)の断面構造においては、P型埋め込み拡散領域4の存在により、電子の通り道が狭くなるため、(L3-L4)の断面構造と比較してRdriftが大きくなり、Rdrift\_12 > Rdrift\_34の関係を満た

50

す。

【0064】

従って、数3, 数4によりRon\_12 > Ron\_34となり、この結果と数1により、本実施形態のNチャネルLDMOSトランジスタのオン抵抗Ronは、以下の数5の関係を満たす。

(数5)

$$1/Ron = 1/Ron_{12} + 1/Ron_{34} > 2/Ron_{12}$$

【0065】

数5において、最右辺の「 $2/Ron_{12}$ 」とは、P型ボディ領域3の底面にP型埋め込み拡散領域が形成されていない場合のLDMOSトランジスタのオン抵抗の逆数に対応する。そして、最左辺の $1/Ron$ は、図1及び図2に示す本実施形態のLDMOSトランジスタのオン抵抗の逆数に対応する。よって、数5により、本実施形態のNチャネルLDMOSトランジスタは、図17の従来構成と同様に、P型埋め込み拡散領域を備えない従来のLDMOSトランジスタのオン抵抗よりも低減できることが分かる。

10

【0066】

次にオフ耐圧について述べる。図4は、オフ耐圧を説明するための図である。図4(a)は、図1～図3と同様、本実施形態のLDMOSトランジスタの平面視概略図であるが、短冊型形状に構成されるP型埋め込み拡散領域4の各短冊の間隔、すなわち延伸方向に直交する方向の形成間隔(スリット間隔)をLslitとして付記している。また、図4(b)は、この形成間隔Lslitの長さとLDMOSトランジスタのオフ耐圧の関係をグラフにしたものである。

20

【0067】

図4(b)に示すように、オフ耐圧は、P型埋め込み拡散領域4の形成間隔Lslitに依存し、 $Lslit = 0 \mu m$ 、すなわちP型埋め込み拡散領域4が間隔を空けずに形成されている場合(図17に示す従来のLDMOSトランジスタと同様の構造の場合)に最も耐圧が高くなる。一方、P型ボディ領域3の図4(a)の紙面上縦方向に延伸する長さをWとしたときに、 $Lslit = W$ の場合、すなわち、P型ボディ領域3の全領域の底面にP型埋め込み拡散領域4が存在しない場合に最も耐圧が低くなる。

20

【0068】

これは以下の理由による。すなわち、P型埋め込み拡散領域4が間隔を空けずに形成されている場合には、図5(a)に示すように、ソース領域6とドレイン領域8(或いはドリフト領域5)が対向する全領域においてP型埋め込み拡散領域4が形成されているため、図中の領域Aに示すゲートエッジの電界が十分に緩和されて、オフ耐圧が高くなる。これに対し、P型ボディ領域3の全領域の底面にP型埋め込み拡散領域4が存在しない場合、上記図中の領域Aに示すゲートエッジの電界が緩和されず、オフ耐圧が低くなる。

30

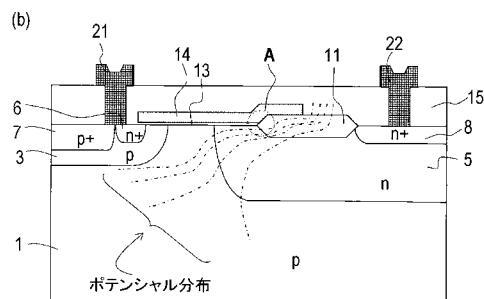

【0069】

図5に、P型埋め込み拡散領域4が存在する場合(a)と存在しない場合(b)のポテンシャル分布の概念図を示す。P型埋め込み拡散領域4が存在する場合は、N型ドレイン領域8の近傍まで空乏層が伸びるため、領域A近傍に電界が集中するということがない。これに対し、P型埋め込み拡散領域4が存在しない場合は、空乏層がほとんど伸びないため、領域A近傍に電界が集中し、オフ耐圧が低下する。例えば、オフ耐圧が100V以上のLDMOSトランジスタを設計する場合、P型埋め込み拡散領域4が存在する場合には120V程度のオフ耐圧を有するものが、P型埋め込み拡散領域4が存在しない場合には40V程度までオフ耐圧が低下する。

40

【0070】

図4(b)に示すように、オフ耐圧はP型埋め込み拡散領域4の形成間隔Lslitに依存し、 $Lslit$ をドリフト長Ldrift以下に設計するとオフ耐圧が上昇し始め、 $Ldrift/2$ よりも小さく設計すると、十分に耐圧が向上できる。このため、 $Lslit$ は $Ldrift/2$ よりも小さく設定することが望ましい(例えば図4(b)中のy)。このときの空乏層の状態を図6(a)に示す。なお、同図には、比較のために、(b)にP型埋め込み拡散領域4が全面に形成されている場合の空乏層の状態を、(c)にはP型埋め込み拡散領域4が形成されて

50

いない場合の空乏層の状態を併記している。

【0071】

図6(a)に示すように、P型埋め込み拡散領域4が形成されている箇所と形成されていない箇所で空乏層D1の伸びが異なるが、適切なLslitの値に設定して隣接するP型埋め込み拡散領域4の影響を及ぼすことにより、P型埋め込み拡散領域4が形成されていない領域においても、空乏層をドレイン領域8側に伸ばすことが可能である。P型ボディ領域3の全領域の底面にP型埋め込み拡散領域4が存在する場合(図6(b))の空乏層D2ほどはドレイン領域8側に伸びないとしても、P型ボディ領域3の全領域の底面にP型埋め込み拡散領域4が存在しない場合(図6(c))の空乏層D3と比べると、十分にドレイン領域8側に空乏層を伸ばすことができる。これにより、ゲートエッジ(図5の領域A)付近に電界が集中するのを回避でき、オフ耐圧が低下するのを防ぐことができる。

10

【0072】

このとき、図4(b)に示したように、P型埋め込み拡散領域4の形成間隔Lslitを、Ldrift/2以下に設定すれば、P型埋め込み拡散領域4をP型ボディ領域3の全領域の底面に形成した場合とほぼ同等のオフ耐圧を実現できる。

【0073】

次に、オン耐圧について述べる。前述の通り、オン耐圧を向上させるためには、ゲートオン時にドレイン電圧を増大させた場合のアバランシェ電流を低減する必要があるが、そのアバランシェ電流I<sub>body</sub>は、以下の数6によって示される。

【0074】

【数6】

$$I_{body} = I_{drain} \times \frac{a(T) \times \lambda}{E_{cri}} \times E_{max} \times \exp\left(-\frac{E_{cri}}{E_{max}}\right)$$

【0075】

なお、上記数6において、E<sub>max</sub>はゲートオン時にドレイン電圧を増大させた場合の最大電界値、E<sub>cri</sub>は臨界電界、(T)は温度係数が正の定数、I<sub>drain</sub>は上記最大電界箇所に流れるドレイン電流を示し、はデバイス構造が同一であれば一定となる定数である。

20

【0076】

数6によれば、アバランシェ電流を低減させるためには、E<sub>max</sub>を低減させるか、あるいは、I<sub>drain</sub>、つまり最大電界箇所を流れるドレイン電流値を低減させる必要がある。本発明に係るLDMOSトランジスタは、後者、すなわち最大電界箇所を流れるドレイン電流値I<sub>drain</sub>を低減させることによりアバランシェ電流を低減させる。

30

【0077】

図17に示した従来のLDMOSトランジスタにおいて、ゲートオン時にドレイン電圧を上昇させた場合、図7(b)の概略図に示すように、電界集中箇所E2はN型ドレイン領域8のソース領域7側エッジ近傍となり、ドレイン電流I<sub>drain</sub>全てがこの最大電界箇所E2に流れることになる。

【0078】

これに対し、本実施形態のLDMOSトランジスタにおいて、ゲートオン時にドレイン電圧を上昇させた場合には、図7(a)の概略図に示すように、電界集中箇所E1は埋め込み拡散領域4が形成されている外側位置におけるN型ドレイン領域8のソース領域7側エッジ近傍となる。すなわち、P型埋め込み拡散領域4の形成間隔に伴い、この電界集中箇所E1も、N型ドレイン領域8のソース領域7側エッジ近傍において所定の間隔を有して形成される。これは、ゲートオン時にはリーチスルーバイオードによる電界集中が起こるため、P型埋め込み拡散領域4が形成されている領域においては、空乏層がドレイン領域8側にシフトするためである。

40

【0079】

ここで、P型埋め込み拡散領域4が形成されている箇所のドレイン電流をI<sub>drain1</sub>、最大電界をE<sub>max1</sub>とすると、そのアバランシェ電流I<sub>body1</sub>は以下の数7によって示される。

50

【 0 0 8 0 】

【数 7】

$$I_{body1} = I_{drain1} \times \frac{\alpha(T) \times \lambda}{E_{cri}} \times E_{max1} \times \exp\left(-\frac{E_{cri}}{E_{max1}}\right)$$

【 0 0 8 1 】

また、P型埋め込み拡散領域4が形成されていない箇所のドレイン電流を $I_{drain2}$ 、最大電界を $E_{max2}$ とすると、そのアバランシェ電流 $I_{body2}$ は以下の数8によって示される。

【 0 0 8 2 】

【数 8】

$$I_{body2} = I_{drain2} \times \frac{\alpha(T) \times \lambda}{E_{cri}} \times E_{max2} \times \exp\left(-\frac{E_{cri}}{E_{max2}}\right)$$

【 0 0 8 3 】

ここで、図A7(a)に示したように、電界が集中する箇所E1はP型埋め込み拡散領域4が形成されている領域であるため、 $E_{max1} > E_{max2}$ が成立する。よって、数7及び数8より、 $I_{body1} > I_{body2}$ が成り立つ。

【 0 0 8 4 】

従って、本実施形態に係るLDMOSのトータルのアバランシェ電流 $I_{body}$ は、以下の数9の関係を満たす。

(数 9)

$$I_{body} = I_{body1} + I_{body2} < 2I_{body1}$$

【 0 0 8 5 】

数9において、最右辺の「 $2I_{body1}$ 」は、図17に示す従来のLDMOSトランジスタ、つまり、P型ボディ領域3の全ての底面に連続し、且つその先端がN型ドリフト領域5内に到達するようP型埋め込み拡散領域91が全面的に埋め込まれている場合のLDMOSトランジスタのアバランシェ電流に対応する。そして、最左辺の「 $I_{body}$ 」は、本実施形態のLDMOSトランジスタのアバランシェ電流を表わしている。従って、数9より、本実施形態のLDMOSトランジスタのアバランシェ電流は、従来のLDMOSトランジスタのアバランシェ電流よりも低減できることが分かる。

【 0 0 8 6 】

従って、図8に示すように、P型埋め込み拡散領域4を、P型ボディ領域3の一部底面に連結させることで短冊型に形成した場合のLDMOSトランジスタ(実線M1)は、P型ボディ領域3の全ての底面に形成し、その先端がN型ドリフト領域5内に到達するよう全面的に埋め込み形成した場合(破線M2)と比較して、アバランシェ電流を低減でき、結果的にオン耐圧を向上することができる。

【 0 0 8 7 】

以上のように、本実施形態のLDMOSトランジスタによれば、オフ耐圧、オン耐圧、オン抵抗の相互のトレードオフ関係を改善させることにより、オン抵抗を増大させることなく、高耐圧化を実現させることが可能となる。

【 0 0 8 8 】

なお、本実施形態において、図1(b)内のL5からL6の方向、つまり、ゲートエッジからN型ドレイン領域8に向かう方向に、N型ドリフト領域5の濃度が高濃度になるように濃度勾配を有するように形成するのも好適である。このようにすることで、最も電界の集中しやすいゲートエッジ近傍のN型ドリフト領域5の濃度が低くなるため、ゲートオフ時の電界緩和が促進される。更に、ゲートオン時では、逆に最も電界の集中しやすいN型ドレイン領域8近傍の濃度が高いことからリーチスルーバイオードによる電界集中を回避することができる。これにより、オフ耐圧とオン耐圧のトレードオフ関係をより改善することができる。

【 0 0 8 9 】

10

20

30

40

50

以下、図9を参照して、本実施形態のLDMOSトランジスタの製造方法につき説明する。

【0090】

図9(a)に示すように、このNチャネルLDMOSトランジスタは、P型半導体基板1の表面の一部にフィールド酸化膜(LOCOS酸化膜)11を形成し、P型不純物、例えばボロンの注入により、P型ボディ領域3を形成する。図9(a)中のLOCOSの長さ、つまりドリフト長は、100V以上の高耐圧化を図る場合は、例えば6μm以上に設定される。

【0091】

その後、P型不純物、例えばボロンの注入により、P型埋め込み拡散領域4を形成する。このとき、L1-L2断面図に示すようにP型不純物が注入される領域と、L3-L4断面図に示すようにP型不純物が注入されない領域が形成されるよう、交互にスリットが設けられたマスクを用いて不純物注入を行う。注入エネルギーは、1MeV以上の高エネルギー注入とする。これにより、P型埋め込み拡散領域4は、図1(a)に示すような短冊型形状を示すこととなる。

10

【0092】

次に、P型ボディ領域3と離間した位置に、N型不純物、例えばリンの注入を、例えば300KeV以上の注入エネルギーにて行い、N型ドリフト領域5を形成する。このN型ドリフト領域5は、LDMOSトランジスタの耐圧を下げることなく、オン抵抗を低減させるために形成される。

20

【0093】

次に、図9(b)に示すように、P型半導体基板1の表面領域にゲート酸化膜13を形成した後、P型ボディ領域3の一部上方及びN型ドリフト領域5の一部上方にまたがるようにゲート電極14を形成する。ゲート電極14形成工程としては、例えば、リンがドープされたポリシリコン膜をCVD法により形成し、その上にフォトエッチング技術によってレジストをパターンニングした後、ドライエッチング技術等によって前記のポリシリコン膜を加工することで行う。なお、本実施形態では、フィールド酸化膜11が形成されているため、ゲート電極14はN型ドリフト領域5の上方に位置するフィールド酸化膜11の一部上層にまたがるように形成される。

30

【0094】

次に、例えばリン又は砒素の注入によってN型ソース領域6、及びN型ドレイン領域8を形成すると共に、例えばボロン等の注入によってP型ボディコンタクト領域7を形成する。

【0095】

その後は、図9(c)に示すように、表面に例えば常圧CVD法によって層間絶縁膜膜15を形成し、リフローして表面段差を軽減する。この後、ゲート電極13、N型ドレイン領域8、N型ソース領域6、及びP型ボディコンタクト領域7の上において、層間絶縁膜膜15にコンタクトエッチを行い、開口を形成する。そして、例えば、スパッタによってアルミニウム膜を成長させた後、該アルミニウム膜をフォトエッチング及びドライエッティングによってパターンニングして、金属電極(21, 22)を形成する。

40

【0096】

なお、N型ドリフト領域5に濃度勾配を持たせるためには、N型ドリフト領域5を形成すべくN型不純物イオンを注入した後、例えば、950以上的熱拡散により横方向に濃度勾配を持たせるようにすれば良い。若しくは、N型不純物イオン注入時において、マスクを複数用いて異なるドーズ量の注入を実施することにより横方向に濃度勾配を持たせることも可能である。

【0097】

[第2実施形態]

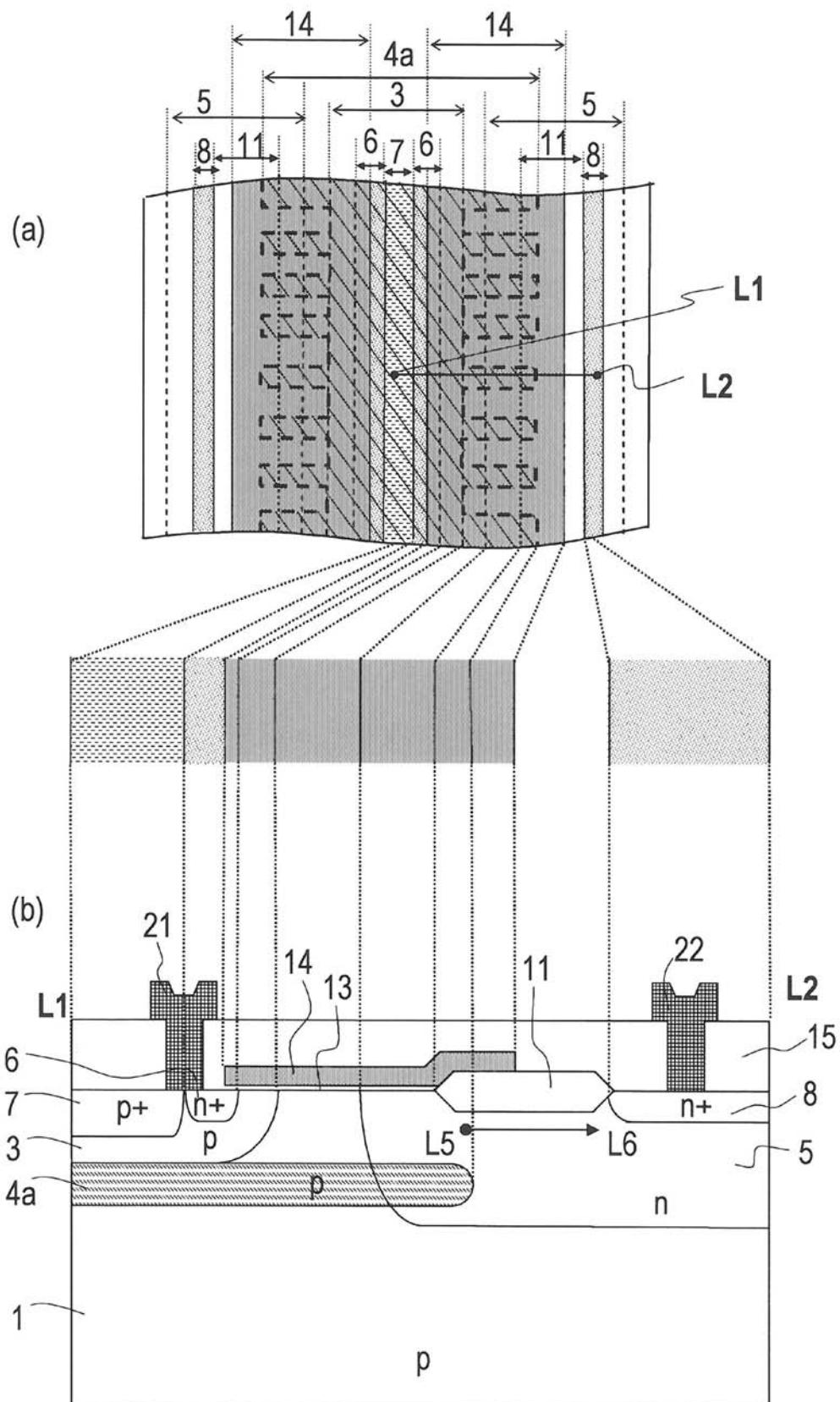

本発明の半導体装置の第1実施形態につき、図10~図12の各図を参照しながら説明する。なお、以下の各図において、図17或いは第1実施形態と同一の構成要素について

50

は同一の符号を付し、その説明を適宜省略する。

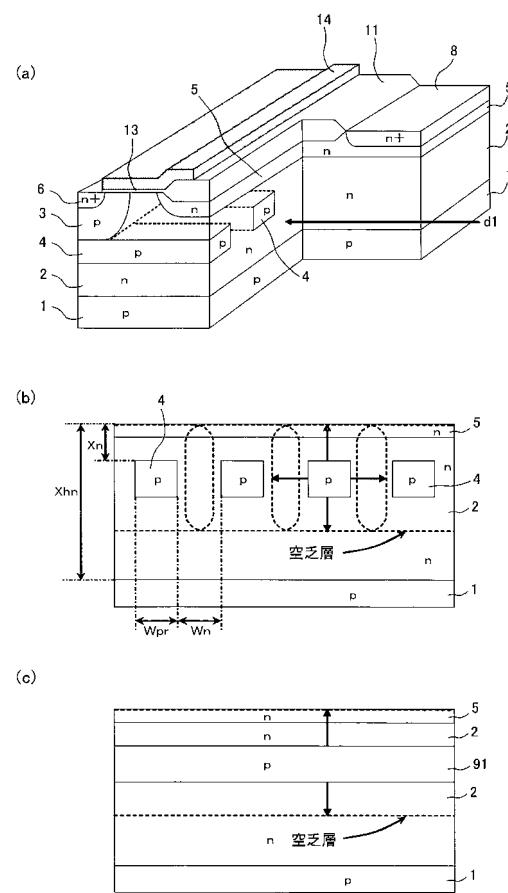

【0098】

本実施形態のLDMOSトランジスタは、P型埋め込み拡散領域4をP型ボディ領域3の一部底面に離散的に連結させ、且つその先端部がドリフト領域5内に到達するように各離散部分をドリフト領域5に向かう方向に延伸させることで、短冊型形状とする点においては第1実施形態と同様である。そして、第1実施形態と比較して、P型半導体基板1上にN型拡散領域2を有し、このN型拡散領域2上にP型ボディ領域3やN型ドリフト領域5が形成される点が異なる。このN型拡散領域2を、以下では「N型ウェル2」と呼ぶ。

【0099】

本実施形態によれば、P型ボディ領域3とP型半導体基板1の間にN型ウェル2（N型拡散領域）が形成されているため、ソース領域8がP型半導体基板1（GND電位）に対して電気的に良好に分離される。これにより、ソース電極がP型半導体基板1に対して電源電圧相当の耐圧を要求される場合でも使用することができ、第1の実施形態に係るLDMOSトランジスタと比較して、回路上の利用範囲が広い点で有効である。

【0100】

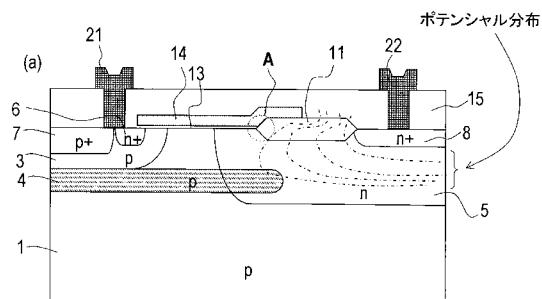

図10は、本実施形態のLDMOSの概略構造図であり、（a）が立体概略図を、（b）が（a）の立体概略図をd1方向に見たときの断面構造図である。なお、比較のために、（c）には、従来のLDMOSトランジスタ（図17の構造）を（a）のように図示した場合においてd1方向に見たときの断面構造図を図示している。

【0101】

図17に示した従来のLDMOSトランジスタ、すなわち、P型埋め込み拡散領域91をP型ボディ領域3の底面全面に連結させ、且つその先端がN型ドリフト領域5内に到達するように全面的に埋め込み形成した従来構成のLDMOSトランジスタにおいて、図10（c）に示すように、ゲートオフ時に、ドレイン電圧を増大させた場合、空乏層がP型埋め込み拡散領域91の上下に伸びる（図中の破線）。これにより、P型埋め込み拡散領域91の上方に位置するN型ドリフト領域5を完全に空乏化することにより、表面電界が緩和されオフ耐圧が増大される。

【0102】

一方、本実施形態のLDMOSトランジスタにおいては、図10（b）に示すように、ゲートオフ時に、ドレイン電圧を増大させた場合、空乏層がP型埋め込み拡散領域4の上下左右に伸びる（図中の破線）。このとき、スリット幅Lslit、及びP型埋め込み拡散領域4の深さXnを適切に調整することにより、P型埋め込み拡散領域4の左右及び上方を完全に空乏化させることができるとなる。このようにして表面電界を緩和することにより、オフ耐圧を増大させることができるとなる。オフ耐圧は、P型埋め込み拡散領域4の幅Wprとスリット幅Lslitの比  $= Lslit / Wpr$  に依存するが、詳細は後述する。なお、図10（b）内におけるWnは、P型埋め込み拡散領域4に挟まれた箇所におけるN型ウェル2の幅を表わしているが、この値はすなわちP型埋め込み拡散領域4の形成間隔Lslitに対応するものである。

【0103】

また、オン耐圧に関しては、第1実施形態と同様に、従来構成と比較してアバランシェ電流を低減でき、結果的にオン耐圧を向上することができる。第1実施形態と説明が重複するため、ここでは割愛する。

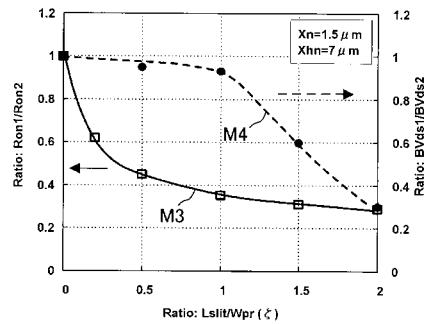

【0104】

次にオン抵抗に関して、図10（b）及び図11を用いて説明する。図11は、オン抵抗比及びオフ耐圧比と、 $(= Lslit / Wpr)$  の関係を示すグラフである。図11において、実線M3がオン抵抗比と $(= Lslit / Wpr)$  の関係を示しており、破線M4がオフ耐圧比と $(= Lslit / Wpr)$  の関係を示している。

【0105】

図10（b）に示すように、P型埋め込み拡散領域4の深さをXn、幅をWpr、スリット

10

20

30

40

50

幅をLslit、N型ウェル2の深さをXhnとする。また、図10(b)に示す本実施形態に係るLDMOSトランジスタのオン抵抗をRon1、図10(c)に示す従来のLDMOSトランジスタのオン抵抗をRon2とすると、両者のオン抵抗比:Ron1 / Ron2は、図11に示すように、 $\alpha = Lslit / Wpr$ に依存し、 $\alpha$ が大きくなる程、オン抵抗比は低減できる。 $\alpha$ の値が大きくなることは、すなわちP型埋め込み拡散領域4の形成幅に対する同領域の形成間隔が大きいことを意味しており、このとき、第1実施形態で説明したように、Rdriftの抵抗値が低い領域が増えるため、オン抵抗値が低下する。

#### 【0106】

オフ耐圧に関して説明する。図10(b)に示す本実施形態に係るLDMOSトランジスタのオフ耐圧をBVds1、図10(c)に示す従来のLDMOSトランジスタのオフ耐圧をBVds2とすると、両者の耐圧比:BVds1 / BVds2は、図11に示すように、 $\alpha = Lslit / Wpr$ に依存し、 $\alpha$ が大きくなる程、オフ耐圧比は小さくなる。P型埋め込み拡散領域4が間隔を有して形成されている場合、図10(b)に示すように、このP型埋め込み拡散領域4から伸びる空乏層が届く範囲内では耐圧を確保できる一方、空乏層が届かない領域内においては耐圧が低下する。図11では、P型埋め込み拡散領域4のスリット幅がその形成幅より広くなると( $\alpha > 1$ )、P型埋め込み拡散領域4から伸びる空乏層によって届かない領域が存在し、耐圧が急激に低下していることが分かる。

#### 【0107】

従って、図11によれば、オフ耐圧を考慮すると、 $\alpha = Lslit / Wpr$ を1以下に設定することが望ましく、例えば、 $\alpha = 0.5$ の時、オン抵抗比は0.45となり、本実施形態により、オフ耐圧を高く確保しながら、オン抵抗が大幅に低減できることが分かる。なお、この点は第1実施形態の構造においても同様である。

#### 【0108】

なお、近年、オフ耐圧とオン抵抗のトレードオフ関係を改善することが可能な装置として、特開2000-28617号公報に記載された、いわゆるマルチリサーフ構造、スーパージャンクション構造のLDMOSトランジスタが知られている。この種のMOSFETの特徴は、図21に示すようにドリフト層としてN型拡散領域及びP型拡散領域がストライプ状に形成されてお互いに交互に配置されていることである。このような構造にすることで、ドリフト層が空乏化しやすく、ドリフト層のドーズ量の濃度を高くできるため、オン抵抗を低減できるという特徴がある。

#### 【0109】

しかし、この従来構造では、P型拡散領域が基板表面に存在するため、ゲートオン時の電流がN型拡散領域のみにしか流れない。一方、本実施形態によれば、図10(b)に示すようにP型拡散領域が埋め込み拡散領域4として形成されているため、ゲートオン時の電流は、P型埋め込み拡散領域4の上方のN型ウェル2と、離間して形成された複数のP型埋め込み拡散領域4に挟まれた位置に形成されるN型ウェル2とに流れるため、オン抵抗を低減できる点で有利である。

#### 【0110】

ところで、P型埋め込み拡散領域4によるRESURF効果は、P型埋め込み拡散領域4の実効的な不純物濃度に大きく依存し、N型ドリフト領域5の濃度に合わせて最適化される。第1実施形態のように、N型ドリフト領域5をP型埋め込み拡散領域4よりも深く形成した場合、P型埋め込み拡散領域4の不純物濃度がN型ドリフト領域5により打ち消され、P型埋め込み拡散領域4の実効的な不純物濃度が一定程度低下することが想定される。従って、この濃度低下を想定してLDMOSトランジスタを設計する必要がある。

#### 【0111】

しかしながら、図10(a)に示すように、本実施形態では、N型ウェル2を設けることにより、N型ドリフト領域5をP型埋め込み拡散領域4よりも浅く形成することが可能である。このようにすることで、P型埋め込み拡散領域4の実効的な濃度に対するN型ドリフト領域5の濃度の影響を第1実施形態よりも小さくすることができ、LDMOSトランジスタの設計を簡素化することができる。更に、製造プロセス時においてN型ドリフト

10

20

30

40

50

領域5の濃度にバラツキが生じた場合でも、P型埋め込み拡散領域4の実効的濃度への影響を小さくできるため、安定した電気的特性を示すLDMOSトランジスタの製造が可能となる。

#### 【0112】

また、本実施形態では、N型ドリフト領域5とN型ウェル2を別々に濃度設定ができる。このため、N型ドリフト領域5の濃度を高く設定してオン抵抗を低減させると共に、N型ウェル2をN型ドリフト領域5よりも低濃度とすることで、オフ耐圧を低下させないようになることが可能となる。オフ耐圧を低下させないためには、図10(b)に示すP型埋め込み拡散領域4の上方及び左右を完全に空乏化する必要があるが、本実施形態の構成によれば、上方に関してはP型埋め込み拡散領域の注入深さXnを調整し、左右に関してはN型ウェル2の濃度を低く設定することによりこれを実現することができる。

10

#### 【0113】

P型埋め込み拡散領域4の上方には、N型ドリフト領域5が位置しており、P型埋め込み拡散領域4の左右に形成されているN型ウェル2よりもその濃度が高いため、完全空乏化が困難となる。従って、オフ耐圧のみを考慮すると、P型埋め込み拡散領域Xnを浅く形成することが望ましい。しかしながら、この注入深さXnを浅くすると、いわゆる擬似飽和現象(Quasi-Saturation)が顕在化する。擬似飽和現象とは、ゲートオン時のドレイン電流が、通常のMOSトランジスタのようにチャネルのピンチオフにより飽和するのではなく、ドリフト領域5の電子飽和速度により飽和する現象であり、ドレイン電流の飽和電流値を下げるだけではなく、オン抵抗も増大してしまうという問題がある。

20

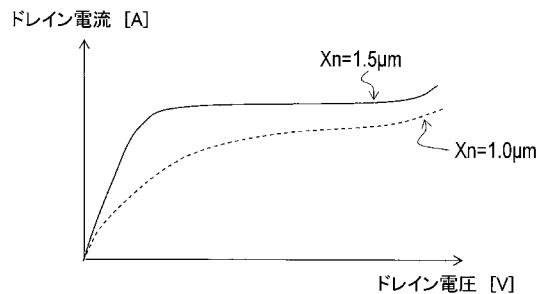

#### 【0114】

図12に、Xn = 1 μmの場合とXn = 1.5 μmの場合の、ゲートオン時のドレイン電圧に対するドレイン電流の関係を示す。なお、図12のグラフでは、オフ耐圧が同一となるようにN型ドリフト領域4の濃度が最適化されている。

20

#### 【0115】

図12に示されるように、Xn = 1 μmの場合と比較して、Xn = 1.5 μmの場合の方が、ドレイン電流の飽和電流値が高く維持され、オン抵抗を低くすることができる。従って、P型埋め込み拡散領域4の注入深さXnについては、Xn = 1.5 μmと設定するのが好適である。これは、第1実施形態の構成においても同様である。

30

#### 【0116】

以下、図13を参照して、本実施形態のLDMOSトランジスタの製造方法につき説明する。なお、図9の場合と同様、P型埋め込み拡散領域4の形成箇所における断面図(L1-L2断面図)と、P型埋め込み拡散領域4の非形成箇所における断面図(L3-L4断面図)を併記している。

#### 【0117】

図13(a)に示すように、このNチャネルLDMOSトランジスタは、P型半導体基板1に対してN型不純物を注入し、高温ドライブインによる熱拡散によりN型ウェル2を所望の深さに形成する。N型不純物としては、例えばリンを使用し、注入エネルギーは例えば2MeV以上、ドーズ量は $1.0 \times 10^{13} \text{ cm}^{-2}$ 以下とする。また、不純物注入を行う領域は、例えば、高エネルギー注入に対応した厚膜のレジストを用い、フォトエッチング技術等によって注入を行う領域を開口するようにパターンニングすることによって規定する。その後、N型ウェル2の表面の一部にフィールド酸化膜(LOCOS酸化膜)11を形成する。ドリフト長は、100V以上の高耐圧化を図る場合は、例えば6 μm以上に設定される。なお、図13の構成では、フィールド酸化膜11の、ソース領域6からドレイン領域8に向かう方向に係る長さ(LCOS長)が前記ドリフト長に対応する。

40

#### 【0118】

次に、図13(b)に示すように、P型不純物、例えばボロンの注入によりP型ボディ領域3を形成する。その後、P型不純物、例えばボロンの注入によりP型埋め込み拡散領域4を形成する。このとき、L1-L2断面図に示すようにP型不純物が注入される領域と、L3-L4断面図に示すようにP型不純物が注入されない領域が形成されるよう、交

50

互にスリットが設けられたマスクを用いて不純物注入を行う。注入エネルギーは、1 MeV以上の高エネルギー注入とする。これにより、P型埋め込み拡散領域4は、図1(a)に示すような短冊型形状を示すこととなる。

【0119】

次に、図13(c)に示すように、P型ボディ領域3と離間した位置に、N型不純物、例えばリンの注入を、例えば300KeV以上の注入エネルギーにて行い、N型ドリフト領域5を形成する。このN型ドリフト領域5は、LDMOSトランジスタの耐圧を下げる事なく、オン抵抗を低減させるために形成される。

【0120】

なお、N型ドリフト領域5をP型埋め込み拡散領域4よりも浅く形成する場合には、N型ドリフト領域5の深さが例えば1μm以下、P型埋め込み拡散領域4の深さが例えば1.5μm以上になるよう、それぞれの不純物イオン注入条件を設定する。また、N型ウェル2の濃度をN型ドリフト領域5よりも低く設定する場合には、例えばN型ウェル2の濃度を $3.0 \times 10^{16} \text{ cm}^{-3}$ 以下に、N型ドリフト領域5の濃度を $3.0 \times 10^{16} \text{ cm}^{-3}$ 以上で、N型ソース/ドレイン領域(6,8)の不純物濃度以下に設定する。

10

【0121】

その後、第1実施形態と同様、ゲート酸化膜13及びゲート電極14を形成した後、図13(d)に示すように、例えばリン又は砒素の注入によってN型ソース領域6、及びN型ドレイン領域8を形成すると共に、例えばボロン等の注入によってP型ボディコンタクト領域7を形成する。そして、層間絶縁膜15、金属電極(21,22)を形成する。

20

【0122】

なお、本実施形態においても、第1実施形態と同様、ゲートエッジからN型ドレイン領域8に向かう方向に、N型ドリフト領域5の濃度が高濃度になるように濃度勾配を有するように形成するのも好適である。そのための方法についても、第1実施形態で上述したのと同様の方法を利用することができる。

【0123】

[別実施形態]

以下、別実施形態につき説明する。

【0124】

1 図14に示すように、P型埋め込み拡散領域4のスリット形状を台形形状として形成しても良い。このとき、特に、P型埋め込み拡散領域4の幅 $W_p(x)$ を、N型ドレイン領域8に近付くほど大きくし、逆にN型ドリフト領域5の幅 $W_n(x)$ を、N型ドレイン領域8に近付くほど小さくするのが好ましい。図14において、(a)は上面視概略図を、(b)は立体概略図をそれぞれ示している。また、(c)は(a)内的一部領域 $X_1$ を模式的に拡大したものである。

30

【0125】

一般的に、スーパージャンクション構造によって高耐圧を実現するためには、交互に配置されているN型領域とP型領域を完全空乏化する必要があるが、完全空乏化するためには、P型埋め込み拡散領域の濃度を $N_a(x)$ 、N型ドリフト領域の濃度を $N_d(x)$ とすると、下記数10の関係を満たす必要がある。

40

(数10)

$$N_a(x) \times W_p(x) = N_d(x) \times W_n(x)$$

【0126】

従って、本別実施形態においては、P型埋め込み拡散領域4をN型ドレイン領域8に近づくほど低濃度となるように形成し、逆に、N型ドリフト領域5をN型ドレイン領域8に近づくほど高濃度になるように形成するのが好ましい。

【0127】

前述の通り、オフ耐圧時にはゲートエッジの電界緩和をすることが重要となるが、ゲートエッジの上部にはゲート電極14が存在するため、ゲート電極14によるフィールドプレート効果によりP型埋め込み拡散領域4による電界緩和のアシストが小さくても十分に

50

電界緩和がなされる。従って、ゲートエッジ近傍ではP型埋め込み拡散領域4の幅W<sub>P</sub>を小さく形成し、一方、フィールドプレート効果が小さくなるN型ドレイン領域8近傍では、P型埋め込み拡散領域4の幅W<sub>P</sub>を大きく形成する。このようにP型埋め込み拡散領域4の幅W<sub>P</sub>(x)、及び不純物濃度N<sub>A</sub>(x)を最適化することにより、例えば、全体的にN型ドリフト領域5の不純物濃度N<sub>D</sub>(x)を濃くしたり、あるいはN型ドリフト領域5の幅W<sub>N</sub>(x)を大きく形成することが可能となるため、結果的にN型ドレイン領域5の抵抗値を低減することでき、オン抵抗の低減が可能となる。

#### 【0128】

なお、本別実施形態では、第2実施形態の図10と同様、N型ウェル2が形成されている場合について図14を参照して説明したが、第1実施形態の構成のように、N型ウェル2が形成されていない場合においても同様に実現可能である。

10

#### 【0129】

2 上記第1実施形態では、P型埋め込み拡散領域4を短冊型形状に構成する場合を例に挙げて説明したが、少なくとも、N型ドリフト領域5内、並びにP型ボディ領域3とN型ドリフト領域4の間でP型埋め込み拡散領域4を離散的に形成すれば良い。

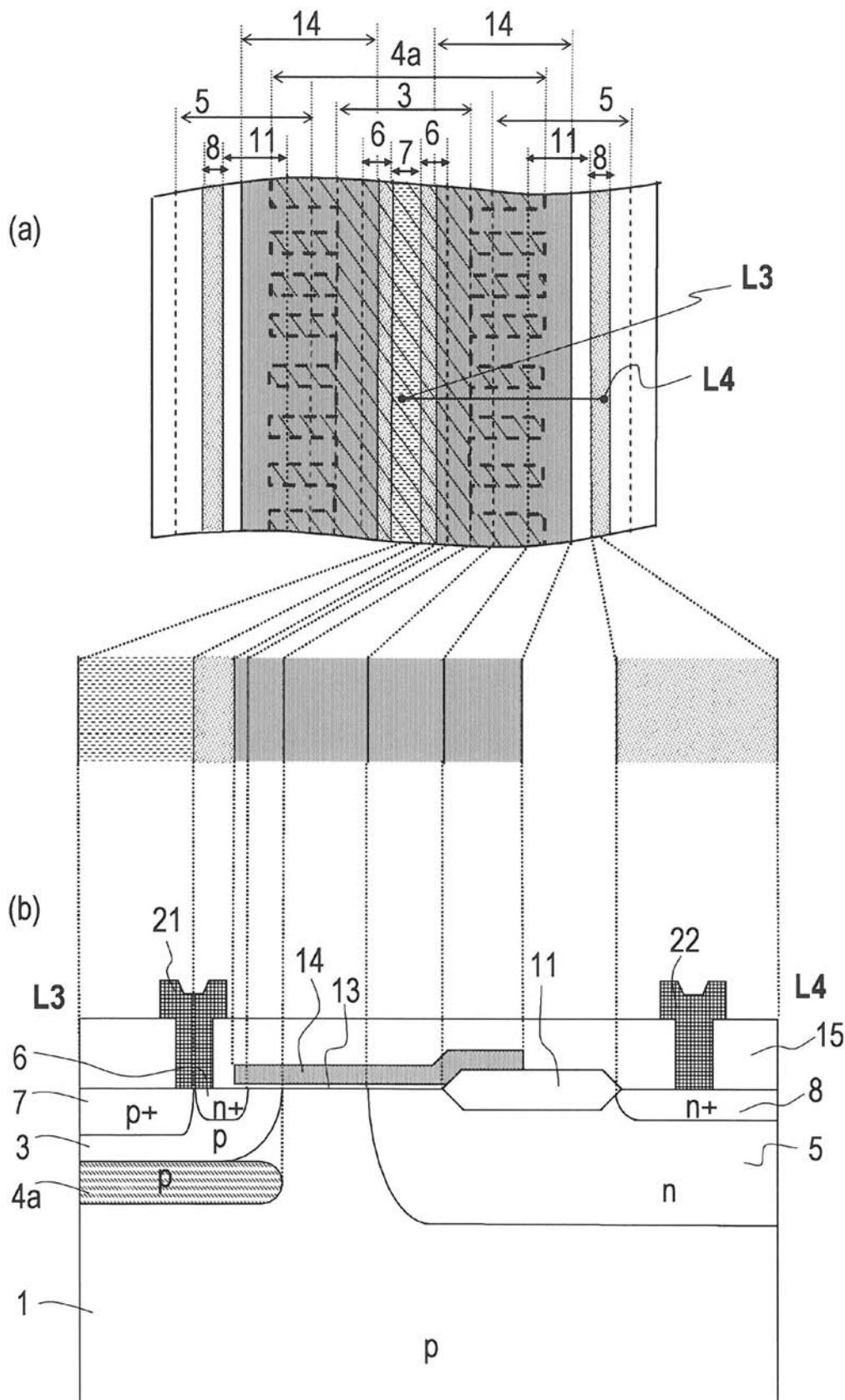

#### 【0130】

つまり、P型埋め込み拡散領域4を、P型ボディ領域3の底面位置においては、P型ボディ領域3の全底面に連結させる一方、P型ボディ領域3の外側(N型ドレイン領域8側)位置においては、P型ボディ領域3からN型ドリフト領域4に向かって離散的に延伸させて複数の突出部を形成すると共に、これら各突出部の先端をN型ドリフト領域4内に到達させようにも構わない。この場合の概略構造図を、図1及び図2の図示方法にならって図15及び図16に示す。図15(a)及び図16(a)は上面視概略図であり、両者は全く同じ図である。図15(b)及び図16(b)は断面概略図であるが、それぞれは切断位置が異なっており、図15(b)は、線L1-L2で切断した部分の断面を、図16(b)は、線L3-L4で切断した部分の断面を示している。

20

#### 【0131】

本別実施形態では、P型ボディ領域3の底面位置においては、全面にP型埋め込み拡散領域4が形成されているため、図2の場合と異なり、線L3-L4で切断した部分の断面図においてもP型埋め込み拡散領域4が表示されている。一方で、P型ボディ領域3とN型ドリフト領域5の対向位置、並びN型ドリフト領域5の内部位置においては、図1及び図2の場合と同様、離散的に形成されているため、線L3-L4で切断した部分の断面図においてP型埋め込み拡散領域4が表示されていない。

30

#### 【0132】

このように、P型埋め込み拡散領域4を櫛型に構成した場合であっても、図1及び図2に示す第1実施形態の構造と同様、N型ドリフト領域5内、並びにP型ボディ領域3とN型ドリフト領域5の間では離散的に形成されているため、電界集中箇所は、図7(a)と同様に離散的に形成される。よって、本別実施形態の構造においても、ドレイン電流を電界集中箇所を通る電流経路と電界集中箇所を通らない電流経路とに分けて流すことができるため、P型埋め込み拡散領域91が全面的に埋め込まれている図17に示す従来構成と比べて、ドレイン電流(アバランシェ電流)を少なくすることができ、オン耐圧を向上させることが可能となる。

40

#### 【0133】

同様に、第2実施形態の構成であれば、少なくともN型ドリフト領域5の下方位置におけるN型ウェル2内、及びP型ボディ領域3とN型ドリフト領域4の間の下方位置におけるN型ウェル2内において、P型埋め込み拡散領域4を離散的に形成すれば良い。つまり、P型埋め込み拡散領域4を、P型ボディ領域3の底面位置においては、P型ボディ領域3の全底面に連結させる一方、P型ボディ領域3の外側(N型ドレイン領域8側)位置においては、P型ボディ領域3からN型ドリフト領域4に向かって離散的に延伸させて複数の突出部を形成すると共に、これら各突出部の先端がN型ドリフト領域4の下方位置におけるN型ウェル2内に到達するようにも構わない。

50

## 【0134】

3 上述の各実施形態では、フィールド酸化膜11を形成し、その一部上方にゲート電極14が乗り上げるように形成される場合を例に挙げて説明した。しかし、本発明の技術は、フィールド酸化膜11を形成することなく、P型ボディ領域3の一部及びN型ドリフト領域5の一部に共通にオーバーラップしてゲート酸化膜13を形成し、その上層にゲート電極14を形成した場合でも、同様の効果を実現できる。

## 【0135】

4 上述の各実施形態において、P型埋め込み拡散領域4のスリット幅（形成間隔）は必ずしも等間隔で形成される必要はない。

## 【0136】

5 上述の各実施形態では、P型半導体基板上に、P型のボディ領域とN型のソース／ドレイン領域を有してなるNチャネル型のLDMOSトランジスタについて説明を行ったが、各極性を反転させることにより、同様の効果を示すPチャネル型のLDMOSトランジスタを実現することができる。

## 【0137】

6 上述の各実施形態では、ソース領域7をドレイン領域8が取り囲むような形状を想定したが、ソース領域7とドレイン領域8の位置関係は逆転しても構わない。この場合、P型ボディ領域3がN型ドリフト領域5を取り囲むような形状となる。

## 【0138】

7 上述の実施形態では、ソース電極21とボディ領域3の接触抵抗を低減させるべく、ボディ領域3内に高濃度P型のボディコンタクト領域7を形成していたが、ボディコンタクト領域7を形成しない場合であっても、オフ耐圧、オン耐圧、オン抵抗の相互のトレードオフ関係が改善されたLDMOSトランジスタを実現することは可能である。

## 【符号の説明】

## 【0139】

- 1 : 半導体基板

- 2 : N型拡散領域（N型ウェル）

- 3 : ボディ領域

- 4 : 埋め込み拡散領域

- 5 : ドリフト領域

- 6 : ソース領域

- 7 : ボディコンタクト領域

- 8 : ドレイン領域

- 11 : フィールド酸化膜

- 13 : ゲート酸化膜

- 14 : ゲート電極

- 15 : 層間絶縁膜

- 21 : ソース電極

- 22 : ドレイン電極

- 25 : 追加ドリフト領域

- 91 : 埋め込み拡散領域

10

20

30

40

【図5】

【図8】

【図9】

【図10】

【 図 1 1 】

【 図 1 2 】

【 図 1 3 】

【 図 1 8 】

【 図 2 0 】

〔 図 1 9 〕

【 2 1 】

【図1】

【図2】

【図3】

【図 4】

【図6】

【図7】

【図 14】

【図 15】

【図 16】

【図 17】