# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) Int. CI.<sup>6</sup> GO6F 15/78 (11) 공개번호 특1998-018035

(43) 공개일자 1998년06월05일

| (21) 출원번호<br>(22) 출원일자 | 특 1997-005520<br>1997년02월24일                                     |

|------------------------|------------------------------------------------------------------|

| (30) 우선권주장<br>(71) 출원인 | 213880 1996년08월13일 일본(JP)<br>후지쓰 가부시끼가이샤 세끼자와 다다시                |

| (72) 발명자               | 일본국 가나가와켄 가와사키시 나가하라구 가미고다나카 4-1-1<br>우찌다 토시야                    |

| (74) 대리인               | 일본국 가나가와켄 가와사키시 나가하라구 가미고다나카 4-1-1 후지쓰 가부<br>시끼가이샤 내<br>문기상, 조기호 |

|                        |                                                                  |

심사청구 : 있음

#### (54) 반도체 집적회로, 반도체 집적회로 모듈 및 반도체 집적회로 시스템

#### 요약

본 발명은 위상 동기된 제어 신호를 복수의 대상에 공급하는 반도체 집적회로, 반도체집적 회로 모듈 및 반도체 집적 회로 시스템에 관한 것으로서, 대상의 물리적인 위치에 관계없이 위상 동기된 제어 신호를 공급하는 것을 목적으로 한다.

제1 지연 제어 회로(21)의 출력단으로부터 복수의 대상 회로(50~57)의 각각의 입력단까지 각 실제 배선 (41)의 길이를 거의 등거리로 하고, 더미 배선 수단(42)의 배선 부하의 크기를제1 지연 제어 회로(21)에서 하나의 해당 대상 회로(50~57)까지의 실제 배선(41)의 배선 부하의 크기와 거의 일치하도록 구성한다.

#### 대표도

#### <del>5</del>5

# 명세서

## 도면의 간단한 설명

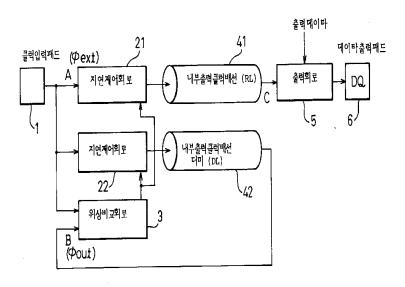

도 1은 관련 기술로서 반도체 집적 회로의 일례를 개략적으로 나타낸 블럭도.

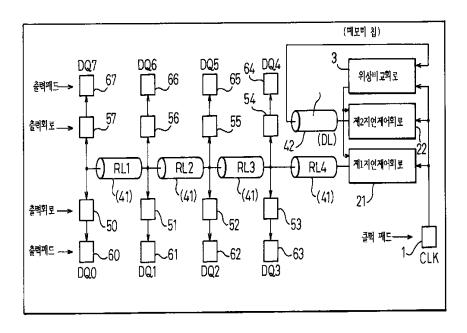

도 2는 도 1에 도시된 반도체 집적 회로에서 클럭 배선의 모양을 나타낸 블럭도.

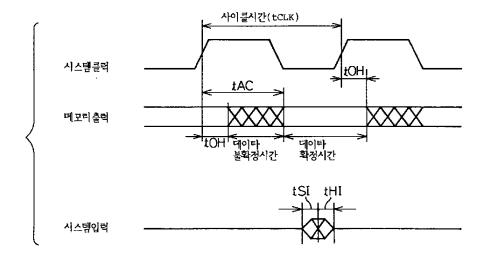

도 3은 도 2에 도시된 반도체 집적 회로에 있어서 과제를 설명하기 위한 도면.

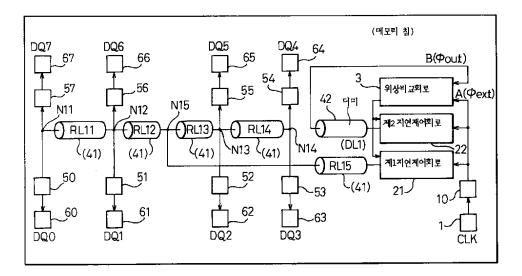

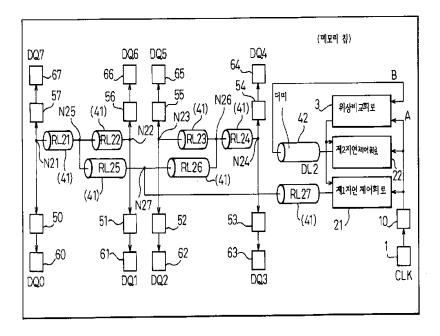

도 4는 본 발명을 적용한 반도체 집적 회로의 일 실시예를 나타내는 블럭도.

도 5는 본 발명을 적용한 반도체 집적 회로의 다른 실시예를 나타내는 블럭도.

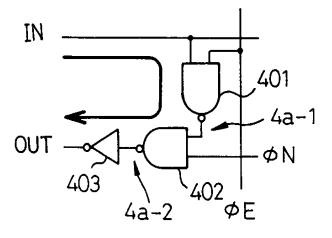

도 6a 내지 도 6c는 본 발명의 반도체 집적 회로에 있어서 지연 제어 회로(지연부)의 일 구성예를 설명하 기 위한 도면.

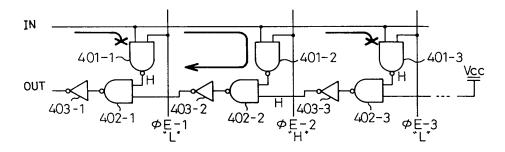

도 7은 본 발명에 의한 반도체 집적 회로에 있어서 지연 제어 회로(제어부)의 다른 구성예를 설명하기 위한 도면.

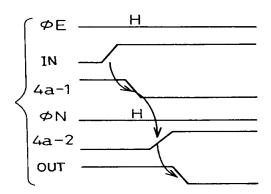

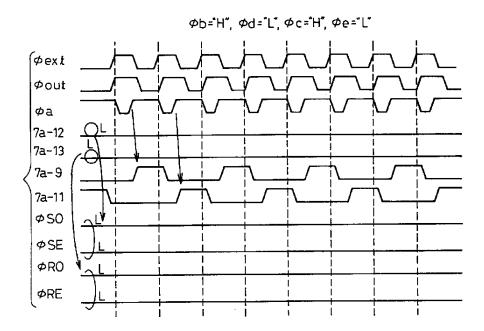

도 8은 도 7에 도시된 지연 제어 회로의 동작을 설명하기 위한 타이밍도.

도 9는 본 발명의 반도체 집적 회로에 있어서 위상 비교 회로(위상비교부)의 일 구성예를 설명하기 위한 도면.

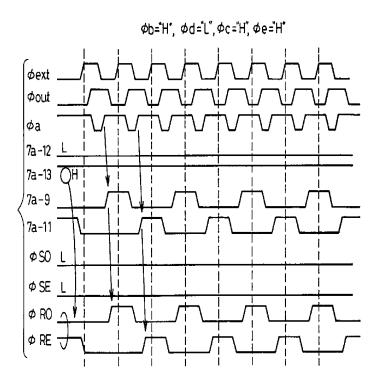

도 10은 도 9에 도시된 위상 비교 회로의 동작을 설명하기 위한 타이밍도.

도 11은 본 발명에 의한 반도체 집적 회로에서 위상 비교 회로(증폭회로부)의 일 구성예를 설명하기 위한 도면.

도 12는 도 11에 도시된 위상 비교 회로에서 JK 플립플롭의 동작을 설명하기 위한 타이밍도.

도 13은 도 11에 도시된 위상 비교 회로에서의 증폭 회로부의 동작을 설명하기 위한 타이밍도(카운트-업시).

도 14는 도 11에 도시된 위상 비교 회로에서의 증폭 회로부의 동작을 설명하기 위한 타이밍도(카운트-유지시).

- 도 15는 도 11의 위상 비교 회로에서 증폭 회로부의 동작을 설명하기 위한 타이밍도(카운트-다운시).

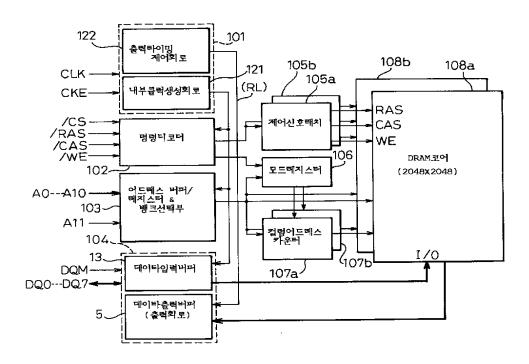

- 도 16은 본 발명에 의한 반도체 집적 회로가 적용되는 일례로서 동기 DRAM의 구성을 나타내는 도면.

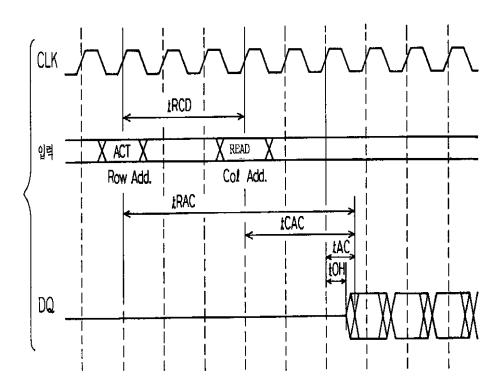

- 도 17은 도 16에 도시된 동기 DRAM의 동작을 설명하기 위한 타이밍도.

- 도 18은 도 16에 도시된 동기 DRAM의 여부 구성을 개략적으로 나타낸 블럭도.

- 도 19는 본 발명에 의한 반도체 집적 회로에서 출력회로(데이터 출력버퍼 회로)의 일 구성예를 설명하기 위한 도면.

- 도 20은 본 발명에 의한 반도체 집적 회로에서더미 내부 출력 클럭 배선(더미 배선)의 일 구성예를 설명하기 위한 도면.

- 도 21은 본 발명을 적용한 메모리 모듈의 일 예를 나타내는 도면.

- 도 22는 본 발명을 적용한 메모리 시스템의 일 예를 나타내는 도면.

- \* 도면의 주요 부분에 대한 부호의 설명\*

- 1 ...클럭 입력 패드3 ...위상 비교 회로

- 5, 50~57... 출력회로(출력 버퍼 회로)6, 60~67...데이터 출력 패드

- 10...클럭 버퍼 회로21, 221, 321...지연 제어 회로

- 22, 222, 322...지연 제어 회로

- 41, 241, 341...내부 출력 클럭 배선(실제 배선)

- 42, 242, 342...더미 내부 출력 클럭 배선(더미 배선)

#### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술분야 및 그 분야의 종래기술

본 발명은 위상 동기된 제어 신호를 복수의 대상에 공급하는 반도체 집적 회로, 반도체 집적 회로 모듈 및 반도체 집적 회로 시스템에 관한 것이다. 근년 반도체 집적 회로는 고속화 및 고집적화가 진행됨에 따라, 클럭 신호에 대해서도, 위상 동기된 클럭 신호를 복수의 회로(출력 패드)로 공급함이 필요하게되었다. 예를들어 동기 다이내믹 랜덤 액세스 메모리(SDRAM: Synchronous Dynamic Random Access Memory)의 복수의 출력 버퍼 회로에 대하여는 각 출력 버퍼 회로가 형성되어 있는 칩위의 위치에 관계없 이 위상 동기된 클럭 신호를 공급할 필요가 있다. 이러한 위상 동기된 신호의 필요성은 반도체 집적 회로 에 있어서 클럭 신호뿐만 아니라 다른 제어 신호에 있어서도 마찬가지이다.또, 반도체 집적 회로에서 제 어 신호의 동기는 반도체 집적 회로 모듈(예컨대 메모리 모듈) 상에서의 제어 신호, 또는 반도체 집적 회로 로 시스템(예컨대 메모리 시스템)에 있어서 제어 신호에 관하여도 요망되었다.

최근 메모리 장치는, 예컨대 100MHz 이상의 동작 속도를 달성하고, DLL ( Delay Locked Line ) 등의 기술을 이용하여 외부 입력 클럭 신호와 내부 출력 클럭 신호와의 위상을 맞춤에 의해 내부 클럭 배선에 의한 지연을 밖에서는 보이지 않도록 하여 액세스 시간의 지연 또는 불균형을 억제하는 방법이 사용되고 있다.

이러한 DLL 기술에서는 내부 출력 클럭 신호선의 부하에 의한 전파 지연을 어림하기위해서 더미의 내부 출력 클럭 배선을 마련하고있다. 도 I은 관련 기술로서 반도체 집적 회로의 일 예를 개략적으로 나타낸 블럭도로서, DLL 회로를 개략적으로 나타낸 것이다. 도 1에 있어서 참조 부호 I은 클럭 입력 패드를 나타 내고, 참조 부호 5는 출력회로(대상 회로)를 나타내며, 참조 부호 6은 데이터 출력 패드를 나타낸다. 또 한 참조 부호 3은 위상 비교 회로를 나타내고, 참조 부호 21 및 22는 위상 비교 회로(3)의 출력에 의해서 지연 시간이 가변 제어되는 지연 제어 회로를 나타내며, 참조 부호 41은 지연 제어 회로(2I)에서 출력회 로(5) 사이의 내부 출력클럭 배선(실제 배선)을 나타내며, 참조 부호 42는 상기 내부 출력 클럭 배선과 동등한 배선 부하를 갖는 더미 내부 출력 클럭 배선(더미 배선)을 나타낸다.

도 1에 도시된 바와 같이, DLL 회로에서는, 위상 비교 회로(3)의 한쪽 입력(지연 제어 회로(21, 22)의 입력: 비교 기준 신호(Øext)) A에서 위상 비교 회로(3)의 다른 쪽 입력(비교 대상 신호(Øout)) B까지의지연이 꼭 1 클럭분의 시간이 되도록 위상 비교 회로(3)에서 2개의 입력 신호의 위상을 비교하여 그 비교결과에 따라 지연 제어 회로(21, 22)의 지연량의 제어가 수행된다. 그 결과 실제로 사용하는 출력회로(5)의 클럭 입력단(C)에서의 내부 클럭 신호의 입력클럭 A에 대한 지연도 꼭 1 클럭분의 시간이 되어, 외견상, 실제 배선(41)의 전파 지연이 없게 된다.

#### 발명이 이루고자 하는 기술적 과제

도 2는 도 1에 도시된 반도체 집적 회로에서 클럭배선의 모양을 나타낸 블록도이다.즉 도 2에 도시된 회로에서는 도 1에서 출력회로(5) 및 데이터 출력패드(6)가 칩(메모리·칩)상에 서로 다른 위치에 마련된복수(도면상에서는 8개)의 출력회로( $50\sim57$ ) 및 데이터 출력 패드( $60\sim67$ )( $000\sim007$ )로 구성되어 있다.여기서 각 출력회로( $50\sim57$ )는, 예컨대 SDRAM 에서 복수의 출력 버퍼 회로에 대응하는 것이다.

이와 같이 데이터 출력 패드 $(60\sim67)($ 출력회로 $(50\sim57))$ 가 칩내에 복수 존재하는 경우에는 그 것들의 물리적 위치가 각각 다르기 때문에 실제 배선(41)의 길이(내부 출력 클럭 배선의 부하)도 각 출력회로 $(50\sim57)$ 의 위치에 따라 다르다. 따라서 어느 출력회로(데이터 출력 패드)에 맞춰 더미 배선(42)을 규정하면

다른 출력회로(데이터 출력 패드)에는 약간의 오차가 발생하게 된다.

구체적으로 도 2에 있어서, 예컨대, 더미 배선(42)의 길이(DL)을 지연 제어 회로(제1 지연 제어 회로)(21)로부터 가장 가까운 위치에 있는 출력회로(53, 54)까지의 실제 배선(41)의 길이(RL4)와 같도록 설정하면(DL=RL4), 출력회로(53, 54)에 입력되는 내부 클럭의 위상은 클럭 패드에 입력되는 외부 클럭 신호의 위상과 일치한다. 그렇지만 이 경우 제 지연 제어 회로(21)로부터 가장 먼 위치에 있는 데이터 출력패드(60, 67)(DQO, DQ7)에서는 지연 제어 회로(21)로부터 출력회로(50, 57)까지의 실제 배선(41)의 길이가 RL1+RL2+RL3+RL4 가 되기 때문에, 실제 배선의 길이(RL1+RL2+RL3)에 대응하는 더미 배선(DL)이 없으며그에 의해 실제 배선(RL1+RL2+RL3)에 대응하는 전파 지연(오차)분 내부 클럭의 공급 타이밍이 느려지게된다.

도 3은 도 2의 반도체 집적 회로에서 과제를 설명하기 위한 도면으로서, 반도체 집적 회로의 일 예인 SDRAM의 동작에서 과제를 설명하기 위한 것이다. 또한 본 발명의 대상으로 하는 반도체 집적 회로의 일 예로서 SDRAM은 뒤에 상술한다. 도 3에 있어서 tAC는 시스템 클럭(CLK)에서의 클럭 액세스 시간을 나타내고, tOH는 전 사이클 또는 다음 사이클에의 출력 데이터 보유 시간을 나타낸다. SDRAM의 특성의 불균형, 온도 의존성, 전원전압 의존성을 생각하면 tAC과 tOH는 일치하지 않고, 어떤 폭을 유지한다. 이 시간은데이터가 불확정한 시간으로서,어떠한 데이터가 출력될지 모르는 시간을 의미하며, 메모리 시스템에서는 사용할 수 없는 시간 소위 데드 밴드(dead band)가 된다. 기타 도시하고 있지 않지만 이 데드 밴드에는보드상의 배선 지연 시간, 불균형도 포함된다.

한편, SDRAM의 출력을 시스템측에서 받아들이는 경우에는, 셋트-업 시간(t SI), 유지 시간(tHI)이 필요하고, 이 시간은 메모리 출력의 데이터가 확정되는 시간 이내일 필요가 있다. 그 시간은 도면에서는 (tCLK+tOH-tAC)가 된다.

예를 들어 100MHz에서 동작하는 시스템을 생각하면, 사이클 시간(tCLK)은 10ns, 메모리 액세스 시간(tAC)은 6ns, 유지 시간(tOH)은 3ns로 하면, 7ns가 시스템측에서 사용할 수 있는 시간이 된다. 통상의 입력회로를 사용한 시스템에서 수신측 논리의 셋트-업 시간, 유지 시간의 합계(tSI+tHI)는 3ns이고 나머지4ns가 보드상에서의 신호 지연이며, DQ 단자간의 불균형등의 시스템 여유 시간이 된다. 보드상에서의 신호 전파 시간 등을 생각하면, 이 값은 시스템에 있어서 대단히 엄격한 값이라고 할 수 있다. 더욱 고속의시스템이 되면 점점 엄격한 타이밍 조정이 필요하게 되는 것은 말할 필요도 없다. 이 때문에 도 3에 도시된 데이터의 불확정 시간을 될 수 있는 한 작게 하는 것이 중요하다.

데이터의 불확정 시간을 짧게 하기 위해서는, 예를 들면, 도 2을 참조하여 설명한 데이터 출력 패드( $60 \sim 67$ )(출력회로( $50 \sim 57$ ))가 칩내에 다른 위치에 마련되고 있는 경우라도 항상 데이터가 외부 클럭(CLK)에 대하여 소정의 위상으로 출력되고, 즉 클럭 액세스 시간(tAC)이 항상 일정하게 되는 것이 좋다. 만약 데이터의 출력이 외부 클럭(CLK)의 상승에 동기하여 행하여지는 것이 요망되며 클럭 액세스 시간(tAC)이 항상 영(tAC)이 된 된다.

이상, 동기 DRAM을 예로서, 외부에서 입력되는 신호에 동기하여 출력신호가 출력되어야 할 필요성에 관해서 설명하였지만 이것은 동기 DRAM에 한하지 않고,많은 반도체 집적 회로에 공통된 것이다. 반도체 집적 회로의 내부에 관하여는 각 반도체 소자에서 소망의 동작을 할 수 있도록 각종의 대책을 세우는 것이 가능하지만 각 반도체 집적 회로의 내부에서의 처리결과를 출력하는 경우에는 다른 반도체 소자와의 관계를 규정할 필요가 있어 출력 타이밍를 일정하게 하는 것이 중요하다.

상술한 바와 같이, 각 데이터 출력 패드(60~67)까지의 실제 배선의 길이의 차이에 따른 전파 지연(오차)를 단순히 회피하기 위해서는, 더미의 내부 출력 클럭 배선(더미 배선)(42), 위상 비교 회로(3) 및 지연 제어 회로(제1 및 제2 지연 제어 회로)(21, 22)를 데이터 출력 패드의 수만큼 마련하는 것이 좋지만, 이와 같이 하면 회로 면적이라든지 소비 전력 등의 면에서 불리하다. 상술한 종래 기술의 과제는 1개의 칩으로 구성된 반도체 집적 회로(예컨대 메모리 칩)에 있어서만이 아니라, 예를 들면, 1개의 회로 기판으로 구성된 반도체 집적 회로 모듈(예를 들면, 메모리 모듈) 및 복수의 회로 기판을 포함하는 반도체 집적 회로 시스템(예를 들면 메모리시스템) 등에 있어서도 그러하다.

본 발명은 상술한 종래의 반도체 집적 회로가 갖는 과제에 비추어 보아, 대상으로 하는 복수의 회로 또는 패드가 마련된 물리적인 위치에 관계없이 각 회로 또는 패드에 대하여 위상 동기된 제어 신호를 공급하는 것을 목적으로 한다. 또한 본 발명은 반도체 집적 회로 모듈 및 반도체 집적 회로 시스템에 대하여도 똑 같이 위상 동기된 제어 신호를 공급하는 것을 목적으로 한다.

## 발명의 구성 및 작용

본 발명의 제1 형태에 의하면 제어 신호가 공급되는 제1 및 제2 지연 제어 회로와;제1 지연 제어 회로의 출력 신호가 각각 실제 배선을 통하여 공급되는 복수의 대상 회로와 ;상기제2 지연 제어 회로의 더미 출력 신호가 더미 배선 수단을 통하여 공급되며 상기제어 신호와 더미 배선 수단의 출력 신호의 위상을 비교하여 그 비교 결과에 의해 상기 제1 및 제2 지연 제어 회로에서의 지연 시간을 제어하는 위상 비교 회로를 구비하며, 상기 제1 지연 제어 회로의 출력단에서 상기 복수의 대상 회로의 각 입력단까지의 각 실제 배선의 길이를 각각 거의 등거리로 하며 상기 더미 배선 수단의 배선 부하의 크기를 해당 제1 지연 제어 회로에서 하나의대상 회로까지의 실제 배선의 배선 부하의 크기에 거의 일치시킨 것을 특징으로 하는 반도체 집적 회로가 제공된다.

또한 본 발명의 제2 형태에 의하면 제어 신호가 공급되는 제1 및 제2 지연 제어 회로와 ; 제1 지연 제어 회로의 출력 신호가 각각 실제 배선을 통하여 공급되는 복수의 대상 반도체 집적 회로와 ; 상기제2 지연 제어 회로의 더미출력신호가 더미 배선수단을 통하여 공급되며 상기 제어 신호와더미 배선 수단의 출력신호의 위상을 비교하여 그 비교 결과에 의해 상기 제1 및 제2 지연 제어 회로에서의 지연 시간을 제어하는 위상 비교 회로를 구비하며, 상기 제1 지연 제어 회로의 출력단에서 상기 복수의 대상 반도체 집적 회로의 각각의 입력단까지의 각 실제 배선의 길이를 각각 거의 등거리로 하고 상기 더미 배선수단의 배선부하의 크기를 해당 제1 지연 제어 회로에서 하나의 해당 대상 반도체 집적 회로까지의 실제 배선의 배선

부하의 크기에 거의 일치시킨 것을 특징으로 하는 반도체 집적 회로 모듈이 제공된다.

또한 본 발명의 제3의 형태에 의하면 제어 신호가 공급되는 제1 및 제2 지연 제어 회로와;제1 지연 제어 회로의 출력 신호가 각각 실제 배선을 통하여 공급되는 복수의 대상 반도체 집적 회로 모듈과 ;상기 제2 지연 제어 회로의 더미출력 신호가 더미 배선수단을 통하여 공급되어 상기 제어 신호와 해당 더미 배선 수단의 출력신호의 위상을 비교하여 그 비교 결과에 의해 상기 제1 및 제2 지연 제어 회로에서의 지연 시 간을 제어하는 위상 비교 회로를 구비하며, 상기 제1 지연 제어 회로의 출력단에서 상기 복수의 대상 반 도체 집적 회로 모듈의 각각의 입력단까지의 각 실제 배선의 길이를 각각 거의 등거리로 하고 상기 더미 배선 수단의 배선 부하의 크기를 해당 제1 지연 제어 회로에서 하나의 대상 반도체 집적 회로 모듈까지의 실제 배선의 배선 부하의 크기에 거의 일치시킨 것을 특징으로 하는 반도체 집적 회로 시스템이 제공된다.

본 발명의 반도체 집적 회로에 의하면 제1 지연 제어 회로의 출력단에서 복수의 대상 회로의 각각의 입력 단까지의 각 실제 배선의 길이는 각각 거의 등거리가 되도록 규정된다. 또한 더미 배선 수단의 배선 부하 의 크기는 제1 지연 제어 회로에서 하나의 대상 회로까지의 실제 배선의 배선 부하의 크기에 거의 일치하 도록설정된다.

또한 본 발명의 반도체 집적 회로 모듈에 의하면 제I 지연 제어 회로의 출력단에서 복수의 대상 반도체 집적 회로의 각각의 입력단까지의 각 실제 배선의 길이는 각각 거의 등거리로 규정된다. 또 더미 배선 수 단의 배선 부하의 크기는제I 지연 제어 회로에서 하나의 대상 반도체 집적 회로까지의 실제 배선의 배선 부하의 크기에 거의 일치하도록 설정된다.

또한,본 발명의 반도체 집적 회로 시스템에 의하면 제1 지연 제어 회로의 출력단에서 복수의 대상 반도체 집적 회로 모듈의 각각의 입력단까지의 각 실제 배선의 길이는 각각 거의 등거리로 규정된다. 또한, 더미 배선 수단의 배선 부하의 크기는 제1 지연 제어 회로에서 하나의 대상 반도체 집적 회로 모듈까지의 실제 배선의 배선 부하의 크기에 거의 일치하도록 설정된다.

이것에 의해서 대상 회로(대상 반도체 집적 회로 또는 대상 반도체 집적 회로 모듈)가 마련된 물리적인 위치에 관계없이 각 대상 회로에 대하여 위상동기된 제어 신호를 공급할 수 있다.

#### 실시여

이어서, 첨부한 도면들을 참조하여 본 발명에 의한 반도체 집적 회로, 반도체 집적 회로 모듈 및 반도체 집적 회로 시스템의 실시예를 설명한다.

도 4는본 발명을 적용한 반도체 집적 회로의 일 실시예를 나타낸 블럭도이고, DLL 회로를 개략적으로 나타낸 것이다. 도 4에 있어서, 참조 부호 I은 클럭입력 패드를 나타내고, 참조 부호 I0은클럭 버퍼 회로를 나타내며, 참조 부호 I0은클럭 버퍼 회로(대상 회로)를 나타내고, 참조 부호 I00~67은 데이터출력패드(DQ0~DQ7)를 나타낸다. 또한 참조 부호 I1은 제1 지연 제어 회로를 나타내고, 참조 부호 I2는 제2 지연 제어 회로를 나타내며, 참조 부호 I3은 위상 비교 회로를 나타내고, 참조 부호 I41은 내부 출력 클럭 배선(실제 배선)를 나타내고 참조 부호 I42는 더미의 내부 출력 클럭 배선(더미 배선)을 나타낸다.

도4에 나타낸 바와같이 클럭 신호(CLK) (A:비교기준신호(øext))는 클럭입력패드(1) 및 클럭 버퍼회로 (10)를 거쳐서 제1 지연 제어회로(21), 제2 지연 제어 회로(22) 및 위상 비교 회로(3)의 한쪽 입력에 공급되어 있다. 제1 지연제어회로(21)의 출력신호(클럭신호)는 이하에 상술한 바와같이 각각 실제배선(41)을 거쳐서 각 출력 버퍼 회로(50~57)에 공급되어 있다. 여기서 위상비교회로(3)의 다른쪽 입력에는 더미배선(42)을 거쳐서 제2 지연제어회로(22)의 출력(더미의 클럭신호, B: 비교대상신호(øout))가 공급되고, 위상 비교 회로(3)는이들 2개의 입력신호의 위상을 비교하여 제1 및 제2 지연제어회로(21, 2 2)를 제어하도록 되어 있다.또 이 DLL 회로의 상세한 것은 후에 도면을 참조하여 상술한다.

도4에 나타낸 바와같이, 상술한 도2의 반도체 집적회로와 같이 출력회로( $50\sim57$ ) 및 데이터 출력 패드( $60\sim67$ )는 칩(메모리칩)상의 다른 위치에 설비되어 있다. 이 도4에 나타낸 본 발명의 제1 실시예에서는 도2의 실제 배선(RL2)의 중앙부에 노드(RL1)를 설비하고, 상기 노드(RL1)에 대해서 지연제어회로(RL1)로 부터의 실제배선(RL1)을 접속하도록 되어 있다. 즉 도2의 실제배선(RL2)은 실제배선(RL2)의 반분 길이를 갖는 2개의 실제배선(RL12, RL13)으로 분할된다. 따라서 지연 제어회로(RL11, RL13)의 출력단과 노드(RL13)의 사이에 실제배선(RL15)이 배치되고, 노드(RL13)와 노드(RL15)의 사이에 실제배선(RL15)이 배치되고, 모드(RL15)와 노드(RL15)와 노드(RL15)의 사이에 실제배선(RL15)의 배치되고 또 노드(RL15)의 생리하도록 규정되어 있다.

이때 더미배선(42)의 길이(DL1)를 예를들어 실제배선(41)의 길이를 RLI5+RL13 (또는 RL15+RL12)로 설정함으로서, 버퍼출력회로(52, 55, 51, 56)(데이터 출력패드(62, 65, 61, 66))에 공급되는 내부클럭의 상승(또는 하강)의 타이밍을 클럭 신호(A)의 상승(또는 하강)의 타이밍과 일치시킬 수 있어, 이 들 버퍼출력회로 각각에 대한 내부클럭의 공급타이밍의 오차를 없앨 수 있다. 이 경우 버퍼출력회로(53, 54, 50, 57)(데이터 출력패드(63, 64, 60, 67))에서는 실제배선의 길이(RL14)(RL11)에 대응하는 더미배선이 설비되어 있지 않기 때문에, 실제배선에 대응하는 전파지연(오차)이 발생하게 된다. 다만 이들의 데이터 출력패드(63, 64, 60, 67)에 있어서 오차는 상술한 도2에 있어서 데이터 출력 패드(60, 67)등의 오차보다는 작게 되어 있어 개선효과를 얻는다.

즉 본실시예에서는 제1 지연제어회로(21)의 출력단에서 각 출력회로(대상회로)(50 $\sim$ 57)의 입력단까지의 각 실제배선(41)을 대칭성을 갖는 트리상으로서 규정하고 더미배선(42)의 길이(DL)를 제1 지연 제어회로에서 임의의 출력회로까지의 실제배선의 거리와 거의 일치시키고 있다.

도5는 본 발명을 적용한 반도체 집적회로의 다른 실시예를 나타내는 블럭도이고 상술한 도4의 실시예를 개선한 것이다. 여기서 제1 지연 제어회로(21), 제2 지연 제어회로(22) 및 위상 비교회로(3)등의 구성은 상술한 도4의 실시예와 같다. 여기서 제1 지연제어회로(21)의 출력단과 노드(N27)사이에 실제배선(RL27)이 배치되고, 노드(N27)와 노드(N25) 사이에 실제배선(RL25)이 배치되고, 또 노드(N27)와 노드(N26) 사이

에 실제배선(RL26)이 배치된다. 또 노드(N25)와 노드(N21) 사이에 실제배선(RL21)이 배치되고 노드(N25)와 노드(N22) 사이에 실제배선(RL22)이 배치되고 또 노드(N26)와 노드(N23) 사이에 실제배선(RL23)이 배치되고, 노드(N26)와 노드(N24) 사이에 실제배선(RL24)이 배치되어 있다.

도5에 나타낸 바와같이 본 실시예에서는 제1 지연 제어회로(21)의 출력단에서 각 출력 버퍼 회로(50~5 7)의 입력단까지의 각 실제배선(41)의 길이를 등거리가 되도록 규정하고 있다. 즉 실제배선(41)의 길이 (RL25)는 RL26과 같고(RL25=RL26) 또한 실제배선(41)의 길이(RL21, RL22, RL23, RL24)는 모두 같도록 (RL21=RL22=RL23=RL24) 규정되어 있다.

따라서 출력버퍼회로(50, 57)(출력패드(60, 67))까지의 실제배선의 길이는 RL27+RL25+RL21, 출력버퍼회로 (51, 56)(출력패드(61, 66))까지의 실제배선 길이는 RL27+RL25+RL22, 출력버퍼회로(52, 55)(출력패드(62,65))까지의 실제배선의 길이는 RL27+RL26+RL23, 그리고 출력 버퍼 회로(53, 54)(출력패드(63,64))까지의 실제배선의 길이는 RL27+RL26+RL24이 되고, RL25=RL26 또는 RL21=RL22=RL23=RL24 이므로, 제1 지연 제어회로(21)의 출력단에서 각 출력 버퍼회로(50~57)의 입력단까지의 각 실제배선의 길이가 등거리가 된다.

또 더미배선(42)의 길이(DL2)를 상기 제1 지연제어회로(21)의 출력단에서 각 출력버퍼회로(50~57)의 입력단까지의 실제배선의 길이(RL27+RL25+RL21)(=RL27+ RL25+RL22=RL27+RL26+RL23=RL27+RL26+RL24)와 일치시킴으로서 모든 출력패드(60~67)에 있어서 출력타이밍 예를들어, SDRAM의 판독데이터의 출력타이밍을 동기시킬 수 있다. 또 도5의 구성에 있어서, 제2 지연제어회로(22) 및 더미배선(42)을 제거하고, 그 대신노드(N24)의 신호를 위상 비교회로(3)의 다른쪽 입력으로 하고, 한쪽 입력인 클럭입력패드(I)로부터의 신호(외부클럭(CLK))와 비교하는 방법도 생각할 수 있지만, 이 방법에서는 노드(N24)의 신호와 위상비교회로(3)의 다른쪽 입력신호 사이에 지연이 생기는 일이 없도록 하기 위해서, 노드(N24)를 위상비교회로(3)의 다른쪽 입력단에 근접하여 배치할 필요가 있어 레이아웃에 크게 제한을 받는다. 또한 노드(N24)와 위상 비교회로(3)를 근접하여 배치하면 이로 인한 배선지연에 의해 외부 클럭와 각 출력회로(50~57)에 입력되는 내부 클럭의 동기가 취하지 않게 된다.따라서 본 발명으로서는 제2 지연제어회로(22) 및 더미배선(42)을 설비한 구성으로 하고 있다.

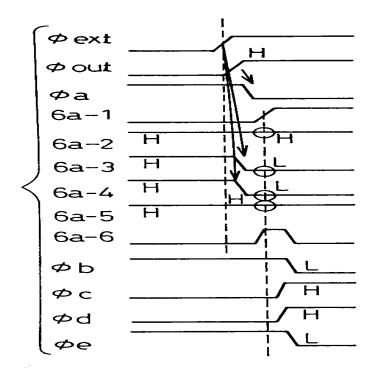

도6은 본 발명의 반도체 집적회로에 있어서 지연 제어회로(지연부)(21, 22)의 일구성예를 설명하기 위한도면이고, 동도( a )는 I비트분의 지연회로의 구성을 나타내고 동도( b )는 I비트분의 지연회로의 동작의타임챠트를 나타내고, 그리고 동도( c )는 1 비트분의 지연회로를 복수단 접속한 때의 구성과 동작설명을나타내는 것이 것이다.

도면6( a )에 나타낸 바와같이 I비트분의 지연회로는 2개의 NAND 게이트(401, 402) 및 인버터(403)를 구비하여 구성된다. 이 1비트분의 지연회로의 동작을 도6( b )를 참조하여 설명하면 입력(ØE)는 활성화신호(이네이블신호)로 고레벨 H일 때에 지연회로가 동작한다. 도6( b )에서는 이네이블신호(ØE)가 고레벨 H로 되어 신호의 액세스가 가능하게 된 상태를 나타내고 있다.또 도6( b )에 있어서, IN은 1비트분의 지연회로에의 입력 신호를 나타내고, ØN은 복수단접속된 지연회로중 인접하는 오른쪽 지연회로에서의 신호,OUT는 1비트분의 지연회로의 출력신호, 그리고 4a-1 및 4a-2는 도6( a )의 회로에서 대응하는 노드의 파형을 나타내고 있다. 따라서 OUT는 좌측에 인접하는 1 비트분의 지연회로에서의 신호(ØN)에 대응한다.

신호( $\emptyset$ N)가 저레벨 L인 때에는 출력신호(OUT)는 항상 저레벨 L이 되고 또 신호( $\emptyset$ N)가 고레벨 H이고 신호( $\emptyset$ E)가 저레벨 L 인때에는 출력신호(OUT)는 고레벨 H 이 된다.신호( $\emptyset$ N)가 고레벨 H 이고 신호( $\emptyset$ E)가 고레벨 H 인때 입력 신호(IN)가 저레벨 L 이면 출력신호(OUT)는 고레벨 H이 되고,IN이 고레벨 H 이면 저레벨 L 이 된다.

도6( a )의 회로에 의하면, 이네이블신호(øE)가 고레벨 H상태에서 입력 신호(IN)가 상승하면, 그 입력신호는 화살표의 경로로 전파되지만 이네이블신호(øE)가 저레벨 L 상태에서는 입력신호(IN)가 출력(OUT)으로 화살표 경로로 전파하지 않는다. 도6( c )은 도6( a )에 나타낸 1 비트분의 지연회로를 복수단 캐스케이드 접속한 예이고, 실제의 지연회로에 상당한다. 여기서 도6( c )에서는 3단밖에 없지만 실제로는 다수단 접속되어 있다. 또 이네이블신호(øE)의 신호선은 회로요소마다øE-1, øE-2, øE-3의 복수개있고, 이들 신호는 지연제어회로에 의해서 제어된다. 또 도6( a )~( c )에 나타낸 지연제어회로는 도4및 도5에서는 지연 제어회로(21, 22)에 포함되어 있다.

도6( c )에서는 중앙의 1 비트분의 지연회로가 활성화 되어 있고, 이네이블신호( $\emptyset$ E-2)가 고레벨 H로 되어 있다. 이 경우 입력신호(IN)가 저레벨 L로 부터 고레벨 H로 변화하면, 좌단의 1비트분의 지연회로와 우단의 I비트분의 지연회로의 이네이블신호( $\emptyset$ EI 및  $\emptyset$ E-3)는 저레벨 L 이므로 굵은선과 같이 입력신호(IN)는 NAND 게이트(IN01-1 및 I01-3)에서 정지된다.

한편, 활성화되어 있는 중앙의 1 비트분의 지연회로의 이네이블신호(øE-2)는 고레벨 H 레벨이므로, 입력신호(IN)는 NAND 게이트(401-2)를 통과한다. 오른쪽의 1비트분의 지연회로의 출력신호(OUT)은 고레벨 H 이므로 입력신호(IN)는 NAND 게이트(402-2)도 통과하여 출력신호(OUT)로서 저레벨 L의 신호가 전달된다. 상기 한바와 같이 오른쪽 출력신호(OUT) 즉, 이네이블신호(øN)가 저레벨 L인 때에는 출력신호(OUT)는 항상 저레벨 L이 되기 때문에,이 저레벨 L의 신호가 좌측의 1 비트분의 지연회로의 NAND 게이트 및 인버터에 순차 전달되어,최종적인 출력신호로서 출력된다.

이와 같이 활성화된 1비트분의 지연회로를 거쳐서 입력 신호(IN)는 반송되도록 신호전달되어 최종적인 출력신호가 된다. 즉 어떤 부분의 이네이블신호(ØE)를 고레벨 H로 할지 여부에 따라서 지연량을 제어할 수있다. 1 비트분의 지연량은 NAND 게이트와 인버터의 합계의 신호전파시간으로 결정되고, 이 시간이 DLL회로의 지연단위시간이 되고, 전체 지연시간은 I비트분의 지연량으로 통과하는 단수를 곱한 량이 된다.

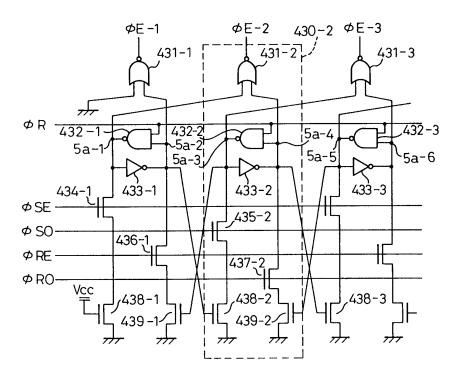

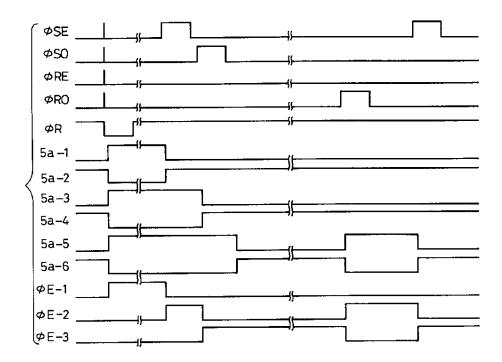

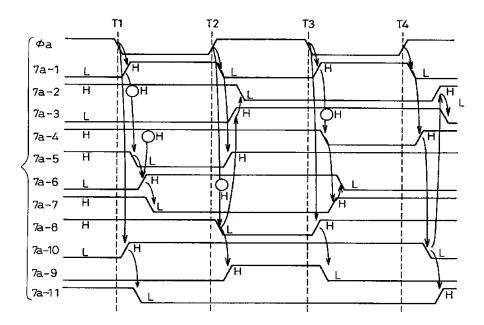

도7은 본 발명의 반도체 집적회로에 있어서 지연 제어회로(제어부)의 일구성예를 설명하기 위한도면이다. 도7에 나타낸 바와같이 지연제어회로도 점선으로 둘러싼 1 비트분의 지연제어회로(430-2)를 지연회로의 단수분 접속한 구성으로 되어 있고각 단의 출력이 지연회로의 각 단의 이네이블신호(øE)가된다.

구체적으로 1 비트분의 지연제어회로(430-2)는 NAND 게이트(432-2)와 인버터(433-2)로 구성되는 플립 플롭의 양단에 각각 직렬로 접속된 트랜지스터(435-2,437-2, 438-2, 439-2) 및 NOR 게이트(431-2)를 갖고 있다. 트랜지스터(438-2)의 게이트는 전단의 1 비트분의 지연제어회로의 노드(5a-2)에 트랜지스터(439-2)의 게이트는 후단의 1 비트분의 지연제어회로의 노드(5a-5)에 접속되어, 전단과 후단의 신호를 받게 된다. 한편 직렬접속이 되어 있는 다른쪽 트랜지스터에는 카운트엎할 때의 셋트신호(∅SE 및 ∅SO)와 카운트다운 할 때의 리셋신호(ಠRE 및 ಠRO)가 1 비트 걸러 회로에 접속되어 있다.

도7에 나타낸 바와같이 중앙의 1 비트분의 지연제어회로(430-2)에서는 트랜지스터(435-2)의 게이트에 셋트신호( $\emptyset$ SO)가 공급되고 트랜지스터(437-2)에 리셋신호( $\emptyset$ RO)가 공급되고, 또 지연제어회로(430-2)의 전단 및 후단의 양측 회로의 각 대응하는 트랜지스터의 게이트에는 각각 셋트신호( $\emptyset$ SE) 및 리셋신호( $\emptyset$ RE)가 공급되어 있다. 또한 NOR 게이트(431-2)에는 좌측(전단의) 회로의 노드(5a-1)와 회로(430-2)의 노드(5a-4)의 신호가 입력되는 구성으로 되어 있다. 또  $\emptyset$ R는 지연제어회로를 리셋하는 신호로 전원투입후에 일시적으로 저레벨 L 수준이 되고 그후에는 고레벨 H로 고정된다.

도8은 도7의 지연 제어회로의 동작을 설명하기 위한 타이밍도이다. 도8에 나타낸 바와같이, 우선 리셋신호( $\emptyset$ R)가 일시적으로 저레벨 L이 되어 노드(5a-1, 5a-3, 5a-5)가 고레벨 H, 또 노드(5a-2, 5a-4, 5a-6)가 저레벨 L로 셋트 된다. 그리고 카운트업할 때에는 카운트업신호(셋트신호)( $\emptyset$ SE 및  $\emptyset$ SO)가 교대로 고레벨H과 저레벨 L을 반복한다.

셋트신호( $\emptyset$ SE)가 저레벨 L로부터 고레벨 H 이 되면 노드(5a-1)는 접지되어 저레벨 L이 되고 또 노드(5a-2)는 고레벨 H로 변화한다. 노드(5a-2)가 고레벨 H로 변화한 것을 받아 출력신호(이네이블신호)( $\emptyset$ E-1)는 고레벨 H 로부터 저레벨 L로 변화한다. 이 상태는 플립플롭에 래치되기 때문에 셋트신호( $\emptyset$ SE)가 저레벨 L로 복귀되어도 이네이블신호( $\emptyset$ E-1)는 그대로 저레벨 L 이다. 그리고 노드(5a-1)가 저레벨 L로 변화한 것을 받아 이네이블신호( $\emptyset$ E-2)가 저레벨 L로부터 고레벨 H로 변화한다. 노드(5a-2)가 고레벨 H로 변화했기 때문에 트랜지스터(438-2)는 온상태가 되어 셋트신호( $\emptyset$ SO)가 저레벨 L로부터 고레벨 H이 되면 노드(5a-3)는 접지되어 저레벨 L로 또 노드(5a-4)는 고레벨 H로 변화한다. 또 노드(5a-4)가 고레벨 H로 변화한 것을 받아 이네이블신호( $\emptyset$ E-2)는 고레벨 H로부터 저레벨 L로 변화한다. 이 상태는 플립플롭에 래치되기 때문에 셋트신호( $\emptyset$ SO)가 저레벨 L로 복귀되어도 이네이블신호( $\emptyset$ E-2)는 그대로 저레벨 L이다.

그리고 노드(5a-3)가 저레벨 L로 변화한 것을 받아 이네이블신호(ØE-3)가 저레벨 L로부터 고레벨 H로 변화한다. 도8에서는 셋트신호(ØSE 및 ØSO)가 I 펄스씩 나와 있기는 해도 지연제어회로가 어느단에도 접속되어 있고 셋트신호(ØSE 및 ØSO)가 교대로 고레벨 H과 저레벨 L을 반복하면 출력신호(이네이블신호)(ØE)가 고레벨 H가 되는 단의 위치가 순차 오른쪽으로 이동한다. 따라서 위상비교회로(3)의 비교결과에 의하여 지연량을 증가시킬 필요가 있는 경우에는 교대로 셋트신호(ØSE 및 ØSO)의 펄스를 입력하면 된다.

카운트업신호(셋트신호)(øSE 및 øSO)와 카운트다운신호(리셋신호)(øRE 및 øRO)이 출력되지 않는 상태즉 저레벨 L 인 상태가 유지되면 이네이블신호(øE)는 고레벨 H 이 되는 단의 위치가 고정된다. 따라서위상 비교회로(3)의 비교결과에 의하여 지연량을 유지할 필요가 있는 경우에는 신호(øSE øSO øRE 및øRO)의 펄스를 입력하지 않도록 한다.

카운트다운할 때에는 리셋신호(øRE 및 øRO)의 펄스를 교대로 입력하면 카운트 업때와 반대로 출력(øE)이 고레벨 H이 되는 단의 위치가 순차 좌측으로 이동한다. 이상 설명한 바와같이 도7에 나타낸 지연제 어회로에서는 펄스를 입력함으로서 이네이블신호(øE)가 고레벨 H 이 되는 단의 위치를 하나씩 이동시키는 것이 가능하고, 이들의 이네이블신호(øE)에서 도6(c)에 나타낸 지연회로를 제어하면 지연량을 1단위씩 제어할 수 있다. 또 도7에 나타낸 지연제어회로(제어부)는 도4 및 도5에서는 위상 비교회로(3)에 포함되어 있다.

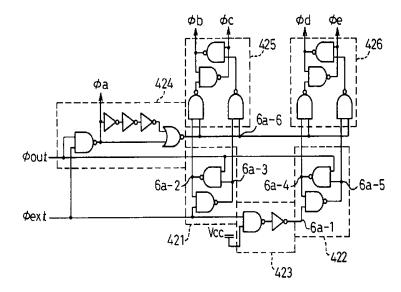

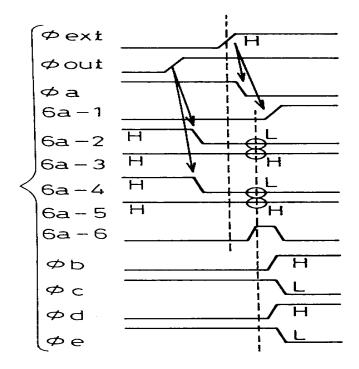

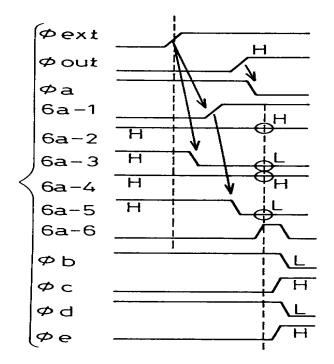

도9는 본 발명의 반도체 집적회로에 있어서 위상 비교회로(위상비교부)의 일구성예를 설명하기 위한 도면이고 도 10은 도9의 위상 비교회로의 동작을 설명하기 위한 타이밍도이다. 위상 비교회로(3)는 도9에 나타낸 위상비교부와 후술하는 도 11에 나타낸 증폭회로부의 2개의 회로부분으로 구성되어 있다.

도9에 있어서 참조부호 Ø out 및 Ø ext는 이 위상 비교회로에서 비교하는 출력신호와 외부클럭신호를 나타내고, 신호(Ø ext)를 기준으로 신호(Ø out)의 위상이 판정되고 또 Ø a  $\sim$  Ø e는 증폭회로에 접속되는 출력신호를 나타내고 있다. 도9에 나타낸 위상 비교회로(3)의 위상비교부는 2개의 NAND 게이트로 구성된 플립 플롭회로(421, 422), 그 상태를 래치하는 래치회로(425 및 426), 래치회로의 활성화신호를 생성하는 회로 (424) 및 외부클럭신호(Ø ext)의 위상허용치를 얻는 1 지연분의 지연회로(423)를 구비하여 구성되어있다.

도10( a )는 비교대상신호( $\emptyset$ out)가 비교기준신호( $\emptyset$ ext)보다도위상이 앞서있는 경우 즉 신호( $\emptyset$ out)가 신호( $\emptyset$ ext) 보다 먼저 저레벨 L로부터 고레벨H 이 되는 경우를 나타내고 있다. 신호( $\emptyset$ out)와 신호( $\emptyset$ ext)가 같이 저레벨 L인 때는 플립플롭회로(421 및 422)의 노드(6a-2, 6a-3, 6a-4, 6a-5)는 모두 고레벨 H로 되어 있다. 신호( $\emptyset$ out)가 저레벨 L로부터 고레벨 H로 변화하면, 노드(6a-2 및 6a-4)는 같이 고레벨 H로부터 저레벨 L로 변화한다. 그 후 신호( $\emptyset$ ext)가 저레벨 L로부터 고레벨 H이 되고 또 1지연분 만큼 늦어져 노드(6a-1)가 저레벨 L로부터 고레벨 H 이 되나 플립플롭의 양단 전위는 이미 확정되어 있기때문에 하등 변화는 생기지 않는다. 결국 노드(6a-2)는 저레벨 L, 노드(6a-3)는 고레벨 H, 노드(6a-4)는 저레벨 L 그리고 노드(6a-5)는 고레벨 H을 유지한다.

한편 신호(øext)가 저레벨 L로부터 고레벨 H로 변화함에 따라 회로(424)의 출력신호(øa)는 저레벨 L로부터 고레벨 H로 변화하여, 노드(6a-6)에는 일시적으로 고레벨 H 수준이 되는 펄스가 인가된다. 이 노드(6a-6)는 래치회로(425 및 426)의 NAND 게이트의 입력으로 되어있기 때문에 NAND 게이트가 일시적으로 활성화되어 플립플롭회로(421 및 422)의 양단의 전위상태를 래치회로(425 및 426)에 취입된다. 최종적으로는 출력신호(øb)가 고레벨 H 출력신호(øc)가 저레벨 L 출력신호(ød)가 고레벨 H, 그리고 출력신호(øe)가 저레벨 L이 된다.

다음에 도10( b )는 비교대상신호( $\emptyset$ out)와 비교기준신호( $\emptyset$ ext)의 위상이 거의 같고, 신호( $\emptyset$ out)가 신호( $\emptyset$ ext)와 거의 동시에 저레벨 L로부터 고레벨 H 가 되는 경우를 나타내고 있다. 신호( $\emptyset$ out)의 상승시점과 노드(6a-1)의 상승시점의 시간차내에 신호( $\emptyset$ out)가 저레벨 L로부터 고레벨 H로 변화한 때, 먼저신호( $\emptyset$ ext)가 저레벨 L로부터 고레벨 H이 됨으로서 플립플롭(421)의 노드(6a-3)가 저레벨 L로부터 고레벨 H로 변화한다. 플립플롭(422)에서는 노드(6a-1)가 그대로 저레벨 L이기 때문에 반대로 노드(6a-4)가고레벨 H로부터 저레벨 L로 변화한다. 그 후 노드(6a-1)가 고레벨 H로부터 저레벨 L로 변화하지만 플립플롭(422)의 상태는 이미 결정되므로 하등 변화는 생기지 않는다. 그 후 노드(6a-6)가 일시적으로 고레벨 H이 되므로 래치회로에는 이 상태가 기억되고, 결국 출력신호( $\emptyset$ b)가 저레벨, L 출력신호( $\emptyset$ c)가 고레벨 H, 출력신호( $\emptyset$ d)가 고레벨 H, 그리고 출력신호( $\emptyset$ 5e)가 저레벨 L이 된다.

또 도 10 ( c )는 비교대상신호(øout)가 비교기준신호(øext)보다도 위상이 늦어져 있고, øout가 øext 보다 후에 저레벨 L 로부터 고레벨 H이 되는 경우를 나타내고 있다. 이 경우는 øext에 의해서 2개의 플 립플롭회로(421, 422)에 변화가 생겨 노드(6a-3)와 노드(6a-5)가 고레벨 H로부터 저레벨 L로 변화한다. 그리고 최종적으로는 øb가 저레벨 L,øc가 고레벨 H, ød가 저레벨 L,øe가 고레벨 H 이 된다.

이와 같이 신호(비교기준신호)(øext)의 상승시간을 기준으로 신호(비교대상신호)(øout)의 상승시간이 그 이전에 고레벨 H로 되거나 거의 동시또는 늦게 고레벨 H이 되었는지의 여부를 검출할 수 있다. 이들의 검출결과를 출력신호(øb, øc, ød 및 øe)의 값으로서 래치해 놓고,그 값에 근거하여 지연제어회로를 카운트업할지를 결정한다.

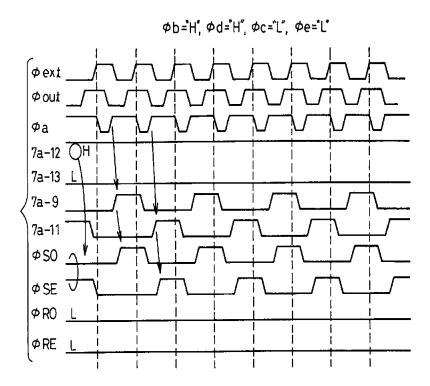

도11은 본 발명의 반도체 집적회로에 있어서 위상 비교회로(증폭회로부)의 일구성예를 설명하기 위한 도면이고,도12는 도11의 위상 비교회로에서의 JK 플립플롭의 동작을 설명하기 위한 타이밍도이다.

도11에 나타낸 바와같이 위상 비교회로(3)의 증폭회로부는 JK 플립플롭(427)과 NAND 게이트 및 인버터로 구성되는 증폭부(428)의 2개 부분을 구비하여 구성되어 있다. JK 플립플롭(427)에는 도9의 위상비교부에서의 출력신호(øa)가 입력되고, 신호(øa)가 저레벨 L인지 고레벨 H 인지에 따라서 노드(7a-9 및 7a-11)의 전위가 교대로 저레벨 L과 고레벨 H을 반복하게 된다. 증폭부(428)는 JK 플립플롭(427)의 출력신호와 신호(øb 및 ød)의 신호를 받아 증폭하여 출력한다.

우선 JK 플립플롭(427)의 동작을 도12의 타이밍챠트를 참조하여 설명한다. 시간(T1)에서 신호(øa)가 고 레벨 H로부터 저레벨 L로 변화하면 노드(7a-1 및 7a-10)가 저레벨 L로부터 고레벨 H로 변화한다. 한편 노드(7a-1)의 변화에 따라서 노드(7a-5, 7a-6 및 7a-7)가 변화하나 신호(øa)가 저레벨 L 이기 때문에 노드(7a-8)는 변화하지 않는다. 결국 노드(7a-9)은 변하지 않고 출력(7a-11)만이 저레벨 L로부터 고레벨 H이 된다. 다음에 시간(T2)로 되어 øa가 저레벨 L로부터 고레벨 H로 변화하면, 시간(T1)에서와 반대로노드(7a-8)는 고레벨 H로부터 저레벨 L로 7a-10은 7a-7가 변화하지 않기 때문에 변화하지 않고, 출력노드(7a-9)는 저레벨 L로부터 고레벨 H로 변화하여 노드(7a-11)는 변화하지 않는다. 이와 같이 JK 플립플롭회로(427)는 신호(øa)의 움직임에 따라서 노드(7a-9 및 7a-II)는 교대로 고레벨 H과 저레벨 L을 반복하다

도13은 도11의 위상 비교회로에서의 증폭회로부의 동작을 설명하기 위한 타이밍도이고(카운트업시)이고, 도14는 도11의 위상 비교회로에서의 증폭회로부의 동작을 설명하기 위한 타이밍도(카운트유지시)이고, 도 15는 도11의 위상 비교회로에서의 증폭회로부의 동작을 설명하기 위한 타이밍도(카운트다운시)이다. 다음 에 증폭부(428)의 동작을 도13~도15를 참조하여 설명한다.

도13은 비교기준신호(øext)의 상승에 대해서 비교대상신호(øout)가 먼저 저레벨 L로부터 고레벨 H이 되는 경우를 나타내고 있다. 이 경우 위상비교부에서의 입력 신호는 신호(øb)가 고레벨 H″,신호(øc)가 저레벨 L,신호(ød)가 고레벨 H, 그리고 신호(øe)가 저레벨 L 이다. 결국 노드(7a-12)가 고레벨 H가 되고, 노드(7a-13)가 저레벨 L로 고정되고, 셋트신호(øSO 및 øSE)는 JK 플립플롭의 상태에 따라서 변화하지만 리셋신호(øRO 및 øRE)는 7a-130이 저레벨 L이기 때문에 변화하지 않는다.

도14는 비교대상신호( $\emptyset$  out)가 비교기준신호( $\emptyset$  ext)와 거의 동시에 저레벨 L로부터 고레벨 H이 되는 경우를 나타내고 있다. 이 경우 위상비교부로부터의 입력신호는 신호( $\emptyset$  b)가 저레벨 L, 신호( $\emptyset$  c)가 고레벨 H, 신호( $\emptyset$  d)가 고레벨 H, 그리고 신호( $\emptyset$  e)가 저레벨 L 이다.결국 노드(7a-12 및 7a-13)가 저레벨 L로 고정되고, 리셋신호( $\emptyset$  SO 및  $\emptyset$  SE)는 JK 플립플롭의 출력이 증폭부에 영향을 주지 않고 신호( $\emptyset$  SO,  $\emptyset$  SE,  $\emptyset$  RO 및  $\emptyset$  RE)는 저레벨 L에 그대로 고정된다.

도15은 비교대상신호( $\emptyset$  out)가 비교기준신호( $\emptyset$  ext)의 상승에 대해서 늦어져, 저레벨 L로부터 고레벨 H이 되는 경우를 나타내고 있다. 이 경우의 위상비교부에서의 입력신호는 신호( $\emptyset$ b)가 저레벨 L 신호( $\emptyset$ c)가고레벨 H, 신호( $\emptyset$ d)가 저레벨 L, 그리고 신호( $\emptyset$ e)가 고레벨 H 이다. 결국 노드(7a-12)가 저레벨 L로 고정되고,노드(7a-13)가 고레벨 H로 고정되어 리셋신호( $\emptyset$ RO 및  $\emptyset$ RE)는 JK 플립플롭의 상태에 따라서 변화하지만 셋트신호( $\emptyset$ SO 및  $\emptyset$ SE)는 노드(7a-13)가 저레벨 L이기 때문에 변화하지 않는다.

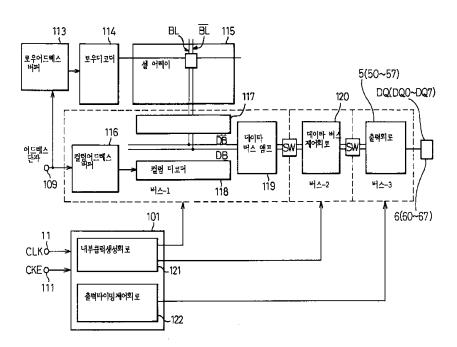

도16은 본 발명에 의한 반도체 집적회로가 적용되는 일례로서 동기 DRAM의 구성을 나타낸 도면이고, 도17은 도16의 동기 DRAM의 동작을 설명하기 위한 타이밍도이다. 본 발명이 적용되는 반도체 집적회로의 일례로서의 동기 DRAM(SDRAM)은 예를들어 파이프라인방식이 채용되고 16M·2뱅크·8비트폭의 것으로서 구성되어 있다.

도16에 나타낸 바와같이SDRAM은 범용DRAM의 DRAM코어(108a, 108b)외에 클럭버퍼(101), 컴맨드디코더(102), 어드레스버퍼/레지스터뱅크, 어드레스실렉트(어드레스버퍼)(103), I/O 데이터버퍼/레지스터(104), 제어신호래치(105a, 105b), 모드레지스터(106), 칼럼어드레스카운터(107a, 107b)를 구비하고 있다. 여기서 /CS, /RAS, /CAS, /WE 단자는 종래의 동작과는 달리 조합시켜 각종 컴맨드를 입력함으로서 동작모드가 결정되게 되어 있다. 각종 컴맨드는 컴맨드디코더로 해독되어동작모드에 따라서 각 회로를 제어하게된다.또한 /CS, /RAS, /CAS, /WE, 신호는 제어 신호래치(105a, 105b)에도 입력되어, 다음 컴맨드가 입력될때까지 그 상태가 래치된다.

어드레스신호는 어드레스 버퍼(103)에서 증폭되어 각 뱅크의 로드어드레스로서 사용되는 외에 컬럼 어드

레스카운터(107a 및 107b)의 초기값으로서 사용된다.

클럭버퍼(101)는 내부 클럭생성회로(121) 및 출력타이밍제어회로(122)를 구비하고있다. 내부 클럭생성회로(121)는 외부 클럭(CLK)에서 통상의 내부 클럭 신호를 생성하는 것이고,또한 출력 타이밍제어회로(122)는 전술한 바와같이 DLL을 적용하여 정확한 지연제어(위상제어)를 행한 클럭신호를 발생하기 위한 것이다.

I/O 데이터버퍼/레지스터(104)는 데이터입력버퍼(13) 및 데이터출력버퍼(5)(출력회로(50~57))를 구비하여 DRAM 코어(108a 및 108b)에서 판독된 신호는 데이터출력버퍼(5)에 의해 소정 수준으로 증폭되어, 출력 타이밍제어회로(122)로 부터의 클럭 신호에 따른 타이밍으로 데이터가 패드(DQO~DQ7)를 거쳐서 출력된다. 또한 입력데이터에 관대해서도 패드(DQO~DQ7)로부터 입력된 데이터는 데이터입력버퍼(13)를 거쳐서 기입된다. 여기서 본 발명의 반도체 집적회로가 대상으로 하고 있는 실제배선(RL)은 이 출력타이밍제어회로(122)로 부터 각 데이터출력버퍼(5) 까지의 배선에 대응하고 있다.

상기한 SDRAM의 판독동작을 도17을 참조하여 설명한다. 우선 외부클럭(CLK)은 이 SDRAM이 사용되는 시스템으로부터 공급되는 신호이고, 이 CLK의 상승에 동기하여 각종 컴맨드, 어드레스신호, 입력데이터를 기입 또는 출력데이터를 출력하도록 동작한다.

SDRAM에서 데이터를 판독해 내는 경우, 컴맨드신호(/CS, /RAS, /CAS, /WE 신호)의 조합으로부터 액티브 (ACT) 컴맨드를 컴맨드단자에 입력하고 어드레스단자에는 로우어드레스신호를 입력한다. 이 컴맨드 로우어드레스가 입력되면, SDRAM은 활성상태가 되고 로우어드레스에 따른 워드선을 선택하여 워드선 상의 셀정보를 비트선에 출력하고 센스앰프로 증폭한다.

또 로우 어드레스에 관계된 부분의 동작시간(tRCD) 후에 리드컴맨드(Read)와 컬럼어드레스를 입력한다. 컬럼어드레스에 따라서 선택된 센스앰프데이터를 데이터버스선으로 출력하고, 데이터버스앰프에서 증폭하고, 출력버퍼에서 더 증폭하여, 출력단자(DQ)로 데이터를 출력한다. 이 들 일련의 동작은 범용 DRAM의 경우과 완전히 동일한 동작이지만,SDRAM의 경우, 컬럼 어드레스에 관계하는 회로가 파이프라인동작하게 되어 있고, 리드데이터는 매사이클 연속하여 출력되게 된다. 이것에 의해 데이터전송속도는 외부 클럭의 주기로 되다.

SDRAM 에서의 액세스 시간에는 3종류 이고, 어느것이나 CLK의 상승시점을 기준으로 하여 정의된다. 도17에 있어서 tRAC는 로우어드레스 액세스시간,tCAC은 컬럼 어드레스 액세스시간, tAC은 클럭액세스 시간을 나타내고 있다. 이 SDRAM을 고속메모리시스템에서 사용하는 경우 컴맨드를 입력하고 나서 최초로 데이터를 얻을 때 까지의 시간인 tRAC나 tCAC도 중요하지만 도3에서 설명한 바와같이 클럭 액세스 시간(tAC)도 중요한 것이다.

도18은 도16의 동기 DRAM의 요부구성을 개략적으로 나타낸 블럭도이고 SDRAM 에서의 파이프라인동작을 설명하기 위한 것으로 일례로서 파이프가 3단구비되어 있는 경우를 나타내고 있다.

SDRAM 에서의 컬럼 어드레스에 관계하는 처리회로는 처리의 흐름에 따라서 복수단으로 분할되어 있고, 분 할된 각 단의 회로를 파이프라고 한다.

클럭 버퍼(101)는 도16을 참조하여 설명한 바와같이 내부 클럭생성회로(121)및 출력타이밍제어회로(122)를 구비하고, 내부 클럭생성회로(121)의 출력(통상의 내부 클럭신호)가 파이프(1)및 파이프(2)에 공급되어 출력타이밍제어회로(122)의 출력(위상제어된 내부클럭신호)이 파이프(3)의 출력회로(5)(데이터출력버퍼: 50~57)에 공급되도록 되어 있다.

각 파이프는 공급된 내부 클럭신호에 따라서 제어되고, 각 파이프 사이에는파이프간의 신호 전달타이밍을 제어하는 스위치가 구비되어 있고, 이들 스위치(h)도 클럭버퍼(101)(내부 클럭생성회로(121))에서 생성된 내부클럭신호에 의해 제어된다.

18에 나타낸 예에서는 파이프(1)에 있어서 컬럼 어드레스 버퍼(116)에서 어드레스신호를 증폭하여 컬럼디코더(118)에 어드레스신호를 보내고 컬럼디코더(118)에서 선택된 어드레스번지에 상당하는 센스앰프회로(117)의 정보를 데이터버스로 출력하여 데이터버스의 정보를 데이터버스앰프(119)로 증폭할때까지 행해진다. 또한 파이프(2)에는 데이터버스제어회로(120)만이 설비되고, 파이프(3)는 I/0버퍼(104)(출력회로(5))로 구성되어 있다. 또 I/0 버퍼(104)에 있어서 데이터입력버퍼(13)는 도18에서는 생략되어 있다.

그리고 각 파이프내의 회로도 클럭사이클시간내에 동작완료하면, 파이프와 파이프 사이에 있는 스위치를 클럭 신호로 동기하여 개폐함으로서 릴레이식으로 데이터를 보낸다. 이것에 의해, 각 파이프에서의 처리 가 병행하여 행해지게 되어, 출력단자에는 클럭신호에 동기하여 연속적으로 데이터가 출력되게 된다.

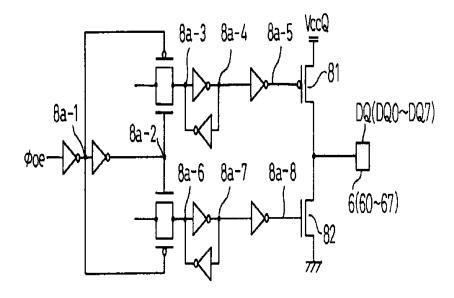

도19는 본 발명에 의한 반도체 집적회로에 있어서, 출력회로(데이터출력 버퍼회로:5, 50~57)의일구성예를 설명하기 위한 도면이다. 도18 및 도19에 나타낸 바와같이 도19에 있어서 Data1 및 Data2은 셀어레이 (115)로부터 판독되고, 센스앰프(117)와 데이터버스앰프(II9)와 데이터버스제어회로(120)를 거쳐서 출력된 기억데이터에 대응하는 신호이고 Data1 및 Data2는 출력데이터가 고레벨 H인 경우에는 동시에 저레벨 L이고, 출력데이터가 저레벨 L인 경우에는 동시에 고레벨 H 이다. 또출력데이터가 고레벨 H도 저레벨 L도 아닌 하이임피던스상태(하이셋트상태)를 취하는 것도 가능하고, 이 경우에는 데이터버스제어회로(120)에 있어서 Data1가 고레벨 H로 Data2가 저레벨 L이 되도록 변환된다. 신호(Øoe)는 출력타이밍제어회로 (122)(제1지연 제어회로(21))의 출력신호(클럭신호)에 대응하는 것이므로, 출력회로(5)(50~57)의 이네이블신호로서 기능하는 것이다.

클럭신호(øoe)가 고레벨 HOI 되면 Datal 과 Data2 정보가 데이터 출력패드(6)(60~67)에 출현하도록 동작한다. 예를들어 데이터 출력패드(6)에 고레벨 H을 출력하는 경우를 상정하면, 클럭신호(øoe)가 저레벨 L로부터 고레벨 H로 변화하여, 노드(8a-I)가 저레벨 L로,노드(8a-2)가 고레벨 H로 되고, 트랜스퍼게이트가 온(ON)되어,Data1 및 Data2가 노드(8a-3 및 8a-6)로 전달된다. 그 결과 노드(8a-5)가 저레벨 L로,노드(8a-8)가 고레벨 HOI 되면, 출력용 P채널트랜지스터(81)는 온이 되고, 또 N채널트랜지스터(82)는 오프 되어 데이터 출력패드(6)에는 고레벨 H의 출력이 나타나게 된다. 또 클럭신호(øoe)가 저레벨 L 이 되

면 트랜스퍼 게이트는 오프(OFF) 되어 출력상태가 유지된다.

이상 설명에서는 본 발명의 반도체 집적회로를 동기 DRAM으로서 설명했지만, 본 발명은 동기 DRAM에 한정되지 않고 외부에서 입력되는 신호에 동기하여 출력신호가 출력되는 반도체 집적회로이면 어떠한 것도 적용가능하다.

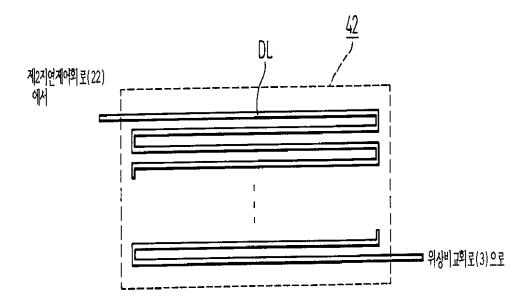

도20은 본 발명에 관한 반도체 집적회로에 있어서 더미의 내부출력클럭 배선(42)(더미배선(DL))의 일구성예를 설명하기 위한 도면이다. 도20에서 명백한 바와같이 더미배선(DL)은 예를들어칩상에 형성되고 실제배선(RL)과 동일한 선폭의 배선으로 형성되어 있다. 또 이하에 설명하는 반도체 집적회로 모듈에서의 더미의 내부출력클럭 배선(242) 및 반도체 집적회로 시스템에 있어서 더미의 내부출력클럭 배선(342)에 관하여도 동일하게 모듈상 또는 회로기판상에 더미용 배선을 구비하게 된다. 또 이 더미배선 대신에 소정값을 갖는 용량소자 또는 저항소자등을 조합시켜 대용할 수도 있다.

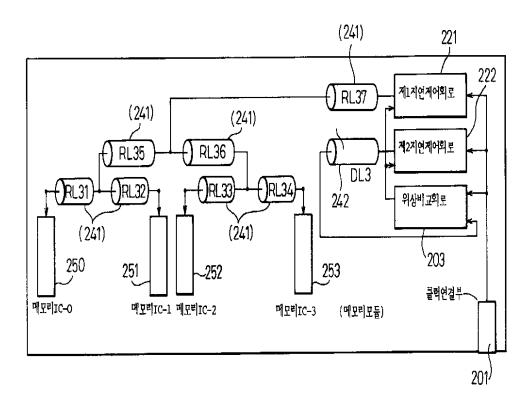

도 21은 본 발명을 적용한 메모리 모듈(SIMM : Single Inline Memory Module 이나 DIMM=Dual Inline Memory Module)의 일례를 나타낸 도면이고 DLL 회로를 개략적으로 나타낸 것이다. 도 21에 있어서 참조부호 201은 클럭 콘넥터부, 또 250~253은 메모리 IC(대상회로)를 나타내고 있다. 또 참조부호 221은 제1 지연 제어회로, 222는 제2 지연 제어회로, 203은 위상 비교회로, 241는 내부출력클럭 배선(실제배선), 그리고 242는 더미의 내부출력클럭 배선(더미배선)을 나타내고 있다.

도 21에 나타낸 바와같이 클럭 신호(CLK)는 클럭 콘넥터부(201)를 거쳐서 제I 지연제어회로(221), 제2 지연제어회로(222) 및 위상 비교회로(203)의 한쪽의 입력에 공급되어 있다. 제1 지연제어회로(221)의 출력신호(클럭신호)는 예를들어 도5에 나타낸 반도체 집적회로와 같이 각각 실제배선(241)을 거쳐서, 각 메모리IC(250~ 253)에 공급되어 있다. 여기서 위상 비교회로(203)의 다른쪽 입력에는 더미배선(242)을 거쳐서 제2 지연 제어회로(222)의 출력(더미의 클럭신호)가 공급되고, 위상비교회로(203)는 이 들 2개의 입력신호의 위상을 비교하여 제1 및 제2 지연 제어회로(221, 222)를 제어하도록 되어 있다. 또 이 DLL 회로의상세한 것은 도면을 참조하여 상술한 대로이다.

도 21에 나타낸 메모리 모듈(반도체 집적회로 모듈)은 도5의 반도체 집적회로에 있어서 출력버퍼회로(50~57)(또는 데이터 출력패드(60~67))를 메모리IC(250~ 253)에 대응시킨 것에 상당한다. 도21에 나타낸 바와같이, 본실시예에서는 제I 지연 제어회로(221)의 출력단에서 각 메모리IC(250~253)(각 메모리 IC의 클럭입력패드)까지의 각 실제배선(241)의 길이가 등거리가 되도록 규정하고 있다. 즉 실제배선(241)의 길이(RL35)는 RL36과 동일하게(RL35=RL36), 또 실제배선(41)의 길이(RL31, RL32,RL33, RL34)는 모두 동일하게(RL31=RL32=RL33)되도록 규정되어 있다.

따라서 메모리IC(250)까지의 실제배선의 길이는 RL37+RL35+RL31, 메모리 IC(251)까지의 실제배선의 길이는 RL37+RL35+RL32, 메모리IC(252)까지의 실제배선의 길이는 RL37+RL36+RL33, 그리고 메모리IC(253) 까지의 실제배선의 길이는 RL37+RL36+RL34이 되고,RL35=RL36 또한 RL31=RL32=RL33=RL34 이므로, 제1 지연 제어회로(221)의 출력단에서 각 메모리IC(250~253)의 클럭입력패드까지의 각 실제배선의 길이가 등거리가된다. 또 더미배선(242)의 길이(DL3)를 상기 제1 지연 제어회로(221)의 출력단에서 각 메모리IC(250~253)의 클럭입력패드까지의 실제배선 길이

(RL37+RL35+RL31)(=RL37+RL35+RL32=RL37+RL36+RL33=RL37+RL36+RL34)에 일치시킴으로서 모든 메모리IC(250~253)에 있어서 동작타이밍을 동기시킬 수 있다.

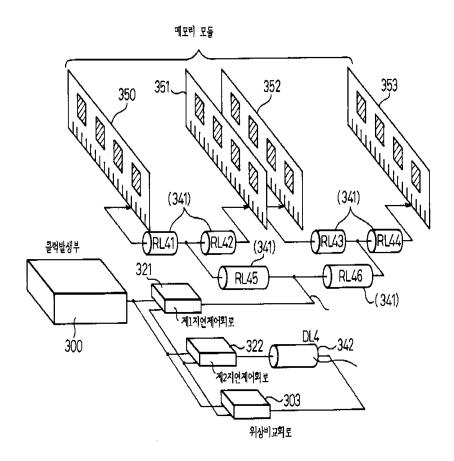

도22는 본 발명을 적용한 메모리시스템의 일례를 나타낸 도면이다. 도22에 있어서 참조부호 300은 클럭제 네레이터, 또 350~353은 메모리 모듈(대상회로)을 나타내고 있다. 또 참조부호 321은 제1 지연제어회로, 322는 제2 지연제어회로, 303은 위상 비교회로,341는 내부출력클럭 배선(실제배선), 그리고 342는 더미의 내부출력클럭 배선(더미배선)을 나타내고 있다.

도22에 나타낸 바와같이 클럭제네레이터(300)에서 발생된 클럭신호(CLK)는 제1 지연 제어회로(321), 제2 지연제어회로(322) 및 위상 비교회로(303)의 한쪽 입력에 공급되어 있다. 제1 지연제어회로(321)의 출력신호(클럭신호)는 예를들어 도21에 나타낸 메모리 모듈과 동일하게, 각각 실제배선(341)을 거쳐서 각 메모리 모듈(350~353)에 공급되어 있다. 여기서 위상 비교회로(303)의 다른쪽 입력에는 더미배선(342)을 거쳐서 제2 지연제어회로(322)의 출력(더미의 클럭신호)가 공급되고, 위상 비교회로(303)는 이 들 2개의입력 신호의 위상을 비교하여, 제1 및 제2 지연제어회로(321, 322)를 제어하게 되어 있다.또 이 DLL 회로의 상세한 것은 도면을 참조하여 상술한 바와같다.

도22에 나타낸 메모리시스템(반도체 집적회로 시스템)은 도21의 메모리 모듈에서의 메모리IC(250~253)를 메모리 모듈(350~353)에 대응시킨 것에 상당한다.

도 22에 나타낸 바와같이 본실시예에서는 제1 지연 제어회로(321)의 출력단에서 각 메모리 모듈(350~353)(각 메모리 모듈의 클럭입력단자)까지의 각 실제배선(341)의 길이가 등거리가 되도록 규정하고 있다.즉 실제배선(341)의 길이(RL45)는 RL46과 동일하게(RL45=RL46),또 실제배선(341)의 길이(RL41, RL42, RL43, RL44)는 완전 동일하게(RL41=RL42=RL43=RL44) 되도록 규정되어 있다.

따라서 메모리 모듈(350)까지의 실제배선의 길이는 RL47+RL45+RL41, 메모리 모듈(351)까지의 실제배선의 길이는 RL47+RL45+RL42,메모리 모듈(352) 까지의 실제배선의 길이는 RL47+RL46+RL43, 그리고 메모리 모듈(353) 까지의 실제배선의 길이는 RL47+RL46+RL44이 되고, RL45=RL46, 또 RL41=RL42=RL43=RL44이므로, 제1 지연 제어회로(221)의 출력단에서 각 메모리IC(250~253)의 클럭입력패드까지의 각 실제배선의 길이가 등 거리가 된다. 또 더미배선(242)의 길이(DL3)를 상기 제1 지연 제어회로(221)의 출력단에서 각 메모리 모듈(350~353)의 클럭입력단자까지의 실제배선의길이

(RL47+RL45+RL41)(=RL47+RL45+RL42=RL47+RL46+RL43=RL47+RL46+RL44)에 일치시킴으로서, 모든 메모리 모듈 (350~353)에 있어서 동작타이밍을 동기시킬 수 있다.

또 상술한 도21 및 도22에서는 도5의 반도체 집적회로에 대응한 구성을 나타내어 설명했으나, 도4의 반도체 집적회로의 구성을 메모리 모듈 또는 메모리시스템에 적용할 수 있는 것은 말할 필요도 없다. 이상의 설명에서는 메모리(SDRAM), 메모리모듈 및 메모리시스템을 예로서 설명했지만, 본 발명은 다른 다양한 반 도체 집적회로, 반도체 집적회로 모듈 및 반도체 집적회로 시스템에 대해서도 폭넓게 적용할 수 있다. 또 상기 각 실시예에서는 제어신호로서 클럭 신호를 예로 들어 설명했으나, 제어신호로서는 클럭 신호에 한정되는 것이 아님은 물론이다.

#### 발명의 효과

이상 상술한 바와같이, 본 발명의 반도체 집적회로에 의하면 대상으로 하는 복수의 회로 또는 패드가 구비된 물리적인 위치에 관계없이, 회로 또는 패드에 대해서 위상동기된 제어신호를 공급할 수 있다. 또 본발명에 의하면 반도체 집적회로 모듈 및 반도체 집적회로 시스템에 대해서도 동일하게 위상동기된 제어신호를 공급할 수 있다.

#### (57) 청구의 범위

#### 청구항 1

제어 신호(CLK)가 공급되는 제1 및 제2 지연 제어회로(21, 22);

제1 지연 제어회로(21)의 출력 신호가 각각 실제 배선(41)을 통하여 공급되는 복수의 대상 회로(5;50~57);

상기제2 지연 제어회로(22)의 더미 출력 신호가 더미배선 수단(42)을 통하여 공급되고 상기제어 신호와 해당 더미배선 수단의 출력 신호의 위상을 비교하여 그 비교 결과에 의해 상기 제1 및 제2지연 제어회로 에서의 지연 시간을 제어하는 위상 비교회로(3)를 구비한 반도체 집적회로에 있어서,

상기제1 지연 제어회로(21)의 출력단에서 상기복수의 대상회로(5;  $50\sim7$ )의 각각의 입력단까지의 각 실제 배선(41)의 길이를 각각 거의 등거리로 하고, 상기 더미배선 수단(42)의 배선 부하의 크기를 제1 지연 제 어회로(21)에서 하나의 해당 대상 회로(5;  $50\sim57$ )까지의 실제배선(41)의 배선부하의 크기에 거의 일치시킨 것을 특징으로 하는 반도체 집적회로.

#### 청구항 2

제1항에 있어서, 상기 더미배선수단(42)의 배선 길이를 상기 제1 지연 제어회로(21)에서 하나의 상기 대상 회로(5;50~57)까지의 실제배선(41)의 배선 길이와 거의 일치시킨 것을 특징으로 하는 반도체 집적회로

## 청구항 3

제1항에 있어서, 상기 제1 지연 제어회로(21)의 출력단에서 상기 각 대상 회로(5;50 $\sim$ 57)의 입력단까지의 각 실제배선(41)을 트리 형태로 구성하고, 각 분기부로부터 다음 분기부 또는 해당 대상 회로의 입력단까지 각 분기 배선의 거리가 같게 한 것을 특징으로 하는 반도체 집적회로.

## 청구항 4

제어 신호(CLK)가 공급되는 제I 및 제2 지연 제어회로(21, 22);

제1 지연 제어회로(21)의 출력 신호가 각각 실제배선(41)을 통하여 공급되는 복수의 대상회로(5;50~57);

상기 제2 지연 제어회로(22)의 더미 출력 신호가 더미배선 수단(42)을 통하여 공급되며, 상기 제어 신호와 해당 더미배선 수단의 출력 신호의 위상을 비교하여, 그 비교 결과에 의해 상기 제1 및 제2 지연 제어회로에서의 지연 시간을 제어하는 위상 비교회로(3)를 구비한 반도체 집적회로에 있어서.

상기 제1 지연 제어회로(21)의 출력단에서 상기 복수의 대상 회로(5;50 $\sim$ 57)의 입력단까지의 실제배선 (41)을 대칭성을 갖는 트리 상태로 배치하고, 상기 더미배선 수단(42)의 배선 부하의 크기를 제1 지연 제어회로(21)로부터 임의의 상기 대상 회로(5;50 $\sim$ 57)까지의 실제배선(41)의 배선 부하의 크기와 거의 일치시킨 것을 특징으로 하는 반도체 집적회로.

#### 청구항 5

제4항에 있어서, 상기 더미배선 수단(42)의 배선 길이을 상기 제1 지연 제어회로(21)로부터 하나의 상기 대상회로(5;50 $\sim$ 57)까지의 실제배선(41)의 배선 길이와 거의 일치시킨 것을 특징으로 하는 반도체 집적회로.

#### 청구항 6

제어 신호(CLK)가 공급되는 제1 및 제2 지연 제어회로(21, 22);

제1 지연 제어회로(21)의 출력 신호가 각각 실제배선(41)을 통하여 공급되는 복수의 대상회로(5;50~57);

상기 제2 지연 제어회로(22)의 더미 출력 신호가 더미배선 수단(42)을 통하여 공급되며, 상기 제어 신호와 해당 더미배선 수단의 출력 신호의 위상을 비교하여, 그 비교 결과에 의해 상기 제1 및 제2 지연 제어회로에서의 지연시간을 제어하는 위상 비교회로(3)를 구비한 반도체 집적회로에 있어서,

상기 복수의 대상 회로(5;50~57)는 복수 그룹으로 구성되며, 각 그룹은 상기 제I 지연 제어회로의 출력 신호를 받는 노드를 가지며, 상기 제I 지연 제어회로(21)의 출력단에서 상기 복수 그룹의 각 노드까지의 실제배선을 대칭성을 갖는 트리 상태로 배치하고, 상기 더미배선 수단(42)의 배선 부하의 크기를 제1 지 연 제어회로(21)로부터 하나의 상기 노드까지의 실제배선(41)의 배선 부하의 크기에 거의 일치시킨 것을 특징으로 하는 반도체 집적회로.

## 청구항 7

제6항에 있어서, 상기 더미배선 수단(42)의 배선 길이를 상기 제1 지연 제어회로(21)에서 하나의 상기 대상 회로(5;50~57)까지의 실제배선(41)의 배선 길이와 거의 일치시킨 것을 특징으로 하는 반도체 집적회로

## 청구항 8

제1항 내지 제7항중 어느 한 항에 있어서, 상기 제어 신호는 상기 각 대상회로에 공급하는 클럭 신호 (CLK)인 것을 특징으로 하는 반도체 집적회로.

#### 청구항 9

제1항 내지 제7항중 어느 한 항에 있어서, 상기 반도체 집적회로는 동기 DRAM이고, 상기 각 대상회로(5; 50~57)는 동기 DRAM의 데이터 출력 버퍼 회로인 것을 특징으로 하는 반도체 집적회로.

#### 청구항 10

제9항에 있어서, 상기 제어 신호는 상기 각 데이터 출력 버퍼 회로(5;50~ 57)의 인에이블 신호인 것을 특징으로 하는 반도체 집적회로.

## 청구항 11

제어 신호(CLK)가 공급되는 제1 및 제2 지연 제어회로(221, 222);

제I 지연 제어회로(221)의 출력 신호가 각각 실제배선(241)을 통하여 공급되는 복수의 대상 반도체 집적 히로(250~253):

상기 제2 지연 제어회로(222)의 더미 출력 신호가 더미배선 수단(242)을 통하여 공급되며, 상기 제어 신호와 해당 더미배선 수단의 출력 신호의 위상을 비교하여, 그 비교 결과에 의해 상기 제1 및 제2 지연 제어회로에서의 지연시간을 제어하는 위상 비교회로(203)를 구비한 반도체 집적회로 모듈에 있어서,

상기 제I 지연 제어회로(221)의 출력단에서 상기 복수의 대상 반도체 집적회로(250~253)의 각각의 입력 단까지의 각 실제배선(241)의 길이를 각각 거의 등거리로 하고, 상기 더미배선 수단(242)의 배선 부하의 크기를 제1 지연 제어회로(221)로부터 하나의 해당 대상 반도체 집적회로(250~253)까지의 실제배선(24 1)의 배선부하의 크기에 거의 일치시킨 것을 특징으로 하는 반도체 집적회로 모듈.

#### 청구항 12

제11항에 있어서, 상기 더미배선 수단(242)의 배선 길이를 상기 제1 지연 제어회로(221)에서 하나의 상기 대상 반도체 집적회로(250 $\sim$ 253)까지의 실제배선(241)의 배선 길이와 거의 일치시킨 것을 특징으로 하는 반도체 집적회로 모듈.

#### 청구항 13

제11항에 있어서, 상기 제1 지연 제어회로(221)의 출력단에서 상기 각 대상 반도체 집적회로(250~253)의 입력단까지의 각 실제배선(241)을 트리 상태로 구성하고, 각 분기부로부터 다음 분기부 또는 대상 반도체 집적회로의 입력단까지 각 분기 배선의 거리가 같게 한 것을 특징으로 하는 반도체 집적회로 모듈.

#### 청구항 14

제어 신호(CLK)가 공급되는 제1 및 제2 지연 제어회로(221, 222);

제I 지연 제어회로(221)의 출력 신호가 각각 실제배선(241)을 통하여 공급되는 복수의 대상 반도체 집적회로(250 $\sim$ 253);

상기 제2 지연 제어회로(222)의 더미 출력 신호가 더미배선 수단(242)을 통하여 공급되며, 상기 제어 신호와 해당 더미배선 수단의 출력 신호의 위상을 비교하여, 그 비교 결과에 의해 상기 제1 및 제2 지연 제어회로에서의 지연시간을 제어하는 위상 비교회로(203)를 구비한 반도체 집적회로 모듈에 있어서.

상기 제1 지연 제어회로(221)의 출력단에서 상기 복수의 대상 반도체 집적회로(250~253)의 입력단까지의실제배선(241)을 대칭성을 갖는 트리 상태로 배치하고,상기 더미배선 수단(242)의 배선 부하의 크기를 제1 지연 제어회로(221)에서 임의의 상기 대상 반도체 집적회로(250~253)까지의 실제배선(241)의 배선부하의 크기에 거의 일치시킨 것을 특징으로 하는 반도체 집적회로 모듈.

#### 청구항 15

제14항에 있어서, 상기 더미배선 수단(242)의 배선 길이를 상기 제1 지연 제어회로(221)에서 하나의 상기 대상 반도체 집적회로(250 $\sim$ 253)까지의 실제배선(241)의 배선 길이와 거의 일치시킨 것을 특징으로 하는 반도체 집적회로 모듈.

#### 청구항 16

제어 신호(CLK)가 공급되는 제1 및 제2 지연 제어회로(221, 222);

제1 지연 제어회로(221)의 출력 신호가 각각 실제배선(241)을 통하여 공급되는 복수의 대상 반도체 집적회로(250 $\sim$ 253);

상기 제2 지연 제어회로(222)의 더미 출력 신호가 더미배선 수단(242)을 통하여 공급되며, 상기 제어 신호와 해당 더미배선 수단의 출력 신호의 위상을 비교하여, 그 비교 결과에 의해 상기 제1 및 제2 지연 제어회로에서의 지연시간을 제어하는 위상 비교회로(203)를 구비한 반도체 집적회로 모듈에 있어서,

상기 복수의 대상 반도체 집적회로(250~253)는 복수 그룹으로 구성하며, 각 그룹은 상기 제1 지연 제어

회로의 출력 신호를 수신하는 노드를 구비하고, 상기 제I의 지연 제어회로(221)의 출력단에서 상기 복수의 그룹의 각 노드까지의 실제배선을 대칭성을 갖는 트리 상태로 배치하고, 상기 더미배선 수단(242)의 배선 부하의 크기를 제1 지연 제어회로(221)에서 하나의 상기 노드까지의 실제배선(241)의 배선 부하의 크기에 거의 일치시킨 것을 특징으로 하는 반도체 집적회로 모듈.

#### 청구항 17

제16항에 있어서, 상기 더미배선 수단(242)의 배선 길이를 상기 제1의 지연 제어회로(221)에서 하나의 상기 대상 반도체 집적회로(250~253)까지의 실제배선(241)의 배선 길이와 거의 일치시킨 것을 특징으로 하는 반도체 집적회로 모듈.

#### 청구항 18

제11항 내지 제17항중 어느 한 항에 있어서, 상기 반도체 집적회로 모듈는 메모리 모듈이고, 상기 각 대상 반도체 집적회로(250~253)는 메모리 모듈의 메모리 칩인 것을 특징으로 하는 반도체 집적회로 모듈.

#### 청구항 19

제11항 내지 제17항중 어느 한 항에 있어서, 상기 제어 신호는 클럭 신호이고, 상기 각 대상 반도체 집적회로(250~253)의 입력단은 클럭 입력 단자인 것을 특징으로 하는 반도체 집적회로 모듈.

#### 청구항 20

제어 신호(CLK)가 공급되는 제I 및 제2 지연 제어회로(321, 322);

제1 지연 제어회로(321)의 출력 신호가 각각 실제배선(341)을 통하여 공급되는 복수의 대상 반도체 집적 회로 모듈(350~353);

상기 제2 지연 제어회로(322)의 더미 출력 신호가 더미배선 수단(342)을 통하여 공급되며, 상기 제어 신호와 해당 더미배선 수단의 출력 신호의 위상을 비교하여, 그 비교결과에 의해 상기 제1 및 제2 지연 제어회로에서의 지연 시간을 제어하는 위상 비교회로(303)를 구비한 반도체 집적회로 시스템에 있어서,

상기 제1 지연 제어회로(321)의 출력단에서 상기 복수의 대상 반도체 집적회로 모듈(350~353)의 각각의 입력단까지의 각 실제배선(341)의 길이를 각각 거의 등거리로 하고, 상기 더미배선 수단(342)의 배선 부 하의 크기를 제1 지연 제어회로(321)에서 하나의 해당 대상 반도체 집적회로 모듈(350~353)까지의 실제 배선(241)의 배선 부하의 크기에 거의 일치시킨 것을 특징으로 하는 반도체 집적회로 시스템.

#### 청구항 21

제20항에 있어서, 상기 더미배선 수단(342)의 배선 길이를 상기 제1 지연 제어회로(321)에서 하나의 상기각 대상 반도체 집적회로 모듈(350~353)까지의 실제배선(341)의 배선 길이와 거의 일치시킨 것을 특징으로 하는 반도체 집적회로 시스템.

#### 청구항 22

제20항에 있어서, 상기 제1의 지연 제어회로(321)의 출력단에서 상기 각 대상 반도체 집적회로 모듈(350  $\sim$ 353)의 입력단까지의 각 실제배선(341)을 트리 상태로 구성하고, 각 분기부로부터 다음 분기부 또는 대상 반도체 집적회로 모듈의 입력단까지 각 분기 배선의 거리가 같도록 구성한 것을 특징으로 하는 반도체 집적회로 시스템.

## 청구항 23

제어 신호(CLK)가 공급되는 제1 및 제2 지연 제어회로(321, 322);

제1 지연 제어회로(321)의 출력 신호가 각각 실제배선(341)을 통하여 공급되는 복수의 대상 반도체 집적 회로 모듈(350~353);

상기 제2 지연 제어회로(322)의 더미 출력 신호가 더미배선 수단(342)을 통하여 공급되며, 상기 제어 신호와 해당 더미배선 수단의 출력 신호의 위상을 비교하여, 그 비교 결과에 의해 상기 제1 및 제2 지연 제어회로에서의 지연 시간을 제어하는 위상 비교회로(303)를 구비한 반도체 집적회로 시스템에 있어서,

상기 제1 지연 제어회로(321)의 출력단에서 상기 복수의 대상 반도체 집적회로 모듈(350~353)의 입력단까지의 실제배선(341)을 대청성을 갖는 트리 상태로 배치하고, 상기 더미배선 수단(342)의 배선 부하의 크기를 제1 지연 제어회로(321)에서 임의의 상기 대상 반도체 집적회로 모듈(350~353)까지의 실제배선(341)의 배선 부하의 크기에 거의 일치시킨 것을 특징으로 하는 반도체 집적회로 시스템.

#### 청구항 24

제23항에 있어서, 상기 더미배선 수단(342)의 배선 길이를 상기 제1 지연 제어회로(321)에서 하나의 상기 대상 반도체 집적회로 모듈(350~353)까지의 실제배선(341)의 배선 길이와 거의 일치시킨 것을 특징으로하는 반도체 집적회로 시스템.

#### 청구항 25

제어 신호(CLK)가 공급되는 제1 및 제2 지연 제어회로(321, 322);

제1 지연 제어회로(321)의 출력 신호가 각각 실제배선(341)을 통하여 공급되는 복수의 대상 반도체 집적회로 모듈(350 $\sim$ 353);

상기 제2 지연 제어회로(322)의 더미 출력 신호가 더미배선 수단(342)을 통하여 공급되며, 상기 제어 신

호와 해당 더미배선 수단의 출력 신호의 위상을 비교하여, 그 비교 결과에 의해 상기 제1 및 제2 지연 제 어회로에서의 지연 시간을 제어하는 위상 비교회로(303)를 구비한 반도체 집적회로 시스템에 있어서,

상기 복수의 대상 반도체 집적회로 모듈(350~353)은 복수 그룹으로 구성하며, 각 그룹은 상기 제1 지연 제어회로의 출력 신호를 받는 노드를 구비하며, 상기 제1 지연 제어회로(321)의 출력단에서 상기 복수 그룹의 각 노드 사이의 실제배선을 대칭성을 갖는 트리 상태로 배치하고, 상기 더미 배선 수단(342)의 배선 부하의 크기를 제1 지연 제어회로(321)에서 하나의 상기 노드까지의 실제배선(341)의 배선 부하의 크기에 거의 일치시킨 것을 특징으로 하는 반도체 집적회로 시스템.

#### 청구항 26

제25항에 있어서, 상기 더미배선 수단(342)의 배선 길이를 상기 제1 지연 제어회로(321)에서 하나의 상기 대상 반도체 집적회로 모듈(350~353)까지의 실제배선(341)의 배선 길이와 거의 일치시킨 것을 특징으로하는 반도체 집적회로 시스템.

### 청구항 27

제20항 내지 제26항중 어느 한 항에 있어서, 상기 각 대상 반도체 집적회로 모듈( $350\sim353$ )은 메모리 모듈이고, 각 대상 반도체 집적회로 모듈( $350\sim353$ )의 입력단은 클럭 입력 단자인 것을 특징으로 하는 반도체 집적회로 시스템.

#### 도면

도면3

## 도면6a

# 도면6b

## 도면6c

## 도면10a

## 도면10b

## 도면10c

도면13

# <u>5(50~57)</u>