(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-250489

(P2005-250489A)

(43) 公開日 平成17年9月15日(2005.9.15)

(51) Int.C1.<sup>7</sup>

F 1

テーマコード(参考)

G09G 3/28

G09G 3/28

J

5C058

G09G 3/20

G09G 3/20

611C

5C080

H04N 5/66

G09G 3/20

622B

5C580

G09G 3/20

622C

G09G 3/20

622D

審査請求 未請求 請求項の数 36 O L (全 17 頁) 最終頁に続く

(21) 出願番号

特願2005-63177(P2005-63177)

(22) 出願日

平成17年3月7日(2005.3.7)

(31) 優先権主張番号

10-2004-0015057

(32) 優先日

平成16年3月5日(2004.3.5)

(33) 優先権主張国

韓国(KR)

(71) 出願人

590001669

エルジー電子株式会社

大韓民国, ソウル特別市永登浦区汝矣島洞

20

(74) 代理人

110000165

グローバル・アイピー東京特許業務法人

(72) 発明者

ムン ソンハク

大韓民国, 152-774, ソウル, グローブ, シンドリムードン, デリム 2チャアパート, 201-1002

F ターム(参考) 5C058 AA11 BA04 BA33 BB09

5C080 AA05 BB05 DD12 DD17 FF12

HH04 HH05 JJ02 JJ03 JJ04

JJ06

5C580 AA03 BA03 BA14 BA19 BB22

FA06

(54) 【発明の名称】 プラズマディスプレイパネルの駆動装置及び駆動方法

(57) 【要約】 (修正有)

【課題】電磁波干渉を最小化することと共に安全性向上させるようにしたプラズマディスプレイパネルの駆動装置及び方法を提供する。

【解決手段】お互いに並んで形成される多数の走査電極及び維持電極と、サステイン期間の間走査電極に正極性及び負極性のサステインパルスを交番的に供給するための走査駆動部を備え、維持電極は基底電圧源に接続されいつも基底電位を維持する。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

複数の走査電極と、

前記複数の走査電極と並んで形成されると共に、基底電圧源に接続されて基底電位を維持する複数の維持電極と、

サステイン期間の間、前記複数の走査電極にサステインパルスを供給するための走査駆動部と、前記備えることを特徴とするプラズマディスプレイ装置。

**【請求項 2】**

前記走査駆動部は、

サステイン期間の間、前記複数の走査電極に第1極性及び第2極性のサステインパルスを交番的に供給することを特徴とする、請求項1記載のプラズマディスプレイ装置。 10

**【請求項 3】**

複数の走査電極と、

前記複数の走査電極と並んで形成されると共に、基底電圧源に接続されて基底電圧を維持する複数の維持電極と、

サステイン期間の間、前記複数の走査電極に第1極性及び第2極性のサステインパルスを交番的に供給するための走査駆動部と、

前記ことを特徴とするプラズマディスプレイ装置。

**【請求項 4】**

前記走査駆動部は、

第1極性のサステインパルスを前記複数の走査電極に供給するための第1スイッチング素子と、

第2極性のサステインパルスを前記複数の走査電極に供給するための第2スイッチング素子と、

前記複数の走査電極が基底電位を供給する第3スイッチング素子とを含むことを特徴とする、

請求項3記載のプラズマディスプレイ装置。 20

**【請求項 5】**

前記走査駆動部は、

前記第1スイッチング素子及び前記第2スイッチング素子と前記複数の走査電極との間に接続され、前記第1極性のサステインパルス及び前記第2極性のサステインパルスを走査電極に交番的に供給するための第4スイッチング素子をさらに含むことを特徴とする、請求項4記載のプラズマディスプレイ装置。 30

**【請求項 6】**

前記第1極性のサステインパルスと前記第2極性のサステインパルスは、互いに逆極性であることを特徴とする、請求項3記載のプラズマディスプレイ装置。

**【請求項 7】**

前記第1極性のサステインパルスは正極性であり、前記第2極性のサステインパルスは負極性であることを特徴とする、請求項6記載のプラズマディスプレイ装置。

**【請求項 8】**

前記第1スイッチング素子は、前記第1極性サステインパルス電源と前記複数の走査電極との間に配置されることを特徴とする、請求項3記載のプラズマディスプレイ装置。 40

**【請求項 9】**

前記第2スイッチング素子は、前記第2極性サステインパルス電源と前記複数の走査電極との間に配置されることを特徴とする、請求項3記載のプラズマディスプレイ装置。

**【請求項 10】**

前記第3スイッチング素子は、基底電圧源と前記複数の走査電極との間に配置されることを特徴とする、請求項3記載のプラズマディスプレイ装置。

**【請求項 11】**

前記走査駆動部は、前記第1極性サステインパルスを生成するために、前記第1スイチ

50

ング素子と前記第3スイチング素子を交番的に選択することを特徴とする、請求項4記載のプラズマディスプレイ装置。

【請求項12】

前記走査駆動部は、前記第2極性サステインパルスを生成するために前記第2スイチング素子と、前記第3スイチング素子を交番的に選択することを特徴とする、請求項4記載のプラズマディスプレイ装置。

【請求項13】

多数の走査電極と、

前記複数の走査電極と並んで形成されると共に、基底電圧源に接続されて基底電位を維持する複数の維持電極と、

サステイン期間の間、前記複数の走査電極に互いに違う極性のサステインパルスを交番的に供給するために別途の負極性電圧源を備える走査駆動部と、

を備えることを特徴とするプラズマディスプレイ装置。

【請求項14】

前記走査駆動部は、

第1極性のサステインパルスを前記多数の走査電極に供給するための第1スイチング素子と、

第2極性のサステインパルスを前記多数の走査電極に供給するための第2スイチング素子と、

前記多数の走査電極に基底電位を供給する第3スイチング素子と、

を備えることを特徴とする請求項13記載のプラズマディスプレイ装置。

【請求項15】

前記走査駆動部は

前記第1極性のサステインパルス及び前記第2極性のサステインパルスを走査電極に交番的に供給するための第4スイチング素子及び第5スイチング素子をさらに含むことを特徴とする、請求項14記載のプラズマディスプレイ装置。

【請求項16】

前記第1極性のサステインパルスと前記第2極性のサステインパルスとは、逆極性であることを特徴とする、請求項14記載のプラズマディスプレイ装置。

【請求項17】

前記第1極性のサステインパルスは正極性であり、前記第2極性のサステインパルスは負極性であることを特徴とする、請求項16記載のプラズマディスプレイ装置。

【請求項18】

前記第1スイチング素子は、前記第1極性サステインパルス電源と、前記複数の走査電極との間に配置されることを特徴とする、請求項14記載のプラズマディスプレイ装置。

【請求項19】

前記第2スイチング素子は、前記第2極性サステインパルス電源と、前記複数の走査電極の間に配置されることを特徴とする、請求項14記載のプラズマディスプレイ装置。

【請求項20】

前記第3スイチング素子は、基底電圧源と、前記複数の走査電極との間に配置されることを特徴とする、請求項14記載のプラズマディスプレイ装置。

【請求項21】

前記走査駆動部は、前記第1極性サステインパルスを生成するために、前記第1スイチング素子と前記第3スイチング素子とを交番的に選択することを特徴とする、請求項14記載のプラズマディスプレイ装置。

【請求項22】

前記走査駆動部は前記第2極性サステインパルスを生成するために、前記第2スイチング素子と前記第3スイチング素子を交番的に選択することを特徴とする、請求項14記載のプラズマディスプレイ装置。

**【請求項 2 3】**

前記走査駆動部は、前記第2極性サステインパルスを生成するために、前記第2スイチング素子と前記第3スイチング素子とを交番的に選択することを特徴とする、請求項14記載のプラズマディスプレイ装置。

**【請求項 2 4】**

前記走査駆動部は、前記第2極性サステインパルスを生成するために、前記第4スイチング素子と前記第5スイチング素子とを交番的に選択することを特徴とする、請求項22記載のプラズマディスプレイ装置。

**【請求項 2 5】**

サーブフィールドのサステイン期間の間、複数の走査電極に、正極性及び負極性のサステインパルスを交番的に印加する段階と、10

前記サステイン期間の間、前記複数の走査電極と並んで形成される多数の維持電極に基底電位を供給する段階と、

を含むことを特徴とするプラズマディスプレイパネルの駆動方法。

**【請求項 2 6】**

前記負極性のサステインパルスは、別途の負極性電圧源から印加されることを特徴とする、請求項25記載のプラズマディスプレイパネルの駆動方法。

**【請求項 2 7】**

前記複数の維持電極を基底電圧源に接続して、前記複数の維持電極を基底電位を維持することを特徴とする、請求項25記載のプラズマディスプレイパネルの駆動方法。20

**【請求項 2 8】**

前記走査電極にサステインパルスを交番的に印加する段階は、

正極性パルスを印加する段階と、

基底電圧パルスを印加する段階と、

負極性パルスを印加する段階と、

を含むことを特徴とするプラズマディスプレイパネルの駆動方法。

**【請求項 2 9】**

第1走査電極と、

前記第1走査電極に沿って配置され、基底電圧に維持された第1維持電極と、

前記第1走査電極に接続された第1スイッチング素子と、30

前記第1スイッチング素子に並列接続された第1ダイオードと、

前記第1スイッチング素子と正極性電圧源との間に接続された第2スイッチング素子と、

前記第1スイッチング素子と負極性電圧源との間に接続された第3スイッチング素子と、

を備えるプラズマディスプレイ装置。

**【請求項 3 0】**

サステイン期間において、

前記第2スイッチング素子及び前記第1ダイオードを介して、前記正極性電圧源と前記第1走査電極とを導通させ、40

前記第3スイッチング素子及び前記第1スイッチング素子を介して、前記負極性電圧源と前記第1走査電極とを導通させるように、

前記第1乃至第3スイッチング素子を制御するタイミング制御部をさらに備える、

請求項29に記載のプラズマディスプレイ装置。

**【請求項 3 1】**

第2走査電極と、前記第2走査電極に沿って配置され基底電圧に維持された第2維持電極をさらに備え、

前記タイミング制御部は、

アドレス期間において、前記第3スイッチング素子を導通させた状態で、前記第1スイッチング素子を順次導通させて、前記第1走査電極及び前記第2走査電極に順次に正極性電50

圧源を導通させるように、前記第1及び第3スイッチング素子をさらに制御する、請求項31に記載のプラズマディスプレイ装置。

**【請求項32】**

前記第1スイッチング素子と基底電圧源との間に接続された第4スイッチング素子をさらに備える、請求項29に記載のプラズマディスプレイ装置。

**【請求項33】**

サステイン期間において、

前記第2スイッチング素子及び前記第1ダイオードを介して、前記正極性電圧源と前記第1走査電極とを導通させ、

前記第4スイッチング素子及び前記第1スイッチング素子を介して、前記基底電圧源と前記第1走査電極とを導通させ、

前記第3スイッチング素子及び前記第1スイッチング素子を介して、前記負極性電圧源と前記第1走査電極とを導通させるように、

前記第1乃至第4スイッチング素子を制御するタイミング制御部をさらに備える、

請求項32に記載のプラズマディスプレイ装置。

**【請求項34】**

第1走査電極と、

前記第1走査電極に沿って配置され、基底電圧に維持された第1維持電極と、

前記第1走査電極に接続された第1スイッチング素子と、

前記第1スイッチング素子に並列接続された第1ダイオードと、

前記第1スイッチング素子と正極性電圧源との間に接続された第2スイッチング素子と、

前記第1スイッチング素子と基底電圧源との間に接続された第3スイッチング素子と、

前記第1走査電極に接続された第4スイッチング素子と、

前記第4スイッチング素子と負極性電圧源との間に接続された第5スイッチング素子と、

を備えるプラズマディスプレイ装置。

**【請求項35】**

サステイン期間において、

前記第2スイッチング素子及び前記第1ダイオードを介して、前記正極性電圧源と前記第1走査電極とを導通させ、

前記第3スイッチング素子及び前記第1スイッチング素子を介して、前記基底電圧源と前記第1走査電極とを導通させ、

前記第5スイッチング素子及び前記第4スイッチング素子を介して、前記負極性電圧源と前記第1走査電極とを導通させるように、

前記第1乃至第5スイッチング素子を制御するタイミング制御部をさらに備える、

請求項33に記載のプラズマディスプレイ装置。

**【請求項36】**

第2走査電極と、前記第2走査電極に沿って配置され基底電圧に維持された第2維持電極をさらに備え、

前記タイミング制御部は、

アドレス期間において、前記5スイッチング素子を導通させた状態で、前記第1スイッチング素子を順次導通させて、前記第1走査電極及び前記第2走査電極に順次に正極性電圧源を導通させるように、前記第1及び第5スイッチング素子をさらに制御する、

請求項35に記載のプラズマディスプレイ装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

10

20

30

40

50

本発明は、プラズマディスプレイパネルの駆動装置及び駆動方法に関し、特に、電磁波干渉を最小化することと共に安全性を向上させるようにしたプラズマディスプレイパネルの駆動装置及び駆動方法に関する。

#### 【背景技術】

##### 【0002】

プラズマディスプレイパネル(Plasma Display Panel :以下 "PDP"だとする)は、He+Xe、Ne+XeまたはHe+Xe+Neなどの不活性混合ガスの放電の時発生する147nmの紫外線によって蛍光体を発光させることで、文字またはグラフィックを含んだ画像を表示する。このようなPDPは、薄膜化と大型化が容易するだけでなく、最近の技術開発に伴い、大きく向上した画質を提供する。特に、3電極交流面放電型PDPは、放電の時表面に壁電荷が蓄積されて放電によって発生されるスパッタリング(SPUTTERING)から電極を保護するため、低電圧駆動と長寿命の長所を持つ。10

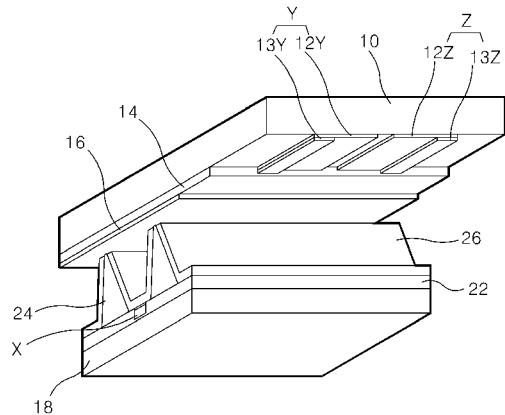

##### 【0003】

図1を参照すれば、3電極交流面放電型PDPの放電セルは上部基板10上に形成された走査電極(Y)及び維持電極(Z)と、下部基板18上に形成されたアドレス電極(X)を備える。走査電極(Y)と維持電極(Z)それぞれは、透明電極12Y、12Zと、透明電極12Y、12Zの線幅より小さな線幅を持って透明電極の一側端に形成される金属バス電極13Y、13Zとを含む。

##### 【0004】

透明電極12Y、12Zは、通常インジウムティンオキサイド(Indium-Tin-Oxide : ITO)で上部基板10上に形成される。金属バス電極13Y、13Zは、通常クロム(Cr)などの金属で透明電極12Y、12Z上に形成されて抵抗が高い透明電極12Y、12Zによる電圧降下を減らす役目をする。20

##### 【0005】

走査電極(Y)と維持電極(Z)が並んで形成された上部基板10には、上部誘電体層14と保護膜16が積層される。上部誘電体層14にはプラズマ放電の時発生された壁電荷が蓄積される。保護膜16はプラズマ放電の時発生されたスパッタリングによる上部誘電体層14の損傷を防止することと共に2次電子の放出効率を高めるようになる。保護膜16は、通常、酸化マグネシウム(MgO)が利用される。

##### 【0006】

アドレス電極(X)が形成された下部基板18上には下部誘電体層22、隔壁24が形成されている。下部誘電体層22と隔壁24表面には、蛍光体層26が塗布される。30

##### 【0007】

アドレス電極(X)は、走査電極(Y)及び維持電極(Z)と交差される方向に形成される。隔壁24はアドレス電極(X)と並んで形成されて放電によって生成された紫外線及び可視光が、隣接した放電セルに漏洩することを防止する。蛍光体層26は、プラズマ放電の時発生された紫外線によって励起されて赤、緑または青色の中の一つの可視光線を発生する。

##### 【0008】

上/下部基板10、18と、隔壁24の間に設置された放電空間には不活性混合ガスが注入される。40

##### 【0009】

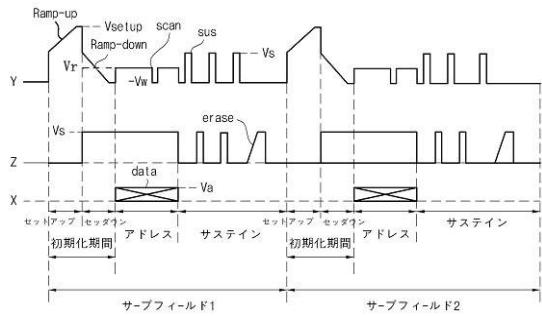

このようなPDPは画像の階調を具現するために、一のフレームを発光回数が異なる複数のサブフィールドに分割して時分割駆動する。各サブフィールドは、前画面を初期化させるための初期化期間と、走査ラインを選択して選択された走査ラインでセルを選択するためのアドレス期間と、放電回数によって階調を具現するサステイン期間とに分けられる。

##### 【0010】

ここで初期化期間は、上昇ランプ波形が供給されるセットアップ期間と、下降ランプ波形が供給されるセッダウン期間とに分けられる。例えば256階調で画像を表示しよう50

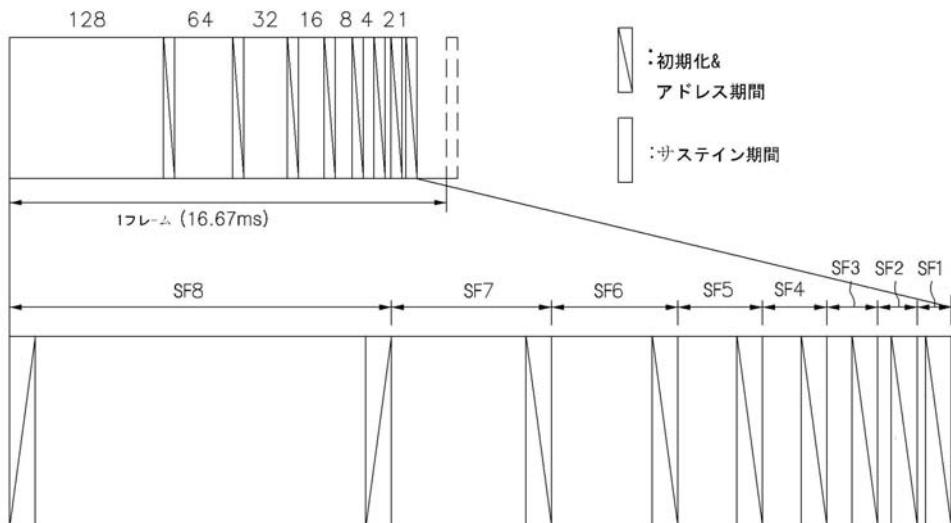

とする場合には、図2のように1/60秒にあたるフレーム期間(16.67ms)は、8個のサーブフィールド(SF1乃至SF8)で分けられる。8個のサーブフィールド(SF1乃至SF8)それぞれは、前述したように初期化期間と、アドレス期間と、サステイン期間とに分けられる。各サーブフィールドの初期化期間とアドレス期間とは各サーブフィールド毎に等しい一方、サステイン期間は各サーブフィールドで $2^n$ (n=0, 1, 2, 3, 4, 5, 6, 7)の割合で増加される。

#### 【0011】

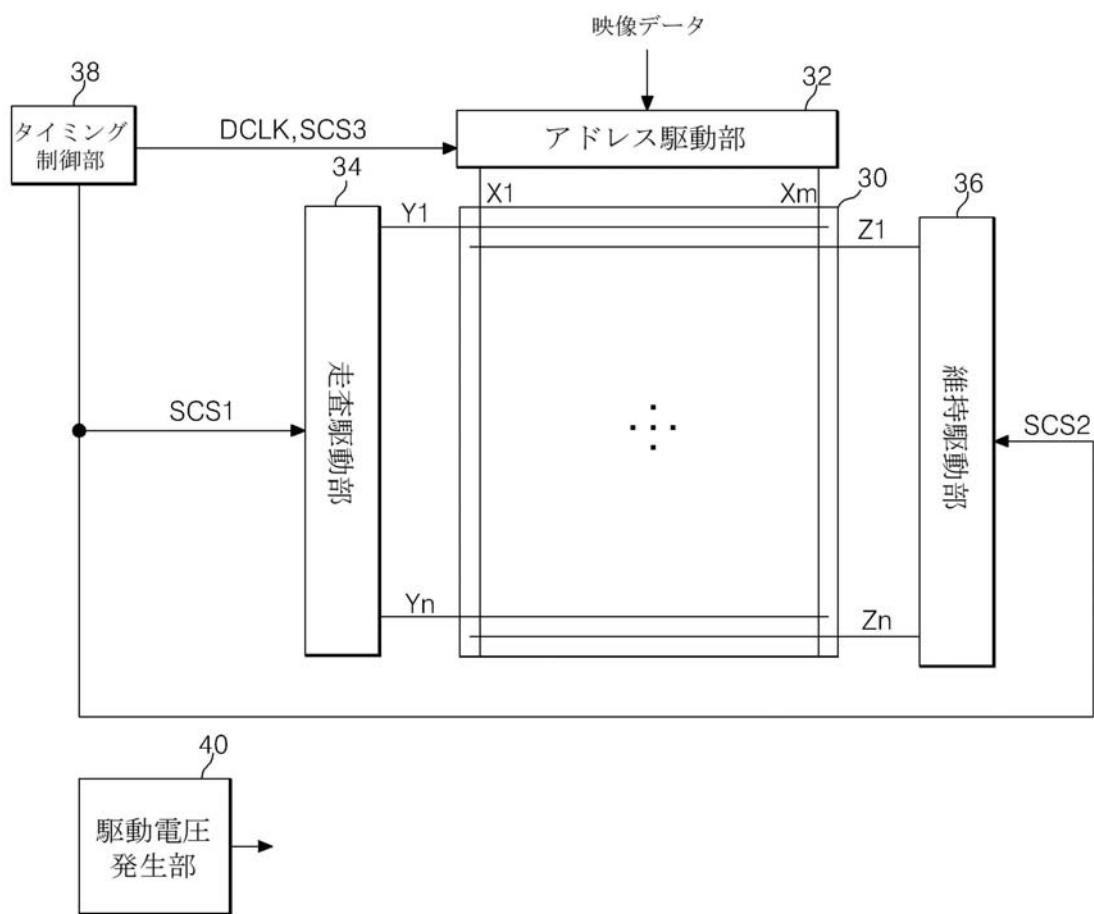

図3は従来のプラズマディスプレイパネルの駆動装置を示す図である。

#### 【0012】

図3を参照すれば従来のPDPの駆動装置は、パネル30に設置されたアドレス電極(X1乃至Xm)を駆動するためのアドレス駆動部32と、パネル30に設置された走査電極(Y1乃至Yn)を駆動するための走査駆動部34と、パネル30に設置された維持電極(Z1乃至Zn)を駆動するための維持駆動部36と、駆動部32, 34, 36で駆動電圧を供給するための駆動電圧発生部40と、駆動部32, 34, 36で制御信号(SCS1乃至SCS3)を供給するためのタイミング制御部38を備える。10

#### 【0013】

駆動電圧発生部40は、図4のような駆動波形が生成されることができるよう色々な駆動電圧を生成してアドレス駆動部32、走査駆動部34及び維持駆動部36に供給する。例えば、駆動電圧発生部40は、Vsetup、-Vw, Vr及びVsなどの電圧を生成して走査駆動部34に供給してVs電圧を生成して維持駆動部36に供給する。そして駆動電圧発生部40は、Vaの電圧を生成してアドレス駆動部32に供給する。20

#### 【0014】

タイミング制御部38は、図4のような駆動波形が生成されることができるよう色々なスイチング制御信号を生成してアドレス駆動部32、走査駆動部34及び維持駆動部36に供給する。例えばタイミング制御部38は、第1スイチング制御信号(SCS1)を生成して走査駆動部34に供給して、第2スイチング制御信号(SCS2)を生成して維持駆動部36に供給する。そしてタイミング制御部38は、第3スイチング制御信号(SCS3)及びデータクロッククロック(DCLK)をアドレス駆動部32に供給する。

#### 【0015】

アドレス駆動部32は、タイミング制御部38から供給されるデータクロッククロック(DCLK)及び第3スイチング制御信号(SCS3)によって制御されながら、外部から供給される映像データ(data)をアドレス電極(X1乃至Xm)に供給する。30

#### 【0016】

走査駆動部34は、タイミング制御部38から供給される第1スイチング制御信号(SCS1)によって制御されながら、リセットパルス、スキャンパルス(scan)及びサステインパルス(sus)を走査電極(Y1乃至Ym)に供給する。

#### 【0017】

維持駆動部36は、タイミング制御部38から供給される第2スイチング制御信号(SCS2)によって制御されながら、正極性電圧(Vs)、サステインパルス(sus)及び消去パルス(erase)を維持電極(Z1乃至Zm)に供給する。40

#### 【0018】

電極に供給される駆動波形を図4を参照して詳細に説明すれば、先に初期化期間の中セットアップ期間には、すべての走査電極(Y)に上昇ランプ波形(Ramp-up)が共に印加される。この上昇ランプ波形(Ramp-up)によって全画面のセル内には微弱な放電が起きたようになって、セル内に壁電荷が生成される。

#### 【0019】

セッダウン期間には、上昇ランプ波形(Ramp-up)が供給された後、上昇ランプ波形(Ramp-up)のピーク電圧より低い正極性電圧から下降する下降ランプ波形(Ramp-down)が全走査電極(Y)に共に印加される。下降ランプ波形(Ramp-down)は、セル内に微弱な消去放電を起こすことことで、セットアップ放電によって生成された壁電荷及び空間電荷の中で、不要電荷

を消去させ、全画面のセル内にアドレス放電に必要な壁電荷を均一に残留させる。

#### 【0020】

アドレス期間には、負極性スキャンパルス(scan)が走査電極(Y)に順次に印加されることと共に、アドレス電極(X)に正極性のデータパルス(data)が印加される。このスキャンパルス(scan)とデータパルス(data)の電圧の差と、初期化期間に生成された壁電圧が加わりながら、データパルス(data)が印加されるセル内にはアドレス放電が発生される。アドレス放電によって選択されたセル内には壁電荷が生成される。

#### 【0021】

一方、セッダウンド期間とアドレス期間の間に、維持電極(Z)には、サステイン電圧レベル(Vs)の正極性直流電圧が供給される。

10

#### 【0022】

サステイン期間には、走査電極(Y)と維持電極(Z)に交番的にサステインパルス(sus)が印加される。そして、アドレス放電によって選択されたセルでは、セル内の壁電圧とサステインパルス(sus)とが加わりながら、毎サステインパルス(sus)が印加されるごとに、走査電極(Y)と維持電極(Z)の間に面放電形態でサステイン放電が起きる。最後に、サステイン放電の完了した後には、パルス幅が小さな消去ランプ波形(erase)が維持電極(Z)に供給されて、セル内の壁電荷を消去させる。

#### 【0023】

このような従来のPDPでサステイン期間の間、走査電極(Y)及び維持電極(Z)は交番的にサステインパルス(sus)を供給受ける。走査電極(Y)にサステインパルス(sus)が供給される時、維持電極(Z)に基底電圧(GND)が供給される一方、維持電極(Y)にサステインパルス(sus)が供給される時、走査電極(Z)に基底電圧(GND)が供給される。すなわち、特定電極(YまたはZ)にサステインパルス(sus)が供給される時、高い電流が流れるため、サステインパルス(sus)が供給されない残り電極は、基底電圧源(GND)に接続されて動作を安定化させるようになる。しかし、サステイン期間の間、走査電極(Y)及び維持電極(Z)がサステインパルス(sus)及び基底電圧源(GND)に交番的に接続されるために、走査駆動部34及び維持駆動部36内部に含まれたスイチング素子のスイチング動作回数が多く、これに従って高いEMIが発生される問題点が発生される。そして従来には走査電極(Y)及び維持電極(Z)が基底電圧(GND)と接続されるために多くのスイチング素子を経由するから(すなわち線路が長くなるから)追加的なノイズが発生される問題点が発生される。

20

30

#### 【0024】

また、一般的にPDPの動作を安定化させるためには走査電極(Y)及び維持電極(Z)中交互に何れか一つの電極を基底電圧源(GND)に接続して電圧レベルを安定化させなければならない。実際には、走査電極(Y)及び維持電極(Z)中どの一つの電極が基底電圧源(GND)に接続されれば外部ノイズの流入及び/またはEMIの発生等を最小化することができる。しかし従来には、走査電極(Y)及び維持電極(Z)に色々な駆動波形を供給するからPDPの安全性を確保すること困難な実情である。

40

#### 【0025】

そして従来には走査駆動部34及び維持駆動部36は走査電極(Y)及び維持電極(Z)それぞれにプッシュプル型(push-pull)に接続されるスイチング素子を備える。このようにプッシュプル型でスイチング素子が接続されれば多くのスイチング素子が必要になって製造費用が高くなることとともに、漏洩電流等が発生される問題点がある。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0026】

本発明の目的は電磁波干渉を最小化することとともに安全性を向上させようとしたプラズマディスプレイパネルの駆動装置及び方法を提供するのである。

#### 【課題を解決するための手段】

#### 【0027】

本発明のプラズマディスプレイパネルの駆動装置はお互いに並んで形成される多数の走

50

査電極及び維持電極とサステイン期間の間走査電極で正極性及び負極性のサステインパルスを交番的に供給するための走査駆動部を備えて維持電極は基底電圧源に接続されいつも基底電位を維持する。

#### 【0028】

前記走査駆動部は正極性のサステイン電圧源と走査電極の間に設置される第1スイチング素子と負極性のサステイン電圧源と走査電極の間に設置される第2スイチング素子と基底電圧源と走査電極の間に設置される第3スイチング素子と第1乃至第3スイチング素子の共通端子と走査電極の間に並列でそれぞれ設置される第4スイチング素子及びダイオードを備える。

#### 【0029】

前記第1スイチング素子がターン-オンすると正極性サステイン電圧源の電圧が第1スイチング素子及びダイオードを経由して正極性のサステインパルスとして走査電極に供給される。

#### 【0030】

前記正極性のサステインパルスが供給された後第3スイチング素子及び第4スイチング素子がターン-オンされると共に負極性のサステインパルスが供給された後第3スイチング素子がターン-オンされて走査電極で基底電圧源の電圧が供給される。

#### 【0031】

前記走査駆動部は正極性のサステイン電圧源と走査電極の間に設置される第1スイチング素子と負極性のサステイン電圧源と走査電極の間に設置される第2スイチング素子と基底電圧源と走査電極の間に設置される第3スイチング素子と第2スイチング素子と走査電極の間にそれぞれ設置される第4スイチング素子らと、第1スイチング素子及び第3スイチング素子の共通端子と走査電極の間に並列でそれぞれ設置される第5スイチング素子及びダイオードを備える。

#### 【0032】

前記第1スイチング素子がターン-オンされると正極性サステイン電圧源の電圧が第1スイチング素子及びダイオードを経由して正極性のサステインパルスとして走査電極に供給される。

#### 【0033】

前記第2スイチング素子及び第4スイチング素子がターン-オンされると負極性のサステインパルスが走査電極に供給される。

#### 【0034】

前記正極性のサステインパルスが供給された後第3スイチング素子及び第5スイチング素子がターン-オンされると共に負極性のサステインパルスが供給された後第3スイチング素子がターン-オされて走査電極に基底電圧源の電圧が供給される。

#### 【0035】

本発明のプラズマディスプレイパネルの駆動方法はサーブフィールドのサステイン期間の間走査電極に正極性及び負極性のサステインパルスが交番的に供給される段階とソスピルド期間の間走査電極と並んで形成される維持電極に基底電位が供給される段階を含む。

#### 【発明の効果】

#### 【0036】

本発明では維持電極がいつも基底電圧を維持するから外部のイズ流入及びEMI発生などを最小化することができる。また、本発明では維持電極がいつも基底電圧を維持するから、すなわち電流の流れ経路が短縮されるから追加的なノイズの発生抑制等プラズマディスプレイパネルの安全性を確保することができる。

#### 【発明を実施するための最良の形態】

#### 【0037】

以下本発明の実施形態らを添付した図面に基づいて詳細に説明する。

#### 【0038】

10

20

30

40

50

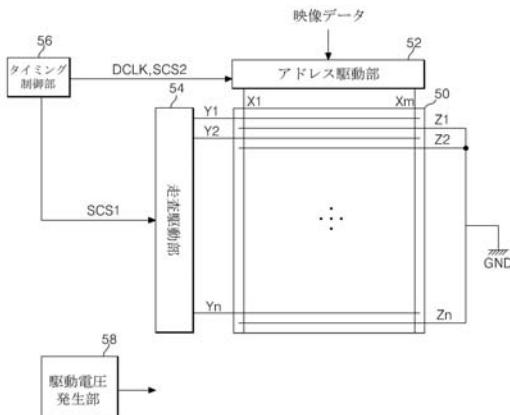

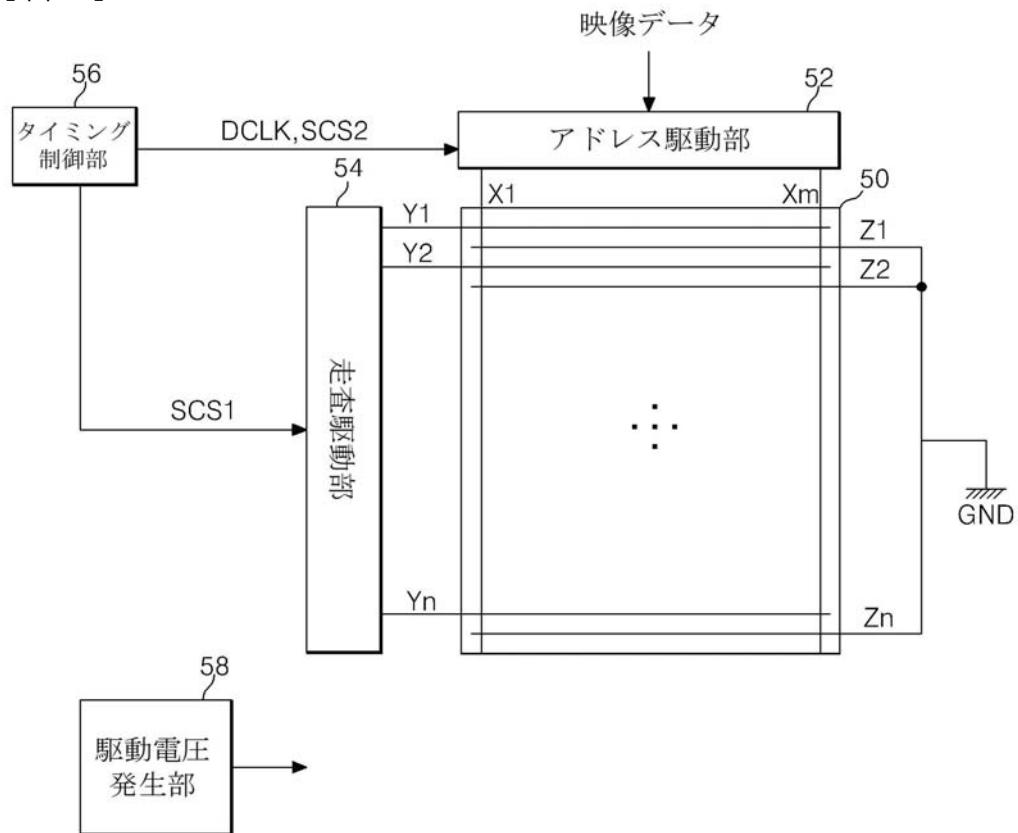

図5は、本発明の実施形態によるプラズマディスプレイパネルの駆動装置を示す図である。

#### 【0039】

図5を参照すれば、本発明の実施形態によるPDPの駆動装置は、パネル50に設置されたアドレス電極(X1乃至Xm)を駆動するためのアドレス駆動部52と、パネル50に設置された走査電極(Y1乃至Yn)を駆動するための走査駆動部54と、駆動部52、54に駆動電圧を供給するための駆動電圧発生部58と、駆動部52、54に制御信号(SCS1、SCS2)を供給するためのタイミング制御部56とを備える。ここでパネル50に設置された維持電極(Z1乃至Zn)は、基底電圧源(GND)に接続される。(すなわち、維持駆動部が省略される)

駆動電圧発生部58は、所定の駆動波形が生成されるようにより複数の駆動電圧を生成して、アドレス駆動部52及び走査駆動部54に供給する。10

#### 【0040】

タイミング制御部56は、所定の駆動波形が生成されるようにより複数のスイチング制御信号を生成してアドレス駆動部52及び走査駆動部54に供給する。例えばタイミング制御部56は、第1スイチング制御信号(SCS1)を生成して走査駆動部54に供給する。そしてタイミング制御部56は、第2スイチング制御信号(SCS2)及びデータクロック(DCLK)を生成してアドレス駆動部52に供給する。

#### 【0041】

アドレス駆動部52は、タイミング制御部56から供給されるデータクロック(DCLK)及び第2スイチング制御信号(SCS2)によって制御されながら、外部から供給される映像データ(data)をアドレス電極(X1乃至Xm)に供給する。20

#### 【0042】

走査駆動部54は、タイミング制御部56から供給される第1スイチング制御信号(SCS1)によって制御されながらセットパルス、スキャンパルス、負極性及び正極性のサステインパルスを走査電極(Y1乃至Ym)に供給する。ここで走査駆動部54は、常に基底電圧(GND)を供給受ける維持電極(Z1乃至Zn)と走査電極(Y1乃至Ym)との間でサステイン放電を起こすために、走査電極(Y1乃至Ym)に負極性及び正極性に交番されるサステインパルスを供給する。

#### 【0043】

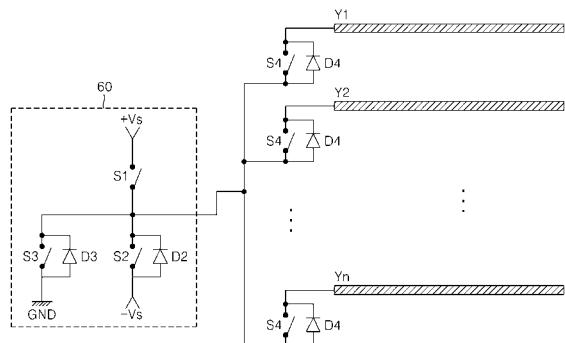

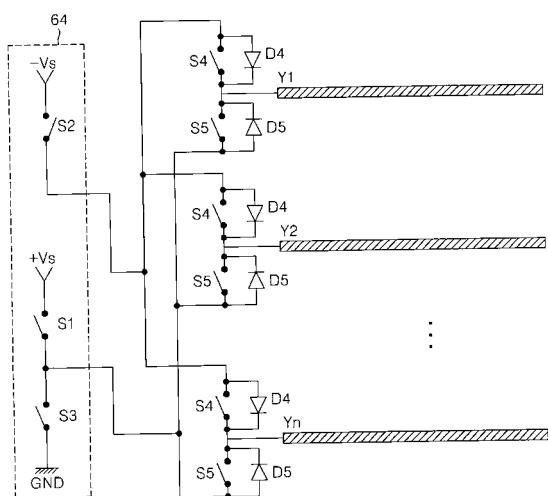

図6は、図5に示した走査駆動部を詳細に示す図である。30

#### 【0044】

図6に示したのように、走査駆動部54は、駆動電圧供給部60と、走査電極(Y1乃至Ym)それぞれと接続されるように設置される第4スイッチ(S4)を備える。第4スイッチ(S4)は、駆動電圧供給部60と走査電極(Y)の間に設置されて、駆動電圧供給部60からの駆動電圧を走査電極(Y)に供給する。ここで第4スイッチ(S4)は、オープンドレーン(open drain)方式に接続される。

#### 【0045】

この時、本発明によるスイッチはMOS TR、FET、IGBT、SCRなどによって具現が可能である。第4スイッチ(S4)がオープンドレーン方式に接続されれば走査電極(Y1乃至Yn)の間に漏洩電流などが発生されることを防止することができる。また、第4スイッチ(S4)は、それぞれの走査電極(Y)ごとに一つずつ設置されるから、走査駆動部54に実装される部品数を最小化することができる。そして、駆動電圧供給部60と走査電極(Y)の間にはそれぞれの第4スイッチ(S4)と並列に接続される第4ダイオード(D4)がさらに設置される。(ここで第4ダイオード(D4)は第4スイッチ(S4)の内部ダイオードまたは追加的に設置される外部ダイオードの何れで有っても良い。) 第4ダイオード(D4)は、駆動電圧供給部60からの駆動電圧を走査電極(Y)で供給すると共に、走査電極(Y)からの駆動電圧が駆動電圧供給部60に供給されることを防止するように設置される。即ち、走査電極Yから駆動電圧供給部60に電流が逆流することを防止する。40

#### 【0046】

駆動電圧供給部60は、正極性のサステイン電圧源(+Vs)と第4スイッチ(S4)の間に接50

続される第1スイッチ(S1)と、負極性のサステイン電圧源(-Vs)と第4スイッチ(S4)の間に接続される第2スイッチ(S2)と、基底電圧源(GND)と第4スイッチ(S4)の間に接続される第3スイッチ(S3)とを備える。第1スイッチ(S1)乃至第3スイッチ(S3)は、タイミング制御部56の制御によってターン-オン及びターン-オフされる。

#### 【0047】

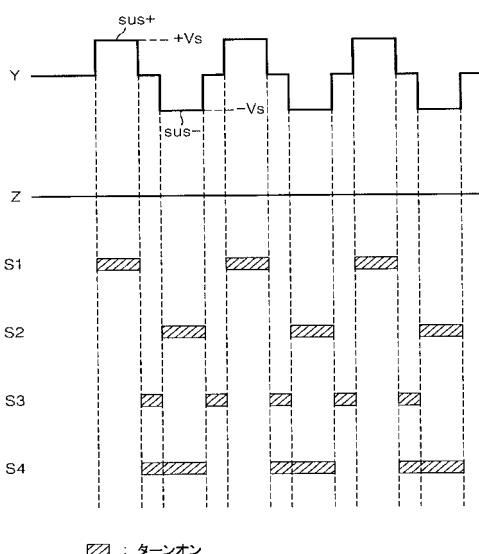

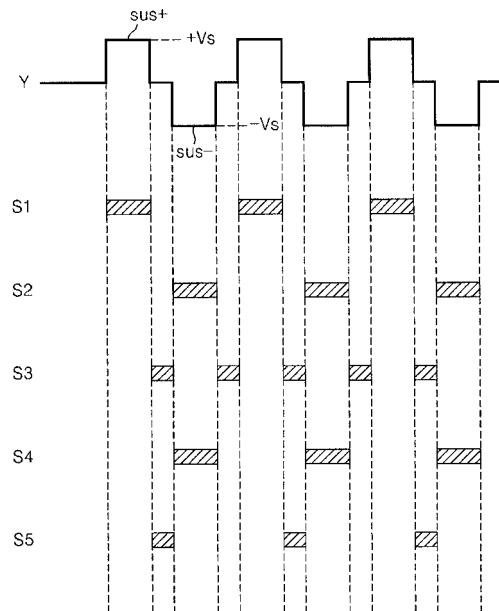

図7は、図6に示したスイチングのタイミング図に対応して、走査電極に供給されるサステインパルスを示す図である。

#### 【0048】

図7を参照して、走査駆動部54からサステインパルスが供給される過程を詳細に説明する。図示されたのように、本発明のサステイン期間の間、維持電極(Z)は基底電位(GND)に維持して、走査電極(Y)には、正極性サステインパルス(sus+)及び負極性サステインパルス(sus-)を交番的に供給する(実際には、正極性及び負極性の電圧(+Vs、-Vs)の間には基底電圧(GND)が所定時間供給される)。そして、先立つアドレス期間に選択されたセル内の壁電圧と、正極性または負極性のサステインパルス(sus+、sus-)の電圧値が加わりながら、毎サステインパルス(sus+、sus-)が印加されるごとに、走査電極(Y)と維持電極(Z)との間に面放電形態でサステイン放電が起きるようになる。

#### 【0049】

これを詳細に説明すれば、先に正極性サステインパルス(sus+)が供給される時、第1スイッチ(S1)がターン-オンされる。第1スイッチ(S1)がターン-オンされると、正極性サステイン電圧源(+Vs)の電圧が第1スイッチ(S1)及び第4ダイオード(D4)を経由して走査電極(Y1乃至Yn)に供給される。この時走査電極(Y1乃至Yn)には、正極性のサステインパルス(sus+)が供給される。

#### 【0050】

走査電極(Y1乃至Yn)に正極性のサステインパルス(sus+)が供給された後、第3スイッチ(S3)及び第4スイッチ(S4)がターン-オンされる。第3スイッチ(S3)がターン-オンされると、基底電圧源(GND)の電圧が第3スイッチ(S3)及び第4スイッチ(S4)を経由して走査電極(Y1乃至Yn)に供給される。

#### 【0051】

走査電極(Y1乃至Yn)に基底電圧(GND)が供給された後、第3スイッチ(S3)がターン-オフされる共に、第2スイッチ(S2)がターン-オンされる。第2スイッチ(S2)がターン-オンされると、負極性サステイン電圧源(-Vs)の電圧が第2スイッチ(S2)及び第4スイッチ(S4)を経由して走査電極(Y1乃至Yn)に供給される。この時、走査電極(Y1乃至Yn)には、負極性のサステインパルス(sus-)が供給される。

#### 【0052】

走査電極(Y1乃至Yn)に負極性のサステインパルス(sus-)が供給された後、第3スイッチ(S3)がターン-オンされると共に、第2スイッチ(S2)及び第4スイッチ(S4)がターン-オフされる。第3スイッチ(S3)がターン-オフされると、第3スイッチ(S3)及び第4ダイオード(D4)を経由して走査電極(Y1乃至Yn)に基底電圧(GND)が供給される。実際に本発明では、このような過程を繰り返しながら走査電極(Y1乃至Yn)に正極性または負極性のサステインパルス(sus+, sus-)を交番的に供給する。

#### 【0053】

一方、アドレス期間には、第2スイッチ(S2)がターン-オン状態を維持する。そして、第2スイッチ(S2)がターン-オン状態を維持する状態で、第4スイッチ(S4)が順にターン-オンされながら、各走査電極(Y)に順にスキャンパルス(scan)を供給するようになる。

#### 【0054】

この時、アドレス駆動部52は、スキャンパルス(scan)に同期されるデータパルスをデータライン(X1乃至Xm)に供給する。

#### 【0055】

このような本発明では、維持電極(Z)は常に(ひとつのサーブフィールド期間の間)基底

10

20

30

40

50

電圧源(GND)の電圧を供給受ける。このように維持電極(Z)が常に基底電圧源(GND)の供給を受ければ、外部ノイズの流入及び/またはEMIの発生等を最小化することができ、これに従ってPDPの安全性をより向上させることができる。

#### 【0056】

そして本発明では、維持電極(Z)は常に基底電圧源(GND)に接続されるから、従来のような維持駆動部を省略することができ、これに従って、維持駆動部の駆動によって生成されるEMIなどの発生を防止することができる。そして本発明では、維持電極(Z)が直接的に基底電圧源(GND)に接続されるから、ノイズの追加発生を抑制することができる。また本発明では、それぞれの走査電極(Y)に一つのスイッチング素子(S4)だけがオフドレーン方式に接続されるから、部品数を最小化して製造費用を節減することと共に電極間漏洩電流が発生することを防止することができる。10

#### 【0057】

一方、本発明では、走査駆動部54は様々な形態で構成されることがある。例えば本発明の走査駆動部54は、図8のように構成されることができる。

#### 【0058】

図8を参照すれば、本発明の走査駆動部54は、駆動電圧供給部64と、走査電極(Y1乃至Ym)それぞれと接続されるように設置される第4スイッチ(S4)及び第5スイッチ(S5)を備える。

#### 【0059】

駆動電圧供給部64は、正極性のサステイン電圧源(+Vs)に接続される第1スイッチ(S1)と、基底電圧源(GND)に接続される第3スイッチと、負極性のサステイン電圧源(-Vs)に接続される第2スイッチ(S2)とを備える。第1スイッチ(S1)乃至第3スイッチ(S3)は、タイミング制御部56の制御によってターン-オン及びターン-オフされる。20

#### 【0060】

第4スイッチ(S4)は、第2スイッチ(S2)と走査電極(Y1乃至Ym)間にそれぞれ設置されて、タイミング制御部56の制御によってターン-オン及びターン-オフされる。第5スイッチ(S5)は、第1及び第3スイッチS1、S3の共通端子と、走査電極(Y1乃至Ym)との間にそれぞれ設置されて、タイミング制御部56の制御によってターン-オン及びターン-オフされる。ここで、第4スイッチ(S4)は、第4ダイオード(D4)と並列に接続され、第5スイッチ(S5)は、第5ダイオード(D5)と並列に接続される。第4ダイオード(D4)及び第5ダイオード(D5)は、走査電極(Y1)からの駆動電圧が駆動電圧供給部64に供給されないように設置される。30

#### 【0061】

このような走査駆動部54からサステインパルスが供給される過程を図9を参照して詳細に説明する。

#### 【0062】

図9を参照すれば、先に第1スイッチ(S1)がターン-オンされる。第1スイッチ(S1)がターン-オンされると、正極性サステイン電圧源(+Vs)の電圧が第1スイッチ(S1)及び第5ダイオード(D5)を経由して走査電極(Y1乃至Yn)に供給される。この時走査電極(Y1乃至Yn)では正極性のサステインパルス(sus+)が供給される。40

#### 【0063】

走査電極(Y1乃至Yn)で正極性のサステインパルス(sus+)が供給された後、第1スイッチ(S1)がターン-オフされると共に、第3スイッチ(S3)及び第5スイッチ(S5)がターン-オンされる。第3スイッチ(S3)及び第5スイッチ(S5)がターン-オンされると、基底電圧源(GND)の電圧が第3スイッチ(S3)及び第5スイッチ(S5)を経由して走査電極(Y1乃至Yn)に供給される。

#### 【0064】

走査電極(Y1乃至Yn)に基底電圧(GND)が供給された後、第3及び第5スイッチ(S3、S5)がターン-オフされると共に、第2及び第4スイッチ(S2, S4)がターン-オンされる。第2及び第4スイッチ(S2, S4)がターン-オンされると、負極性サステイン電圧源(-Vs)の50

電圧が第2スイッチ(S2)及び第4スイッチ(S4)を経由して走査電極(Y1乃至Yn)に供給される。この時、走査電極(Y1乃至Yn)では、負極性サステインパルス(sus-)が供給される。

#### 【0065】

走査電極(Y1乃至Yn)に負極性のサステインパルス(sus-)が供給された後、第2及び第4スイッチ(S2,S4)がターン-オフされると共に、第3スイッチ(S3)がターン-オンされる。第3スイッチ(S3)がターン-オンされると、第3スイッチ(S3)及び第5ダイオード(D5)を経由して、走査電極(Y1乃至Yn)に基底電圧(GND)が供給される。実際には、本発明ではこのような過程を繰り返しながら走査電極(Y1乃至Yn)に正極性または負極性のサステインパルス(sus+,sus-)を交番的に供給する。

#### 【0066】

一方、アドレス期間には第2スイッチ(S2)がターン-オン状態を維持する。そして、第2スイッチ(S2)がターン-オン状態を維持する状態で、第4スイッチ(S4)が順にターン-オンされ、順次的なスキャンパルス(scan)を走査電極(Y)で供給するようになる。この時、アドレス駆動部52では、スキャンパルス(scan)に同期されるデータパルスをデータライン(X1乃至Xm)に供給する。

#### 【0067】

このような本発明では、維持電極(Z)は常に(ひとつのサーブフィールド期間の間)基底電圧源(GND)の電圧を供給受ける。このように、維持電極(Z)に常に基底電圧源(GND)が供給されれば、外部ノイズの流入及び/またはEMIの発生等を最小化することができ、これに従ってPDPの安全性をより向上させることができる。

#### 【0068】

そして本発明では、維持電極(Z)は常に基底電圧源(GND)に接続されるから、従来のような維持駆動部が省略できることができる、これに従って維持駆動部の駆動によって生成されるEMIなどの発生を防止することができる。そして本発明では、維持電極(Z)が直接的に基底電圧源(GND)に接続されるからノイズの追加発生を抑制することができる。

#### 【図面の簡単な説明】

#### 【0069】

【図1】従来の3電極交流面放電型プラズマディスプレイパネルの放電セル構造を示す斜視図。

【図2】プラズマディスプレイパネルのひとつフレームを示す図。

【図3】従来のプラズマディスプレイパネルの駆動装置を示す図。

【図4】従来のプラズマディスプレイパネルの駆動方法を示す波形図。

【図5】本発明の実施形態によるプラズマディスプレイパネルの駆動装置を示す図。

【図6】図5に示した走査駆動部を詳細に示す図。

【図7】図6に示したスイチングらのタイミング図に対応して走査電極に供給されるサステインパルスを図。

【図8】図5に示した走査駆動部の他の実施形態を詳細に示す図。

【図9】図8に示したスイチングらのタイミング図に対応して走査電極に供給されるサステインパルスを示す図である。

【図1】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

G 09 G 3/20 624 L

H 04 N 5/66 101 B