| DOMANDA DI INVENZIONE NUMERO | 102021000027515 |

|------------------------------|-----------------|

| Data Deposito                | 27/10/2021      |

| Data Pubblicazione           | 27/04/2023      |

## Classifiche IPC

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| Н       | 01     | L           | 39     | 22          |

## Titolo

Superconducting variable inductance transistor

15

1

## **DESCRIZIONE**

Allegata alla domanda di brevetto con il seguente titolo:

"Transistor superconduttivo ad induttanza variabile"

Richiedente: CONSIGLIO NAZIONALE DELLE RICERCHE

P.le Aldo Moro 7 00185 ROMA RM

\*\*\*\*\*

La presente invenzione riguarda un transistor superconduttivo ad induttanza variabile, in particolare un transistor controllato attraverso l'applicazione di un campo elettrico.

L'elettronica superconduttiva moderna si basa sulla modulazione della supercorrente critica Ic di un superconduttore e, di conseguenza, della sua induttanza cinetica, attraverso un bias generato da un elettrodo di gate (Phys. C 482, 6 (2012)).

In questo contesto, sono stati proposti diversi approcci e architetture.

I transistor superconduttivi ad effetto di campo (SuFET) attualmente noti sono realizzati utilizzando un canale conduttivo comprendente un ossido superconduttivo la cui bassa densità di portatori di carica può essere modulata applicando al canale conduttivo un campo elettrico generato attraverso un elettrodo di gate. Come risultato, le proprietà superconduttive del canale vengono modificate (vedere Physica B 135, 124 (1985), documento US5240906, documento US 2011/0254053).

Altri dispositivi superconduttivi ad effetto di campo (FETs) sfruttano due elettrodi superconduttivi separati da un canale conduttivo (vedere documenti US5024993, US5232905, US5272358, US5380704, US5422336, US 5434530) o da una barriera conduttiva (vedere US5441926) di materiale conduttivo (semiconduttivo) con una bassa densità di portatori liberi, sul quale agisce l'elettrodo di gate (JoFET). In questo modo, la supercorrente circolante tra gli elettrodi è controllata dalla tensione di gate che influenza la resistività del canale semiconduttivo.

15

20

25

Un altro approccio consiste nel controllare la corrente di quasiparticelle di un canale attraverso l'iniezione di una corrente da un elettrodo di gate (metallico o superconduttivo), il quale controlla la corrente tunnel che scorre attraverso un semiconduttore collegato a due elettrodi superconduttivi (vedere documento US 4575741).

Un ulteriore approccio consiste nel controllare la supercorrente di un canale attraverso due gate superconduttivi, che controllano il tunnelling risonante, mediato da un ferromagnete, che scorre tra due elettrodi di metallo normale o elettrodi superconduttivi (vedere documento US 6344659).

I materiali superconduttivi sono anche usati nei transistor a giunzione bipolare (BJTs), dove una corrente di quasiparticelle che fluisce tra una base (superconduttore) e un collettore (superconduttore) è controllata da una corrente circolante tra un emettitore (metallo o superconduttore) e la base (vedere documenti US4157555, EP0163031B1, US 4575741, EP0357321A2, US5318952, US6344659).

Tutte le tecnologie di cui sopra si basano su processi di realizzazione che comprendenti numerosi e complessi passaggi di fabbricazione. I materiali usati sono complessi da sintetizzare e la qualità generale necessaria per il corretto funzionamento di questi dispositivi necessita dell'uso di substrati dedicati, che non sono facilmente compatibili con la produzione su larga scala.

Inoltre, la modulazione della conduttività del canale è limitata e il suo miglioramento necessita della produzione di canali con spessore paragonabile a quello dell'unità di cella del materiale del canale stesso. Per queste ragioni, queste tecnologie non sono utilizzate per la produzione industriale.

I metalli superconduttivi sono usati anche per la realizzazione di transistor basati sulla modulazione della corrente critica di un canale attraverso un campo magnetico (vedere cryotron, Electron. Rad. Eng. 25, 387 (1963)) o attraverso l'iniezione controllata di corrente (vedere

10

15

20

25

nanocryotron, Nano Lett. 14, 5784 (2014); Supercond. Sci. Technol. 30, 044002 (2017)).

Queste architetture sono basate su una semplice tecnologia costruttiva, ma il controllo del transistor attraverso una corrente rende difficile interfacciare questi dispositivi con i dispositivi a semiconduttore tradizionali. Inoltre, i nanocryotrons presentano una scarsa velocità di operazione dal momento che la loro dinamica è limitata dalla verlocità di termalizzazione del superconduttore (tipicamente dell'ordine dei microsecondi).

Oltre a quello di cui sopra è interessante notare che la tecnologia computazionale superconduttiva con le maggiori applicazioni industriali è rappresentata dall'approccio rapid single flux quantum (RSFQ), nel quale campi magnetici vengono utilizzati per cambiare uno stato logico codificato attraverso la presenza o l'assenza di un quando di flusso magnetico (vedere IEEE Trans. Magn. 23, 759 (1987); IEEE Trans. Appl. Supercond. 21, 760 (2011); IEEE Trans. Appl. Supercon. 29, 1102805 (2019)). I circuiti RSFQ presuppongono l'uso di giunzioni Josephson combinate con induttori superconduttivi e la loro integrazione con la tecnologia CMOS non è semplice.

In anni recenti, sono stati sviluppati dispositivi ad effetto di campo nei quali un campo elettrico modula la corrente critica di un superconduttore metallico senza cambiarne la densità di carica superficiale. La soppressione della supercorrente non dipende dal segno della tensione di gate e questo è stato dimostrato in nanofili e film sottili (vedere Nat. Nanotech. 13, 802 (2018)), in giunzioni Josephson (Nano Lett. 18, 4195 (2018); Phys. Rev. Appl. 11, 024061 (2019); Appl. Phys. Lett. 116, 242601 (2020); Appl. Phys. Lett. 116, 252601 (2020)), in sistemi metallici prossimizzati (ACS Nano 13, 7871 (2019)) e in interferometri (Nano Lett. 19, 6263 (2019)). Sono anche stati proposti alcuni circuiti elettronici basati su questa tecnologia e operanti in DC (vedere Phys. Rev. Appl. 11, 024061 (2019), AVS Quantum Sci. 1, 016501 (2019)).

15

20

25

I sopracitati effetti si riferiscono alla risposta statica (in DC) di un circuito superconduttivo. Quando si considerano segnali dipendenti dal tempo, una costrizione superconduttiva mostra una componente induttiva inversamente proporzionale alla sua corrente critica (la cosiddetta "Induttanza Josephson", L<sub>J</sub> ∝ 1/Ic). Allo stesso modo, fili superconduttori sottili con bassa densità di carica esibiscono induttanza cinetica. Per dispositivi tipici, il contributo induttivo diventa significativo nel dominio della radiofrequenza e delle microonde. Il controllo in-situ dell'induttanza Josephson è stato ottenuto induttivamente in dispositivi di tipo SQUID (Superconducting Quantum Interference Device), portando realizzazione, per esempio, di risonatori con frequenze regolabili su un largo spettro (J. Low Temp. Phys. 151, 1034 (2008); Appl. Phys. Lett. 114, 192601 (2019)) e interruttori criogenici a microonde (Phys. Rev. Appl. 6, 024009 (2016)).

Alternativamente, anche un'iniezione diretta di corrente attraverso una costrizione (o un nanofilo) è stata sfruttata per regolare l'induttanza dello stesso, anche se in un intervallo di frequenze più limitato (Appl. Phys. Lett. 108, 172601 (2016)).

In definitiva. usando ibride superconduttoregiunzioni semiconduttore è possibile un ottenere controllo elettrostatico dell'induttanza Josephson. Con questa tecnica sono stati proposti dispositivi quantistici operanti alle frequenze delle microonde. (Phys. Rev. Lett. 115, 127001; ibid, 127002 (2015); Nat. Nano. 13, 915 (2018)). Applicando una modulazione dell'induttanza a predeterminate frequenze (modi caratteristici del sistema e sue armoniche, somme e differenze delle frequenze modali), una serie di interazione tra questi modi vengono rese possibili. Queste interazioni sono state sfruttate per ottenere un'amplificazione parametrica vicina al limite quantistico (Appl. Phys. Lett. 93, 042510 (2008)), porte quantistiche tra differenti qubit (Phys. Rev. Applied 6, 064007 (2016)), entanglement ad ampio spettro con radiazione

10

15

20

25

30

a microonde (Phys. Rev. Lett. 124, 140503 (2020)) e down-conversion parametrica spontanea a tre fotoni (Phys. Rev. X 10, 011011 (2020)).

Come indicato precedentemente, nonostante le grandi prestazioni di questi dispositivi, è molto difficile usarli nell'industria a causa dei limiti di produzione dovuti alle loro caratteristiche fisiche e ai materiali coinvolti, gli alti costi di realizzazione e la difficile integrazione di questi dispositivi con i dispositivi standard CMOS utilizzati attualmente nei prodotti commerciali.

Per esempio, le industrie non sono ancora state in grado di usare direttamente questi dispositivi noti in apparati per migliorare la lentezza dell'equipaggiamento delle comunicazioni satellitari e terrestri o per incrementare la potenza computazionale dei supercomputer, che rappresentano oggi le due maggiori sfide dell'industria elettronica.

Esiste dunque la necessità di fornire un transistor superconduttivo ad induttanza variabile che permetta di ottenere dispositivi con alte prestazioni in termini di velocità di switch, dimensioni complessive ed energia dissipata, che possa essere prodotto con facilità attraverso un processo economico e che possa essere completamente integrato con i dispositivi CMOS, superando in tal modo i problemi della tecnologia precedente.

Questi e altri scopi sono pienamente raggiunti grazie ad un transistor superconduttivo a induttanza variabile avente le caratteristiche definite nella rivendicazione indipendente 1.

Forme di realizzazione preferite dell'invenzione sono specificate nelle rivendicazioni dipendenti, il cui contenuto deve essere inteso come parte integrale o integrante della presente descrizione.

Ulteriori caratteristiche e vantaggi della presente invenzione risulteranno evidenti dalla seguente descrizione, fornita solo a titolo di esempio non limitativo, con riferimento ai disegni allegati, in cui:

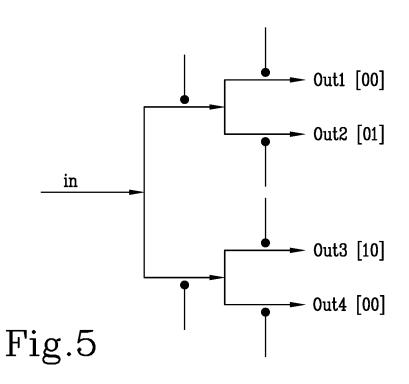

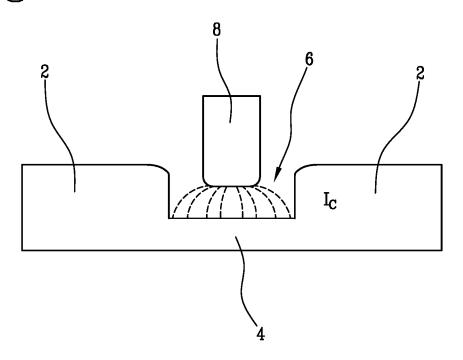

- La Figura 1 mostra una vista laterale schematica di un transistor superconduttivo a induttanza variabile secondo la presente invenzione;

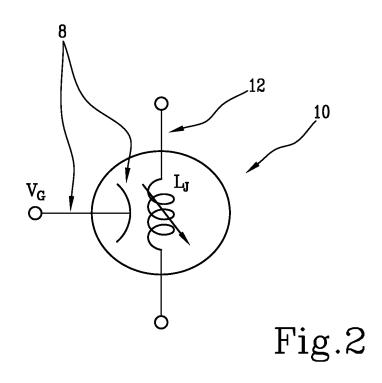

- la Figura 2 mostra un simbolo di circuito del transistor superconduttivo della Figura 1;

10

15

20

25

- La Figura 3 mostra uno schema circuitale di uno switch a microonde SPDT (single-pole, double-throw);

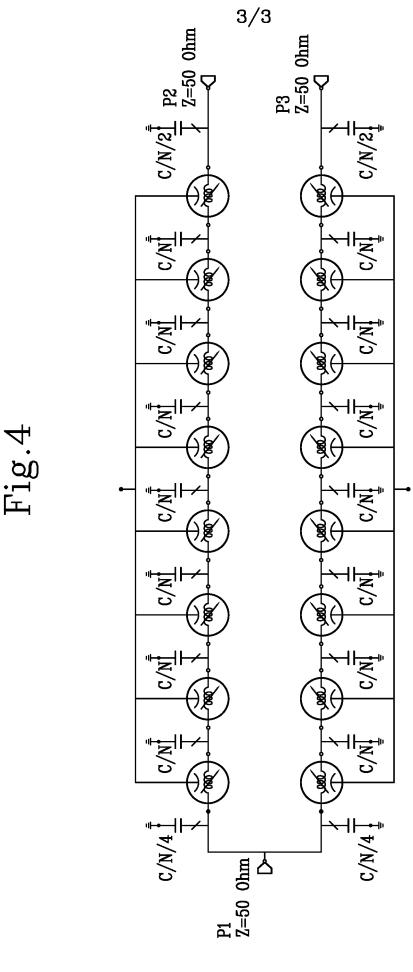

- La Figura 4 mostra uno schema circuitale di uno switch a microonde SPDT (single-pole, double-throw) realizzato con N sezioni; e

- La Figura 5 mostra un interruttore a microonde single-pole, fourthrow quadripolare 1:4 ottenuto con tre switch single-pole, double throw.

In sintesi, il transistor superconduttivo a induttanza variabile della presente invenzione permette di ottenere dispositivi con elevate prestazioni in termini di velocità di commutazione, ingombro ed energia dissipata e, inoltre, permette di implementare una logica binaria in grado di raggiungere frequenze di clock almeno 100 volte superiori a quelle dei prodotti attualmente disponibili sul mercato.

In particolare, il transistor superconduttivo a induttanza variabile della presente invenzione sfrutta la possibilità di modulare la corrente critica (Ic) di un canale metallico superconduttivo attraverso l'applicazione di una tensione predeterminata a un elettrodo di controllo (gate) del transistor superconduttore.

L'induttanza Josephson  $L_J$  ( $L_J \propto \hbar/Ic$ , dove  $\hbar$  è la costante di Planck ridotta) del canale superconduttivo del transistor superconduttivo può essere regolata tra due stati, cioè un primo stato "0" (bassa impedenza/induttanza) e un secondo stato "1" (alta impedenza/induttanza).

In particolare, è possibile regolare solo la parte immaginaria dell'impedenza totale della giunzione, cioè cambiare solo il valore dell'induttanza di Josephson L<sub>J</sub>, mantenendo il transistor nello stato superconduttivo.

In questo modo, la caduta di tensione alternata (AC) alle estremità del canale superconduttivo è uguale a:

$$V(\omega) = I(\omega)Z(\omega, V_G)$$

(1)

10

15

20

25

30

dove  $V_G$  è la tensione di gate,  $I(\omega)$  è la corrente alternata che scorre nel canale superconduttivo e  $Z(\omega,\ V_G)$  è l'impedenza del canale superconduttivo che, per una frequenza di lavoro predeterminata  $\omega$ , dipende solo dalla tensione di gate  $V_G$ .

La tensione di gate può essere controllata sia in regime quasi-statico (frequenza operativa di almeno un ordine di grandezza inferiore alla frequenza del segnale) che in regime di alta frequenza (frequenza operativa paragonabile alla frequenza del segnale).

Il transistor superconduttivo a induttanza variabile della presente invenzione può essere usato per ottenere dispositivi avanzati a radiofrequenza come switch, convertitori digitale-analogico (DAC), porte logiche, ecc. Tali dispositivi elettronici sono caratterizzati da un'alta efficienza energetica e da una frequenza operativa dell'ordine dei THz. Inoltre, l'uso di una tensione per controllare l'impedenza del transistor assicura la compatibilità con i dispositivi standard della tecnologia a semiconduttore esistenti (CMOS).

Il principio fisico che agisce nel transistor superconduttivo a induttanza variabile della presente invenzione è stato dimostrato dal gruppo di ricerca sulle tecnologie quantistiche superconduttive dell'Istituto Nanoscienze di Pisa (Nat. Nanotech. 13, 802 (2018); Nano Lett. 18, 4195 (2018); Phys. Rev. Appl. 11, 024061 (2019); ACS Nano 13, 7871 (2019); Nano Lett. 19, 6263 (2019); AVS Quantum Sci. 1, 016501 (2019); Appl. Phys. Lett. 116, 242601 (2020); Appl. Phys. Lett. 116, 252601 (2020)).

I dispositivi divulgati nelle pubblicazioni di cui sopra possono essere realizzati utilizzando metalli superconduttori, cioè metalli che mostrano proprietà di trasporto di carica non dissipative al di sotto di una temperatura caratteristica chiamata temperatura critica (Tc). La massima corrente non dissipativa che può essere sostenuta da questi dispositivi è la cosiddetta corrente critica (Ic). La corrente critica Ic è una proprietà di ogni materiale e dipende dalla geometria del dispositivo, ma può essere controllata

15

20

25

30

applicando una tensione di gate predeterminata a un elettrodo di controllo (elettrodo di gate) posto vicino al canale superconduttivo.

In particolare, è possibile regolare continuamente il valore della corrente critica Ic da un valore iniziale (quando la tensione di gate  $V_G$  è uguale a 0) fino alla sua completa soppressione (la corrente critica Ic è uguale a 0 per una tensione di gate  $V_G \ge V_C$ , dove  $V_C$  è la tensione critica oltre la quale il transistor perde lo stato superconduttivo), variando continuamente l'induttanza di Josephson LJ e la resistenza residua del filo generata dalle quasiparticelle (RJ).

I dispositivi divulgati nelle pubblicazioni di cui sopra lavorano tra uno stato superconduttivo e uno stato dissipativo, mentre il transistor superconduttivo a induttanza variabile della presente invenzione opera tra due stati puramente superconduttivi, caratterizzati da una diversa induttanza Josephson.

La Figura 1 mostra una vista schematica laterale di un transistor superconduttivo a induttanza variabile 1 secondo la presente invenzione. Il transistor superconduttivo 1 comprende un canale superconduttivo 2 composto interamente da un metallo superconduttivo. Una regione interna 4 del canale superconduttivo 2 è predisposta per essere influenzata da un campo elettrico 6 generato dall'applicazione di una tensione di gate VG ad un elettrodo di gate 8 del transistor superconduttivo 1. L'elettrodo di gate 8 è posto in corrispondenza di detta regione interna 4.

La Figura 2 mostra un simbolo del circuito 10 del transistor superconduttivo 1 della Figura 1. L'elettrodo di gate 8 è il filo orizzontale, mentre il filo verticale 12 rappresenta un'induttanza variabile L<sub>J</sub>.

Il transistor superconduttivo 1 è capace di commutare tra un primo stato "0" in cui l'induttanza variabile  $L_J$  ha un primo valore  $L_0$ , e un secondo stato "1" in cui l'induttanza variabile  $L_J$  ha un secondo valore  $L_1$ .

Il secondo valore L<sub>1</sub> è maggiore del primo valore L<sub>0</sub> ma il transistor superconduttivo 1 rimane, in entrambi gli stati, nella condizione di superconduzione ed è controllato attraverso l'elettrodo di gate 8.

In particolare, si applica la seguente equazione:

$$L_1 = 10 L_0$$

(2)

Le frequenze di funzionamento del transistor superconduttivo 1 dipendono dal metallo superconduttivo del canale superconduttivo 2, dalla temperatura di funzionamento e dal contrasto richiesto tra il primo e il secondo stato.

Per esempio, ad una temperatura T inferiore alla temperatura critica

10 Tc, un transistor superconduttivo 1 con un canale superconduttivo in alluminio 4 presenta un gap superconduttivo (determinato sperimentalmente e sostanzialmente uguale al valore noto):

$$\Delta \sim 200 \ \mu eV$$

(3)

15

5

e, quindi, una prima frequenza operativa di stato ω₀ limitata a:

$$\omega_0 = \frac{R_0}{L_0} \sim \frac{2\Delta}{h} \sim 100 \ GHz \tag{4}$$

dove h è la costante di Planck, e  $L_0$  e  $R_0$  sono l'induttanza Josephson e la resistenza di quasi-particella del filo con  $V_G$  =0, cioè il contributo di quasi-particella alla resistenza del canale superconduttivo 4 come previsto dal modello a due fluidi, con la tensione di gate  $V_G$  uguale a 0. Questa frequenza operativa di primo stato  $\omega_0$  è la frequenza del transistor superconduttivo 1 nel primo stato (con primo valore  $L_0$ ).

Per la configurazione ad alta induttanza ( $L_1$  = 10 $L_0$ ), si ottiene una frequenza operativa di secondo stato  $\omega_1$  come il rapporto delle due impedenze:

30

$$\omega_1 = \frac{R_1}{L_1} \sim \frac{2\Delta}{h} \frac{L_0}{L_1} \sim 10 \ GHz \tag{5}$$

assumendo una variazione trascurabile della resistenza di quasi-particella ( $R_1 \cong R_0$ ), cioè con la resistenza di quasi-particella ad una tensione di gate predeterminata  $V_G$  sostanzialmente uguale alla resistenza di quasi-particella del filo a zero-gate, cioè quando la tensione di gate  $V_G$  è uguale a 0. Questa frequenza operativa del secondo stato  $\omega_1$  è la frequenza del transistor superconduttivo 1 nel secondo stato (con secondo valore  $L_1$ ).

Nel caso in cui il cambiamento di  $R_1$  non sia trascurabile rispetto a  $R_0$ , la frequenza  $\omega_1$  è ulteriormente ridotta dal rapporto  $R_1/R_0$ .

Il limite superiore della frequenza di funzionamento degli switch superconduttivi basati sul transistor superconduttivo 1 della presente invenzione è la frequenza di funzionamento del primo stato  $\omega_0$  poiché, come dettagliato qui sotto, la frequenza di funzionamento del secondo stato  $\omega_1$  è caratteristica di uno stato di canale chiuso.

Utilizzando materiali superconduttivi con una temperatura critica  $T_C$  più alta, per esempio il niobio ( $T_C \sim 9$  K), è possibile aumentare la frequenza operativa massima dei transistor a impedenza:

$$\omega < \frac{2\Delta_{\rm Nb}}{h} \sim 1500 \; GHz \tag{6}$$

20

25

10

15

dato il maggiore gap superconduttivo del niobio ( $\Delta_{Nb} \sim 3 \ meV$ ).

La Figura 3 mostra uno schema circuitale di uno switch a microonde SPDT (single-pole, double-throw).

Un segnale proveniente da una prima porta  $P_1$  può essere inviato a una seconda porta  $P_2$ , o a una terza porta  $P_3$ , applicando le rispettive prime e seconde tensioni  $V_2$ ,  $V_3$  agli elettrodi di gate che controllano i rispettivi transistor superconduttivi ad induttanza variabile 1a, 1b.

Le tensioni applicate  $V_2$ ,  $V_3$  sono scelte tra un valore di apertura per cui il rispettivo transistor superconduttivo 1a, 1b ha un valore di induttanza basso,  $L_0$  (stato "aperto"), e un valore di chiusura per cui il transistor 1a, 1b ha un valore di induttanza alto,  $L_1 \ge 10$   $L_0$  (stato "chiuso").

20

25

Per selezionare la seconda porta  $P_2$  (rispettivamente, la terza porta  $P_3$ ), si assegna alla prima tensione  $V_2$  (rispettivamente, la seconda tensione  $V_3$ ) il valore aperto, e alla seconda tensione  $V_3$  (rispettivamente, prima tensione  $V_2$ ) il valore chiuso.

Negli stati aperto e chiuso, il transistor superconduttivo 1a, 1b ha un'impedenza immaginaria  $Z_{LJ}\cong i\omega L_J$  dove  $L_J(V_G)$  è l'induttanza di giunzione che varia tra  $L_0$  e  $L_1$  e il contributo dovuto alla resistenza di quasiparticella è trascurato.

Per garantire un buon isolamento (isolamento > 20 dB), la 10 condizione:

$$|Z_{L1}| \gg |Z_0|$$

(7)

deve essere verificata, dove  $Z_0$  è l'impedenza delle porte  $P_1$ ,  $P_2$ ,  $P_3$  (tipicamente, 50 ohm).

Questa condizione può limitare le frequenze di funzionamento del dispositivo:

$$\omega > \frac{Z_0}{L_1} \sim 1 \ GHz \tag{8}$$

per transistor induttivi (L<sub>1</sub> ≥ 50 nH).

A differenza dei limiti di frequenza indotti dalla scelta del materiale superconduttivo, questa frequenza può essere opportunamente scalata scegliendo la geometria appropriata del transistor superconduttivo 1a, 1b o aumentando la modulazione dell'induttanza (cioè,  $L_1\gg 10L_0$ ).

Se la variazione sulla resistenza di quasi-particella non è trascurabile, si deve aggiungere a questa condizione la condizione  $R_1\gg Z_0$ . Quest'ultima può essere facilmente ottenuta aumentando, per esempio, la resistenza di stato normale  $(R_N\gg Z_0)$  che, per definizione, è sempre inferiore alla resistenza di quasi-particella  $(R_1\geq R_N)$ .

Inoltre, per minimizzare le perdite di segnale in riflessione, 30 l'impedenza di ingresso vista dalla prima porta  $P_1$  deve essere resa il più possibile vicina a  $Z_0$  (cioè,  $|Z_{L0}| \le Z_0$ ). Se questa condizione è difficile da

15

20

30

ottenere, è possibile ottimizzare la trasmissione per mezzo di tecniche di adattamento di impedenza di per sé note, realizzate con opportuni circuiti elettronici, come mostrato in Figura 3.

Più grande è il gap del superconduttore, più rilevante è l'adattamento di impedenza, e quindi più alta è la frequenza della banda di interesse.

L'aggiunta di condensatori proporzionali a:

$$C = L_J/Z_0^2 (9)$$

fornisce un buon matching per frequenze molto minori della frequenza di risonanza del circuito (uguale a  $1/(2 \pi C L_J)$  ).

Questo vincolo può essere ulteriormente rilassato dividendo il circuito in N sezioni, ognuna con la resistenza di stato normale Z<sub>L</sub> /N, come mostrato nella Figura 4, che rappresenta uno schema circuitale di un interruttore a microonde single-pole, double-throw (SPDT) realizzato con N sezioni (N=8).

Assumendo la piena riproducibilità dei transistor superconduttivi 1a, 1b, essi possono essere controllati da una stessa sorgente di tensione.

Dato che questo è un dispositivo ad impedenza bilanciata, lo switch di Figura 3 può essere integrato con altri dispositivi simili per fare switch del tipo "single-pole:  $2^x$ -throw" (x è un numero naturale). Il numero di switch elementari necessari per fare ciò è uguale a $\sum_{i=0}^{x-1} 2^i = 2^x - 1$ . Per esempio, con tre switch elementari (x=2) si può realizzare uno switch a quattro uscite 1:4, con sette switch elementari (x=6) si può realizzare uno switch 1:8, e così via (il numero di uscite è uguale a  $2^x$ ).

La Figura 5 mostra uno switch a microonde single-pole four-throw 1:4 ottenuto con tre single-pole, double-throw switch.

D'altra parte, il numero di tensioni di gate  $V_G$  che devono essere specificate indipendentemente è uguale a 2x. Quindi, c'è una scala esponenziale del numero di gate di uscita, rispetto a una scala lineare del numero di controlli indipendenti richiesti.

10

15

20

25

Infine, sommando le tensioni applicate da diverse fonti, è possibile sfruttare la bipolarità del dispositivo in modo che solo un controllo indipendente debba essere applicato a ciascuno switch elementare, in aggiunta a una tensione comune. Il numero di controlli richiesti in questo caso si riduce a 1+x.

Le funzionalità del transistor superconduttivo 1, 1a, 1b qui descritte si riferiscono a un controllo digitale fissato da due distinti valori di tensione di gate. In particolare, il valore dell'induttanza di uscita L<sub>0</sub> o L<sub>1</sub> dipende dal valore del segnale digitale di ingresso (0 o 1) che viene fornito all'elettrodo di gate 8. Questo approccio è ideale per realizzare switch, DAC, porte logiche, ecc.

Data la flessibilità di funzionamento del transistor superconduttivo 1, 1a, 1b della presente invenzione, è anche possibile eseguire un controllo parametrico. In questo caso il segnale che controlla il gate 8 contiene una componente continua e una sinusoidale. In questo modo l'induttanza del transistor superconduttivo 1, 1a, 1b acquista una componente oscillante con la frequenza del segnale (e successive armoniche).

I vantaggi legati all'uso di due stati superconduttivi invece della condizione resistiva/superconduttiva dei dispositivi precedenti sono principalmente due: (i) una maggiore separazione tra i valori di impedenza nei due stati, e (ii) una riduzione della dissipazione di potenza in quanto il transistor superconduttivo 1 opera sempre nello stato superconduttivo.

Inoltre, rispetto ai dispositivi a controllo magnetico di tipo SQUID, il controllo elettrostatico fornisce una migliore stabilità, riduzione del rumore e abbattimento del crosstalk tra diversi dispositivi.

Rispetto ai dispositivi ibridi super-semiconduttivi a effetto campo, la monoliticità del transistor superconduttivo 1, 1a, 1b offre una maggiore semplicità di fabbricazione, un costo di fabbricazione inferiore e una maggiore stabilità. I due stati di induttanza possono così essere selezionati grazie alla soppressione della corrente critica dovuta alla tensione di gate  $V_{\rm G}$ .

15

20

25

Il vantaggio principale della tecnologia della presente invenzione consiste nel combinare l'efficienza energetica delle piattaforme di calcolo basate su superconduttori con la possibilità di utilizzare la codifica convenzionale dei segnali logici basata sui livelli di tensione. Si ottiene così una maggiore scalabilità e integrabilità rispetto alle attuali tecnologie già utilizzate per applicazioni su larga scala che sono basate o su semiconduttori o su superconduttori.

In particolare, rispetto alle tecnologie superconduttive di calcolo che sono disponibili in commercio, la presente tecnologia è resistente alle perturbazioni magnetiche esterne perché non comporta l'uso di flussi magnetici o bias di corrente, offre una scalabilità del dispositivo molto più alta, ha un fan-out maggiore e una resistenza gatwe-cansale più alta (queste proprietà sono essenziali per massimizzare la trasmissione dei segnali ai dispositivi a valle senza che le informazioni vengano perse) e ha una velocità di commutazione molto più alta.

La necessità di sistemi di raffreddamento e di liquidi criogenici per portare il transistor superconduttivo 1, 1a, 1b al di sotto della temperatura critica dei materiali superconduttivu può essere superata utilizzando criostati a ciclo chiuso (cioè criostati a secco), che sono attualmente disponibili sul mercato e permettono di raggiungere le temperature operative necessarie in modo efficiente, rapido ed economico.

Infatti, i criostati a secco sono già adottati per applicazioni su larga scala (sia commerciali che industriali) che richiedono temperature operative inferiori a quelle dell'azoto liquido come, per esempio, le piattaforme di calcolo superconduttive basate sulla logica rapid single flux quantum (RSFQ).

Il transistor superconduttivo 1, 1a, 1b della presente invenzione offre un alto grado di compatibilità con qualsiasi altra tecnologia superconduttiva e quantistica disponibile sul mercato. A differenza della tecnologia RSFQ, la presente tecnologia non richiede un'interfaccia aggiuntiva per un sistema CMOS, il che significa che il transistor superconduttivo 1, 1a, 1b è

10

naturalmente adatto a piattaforme di calcolo ibride superconduttore/semiconduttore.

Altri vantaggi includono la sua piena compatibilità con le tecniche di fabbricazione attualmente utilizzate per la realizzazione di processori quantistici basati su superconduttori. Grazie alla tecnologia attuale è possibile ottenere un'integrazione diretta di switch a microonde e risonatori regolabili in frequenza con i processori quantistici, il che faciliterebbe l'implementazione di operazioni di misurazione e controllo sugli stessi processori.

Chiaramente, il principio dell'invenzione rimanendo lo stesso, le realizzazioni e i dettagli di produzione possono essere variati considerevolmente da ciò che è stato descritto e illustrato puramente a titolo di esempio non limitativo, senza allontanarsi dall'ambito di protezione del presente come definito nelle rivendicazioni allegate.

IL MANDATARIO Ing Valeria FASSIO (Albo iscr. n. 1311B)

10

15

20

25

30

1

## RIVENDICAZIONI

- 1. Transistor superconduttivo a induttanza variabile (1) comprendente:

- un canale superconduttivo (2) in metallo superconduttore, il canale superconduttivo (2) avendo un valore predefinito di induttanza Josephson (LJ);

- un elettrodo di gate (8) posto in corrispondenza di una regione interna (4) del canale superconduttivo (2);

in cui detta regione interna (4) è predisposta per essere influenzata da un campo elettrico (6) generato dall'applicazione di una tensione di gate ( $V_G$ ) a detto elettrodo di gate (8), il transistor superconduttivo (1) essendo in grado di commutare tra un primo stato in cui l'induttanza Josephson ( $L_J$ ) ha un primo valore ( $L_0$ ) e un secondo stato in cui l'induttanza Josephson ( $L_J$ ) ha un secondo valore ( $L_1$ ), il secondo valore ( $L_1$ ) dell'induttanza Josephson essendo maggiore del primo valore ( $L_0$ ) dell'induttanza Josephson e il transistor superconduttivo (1) rimanendo, sia nel primo che nel secondo stato, in una condizione di superconduttività.

- 2. Transistor superconduttivo a induttanza variabile (1) secondo la rivendicazione 1, dove il secondo valore ( $L_1$ ) dell'induttanza Josephson è uguale a dieci volte il primo valore ( $L_0$ ).

- 3. Transistor superconduttivo a induttanza variabile (1) secondo le rivendicazioni 1 o 2, in cui il valore dell'induttanza (L<sub>J</sub>) comprende una parte immaginaria e il transistor superconduttivo (1) è predisposto per commutare dal primo stato al secondo stato cambiando soltanto la parte immaginaria di detto valore dell'induttanza (L<sub>J</sub>).

- 4. Transistor superconduttivo a induttanza variabile (1) secondo una delle rivendicazioni precedenti, in cui il transistor superconduttivo (1) ha un canale superconduttivo in alluminio (2) che presenta un gap superconduttivo pari a:

10

15

2

$$\Delta \sim 200 \ \mu eV$$

e, quindi, una frequenza operativa di primo stato  $(\omega_0)$  pari a:

$$\omega_0 = \frac{R_0}{L_0} \sim \frac{2\Delta}{h} \sim 100 \; GHz$$

dove h è la costante di Planck, e  $L_0$  e  $R_0$  sono l'induttanza Josephson e la resistenza di quasi-particella della regione interna (4) con la tensione di gate ( $V_G$ ) uguale a 0, questa prima frequenza operativa di stato ( $\omega_0$ ) essendo la frequenza del transistor superconduttivo (1) nel primo stato.

5. Transistor superconduttivo a induttanza variabile (1) secondo la rivendicazione 4, in cui il transistor superconduttivo (1) ha una frequenza operativa di secondo stato ( $\omega_1$ ) uguale a:

$$\omega_1 = \frac{R_1}{L_1} \sim \frac{2\Delta}{h} \frac{L_0}{L_1} \sim 10 \ GHz$$

dove h è la costante di Planck, e  $L_1$  e  $R_1$  sono l'induttanza Josephson e la resistenza di quasi-particella della regione interna (4) con una tensione di gate predeterminata ( $V_G$ ) sostanzialmente uguale alla resistenza quasi-particella della regione interna (4) con la tensione di gate ( $V_G$ ) uguale a 0, questa frequenza operativa del secondo stato ( $\omega_1$ ) essendo la frequenza del transistor superconduttivo (1) nel secondo stato.

25

30

20

6. Transistor superconduttivo a induttanza variabile (1) secondo la rivendicazione 5, in cui la resistenza di quasi-particella della regione interna (4) con una tensione di gate predeterminata ( $V_G$ ) è diversa dalla resistenza di quasi-particella della regione interna (4) con la tensione di gate ( $V_G$ ) uguale a 0 e la frequenza operativa del secondo stato ( $\omega_1$ ) è ulteriormente

ridotta dal rapporto  $R_1/R_0$ .

IL MANDATARIO Ing Valeria FASSIO (Albo iscr. n. 1311B)

Fig.1

Fig.3  $\begin{array}{c} V_2 \\ \hline C/4 \\ \hline \end{array} \begin{array}{c} V_2 \\ \hline \end{array} \begin{array}{c} C/2 \\ \hline \end{array} \begin{array}{c} P2 \\ Z=50 \text{ Ohm} \end{array} \end{array}$