(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년05월09일

(11) 등록번호 10-1263065

(24) 등록일자 2013년05월03일

(51) 국제특허분류(Int. C1.)

*H02M 7/49* (2007.01) *H02M 3/155* (2006.01)

*G05F 1/56* (2006.01)

(21) 출원번호 10-2010-0025804

(22) 출원일자 2010년03월23일

심사청구일자 2011년03월23일

(65) 공개번호 10-2010-0106248

(43) 공개일자 2010년10월01일

(30) 우선권주장

JP-P-2009-070181 2009년03월23일 일본(JP)

(56) 선행기술조사문현

JP60257766 A\*

KR100666829 B1

스위칭 전원의 기본설계 서적(저자: 김희준, 출판

사: 성안당), 출판일 2002.01.12\*

JP2001178117 A\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 9 항

심사관 : 배진용

(54) 발명의 명칭 컨버터, 스위칭 전원, 및 화상 형성 장치

### (57) 요 약

컨버터는, 입력 전압을 스위칭하도록 구성되는 스위칭 소자, 스위칭 소자를 구동하도록 구성되는 구동 유닛, 구동 유닛에 펄스 신호를 공급하도록 구성되는 펄스 신호 생성 유닛, 및 구동 유닛을 통하지 않고 스위칭 소자와 펄스 신호 생성 유닛을 접속하도록 구성되는 바이패스 유닛을 포함한다. 입력 전압이 더 낮은 전압으로 스위칭되어 입력 전압의 스위칭이 정지될 때에, 바이패스 유닛의 동작에 의해 스위칭 소자가 온 상태로 유지된다.

## 대 표 도

도 1a

도 1b

## 특허청구의 범위

### 청구항 1

입력 전압을 스위칭하도록 구성되는 스위칭 소자;

상기 스위칭 소자를 구동하도록 구성되고, 트랜지스터를 포함하는 구동 유닛;

상기 구동 유닛에 펄스 신호를 공급하도록 구성되는 펄스 신호 생성 유닛; 및

상기 구동 유닛의 트랜지스터 없이 상기 스위칭 소자와 상기 펄스 신호 생성 유닛을 접속하도록 구성되는 바이패스 유닛을 포함하고,

상기 입력 전압이 더 낮은 전압으로 스위칭되었을 경우, 상기 바이패스 유닛은 상기 스위칭 소자를 항상 온(on) 상태로 유지하는, 컨버터.

### 청구항 2

제1항에 있어서,

상기 스위칭 소자는 전계 효과 트랜지스터(field-effect transistor; FET)를 포함하고, 상기 바이패스 유닛은 저항을 포함하며,

상기 저항은, 상기 구동 유닛을 통하지 않고 상기 FET의 게이트 단자와 상기 펄스 신호 생성 유닛을 접속하도록 구성되는, 컨버터.

### 청구항 3

제1항 또는 제2항에 있어서,

상기 구동 유닛은, NPN 트랜지스터와 다이오드를 포함하는 회로, 또는 PNP 트랜지스터와 다이오드를 포함하는 회로를 포함하는, 컨버터.

### 청구항 4

제1항 또는 제2항에 있어서,

상기 구동 유닛은, NPN 트랜지스터와 PNP 트랜지스터의 조합인 푸시풀 회로(push-pull circuit)를 포함하는, 컨버터.

### 청구항 5

삭제

### 청구항 6

전압을 변환하여 제1 전압을 출력하도록 구성되는 제1 컨버터; 및

상기 제1 전압을 변환하여 제2 전압을 출력하도록 구성되는 제2 컨버터를 포함하는 전원이며,

상기 제2 컨버터는, 상기 제1 전압을 스위칭하도록 구성되는 스위칭 소자; 상기 스위칭 소자를 구동하도록 구성되고, 트랜지스터를 포함하는 구동 유닛; 상기 구동 유닛에 펄스 신호를 공급하도록 구성되는 펄스 신호 생성 유닛; 및 상기 구동 유닛의 트랜지스터 없이 상기 스위칭 소자와 상기 펄스 신호 생성 유닛을 접속하도록 구성되는 바이패스 유닛을 포함하고,

절전 모드로 이행하기 위하여 상기 제 1 전압이 더 낮은 전압으로 스위칭되었을 경우, 상기 바이패스 유닛은 상기 스위칭 소자를 항상 온 상태로 유지하는, 전원.

### 청구항 7

제6항에 있어서,

상기 스위칭 소자는 전계 효과 트랜지스터(FET)를 포함하고, 상기 바이패스 유닛은 저항을 포함하며, 상기 저항은, 상기 구동 유닛을 통하지 않고 상기 FET의 게이트 단자와 상기 펄스 신호 생성 유닛을 접속하도록 구성되는, 전원.

### 청구항 8

제6항 또는 제7항에 있어서,

상기 구동 유닛은, NPN 트랜지스터와 다이오드를 포함하는 회로, 또는 PNP 트랜지스터와 다이오드를 포함하는 회로를 포함하는, 전원.

### 청구항 9

제6항 또는 제7항에 있어서,

상기 구동 유닛은, NPN 트랜지스터와 PNP 트랜지스터의 조합인 푸시풀 회로를 포함하는, 전원.

### 청구항 10

삭제

### 청구항 11

기록재 상에 화상을 형성하도록 구성되는 화상 형성 장치이며, 상기 화상 형성 장치는,

화상 형성 구동 유닛;

상기 화상 형성 구동 유닛을 제어하도록 구성되는 제어 유닛; 및

상기 화상 형성 구동 유닛과 상기 제어 유닛에 전압을 공급하도록 구성되는 전원을 포함하고,

상기 전원은, 전압을 변환하여 제1 전압을 출력하도록 구성되는 제1 컨버터; 및 상기 제1 전압을 변환하여 제2 전압을 출력하도록 구성되는 제2 컨버터를 포함하고,

상기 제2 컨버터는, 상기 제1 전압을 스위칭하도록 구성되는 스위칭 소자; 상기 스위칭 소자를 구동하도록 구성되고, 트랜지스터를 포함하는 구동 유닛; 상기 구동 유닛에 펄스 신호를 공급하도록 구성되는 펄스 신호 생성 유닛; 및 상기 구동 유닛의 트랜지스터 없이 상기 스위칭 소자와 상기 펄스 신호 생성 유닛을 접속하도록 구성되는 바이패스 유닛을 포함하고,

상기 제1 전압은 상기 화상 형성 구동 유닛에 공급되고 상기 제2 전압은 상기 제어 유닛에 공급되며,

절전 모드로 이행하기 위하여 상기 제1 전압이 더 낮은 전압으로 스위칭되었을 경우, 상기 바이패스 유닛은 상기 스위칭 소자를 항상 온 상태로 유지하는, 화상 형성 장치.

## 명세서

### 기술 분야

[0001] 본 발명은 전압을 변환하도록 구성되는 컨버터, 컨버터를 포함하는 스위칭 전원, 및 스위칭 전원을 포함하는 화상 형성 장치에 관한 것이다.

### 배경 기술

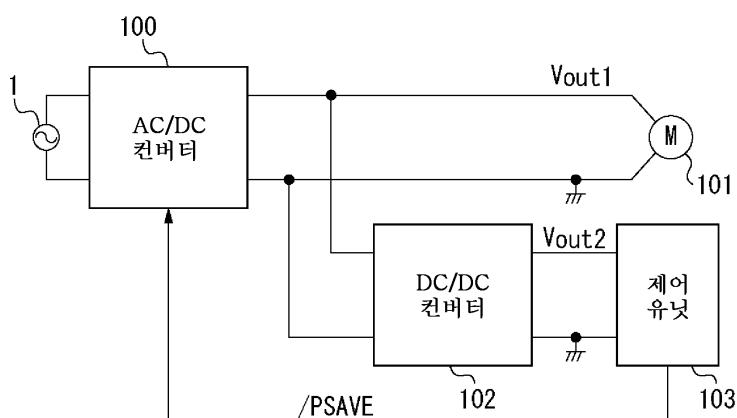

[0002] 도 9는 전형적인 스위칭 전원을 포함하는 디바이스의 블록도의 예를 도시한다. 도 9에서, AC/DC 컨버터(100)는 상용 전원(1)으로부터의 교류 전압을 직류 전압 Vout1로 변압한다. 전압 Vout1은, 모터 등의 액추에이터(101)에 공급된다. 전압 Vout1은 DC/DC 컨버터(102)에도 공급된다. DC/DC 컨버터(102)는 전압 Vout1을 직류 전압 Vout2로 변압한다. 전압 Vout2는, 디바이스를 제어하도록 구성되는 제어 유닛(103)에 공급된다.

[0003] 일반적으로, 액추에이터(101)에 대한 전원 전압 Vout1은, 제어 유닛(103)에 대한 전원 전압 Vout2보다 높게 설정된다. 예를 들어, 일반적으로, 전압 Vout1이 DC 24.0V일 때( $Vout1 = DC 24.0V$ ), 전압 Vout2는 DC 3.30V로 설정되거나( $Vout2 = DC 3.30V$ ), 또는 전압 Vout1이 DC 12.0V일 때( $Vout1 = DC 12.0V$ ), 전압 Vout2는 DC 1.80V

로 설정된다( $V_{out2} = DC\ 1.80V$ ). 이하의 설명에서, 전압  $V_{out1}$ 이 DC 24.0V이고( $V_{out1} = DC\ 24.0V$ ) 전압  $V_{out2}$ 가 DC 3.30V인( $V_{out2} = DC\ 3.30V$ ) 예가 설명될 것이다. 여기에서, "AC"는 교류 전압을 나타내고, "DC"는 직류 전압을 나타낸다.

- [0004] 전형적인 스위칭 전원으로서, AC/DC 컨버터와 DC/DC 컨버터를 포함하는 전원의 구성이, 일본 공개 특허 제2003-266878호에 개시되어 있다.

- [0005] 요즘, 대기 상태의 전자 디바이스의 전력 소비를 더욱 저감하는 것이 강하게 소망되어왔다. 전술한 일본 공개 특허 제2003-266878호에 개시된 스위칭 전원을 포함하는 디바이스에서, 통상 동작 모드와 전력 소비를 감소시키기 위한 절전 모드가 제공된다. 절전 모드에서는, 스위칭 전원의 동작 상태가 변화되어, 대기 전력 소비를 감소시킨다. 스위칭 전원의 동작이 도 9와 도 10을 참조하여 아래에서 설명될 것이다.

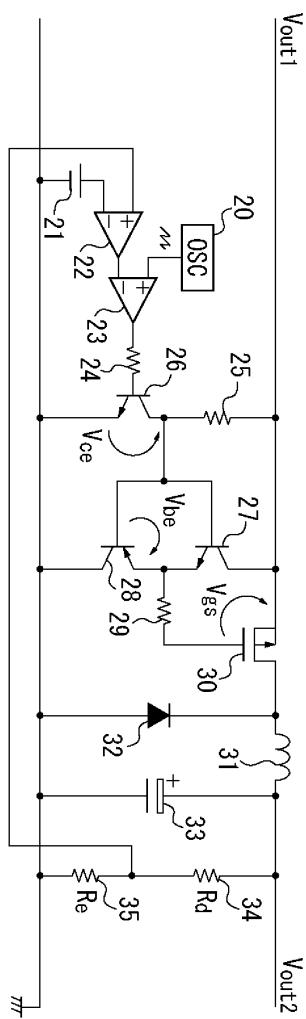

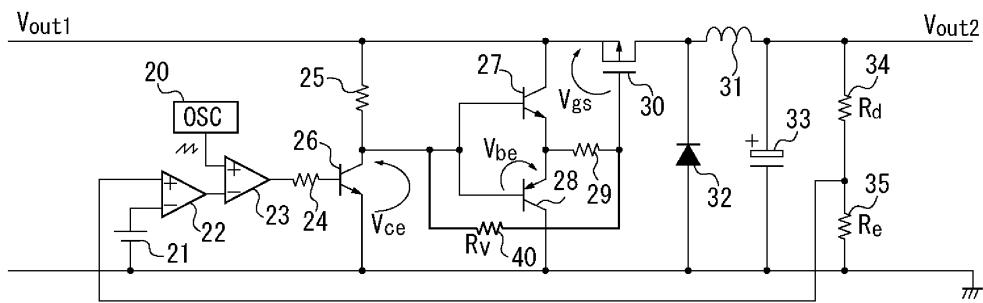

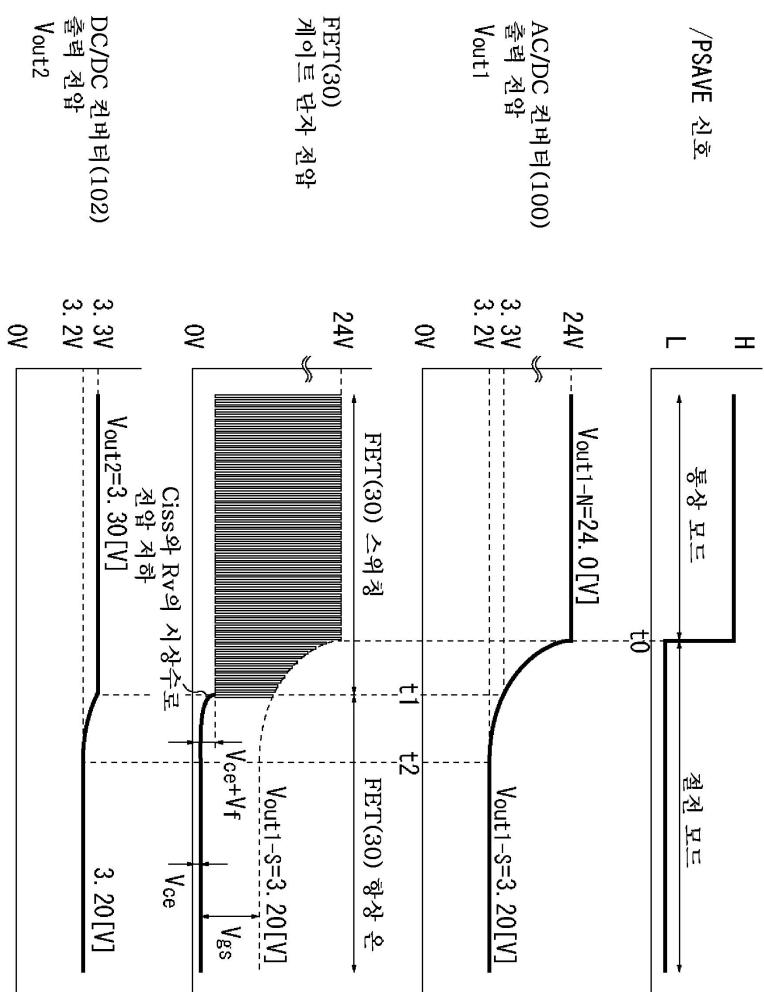

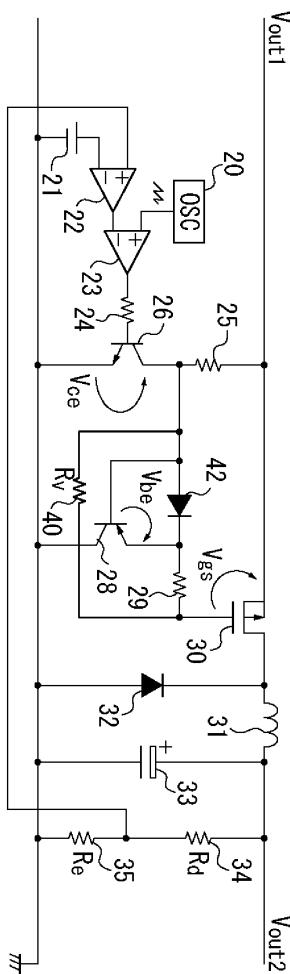

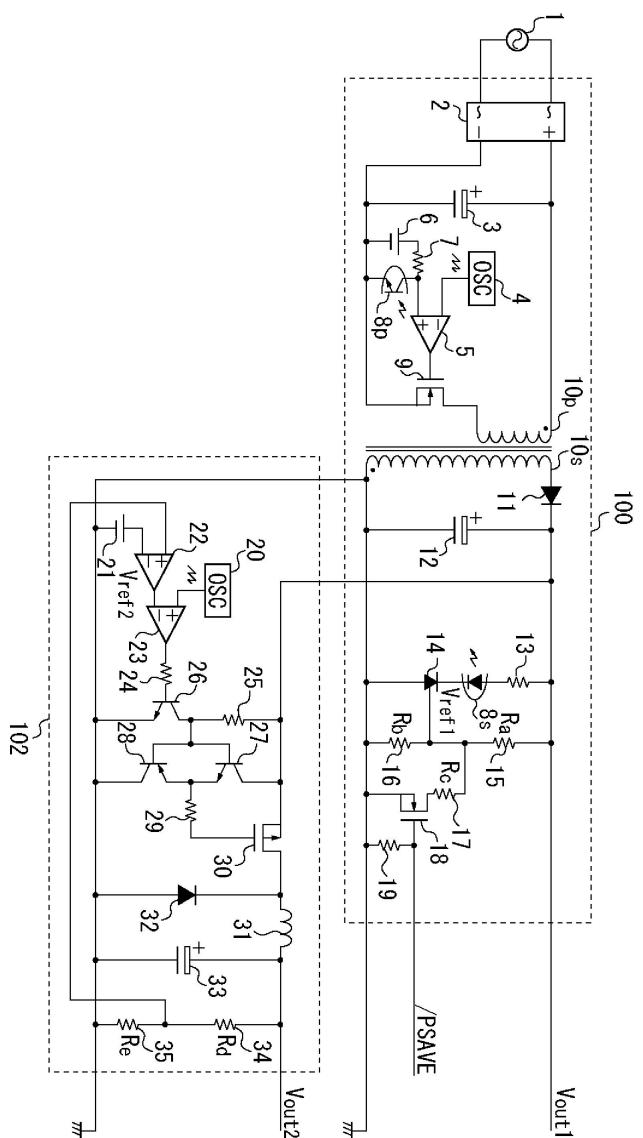

- [0006] 도 10은 상용 전원으로부터의 교류 전압을 직류 전압으로 변환하기 위한 AC/DC 컨버터(100) 및 AC/DC 컨버터(100)로부터의 직류 전압을 다른 직류 전압으로 변환하기 위한 DC/DC 컨버터(102)를 포함하는 스위칭 전원의 회로도이다. 여기에서, 스위칭 전원에 있어서, AC/DC 컨버터는 제1 컨버터로서 기능하며, DC/DC 컨버터는 제2 컨버터로서 기능한다. AC/DC 컨버터의 출력 전압은 제1 전압이며, DC/DC 컨버터의 출력 전압은 제2 전압이다. 본 예에서는, 24.0V의 제1 전압 및 3.30V의 제2 전압을 출력하는 스위칭 전원으로서 스위칭 전원이 설명된다. 다음에, 스위칭 전원의 기본 동작이 설명될 것이다.

- [0007] 우선, 제1 컨버터로서 기능하는 AC/DC 컨버터(100)가 설명될 것이다. 상용 전원(1)의 교류 전압은, 브리지 다이오드(2) 및 1차 평활 콘덴서(3)에 의해 정류 및 평활되어, 직류 전압으로서 출력된다. 직류 전압은 변압기의 1차 권선(10p)을 통하여 스위칭 소자로서 기능하는 전계 효과 트랜지스터(field-effect transistor; FET)(9)에 공급된다. FET(9)의 게이트 단자에는, 비교기(5), 삼각파 발생기(4), 정전압원(6), 저항(7), 및 광결합기(8p)를 포함하는 펄스폭 변조(pulse-width modulation; PWM) 회로가 접속된다. 그리하여 FET(9)는, 광결합기(8p)에 귀환되는 출력 전압의 오차 정보에 기초하여 PWM 스위칭을 행한다. PWM 스위칭이 수행될 때, 이것은 변압기의 2차 권선(10s)에, 펄스 전압을 유도(introduce)한다. 이 펄스 전압은, 다이오드(11) 및 2차 평활 콘덴서(12)에 의해 정류 및 평활되어, 직류 전압  $V_{out1}$ 으로서 출력된다. 전압  $V_{out1}$ 은, 저항들(15, 16 및 13), 센트레귤레이터(14), 및 광결합기(8s)를 포함하는 오차 증폭 회로에 공급된다. 그리하여, FET(9)는 전압  $V_{out1}$ 의 오차 정보에 기초하여 PWM 스위칭을 행한다. 이러한 구성으로써, 전압  $V_{out1}$ 은 일정하게 된다.

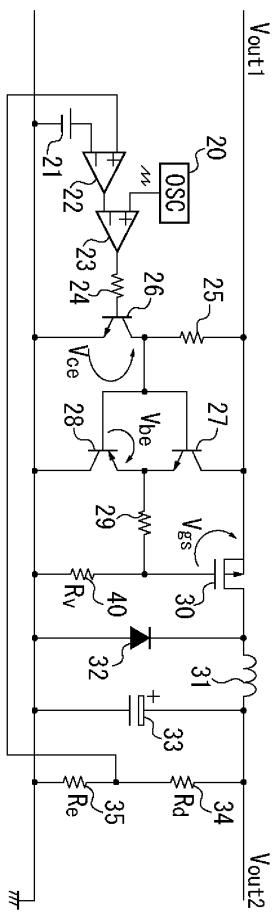

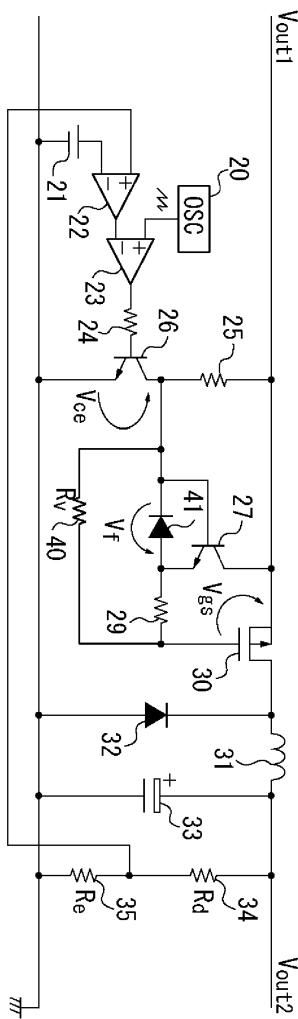

- [0008] 다음에, 제2 컨버터로서 기능하는 DC/DC 컨버터(102)가 설명될 것이다. AC/DC 컨버터(100)의 출력 전압  $V_{out1}$ 은, DC/DC 컨버터(102)로의 입력 전압으로서 스위칭 소자로서 기능하는 FET(30)에 공급된다. FET(30)의 게이트 단자에는, 저항(29)을 통하여, 트랜지스터(27 및 28)를 포함하는 푸시풀 회로(push-pull circuit)가 접속된다. 이 푸시풀 회로는 FET(30)를 구동하기 위한 구동 유닛으로서 기능한다. 푸시풀 회로는 FET(30)의 게이트 입력 전하  $Q_g$ 의 충방전 속도를 향상시킴으로써 스위칭 속도를 향상시키기 위해서 사용된다. 푸시풀 회로에는, 펄스 신호 생성 유닛으로서 기능하고, 저항들(25 및 24), 트랜지스터(26), 비교기들(23, 22), 삼각파 발생기(20) 및 정전압원(21)을 포함하는 PWM 회로가 접속된다. 이러한 PWM 회로는 FET(30)를 스위칭하기 위한 펄스 신호(이하, PWM 신호라고도 칭한다)를 출력한다. FET(30)는, 비교기(22)에 귀환되는 출력 전압의 오차 정보에 기초하여 출력되는 PWM 신호를 기초로 PWM 스위칭을 행한다. 이러한 구성으로써, 인더터(31) 및 다이오드(32)에 펄스 전압이 공급된다. 이 펄스 전압은, 인더터(31), 다이오드(32) 및 전해 콘덴서(33)에 의해 정류되어, 출력 전압  $V_{out2}$ 로서 출력된다. 출력 전압  $V_{out2}$ 는, 저항들(34 및 35)에 의해 분할되어, 비교기(22)에 공급된다. 그리하여, 전술한 바와 같이, FET(30)는 전압  $V_{out2}$ 의 오차 정보에 기초하여 PWM 스위칭을 행한다. 이러한 구성으로써, 전압  $V_{out2}$ 가 일정해진다. 여기서, 전술한 PWM 신호는 펄스폭 변조 신호이며, "PWM 스위칭"은 펄스 폭 변조 신호의 시간 폭에 따른 FET의 스위칭 동작을 칭한다.

- [0009] 도 9에서, 제어 유닛(103)으로부터 AC/DC 컨버터(100)에 절전 신호(이하, /PSAVE 신호라고 칭한다)가 공급된다. 제어 유닛(103)으로부터의 /PSAVE 신호에 의해 절전 모드로의 이행이 지시되면, AC/DC 컨버터(100)의 출력 전압이 감소된다. 그 후, DC/DC 컨버터(102)의 FET(30)를 항상 온(on) 상태로 유지하면서 동작 상태가 절전 모드로 이행되어 전력 소비 감소를 실현한다.

## 발명의 내용

### 해결하려는 과제

- [0010] 여기서, FET(30)로서 범용 소자를 사용할 때, 범용 FET를 항상 온(on) 상태로 유지하기 위한 ON 문턱 전압(ON

threshold voltage)은, 종종, 예를 들어 2.5V 이상이다. 이러한 소자를 사용할 때, 예를 들어, 절전 모드에서 FET의 게이트 단자 전압이 2.5V 미만이면, 도 9에 도시된 스위칭 전원에서 FET를 확실하게 턴 온 할 수 없는 경우가 생길 수 있다. FET와 관계 없이, 전원 회로가 범용의 소자나 부품을 포함할 때, ON 문턱 전압은 2.5V 미만이 된다. 이 문제를 해결하기 위해서, 낮은 ON 문턱 전압을 갖는 소자를 사용할 수 있다. 그러나, 낮은 ON 문턱 전압을 갖는 FET는, 그 게이트 단자의 감도를 향상시키기 위해서, 그러한 FET를 제조하는 데 더욱 미세한 반도체 프로세스를 사용하기 때문에 고가일 수 있다.

- [0011] 또한, 낮은 ON 문턱 전압을 갖는 고가의 FET를 사용할 때, 그러한 FET는 미세 프로세스에서 제조되기 때문에, 드레인과 소스 사이의 내전압이 낮아지는 경향이 있다. 그러나, 전술한 스위칭 전원에서는, 통상 모드의 AC/DC 컨버터의 출력 전압이 높아져, 높은 FET 드레인-소스 내전압이 사용된다. 그리하여, 낮은 ON 문턱 전압을 갖는 고가의 FET는 충분한 드레인-소스 내전압을 갖지 않는다.

### 과제의 해결 수단

- [0012] 본 발명의 양태에 따르면, 컨버터는, 입력 전압을 스위칭하도록 구성되는 스위칭 소자, 스위칭 소자를 구동하도록 구성되는 구동 유닛, 구동 유닛에 펄스 신호를 공급하도록 구성되는 펄스 신호 생성 유닛, 및 구동 유닛을 통하지 않고 스위칭 소자와 펄스 신호 생성 유닛을 접속하도록 구성되는 바이패스 유닛을 포함한다. 입력 전압이 더 낮은 전압으로 스위칭되어 입력 전압의 스위칭이 정지될 때에, 바이패스 유닛의 동작에 의해 스위칭 소자가 온 상태로 유지된다.

- [0013] 본 발명의 다른 특징 및 양태는, 첨부 도면을 참조하여 이하의 예시적인 실시예의 상세한 설명으로부터 명백해질 것이다.

### 도면의 간단한 설명

- [0014] 본 명세서에 포함되어 그 일부를 이루는 첨부 도면은, 본 발명의 예시적인 실시예, 특징, 및 양태를 도시하며, 발명을 실시하기 위한 구체적인 내용과 함께 본 발명의 원리들을 설명한다.

- 도 1a 및 도 1b는 본 발명의 제1 예시적인 실시예에 따른 스위칭 전원의 회로 블록도이다.

- 도 2는 제1 예시적인 실시예에 따른 스위칭 전원의 동작 상태를 도시하는 도면이다.

- 도 3a 내지 도 3c는 제1 예시적인 실시예에 따른 스위칭 전원의 회로 구성의 변형예를 도시하는 도면이다.

- 도 4는 제1 예시적인 실시예에 따른 스위칭 전원의 동작 상태를 도시하는 도면이다.

- 도 5a 및 도 5b는 본 발명의 제2 예시적인 실시예에 따른 스위칭 전원의 회로 블록도이다.

- 도 6은 제2 예시적인 실시예에 따른 스위칭 전원의 동작 상태를 도시하는 도면이다.

- 도 7a 및 도 7b는 본 발명의 제3 예시적인 실시예에 따른 스위칭 전원의 회로 블록도이다.

- 도 8은 제3 예시적인 실시예에 따른 스위칭 전원의 동작 상태를 도시하는 도면이다.

- 도 9는 스위칭 전원의 블록도이다.

- 도 10은 스위칭 전원의 회로 블록도이다.

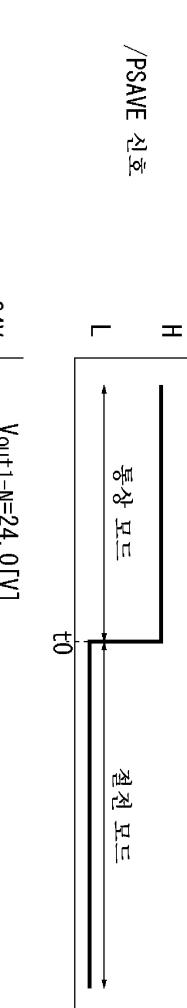

- 도 11은 스위칭 전원의 동작 상태를 도시하는 도면이다.

- 도 12는 스위칭 전원의 회로 블록도이다.

### 발명을 실시하기 위한 구체적인 내용

- [0015] 본 발명의 다양한 예시적인 실시예, 특징, 및 양태가 도면을 참조하여 아래에서 상세하게 설명될 것이다.

- [0016] 우선, 본 발명의 예시적인 실시예의 구성을 설명하기 전에, 본 발명의 배경 구성에서의 문제점이, 도 9, 도 10, 도 11 및 도 12를 참조하여 설명될 것이다.

- [0017] 전술한 바와 같이, 도 9에서, 제어 유닛(103)으로부터 AC/DC 컨버터(100)에 절전 신호(/PSAVE 신호)가 공급될 때, 도 10에 도시된 스위칭 전원은 절전 모드로 이행한다.

- [0018] 이하에, 도 10을 참조하여 절전 모드의 동작이 설명될 것이다. 제어 유닛(103)은 하이(H) 레벨의 /PSAVE 신호

를 공급하여 디바이스를 통상 모드로 설정하거나 또는 로우(L) 레벨의 /PSAVE 신호를 공급하여 디바이스를 절전 모드로 설정한다. 여기에서 /PSAVE 신호는, AC/DC 컨버터(100)의 오차 증폭 회로의 FET(18)에 공급된다. 통상 모드에서, 즉 /PSAVE 신호가 H 레벨일 때, FET(18)는 턴 온되고, 저항(16)과 저항(17)이 병렬로 접속된다. 출력 전압 Vout1은 저항(15)과 병렬 저항들(저항(16)//저항(17))로 분할되고 분할된 전압은 센트 레귤레이터(14)의 레퍼런스 단자에 공급된다. 그리하여, 저항들(15, 16 및 17)의 저항치 각각을 "Ra", "Rb" 및 "Rc"로 나타내고, 센트 레귤레이터(14)의 레퍼런스 전압을 "Vref1"로 나타낼 때, 통상 모드의 출력 전압 Vout1-N은, 수학식 (1)에 의해 근사적으로 표현된다.

[0019] <수학식 1>

$$V_{out1-N} \cong \frac{R_a + (R_b // R_c)}{(R_b // R_c)} \cdot V_{ref1}$$

[0020]

[0021] 여기서, "(Rb//Rc)"는 Rb와 Rc의 병렬 저항치이며 수학식 (2)에 의해 표현된다.

[0022] <수학식 2>

$$R_b // R_c = \frac{R_b \cdot R_c}{R_b + R_c}$$

[0023]

[0024] 한편, 절전 모드에서, 즉 /PSAVE 신호가 L 레벨일 때, FET(18)는 턴 오프되고, 저항(17)은 분리된다. 여기에서, 센트 레귤레이터(14)의 레퍼런스 단자에 공급되는 전압은, Vout1을 저항(15)과 저항(16)에 의해 분할하여 얻어진 전압이다. 그리하여, 절전 모드의 출력 전압 Vout1-S는, 수학식 (3)에 의해 근사적으로 표현된다.

[0025] <수학식 3>

$$V_{out1-S} \cong \frac{R_a + R_b}{R_b} \cdot V_{ref1}$$

[0026]

[0027] 그리하여, 절전 모드의 출력 전압 Vout1-S는, 통상 모드의 출력 전압 Vout1-N보다 낮게 된다.

[0028] DC/DC 컨버터(102)의 출력 전압 Vout2도 마찬가지로 구할 수 있다.

[0029] 전압 Vout2를 저항(34)과 저항(35)으로 분할하여 얻어진 전압이, 오차 증폭 회로 내의 비교기(22)에 공급되어, 정전압원(21)의 전압과 비교된다. 그리하여, 저항들(34 및 35)의 저항치 각각을 "Rd" 및 "Re"로 표시하고, 정전압원(21)의 전압을 Vref2로 표시할 때, 출력 전압 Vout2는 수학식 (4)에 의해 근사적으로 표현된다.

[0030] <수학식 4>

$$V_{out2} \cong \frac{R_d + R_e}{R_e} \cdot V_{ref2}$$

[0031]

[0032] 이상의 식을 사용하여, AC/DC 컨버터(100) 및 DC/DC 컨버터(102)의 출력 전압이 이하의 식에 의해 표현되는 것과 같이 설정되도록 저항치들 Ra, Rb, Rc, Rd 및 Re를 설정한다.

[0033] 여기서, 절전 모드의 AC/DC 컨버터(100)의 출력 전압 Vout1-S를, DC/DC 컨버터(102)의 출력 전압 Vout2보다 조금 낮게 설정한다. 본 예에서는, 전압 Vout2가 3.30V인 한편(Vout2 = 3.30V), 전압 Vout1-S는 3.20V(Vout1-S = 3.20V)라고 가정한다. 그러나, 이것은 일례이며, 출력 전압 Vout1-S의 설정치는 제어 유닛(103)의 동작 전원 전압의 범위 내에서 적절하게 선택될 수 있다.

[0034] <수학식 5>

$$V_{out1-N} \cong \frac{R_a + (R_b // R_c)}{(R_b // R_c)} \cdot V_{ref1} = 24.0[V]$$

[0035]

[0036] <수학식 6>

$$V_{out1-S} \cong \frac{R_a + R_b}{R_b} \cdot V_{ref1} = 3.20[V]$$

[0037]

[0038] <수학식 7>

$$V_{out2} \cong \frac{R_d + R_e}{R_e} \cdot V_{ref2} = 3.30[V]$$

[0039]

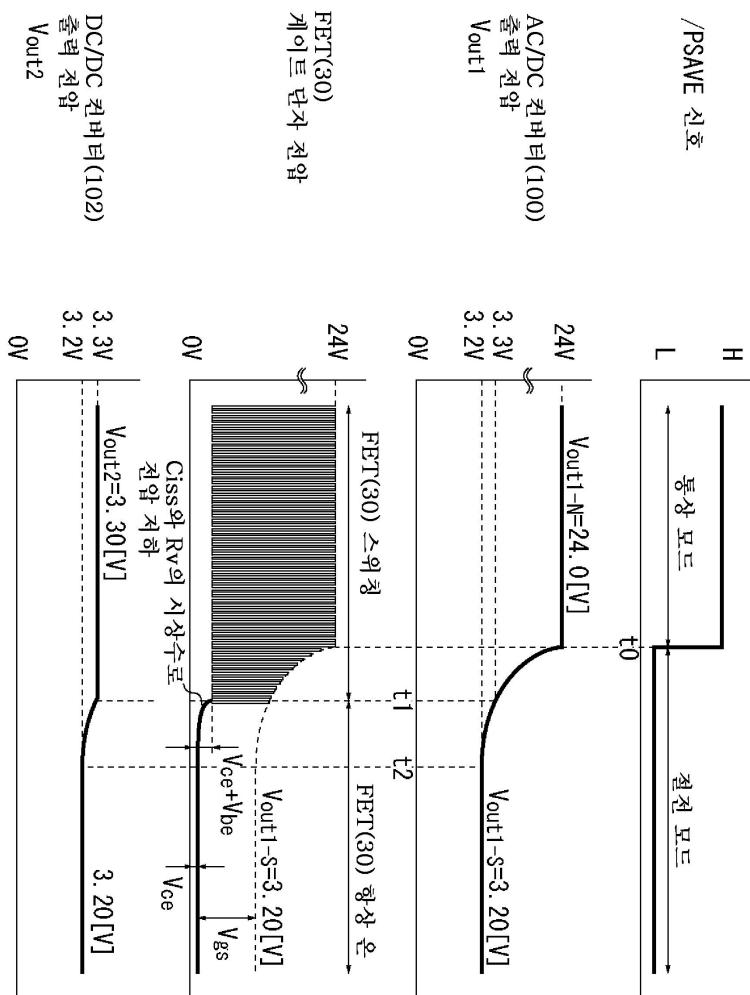

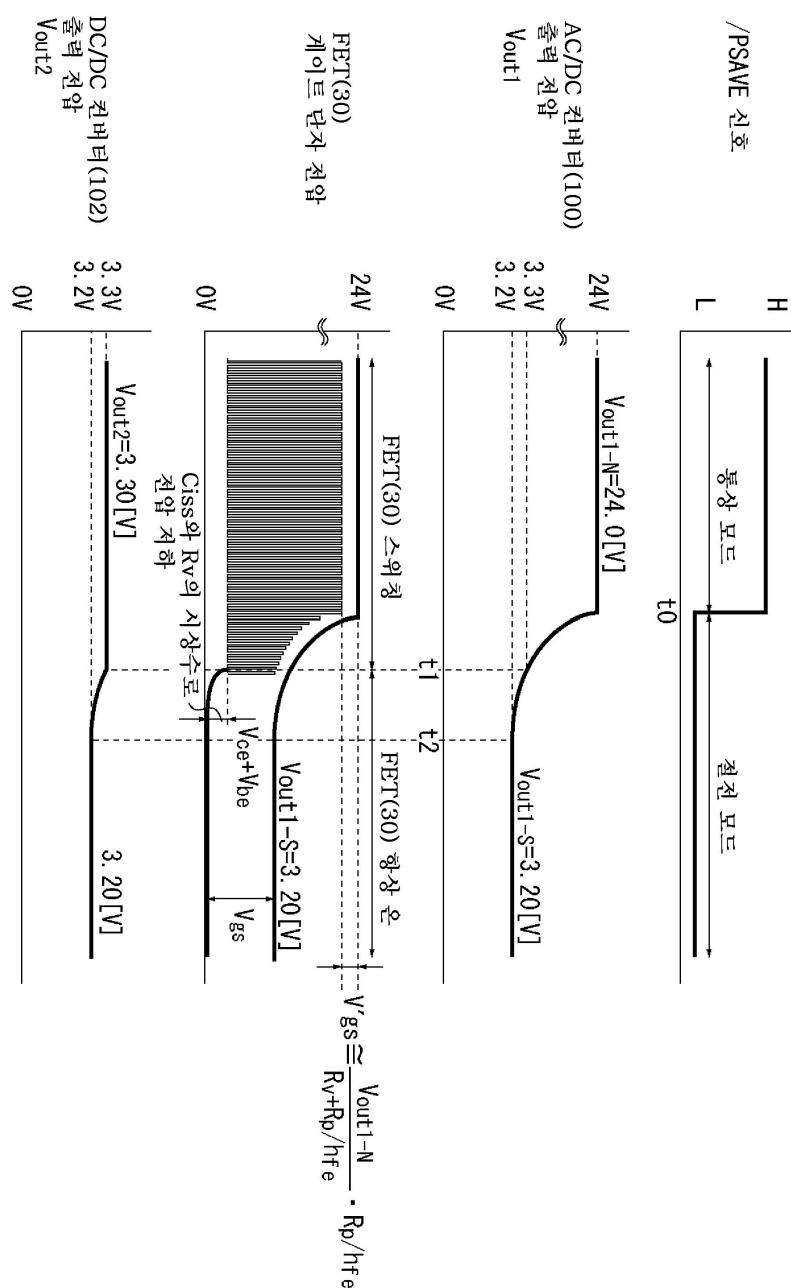

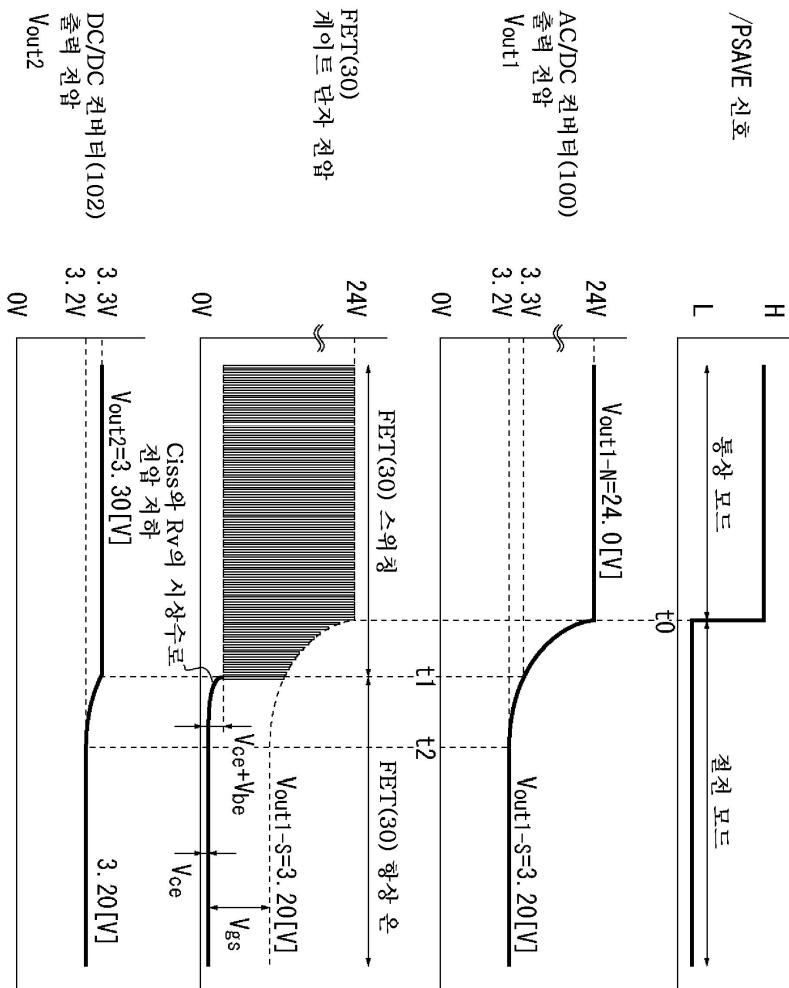

[0040] 이상의 설정에 기초하여, 통상 모드로부터 절전 모드로의 이행을 위한 동작이 도 11을 참조하여 설명될 것이다.

[0041] 도 11에서, 시각 t0 이전에, 제어 유닛(103)은 H 레벨의 /PSAVE 신호를 공급함으로써 디바이스를 통상 모드로 설정한다. 그리하여, AC/DC 컨버터(100)의 출력 전압 Vout1-N이 24.0V이고(Vout1-N = 24.0V), DC/DC 컨버터(102)의 출력 전압 Vout2가 3.30V이다(Vout2 = 3.30V). FET(30)의 게이트 단자에 PWM 펄스가 공급되고, FET(30)는 PWM 펄스에 따라서 스위칭 동작을 행한다. 시각 t0에서, 제어 유닛(103)이 L 레벨의 /PSAVE 신호를 공급하여 디바이스의 모드를 절전 모드로 이행시킨다. 그 후, AC/DC 컨버터(100)의 출력 전압 Vout1은 낮아지기 시작하여, 시각 t2 후에는 3.20V가 된다.

[0042] 이 과정에서, 설명이 DC/DC 컨버터(102)의 동작에 집중될 것이다. AC/DC 컨버터(100)의 출력 전압이 3.30V 이상인 영역에서, FET(30)의 게이트 단자에 PWM 펄스가 공급되어, FET(30)은 스위칭을 행한다. 이러한 구성으로써, DC/DC 컨버터(102)의 출력 전압은, 3.30V에서 일정해진다. 시각 t1 이후, AC/DC 컨버터(100)의 출력 전압이 3.30V보다 낮아질 때, DC/DC 컨버터(102)의 출력 전압은, 제어 목표인 3.30V에서 유지될 수 없기 때문에, FET(30)은 항상 온 상태로 유지된다. 즉, FET(30)은 스위칭을 행하지 않고, 온 상태가 유지되는 도통 상태인 채로 있다. 이러한 구성으로써, DC/DC 컨버터(102)의 출력 전압은 AC/DC 컨버터(100)의 출력 전압과 대략 동일하게 되고 시각 t2 후에는 3.20V가 된다.

[0043] 이상 기술된 바와 같이, 절전 모드에서, AC/DC 컨버터(100)의 출력 전압이 DC/DC 컨버터(102)의 제어 목표 전압 이하가 되어, DC/DC 컨버터(102)의 FET(30)를 항상 온 상태로 유지한다. 이에 의해, 전력 소비를 감소시키기 위한 이하의 효과가 얻어질 수 있다. 우선, AC/DC 컨버터(100)의 출력 전압 Vout1이 낮아질 때, 액추에이터(101)의 전력 소비가 감소된다. 또한, FET(30)에 의한 스위칭이 정지할 때, 스위칭 손실이 방지된다.

[0044] 이러한 절전 모드에서, AC/DC 컨버터(100)의 출력 전압을 감소시키는 것 및, DC/DC 컨버터(102)의 FET(30)를 항상 온 상태로 유지하는 것이 가능한 구성은, 하기의 문제를 갖는다.

[0045] 도 11에 FET(30)의 게이트 단자 전압의 파형에 의해 도시된 바와 같이, FET(30)가 항상 온 상태일 때, FET(30)의 게이트-소스 전압 Vgs는, AC/DC 컨버터(100)의 출력 전압 Vout1-S보다 Vce + Vbe만큼 낮아진다.

[0046] 도 12에 도시된 바와 같이, "Vce"는 트랜지스터(26)의 이미터-콜렉터 전압이고 "Vbe"는 트랜지스터(28)의 베이스-이미터 전압이다. 또한, Vgs는 수학식 (8)에 의해 근사적으로 표현된다.

[0047] <수학식 8>

$$V_{gs} \cong V_{out1-S} - (V_{ce} + V_{be})$$

[0048]

[0049] 전술한 예에서, 전압 Vout1-S는 3.20V이다(Vout1-S = 3.20V). 또한, 일반적인 트랜지스터에서는 전압 Vce가 대략 0.4V(Vce = 0.4V)이고, 전압 Vbe가 대략 0.7V이어서(Vbe = 0.7V), Vgs = 3.20V - (0.4V + 0.7V) = 2.1V와 같이 표현될 수 있다. 그 후, ON 문턱 전압 Vgs-on을 갖는 FET는, 일반적으로 4.0V 또는 적어도 2.5V 이상의 전압을 갖는 소자이다. 전압 Vgs가 2.1V인(Vgs = 2.1V) 본 예에서, 2.5V의 전압 Vgs-on을 갖는 FET를 사용할 때, FET를 확실하게 턴 온 할 수 없다. FET를 확실하게 턴 온하기 위해서, 더 낮은 ON 문턱 전압을 갖는 FET, 또는 예를 들어, 1.5V의 ON 문턱 전압 Vgs-on을 갖는 FET를 사용할 수 있다. 그러나 낮은 ON 문턱 전압을 갖는 FET는, 그러한 FET가 그 게이트 감도를 향상시키기 위하여 더 미세한 반도체 프로세스에서 제조되기 때문에 고가이다. 그리하여, 저렴한 회로 구성으로 FET를 확실하게 턴 온하는 것은 어렵다.

[0050] 또한, 더 낮은 ON 문턱 전압을 갖는 FET는, 그러한 FET가 미세한 프로세스에서 만들어지기 때문에, 더 낮은 드레인-소스 내전압 Vdss를 갖는 경향이 있다. 그러나, 본 예에서는 통상 모드에서 AC/DC 컨버터의 출력 전압

Vout1-N이 하이가 되기 때문에, 높은 드레인-소스 내전압 Vdss를 갖는 FET(30)가 사용되어야 한다. 따라서, 낮은 ON 문턱 전압을 갖는 FET를 사용할 때, 전압 Vdss가 충분하지 않다. 구체적으로는, 가정된 예에서, 전압 Vout1-N이 24.0V이기 때문에(Vout1-N = 24.0V), 30V 또는 40V의 전압 Vdss를 갖는 FET가 사용되어야 한다. 그러나, 일반적으로, 1.5V의 ON 문턱 전압 Vgs-on을 갖는 FET는 전압 Vdss가 대략 10V 내지 20V이기 때문에 적용할 수 없다.

[0051] 다음에, 상기 문제를 해결하기 위하여, 본 발명의 예시적인 실시예의 구성예가 이하의 예시적인 실시예에 기초하여 설명될 것이다.

[0052] 우선, 본 발명의 예시적인 제1 실시예가 설명될 것이다. 여기서, 상기 예의 구성과 유사한 구성을 표시하기 위해서, 동일한 참조 번호가 사용되고, 그 설명은 반복되지 않는다.

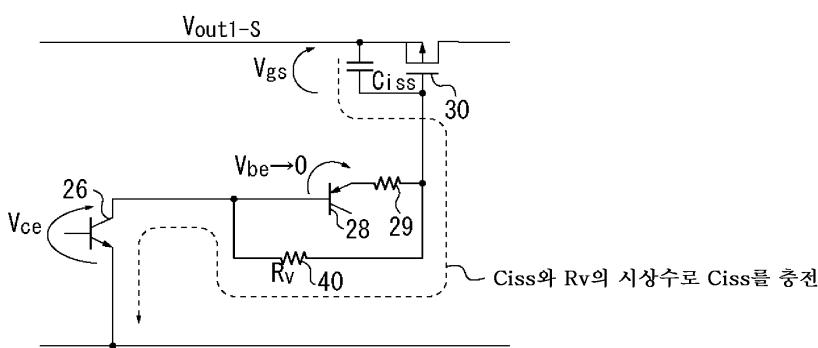

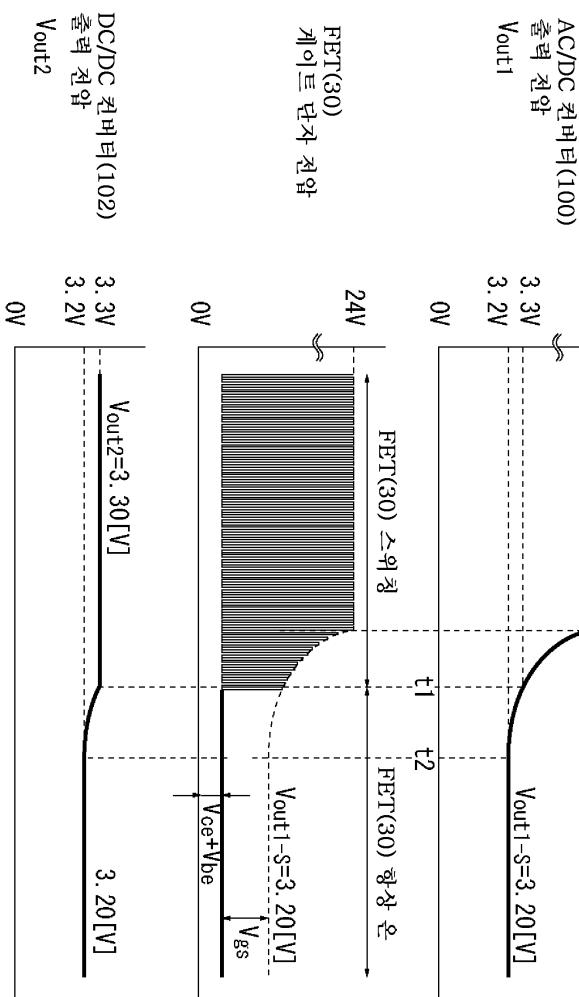

[0053] 도 1a는 제1 예시적인 실시예에 따른 DC/DC 컨버터의 회로 구성을 도시한다. 본 예시적인 실시예는 도 10의 상술된 DC/DC 컨버터(102)에 더하여 바이패스 저항(40)이 FET(30)의 게이트 단자와 트랜지스터(26)의 콜렉터 단자 사이에 제공되는 구성을 갖는다. 바이패스 저항(40)은 FET의 입력 용량을 충전하도록 구성된 바이패스 유닛으로서 기능한다.

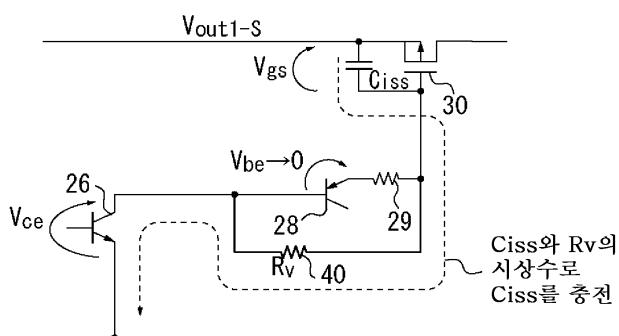

[0054] 본 예시적인 실시예의 구성에서, 절전 모드 동안 AC/DC 컨버터(100)의 출력 전압이 낮아지고 DC/DC 컨버터(102)의 FET(30)를 항상 온 상태로 유지할 때, 도 2에 FET(30)의 게이트 단자 전압의 과정에 의해 도시된 바와 같이, 시각 t1에서, FET(30)의 게이트-소스 전압 Vgs는, AC/DC 컨버터(100)의 출력 전압 Vout1-S보다 Vce + Vbe 만큼 낮아진다. 도 1a에 도시된 바와 같이, "Vce"는 트랜지스터(26)의 이미터-콜렉터 전압을 나타내고 "Vbe"는 트랜지스터(28)의 베이스-이미터 전압을 나타낸다. 그리하여, 전압 "Vgs"는 수학식 (9)로 근사적으로 표현된다.

[0055] <수학식 9>

$$V_{gs} \cong V_{out1-S} - (V_{ce} + V_{be})$$

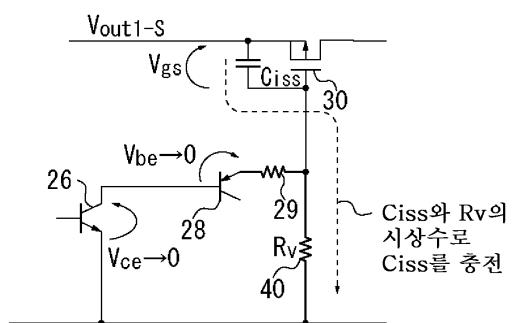

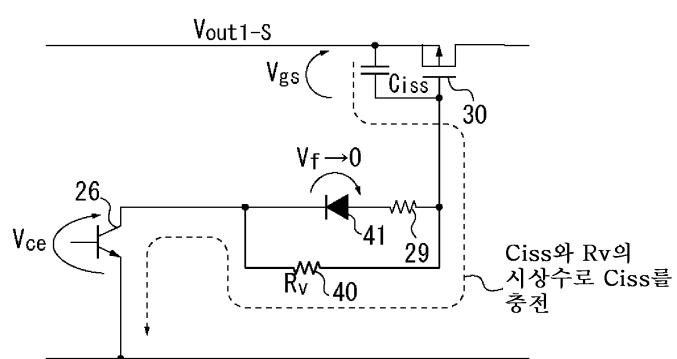

[0056] 그 후, 도 1b에 도시된 바와 같이, FET(30)의 입력 용량은 바이패스 저항(40)을 통해서 충전된다. FET(30)의 입력 용량을 "Ciss"로 나타내고, 바이패스 저항(40)의 저항치를 "Rv"로 나타낼 때, Ciss와 Rv의 시상수로 FET(30)의 입력 용량이 충전되어, 트랜지스터(28)의 베이스-이미터 전압 Vbe가 대략 0V가 된다. 그리하여, FET(30)의 게이트-소스 전압은 수학식 (10)에 의해 표현된다.

[0058] <수학식 10>

$$V_{gs} \cong V_{out1-S} - V_{ce}$$

[0059] 전술한 바와 같이, FET(30)의 게이트 단자와 트랜지스터(26)의 콜렉터 단자의 사이에 바이패스 저항(40)을 추가할 때, 트랜지스터(28)의 베이스와 이미터 사이에 인가되는 전압을 대략 0V로 할 수 있어서, FET(30)의 게이트-소스 전압을 증가시킬 수 있다. 상기 예에서, 전압 Vout1-S는 3.20V이다. 또한, 전형적인 트랜지스터는 약 0.4V의 전압 Vce를 갖기 때문에, Vgs = 3.20V - 0.4V = 2.8V로서 표현될 수 있다. FET의 ON 문턱 전압 Vgs-on은 일반적으로 4.0V 또는 2.5V이다. 전압 Vgs가 2.8V인(Vgs = 2.8V) 본 예에서, 2.5V인 전압 Vgs-on을 갖는 FET가 사용될 때, FET는 확실하게 터 온될 수 있다.

[0061] 도 3a에 도시된 바와 같이, FET(30)의 게이트 단자와 그라운드(GND) 단자의 사이에, 바이패스 저항(40)을 추가함으로써, 유사한 효과를 얻을 수 있다. 도 4에 FET(30)의 게이트 단자 전압의 과정에 의해 도시된 바와 같이, 시각 t1에서, FET(30)의 게이트-소스 전압 Vgs는, AC/DC 컨버터(100)의 출력 전압 Vout1-S보다 Vce + Vbe 만큼 낮아진다. 도 3a에 도시된 바와 같이, "Vce"는 트랜지스터(26)의 이미터-콜렉터 전압을 나타내고, "Vbe"는 트랜지스터(28)의 베이스-이미터 전압을 나타낸다. 그리하여, 전압 Vgs는 수학식 (11)에 의해 근사적으로 표현된다.

[0062] <수학식 11>

$$V_{gs} \cong V_{out1-S} - (V_{ce} + V_{be})$$

[0063] 그 후, 도 3b에 도시된 바와 같이, FET(30)의 입력 용량은 바이패스 저항(40)을 통해서 충전된다. FET(30)의

입력 용량을 "Ciss"로 표현하고, 바이패스 저항(40)의 저항치를 "Rv"로 표현할 때, Ciss와 Rv의 시상수로 FET(30)의 입력 용량이 충전되고, 트랜지스터(26)의 이미터-콜렉터 전압 Vce 및 트랜지스터(28)의 베이스-이미터 전압 Vbe는 대략 0V가 된다. 따라서, FET(30)의 게이트-소스 전압은 수학식 (12)에 의해 표현된다.

[0065] <수학식 12>

$$V_{gs} \cong V_{out1-S}$$

[0066]

[0067] 이상과 같이, FET(30)의 게이트 단자와 GND 단자의 사이에 바이패스 저항(40)이 추가될 때, FET(30)의 게이트-소스 전압을 증가시킬 수 있다. 그러나, FET(30)의 게이트 단자와 GND 단자의 사이에 바이패스 저항(40)을 추가할 때에는 이하의 점에 대하여 주의가 필요하다.

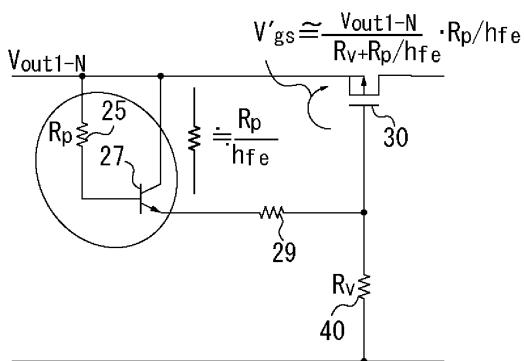

[0068] 도 3c에 도시된 바와 같이, 저항(25)과 트랜지스터(27)는, 외관상, 저항치 "Rp/hfe"에 의해 표현되는 저항과 등가이다. 여기서, "Rp"는 저항(25)의 저항치를 나타내고, "hfe"는 트랜지스터(27)의 전류 증폭률을 나타낸다. 그리하여, 도 4에 도시된 바와 같이, 통상 모드에서 FET(30)이 턴 오프될 때, FET(30)의 게이트-소스 전압 Vgs'와 같은 수학식(13)에 의해 표현된 전압이 남아있을 수 있다. 단, 저항(29)의 저항치는 Rv 및 Rp/hfe보다 충분히 작다고 가정된다.

[0069] <수학식 13>

$$V_{gs}' \cong \frac{V_{out1-N}}{R_v + R_p/h_{fe}} \cdot R_p/h_{fe}$$

[0070]

[0071] 그리하여, 수학식 (13)의 전압 Vgs'가 FET(30)의 OFF 문턱 전압 Vgs-off보다 커지면, FET(30)을 턴 오프할 수 없다. 그리하여, 저항치들 Rv 및 Rp의 설정에 주의가 필요하다. 즉, 전압 Vgs'가 전압 Vgs-off보다 낮아지도록 (Vgs' < Vgs-off), 수학식 (13)에 기초하여 값을 Rv 및 Rp가 설정되어야 한다. 여기서, 도 1a에 도시된 예에서는, FET(30)의 전압 Vgs가 남아있지 않으므로 잔류 전압(residual voltage)을 고려하지 않고 FET(30)가 확실하게 턴 오프될 수 있다.

[0072] 그리하여, 범용 소자를 사용한 저렴한 회로 구성으로써, 절전 모드에서 FET를 확실하게 턴 온 할 수 있다.

[0073] 다음에, 본 발명의 제2 예시적인 실시예가 설명될 것이다. 여기서, 전술한 예의 구성과 유사한 구성을 표시하는 데에 동일한 참조 번호가 사용되고, 그 설명은 반복되지 않는다.

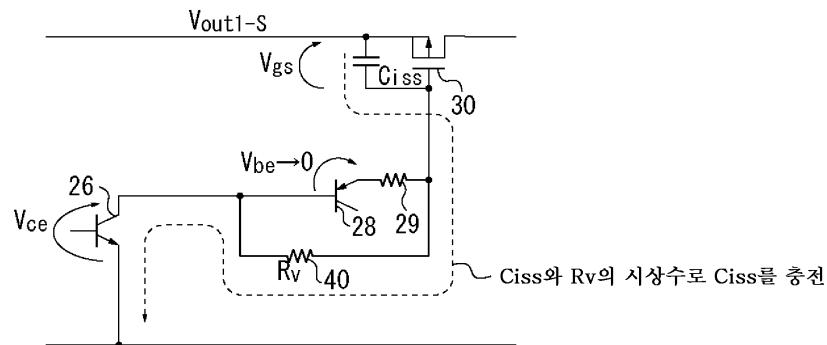

[0074] 도 5a는 제2 예시적인 실시예에 따른 회로 구성을 도시한다. 이러한 회로 구성을 제1 예시적인 실시예의 도 1a의 DC/DC 컨버터에서 트랜지스터(28)의 대체물로서 다이오드(41)가 제공되는 회로를 나타낸다. 푸시풀 회로에서, NPN 트랜지스터(27)는 FET(30)를 턴 오프하는 속도를 향상시키고, PNP 트랜지스터(26)는 FET(30)를 턴 온하는 속도를 향상시킨다. FET(30)를 턴 온하는 속도를 향상시키지 않는 때에는, 본 예시적인 실시예에 따른 도 5a에 도시된 바와 같이, 도 1a의 트랜지스터(28)를 다이오드(41)로 교체할 수 있다.

[0075] 본 예시적인 실시예의 구성에 따르면, 절전 모드 동안, AC/DC 컨버터(100)의 출력 전압이 낮아지고 DC/DC 컨버터(102)의 FET(30)를 항상 온 상태로 유지할 때, 도 6에 FET(30)의 게이트 단자 전압의 파형에 의해 도시된 바와 같이, 시각 t1에서, FET(30)의 게이트-소스 전압 Vgs는, AC/DC 컨버터(100)의 출력 전압 Vout1-S보다 Vce + Vf만큼 낮아진다.

[0076] 도 5a에 도시된 바와 같이, "Vce"는 트랜지스터(26)의 이미터-콜렉터 전압을 나타내고, "Vf"는 다이오드(41)의 순방향 전압을 나타낸다. 그리하여, 전압 Vgs는 수학식 (14)에 의해 근사적으로 표현될 수 있다.

[0077] <수학식 14>

$$V_{gs} \cong V_{out1-S} - (V_{ce} + V_f)$$

[0078]

[0079] 그 후, 도 5b에 도시된 바와 같이, FET(30)의 입력 용량은, 바이패스 저항(40)을 통해서 충전되는 것이 된다. FET(30)의 입력 용량을 "Ciss"로 표현하고 바이패스 저항(40)의 저항치를 "Rv"로 표현하면, Ciss와 Rv의 시상수로 FET(30)의 입력 용량이 충전되어, 다이오드(41)의 순방향 전압 Vf는 대략 0V가 된다.

[0080] 따라서, FET(30)의 게이트-소스 전압은, 수학식 (15)에 의해 표현된다.

[0081] <수학식 15>

$$V_{gs} \cong V_{out1-S} - V_{ce}$$

[0083] 이상과 같이, FET(30)의 게이트 단자와 트랜지스터(26)의 콜렉터 단자의 사이에 바이패스 저항(40)이 추가되기 때문에, 다이오드(41)의 애노드와 캐소드 사이에 인가되는 전압이 대략 0V가 될 수 있고 FET(30)의 게이트-소스 전압이 증가될 수 있다.

[0084] 전술한 구성에서는, 전압  $V_{out1-S}$ 가 3.20V이다. 또한, 일반적인 트랜지스터는 약 0.4V인 전압  $V_{ce}$ 를 갖기 때문에,  $V_{gs} = 3.20V - 0.4V = 2.8V$ 로 표현될 수 있다. FET의 ON 문턱 전압  $V_{gs-on}$ 은 일반적으로 4.0V 또는 2.5V이다. 전압  $V_{gs}$ 가 2.8V인 ( $V_{gs} = 2.8V$ )의 본 예에서, 2.5V인 전압  $V_{gs-on}$ 을 갖는 FET를 사용하면, FET가 확실하게 턴 온될 수 있다.

[0085] 그리하여, 범용의 소자를 포함하는 저렴한 회로 구성에서, 절전 모드 동안 FET를 확실하게 턴 온 할 수 있다.

[0086] 다음에, 본 발명의 제3 예시적인 실시예가 설명될 것이다. 여기서, 전술한 예의 구성과 유사한 구성을 나타내는 데에, 동일한 참조 번호가 사용되고 그 설명은 반복하지 않는다.

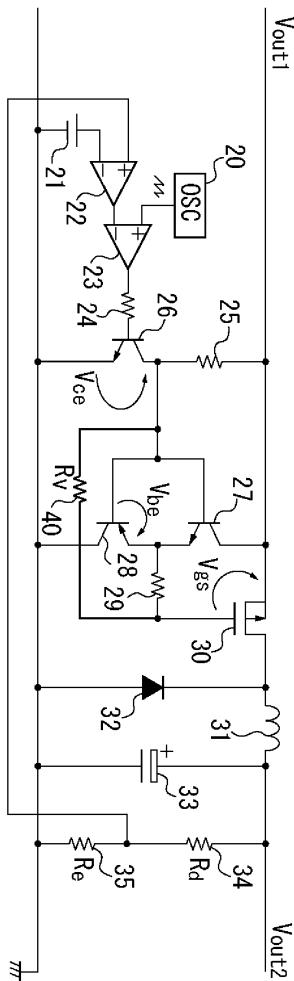

[0087] 도 7a는 본 예시적인 실시예의 회로 구성을 도시한다. 본 회로 구성은 도 1a에 도시된 제1 예시적인 실시예의 DC/DC 컨버터의 트랜지스터(27)의 대체물로서의 다이오드(42)를 포함한다. 도 1a에 도시된 푸시풀 회로에서, NPN 트랜지스터(27)는 FET(30)를 턴 오프하는 속도를 향상시키고, PNP 트랜지스터(28)는 FET(30)를 턴 온하는 속도를 향상시킨다. FET(30)를 턴 오프하는 속도가 향상되지 않을 때, 도 1a의 트랜지스터(27)를, 도 7a에 도시된 바와 같은 다이오드(42)로 교체할 수 있다.

[0088] 본 예시적인 실시예의 구성에서, 절전 모드 동안, AC/DC 컨버터(100)의 출력 전압이 낮아지고 DC/DC 컨버터(102)의 FET(30)를 항상 온 상태로 유지할 때, 도 8에 FET(30)의 게이트 단자 전압의 파형에 의해 도시된 바와 같이, 시각 t1에서, FET(30)의 게이트-소스 전압  $V_{gs}$ 는, AC/DC 컨버터의 출력 전압  $V_{out1-S}$ 보다  $V_{ce} + V_{be}$ 만큼 낮다. 도 7a에 도시된 바와 같이, "Vce"는 트랜지스터(26)의 이미터-콜렉터 전압을 나타내고, "Vbe"는 트랜지스터(28)의 베이스-이미터 전압을 나타낸다. 그리하여, 전압  $V_{gs}$ 는 수학식 (16)에 의해 근사적으로 표현될 수 있다.

[0089] <수학식 16>

$$V_{gs} \cong V_{out1-S} - (V_{ce} + V_{be})$$

[0090] 그 후, 도 7b에 도시된 바와 같이, FET(30)의 입력 용량은 바이패스 저항(40)을 통해서 충전되는 것이 된다. FET(30)의 입력 용량을 "Ciss"로 나타내고, 바이패스 저항(40)의 저항치를 "Rv"로 나타내면, Ciss와 Rv의 시상으로 FET(30)의 입력 용량이 충전되어, 트랜지스터(28)의 베이스-이미터 전압  $V_{be}$ 가 대략 0V가 된다. 그리하여 FET(30)의 게이트-소스 전압  $V_{gs}$ 는 수학식 (17)로 표현된다.

[0092] <수학식 17>

$$V_{gs} \cong V_{out1-S} - V_{ce}$$

[0094] 전술된 바와 같이, FET(30)의 게이트 단자와 트랜지스터(26)의 콜렉터 단자 사이에 바이패스 저항(40)이 추가될 때, 트랜지스터(28)의 베이스와 이미터 사이에 인가되는 전압이 대략 0V가 될 수 있고, FET(30)의 게이트-소스 전압이 증가된다.

[0095] 배경 기술의 설명된 예에서는, 전압  $V_{out1-S}$ 는 3.20V이다. 또한, 일반적인 트랜지스터는 0.4V의 전압  $V_{ce}$ 를 갖기 때문에,  $V_{gs} = 3.20V - 0.4V = 2.8V$ 로 표현될 수 있다. FET의 ON 문턱 전압  $V_{gs-on}$ 은 일반적으로 4.0V 또는 2.5V이다. 전압  $V_{gs}$ 가 2.8V인( $V_{gs} = 2.8V$ ) 본 예에서, 2.5V의 전압  $V_{gs-on}$ 을 갖는 FET를 사용할 때, FET를 확실하게 턴 온할 수 있다.

[0096] 상기 제1 내지 제3 예시적인 실시예에서 설명된 DC/DC 컨버터를 갖는 스위칭 전원을, 예를 들어, 기록재 상에 화상을 형성하는 화상 형성 장치에 적용할 수 있다. 화상 형성 장치의 예는, 원고를 복사하는 복사기, 및 레이

저 범 프린터 또는 잉크젯 프린터와 같은 컴퓨터로부터의 지시에 응답하여 동작하는 프린터를 포함한다.

- [0097] 예를 들어, 상술한 제1 내지 제3 예시적인 실시예의 AC/DC 컨버터로부터의 출력 전압( $V_{out1}$ )은 화상 형성 장치의 화상 형성 구동 유닛으로서 사용되는 구동 모터에 공급되고, DC/DC 컨버터로부터의 출력 전압( $V_{out2}$ )은 CPU를 포함하는 제어 유닛에 공급된다. 여기서, 화상 형성 장치의 구동 모터의 예는, 기록지를 반송하는 반송 롤러의 구동 모터, 및 화상 형성 구동 유닛을 구동하는 모터를 포함한다.

- [0098] 그러한 화상 형성 장치는 화상을 형성하기 위한 동작 모드에 더하여, 화상 형성을 행하지 않을 때 대기 상태 동안 전력 소비를 감소시키기 위한 절전 모드를 갖는다. 이 절전 모드에서, 구동 모터에 공급되는 전력을 던 오프해서 전술한 바와 같이 스위칭 전원을 절전 모드로 이행시킬 수 있다. 즉, 스위칭 전원을 제어 유닛에만 전력을 공급하는 상태로 이행시킨다. 이에 의해, 화상 형성 장치의 절전 모드에서, 저렴한 구성을 갖는 스위칭 전원으로, 확실하게 절전 모드에서의 동작이 수행될 수 있다.

- [0099] 본 발명이 예시적인 실시예들을 참조하여 설명되었지만, 본 발명이 개시된 예시적인 실시예들에 한정되지 않는다는 것이 이해되어야 한다. 하기의 청구항들의 범위는 모든 변형들, 등가의 구조들 및 기능들을 포함하도록 최광의의 해석을 따라야 한다.

### 부호의 설명

- [0100]

- 20: 삼각파 발생기

- 21: 정전압원

- 22, 23: 비교기

- 27, 28: 트랜지스터

- 30: FET

- 31: 인덕터

- 32: 다이오드

도면

도면1a

도면1b

## 도면2

도면3a

도면3b

도면3c

도면4

도면5a

도면5b

## 도면6

도면7a

도면7b

도면8

도면9

도면10

도면11

도면12