(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2018년02월22일

(11) 등록번호 10-1831275

(24) 등록일자 2018년02월14일

- (51) 국제특허분류(Int. Cl.)

*H01L 25/065* (2006.01) *H01L 23/66* (2006.01)

- (21) 출원번호 10-2013-7004577

- (22) 출원일자(국제) 2011년08월04일

심사청구일자 2016년05월18일

- (85) 번역문제출일자 2013년02월22일

- (65) 공개번호 10-2013-0094805

- (43) 공개일자 2013년08월26일

- (86) 국제출원번호 PCT/US2011/046518

- (87) 국제공개번호 WO 2012/027081

국제공개일자 2012년03월01일

- (30) 우선권주장

12/868,577 2010년08월25일 미국(US)

- (56) 선행기술조사문헌

JP09044272 A\*

US07215845 B1\*

\*는 심사관에 의하여 인용된 문헌

- (73) 특허권자

오라클 인터내셔널 코포레이션

미국, 캘리포니아 94065, 레드우드 시티, 오라클

파크웨이 500

- (72) 발명자

하라다, 존 에이.

미국 94041 캘리포니아주 마운틴 뷰 처치 스트리

트 531

더글라스, 데이비드 씨.

미국 94301 캘리포니아주 팔로 알토 바이런 스트

리트 334

드로스트, 로버트 제이.

미국 94024 캘리포니아주 로스 알토스 비아 마데

라스 2211

- (74) 대리인

양영준, 백만기, 정은진

전체 청구항 수 : 총 20 항

심사관 : 안경민

(54) 발명의 명칭 램프-스택 칩 패키지의 광 통신

**(57) 요 약**

램프-스택 칩 패키지가 설명된다. 이러한 칩 패키지는 칩들의 수직 스택, 또는 수평 방향으로 서로 오프셋되는 반도체 다이들을 포함하여, 계단식 테라스를 규정한다. 계단식 테라스에 거의 평행하게 배치되는 고-대역폭 램프 컴포넌트가 반도체 다이들에 기계적으로 결합된다. 또한, 램프 컴포넌트는 광신호를 전달하는 광도파로, 및 반도체 다이들 중 하나에 광신호를 광학적으로 결합하는 광 결합 컴포넌트를 포함하여, 반도체 다이와 램프 컴포넌트 사이의 광신호의 고-대역폭 통신을 용이하게 한다.

**대 표 도**

## 명세서

### 청구범위

#### 청구항 1

칩 패키지로서,

수직 방향의 수직 스택으로 배열된 반도체 다이들의 세트 - 상기 반도체 다이들의 세트는 상기 수직 스택 내의 제1 반도체 다이에 수직이고, 상기 제1 반도체 다이 다음의, 각각의 반도체 다이는, 상기 수직 스택 내의 직전(immediately preceding) 반도체 다이로부터의 오프셋 값만큼 수평 방향으로 오프셋되어, 상기 수직 스택의 일측에서 계단식 테라스(stepped terrace)를 규정함 - ; 및

상기 반도체 다이들에 기계적으로 견고하게 결합된 램프 컴포넌트(ramp component) - 상기 램프 컴포넌트는 상기 수직 스택의 상기 일측에 배치됨 -

를 포함하며,

상기 램프 컴포넌트는, 상기 수평 방향과 상기 수직 방향 사이에 있는 상기 계단식 테라스를 따르는 방향에 평행하고,

상기 램프 컴포넌트는,

광신호를 전달하도록 구성된 광도파로(waveguide), 및

상기 반도체 다이들의 세트 내의 반도체 다이(a semiconductor die)에 상기 광신호를 광학적으로 결합하도록 구성된 광 결합 컴포넌트(optical coupling component)를 포함하고,

각각의 반도체 다이는, 상기 수평 방향에 평행하고 상기 계단식 테라스 상에 있는 상기 반도체 다이의 표면 상의 땜납 패드를 포함하고,

상기 램프 컴포넌트는 상기 땜납 패드들 중 대응하는 땜납 패드를 사용하여 각각의 반도체 다이에 견고하게 결합되는 칩 패키지.

#### 청구항 2

제1항에 있어서,

상기 램프 컴포넌트는 상기 광 결합 컴포넌트를 포함하는 광 결합 컴포넌트들의 세트를 포함하고,

상기 광 결합 컴포넌트들의 세트 내의 소정의(given) 광 결합 컴포넌트는, 상기 반도체 다이를 포함하는 상기 반도체 다이들의 세트 내의 소정의 반도체 다이에 상기 광신호를 광학적으로 결합하도록 구성되는 칩 패키지.

#### 청구항 3

제1항에 있어서,

상기 광도파로는 상기 계단식 테라스를 따르는 방향으로 상기 광신호를 전달하도록 구성되고,

상기 광 결합 컴포넌트는 상기 반도체 다이의 평면(a plane)에 상기 광신호를 재지향(redirect)시키는 칩 패키지.

#### 청구항 4

제3항에 있어서,

상기 광신호는 상기 반도체 다이의 예지를 통해 상기 반도체 다이에 광학적으로 결합되는 칩 패키지.

#### 청구항 5

제1항에 있어서,

상기 광도파로는 상기 계단식 테라스를 따르는 방향으로 상기 광신호를 전달하도록 구성되고,

상기 광 결합 컴포넌트는 상기 반도체 다이의 표면(a surface)에 법선(normal)을 따라 광신호를 재지향시키는 칩 패키지.

### 청구항 6

제5항에 있어서,

상기 광신호는 상기 반도체 다이의 예지 이외의 상기 반도체 다이의 상기 표면상의 위치(a position)에서 상기 반도체 다이에 광학적으로 결합되는 칩 패키지.

### 청구항 7

제1항에 있어서,

상기 반도체 다이들의 세트 내의 한 쌍의 반도체 다이는 상기 램프 컴포넌트를 이용하지 않고 상기 쌍 내의 제1 반도체 다이로부터 상기 쌍 내의 제2 반도체 다이로 상기 광신호를 광학적으로 결합하도록 구성되는 칩 패키지.

### 청구항 8

제1항에 있어서,

상기 램프 컴포넌트는 반도체 이외의 재료 상에 제조되는 칩 패키지.

### 청구항 9

제1항에 있어서,

상기 램프 컴포넌트는 또 다른 반도체 다이인 칩 패키지.

### 청구항 10

제1항에 있어서,

상기 램프 컴포넌트는, 납땜(solder), 미세 스프링들(microsprings) 및 이방성 도전성 필름(anisotropic conductive film) 중 적어도 하나를 이용하여 상기 반도체 다이들의 각각에 결합되는 칩 패키지.

### 청구항 11

칩 패키지를 포함하는 전자 디바이스로서,

상기 칩 패키지는,

수직 방향의 수직 스택으로 배열된 반도체 다이들의 세트 - 상기 반도체 다이들의 세트는 상기 수직 스택 내의 제1 반도체 다이에 수직이고, 상기 제1 반도체 다이 다음의, 각각의 반도체 다이는, 상기 수직 스택 내의 직전 반도체 다이로부터의 오프셋 값만큼 수평 방향으로 오프셋되어, 상기 수직 스택의 일 측에서 계단식 테라스를 규정함 - ; 및

상기 반도체 다이들에 기계적으로 견고하게 결합된 램프 컴포넌트 - 상기 램프 컴포넌트는 상기 수직 스택의 상기 일 측에 배치됨 -

를 포함하고,

상기 램프 컴포넌트는, 상기 수평 방향과 상기 수직 방향 사이에 있는 상기 계단식 테라스를 따르는 방향에 평행하고,

상기 램프 컴포넌트는,

광신호를 전달하도록 구성된 광도파로, 및

상기 반도체 다이들의 세트 내의 반도체 다이(a semiconductor die)에 상기 광신호를 광학적으로 결합하도록 구성된 광 결합 컴포넌트를 포함하고,

각각의 반도체 다이는, 상기 수평 방향에 평행하고 상기 계단식 테라스 상에 있는 상기 반도체 다이의 표면 상

의 램프 패드를 포함하고,

상기 램프 컴포넌트는 상기 램프 패드들 중 대응하는 램프 패드를 사용하여 각각의 반도체 다이에 견고하게 결합되는 전자 디바이스.

### 청구항 12

제11항에 있어서,

상기 램프 컴포넌트는 상기 광 결합 컴포넌트를 포함하는 광 결합 컴포넌트들의 세트를 포함하고,

상기 광 결합 컴포넌트들의 세트 내의 소정의 광 결합 컴포넌트는, 상기 반도체 다이를 포함하는 상기 반도체 다이들의 세트 내의 소정의 반도체 다이에 상기 광신호를 광학적으로 결합하도록 구성되는 전자 디바이스.

### 청구항 13

제11항에 있어서,

상기 광도파로는 상기 계단식 테라스를 따르는 방향으로 상기 광신호를 전달하도록 구성되고,

상기 광 결합 컴포넌트는 상기 반도체 다이의 평면에 상기 광신호를 재지향시키는 전자 디바이스.

### 청구항 14

제13항에 있어서,

상기 광신호는 상기 반도체 다이의 에지를 통해 상기 반도체 다이에 광학적으로 결합되는 전자 디바이스.

### 청구항 15

제11항에 있어서,

상기 광도파로는 상기 계단식 테라스를 따르는 방향으로 상기 광신호를 전달하도록 구성되고,

상기 광 결합 컴포넌트는 상기 반도체 다이의 표면에 법선을 따라 상기 광신호를 재지향시키는 전자 디바이스.

### 청구항 16

제15항에 있어서,

상기 광신호는 상기 반도체 다이의 에지 이외의 상기 반도체 다이의 상기 표면상의 위치에서 상기 반도체 다이에 광학적으로 결합되는 전자 디바이스.

### 청구항 17

제11항에 있어서,

상기 반도체 다이들의 세트 내의 한 쌍의 반도체 다이는, 상기 램프 컴포넌트를 이용하지 않고, 상기 쌍 내의 제1 반도체 다이로부터 상기 쌍 내의 제2 반도체 다이로 상기 광신호를 광학적으로 결합하도록 구성되는 전자 디바이스.

### 청구항 18

제11항에 있어서,

상기 램프 컴포넌트는 반도체 이외의 재료(material) 상에 제조되는 전자 디바이스.

### 청구항 19

제11항에 있어서,

상기 램프 컴포넌트는 또 다른 반도체 다이인 전자 디바이스.

### 청구항 20

광신호를 전달(communicating)하기 위한 방법으로서,

수직 방향의 수직 스택으로 배열되는 반도체 다이들의 세트에 기계적으로 견고하게 결합되는 램프 컴포넌트에 있는 광도파로에서 상기 광신호를 전달하는 단계 - 상기 반도체 다이들은 수평 방향으로 서로 오프셋되어, 상기 수직 스택의 일 측에서 계단식 테라스를 규정하며, 상기 램프 컴포넌트는, 상기 수평 방향과 상기 수직 방향 사이에 있는 상기 계단식 테라스를 따르는 방향에 평행한 상기 수직 스택의 상기 일 측에 배치됨 - ; 및

광 결합 컴포넌트를 이용하여 상기 반도체 다이들의 세트 내의 반도체 다이에 상기 광도파로로부터의 상기 광신호를 광학적으로 결합하는 단계

를 포함하고,

각각의 반도체 다이는, 상기 수평 방향에 평행하고 상기 계단식 테라스 상에 있는 상기 반도체 다이의 표면 상의 땜납 패드를 포함하고,

상기 램프 컴포넌트는 상기 땜납 패드들 중 대응하는 땜납 패드를 사용하여 각각의 반도체 다이에 견고하게 결합되는 광신호 전달 방법.

## 발명의 설명

### 기술 분야

[0001] 본 개시물은 일반적으로 반도체 칩 패키지의 설계에 관한 것이다. 보다 구체적으로, 본 개시물은 스택(stack)으로 배열된 칩들의 그룹, 및 스택에 대하여 비스듬히 있고 반도체 다이들과 광신호들로 통신하는 램프 컴포넌트(ramp component)를 포함하는 반도체 칩 패키지에 관한 것이다.

### 배경 기술

[0002] 적층된 반도체 칩들을 포함하는 칩 패키지들은 인쇄 회로 기판에 접속되는 개별적으로 패키지된 종래의 칩들에 비해 상당히 높은 성능을 제공할 수 있다. 이러한 칩 패키지들은 또한 특정 장점들, 이를테면, 스택에 있는 상이한 칩들에 대해 상이한 프로세스들을 이용하는 능력, 고 밀도로직 및 메모리를 조합하는 능력, 및 적은 전력을 이용하여 데이터를 전송하는 능력을 제공한다. 예를 들어, DRAM(dynamic random access memory)을 구현하는 칩들의 스택은 입/출력(I/O)과 제어기 기능들을 구현하기 위해 기본 칩에서 높은-금속-층-수(high-metal-layer-count), 고-성능 로직 프로세스(high-performance logic process)를 이용할 수 있고, 스택의 나머지를 위해 더 낮은 금속-층-수(lower metal-layer-count), DRAM-전문 처리 칩들(DRAM-specialized processed chips)의 세트가 이용될 수 있다. 이러한 방식에서, 조합된 칩들의 세트는, DRAM 프로세스를 이용하여 제조된 I/O과 제어기 기능들을 포함하는 단일 칩; 로직 프로세스를 이용하여 제조된 메모리 회로들을 포함하는 단일 칩; 또는 로직 및 메모리 물리적 구조물을 모두를 만들기 위해 단일 프로세스를 이용하려는 시도에 의해 구성된 시스템보다 성능이 더 우수하고 비용이 더 저렴하다.

[0003] 그러나, 적층된 반도체 칩들 사이에서 저-비용, 고-성능(예컨대, 고-대역폭) 상호접속들을 얻는 것은 어려울 수 있다. 예를 들어, 반도체 칩들은, 칩들이 칩 에지들의 계단(staircase)을 정의하기 위해 서로 오프셋 되는 칩들의 스택에서 표면들 상의 노출된 본드 패드들 사이에 와이어 본드들을 이용하여 전기적으로 결합될 수 있다. 그러나, 이러한 와이어 본드들은 저-비용 조립 기술들을 이용하여 구현될 수 있는 한편, 결과적으로 와이어 본드들은 일반적으로 저 대역폭을 갖는다.

[0004] 반면, TSV들(Through-Silicon Vias)은 일반적으로 와이어 본드들보다 고 대역폭을 갖는다. TSV 제조(fabrication) 기술에서, 칩들은, 그들의 액티브 페이스(active face) 상의 금속 층들 중 하나 이상이 그들의 백 페이스(back face) 상의 새로운 패드들에 도전적으로(conductively) 접속되도록 처리된다. 그 다음, 칩들이 스택에서 접착적으로(adhesively) 접속되어, 하나의 칩의 백 페이스 상의 새로운 패드들은 인접한 칩의 액티브 페이스 상의 대응하는 패드들과 도전적 콘택트를 만든다.

[0005] 하지만, TSV들은 일반적으로 와이어 본드들보다 더 비싸다. 이는, TSV들이 칩의 액티브 실리콘층을 관통하기 때문이다. 그 결과, TSV는 트랜지스터들 또는 배선을 위해 이용될 수 있는 구역(area)을 차지한다. 이러한 기회 비용은 클 수 있다. 예를 들어, TSV 배제(exclusion) 또는 차단(keep-out) 직경이  $20\mu\text{m}$ 이고, TSV들이  $30\mu\text{m}$  피치로 놓이는 경우, 실리콘 구역의 거의 45%가 TSV들에 의해 점유된다(consumed). 이는 스택에 있는 칩들에서 임의의 회로들에 대한 면적당 비용을 대략 두 배로 증가시킨다. (사실, 회로들은 일반적으로 TSV들을 수용하기

위해 넓은 공간을 차지하기 때문에 오버헤드가 훨씬 더 클 가능성이 있고, 이는 더 많은 구역을 낭비한다.) 또한, TSV 제조는 보통 추가의 처리 동작들을 수반하고, 이는 또한 비용을 증가시킨다.

[0006] 따라서, 위에서 설명한 문제들 없이 적층된 칩들의 장점들을 제공하는 칩 패키지가 필요하다.

### 발명의 내용

[0007] 본 개시물의 하나의 실시예는 칩 패키지를 제공한다. 이러한 칩 패키지는 수직 방향의 수직 스택으로 배열되는 반도체 다이들의 세트를 포함하고, 이는 수직 스택에 있는 제1 반도체 다이에 실질적으로 수직이다. 또한, 제1 반도체 다이 이후의, 각각의 반도체 다이는 수직 스택에 있는 직전(immediately preceding) 반도체 다이로부터의 오프셋 값에 의해 수평 방향으로 오프셋되어, 수직 스택의 일 측에서 계단식 테라스(stepped terrace)를 규정한다. 또한, 칩 패키지에서 램프 컴포넌트가 반도체 다이들에게 기계적으로 견고하게 결합된다. 이러한 램프 컴포넌트는 수직 스택의 일 측에 배치되고, 계단식 테라스를 따르는 방향에 거의 평행한데, 이는 수평 방향과 수직 방향 사이에 있다. 또한, 램프 컴포넌트는: 광신호를 전달하는 광도파로(optical waveguide), 및 반도체 다이들의 세트에서 한 반도체 다이(a semiconductor die)에 광신호를 광학적으로 결합하는 광 결합 컴포넌트(optical coupling component)를 포함한다.

[0008] 일부 실시예들에서, 램프 컴포넌트는 광 결합 컴포넌트를 포함하는 광 결합 컴포넌트들의 세트를 포함한다. 또한, 광 결합 컴포넌트들의 세트에서 소정의(given) 광 결합 컴포넌트는 반도체 다이들의 세트에서 소정의(given) 반도체 다이에 광신호를 광학적으로 결합할 수 있는데, 이는 반도체 다이를 포함한다.

[0009] 광도파로는 계단식 테라스를 따르는 방향으로 광신호를 전달할 수 있다는 것에 주목한다. 또한, 광 결합 컴포넌트는 반도체 다이의 한 평면(a plane)으로 광신호를 재지향(redirect)할 수 있다. 예를 들어, 광신호는 반도체 다이의 에지를 통해 반도체 다이에 광학적으로 결합될 수 있다. 대안적으로, 광 결합 컴포넌트는 램프 컴포넌트의 표면에 법선(normal)을 따라 광신호를 재지향할 수 있다. 따라서, 광신호는 반도체 다이의 에지 외에 반도체 다이의 표면상의 한 위치(a position)에서 반도체 다이에 광학적으로 결합될 수 있다.

[0010] 또한, 반도체 다이들의 세트에서 한 쌍의 반도체 다이는, 램프 컴포넌트를 이용하지 않고, 상기 쌍에서의 제1 반도체 다이로부터 상기 쌍에서의 제2 반도체 다이로 광신호를 광학적으로 결합할 수 있다.

[0011] 일부 실시예들에서, 램프 컴포넌트는 반도체 이외의 재료 상에 제조된다. 또한, 램프 컴포넌트는 또 다른 반도체 다이일 수 있다.

[0012] 일부 실시예들에서, 램프 컴포넌트는: 납땜(solder), 미세 스프링들(microsprings) 및/또는 이방성 도전성 필름(anisotropic conductive film) 중 적어도 하나를 이용하여 반도체 다이를 각각에 결합된다.

[0013] 또 다른 실시예는 칩 패키지를 포함하는 전자 디바이스(이를테면, 컴퓨터 시스템)를 제공한다.

[0014] 또 다른 실시예는 광신호로 통신(communicate)하기 위한 방법을 제공한다. 이러한 방법 동안, 광신호는 수직 방향의 수직 스택으로 배열되는 반도체 다이들의 세트에 기계적으로 견고하게 결합되는 램프 컴포넌트에 있는 광도파로에서 전달된다. 반도체 다이들은 수평 방향에서 서로 오프셋되어, 수직 스택의 일 측에서 계단식 테라스를 규정한다는 것에 주목한다. 또한, 램프 컴포넌트는 계단식 테라스를 따르는 방향에 거의 평행한 수직 스택의 일 측에 배치되는데, 이는 수평 방향과 수직 방향 사이에 있다. 그 다음, 광신호는, 광 결합 컴포넌트를 이용하여, 반도체 다이들의 세트에서 한 반도체 다이에 광학적으로 결합된다.

### 도면의 간단한 설명

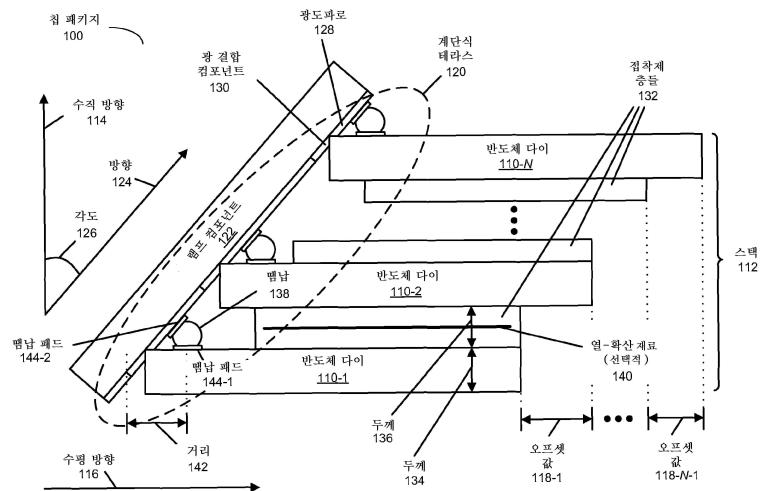

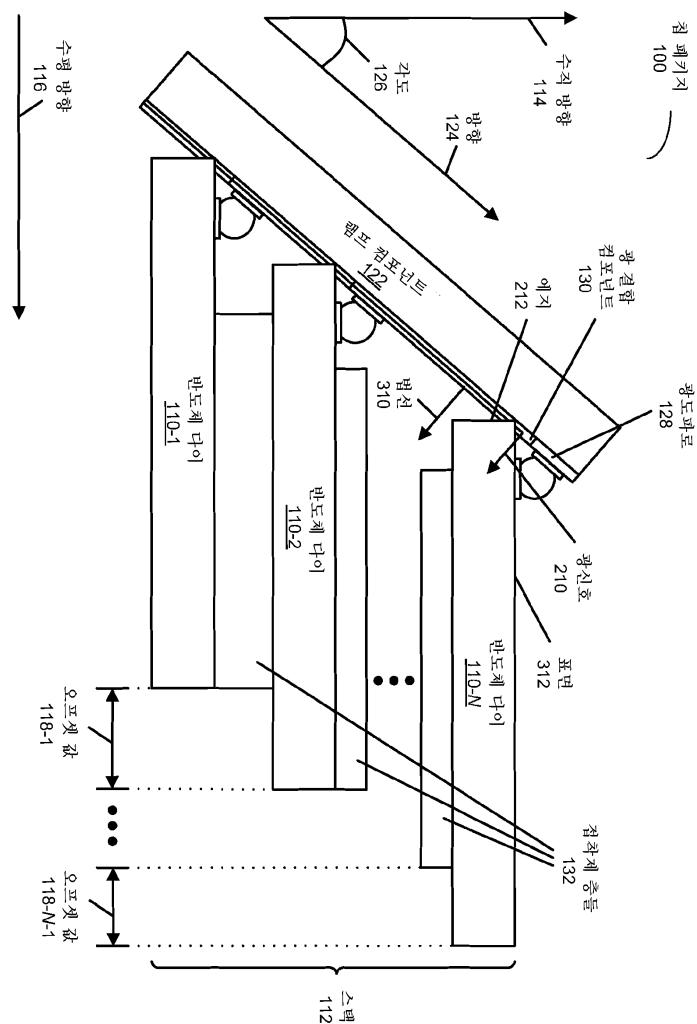

[0015] 도 1은 본 개시물의 일 실시예에 따른 칩 패키지의 측면도를 도시하는 블록도이다.

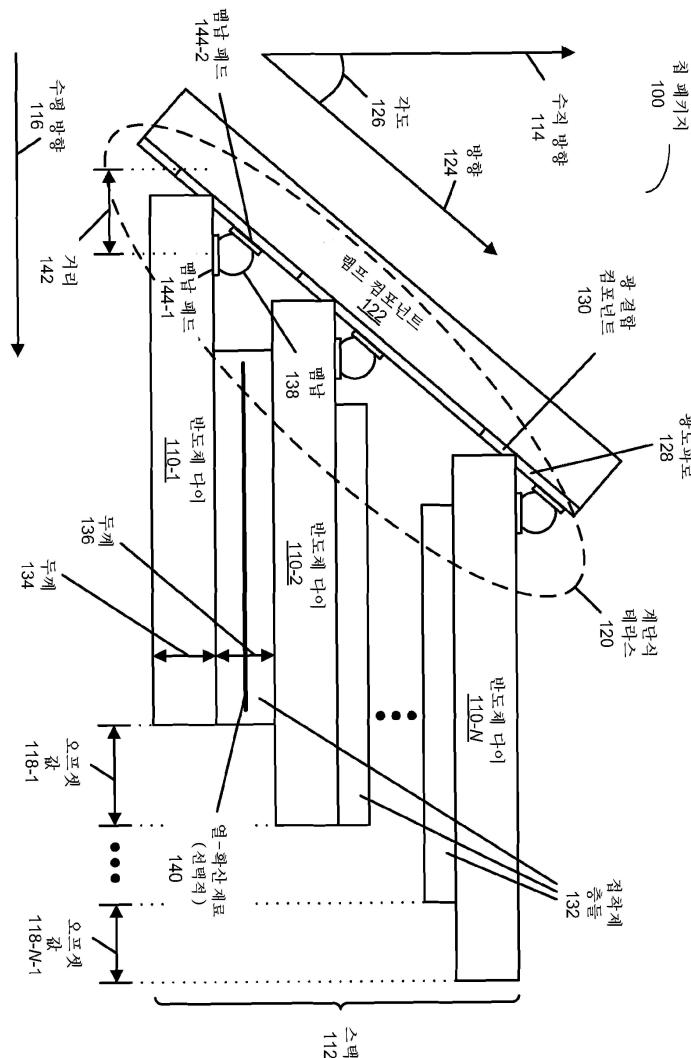

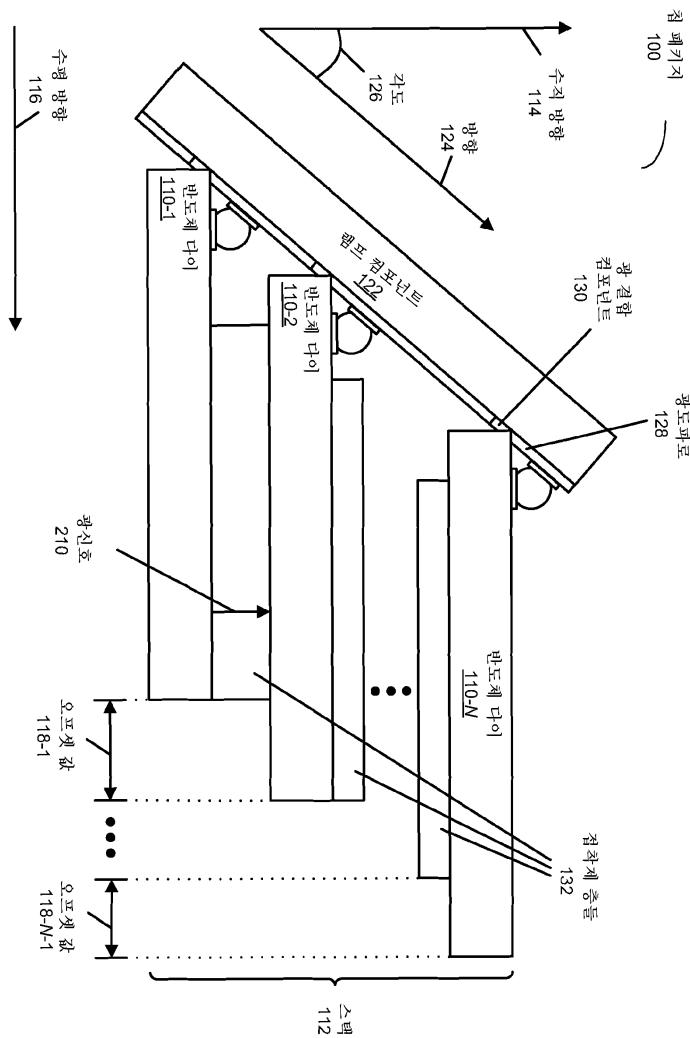

도 2는 본 개시물의 일 실시예에 따른 도 1에서의 칩 패키지의 측면도를 도시하는 블록도이다.

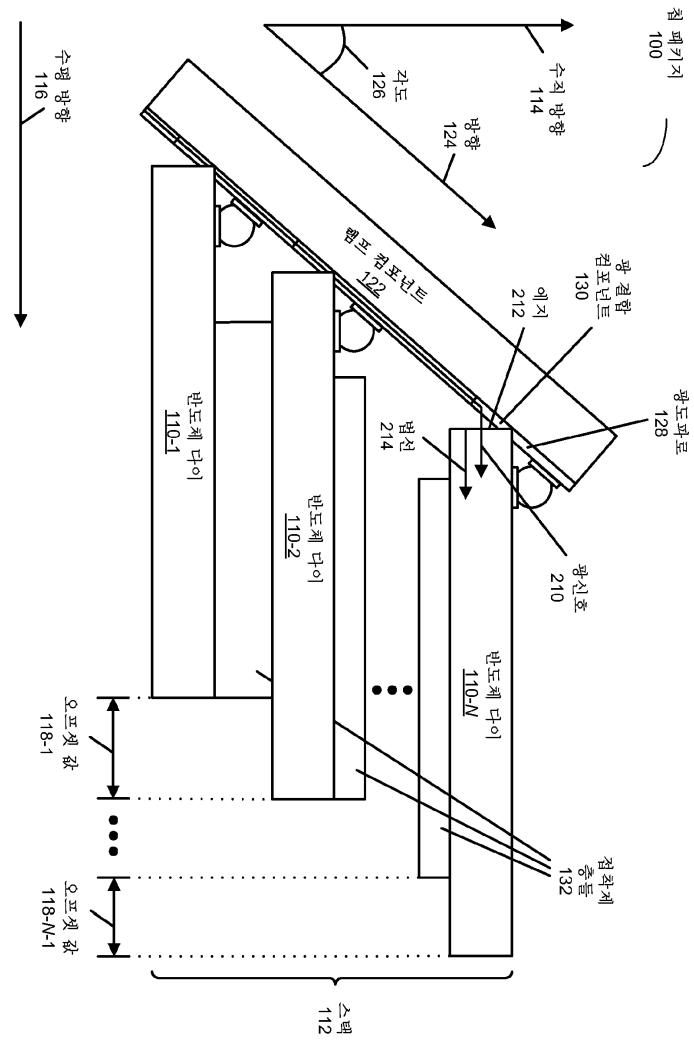

도 3은 본 개시물의 일 실시예에 따른 도 1에서의 칩 패키지의 측면도를 도시하는 블록도이다.

도 4는 본 개시물의 일 실시예에 따른 도 1에서의 칩 패키지의 측면도를 도시하는 블록도이다.

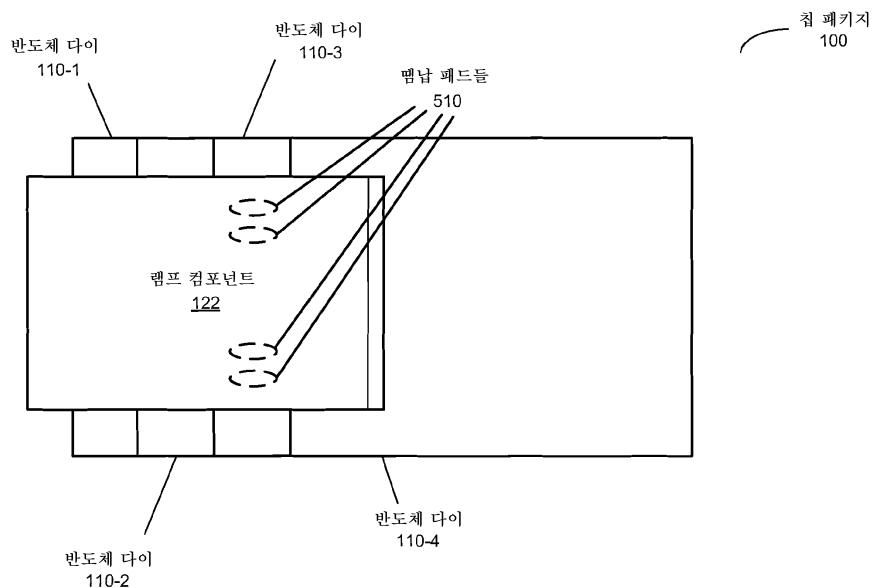

도 5는 본 개시물의 일 실시예에 따른 도 1에서의 칩 패키지의 상면도를 도시하는 블록도이다.

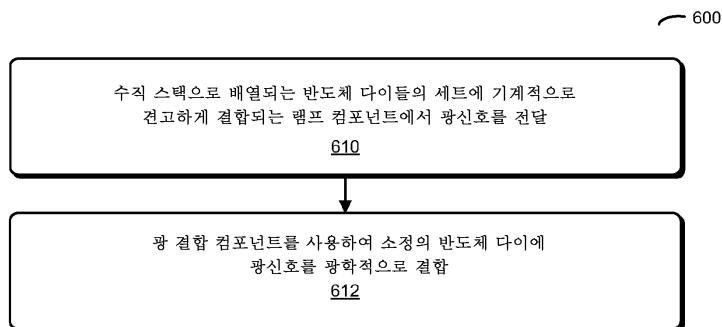

도 6은 본 개시물의 일 실시예에 따른 칩 패키지에서 광신호로 통신하기 위한 방법을 도시하는 순서도이다.

도 7은 본 개시물의 일 실시예에 따른 칩 패키지를 포함하는 전자 디바이스를 도시하는 블록도이다.

같은 참조 부호들은 도면들 전체에 걸쳐 대응하는 부분들을 지칭한다는 것에 주목한다. 또한, 동일한 부분에 대한 다수의 사례들(instances)은 대시(dash)에 의해 사례 번호(instance number)로부터 분리된 공통 접두사에 의해 명시된다.

### 발명을 실시하기 위한 구체적인 내용

[0016]

칩 패키지, 칩 패키지를 포함하는 전자 디바이스, 및 칩 패키지에서 광신호로 통신하기 위한 방법에 대한 실시 예들이 설명된다. 이러한 칩 패키지는 수평 방향에서 서로 오프셋되는 반도체 다이들 또는 칩들의 수직 스택을 포함하여, 계단식 테라스(stepped terrace)를 규정한다. 계단식 테라스에 거의 평행하게 배치되는 고-대역폭 램프 컴포넌트는 반도체 다이들에 기계적으로 결합된다. 또한, 램프 컴포넌트는 광신호를 전달하는 광도파로, 및 반도체 다이들 중 하나에 광신호를 광학적으로 결합하는 광 결합 컴포넌트를 포함하여, 반도체 다이와 램프 컴포넌트 사이에서 광신호의 고-대역폭 통신을 용이하게(facilitating) 한다.

[0017]

반도체 다이들에서 비용이 많이 들고 구역을 점유하는(area-consuming) TSV들(through-silicon vias)에 대한 필요성을 제거함으로써, 칩 패키지는 고 대역폭 및 저 비용을 제공할 수 있다. 예를 들어, 반도체 다이들에서 TSV들과 관련된 처리 동작들 및 낭비되는 구역을 포함으로써 비용이 감소될 수 있다. 따라서, 스택에 있는 칩들은 표준 처리 기술들을 이용하여 제조될 수 있다. 또한, 땜납, 미세 스프링들 및/또는 이방성 필름은 비용이 더 저렴할 수 있고 및/또는 와이어 본딩보다 개선된 신뢰도를 제공할 수 있다. 또한, 램프 컴포넌트는 와이어 본딩보다 더 높은 컴포넌트간 통신 대역폭 및 감소된 대기시간(latency)을 제공할 수 있고, TSV들을 포함하는 반도체 다이들에 의해 제공되는 것과 유사한(comparable) 통신 대역폭 및 대기시간을 가질 수 있다.

[0018]

이제 칩 패키지의 실시예들을 설명한다. 도 1은 칩 패키지(100)의 측면도를 도시하는 블록도를 제시한다. 이러한 칩 패키지(때로는 '램프-스택 칩 패키지(ramp-stack chip package)'로 지칭됨)에서, 반도체 다이들의 세트(110)는 수직 방향(114)의 스택(112)으로 배열된다. 수직 방향(114)은 스택(112)에서 반도체 다이(110-1)에 실질적으로 수직(및, 따라서, 반도체 다이(110-1)의 한 평면에서 수평 방향(116)에 실질적으로 수직)이라는 것에 주목한다. 또한, 반도체 다이(110-1) 이후의, 각각의 반도체 다이는 스택(112)에서 직전 반도체 다이로부터의 오프셋 값들(118) 중 관련된 것에 의해 수평 방향(116)으로 오프셋될 수 있어, 스택(112)의 일 측에서 계단식 테라스(120)를 규정한다. 이러한 오프셋 값들은 반도체 다이들의 세트(110)에 대해 거의 일정한 값을 가질 수 있고 또는 반도체 다이들의 세트(110)에 따라 다를 수 있다(즉, 계단식 테라스(120)에서 상이한 계단들에 대한 오프셋 값들이 서로 다를 수 있다).

[0019]

또한, 고-대역폭 램프 컴포넌트(122)는 반도체 다이들(110)에 기계적으로 견고하게 결합된다. 예를 들어, 반도체 다이들(110)에 견고한 기계적 및/또는 전기적 결합(이를테면, 반도체 다이들(110)에 전기 신호들을 결합하고/하거나 전력을 공급하는 등)은, 땜납 볼(solder ball; 138)과 같은 땜납 볼들을 통해 발생할 수 있다. 이러한 램프 컴포넌트(122)는 스택(112)의 일 측 상에 배치되고, 계단식 테라스(120)를 따르는 방향(124)에 (각도(126)에서) 거의 평행한데, 이는 수평 방향(116)과 수직 방향(114) 사이에 있다.

[0020]

또한, 램프 컴포넌트(122)는 방향(124)을 따라 광신호를 전달하는 광도파로(128)를 포함할 수 있고, (광 결합 컴포넌트(130)와 같은) 광 결합 컴포넌트들의 세트는 반도체 다이들(110)로 및/또는 그로부터 광신호를 광학적으로 결합할 수 있어, 반도체 다이들(110)로 및/또는 그로부터 하나 이상의 광신호들의 통신을 용이하게 한다. 소정의 광 결합 컴포넌트는 소정의 반도체 다이로 및/또는 그로부터 광신호를 광학적으로 결합한다는 것에 주목한다(따라서, 광 결합 컴포넌트(130)는 반도체 다이(110-N)로 및/또는 그로부터 광신호를 광학적으로 결합할 수 있다). 또한, 이러한 광 결합 컴포넌트들은: 회절 격자(diffraction grating), 경사진 반사기(angled reflector)나 거울(mirror), 빔 스플리터 및/또는 렌즈를 포함할 수 있다. 더 후술하는 바와 같이, 일부 실시 예들에서, 반도체 다이들(110)로 및/또는 그로부터 광신호로 통신하는 것은 광학적으로 결합된 신호의 광 근접 통신(optical proximity communication)을 수반할 수 있다(이는 고-대역폭 및 저-대기시간 통신을 제공할 수 있다). 또한, 도 1은 램프 컴포넌트(122)에서 V-형상 그루브들(V-shaped grooves)에 배치된 반도체 다이들(110)을 도시하는 반면, 다른 실시예들에서는 램프 컴포넌트(122)에 그러한 그루브들이 존재하지 않을 수 있다(예를 들어, 반도체 다이들(110)과 램프 컴포넌트(122) 사이에 캡이 존재할 수 있다)는 것에 주목한다.

[0021]

스택(112)에서 반도체 다이들(110)은, 150°C에서 10s 안에 경화(cure)하는 에폭시나 글루와 같은, 접착제 층들(adhesive layers)(132)에 의해 서로 기계적으로 결합될 수 있다. 또한, 반도체 다이들(110)의 세트에서 소정의 반도체 다이는 공칭 두께(nominal thickness)(134)를 가질 수 있고, 접착제 층들(132)은 공칭 두께(136)를 가질 수 있다. 그러나, 일부 실시예들에서, 스택(112)에 있는 반도체 다이들(110) 및/또는 접착제 층들(132)의

적어도 일부의 두께가 상이할 수도 있다는 것에 주목한다(예를 들어, 반도체 다이들(110) 및 접착제 층들(132) 중 어느 하나 또는 둘 다의 두께는 수직 방향(114)을 따라 상이할 수 있다).

[0022] 예시적인 실시예에서, 공칭 두께(134)는  $150 \pm 5 \mu\text{m}$ 이다. (그러나, 다른 실시예들에서, 두께(134)는 30과  $250 \mu\text{m}$  사이일 수 있다.) 50과  $100 \mu\text{m}$  사이의 공칭 두께(134)에 대해, 각도(126)는  $15$ 와  $20^\circ$  사이일 수 있다는 것에 주목한다. 일반적으로, 공칭 두께(134)는 스택(112)에 있는 반도체 다이들(110)의 수에 부분적으로 의존한다. 또한, 접착제 층들(132)의 공칭 두께(136)는 최대  $600 \mu\text{m}$ 일 수 있다는 것에 주목한다. (그러나, 다른 실시예들에서, 두께(136)는  $10 \mu\text{m}$ 만큼 작을 수 있다.)

[0023] 또한, 오프셋 값들(118)은 반도체 다이들(110)의 세트에 램프 컴포넌트(122)를 기계적으로 견고하게 결합하는데 이용된 뱀납(이를테면, 뱀납 볼(138))의 공칭 두께 및 방향(124)(또는 각도(126))에 기초하여 결정될 수 있다. 뱀납의 두께는 스택(112)에 걸쳐 거의 일정할 수 있고 또는 스택에 걸쳐(즉, 수직 방향(114)을 따라) 다를 수 있다는 것에 주목한다.

[0024] 일부 실시예들에서, 수직 방향(114)의 반도체 다이들의 세트(110)에 걸쳐 축적된 위치 오류(즉, 스택(112)에 걸쳐 반도체 다이들의 수직 위치들에서 축적된 위치 오류)는 반도체 다이들(110)의 세트 및 반도체 다이들(110) 사이의 접착제 층들(132)과 관련된 수직 오류들의 합계보다 적다. 예를 들어, 축적된 위치 오류는: 반도체 다이들(110)의 두께 편차(thickness variation), 접착제 층들(132)의 두께 편차, 및/또는 접착제 층들(132) 중 적어도 일부에서 선택적 열-확산 재료(optional heat-spreading material; 140)(이를테면, 압착된 흑연 섬유들(pressed graphite fibers))의 두께 편차와 관련될 수 있다. 일부 실시예들에서, 축적된 위치 오류는  $1 \mu\text{m}$ 보다 적을 수 있고,  $0 \mu\text{m}$ 만큼 작을 수 있다. 또한, 반도체 다이들의 세트(110)는, 미리 정의된 값보다 적은(예를 들어, 최대 위치 오류가  $1 \mu\text{m}$ 보다 적을 수 있고,  $0 \mu\text{m}$ 만큼 작을 수 있음), 반도체 다이들(110)의 에지 편차(이를테면, 톱-라인 위치(saw-line position)에서 편차)와 관련되는, 평면에서의 최대 위치 오류(즉, 거리(142)에서의 최대 오류)를 가질 수 있다. 이는, 반도체 다이들(110) 상의 광학적 정렬 마커들(이를테면, 기점 마커들(fiducial markers))을 이용하는 칩 패키지(100)를 조립하기 위해 꽂-앤플레이스 툴(pick-and-place tool)을 이용하여 달성될 수 있고, 거리(142)는 반도체 다이들(110)에 대한 톱 레인(saw lane)의 중심에 대해 측정된다. 또한, 조립 동안, 반도체 다이들(110)은 (스택(112)에서 반도체 다이(110-1) 이후의 각각의 반도체 다이가 그의 직전 반도체 다이를 참조하는 대신) 계단식 테라스(120)를 미러링하는 계단식 테라스를 포함하는 조립 컴포넌트 또는 꾹스처(fixture)를 참조할 수 있다.

[0025] 수직 방향(114)에서 기계적 정렬 오류들을 수용하기 위해, 뱀납 범프들이나 패드들(이를테면, 뱀납 패드(144-1) 및/또는 뱀납 패드(144-2)) 및/또는 뱀납 볼들(138)의 높이 및 피치는 수직 방향(114)을 따라 반도체 다이들(110)의 적어도 일부 사이에서 다를 수 있다는 것에 주목한다. 거리(142)(즉, 반도체 다이(110-1)에 대한 톱 레인(saw lane)의 중심에 대한 뱀납 패드(144-1)의 위치)는  $60 \mu\text{m}$ 일 수 있고, 뱀납 패드들(144)은 각각  $80 \mu\text{m}$  폭을 가질 수 있다는 것에 주목한다. 또한, 뱀납 볼들(이를테면, 뱀납 볼(138))은 리플로 납땜(reflowing)이나 용융(melting) 이전에  $120 \mu\text{m}$ 의 직경을 가질 수 있고, 용융 후에 대략 40과  $60 \mu\text{m}$  사이의 두께를 가질 수 있다. 일부 실시예들에서, 뱀납 볼들의 두 개 이상의 행(row)은 소정의 반도체 다이에 램프 컴포넌트(122)를 견고하게 결합할 수 있다.

[0026] 도 2는 칩 패키지(100)의 측면도를 도시한 블록도를 제시한다. 이러한 예에서, 광신호(210)는 소정의 반도체 다이의 에지(212)를 통해 소정의 반도체 다이(이를테면, 반도체 다이(110-N))에 광학적으로 결합된다(즉, 소정의 반도체 다이의 에지(212)에 수직이고 법선(214)에 평행). 전술한 바와 같이, 일부 실시예들에서, 광신호(210)의 광 결합은 램프 컴포넌트(122)와 소정의 반도체 다이 사이의 광 근접 통신을 수반한다. 또한, 일부 실시예들에서, 광 결합은, 소정의 반도체 다이가 그의 페어런트 웨이퍼(parent wafer)로부터 절단된 후에 에지(212)를 연마(polishing)함으로써 용이하게 된다. 이러한 연마는, 에지(212)의 거칠기가 광신호(210)의 캐리어 파장보다 적도록 보장할 수 있다.

[0027] 일부 실시예들에서, 에지(212)의 연마는, 에지(212)와 관련된 것 이외의 소정의 반도체 다이의 표면을 통해 광신호(210)를 광학적으로 결합함으로써 피할 수 있다. 이는 도 3에 도시되고, 칩 패키지(100)의 측면도를 도시하는 블록도를 제시한다. 특히, 광 결합 컴포넌트(130)는 램프 컴포넌트(122)의 표면에 대한 법선(310)을 따라 광신호(210)를 재지향할 수 있다. 그 다음, 광신호(210)는 (에지(212) 대신) 표면(312)을 통해 소정의 반도체 다이에 들어갈 수 있다. 따라서, 광신호(210)는, 거칠기가 더 작고 광 산란 또는 순실을 줄일 수 있는, 톱 라인(saw line)과 관련되지 않은 표면을 통해 소정의 반도체 다이에 들어갈 수 있다.

[0028] 전술한 실시예들은 광 및/또는 전기 신호들을 반도체 다이들(110)로 및/또는 그로부터 결합하는 램프 컴포넌트

(122)의 이용을 도시하는데 반면, 다른 실시예들에서는, 램프 컴포넌트(122)를 통한 반도체 다이들(110) 사이의 간접 통신과는 대조적으로, 반도체 다이들(110) 사이의 직접 통신(즉, 직접 스택-간 통신(direct intra-stack communication))이 존재할 수 있다. 이는 도 4에 도시되고, 칩 패키지(100)의 측면도를 도시한 블록도를 제시한다. 특히, 광신호(210)는 램프 컴포넌트(122)의 이용 없이 반도체 다이들(110)에서 한 쌍의 반도체 다이(이를테면, 반도체 다이(110-1 및 110-2)) 사이에서 직접적이고 광학적이다. 이러한 직접 통신(또는 램프 컴포넌트(122)와의 통신)을 용이하게 하기 위해, 하나 이상의 반도체 다이들(110)은: 광도파로, 광 결합 컴포넌트(이는 광신호(210)의 전파 방향을 리라우트(reroute) 또는 변경할 수 있음) 및/또는 광원을 포함할 수 있다는 것에 주목한다. 또한, 직접 스택-간 통신은 광신호(210)의 라우팅을 수행하는 하나 이상의 반도체 다이(110)에 의해 가능해 질 수 있다는 것에 주목한다. 일부 실시예들에서, 직접 스택-간 통신은 하나 이상의 반도체 다이(110)에 있는 TSV들 및/또는 이러한 TSV들을 둘러싸는 접착제 층들에 있는 개구들(openings)에 의해 가능해진다.

[0029] 도 5는, 스택(112)(도 1)이 4개의 반도체 다이(110)를 포함하는 칩 패키지(100)의 상면도를 예시하는 블록도를 제시한다. 칩 패키지(100)의 이러한 뷰는, 일부 실시예들에서, 뼈납 패드들(510)이 직사각형 형상이 아닐 수 있다는 것을 예시한다. 예를 들어, 뼈납 패드들(510)은, 이를테면, 폭  $80\mu\text{m}$  및 길이  $120\mu\text{m}$ 의 타원형(oblong shapes)일 수 있다. 반도체 다이들(110) 및/또는 램프 컴포넌트(122) 상의 이러한 뼈납-패드 형상들은 일부 수평 및/또는 수직 위치 오류들을 용인할 수 있다.

[0030] 일부 실시예들에서, 뼈납 패드들은 램프 컴포넌트(122)의 에지로 이동될 수 있다. 이는 수직 배향을 용이하게 할 수 있다(즉, 도 1에서 각도(126)는  $0^\circ$  일 수 있음). 이러한 구성은, 입/출력(I/O) 신호 라인들 및 전력 라인들과 관련된 콘택트들이나 패드들이 ('스파인(spine)' 아래 대신) 램프 컴포넌트의 에지에 있는 메모리 모듈을 용이하게 할 수 있다. 이러한 방식에서, 램프 컴포넌트에서 확산 층들의 수는 감소될 수 있다. 예를 들어, 이러한 메모리 모듈에서 램프 컴포넌트(122)의 에지를 따라 60개의 콘택트들이나 패드들이 존재할 수 있다.

[0031] 다시 도 1을 참조하면, 전술한 설명에서는 램프 컴포넌트(122)와 반도체 다이들(110) 사이에서 또는 반도체 다이들(110) 사이에서 하나 이상의 광신호로 통신하는 것을 예시한 한편, 다른 실시예들에서는, 또한 하나 이상의 전기 신호로 통신된다. 예를 들어, 램프 컴포넌트(122)는 전기 신호를 전달하는 신호 라인을 포함할 수 있다. 이러한 실시예들에서, 램프 컴포넌트(122)는: 뼈납, 미세 스프링들, 마이크로-스피어들(micro-spheres)(볼-인-핏 구성(ball-in-pit configuration)으로), 및/또는 이방성 도전성 필름(이를테면, 때때로 '이방성 도전성 필름'으로 지칭되는, 이방성 탄성중합체(elastomer) 필름)을 포함하는 다양한 기술을 이용하여 반도체 다이들(110)에 전기적으로 및/또는 기계적으로 결합될 수 있다. 반도체 다이들(110)로 및/또는 그로부터의 전기 신호로의 이러한 통신은, 램프 컴포넌트(122) 및 반도체 다이들(110)의 위(on) 또는 근처(near)의 PxC 커넥터들(도시되지 않음)을 통해, 용량성으로 결합된 신호의 용량성으로 결합된 근접 통신(이는 고-대역폭 및 저-대기시간 통신(low-latency communication)을 제공할 수 있음)과 같은 근접 통신(PxC)을 수반할 수 있다.

[0032] 따라서, 일부 실시예들에서, 램프 컴포넌트(122)와 반도체 다이들(110) 사이(및, 더 일반적으로, 칩 패키지에서 컴포넌트들 사이 또는 칩 패키지와 외부 디바이스 사이)의 통신은: 용량성으로 결합된 신호들의 통신(이는 '전기 근접 통신'으로 지칭됨), 전자기적으로 결합된 신호들의 통신(이는 '전자기 근접 통신'으로 지칭됨), 유도적으로(inductively) 결합된 신호들의 통신, 및/또는 용량성으로 결합된 신호들의 통신과 같은, 전자기적으로 결합된 신호들의 PxC를 수반할 수 있다.

[0033] PxC를 이용하여 전기 신호로 통신되는 실시예들에서, 결과로 얻은 전기 콘택트들의 임피던스는, 일반적으로, 도전성 및/또는 용량성일 수 있는데, 즉, 동상 컴포넌트(in-phase component) 및/또는 이상 컴포넌트(out-of-phase component)를 포함하는 복잡한 임피던스를 가질 수 있다. 전기적 콘택트 메커니즘(이를테면, 뼈납, 미세 스프링들, 이방성 층 등)과 무관하게, 콘택트들과 관련된 임피던스가 도전성인 경우, 종래의 송신 및 수신 I/O 회로들은 칩 패키지의 실시예들에 있는 컴포넌트들에서 이용될 수 있다. 그러나, 복잡한(및, 아마도, 가변적인) 임피던스를 갖는 콘택트들에 대해, 송신 및 수신 I/O 회로들은, 2009년 4월 17일에 출원된, Robert J. Drost 등에 의한, 발명의 명칭이 "Receive Circuit for Connectors with Variable Complex Impedance"이며, 그 내용이 여기에 참고로 포함되는, 미국 특허 출원 12/425,871에 기술된 하나 이상의 실시예들을 포함할 수 있다.

[0034] 이제 상기 방법의 실시예들을 설명한다. 도 6은 칩 패키지의 전술한 실시예들 중 하나에서 광신호로 통신하기 위한 방법(600)을 도시하는 순서도를 제시한다. 이러한 방법 동안, 광신호는 수직 방향의 수직 스택으로 배열되는 반도체 다이들의 세트에 기계적으로 견고하게 결합되는 램프 컴포넌트에 있는 광도파로에서 전달된다(동작 610). 반도체 다이들은 수평 방향에서 서로 오프셋되어, 수직 스택의 일 측에서 계단식 테라스를 규정한다는

것에 주목한다. 또한, 램프 컴포넌트는, 계단식 테라스를 따르는 방향에 거의 평행한 수직 스택의 일 측에 배치되는데, 이는 수평 방향과 수직 방향 사이이다. 그 다음, 광신호는, 광 결합 컴포넌트를 이용하여, 반도체 다이들의 세트에서 한 반도체 다이에 광학적으로 결합된다(동작 612).

[0035] 방법(600)의 일부 실시예들에서, 추가의 또는 더 적은 동작들이 존재할 수 있다. 또한, 동작들의 순서는 변경될 수 있고 및/또는 두 개 이상의 동작이 단일 동작으로 조합될 수 있다.

[0036] 이제 전자 디바이스의 실시예들을 설명한다. 도 7은 칩 패키지(710)(이는 칩 패키지의 전술한 실시예들 중 하나일 수 있음)를 포함하는 전자 디바이스(700)를 도시하는 블록도를 제시한다.

[0037] 예시적인 실시예에서, 칩 패키지(이를테면, 칩 패키지의 전술한 실시예들 중 하나)는 고-성능 디바이스들을 용이하게 할 수 있다. 예를 들어, 일부 실시예들에서, 램프-스택 칩 패키지는 듀얼 인-라인(dual in-line) 메모리 모듈에 포함된다. 예를 들어, 램프-스택 칩 패키지에는 80개의 메모리 디바이스(이를테면, 동적 랜덤 액세스 메모리 또는 또 다른 유형의 메모리-저장 디바이스)까지 존재할 수 있다. 필요한 경우, '불량한(bad)' 또는 결함(faulty) 메모리 디바이스들은 디스에이블될 수 있다. 따라서, (80개 중에서) 72개의 메모리 디바이스들이 이용될 수 있다. 또한, 이러한 구성은 메모리 모듈에서 메모리 디바이스들의 전체 대역폭을 노출할 수 있어, 메모리 디바이스들 중 임의의 것에 액세스하는데 대기시간 지연(latency delay)이 거의 또는 전혀 없다.

[0038] 대안적으로, 듀얼 인-라인 메모리 모듈은, 필드 각각이 램프-스택 칩 패키지를 포함할 수 있는 다수의 필드를 포함할 수 있다. 예를 들어, 듀얼 인-라인 메모리 모듈에 네 개의 램프-스택 칩 패키지(각각은 9개의 메모리 디바이스들 포함함)가 존재할 수 있다.

[0039] 일부 실시예들에서, 이들 듀얼 인-라인 메모리 모듈(이는 하나 이상의 램프-스택 칩 패키지를 포함할 수 있음) 중 하나 이상은 프로세서에 결합될 수 있다. 예를 들어, 프로세서는 용량성으로 결합된 신호들의 용량성 근접 통신을 이용하여 하나 이상의 듀얼 인-라인 메모리 모듈에 결합될 수 있다. 그 다음, 프로세서는 C4 땜납 볼들을 이용하여 기판에 장착될 수 있다.

[0040] 따라서, 전자 디바이스(700)는: VLSI 회로, 스위치, 허브, 브리지, 라우터, 통신 시스템, SAN(storage area network), 데이터 센터, 네트워크(이를테면, LAN(local area network)), 및/또는 컴퓨터 시스템(이를테면, 디중-코어 프로세서 컴퓨터 시스템)과 같은, 디바이스 또는 시스템을 포함할 수 있다. 또한, 컴퓨터 시스템은: 서버(이를테면, 멀티-소켓, 멀티-액 서버), 랩톱 컴퓨터, 통신 디바이스나 시스템, 개인용 컴퓨터, 워크 스테이션, 메인프레임 컴퓨터, 블레이드(blade), 기업 컴퓨터, 데이터 센터, 휴대용-컴퓨팅 디바이스, 슈퍼컴퓨터, NAS(network-attached-storage) 시스템, SAN 시스템, 및/또는 또 다른 전자 컴퓨팅 디바이스를 포함할 수 있지만, 이에 한정되지 않는다. 소정의 컴퓨터 시스템은 하나의 위치에 있을 수 있고, 또는 다수의 지리적으로 분산된 위치들에 걸쳐 분포될 수 있다는 것에 주목한다.

[0041] 칩 패키지들(100)(도 1-5) 뿐만 아니라, 전자 디바이스(700)는 더 적은 컴포넌트들 또는 추가의 컴포넌트들을 포함할 수 있다. 예를 들어, 이를테면 램프 컴포넌트 상에 하나 이상의 반도체 다이를 위한 땜납 패드들을 포함하지 않음으로써, 램프-스택 칩 패키지에서 반도체 다이들의 스택에서 규정되는 브레이크들이 존재할 수 있다. 또한, 칩 패키지의 일 실시예에서 하나 이상의 컴포넌트는: 광 변조기, 광 멀티플렉서(이를테면, 가산 필터(add filter)), 광 디-멀티플렉서(이를테면, 드롭 필터(drop filter)), 광 필터 및/또는 광 스위치를 포함할 수 있다.

[0042] 또한, 이러한 디바이스들 및 시스템들은 별개의 항목들의 번호를 갖는 것으로 설명되지만, 이러한 실시예들은, 여기에 설명된 실시예들의 구조적 도식보다는 오히려 제시될 수 있는 다양한 특징들에 대한 기능적 설명을 위한 것이다. 결과적으로, 이러한 실시예들에서, 두 개 이상의 컴포넌트는 단일 컴포넌트로 조합될 수 있고 및/또는 하나 이상의 컴포넌트의 위치는 변경될 수 있다. 또한, 전술한 실시예들에서 기능은, 공지된 바와 같이, 하드웨어에서 더 많이 소프트웨어에서 더 적게, 또는 하드웨어에서 더 적게 소프트웨어에서 더 많이 구현될 수 있다.

[0043] 전술한 실시예들은 칩 패키지에서 반도체 다이들(이를테면 실리콘)을 이용하는 반면, 다른 실시예들에서, 이러한 칩들 중 하나 이상에서 기판 재료로서 반도체 외의 다른 재료가 이용될 수 있다. 그러나, 실리콘이 이용되는 실시예들에서, 반도체 다이들(110)(도 1-5)은 표준 실리콘 처리를 이용하여 제조될 수 있다. 이러한 반도체 다이들은 로직 및/또는 메모리 기능을 지원하는 실리콘 구역을 제공할 수 있다.

[0044] 또한, 도 1을 다시 참조하면, 램프 컴포넌트(122)는, 반도체 다이들(110)에 전기적으로 결합하는 금속 트레이스(trace)들을 갖는 플라스틱 기판과 같은, 패시브 컴포넌트(pассив component)일 수 있다. 예를 들어, 램프 컴

포넌트(122)는 사출-성형 플라스틱(injection-molded plastic)을 이용하여 제조될 수 있다. 대안적으로, 램프 컴포넌트(122)는 하나 이상의 리소그래픽으로(lithographically) 정의된 와이어들, 신호 라인들 또는 광도파로들을 갖춘 또 다른 반도체 다이일 수 있다. 예를 들어, 광도파로(128)(도 1-5)는 실리콘-온-절연체(silicon-on-insulator) 기술을 이용하여 구현될 수 있다. 램프 컴포넌트(122)가 반도체 다이를 포함하는 실시예들에서, 제한 증폭기들(limit amplifiers)과 같은 액티브 디바이스들은 신호 라인들 사이의 크로스-토크를 줄이도록 포함될 수 있다. 또한, 크로스-토크는 차동 시그널링을 이용하는 액티브 또는 패시브 램프 컴포넌트(122) 중 어느 하나에서 감소될 수 있다.

[0045] 일부 실시예들에서, 램프 컴포넌트(122)는, 땜납 볼들(이를테면, 땜납 볼(138))을 통해 반도체 다이들(110) 사이에서 데이터 및 전력 신호들을 왕복하는(shuttle) 트랜지스터들 및 와이어들을 포함한다. 예를 들어, 램프 컴포넌트(122)는 고-전압 신호들을 포함할 수 있다. 이러한 신호들은: 반도체 다이들(110)에 결합하기 위해 커패시터 및/또는 인덕터 개별 컴포넌트들은 물론, 스텝 다운 조정기(step-down regulator)(이를테면, 커패시터-투-커패시터 스텝 다운 조정기)를 이용하는 반도체 다이들(110)에서 이용하기 위해 스텝 다운될 수 있다.

[0046] 또한, 램프 컴포넌트(122)는 메모리를 위한 버퍼 또는 로직 칩, 및/또는 외부 디바이스(들) 및/또는 시스템(들)로의 I/O 커넥터들을 포함할 수 있다. 예를 들어, I/O 커넥터들은: 외부 디바이스들에 결합하기 위한 볼 본드들, 와이어 본드들, 에지 커넥터들 및/또는 PxC 커넥터들 중 하나 이상을 포함할 수 있다. 일부 실시예들에서, 이러한 I/O 커넥터들은 램프 컴포넌트(122)의 배면(back surface) 상에 있을 수 있고, 램프 컴포넌트(122)는, PxC 커넥터들이나 땜납 패드들(예컨대, 땜납 패드(144-2))과 같은, 반도체 다이들(110) 근처의 추가의 커넥터들에 I/O 커넥터들을 결합하는 하나 이상의 TSV(through-silicon vias)를 포함할 수 있다.

[0047] 일부 실시예에서, 램프 컴포넌트(122) 및 반도체 다이(110)는 선택적(optional) 기판(이를테면, 인쇄 회로 기판 또는 반도체 다이) 상에 장착된다. 이러한 선택적 기판은: 외부 디바이스들에 결합하기 위한 볼 본드들, 와이어 본드들, 에지 커넥터들 및/또는 PxC 커넥터들을 포함할 수 있다. 이러한 I/O 커넥터들이 선택적 기판의 배면에 있는 경우, 선택적 기판은 하나 이상의 TSV를 포함할 수 있다.

[0048] 전술한 바와 같이, 일부 실시예들에서, 선택적 열-확산 재료(140)(및, 더 일반적으로, 높은 열전도율을 갖는 반도체 다이들(110) 사이의 중간 재료(intermediate material))는 하나 이상의 반도체 다이들(110) 및/또는 램프 컴포넌트(122) 상의 회로들의 동작 동안 생성된 열을 제거하는 것을 도울 수 있다. 이러한 열 관리는 다음의 열 경로들: 반도체 다이들(110)의 평면에서 제1 열 경로; 접착제 층들(132)의 평면에서 제2 열 경로; 및/또는 선택적 열-확산 재료(140)의 평면에서 제3 열 경로 중 임의의 것을 포함할 수 있다. 특히, 이러한 열 경로들과 관련된 열 플러스(thermal flux)는 칩 패키지의 에지에서의 열 결합(thermal coupling)을 통해 서로 독립적으로 관리될 수 있다. 이러한 열 관리는: 상 변화 냉각(phase change cooling), 집중 냉각(immersion cooling), 및/또는 냉각판(cold plate)의 이용을 포함할 수 있다는 것에 주목한다. 또한, 칩 패키지의 에지에서 단면적을 통해 확산하는 제1 열 경로와 관련된 열 플러스는 공칭 두께(134)의 함수라는 것에 주목한다. 따라서, 열 관리는 더 큰 또는 더 작은 공칭 두께의 반도체 다이들(110)을 갖는 칩 패키지들에서 상이할 수 있다.

[0049] 전술한 실시예들은 칩 패키지의 특정한 구성들을 예시하는 한편, 다수의 기술 및 구성이 컴포넌트들의 기계적 정렬을 구현하는데 이용될 수 있다. 예를 들어, 반도체 다이들(110) 및/또는 램프 컴포넌트(122)는 볼-앤팟(ball-and-pit) 정렬 기술(및, 더 일반적으로, 포지티브-피처-인-네거티브 피처(positive-feature-in-negative-feature) 정렬 기술)을 이용하여 서로에 대해 배치될 수 있다. 특히, 볼들은 스택(112)에 반도체 다이들(110)을 기계적으로 결합 및 상대적으로 정렬하기 위해 에치 피트들(etch pits)로 배치될 수 있다. 다른 실시예들에서, 반구-형상 범프들과 같은 다양한 포지티브 피처들이 이용될 수 있다. 따라서, 일반적으로, 칩 패키지 내의 컴포넌트들 상에서 기계적으로 로킹하는(locking) 포티지브 및 네거티브 표면 피처들의 조합이 칩 패키지를 정렬 및/또는 조립하는데 이용될 수 있다.

[0050] 패키징 및 조립 전에 광범위하게 테스트하기 위해 고 비용 또는 더 낮은 반도체-다이 수율에 직면할 때, 일부 재작업을 허용하는 패키징 기술들은 비용 효율이 더 높다는 것에 주목한다. 따라서, 반도체 다이들(110)과 램프 컴포넌트(122) 사이의 기계적, 광학적 및/또는 전기적 결합이 리메이트가능한(remateable) 실시예들에서, 칩 패키지의 수율은 재작업을 허용하는 것(이를테면, 조립, 테스트 또는 번인(burn-in) 동안 식별되는 불량한 칩을 대체하는 것)에 의해 증가될 수 있다. 이런 점에서, 리메이트가능한 기계적, 광학적 및/또는 전기적 결합은(땡납과 같이) 재작업이나 가열을 필요로 하지 않고 반복적으로(즉, 2회 이상) 구축 및 브레이크될 수 있는 기계적, 광학적, 또는 전기적 결합이라는 것이 이해되어야 한다. 일부 실시예들에서, 리메이트가능한 기계적, 광학적 및/또는 전기적 결합은 서로 결합하도록 설계된 자성(male) 및 웅성(female) 컴포넌트들(이를테면, 서로

스냅하는 컴포넌트들)을 수반한다.

일부 실시예들에서, 전술한 실시예들에서의 칩 패키지의 적어도 일부 주위에 선택적 캡슐화(encapsulation)가 존재할 수 있다. 또한, 칩 패키지에서 컴포넌트들 사이의 에어 갭(air gaps)은 열 제거를 개선하기 위해 언더필(underfill)될 수 있다. 이는 각도(126)를 감소시킴으로써 용이하게 될 수 있는데, 즉, 반도체 다이들(110)은 수직 방향(114)을 향해 더 기울어질(tip) 수 있다.

전술한 설명은 통상의 기술자가 본 개시물을 만들고 이용하는 것을 가능하게 하기 위한 것으로, 특정한 애플리케이션 및 그의 요구 사항의 맥락에서 제공된다. 또한, 본 개시물의 실시예들에 대한 전술한 설명은 단지 예시 및 설명을 목적으로 제시되었다. 이들은 포괄적이거나(exhaustive) 개시된 형태들로 본 개시물을 제한하도록 의도되지 않는다. 따라서, 많은 변형들 및 변경들이 통상의 기술자에게 명백할 것이고, 여기에 정의된 일반적인 원칙들은 본 개시물의 사상 및 범위를 벗어나지 않고 다른 실시예들 및 애플리케이션들에 적용될 수 있다. 또한, 전술한 실시예들에 대한 논의는 본 개시물을 제한하도록 의도되지 않는다. 따라서, 본 개시물은 예시된 실시예들로 제한하도록 의도되지 않고, 여기에 개시된 원칙 및 특징과 일치하는 폭 넓은 범위가 부여될 것이다.

## 도면

## 도면1

## 도면2

### 도면3

도면4

도면5

## 도면6

## 도면7