(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 693 33 359 T2 2004.10.14

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 0 573 170 B1

(21) Deutsches Aktenzeichen: 693 33 359.6

(96) Europäisches Aktenzeichen: 93 303 824.2

(96) Europäischer Anmeldetag: 18.05.1993

(97) Erstveröffentlichung durch das EPA: 08.12.1993

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 17.12.2003

(47) Veröffentlichungstag im Patentblatt: 14.10.2004

(51) Int Cl.<sup>7</sup>: H01L 27/115

H01L 21/82, H01L 29/788

(30) Unionspriorität:

891705 01.06.1992 US

(84) Benannte Vertragsstaaten:

BE, CH, DE, FR, GB, IT, LI, NL

(73) Patentinhaber:

National Semiconductor Corp., Santa Clara, Calif.,

US

(72) Erfinder:

Bergemont, Albert, Santa Clara, California 95014,

US

(74) Vertreter:

Kahler, Käck & Mollekopf, 86899 Landsberg

(54) Bezeichnung: Herstellungsverfahren einer EEPROM-Zellen-Matrix

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingeleitet, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****HINTERGRUND DER ERFINDUNG****1. GEBIET DER ERFINDUNG**

**[0001]** Die vorliegende Erfindung betrifft ein Verfahren zur Herstellung von hochdichten elektrisch löschenbaren, programmierbaren Nur-Lese-Speicher- (EEPROM) Bauelementen und insbesondere die EEPROM-Zellenmatrix-Herstellung über einer P-Potentialmulde und verwendet ein neues Programmier/Löschen-Schema, um die Störung von benachbarten Zellen zu vermeiden, welches keinen Teil der beanspruchten Erfindung darstellt.

**2. ERÖRTERUNG DES STANDES DER TECHNIK**

**[0002]** Die fundamentale Grundherausforderung bei der Erzeugung einer elektrisch löschenbaren, programmierbaren Nur-Lese-Speicher- (EEPROM) Zelle besteht darin, einen steuerbaren und reproduzierbaren elektrischen Effekt zu verwenden, der genügend Nicht-Linearität aufweist, so dass die Speicherzelle bei einer Spannung in weniger als 1 ms beschrieben und gelöscht werden kann und bei einer anderen Spannung ohne irgendeine Änderung der programmierten Daten für mehr als 10 Jahre gelesen werden kann. Fowler-Nordheim-Tunnelung, die zum ersten Mal 1928 von Fowler und Nordheim beschrieben wurde, weist die erforderliche Nicht-Linearität auf und wurde in EEPROM-Speichern umfangreich verwendet.

**[0003]** In Silizium (Si) beträgt die Energiedifferenz zwischen dem Leitungsband und dem Valenzband 1,1 eV. In Siliziumdioxid ( $\text{SiO}_2$ ) beträgt die Energiedifferenz zwischen diesen Bändern etwa 8,1 eV, wobei das Leitungsband in  $\text{SiO}_2$  3,2 eV über jenem in Si liegt. Da die Elektronenenergie etwa 0,025 eV bei thermischer Raumtemperatur beträgt, ist die Wahrscheinlichkeit, dass ein Elektron in Si genügend Wärmeenergie erlangen kann, um die Si- $\text{SiO}_2$ -Barriere zu überwinden und in das Leitungsband in  $\text{SiO}_2$  zu gelangen, sehr klein. Wenn Elektronen in einem schwelbenden Polysiliziumgate, das von  $\text{SiO}_2$  umgeben ist, angeordnet sind, dann stellt dieses Banddiagramm allein die Speicherung von Daten sicher.

**[0004]** Die Fowler-Nordheim-Emission, die früh in diesem Jahrhundert für den Fall der Elektronenemission aus Metallen in Vakuen beobachtet wurde, wurde auch von Lenzliger und Snow 1969 für die Elektronenemission aus Silizium in Siliziumdioxid beobachtet. In Gegenwart eines starken elektrischen Feldes an der Si- $\text{SiO}_2$ -Grenzfläche werden die Energiebänder gestört und es besteht eine kleine, aber endliche Wahrscheinlichkeit, dass ein Elektron im Leitungsband des Si quantenmechanisch durch die Energiebarriere tunneln und in das Leitungsband des  $\text{SiO}_2$  austritt.

**[0005]** Der Tunnelstrom nimmt exponential mit dem angelegten Feld gemäß dem folgenden allgemeinen Stromdichteausdruck zu:

$$J = (AE^2) \exp(-B/E)$$

wobei A und B Konstanten sind und E das Feld an der Si- $\text{SiO}_2$ -Grenzfläche ist.

**[0006]** Dieser Strom ist bei einer Stromdichte von  $10^{-6} \text{ A/cm}^2$  beobachtbar, wenn das Feld an der Si- $\text{SiO}_2$ -Grenzfläche etwa 10 MV/cm beträgt. Lokale Felder mit dieser Größe bei zur Verwendung in der Mikroelektronik praktikablen Spannungen können durch Anlegen einer Spannung über entweder ein dünnes (etwa 100 Å) auf massivem Silizium gezüchtetes Oxid oder über ein dickeres (etwa 500 Å) auf Polysilizium gezüchtes Oxid erhalten werden. Im letzteren Fall entsteht die Feldverstärkung aus der Bildung von texturiertem Polysilizium, d. h. Bereichen mit positiver Krümmung an der Polysilizium-Polysiliziumoxid-Grenzfläche, was zu einer Tunnelverstärkung bei ähnlichen Spannungen wie im ersten Fall führt.

**[0007]** Die theoretisch ideale EEPROM-Speicherzelle umfasst einen einzelnen Transistor, der durch Anlegen von elektrischen Signalen an eine festgelegte Zeile und eine festgelegte Spalte der Speicherzellenmatrix adressierbar ist. Um beispielsweise eine logische "1" oder eine logische "0" in eine Zelle dieser "idealen" Zelle zu schreiben, wird eine Spannung an das Steuergate angelegt, das der Zeile (Wortleitung) der angesteuerten Zelle entspricht, während eine Spannung, die entweder einer "1" oder einer "0" entspricht, an den Sourcepol oder Drainpol angelegt wird, welcher der Spalte (Bitleitung) der angesteuerten Zelle entspricht.

**[0008]** Ein wichtiges Problem, das bei Versuchen angetroffen wird, diese "ideale" Zelle zu realisieren, ist der

Bedarf für einen zusätzlichen Zugriffstransistor in jeder Speicherzelle, um die Ansteuerung einer einzelnen Zeile von Speicherzellen zu ermöglichen, während Daten in der angesteuerten Zelle verändert werden, ohne versehentlich einen Speicher in anderen Zeilen zu beschreiben oder zu löschen. Leider erhöht die Anwesenheit eines zusätzlichen Zugriffstransistors in jeder Speicherzelle die Größe der Zelle und führt zu einer unpraktischen Chipgröße für Megabit-Speicher matrizies mit hoher Dichte.

**[0009]** Es ist daher ein Ziel, eine EEPROM-Zelle bereitzustellen, die keinen zusätzlichen individuellen Zugriffstransistor in jeder Speicherzelle erfordert, um eine zuverlässige Ansteuerung einer einzelnen Zelle zum Ändern von Daten, während versehentliches gleichzeitiges Programmieren oder Löschen in nicht-angesteuerten Zellen ausgeschlossen wird, bereitzustellen.

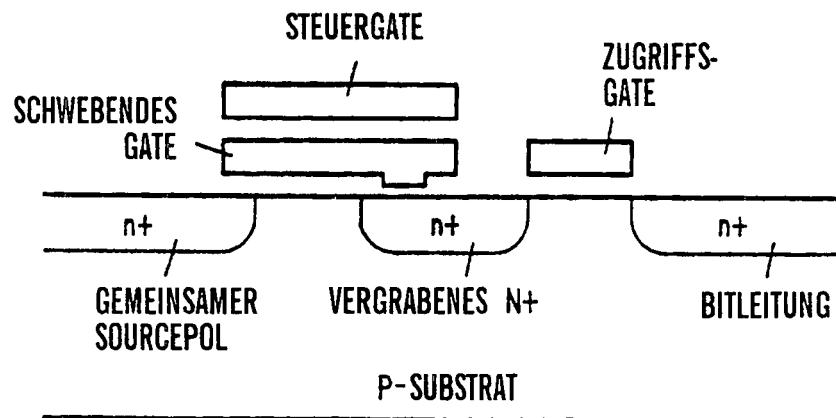

**[0010]** Das Grundkonzept der gut bekannten FLOTOX-EEPROM-Speicherzelle ist in **Fig. 1** gezeigt. In der FLOTOX-Zelle wird das Tunneloxid, das typischerweise weniger als 100 Å dick ist, über einer photolithographisch im Drainbereich (oder einer Erweiterung des Drainbereichs, die vergrabenes N+ genannt wird) festgelegten Fläche gezüchtet. Das Laden des schwebenden Gates zum Programmieren der Zelle wird durch Erden des Sourcepols und des Drainpols und Anlegen einer hohen Spannung an das Steuergate erzielt. Die FLOTOX-Zelle ist derart ausgelegt, dass ein großer Bruchteil der angelegten Spannung über das Tunneloxid gekoppelt wird, was zum Transport von Elektronen vom Drainpol zum schwebenden Gate führt. Das Entladen des schwebenden Gates zum Löschen der Zelle wird durch Erden des Steuergates, Schwebenlassen des Sourcepols und Anlegen einer hohen Spannung an den Drainpol erzielt. In diesem Fall wird das meiste der angelegten Spannung über das Tunneloxid gekoppelt, aber das Feld wird umgekehrt, was zum Tunneln von Elektronen vom schwebenden Gate zum Drainpol führt. Den Sourcepol lässt man schweben, so dass kein kontinuierlicher Stromweg vorhanden ist, ein wichtiger Faktor, wenn eine interne Ladungspumpe verwendet wird, um die hohe Spannung aus einer Versorgung von  $\leq 5V$  zu erzeugen.

**[0011]** Wenn eine einzelne Transistorspeicherzelle in einer typischen Matrix angeordnet ist, wobei die Drainpole mit Metallspalten verbunden sind und die Gates mit gemeinsamen Polysiliziumwortleitungen verbunden sind, bedeutet das Löschen der Zelle, wenn die Wortleitung geerdet ist, dass eine hohe Spannung an alle Drainpole in einer gemeinsamen Spalte angelegt wird. Das Löschen kann in nicht-angesteuerten Zellen verhindert werden, indem nicht-angesteuerte Wortleitungen auf eine hohe Spannung gebracht werden. Dies bedeutet jedoch, dass nicht-angesteuerte Zellen entlang derselben Wortleitung programmiert werden können. Um solche Störungsbedingungen zu vermeiden, verwendet die FLOTOX-Zelle, wie in **Fig. 1** gezeigt, einen individuellen Zugriffstransistor, um den Drainpol von der Spaltenbitleitung zu isolieren. Der Zugriffstransistor ist für Zeilen, die nicht angesteuert werden, gesperrt.

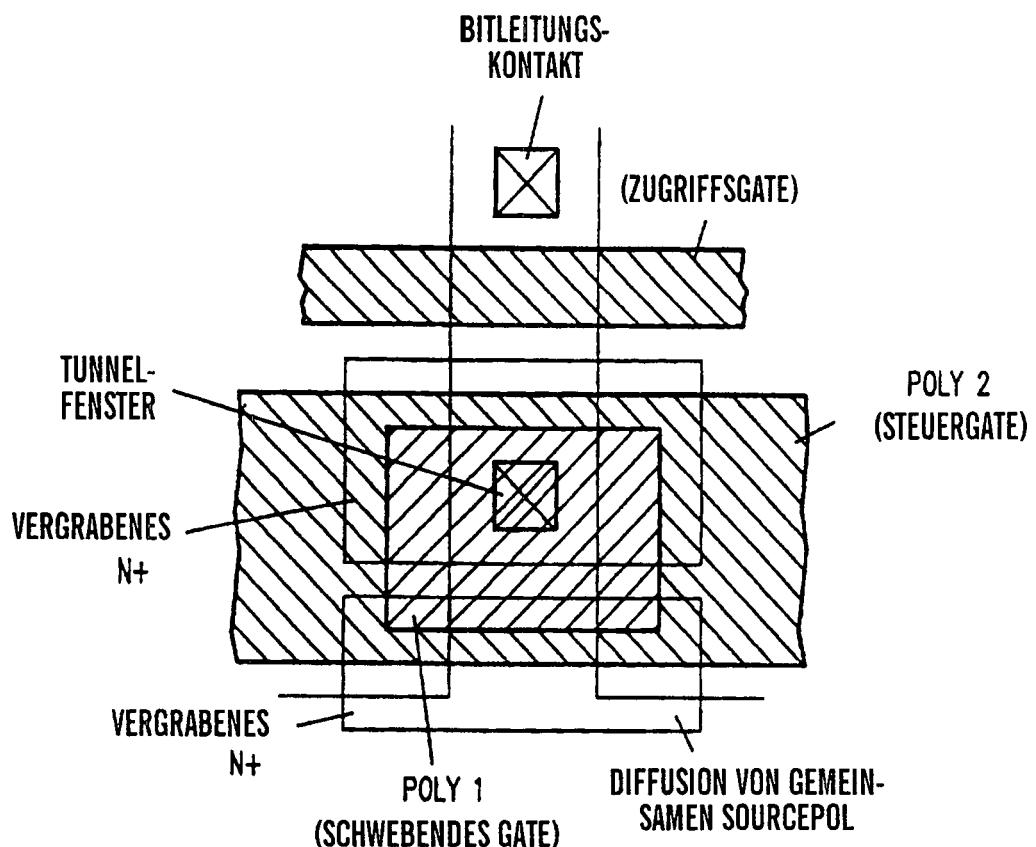

**[0012]** **Fig. 2** stellt eine Anordnung der FLOTOX-Zelle von **Fig. 1** bereit, wobei der Querschnitt von **Fig. 1** zur Wortleitung (Steuergate) und durch das Tunneloxidfenster senkrecht ist.

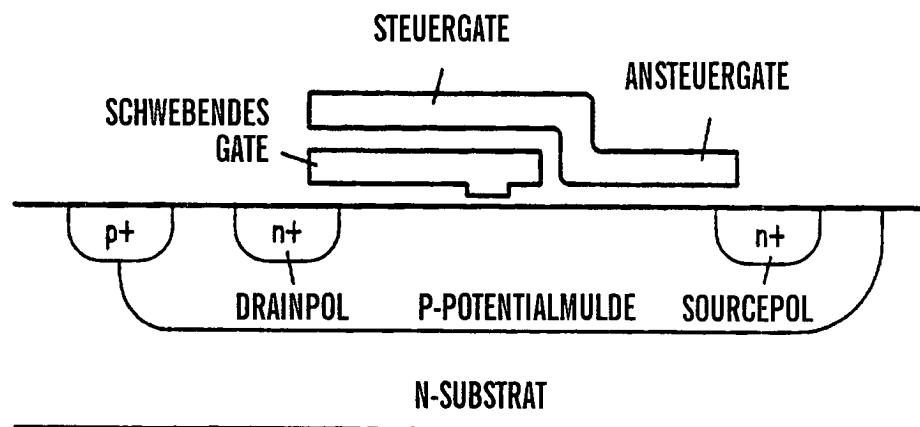

**[0013]** E. K. Shelton, "Low-power EE-PROM can be reprogrammed fast", Electronics, 31. Juli 1980, S. 89–92, offenbart ein grundlegendes EEPROM-Konzept ähnlich dem vorstehend beschriebenen FLOTOX-Konzept. Wie in **Fig. 3** gezeigt, ist jedoch anstelle eines Tunneloxidbereichs, der lithographisch über dem Drainpol (vergrabenes N+) festgelegt ist, der Tunnelbereich der Shelton-Zelle im Kanal unter dem schwebenden Polysiliziumgate festgelegt. Das schwebende Polysiliziumgate erstreckt sich teilweise über die Drainseite des Kanals, während der Rest des Kanals (Sourceseite) von einem darüberliegenden Aluminiumsteuergate überspannt wird. Das Aluminiumsteuergate ist vom schwebenden Polysiliziumgate durch eine dünne Siliziumnitridschicht isoliert.

**[0014]** Ferner ist die Shelton-Speicherzelle in einer P-Potentialmulde auf einem N-Substrat ausgebildet. Die Steuerung des P-Potentialmuldenpotentials ermöglicht die Beseitigung des individuellen Zugriffstransistors in jeder Speicherzelle. Das Potential der P-Potentialmulde und der Sourcepole und Drainpole der nicht-angesteuerten Zellen wird während Programmieroperationen gewählt, um zu verhindern, dass Minoritätsladungsträger irgendeines der schwebenden Gates zum Substrat entladen, während ermöglicht wird, dass ein einzelnes angesteuertes schwebendes Gate programmiert wird.

**[0015]** Das Programmieren der Zelle von **Fig. 3** wird durch Erden der P-Potentialmulde und Verbinden des Drainpols über einen Lastwiderstand mit der Programmierspannung erzielt. Der Sourcepol wird in Abhängigkeit davon, ob eine "1" oder eine "0" gespeichert werden soll, entweder mit der Programmierspannung oder mit der Erdung verbunden. Um die Programmierung einzuleiten, wird das Aluminiumsteuergate mit der hohen Spannung verbunden. Wenn das Sourcepotential auch mit der hohen Spannung verbunden wird, dann steuert der interne Zugriffstransistor nicht durch und die Oberfläche der P-Potentialmulde unterhalb des schwebenden

Gates wird von Elektronen geräumt. Nur eine kleine Potentialdifferenz existiert zwischen der Oberfläche der P-Potentialmulde und dem schwebenden Gate. Daher tunneln keine Elektronen in das Gate und die Zelle bleibt in einem 0-Zustand. Wenn der Sourceanschluss mit der Erdung verbunden wird (um eine 1 zu programmieren), dann steuert der interne Zugriffstransistor durch, das Oberflächenpotential unter dem schwebenden Gate fällt auf nahe 0 V und Elektronen von der Inversionsschicht tunneln durch das dünne Oxid in das schwebende Gate.

**[0016]** Die Zelle von **Fig. 3** wird durch Erden des Steuergates und dann Anheben der P-Potentialmulde auf die Programmierspannung gelöscht. Dies verursacht, dass Elektronen vom Oxid des schwebenden Gates über das Tunneloxid zur P-Potentialmulde tunneln. Wenn die Elektronen durch das Tunneloxid hindurch tunneln, erlangt das schwebende Gate eine positive Nettoladung.

**[0017]** Obwohl sich die Shelton-Zelle von **Fig. 3** von der FLOTOX-Zelle von **Fig. 1** insofern unterscheidet, als sie keinen individuellen Zugriffstransistor verwendet, erfordert sie einen internen Zugriffstransistor und erfordert folglich auch eine relativ große Zellengröße.

**[0018]** Weitere Herstellungsverfahren sind in US 4258466 und WO 9011621 offenbart.

#### ZUSAMMENFASSUNG DER ERFINDUNG

**[0019]** Die Erfindung stellt ein Verfahren zur Herstellung einer elektrisch löschenbaren, programmierbaren Nur-Lese-Speicherzelle in einem Halbleitermaterial mit Leitfähigkeit vom P-Typ bereit, wobei das Halbleitermaterial vom P-Typ eine Potentialmulde (**12**) mit Leitfähigkeit vom P-Typ ist, die in einem Siliziumsubstrat (**10**) mit Leitfähigkeit vom N-Typ ausgebildet ist, wobei das Verfahren in der folgenden Folge besteht.

- (i) Ausbilden von ersten und zweiten beabstandeten ersten Feldoxid-(FOX1) Bereichen (**16**) in dem Halbleitermaterial vom P-Typ, um einen aktiven Bauelementbereich vom P-Typ zwischen diesen festzulegen;

- (ii) Ausbilden von ersten und zweiten beabstandeten vergraben Bitleitungen (**18**) mit Leitfähigkeit vom N-Typ in dem Halbleitermaterial vom P-Typ unmittelbar seitlich benachbart zum ersten bzw. zum zweiten FOX1-Bereich, so dass die erste und die zweite Bitleitung einen Kanalbereich vom P-Typ zwischen sich festlegen;

- (iii) Ausbilden von ersten und zweiten beabstandeten zweiten Feldoxid-(FOX2) Bereichen (**20**), die jeweils über der ersten und der zweiten Bitleitung liegen, und unmittelbar seitlich benachbart zu den jeweiligen ersten und zweiten Feldoxid- (FOX1) Bereichen;

- (iv) Ausbilden einer Schicht aus einem dielektrischen Gatematerial (**22**) auf dem Halbleitermaterial vom P-Typ zwischen dem ersten und dem zweiten FOX2-Bereich mit einem Fenster aus einem dielektrischen Tunnelmaterial (**24**), das darin derart ausgebildet ist, dass die Dicke des dielektrischen Tunnelmaterials geringer ist als die Dicke des dielektrischen Gatematerials;

- (v) Ausbilden einer Schicht aus einem ersten leitenden Material (**26**) über dem dielektrischen Gatematerial, die sich vom ersten FOX2-Bereich über das dielektrische Tunnelmaterial und insgesamt oder teilweise über die restliche Länge des Kanals in Richtung des zweiten FOX2-Bereichs erstreckt, um ein schwebendes Gate der EEPROM-Zelle festzulegen;

- (vi) Ausbilden einer Schicht aus dielektrischem Zwischenmaterial (**28**) über dem schwebenden Gate; und

- (vii) Ausbilden einer Schicht aus einem zweiten leitenden Material (**30**) über dem dielektrischen Zwischenmaterial, um ein Steuergate der EEPROM-Zelle festzulegen.

**[0020]** Eine solche Zelle ist programmierbar durch:

- (a) Halten des Steuergates der EEPROM-Zelle auf einer programmierbaren Spannung;

- (b) Halten der ersten und der zweiten Bitleitung auf einer jeweils niedrigen Versorgungsspannung;

- (c) Halten der P-Potentialmulde auf der niedrigen Versorgungsspannung;

- (d) während die in den obigen Schritten (a)–(c) dargelegten Bedingungen aufrechterhalten werden, Halten des Steuergates von benachbarten EEPROM-Zellen, die die erste und die zweite Bitleitung gemeinsam nutzen, auf der niedrigen Versorgungsspannung; und

- (e) während die in den obigen Schritten (a)–(d) dargelegten Bedingungen aufrechterhalten werden, Halten der ersten und der zweiten Bitleitung von benachbarten EEPROM-Zellen, die dieselbe Steuergateleitung gemeinsam nutzen, auf der Programmierspannung.

#### BESCHREIBUNG DER ZEICHNUNGEN

**[0021]** **Fig. 1** ist eine Querschnittszeichnung, die eine herkömmliche EEPROM-Zellenstruktur darstellt, die einen individuellen Zugriffstransistor verwendet.

[0022] **Fig.** 2 ist eine Anordnung, die die Zellenstruktur von **Fig.** 1 darstellt.

[0023] **Fig.** 3 ist eine Querschnittszeichnung, die eine EEPROM-Zelle des Standes der Technik darstellt, die auf einer P-Potentialmulde hergestellt ist und einen internen Zugriffstransistor verwendet.

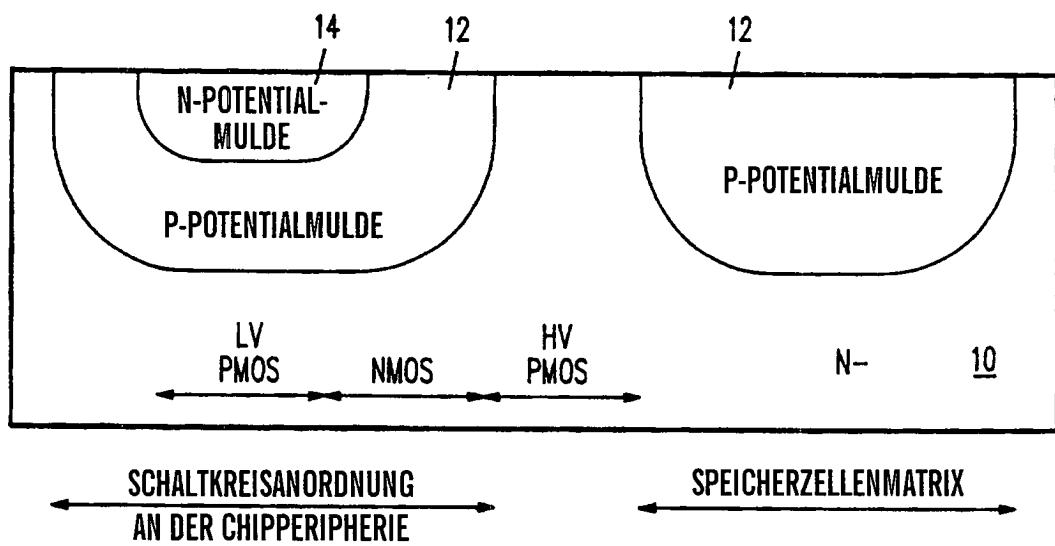

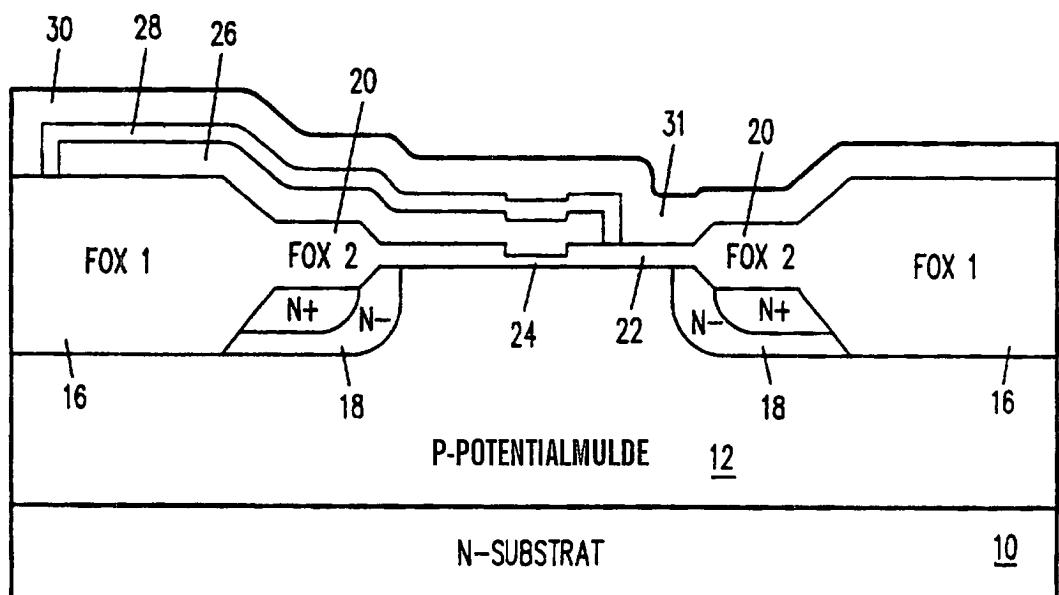

[0024] **Fig.** 4 ist eine Querschnittszeichnung, die eine Struktur mit drei Potentialmulden darstellt, die bei der Herstellung einer hochdichten EEPROM-Zellenmatrix gemäß der vorliegenden Erfindung verwendbar ist.

[0025] **Fig.** 5–7 sind Querschnittszeichnungen, die die Herstellung einer hochdichten EEPROM-Zelle gemäß der vorliegenden Erfindung darstellen.

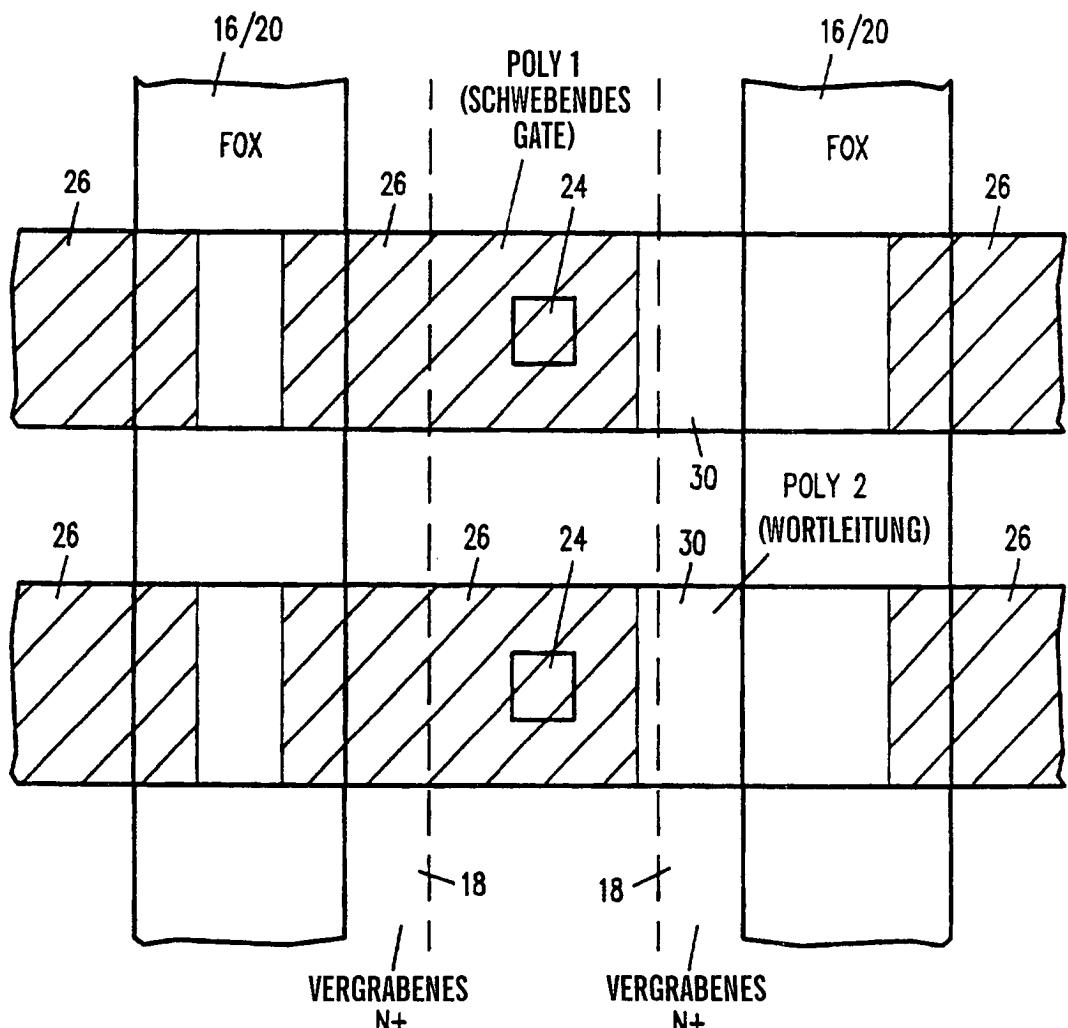

[0026] **Fig.** 8 ist eine Anordnung, die die Zellenstruktur von **Fig.** 7 darstellt.

[0027] **Fig.** 9 ist eine Querschnittszeichnung, die ein alternatives Ausführungsbeispiel einer hochdichten EEPROM-Zelle gemäß der vorliegenden Erfindung darstellt.

[0028] **Fig.** 10 ist eine Anordnung, die die Zellenstruktur von **Fig.** 9 darstellt.

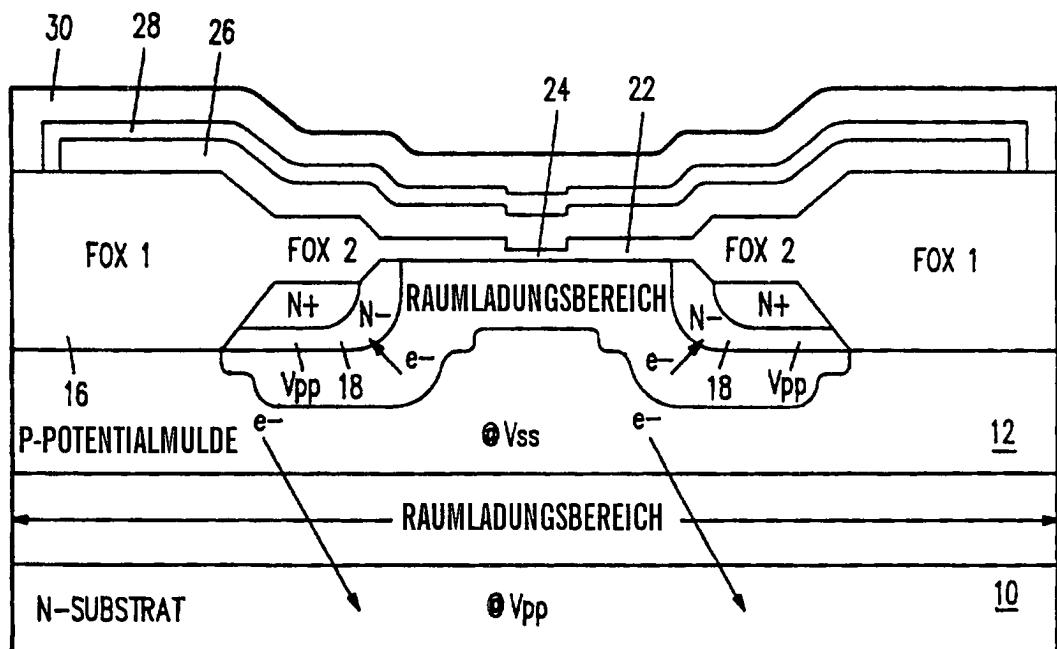

[0029] **Fig.** 11 ist eine Querschnittszeichnung, die Programmiersperrbedingungen in den Zellen von **Fig.** 7/8 und **Fig.** 8/9 während der Programmierung darstellt.

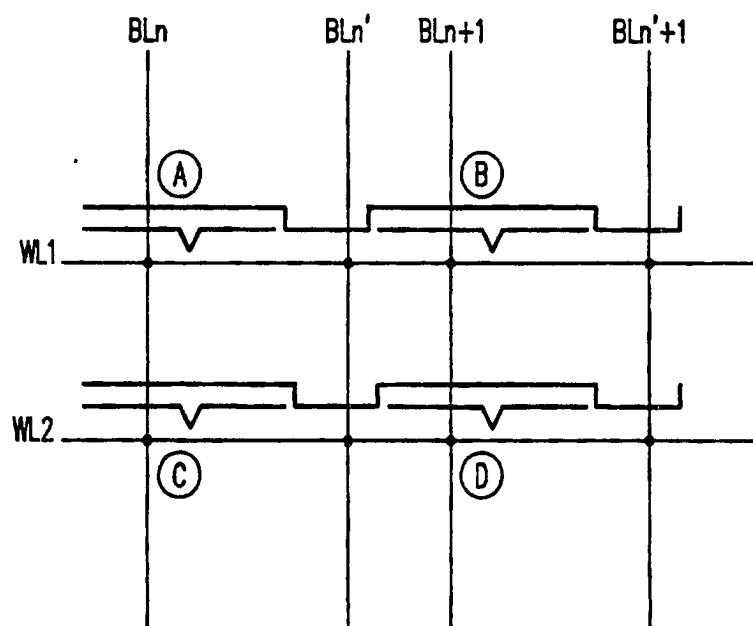

[0030] **Fig.** 12 ist ein schematisches Diagramm, das einen Teil einer hochdichten EEPROM-Zellenmatrix darstellt, welche keinen Teil der beanspruchten Erfindung bildet.

#### AUSFÜHRLICHE BESCHREIBUNG DER ERFINDUNG

[0031] **Fig.** 4–7 stellen die Schritte zur Herstellung einer hochdichten EEPROM-Zelle gemäß der vorliegenden Erfindung dar.

[0032] Mit Bezug auf **Fig.** 4 beginnt der Herstellungsprozess mit einem Siliziumsubstrat **10** mit Leitfähigkeit vom N-Typ. In einem herkömmlichen Vorprozessschritt wird eine anfängliche Oxidschicht (nicht dargestellt) über dem Substrat **10** gezüchtet. Eine Photoresistmaske wird dann über der anfänglichen Oxidschicht ausgebildet und strukturiert, um ausgewählte Oberflächenbereiche des Substrats **10** vom N-Typ festzulegen. Die freigelegten Oberflächenbereiche werden dann mit einer Dotierungssubstanz vom P-Typ implantiert, um P-Potentialmuldenbereiche **12** im Substrat **10** auszubilden. Die Photoresistmaske wird dann von der Oberfläche des Oxids abgelöst und ein thermischer Eindiffundierungsschritt wird durchgeführt, um die P-Potentialmuldenbereiche **12** weiter festzulegen.

[0033] Die anfängliche Oxidschicht wird dann vom Substrat **10** entfernt und eine zweite Oxidschicht (nicht dargestellt) wird über dem Substrat **12** gezüchtet. Das Substrat **12** wird wieder mit Photoresist maskiert, welcher strukturiert wird, um Substratoberflächenbereiche innerhalb dieser P-Potentialmuldenbereiche **12** festzulegen, die schließlich die Schaltkreisanordnung an der Chipperipherie für die EEPROM-Speicherzellenmatrix enthalten. Eine Dotierungssubstanz vom N-Typ wird in die P-Potentialmuldenbereiche **12** an der Peripherie implantiert, um N-Potentialmuldenbereiche **14** festzulegen. Der Photoresist wird dann abgelöst und ein weiterer Eindiffundierungsschritt für sowohl die N-Potentialmuldenbereiche **14** als auch die P-Potentialmuldenbereiche **12** wird durchgeführt. Nach dem Eindiffundierungsschritt wird die zweite Oxidschicht entfernt, was zu der in **Fig.** 4 gezeigten Struktur führt.

[0034] Somit führen die anfänglichen Bearbeitungsschritte zur Ausbildung einer Struktur mit drei Potentialmulden, die das Substrat **10** für die Ausbildung der EEPROM-Speicherzellenmatrix und ihrer Schaltkreisanordnung an der Chipperipherie festlegt. Die N-Potentialmuldenbereiche **14** an der Peripherie werden für die Herstellung von PMOS-Bauelementen mit niedriger Spannung (LV) verwendet. Die P-Potentialmuldenbereiche **12** an der Peripherie werden für die Ausbildung von NMOS-Bauelementen für die Schaltkreisanordnung an der Chipperipherie verwendet. Die P-Potentialmuldenbereiche **12** im Speicherzellenmatrixteil des Substrats **10** werden für die Ausbildung von EEPROM-Speicherzellenbauelementen verwendet. Der Zwischensubstratbereich wird für die Ausbildung von PMOS-Bauelementen mit hoher Spannung (HV) verwendet.

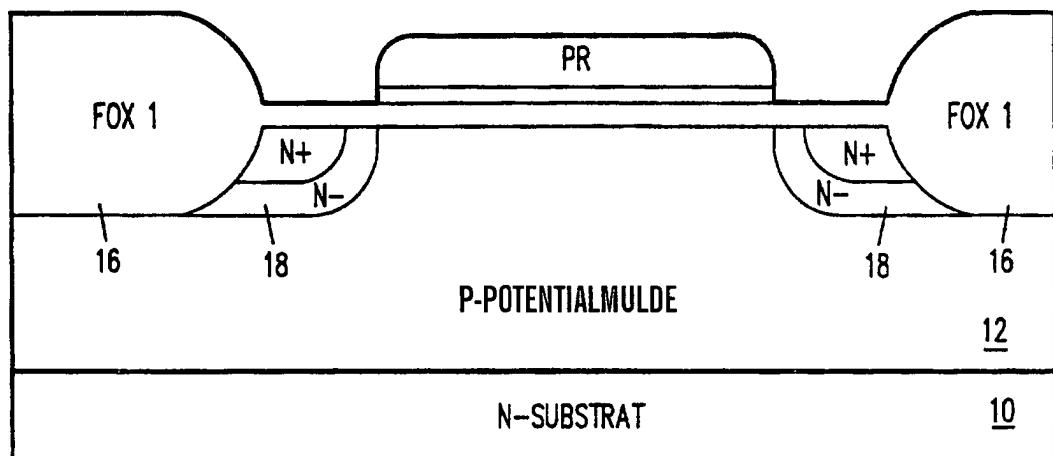

[0035] Mit Bezug auf **Fig.** 5 werden nach der Ausbildung der vorstehend beschriebenen Struktur mit drei Potentialmulden herkömmliche Prozessverfahren verwendet, um Bereiche im Substrat **10** für die Ausbildung von Feldoxid festzulegen. Das heißt, ein Kontaktstellenoxid wird zuerst auf der Oberfläche des Substrats **10** ge-

züchtet, gefolgt von Abscheidung einer darüberliegenden Nitridschicht. Das Kontaktstellenoxid/Nitrid-Komposit wird mit Photoresist maskiert, der dann strukturiert wird, um Bereiche von darunterliegendem Nitrid freizulegen, die schließlich erste Feldoxid-(FOX1) Bereiche festlegen. Das Nitrid wird dann geätzt, der Photoresist wird abgelöst und eine Feldimplantation vom P-Typ wird durch die freiliegenden Kontaktstellenoxidbereiche hindurch durchgeführt. Die Feldimplantationsmaske wird dann abgelöst und erste Feldoxidbereiche (FOX1) **16** werden ausgebildet, wie in **Fig. 5** gezeigt.

**[0036]** Wie weiter in **Fig. 5** gezeigt, werden als nächstes Teile der P-Potentialmuldenbereiche **12** in der Speicherzellenmatrix maskiert, das Nitrid/Oxid-Komposit wird geätzt und eine Arsenimplantation wird durchgeführt, um vergrabene N+-Bitleitungen **18** benachbart zu den FOX1-Feldoxidbereichen **16** festzulegen. Wahlweise kann der Arsenimplantation eine Phosphorimplantation folgen, um abgestufte N+/N–Bitleitungen festzulegen, wodurch die Beständigkeit gegen einen Lawinendurchbruch während des Löschens der EEPROM-Zellen optimiert wird.

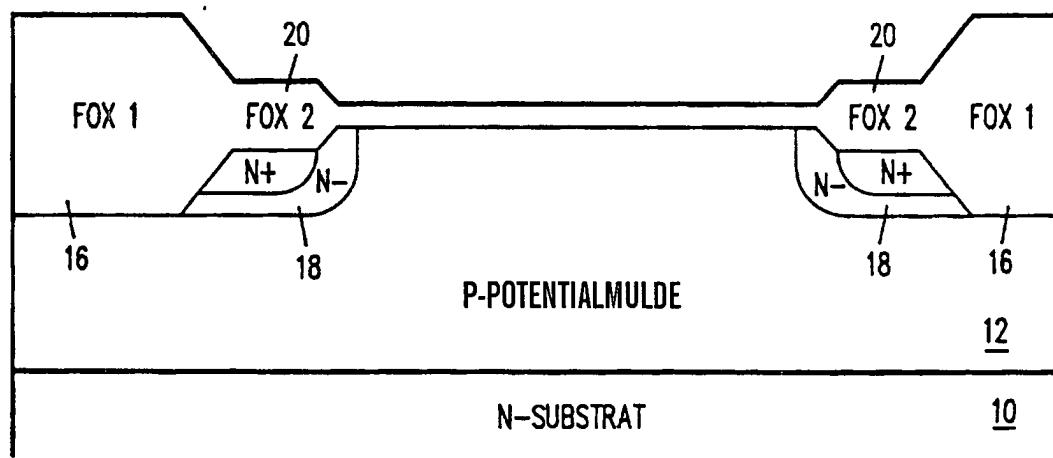

**[0037]** Wie in **Fig. 6** gezeigt, wird der Photoresist dann abgelöst und das Feldoxidwachstum wird durch Ausbildung von zweiten Feldoxidbereichen (FOX2) **20** über den N+/N–Bitleitungen **18** vollendet. Da die Bitleitungen **18** unter dem Feldoxid ausgebildet werden, kann die Größe des aktiven Bereichs des Bauelements verringert werden, was zu einer verringerten Gesamtmatrixgröße führt.

**[0038]** Nach der Vollendung des Feldoxidwachstums, d. h. Ausbildung von FOX1-Bereichen **16** und FOX2-Bereichen **20**, wird die Oxid/Nitrid/Oxid- (ONO) Schicht entfernt und eine Opferoxidschicht (nicht dargestellt) wird ausgebildet. Eine Schwellenspannungsmaske wird dann ausgebildet und strukturiert, um die Kanalbereiche der N-Kanal-Bauelemente der Matrix freizulegen. Eine Schwellenimplantation wird dann durchgeführt, um die Schwellenspannung der Speicherzelltransistoren zu charakterisieren, und die Photoresistmaske wird abgelöst. Dann wird das Opferoxid entfernt.

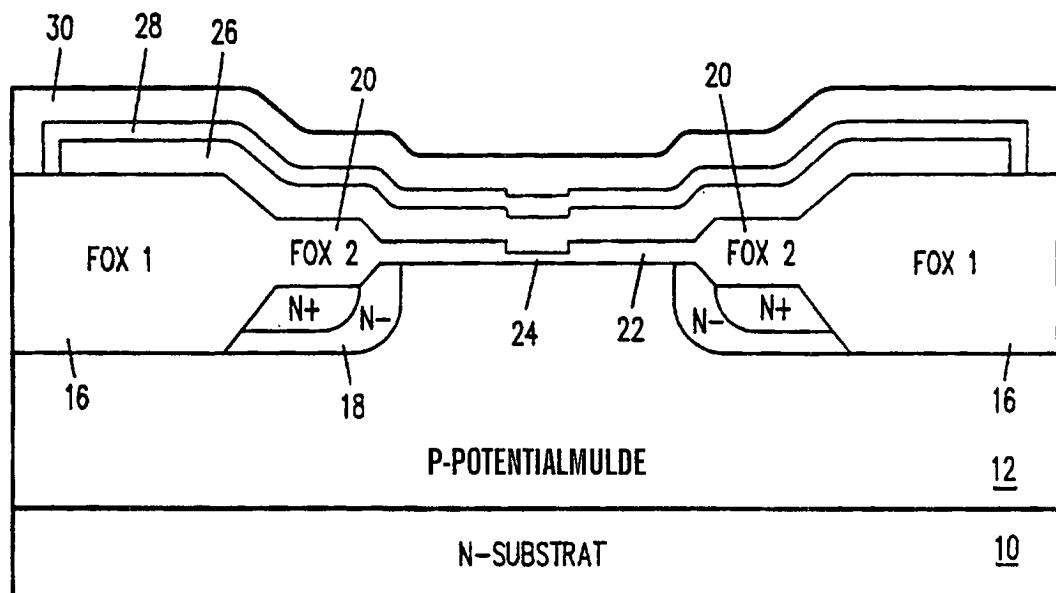

**[0039]** Als nächstes wird eine etwa 30–50 nm (300–500 Å) dicke Gateoxidschicht **22** über den freigelegten Teilen des P-Potentialmuldenbereichs **12** gezüchtet. Eine Tunnelmaske wird dann über dem Gateoxid **22** ausgebildet und strukturiert, um ein Tunnelfenster über der P-Potentialmulde **12** festzulegen. Das Tunnelfenster wird dann bis zur Oberfläche der darunterliegenden P-Potentialmulde **12** durchgeätzt. Die Tunnelmaske wird dann abgelöst und ein etwa 8–10 nm (80–100 Å) dickes Tunneloxid **24** wird im Tunnelfenster gezüchtet. Als nächstes wird eine erste Schicht **26** aus Polysilizium auf dem darunterliegenden Oxid mit einer Dicke von etwa 1500 Å abgeschieden und mit Phosphor dotiert. Das Polysilizium (Poly1) dient als schwebendes Gate für die EEPROM-Zellen der Matrix. Eine dielektrische Kompositsschicht **28** aus Oxid/Nitrid/Oxid (ONO) wird dann auf dem Poly1 ausgebildet. Nach dem Züchten dieser ONO-Schicht **28** wird eine Photoresistmaske verwendet, um Streifen auf dem ONO festzulegen. Der ONO/Poly1-Komposit wird dann plasmageätzt, um parallele Leitungen aus ONO/Poly1 auszubilden.

**[0040]** Nach dem Ablösen des Photoresists von der Poly1-Maske wird ein dünnes Kantenoxid auf den Seitenwänden der Poly1-Leitungen gezüchtet, um eine Isolation von anschließend ausgebildetem leitenden Steuergatematerial vorzusehen.

**[0041]** Als nächstes wird eine Schutzmatrixmaske über dem Speicherzellenmatrixteil des Substrats **10** ausgebildet und die Bauelementausbildung an der Peripherie geht weiter.

**[0042]** Zuerst wird Oxid von den aktiven Bauelementbereichen des Substrats an der Peripherie geätzt und Gateoxid wird auf den aktiven Bauelementbereichen gezüchtet. Eine Schwellenmaske wird dann ausgebildet und eine Implantation vom P-Typ wird durchgeführt, um die Schwelle der peripheren MOS-Bauelemente festzulegen. Die Schwellenphotoresistmaske wird dann abgelöst und die Bearbeitung beginnt, um sowohl die Wortleitungen für die Speicherzellenmatrix als auch die Gates für die MOS-Bauelemente an der Peripherie auszubilden.

**[0043]** Das heißt, eine zweite Schicht aus Polysilizium (Poly2) wird über der Oberfläche des gesamten Bauelements abgeschieden und in herkömmlicher Weise dotiert. Diesem folgt Abscheidung einer darüberliegenden Schicht aus Wolframsilizid. Das Poly2/Wolframsilizid-Komposit wird dann maskiert und geätzt, um die Wortleitungen **30** in der Speicherzellenmatrix und die Gateelektroden der peripheren MOS-Bauelemente festzulegen, wobei die Wortleitungen **30** parallel zu den ONO/Poly1-Leitungen in der Matrix verlaufen und über diesen liegen. Die Poly2-Maske wird dann W-gehärtet und eine selbstpositionierende Ätz- (SAE) Maske wird ausgebildet. Diesem folgt gestapeltes Ätzen der schwebenden Poly1-Gates **26** unter Verwendung der darüberliegenden Poly2-Wortleitungen **30** als Maske für das selbstpositionierende Ätzen des ONO/Poly1-Kompo-

sits.

**[0044]** Der restliche Photoresist wird dann vom Bauelement abgelöst und ein Seitenwandabdichtungs-Oxidationsschritt wird an den Bauelementen im Peripheriebereich und für den Poly1/Poly2-Stapel in der Matrix durchgeführt.

**[0045]** Ab diesem Punkt geht der Prozessablauf gemäß Standard-CMOS-Bearbeitungsverfahren vor sich, wobei zusätzliche Masken zum Ausbilden der PMOS-Transistoren mit hoher Spannung im N-Substrat zwischen der Peripherie und der Speicherzellenmatrix verwendet werden. Die resultierende Zellenstruktur ist in **Fig. 7** gezeigt.

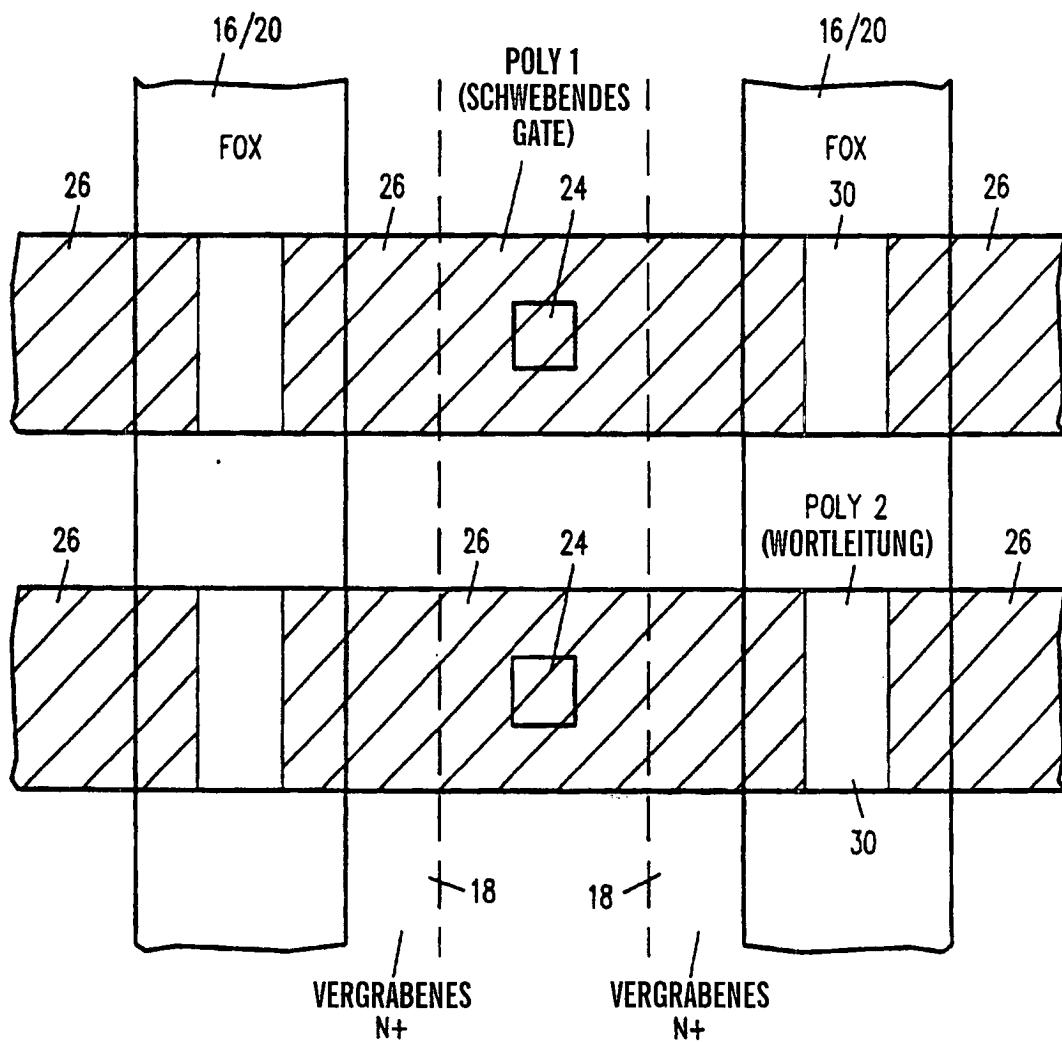

**[0046]** Eine entsprechende Anordnung der Zelle von **Fig. 7** ist in **Fig. 8** gezeigt, wobei der Querschnitt von **Fig. 7** entlang einer Wortleitung **30** in der Anordnung von **Fig. 8** genommen ist.

**[0047]** **Fig. 9** stellt einen Querschnitt eines alternativen Ausführungsbeispiels einer EEPROM-Speicherzelle gemäß der vorliegenden Erfindung dar, wobei das schwebende Poly1-Gate **26** über dem P-Potentialmuldenbereich **12** zwischen vergraben N+-Bitleitungen **18** verkürzt ist. Somit bildet die darüberliegende Poly2-Wortleitung **30** das Gate **31** eines internen Zugriffstransistors in einer Weise ähnlich zu der vorstehend beschriebenen Shelton-Zelle. Aufgrund der von den vorstehend beschriebenen Bearbeitungsverfahren bereitgestellten Vorteile ist jedoch die Zelle von **Fig. 9** kleiner als die Shelton-Zelle und verwendet vielmehr ein Poly2-Zugriffsgate als ein Aluminiumgate.

**[0048]** Eine Anordnung der in **Fig. 9** gezeigten Zelle ist in **Fig. 10** vorgesehen, wobei der Querschnitt von **Fig. 9** entlang einer Wortleitung **30** in der Anordnung von **Fig. 10** genommen ist.

**[0049]** Obwohl die in **Fig. 7** und **8** gezeigte Zelle den in EEPROM-Zellen typischerweise verwendeten Zugriffstransistor beseitigt, ist sie folglich für Überlöschen anfällig, was zu Lesestörungsproblemen führt. Daher kann das Ausführungsbeispiel von **Fig. 7/8** einen speziellen Löschalgorithmus erfordern, um Überlöschen zu verhindern. Die Löschoperation könnte man beispielsweise für einen gewissen festgelegten Zeitraum, z. B. 10  $\mu$ s, ablaufen lassen, wonach die Schwellenspannung  $V_T$  von jeder Zelle in der Matrix gelesen wird. Wenn die Schwellenspannung  $V_T$  von irgendeiner Zelle in der Matrix geringer als ein festgelegter Wert, z. B. 1,2 V, ist, dann wird die Löschprozedur beendet. Wenn die Schwellenspannung aller Zellen oberhalb 1,2 V bleibt, dann wird eine andere zeitgesteuerte Löschiteration durchgeführt.

**[0050]** Wie vorstehend angegeben, umfasst das Ausführungsbeispiel von **Fig. 9/10** einen Ansteuertransistor zum Angehen des Überlöschenproblems, erfordert jedoch dazu eine größere Gesamtzellenfläche.

**[0051]** In beiden Ausführungsbeispielen der Erfindung beruht die resultierende Matrix auf einer neuen kompakten Zelle, die keinen separaten Zugriffstransistor erfordert. Wie vorstehend angegeben, legen ferner in beiden Ausführungsbeispielen die vergrabenen N+-Bereiche nicht den Speichertransistorkanal fest, der vielmehr mit dem Feldoxid selbstpositionierend ist, insbesondere den zweiten FOX2-Feldoxidbereich **20**, wodurch die Zellengröße weiter verringert wird.

**[0052]** Tabelle 1 stellt ein neues Programmierschema für die Ausführungsbeispiele sowohl von **Fig. 7/8** als auch **Fig. 9/10** der Erfindung bereit. Wie in **Fig. 11** gezeigt, wendet sich das Programmiersperrschema von Tabelle I einer tiefen Verarmung während der Programmierung zu, indem bewirkt wird, dass irgendwelche Minoritätsladungsträger (d. h. Elektronen), die thermisch in der P-Potentialmulde **12** oder in den Raumladungsbereichen erzeugt werden, durch die Sperrspannungsübergänge der N-/P-Potentialmulde und der N+-Bitleitung/P-Potentialmulde "aufgesaugt" werden.

TABELLE 1

|                  | Sourcepol       | Drainpol          | Steuergate      | P-Potentialmulde | N-Sub           |

|------------------|-----------------|-------------------|-----------------|------------------|-----------------|

| Schreiben        | V <sub>ss</sub> | V <sub>ss</sub>   | V <sub>pp</sub> | V <sub>ss</sub>  | V <sub>pp</sub> |

| WL-Schreibsperre | V <sub>pp</sub> | V <sub>pp</sub>   | V <sub>pp</sub> | V <sub>ss</sub>  | V <sub>pp</sub> |

| BL-Schreibsperre | V <sub>ss</sub> | V <sub>ss</sub>   | V <sub>ss</sub> | V <sub>ss</sub>  | V <sub>pp</sub> |

| Löschen          | V <sub>pp</sub> | V <sub>pp</sub>   | V <sub>ss</sub> | V <sub>pp</sub>  | V <sub>pp</sub> |

| BL-Löschesperre  | V <sub>pp</sub> | V <sub>pp</sub>   | V <sub>pp</sub> | V <sub>pp</sub>  | V <sub>pp</sub> |

| Lesen            | V <sub>ss</sub> | V <sub>read</sub> | V <sub>cc</sub> | V <sub>ss</sub>  | V <sub>cc</sub> |

**[0053]** Mit Bezug auf **Fig. 12** sind die Programmierbedingungen insbesondere folgendermaßen. Um eine Zelle A zu programmieren, wird eine Wortleitung WL1 auf der Programmierspannung V<sub>pp</sub> gehalten. Die Bitleitung BL<sub>n</sub> und die Bitleitung BL<sub>n+1</sub> werden auf der niedrigen Versorgungsspannung V<sub>ss</sub> gehalten. Die P-Potentialmulde wird auch auf V<sub>ss</sub> gehalten. Dies erzeugt eine Inversionsschicht von Minoritätsladungsträgern im Kanal, was bewirkt, dass Elektronen zum schwebenden Gate tunneln.

**[0054]** Während dieser Operation wird das Programmieren der Zelle C durch Halten der Wortleitung WL2 auf V<sub>ss</sub>, der Bitleitung BL<sub>n</sub> und BL<sub>n+1</sub> auf V<sub>ss</sub> und der P-Potentialmulde auf V<sub>ss</sub> gesperrt. Ferner wird das Programmieren der Zelle B durch Halten der Wortleitung WL1 auf V<sub>pp</sub> und Anheben der Bitleitungen BL<sub>n+1</sub> und BL<sub>n+2</sub> auf die Programmierspannung, während die P-Potentialmulde auf V<sub>ss</sub> gehalten wird, gesperrt. Dies vermeidet das Auftreten von irgendwelchen Minoritätsladungsträgern an der P-Potentialmuldenoberfläche unter dem schwebenden Gate; die einzige Minoritätsladungsträgererzeugung ist thermisch und alle dieser Elektronen werden von der P-Potentialmulde **12** durch die Sperrspannungsübergänge der Bitleitung/P-Potentialmulde und der N-/P-Potentialmulde abgesaugt.

**[0055]** Mit weiterer Bezugnahme auf **Fig. 12** sind die Löschbedingungen für die vorstehend beschriebenen Zelle folgendermaßen. Um die Zelle A und ihre zugehörige Byte- oder Wortleitung zu löschen, wird die Wortleitung WL1 auf V<sub>ss</sub> gehalten, während die Bitleitungen BL<sub>n</sub> und BL<sub>n+1</sub> und BL<sub>n+2</sub> sowie die P-Potentialmulde auf der Programmierspannung V<sub>pp</sub> gehalten werden. Während dieser Operation wird das Löschen der Zelle C durch Halten der Wortleitung WL2 auf der Programmierspannung gesperrt.

**[0056]** Es sollte selbstverständlich sein, dass verschiedene Alternativen für die hierin beschriebenen Ausführungsbeispiele der Erfindung bei der Ausführung der Erfindung verwendet werden können. Es ist vorgesehen, dass die folgenden Ansprüche den Schutzbereich der Erfindung festlegen und dass Verfahren und Strukturen innerhalb des Schutzbereichs dieser Ansprüche und ihrer Äquivalente dadurch erfasst werden.

### Patentansprüche

1. Verfahren zur Herstellung einer elektrisch löschenbaren, programmierbaren Nur-Lese-Speicherzelle in einem Halbleitermaterial mit Leitfähigkeit vom P-Typ, wobei das Halbleitermaterial vom P-Typ eine Potentialmulde (**12**) mit Leitfähigkeit vom P-Typ ist, die in einem Siliziumsubstrat (**10**) mit Leitfähigkeit vom N-Typ ausgebildet ist, wobei das Verfahren in der folgenden Folge besteht:

- (i) Ausbilden von ersten und zweiten beabstandeten ersten Feldoxid- (FOX1) Bereichen (**16**) in dem Halbleitermaterial vom P-Typ, um einen aktiven Bauelementbereich vom P-Typ zwischen diesen festzulegen;

- (ii) Ausbilden von ersten und zweiten beabstandeten vergraben Bitleitungen (**18**) mit Leitfähigkeit vom N-Typ in dem Halbleitermaterial vom P-Typ unmittelbar seitlich benachbart zum ersten bzw. zum zweiten FOX1-Bereich, so dass die erste und die zweite Bitleitung einen Kanalbereich vom P-Typ zwischen sich festlegen;

- (iii) Ausbilden von ersten und zweiten beabstandeten zweiten Feldoxid-(FOX2) Bereichen (**20**), die jeweils über der ersten und der zweiten Bitleitung liegen, und unmittelbar seitlich benachbart zu den jeweiligen ersten und

zweiten Feldoxid-(FOX1) Bereichen;

(iv) Ausbilden einer Schicht aus einem dielektrischen Gatematerial (22) auf dem Halbleitermaterial vom P-Typ zwischen dem ersten und dem zweiten FOX2-Bereich mit einem Fenster aus einem dielektrischen Tunnelmaterial (24), das darin derart ausgebildet ist, dass die Dicke des dielektrischen Tunnelmaterials geringer ist als die Dicke des dielektrischen Gatematerials;

(v) Ausbilden einer Schicht aus einem ersten leitenden Material (26) über dem dielektrischen Gatematerial, die sich vom ersten FOX2-Bereich über das dielektrische Tunnelmaterial und insgesamt oder teilweise über die restliche Länge des Kanals in Richtung des zweiten FOX2-Bereichs erstreckt, um ein schwebendes Gate der EEPROM-Zelle festzulegen;

(vi) Ausbilden einer Schicht aus dielektrischem Zwischenmaterial (28) über dem schwebenden Gate; und

(vii) Ausbilden einer Schicht aus einem zweiten leitenden Material (30) über dem dielektrischen Zwischenmaterial, um ein Steuergate der EEPROM-Zelle festzulegen.

2. Verfahren nach Anspruch 1, wobei die Schicht aus dem ersten leitenden Material nur über einem Teil des Kanalbereichs in Richtung des zweiten FOX2-Bereichs ausgebildet wird, so dass die Schicht aus dem zweiten leitenden Material direkt auf dem dielektrischen Gatematerial ausgebildet wird und über einem restlichen Teil des Kanalbereichs liegt, um dadurch ein internes Zugriffsgate der EEPROM-Zelle festzulegen.

3. Verfahren nach Anspruch 1 oder Anspruch 2, wobei das dielektrische Gatematerial und das dielektrische Tunnelmaterial Siliziumdioxid umfassen.

4. Verfahren nach einem der Ansprüche 1 bis 3, wobei das erste leitende Material Polysilizium umfasst.

5. Verfahren nach einem der Ansprüche 1 bis 4, wobei das dielektrische Zwischenmaterial ein Oxid/Nitrid/Oxid-Komposit umfasst.

6. Verfahren nach einem der Ansprüche 1 bis 5, wobei das zweite leitende Material Polysilizium umfasst.

7. Verfahren nach einem der Ansprüche 1 bis 5, wobei das zweite leitende Material Polysilizium und darüberliegendes Wolframsilizid umfasst.

Es folgen 6 Blatt Zeichnungen

## Anhängende Zeichnungen

STAND DER TECHNIK

FIG. 1

STAND DER TECHNIK

FIG. 2

STAND DER TECHNIK

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12