(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4707396号

(P4707396)

(45) 発行日 平成23年6月22日(2011.6.22)

(24) 登録日 平成23年3月25日(2011.3.25)

(51) Int.Cl.

H03M 1/38 (2006.01)

H03M 1/18 (2006.01)

F 1

H03M 1/38

H03M 1/18

請求項の数 24 (全 12 頁)

(21) 出願番号 特願2004-565705 (P2004-565705)

(86) (22) 出願日 平成15年12月24日 (2003.12.24)

(65) 公表番号 特表2006-512861 (P2006-512861A)

(43) 公表日 平成18年4月13日 (2006.4.13)

(86) 國際出願番号 PCT/US2003/041264

(87) 國際公開番号 WO2004/062109

(87) 國際公開日 平成16年7月22日 (2004.7.22)

審査請求日 平成18年12月11日 (2006.12.11)

(31) 優先権主張番号 10/330,717

(32) 優先日 平成14年12月27日 (2002.12.27)

(33) 優先権主張国 米国(US)

(73) 特許権者 501144003

アナログ・デバイシズ・インコーポレーテッド

アメリカ合衆国マサチューセッツ州ノーウッド, ワン・テクノロジー・ウェイ (番地なし)

(74) 代理人 100102842

弁理士 葛和 清司

(72) 発明者 カーニー, トーマス, ポール

アイルランド、リマリック、バリーキーフ

、メイパーク 18

前置審査

審査官 栗栖 正和

最終頁に続く

(54) 【発明の名称】入力レンジがプログラム可能なS A R A D C (逐次比較型アナログデジタルコンバータ)

## (57) 【特許請求の範囲】

## 【請求項1】

入力電圧レンジがプログラム可能なアナログデジタルコンバータであつて：

特徴的なダイナミックレンジを有する逐次比較型アナログデジタルコンバータ(S A R A D C)；

入力電圧が一つまたは二つ以上の選択されたサンプリングキャパシターにサンプリングされて、入力電圧をS A R A D Cの特徴的なダイナミックレンジに実質的に適合するよう<sup>10</sup>にスケーリングをする入力電圧スケーリングネットワーク；および

一つまたは二つ以上の選択されたサンプリングキャパシターに入力電圧を供給する、複数のハイボルテージサンプリングスイッチを含む入力電圧と入力電圧スケーリングネットワークの間に挿入されたネットワーク

を含む、前記アナログデジタルコンバータ。

## 【請求項2】

入力電圧スケーリングネットワークがS A R A D Cの一部を構成する容量性再配分デジタルアナログコンバータである、請求項1に記載の入力レンジがプログラム可能なアナログデジタルコンバータ。

## 【請求項3】

入力電圧スケーリングネットワークの一つまたは二つ以上の、入力電圧がサンプリングされる要素を選択するレンジデコーダーロジックをさらに含む、請求項1に記載の入力レンジがプログラム可能なアナログデジタルコンバータ。

**【請求項 4】**

入力電圧レンジがバイポーラである、請求項 1 に記載の入力レンジがプログラム可能なアナログデジタルコンバータ。

**【請求項 5】**

ロー・ボルテージからハイボルテージへのレベルシフターのネットワークが制御信号をハイボルテージサンプリングスイッチに接続する請求項 4 に記載の入力レンジがプログラム可能なアナログデジタルコンバータ。

**【請求項 6】**

レンジデコーダーロジックが関連するレンジレジスタに書き込まれたレンジ選択制御ワードに応答する請求項 1 に記載の入力レンジがプログラム可能なアナログデジタルコンバータ。10

**【請求項 7】**

レンジレジスタがデジタル通信インターフェイスを通じてプログラム可能である、請求項 6 に記載の入力レンジがプログラム可能なアナログデジタルコンバータ。

**【請求項 8】**

デジタル通信インターフェイスがシリアル通信インターフェイスである、請求項 7 に記載の入力レンジがプログラム可能なアナログデジタルコンバータ。

**【請求項 9】**

シリアル通信インターフェイスが双方向である、請求項 8 に記載の入力レンジがプログラム可能なアナログデジタルコンバータ。20

**【請求項 10】**

S A R A D C であって：

コンパレータに接続された出力を有する容量性再配分デジタルアナログコンバータ ( C a p D A C ) ；

S A R A D C 入力信号の反復的なサンプリングを制御し、コンパレータの出力をモニターする S A R ロジック；

入力電圧スケーリングネットワークであって、そのネットワークにおいて入力電圧が選択された一つまたは二つ以上のサンプリングキャパシターにサンプリングされ S A R A D C の特徴的なダイナミックレンジに実質的に適合するように入力電圧がスケーリングされる、前記入力電圧スケーリングネットワーク；および30

入力電圧を選択的に C a p D A C アレーの一つまたは二つ以上のキャパシターにサンプリングする、入力電圧と容量性再配分 D A Cとの間に挿入された複数のハイボルテージサンプリングスイッチを含む入力電圧と容量性再配分 D A Cとの間に挿入されたネットワークを含む、前記 S A R A D C 。

**【請求項 11】**

容量性再配分 D A C が入力電圧スケーリングネットワークの少なくとも一部を形成する、請求項 10 に記載の S A R A D C 。

**【請求項 12】**

入力電圧のサンプリングのために C a p D A C の一つまたは二つ以上の要素を選択するレンジデコーダーロジックをさらに含む、請求項 10 に記載の S A R A D C 。40

**【請求項 13】**

入力電圧レンジがバイポーラである、請求項 12 に記載の S A R A D C 。

**【請求項 14】**

ロー・ボルテージからハイボルテージへのレベルシフターのネットワークが制御信号をハイボルテージサンプリングスイッチに接続する、請求項 11 に記載の S A R A D C 。

**【請求項 15】**

レンジデコーダーロジックが関連するレンジレジスタに書き込まれたレンジ選択制御ワードに応答する、請求項 12 に記載の S A R A D C 。

**【請求項 16】**

レンジレジスタがデジタル通信インターフェイスを通じてプログラム可能である、請求50

項 15 に記載の S A R A D C。

【請求項 17】

デジタル通信インターフェイスがシリアル通信インターフェイスである、請求項 16 に記載の S A R A D C。

【請求項 18】

シリアル通信インターフェイスが双方向である、請求項 17 に記載の S A R A D C。

【請求項 19】

S A R A D C であって：

コンパレータに接続された出力を有する容量性再配分デジタルアナログコンバータ (C a p D A C)；

S A R A D C 入力信号の反復的なサンプリングを制御し、コンパレータの出力をモニターする S A R ロジック；

入力電圧スケーリングネットワークであって、そのネットワークにおいて入力電圧が選択された一つまたは二つ以上のサンプリングキャパシターにサンプリングされ、S A R A D C の特徴的なダイナミックレンジに適合するように入力電圧がスケーリングされる、前記入力電圧スケーリングネットワーク；

入力電圧を選択的に C a p D A C アレーの一つまたは二つ以上のキャパシターにサンプリングするために、複数のハイボルテージサンプリングスイッチを含む入力電圧と容量性再配分 D A Cとの間に挿入されたネットワーク；

ハイボルテージサンプリングスイッチのネットワークを前記一つまたは二つ以上のサンプリングキャパシターを選択するように制御するレンジデコーダーロジック；および

レンジデコーダーロジックがレンジ選択制御ワードに応答し、該レンジ選択制御ワードを書き込むためのレンジレジスタ

を含む、前記 S A R A D C。

【請求項 20】

レンジレジスタがインテグラルデジタル通信インターフェイスを通じてプログラム可能である、請求項 19 に記載の S A R A D C。

【請求項 21】

デジタル通信インターフェイスはシリアル通信インターフェイスである、請求項 20 に記載の S A R A D C。

【請求項 22】

C a p D A C は入力電圧スケーリングネットワークの少なくとも一部を構成し、入力電圧は C a p D A C の一つまたは二つ以上の選択されたサンプリングキャパシターにサンプリングされて S A R A D C の特徴的なダイナミックレンジに実質的に適合するように入力電圧スケーリングされる、請求項 19 に記載の S A R A D C。

【請求項 23】

入力電圧スケーリングネットワークが C a p D A C から独立したサンプリングキャパシターのネットワークを含む、請求項 19 に記載の S A R A D C。

【請求項 24】

入力電圧レンジがバイポーラである、請求項 19 に記載の S A R A D C。

【発明の詳細な説明】

【発明の詳細な説明】

【0 0 0 1】

発明の分野

本発明は一般的にアナログ入力信号のスケーリングに関し、特にバイポーラとユニポーラの入力信号の両方を、取得および変換の前に A D C のダイナミックレンジにスケーリングすることに関する。より詳細には、サンプリングキャパシターの選択された組み合わせに対して、ハイボルテージ伝送ゲートを通じてアナログ入力信号をサンプリングし、S A R (逐次比較型) A D C の入力レンジをプログラムすることに関する。

【0 0 0 2】

10

20

30

40

50

発明の背景

多入力、ワイドダイナミックレンジのバイポーラおよびユニポーラの逐次比較型アナログデジタルコンバータ（A D C）は伝統的にアナログ入力についてレジスタデバイダネットワークを使用し、取得および変換が実行される前に、入力信号をコンバータのダイナミックレンジにスケーリングする。従来、A D Cによる変換の前に入力信号を減衰させる方法はうまく利用してきた。しかし、それは多くの明らかな不都合がある。

## 【0003】

第一に、伝統的なレジスタデバイダの方法では、アナログ入力ソースは常にグラウンドまたはある参照電圧に対する負荷抵抗（resistive load）を見なくてはならない。ソースはこの負荷を移動させることができなければならない。第二に、レジスタデバイダネットワークは内部基準（internal reference）および外部入力ソースの両方から電力を消費する。第三の問題は、この従来技術では、許容されたアナログ入力レンジをプログラムする簡単な方法を使用者に提供できることである。第四の不都合は、入力レジスタの大きさがコンバーターのフルパワー帯域幅（full power bandwidth）によって制限されるという事実である。

## 【0004】

レジスタデバイダを形成するレジスタネットワークのノードは集積回路（IC）のピンを通じて使用者がアクセスできるように作ることができる。これで、使用者はハードウェアの接続を通じてレジスタデバイダネットワークを要求されるアナログ入力レンジに適するように設定する事ができる。しかしながら、使用者がレンジを変更したい場合には、ハードウェアを再度接続しなければならない。

## 【0005】

従って、集積回路のアプリケーションに容易に適応でき、入力信号に負荷抵抗をグラウンドへ移動させることを要求せず、電力消費を最小化し、アナログ入力電圧のレンジの修正が要求されるようなイベントにおいて容易にプログラム可能な、アナログ入力電圧のスケーリング技術の需要が生じる。

## 【0006】

発明の概要

これらおよびそのほかの需要は、本発明のプログラム可能な入力電圧レンジシステムおよび方法によって満足される。そこでは、スプリットゲートオキサイドプロセスが、標準的なサブミクロンの5ボルトC M O Sデバイスとして、同一のシリコン基板上のハイボルテージ（±15ボルト）スイッチの使用を可能にする。このプロセスによって、アナログ入力電圧は、事前減衰回路を用いることなく、直接サンプリングキャパシターにサンプリングされる。サンプリングキャパシターの既定の比率によってサンプリングすることのみによって、アナログ入力はS A R（逐次比較型レジスタ）A D Cそれ自体のダイナミックレンジに適応するようにスケーリングないしは減衰される。

## 【0007】

本発明のシステムにおいて、サンプリングキャパシターはS A R A D Cそれ自体に使われている実際の容量性再配分デジタルアナログコンバータ（C a p D A C : capacitive redistribution digital-to-analog converter）または独立したキャパシターアレーとすることができる。C a p D A Cまたは独立したアレーのどのビットにサンプリングするかを選択する事で、入力レンジをプログラムすることができる。一度アナログ入力信号がS A Rコンバータのダイナミックレンジに適応するよう減衰されると、入力信号をデジタルワードに変換するために伝統的なS A R技術を使用することができる。

## 【0008】

これによって、伝統的な方法の問題点のうちの多くは克服される。アナログソースはグラウンドに対する負荷抵抗ではなく、容量性電荷（capacitive load）を見ており、それゆえ、ソースにD C電力を要求しない。第二に、レジスタデバイダネットワークをバイアスする際にさらなる電力を消費しない。最後に、容量性再配分D A Cまたは独立したアレーのどのビットにサンプリングするかを選択する事で、ソフトウェアを通じて入力レン

10

20

30

40

50

ジをプログラムすることができる。

【0009】

本発明の一側面に従って、入力電圧レンジがプログラム可能なアナログデジタルコンバータは、特徴的なダイナミックレンジを有する逐次比較型アナログデジタルコンバータ（S A R A D C）および入力電圧のスケーリングネットワーク含み、入力電圧のスケーリングネットワーク内では、入力電圧が一つまたは二つ以上のサンプリングキャパシターにサンプリングされて、入力電圧を S A R A D C の特徴的なダイナミックレンジに適合するようにスケーリングをする。

【0010】

レンジデコーダーロジックが入力電圧スケーリングネットワークの一つまたは二つ以上の入力電圧がサンプリングされる要素を選択するように、ハイボルテージのサンプリングスイッチのネットワークは入力電圧と入力電圧スケーリングネットワークの間に挿入しても良い。入力電圧のレンジはバイポーラでも良い。

10

【0011】

本発明の他の形態では、ローボルテージからハイボルテージへのレベルシフターのネットワークは制御信号をハイボルテージサンプリングスイッチに接続する。好ましくは、レンジデコーダーロジックは関連するレンジレジスタに書き込まれたレンジ選択制御ワードに応答する。レンジレジスタはデジタル通信インターフェイス（digital communication interface）を通じてプログラム可能としても良い。デジタル通信インターフェイスは、シリアルであって、使用者によってレンジレジスタの両プログラミングを適応させるために双方向通信インターフェイスであって、S A R A D C それ自体の他の関数をプログラムするためであると同時に検証のためにレジスタのコンテンツのリードバックがあることが好ましい。

20

【0012】

本発明の他の側面に従って、S A R A D C は、コンパレータに接続された出力、A D C 入力信号の反復的なサンプリングを制御し、コンパレータの出力をモニターする S A R ロジック、

入力電圧スケーリングネットワークであって、該ネットワークでは、入力電圧が一つまたは二つ以上の選択されたサンプリングキャパシターにサンプリングされて入力電圧を S A R A D C の特徴的なダイナミックレンジに適合するようにスケーリングをする、前記入力電圧スケーリングネットワーク、

30

入力電圧が一つまたは二つ以上のサンプリングキャパシターに選択的にサンプリングされるように、入力電圧と入力電圧スケーリングネットワークの間に挿入されたハイボルテージサンプリングスイッチのネットワーク、

ハイボルテージサンプリングスイッチのネットワークを一つまたは二つ以上のサンプリングキャパシターを選択するように制御するレンジデコーダーロジック、およびレンジデコーダーロジックがレンジ選択制御ワードに応答し、該レンジ選択制御ワードを書き込むためのレンジレジスタ

を有する逐次比較型アナログデジタルコンバータ（S A R A D C）を含む。

40

【0013】

C a p D A C は入力電圧スケーリングネットワークの少なくとも一部を構成しても良く、入力電圧はC a p D A C の一つまたは二つ以上の選択されたサンプリングキャパシターにサンプリングされて、S A R A D C の特徴的なダイナミックレンジに実質的に適合するように入力電圧がスケーリングされても良い。別法では、入力電圧スケーリングネットワークは、C a p D A C のアレーから独立したサンプリングキャパシターのネットワークを含んでもよい。

【0014】

本発明のさらなる目的、特徴、および利点は、以下の説明および図面により明らかになるであろう。

50

## 【0015】

発明の詳細な説明

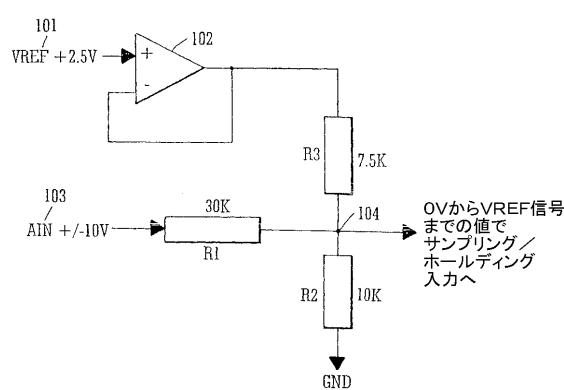

先行技術に比して明らかな利点を提供する入力レンジがプログラム可能なSAR(逐次比較型)ADCをここに記述する。図1は、ワイドレンジのバイポーラおよびユニポーラのアナログ入力信号を変換の前に減衰させる、従来の方法を示す。この例では+2.5ボルトとなっている参照電圧Vrefがバッファ102に入力として適用される。バッファされた参照電圧は、抵抗R1、R2、R3からなるレジスタデバイダーの上端に適用される。

## 【0016】

この例示回路では-10ボルトから+10ボルトの間のレンジとなっているアナログ入力信号Ainが、ボルテージデバイダー入力103に適用される。参照電圧Vrefは、デバイダーネットワークが入力信号をスケーリングおよびレベルシフトした結果と共に、ボルテージデバイダーのバイアス電圧として機能する。アナログ入力電圧は、-10ボルトから+10ボルトまで変化するので、コモンノード104において0ボルトから+2.5ボルトまでの変動を生み出す。

そのスケーリングされた出力電圧と共に、一般的にSARADCのサンプリング/ホールディング入力に連結するのが、この出力ノード104である。本先行技術のネットワークにおいてアナログ入力信号Ainはグラウンドに対して40k(キロオーム)の印加をしなければならないことに留意すべきである。

## 【0017】

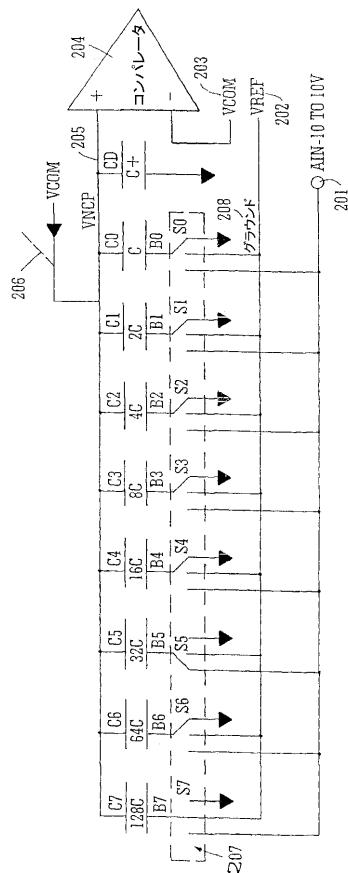

図2は、本発明の原理に従って8ビットのCapDACアレーにサンプリングされたバイポーラ(±10ボルト)のアナログ入力信号を示す。アナログ入力信号のスイッチは±15ボルトのスイッチであって、バイポーラの入力信号を直接サンプリングすることができる。以下にスイッチについてより詳細に記載する。

## 【0018】

図2に関連して、コンパレータおよび全てのSARロジックは5ボルトのサブミクロンのCMOSテクノロジーにより導入できることに留意すべきである。アナログ入力スイッチだけは、より高いゲート電圧を扱うためにより厚いオキサイドゲートを用いる±15ボルトのCMOSデバイスを用いて作られる必要がある。

## 【0019】

±10ボルトの入力レンジのサンプリング中の電荷の等式は、

$$Q_{ncp} = C_{tot} * \{ -Ain * (32C / 256C) + V_{com} \} = C_{tot} * V_n \quad (1)$$

であり、ここで、

$$C_{tot} = 256C$$

である。

すなわち、サンプリングされたアナログ入力電圧は、

$$V_{ncp} = -Ain / 8 + V_{com} \quad (2)$$

となる。

## 【0020】

$V_{com}$ が1.25ボルトである場合には、±10ボルトのレンジ内のあらゆるアナログ入力電圧に対して、サンプリングされたアナログ入力が0ボルトから2.5ボルトの間である。参照電圧が2.5ボルトである場合には、アナログ入力はコンバータのダイナミックレンジ内に保たれ、バイポーラの入力信号は通常のSAR技術を用いて変換できる。

## 【0021】

入力レンジをプログラムするために、単にCapDACアレーのどのビットをサンプリングするかを選択すればよい。8ビットの例が以下の表1に示される。

10

20

30

40

【表1】

| 入力レンジ       | 最上位ビット<br><b>B7</b> | <b>B6</b> | <b>B5</b> | <b>B4</b> | <b>B3</b> | <b>B2</b> | <b>B1</b> | 最下位ビット<br><b>B0</b> | サンプリング後の<br><b>V<sub>nep</sub></b> |

|-------------|---------------------|-----------|-----------|-----------|-----------|-----------|-----------|---------------------|------------------------------------|

| ±10 volts   | Vref                | GND       | Ain       | GND       | GND       | GND       | GND       | GND                 | -Ain/8 + V <sub>com</sub>          |

| ±5 volts    | Vref                | Ain       | GND       | GND       | GND       | GND       | GND       | GND                 | -Ain/4 + V <sub>com</sub>          |

| ±2.5 volts  | Vref                | Ain                 | -Ain/2 + V <sub>com</sub>          |

| 0 to + 10 v | GND                 | Ain       | GND       | GND       | GND       | GND       | GND       | GND                 | -Ain/4 + V <sub>com</sub>          |

| 0 to + 5 v  | GND                 | Ain                 | -Ain/2 + V <sub>com</sub>          |

| 0 to +2.5 v | Ain                 | Ain       | Ain       | Ain       | Ain       | Ain       | Ain       | Ain                 | -Ain + V <sub>com</sub>            |

10

【0022】

この例では、レンジを選択するために必要とされるのは3ビットのみである：一つの極性ビット（polarity bit）（入力信号がバイポーラかユニポーラかを示す）と二つのレンジビットである。以下の表2に種々の入力レンジにおける選択されるビット値を示す。

【表2】

| 入力レンジ       | 極性ビット | レンジビット1 | レンジビット0 |

|-------------|-------|---------|---------|

| ±10 volts   | High  | Low     | Low     |

| ±5 volts    | High  | Low     | High    |

| ±2.5 volts  | High  | High    | High    |

| 0 to + 10 v | Low   | Low     | Low     |

| 0 to + 5 v  | Low   | Low     | High    |

| 0 to +2.5 v | Low   | High    | High    |

20

【0023】

バイポーラの信号に対しては最上位ビット（極性ビット）はサンプリング中参照電圧に保持されることに留意すべきである。その理由は本説明により後に明らかとなるであろう。

【0024】

上述のように、図2は、バイナリーの重み付けをされたキャパシターC<sub>7</sub> ~ C<sub>0</sub>およびコンパレータ204に最も近い部分に備えられた「ダミー」キャパシター（すなわち終端キャパシター）C<sub>D</sub>を含んでなる容量性再配分DAC、すなわちCapDACを示す。C<sub>D</sub>の値は最下位ビットキャパシターC<sub>0</sub>の電気容量と実質的に等しい。図2の回路において、終端キャパシターはアナログ入力をサンプリングしないが、グラウンドに保持されてオフセットを最小化する。図2の8ビットキャパシターアレーは例示の形態である。アレーの総電気容量は256Cであり、ここでCは記載の態様における単位電気容量である。

30

【0025】

この典型的な態様では、最上位ビットB7はスイッチS7によってサンプリング中参照電圧に接続される。スイッチ7は以下でさらに議論するアナログスイッチのアレーの一部である。上位第3位ビットB5はスイッチS5を通じてアナログ入力電圧201に接続される。サンプリング期間が完了するとアナログ入力により累積された電荷は、S5をグラウンドにスイッチすることによってキャパシターアレーのトッププレートに運ばれる。サンプリングキャパシターの全電荷を保存するために、コモンモードスイッチ206が最初に開く。

40

【0026】

従ってこの例では、アナログ入力信号は8つのファクターによって減衰される。従って、+10ボルトから-10ボルトまで変化する入力信号を推定するとき、コンパレータ204は±1.25ボルトを見ている。コモンモード電圧V<sub>com</sub>が1.25ボルトである場合、入力信号はコンパレータ204のコモンモードレンジ内に保たれる。既知の逐次比較技術が入力信号をデジタル化するために使用できる。

50

## 【0027】

最上位ビットトライアルの試験は有用である。先述の通り、サンプリング中最上位ビットは  $V_{ref}$  (2.5 ボルト) に接続された。サンプリング後は、最上位ビットについて何をするのか決定がされるまで、最上位ビットは  $V_{ref}$  のままにされる。一例として、アナログ入力信号が正（例えば、+10 ボルト）であった場合、コンパレータの非反転入力の電圧 (NCP ノード 205) は上記の式(2)で、 $-Ain/8 + V_{com}$  と与えられる。コモンモード電圧  $V_{com}$  が +1.25 ボルトの場合、 $V_{ncp} = 0$  ボルトである。コンパレータ 204 の出力はロジックローレベルになる。

## 【0028】

NCP ノードをコモンモード電圧に収束させることが期待される。これを達成するため 10 に、最上位ビットが  $V_{ref}$  に接続されたままにされる。この部分をグラウンドに切り換えると負電荷がキャパシターアレーのトッププレートに運ばれて NCP 電圧がコモンモード電圧から離れる原因となるからである。ロジックは入力がバイポーラであると判断するであろうから、SAR ロジックはこのような状況下で出力データの第一ビットをロジック 1 に設定するように構成することができる。

## 【0029】

上位第 2 位ビット B6 のトライアルはスイッチ S6 を用いて B6 をグラウンドから  $V_{ref}$  に切り換えることによって開始される。これによって  $V_{ref}/4$  と重み付けられた正電荷がキャパシターアレーのトッププレートに運ばれる。これにより NCP 電圧 20 5 の等式は、 20

$$V_{ncp} = -Ain/8 + V_{com} + V_{ref}/4 \quad (3)$$

となる。

## 【0030】

この例ではサンプリングされたアナログ入力信号は +10 ボルトだったので、コモンモード電圧は +1.25 ボルトであり、参照電圧が +2.5 ボルトであるので、NCP ノード 205 における電圧は 0.625 ボルトである。コンパレータ出力は依然としてロジックローであるが、NCP 電圧はコモンモード電圧に収束し始めている。従って、上位 2 番目のビット B6 は  $V_{ref}$  に接続されたままになる。SAR ロジックはこれをロジック 1 であると解釈し、出力データの二番目のビットを 1 に設定する。8 ビット全てがテストされるまで残りのビットのトライアルも同様に行われ、NPC ノード 205 はコモンノード電圧から最下位ビット 1 つ分以内になる。 30

## 【0031】

アナログ入力電圧が負であるイベントでは逆のことが起こる。アナログ入力信号として -10 ボルトの入力電圧が適用された場合、上記の等式(2)は NCP ノード電圧が 2.5 ボルトであることを示す。コンパレータ出力はロジックハイとなり、SAR ロジックはこれを解釈し、最上位ビット (MSB) を  $V_{ref}$  からグラウンドに切り換え、出力データの第一のビットをロジック 0 に設定する。上位 2 番目のビットのトライアルでは、B6 は  $V_{ref}$  に切れ替えられ、NCP ノードは +1.875 ボルトになり、コンパレータアウトプットはロジックハイのままである。SAR ロジックはグラウンドへ切り換えることでこれを拒否する。従って、SAR プロセスは NCP ノードがコモンモード電圧に収束するまで続けられる。ビットトライアル中の NCP 電圧の等式は以下のように与えられる： 40

## 【0032】

## 【化1】

$$V_{ncp} = -Ain/8 + V_{com} + [-B7 * (Vref/2) + B6 * (Vref/4) + K + B0 * (Vref/256)]$$

## 【0033】

$V_{ref}/2$  の項（最上位ビット）は負号を有しビット 7 の論理補数 (inverse) を乗じる。これは、 $V_{ref}/2$  の項は B7 がロジック 0 のとき（すなわち、実際のアナログ入力電圧が負の極性の場合）にのみ含まれるからである。従って、最上位ビットは符号 50

ビットのように振る舞う。

**【0034】**

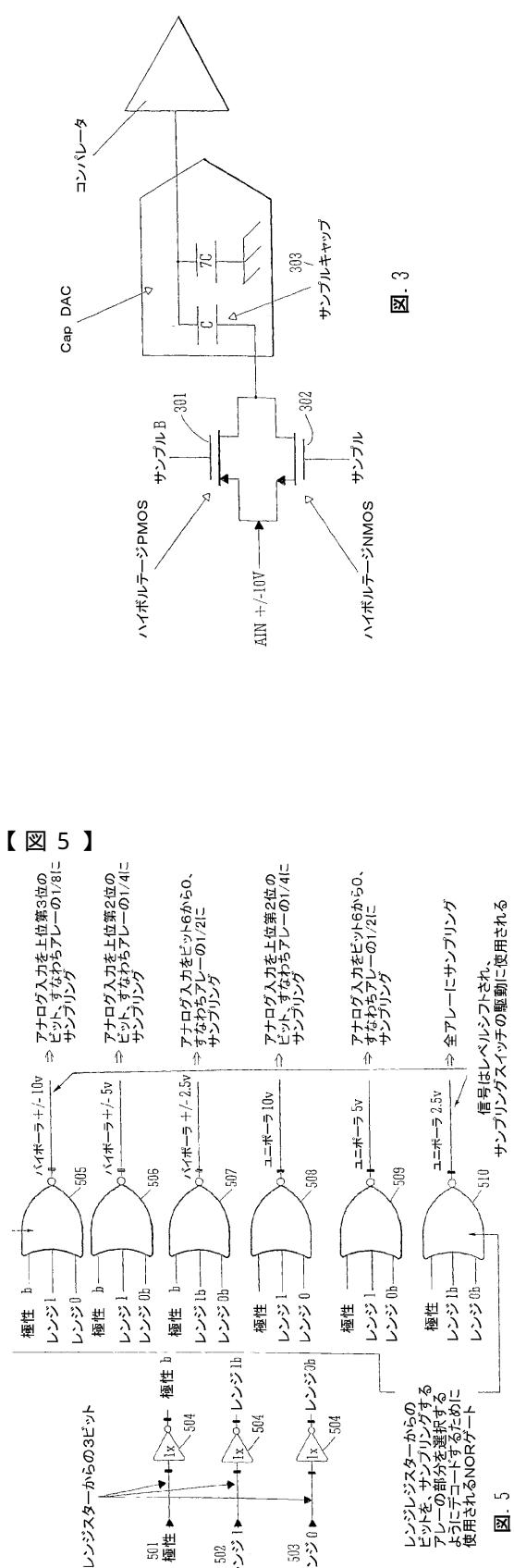

図3は、本発明の使用に適したスイッチング配置の略図である。アナログ入力信号を-10ボルトから+10ボルトの範囲に適応させるために、トランスマッシュゲートが一組の平行な関連するハイボルテージPMOS301およびNMOS302から形成される。好ましくは、図示のデバイスはあらゆる端末間の30ボルトの変動に耐え、±10ボルトのレンジを扱う際に適切なマージンを提供する。ハイボルテージデバイス301、302はアナログ入力信号を取得しサンプリングキャパシター303に直接切り換える。もちろん、ハイボルテージ制御信号はハイボルテージトランジスター301、302のゲートとして要求されるが、これらの制御信号は5ボルトのCMOSレベルからの単純なレベルシフトによって提供されうる。10

**【0035】**

図4は本発明に従ってプログラム可能な入力レンジの特徴を取り入れたSARADCの全体のブロック図であり、一般的に図番400で示される。アナログ入力信号401が、ハイボルテージスイッチ402を通じてCapDACアレーの一つまたは二つ以上のキャパシターに適用される。信号の取得および変換をも制御するSARロジック406は、入力信号がサンプリングされたCapDACアレーのキャパシターを制御する。

**【0036】**

SARロジック406は、レンジプログラミング入力をレンジレジスタ409から受け取るレンジデコーダーロジック407に基づいてこれを実行する。レンジデコーダーロジック407については後にさらに詳細に述べる。当面、レンジレジスタ409の内容は既知のシリアルポート上のレジスタに書き込むことで変化し得る点に留意すれば足りる。レンジレジスタ409へのアクセスを使用者に許可することで、SARADC400のレンジのソフトウェアによるプログラム能力が備えられる。20

**【0037】**

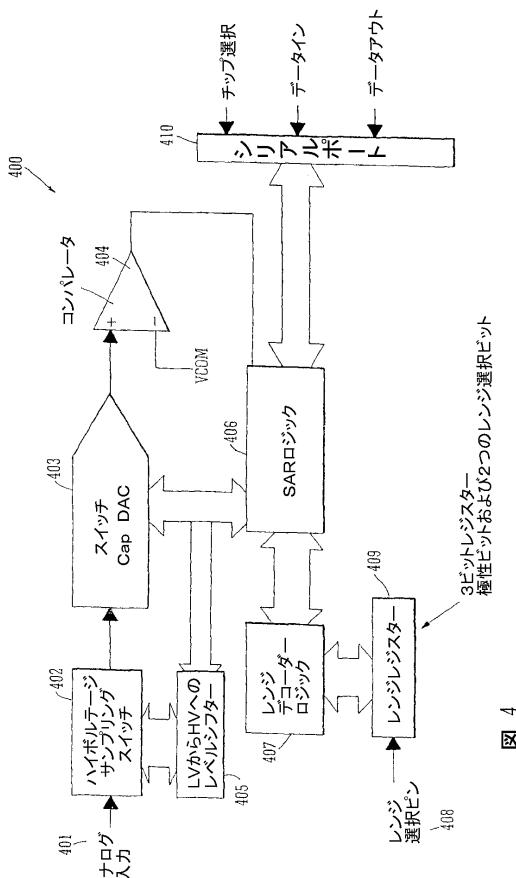

図5はレンジデコーダーロジックの詳細を提供する。もちろん、多数のロジック装置がこの用途を満足させる。図5の装置は、単にSARADCに対する適切なレンジの設定を生成する十分な方法の一つである。SARADCのレンジを制御する三つの入力信号がある。これらは極性ビット501、レンジ1ビット502、レンジ0ビット503である。これらはそれぞれインバーター504に適用され、信号およびその論理補数はデコーダセクションに入手可能となる。30

**【0038】**

デコーダーそれ自体は、入力信号とその論理補数という独自の組み合わせが適用されるNORゲートのアレーである。例えば、アナログ入力信号がバイポーラであって予想される電圧が-10ボルトと+10ボルトの間であるイベント時には、レンジ1およびレンジ2ビットと共に極性ビット501の補数がNORゲート505に適用される。説明したように、適切なスケーリングのためにこのケースでは上位3番目のビットに入力信号がサンプリングされる。制御ビットの独自の組み合わせは異なるNORゲートの入力としてマッピングされ、ソフトウェアプログラミングを通じてSARADCの六つの異なる入力レンジを選択し得る。40

**【0039】**

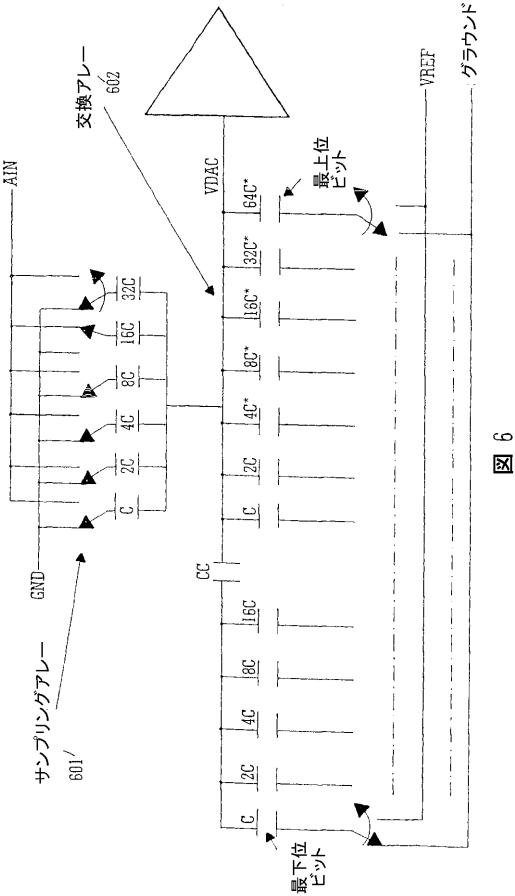

図6は本発明の他の態様を示し、この態様では、CapDACの変換アレー602の選択されたキャパシターに直接サンプリングする代わりに、アナログ入力信号は分離したサンプルアレー601にサンプリングされる。この装置では、選択ロジックは、SARADCのレンジをプログラムするために、サンプルアレー601の一つまたは二つ以上の要素を選択する。本構成の主要な利点は必要とされるハイボルテージスイッチの数を大幅に減らすことである。期待されるとおり、分離したサンプリングアレーを使う場合には、関連するダイエリアを省くことにもなる。

**【0040】**

従来技術に比して明らかな有利な効果を提供する入力レンジがプログラム可能なSAR50

A D Cについてここに説明した。本発明の精神および範囲から離れることなく変更が成されうることを当業者は理解するであろう。したがって、本発明が添付の請求の範囲によつて必要とされるものを超えて限定されることを意図するものではない。

**【図面の簡単な説明】**

**【0041】**

**【図1】**アナログ入力信号を変換の前に減衰させるために使用される、従来のレジスタデバイダー回路を示す図である。

**【図2】**本発明の原理に従つてCap DACアレーにサンプリングされたバイポーラのアナログ入力信号を示す図である。

**【図3】**本発明の使用に適したスイッチングトランジスター配置の略図である。 10

**【図4】**本発明の原理を取り入れた逐次比較型A D Cの全体のブロック図である。

**【図5】**本発明と共に使用するのに適したレンジデコーダーロジックを示す図である。

**【図6】**本発明の他の態様に従つた、変換アレーから分離したサンプルアレーを示す図である。

**【図1】**

**図.1

従来技術**

**【図2】**

**図.2**

【 义 3 】

【図4】

四

【図6】

---

フロントページの続き

(56)参考文献 特開昭57-005428(JP,A)

欧州特許出願公開第00935195(EP,A1)

特開昭61-077430(JP,A)

特開平03-048528(JP,A)

特表2001-517415(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03M 1/00-1/88