(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-26265

(P2013-26265A)

(43) 公開日 平成25年2月4日(2013.2.4)

| (51) Int.Cl.                  | F 1         | テーマコード (参考) |

|-------------------------------|-------------|-------------|

| <b>HO1L 21/3065 (2006.01)</b> | HO1L 21/302 | 102 4M118   |

| <b>HO1L 21/304 (2006.01)</b>  | HO1L 21/304 | 645C 5FO04  |

| <b>HO1L 27/146 (2006.01)</b>  | HO1L 27/14  | A 5F140     |

| <b>HO1L 21/336 (2006.01)</b>  | HO1L 29/78  | 301F 5F157  |

| <b>HO1L 29/78 (2006.01)</b>   |             |             |

審査請求 未請求 請求項の数 10 O L (全 20 頁)

|           |                              |            |                                                                                            |

|-----------|------------------------------|------------|--------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2011-156533 (P2011-156533) | (71) 出願人   | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号                                                     |

| (22) 出願日  | 平成23年7月15日 (2011.7.15)       | (74) 代理人   | 110000925<br>特許業務法人信友国際特許事務所                                                               |

|           |                              | (72) 発明者   | 久保井 信行<br>東京都港区港南1丁目7番1号 ソニー株式会社内                                                          |

|           |                              | (72) 発明者   | 深澤 正永<br>東京都港区港南1丁目7番1号 ソニー株式会社内                                                           |

|           |                              | F ターム (参考) | 4M118 AA05 AB01 BA09 CA02 EA20<br>FA06<br>5F004 AA14 DA15 DA16 DA22 DA23<br>DA25 DB01 DB03 |

|           |                              |            | 最終頁に続く                                                                                     |

(54) 【発明の名称】 プラズマ処理方法、プラズマ処理装置、及び、半導体装置の製造方法

## (57) 【要約】 (修正有)

【課題】結晶欠陥および金属汚染低減が可能な半導体基体の処理方法、そのための装置、また、それを用いた半導体装置の製造方法を提供する。

【解決手段】CとNとを含む混合ガスをプラズマ化してCN活性種を生成し、生成したCN活性種により半導体基体11の半導体層の表面を処理する。特に、前記処理としては、前記半導体基体11の表面の半導体層を前記CN活性種によりパッシベートすることを含む。さらに、そのことにより、表面汚染金属および半導体中の欠陥を除去する。

【選択図】図1

A

B

C

## 【特許請求の範囲】

## 【請求項 1】

C と N とを含む混合ガスをプラズマ化して CN 活性種を生成し、生成した前記 CN 活性種により半導体基体の表面を処理する

プラズマ処理方法。

## 【請求項 2】

前記半導体基体の表面の半導体層を前記 CN 活性種によりパッシベートする請求項 1 に記載のプラズマ処理方法。

## 【請求項 3】

C HF<sub>3</sub>、CH<sub>2</sub>F<sub>2</sub>、C<sub>4</sub>F<sub>8</sub>、C<sub>5</sub>F<sub>8</sub>、CO、C<sub>2</sub>H<sub>5</sub>OH 及び CH<sub>3</sub>OH から選ばれる少なくとも 1 種類以上を含む前記混合ガスを用いる請求項 1 に記載のプラズマ処理方法。 10

## 【請求項 4】

半導体基体に加えるバイアスパワーが 0 W 以上 50 W 以下である請求項 1 に記載のプラズマ処理方法。

## 【請求項 5】

前記プラズマ化する際のトップパワーが 1000 W 以上 2000 W 以下である請求項 1 に記載のプラズマ処理方法。

## 【請求項 6】

前記 CN 活性種により前記半導体基体を処理した後、前記半導体基体上に堆積したポリマー層を薬液により除去する請求項 1 に記載のプラズマ処理方法。 20

## 【請求項 7】

C と N とを含む混合ガスをプラズマ化して CN 活性種を生成し、生成した前記 CN 活性種により半導体基体の表面を処理するプラズマ処理工程と、

前記半導体基体に半導体素子を形成する工程と、を有する

半導体装置の製造方法。

## 【請求項 8】

C と N とを含む混合ガスをプラズマ化し、生成した CN 活性種により半導体基体の表面を処理するプラズマ処理部を備える

プラズマ処理装置。 30

## 【請求項 9】

前記プラズマ処理部は、前記 CN 活性種を生成するプラズマ処理条件のレシピを含むソフトウェアを備える請求項 8 に記載のプラズマ処理装置。

## 【請求項 10】

前記プラズマ処理部は、CN ガスの除去装置を備える請求項 8 に記載のプラズマ処理装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本技術は、半導体基体のプラズマ処理方法、及び、プラズマ処理装置、並びに、半導体装置の製造方法に係わる。 40

## 【背景技術】

## 【0002】

半導体製造において、半導体基体の結晶欠陥や加工中に生じる金属汚染は、装置特性の劣化に大きな影響を与えることが一般に知られている。例えば、MOS (Metal Oxide Semiconductor) や CCD (Charge Coupled Device)、CMOS (Complementary Metal Oxide Semiconductor) イメージングセンサにおける白点・暗電流等の発生が知られている。また、RTS (Random Telegraph Signal noise)、ゲート I-V 特性、さらには太陽電池の変換効率やレーザー出力特性等の装置特性の劣化が知られている。このような、半導体基体の欠陥、汚染をいかに低減するかが半導体装置の製造上の大きな課題の一つとな

10

20

30

40

50

っている。

【0003】

近年、HCN溶液中に存在するCN<sup>-</sup>（シアノイオン）を用いて、半導体基体の結晶欠陥や金属汚染を大きく低減する有用な手法が提案されている（特許文献1、特許文献2参照）。この手法ではCN<sup>-</sup>を半導体基体表面及び基体中に存在する金属や結晶欠陥（ダングリングボンド）と選択的に反応させる。そして、安定錯体を形成して金属を除去する、或いは、ダングリングボンドと結合を形成し欠陥をパッシベートする。この手法では、室温で十分な反応がおこる。また、紫外線や800程度の高熱にも非常に耐性があることが知られている。

【0004】

HCN溶液を用いる方法では、HCNの強い毒性のため、薬液処理の観点から現状の生産ラインでの使用は非常に困難である。このため、触媒を用いてメタンとアンモニアからHCNを生成し、HCN使用後は紫外線照射及びオゾン水処理により炭酸ガスと窒素に無毒化・分解する方法が提案されている（特許文献3参照）。

【0005】

このように、HCNを用いた処理方法は、結晶欠陥および金属汚染低減に対して非常に有効であると考えられている。例えば、シリコン太陽電池に実験レベルで適用され、実際に効率が大きく向上することが報告されている（非特許文献1参照）。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平10-74753号公報

【特許文献2】特開2005-33038号公報

【特許文献3】特開2008-729号公報

【非特許文献】

【0007】

【非特許文献1】O. Maida, A. Asano, M. Takahashi, H. Iwasa, H. Kobayashi, Surf. Sci. 542 (2003) 244

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、上述のHCNを用いる手法を生産ラインで用いるには、専用の新規処理装置の製造がともない、現実的ではない。

【0009】

本技術においては、結晶欠陥及び金属汚染を低減することが可能な半導体基体の処理方法を提供するものである。

【課題を解決するための手段】

【0010】

本技術のプラズマ処理方法は、CとNとを含む混合ガスをプラズマ化してCN活性種を生成し、生成したCN活性種により半導体基体の表面を処理する。

また、本技術の半導体装置の製造方法は、上記プラズマ処理された半導体基体に半導体素子を形成する工程を有する。

【0011】

また、本技術のプラズマ処理装置は、CとNとを含む混合ガスをプラズマ化し、生成したCN活性種により半導体基体の表面を処理するプラズマ処理部を備える。

【0012】

上述のプラズマ処理方法及びプラズマ処理装置によれば、毒性の高いHCN溶液やHCNガスを用いることなく、従来の半導体製造工程で用いられているプラズマ処理工程に適用することで、半導体基体の結晶欠陥の修復や金属汚染の除去が可能である。このため、結晶欠陥及び金属汚染に起因する各種装置特性の劣化を抑制した半導体装置を製造するこ

10

20

30

40

50

とができる。

【発明の効果】

【0013】

本技術によれば、結晶欠陥及び金属汚染を低減することが可能な半導体基体の処理方法を提供することができる。

【図面の簡単な説明】

【0014】

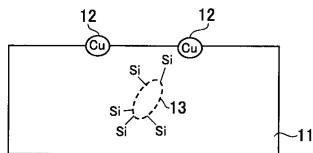

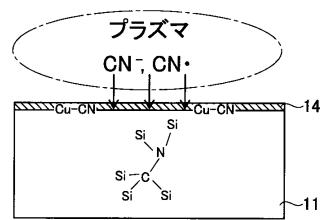

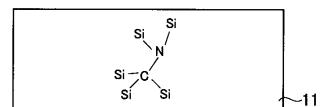

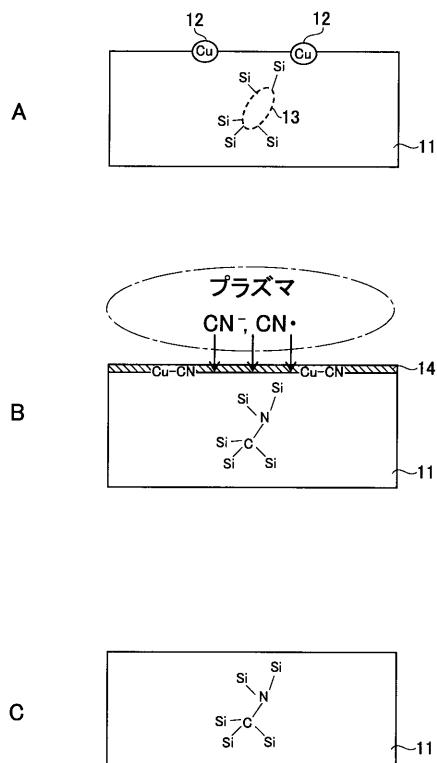

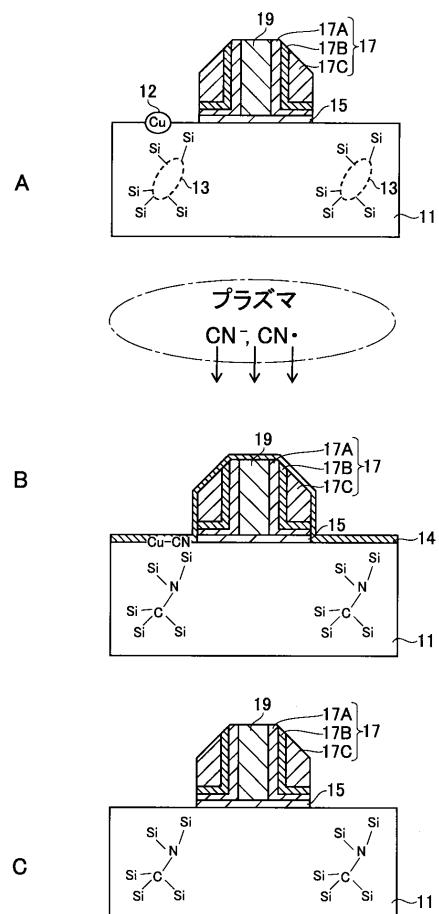

【図1】プラズマ処理方法の第1実施形態を説明する概略工程図である。

【図2】電子機器の実施の形態の構成を示す図である。

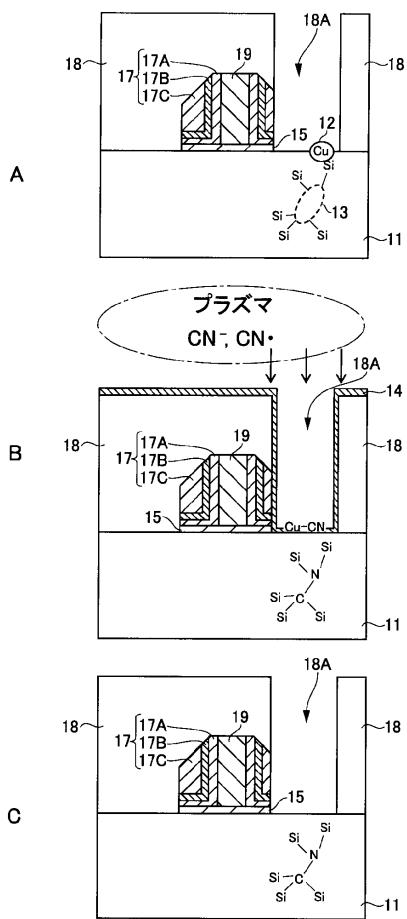

【図3】プラズマ処理方法の第2実施形態を説明する概略工程図である。

10

【図4】プラズマ処理方法の第3実施形態を説明する概略工程図である。

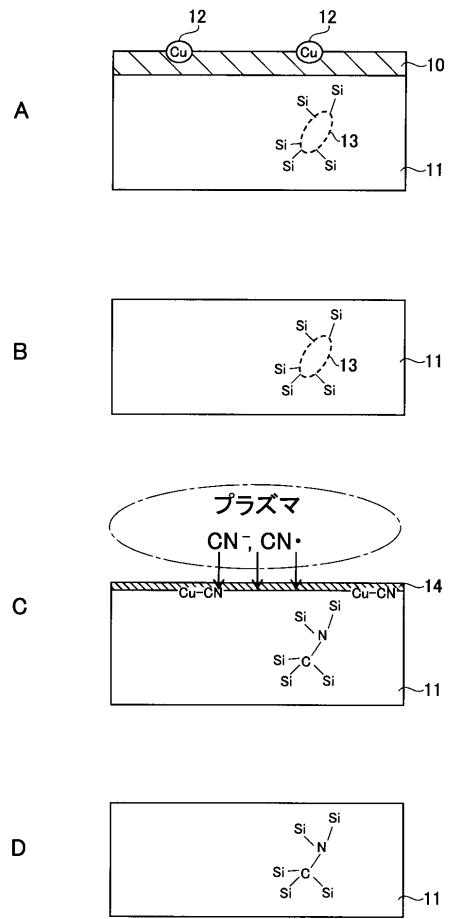

【図5】プラズマ処理方法の第4実施形態を説明する概略工程図である。

【図6】プラズマ処理方法の第5実施形態を説明する概略工程図である。

【図7】プラズマ処理方法の第6実施形態を説明する概略工程図である。

【図8】プラズマ処理方法の第7実施形態を説明する概略工程図である。

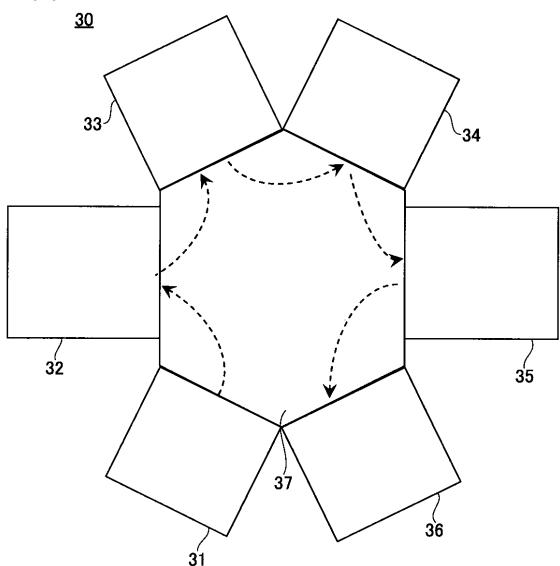

【図9】プラズマ処理装置の実施形態の構成を示す図である。

【図10】図9に示すプラズマ処理装置を用いた処理フロー図である。

【発明を実施するための形態】

【0015】

以下、本技術を実施するための最良の形態の例を説明するが、本技術は以下の例に限定されるものではない。

20

なお、説明は以下の順序で行う。

1. プラズマ処理方法の第1実施形態

2. プラズマ処理方法の第2実施形態

3. プラズマ処理方法の第3実施形態

4. プラズマ処理方法の第4実施形態

5. プラズマ処理方法の第5実施形態

6. プラズマ処理方法の第6実施形態

7. プラズマ処理方法の第7実施形態

8. プラズマ処理装置の実施形態

30

【0016】

1. プラズマ処理方法の第1実施形態

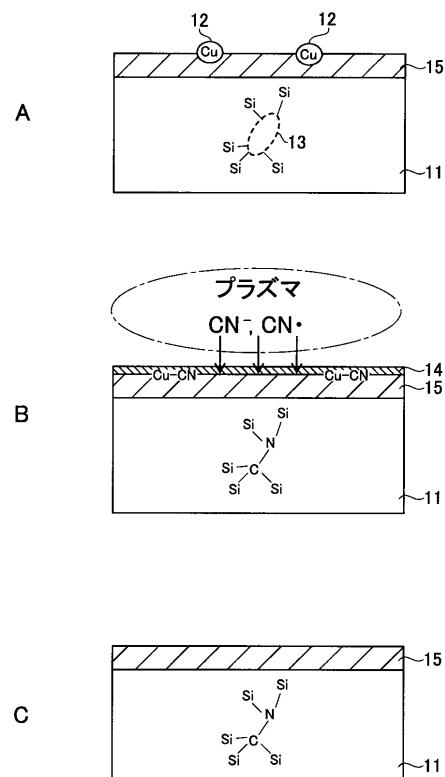

以下、プラズマ処理方法の具体的な実施の形態について説明する。図1に、本実施形態のプラズマ処理方法を説明するための概略工程図を示す。

図1Aに示すように、被処理体となる半導体基体11を準備する。半導体基体11としては、例えば、シリコン基板を準備する。半導体基体11には、汚染金属12、及び、シリコンのダングリングボンド等の結晶欠陥13が存在している。図1Aでは、半導体基体11の汚染金属12の一例としてCuを示している。

【0017】

[プラズマ処理によるCN生成]

次に、図1Bに示すように、プラズマ処理装置を用いて半導体基体11のプラズマ処理を行う。本実施形態では、C(炭素)元素とN(窒素)元素とを含む混合分子ガスを用いたプラズマ処理により、CNラジカル(CN·)やCNイオン(CN+)等のCN活性種を生成させる。

【0018】

プラズマ処理で用いる混合ガスとしては、CとNとを含む分子混合ガスであれば特に限定されない。例えば、Cを含むガスとしては、CHF<sub>3</sub>、CH<sub>2</sub>F<sub>2</sub>、C<sub>4</sub>F<sub>8</sub>、C<sub>5</sub>F<sub>8</sub>、CO、C<sub>2</sub>H<sub>5</sub>OH及びCH<sub>3</sub>OH等の半導体装置の製造工程で使用されているガスを用いることができる。Nを含むガスとしては、N<sub>2</sub>及びNH<sub>3</sub>等の半導体装置の製造工程で使用されているガスを用いることができる。さらに、上記CとNとを含む分子混合ガ

50

スの希釈用ガスとして、Arガス及びHeガスを用いてもよい。

【0019】

上記CとNとを含む分子混合ガスとしては、例えば、CHF<sub>3</sub> / N<sub>2</sub> / (Ar)、CH<sub>2</sub>F<sub>2</sub> / N<sub>2</sub> / (Ar)、C<sub>4</sub>F<sub>8</sub> / N<sub>2</sub> / (Ar)、C<sub>5</sub>F<sub>8</sub> / N<sub>2</sub> / (Ar)、CO / N<sub>2</sub> / (Ar)、CH<sub>3</sub>OH / NH<sub>3</sub> / (Ar)、C<sub>2</sub>H<sub>5</sub>OH / N<sub>2</sub> / (Ar)等の組み合わせを用いることができる。なお、希釈用のAr及びHeは、プラズマが安定して放電できれば、必ずしも必要とはしない。

【0020】

上述の混合ガスに高周波パワーを加えてプラズマ処理を行う。プラズマ処理は、CCP (Capacitive Coupled Plasma) チャンバを用いて行う。また、CCP装置以外にも、ICP (Inductive Coupled Plasma) 装置やECR (Electron Cyclotron Resonance) 装置等を用いてもよい。

10

【0021】

プラズマ処理の処理時間t、ガス圧力P、チャンバ壁温度Tw及びウェハ温度T等の各条件は、CN活性種による処理効果が高く発揮されるように最適化する。

チャンバに加えるトップパワーはガス解離が十分に起きる程度の高い値、例えば、1000 - 2000W程度であることが好ましい。バイアスパワーは、半導体基体11上に堆積するポリマー層14をエッティングし、ターゲットとなる半導体基体11をエッティングしない程度の低い値とする。例えば、バイアスパワーを50W以下程度、好ましくは20W程度若しくはこれよりも低い値とする。バイアスパワーは、使用するガス種やポリマー層14の厚さに応じて最適化する。また、使用するガス種によっては、ポリマー層14が形成されない、又は、ほとんど形成されない条件となる場合がある。この場合には、バイアスパワーを用いない条件(0W)でプラズマ処理を行ってもよい。

20

【0022】

プラズマ処理の各条件の一例を以下に示す。この例は、CMOSイメージセンサのシリコンフォトダイオード加工直後に、CCPエッティングチャンバを用いてプラズマ処理を行う条件である。

ガス流量: CHF<sub>3</sub> / N<sub>2</sub> / Ar = 100 / 100 / 500 sccm

トップパワー: 1000W

30

バイアスパワー: 20W

ガス圧力: 30 mTorr

壁温度Tw: 60

ウェハ温度PT: 20

処理時間t: 10秒

【0023】

上述の条件により、CとNとを含む分子混合ガスをプラズマ化し、CN活性種を生成する。そして、生成したCN活性種に、半導体基体11の表面を曝す。この処理により、CN活性種が半導体基体11表面の汚染金属や、半導体層の結晶欠陥と選択的に反応する。このため、半導体基体11の表面の金属とCN活性種とが安定な金属錯体を形成し、半導体基体11の表面から除去される。

40

【0024】

また、半導体基体11の表面の結晶欠陥、例えばシリコンの未結合手等の欠陥にCN活性種が結合する。例えば、シリコン基板中のダングリングボンドとCNが結合してSi-CN結合が形成される。シリコンの結晶欠陥では、シリコンダングリングボンドと4.5eVという強いSi-CN結合を選択的に形成することで、水素シンターの場合(Si-H、3.1eV)よりも安定性の高い修復ができる。この際、シリコン結晶中のCNによってシリコンのバンドギャップ中に新たなエネルギー準位が形成されない。これは、第一原理計算により確かめられている。このように、半導体基体11中の結晶欠陥を修復することにより、半導体基体11中の欠陥密度を低減することができる。

上述のプラズマ処理では、多結晶シリコンやアモルファスシリコンで数100nm程度

50

、単結晶シリコンや熱酸化膜で数nm程度、TEOS等のCVD形成による酸化膜で数10nmの深さまでCN活性種が入りこみ、結晶中の欠陥を取り除くことができる。

【0025】

[ポリマー層除去処理]

次に、プラズマ処理の際に半導体基体11上に形成されるポリマー層14を除去する。

Cを含むガスとして、フッ素系のガスを用いた場合は半導体基体11の表面に薄いポリマー層14が形成される。このため、図1Cに示すように、SC1(NH<sub>4</sub>OH + H<sub>2</sub>SO<sub>4</sub>)等の薬液により1分間処理し、堆積しているポリマー層14を除去する。薬液を用いたウェット処理により、半導体基体11へのエッチング等の損傷を与えることなく、ポリマー層14の除去が可能である。

10

【0026】

具体的には、アンモニア過酸化水素水(NH<sub>4</sub>OH + H<sub>2</sub>O<sub>2</sub>)若しくは硫酸過酸化水素水(H<sub>2</sub>SO<sub>4</sub> + H<sub>2</sub>O<sub>2</sub>)等による薬液処理である。ポリマー層14の厚さに応じて、例えば、1分程度の薬液処理を行う。この処理時間は、後述する半導体製造装置のレシピにあらかじめ登録しておき、ポリマー層14の厚さに応じて最適化された時間用いる。

【0027】

なお、プラズマ処理工程において選択されるガス種によっては、ポリマー層14が形成されない場合がある。また、プラズマ処理条件を最適化することにより、フッ素系のガスを用いた場合にも、ポリマー層14がエッチングされて堆積しない場合がある。例えば、半導体基体11へのバイアスパワーを20W程度印加することにより、プラズマ処理中に形成されるポリマー層14が、プラズマ励起により同時にエッチングされる。プラズマ処理工程において、これらの条件を最適化することにより、ポリマー層14の形成を抑えることができる。

20

さらに、ガスの流量(比)を最適化することにより、半導体基体11上へのポリマー層14の形成を抑制することが好ましい。ポリマー層14の形成を抑制することにより、堆積したポリマー層14によるCN活性種と半導体基体11との接触効率の阻害を防ぐことができる。また、薬液によるポリマー層14の除去処理の負担を減らすことができる。

最後に、薬液処理後の半導体基体11の表面を、純水を用いて洗浄する。

30

【0028】

上述のプラズマ処理方法は、既存のMOSやイメージングデバイスの製造プロセスにおけるプラズマ処理工程を利用して実施することができる。このため、既存の半導体装置の製造工程への導入が容易である。また、新規な製造装置を導入することなく、既存の生産ラインの製造装置を用いて実行することが可能である。

【0029】

また、上述のプラズマ処理の実施の有無については、諸所の解析手法によって予測判断できる。例えば、ESR(Electron Spin Resonance)による基体中のダングリングボンド量測定とXPS(X-ray Photoelectron Spectroscopy)によるN量の測定等で判断が可能である。

40

【0030】

[本製造方法ないしは本製造装置を使用して製造された半導体装置]

上述のプラズマ処理を施した半導体基体に、各種ダイオード、トランジスタ及び電子部品等の半導体素子(能動素子)を形成して半導体装置を製造することができる。

【0031】

上述のプラズマ処理は、例えば、シリコン単結晶の他にも、Cu<sub>2</sub>OやGaAs等の化合物半導体や酸化物半導体にも適用できる。また、各種不純物がドープされた半導体にも適用できる。例えば、固体撮像素子の画素部を形成するフォトダイオードに、上述のプラズマ処理を適用することにより、フォトダイオードを構成する不純物領域の結晶欠陥を修復することができ、白点や暗電流の発生を低減することができる。また、例えばp-n接合型の太陽電池を構成する半導体基体に上述のプラズマ処理を適用することにより、結晶欠

50

陥を修復することができ、変換効率の向上が可能となる。この半導体基体としては、単結晶型、多結晶型、アモルファス型等のいずれも適用可能である。

【0032】

上述のプラズマ処理を施した半導体基体に形成する各種半導体素子は、従来公知の方法により製造可能である。また、上述のプラズマ処理は、半導体素子を形成する前の半導体基体に施してもよく、また、半導体素子を形成した後の半導体基体に施してもよい。半導体基体に形成したトランジスタのゲート絶縁膜やゲート電極、素子分離、及び、基体上に形成したポリシリコン層、アモルファスシリコン層、並びに、これらに不純物がイオン注入された領域においても、上述のプラズマ処理による結晶欠陥の修復が可能である。

【0033】

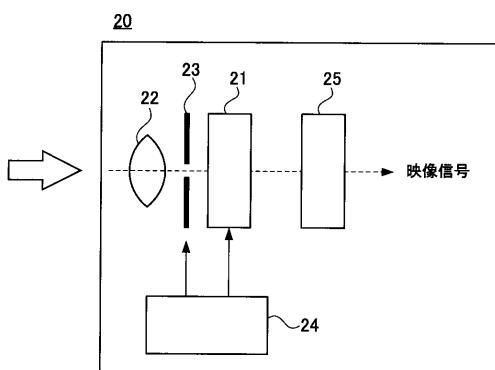

[電子機器]

上述のプラズマ処理が適用されて製造された半導体装置を用いて電子機器を構成することができる。この電子機器の一例として、上述のプラズマ処理が適用された固体撮像素子を備える、静止画像又は動画撮影可能なビデオカメラの構成を図2に示す。固体撮像素子は、例えば、デジタルカメラやビデオカメラ等のカメラシステム、撮像機能を有する携帯電話、又は、撮像機能を備えた他の機器等の電子機器に適用することができる。

【0034】

この例のカメラ20は、固体撮像素子21と、固体撮像素子21の受光センサ部に入射光を導く光学系22と、固体撮像素子21及び光学系22間に設けられたシャッタ装置23と、固体撮像素子21及びシャッタ装置23を駆動する駆動回路24とを備える。さらに、カメラ20は、固体撮像素子21の出力信号を処理する信号処理回路25を備える。

【0035】

固体撮像素子21は、上述したプラズマ処理が適用された半導体基体を用いて製造された半導体装置を適用することができる。

光学系(光学レンズ)22は、被写体からの像光(入射光)を固体撮像素子21の撮像面(不図示)上に結像させる。これにより、固体撮像素子21内に、一定期間、信号電荷が蓄積される。なお、光学系22は、複数の光学レンズを含む光学レンズ群で構成してもよい。また、シャッタ装置23は、入射光の固体撮像素子21への光照射期間及び遮光期間を制御する。

【0036】

駆動回路24は、固体撮像素子21及びシャッタ装置23に駆動信号を供給する。そして、駆動回路24は、供給した駆動信号により、固体撮像素子21の信号処理回路25への信号出力動作、及び、シャッタ装置23のシャッタ動作を制御する。すなわち、この例では、駆動回路24から供給される駆動信号(タイミング信号)により、固体撮像素子21から信号処理回路25への信号転送動作を行う。

【0037】

信号処理回路25は、固体撮像素子21から転送された信号に対して、各種の信号処理を施す。そして、各種信号処理が施された信号(映像信号)は、メモリなどの記憶媒体(不図示)に記憶される、又は、モニタ(不図示)に出力される。

【0038】

上述の固体撮像素子は、可視光の入射光量の分布を検知して画像として撮像する固体撮像素子への適用に限らず、赤外線やX線、あるいは粒子等の入射量の分布を画像として撮像する固体撮像素子に適用可能である。また、広義の意味として、圧力や静電容量など、他の物理量の分布を検知して画像として撮像する指紋検出センサ等の固体撮像素子(物理量分布検知装置)全般に対して適用可能である。

さらに、上述の固体撮像素子は、画素アレイ部の各単位画素を行単位で順に走査して各単位画素から画素信号を読み出す固体撮像素子に限らない。例えば、画素単位で任意の画素を選択して、当該選択画素から画素単位で信号を読み出すX-Yアドレス型の固体撮像素子に対しても適用可能である。

なお、固体撮像素子はワンチップとして形成された形態であってもよいし、撮像部と、

10

20

30

40

50

信号処理部または光学系とがまとめてパッケージングされた撮像機能を有するモジュール状の形態であってもよい。

【0039】

また、本実施形態では電子機器の一例としてカメラについて述べたが、高い画素特性・ロジック特性・エネルギー出力特性を持った半導体デバイス（例えば、CCDやCIS（CMOS Image Sensor）といったセンサーデバイス、メモリーデバイス、レーザーデバイス、ディスプレイデバイス、太陽電池に代表されるエネルギーデバイスなど）等を備える電子機器にも適用可能である。

【0040】

2. プラズマ処理方法の第2実施形態

10

次に、プラズマ処理方法の第2実施形態について説明する。本実施形態のプラズマ処理方法を説明するための概略工程を図3に示す。

まず、図3Aに示すように、被処理体となる半導体基体11を準備する。そして、この半導体基体11上に、例えば、熱酸化法により2nm程度の酸化膜15を形成する。この酸化膜15は、半導体装置に搭載する半導体素子、例えばMOSFETを形成する際のゲート絶縁膜となる。また、半導体基体11には、図3Aに示すように汚染金属12と結晶欠陥13とが存在する。

本実施形態では、形成した酸化膜15上から半導体基体11の半導体層表面にプラズマ処理を行う。

【0041】

20

次に、図3Bに示すように、上述の第1実施形態と同様の方法でC元素とN元素とを含む混合分子ガスをプラズマ化して、CNラジカル(CN·)やCNイオン(CN+)等のCN活性種を生成する。そして、生成したCN活性種に、酸化膜15を形成した半導体基体11の表面を曝す。

この処理により、CN活性種が酸化膜15の表面の汚染金属と選択的に反応する。そして、半導体基体11の表面の金属とCN活性種とが安定な金属錯体を形成し、半導体基体11の表面から除去される。

また、CN活性種が酸化膜15を透過し、半導体基体11の半導体層の表面の結晶欠陥と選択的に反応する。このため、表面に酸化膜15が形成されている場合にも、半導体基体11の半導体層の表面、例えばシリコンの未結合手等の欠陥にCN活性種が結合し、結晶欠陥を修復することができる。

【0042】

30

次に、プラズマ処理の際に半導体基体11上に形成されるポリマー層14を除去する。

Cを含むガスとしてフッ素系のガスを用いた場合、半導体基体11の表面には薄いポリマー層14が形成される。このため、図3Cに示すように、薬液を用いて半導体基体11をウェットエッティング処理し、堆積しているポリマー層14を除去する。プラズマ処理をポリマー層14が形成されない条件で行った場合には、このポリマー層14の除去処理は行わなくてもよい。

最後に、純水を用いて半導体基体11の表面を洗浄する。

【0043】

40

上述のように、半導体基体11に酸化膜15を形成した場合にも、酸化膜15上から半導体基体11の表面をプラズマ処理することで、半導体基体11の結晶欠陥を修復することができる。例えば、上述の熱酸化膜等の緻密な酸化膜の場合には、数nm程度まで半導体基体11の処理が可能である。また、TEOS等の密度の粗い酸化膜の場合には、さらに厚い酸化膜、例えば数10nm程度の厚さの酸化膜が形成されても酸化膜下の半導体層の処理が可能である。

【0044】

酸化膜が形成された半導体基体11をプラズマ処理することにより、半導体基体11の半導体層と酸化膜15との界面に存在する結晶欠陥、例えば、Si/SiO<sub>2</sub>界面の結晶欠陥を低減することができる。従って、トランジスタゲートのI-V特性の向上、RTS

50

ノイズの低減等が可能となる。

【0045】

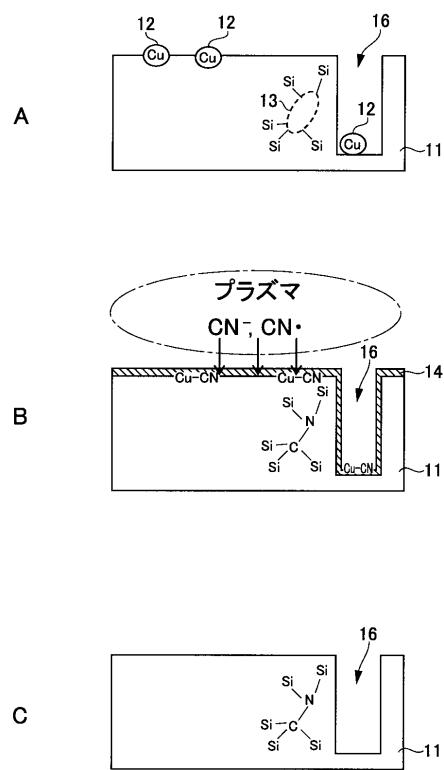

3. プラズマ処理方法の第3実施形態

次に、プラズマ処理方法の第3実施形態について説明する。本実施形態のプラズマ処理方法を説明するための概略工程を図4に示す。

まず、図4Aに示すように、被処理体となる半導体基体11を準備する。そして、この半導体基体11に、例えば、RIE(Reactive Ion Etching)等によりトレンチ16を形成する。このトレンチ16は、例えば、半導体装置に形成する固体撮像素子の画素内で遮光構造となる堀込みである。また、トレンチ16は、STI(Shallow Trench Isolation)を形成するためのトレンチや、縦型トランジスタを形成する際のゲート電極形成用のトレンチ等である。また、半導体基体11には、図4Aに示すように汚染金属12と結晶欠陥13が存在する。

本実施形態では、半導体基体11の表面と、形成したトレンチ16内に露出する面とにプラズマ処理を行う。

【0046】

次に、図4Bに示すように、上述の第1実施形態と同様の方法でC元素とN元素とを含む混合分子ガスをプラズマ化して、CNラジカル(CN·)やCNイオン(CN-)等のCN活性種を生成する。そして、生成したCN活性種に、半導体基体11を曝すことにより、半導体基体11の表面及びトレンチ16の内面がCN活性種により処理される。

【0047】

この処理により、CN活性種が半導体基体11の表面及びトレンチ16内の汚染金属と選択的に反応する。そして、金属とCN活性種とが安定な金属錯体を形成し、半導体基体11上から除去される。

また、半導体基体11の表面と、トレンチ16の内面に露出されている面とから、CN活性種が半導体基体11に侵入する。このため、半導体基体11の表面からトレンチ16の深部まで、半導体基体11の結晶欠陥とCN活性種が選択的に反応し、半導体基体11の結晶欠陥を修復することができる。

【0048】

次に、プラズマ処理の際に半導体基体11上に形成されるポリマー層14を除去する。本実施形態では、トレンチ16内にもポリマー層14が堆積する。このため、図4Cに示すように、薬液を用いて半導体基体11をウェットエッティング処理し、堆積しているポリマー層14を除去する。プラズマ処理をポリマー層14が形成されない条件で行った場合には、このポリマー層14の除去処理は行わなくてもよい。そして、最後に、純水を用いて半導体基体11の表面を洗浄する。

【0049】

上述のように、半導体基体11にトレンチ16を形成した場合にも、形成したトレンチ16の内面ごと半導体基体11のプラズマ処理が可能である。このため、半導体基体11、及び、トレンチ側壁及び底部に形成されている結晶欠陥及び金属汚染を低減することができる。

従って、例えば、トレンチが固体撮像素子の画素内で遮光構造となる堀込みの場合やSTI形成用の場合には、白点や暗電流の体験が可能となる。また、トレンチが縦型トランジスタを形成する際のゲート電極形成用である場合には、ゲート電極の底面及び側面に存在する結晶欠陥及び金属汚染を低減することができ、飽和電荷量(Qs)の向上が期待できる。

【0050】

なお、本実施形態において、半導体基体11上及びトレンチ16の内壁には、第2実施形態のように酸化膜が形成されていてもよい。酸化膜が形成されている場合にも同様に、半導体基体11上及びトレンチ16内のプラズマ処理が可能である。

また、トレンチ形成を行うRIE等のエッティングチャンバと、CN活性種による表面処理を行うプラズマ処理チャンバとは、使用するガス種や処理条件を変更することにより、

10

20

30

40

50

同じ処理装置で行うことが可能である。また、別々の装置により各処理を行ってもよい。

【0051】

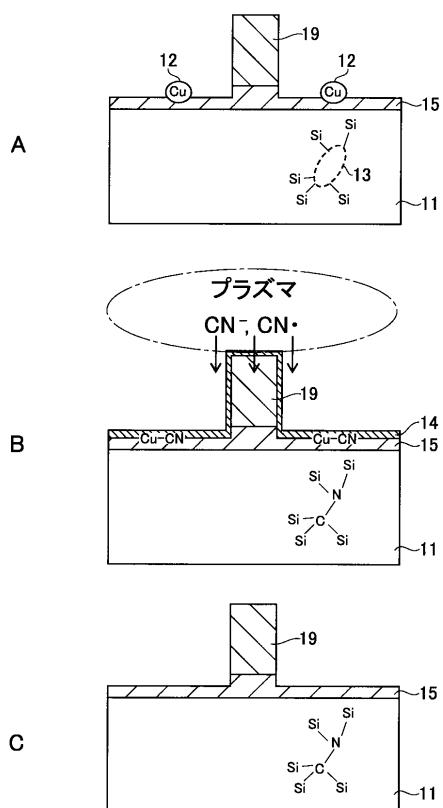

4. プラズマ処理方法の第4実施形態

次に、プラズマ処理方法の第4実施形態について説明する。本実施形態のプラズマ処理方法を説明するための概略工程を図5に示す。

まず、図5Aに示すように、被処理体となる半導体基体11を準備する。そして、この半導体基体11上に、例えば、熱酸化法によりに2nm程度の酸化膜15を形成する。さらに、酸化膜15上にポリシリコン層を形成する。形成したポリシリコン層を、フォトリソグラフィ技術を用いてゲート電極状に加工し、ポリシリコンゲート電極19を形成する。

酸化膜15及びポリシリコンゲート電極19は、半導体装置に搭載する半導体素子、例えば、MOSFETを形成する際のゲート絶縁膜及びゲート電極である。また、半導体基体11には、図5Aに示すように汚染金属12と結晶欠陥13とが存在する。

本実施形態では、形成したポリシリコンゲート電極19と半導体基体11とに同時にプラズマ処理を行う。半導体基体11のプラズマ処理は、形成した酸化膜15上から行う。

【0052】

次に、図5Bに示すように、上述の第1実施形態と同様に、C元素とN元素とを含む混合分子ガスをプラズマ化して、CNラジカル(CN·)やCNイオン(CN+)等のCN活性種を生成する。そして、生成したCN活性種に、酸化膜15を形成した半導体基体11の表面、及び、ポリシリコンゲート電極19を曝す。

【0053】

この処理により、CN活性種が酸化膜15及びポリシリコンゲート電極19の表面の汚染金属と選択的に反応する。そして、汚染金属とCN活性種とが安定な金属錯体を形成し、半導体基体11から除去される。

また、CN活性種が、ポリシリコンゲート電極19の結晶欠陥と選択的に反応する。さらに、CN活性種がポリシリコンゲート電極19及び酸化膜15を透過し、半導体基体11表面の結晶欠陥と選択的に反応する。このため、表面にポリシリコンゲート電極19及び酸化膜15が形成されている場合にも、半導体基体11の表面の結晶欠陥、例えばシリコンの未結合手等の欠陥にCN活性種が結合し、欠陥を修復することができる。

【0054】

次に、プラズマ処理の際に半導体基体11上に形成されるポリマー層14を除去する。本実施形態では、ポリシリコンゲート電極19上にもポリマー層14が堆積する。このため、図5Cに示すように、薬液を用いて半導体基体11をウェットエッティング処理し、堆積しているポリマー層14を除去する。プラズマ処理をポリマー層14が形成されない条件で行った場合には、このポリマー層14の除去処理は行わなくてもよい。そして、最後に、純水を用いて半導体基体11の表面を洗浄する。

【0055】

上述のように、ポリシリコンゲート電極を形成した場合にも、ポリシリコンゲート電極19及び酸化膜15上から半導体基体11の表面をプラズマ処理することで、半導体基体11の結晶欠陥を修復することができる。また、半導体基体11の結晶欠陥の修復と同時に、形成したポリシリコンゲート電極19の結晶欠陥を修復することができる。

【0056】

ポリシリコンやアモルファスシリコンの場合には、数100nm程度まで、CN活性種が侵入する。このため、ポリシリコンゲート電極19に加えて、ポリシリコンゲート電極19下に形成されているゲート絶縁膜、さらに、このゲート絶縁膜15下に形成されている半導体基体11に、CN活性種が侵入する。

この結果、ポリシリコンゲート電極の結晶欠陥、及び、ポリシリコンゲート電極とゲート絶縁膜との界面に存在する結晶欠陥を低減することができる。さらに、半導体基体11と酸化膜との界面に存在する結晶欠陥を低減することができる。従って、上述のポリシリコンゲート電極及びゲート絶縁膜を備える半導体装置のリーク電流の低減、トランジスタ

10

20

30

40

50

ゲートの I - V 特性の向上、RTS ノイズの低減等が可能となる。

【0057】

また、本実施形態のプラズマ処理後に、半導体基体 11 にイオン注入を行うことにより、酸化膜 15 及びポリシリコンゲート電極 19 を備える MOSFET 等の半導体装置を製造することができる。また、予めイオン注入した半導体基体 11 に、上述の酸化膜 15 及びポリシリコンゲート電極 19 を形成し、本実施形態のプラズマ処理を行ってもよい。

このように、本実施形態のプラズマ処理では、従来公知の半導体製造工程に適用することで、上述の結晶欠陥及び汚染金属の低減による作用を有する半導体装置を製造することができる。

【0058】

5. プラズマ処理方法の第 5 実施形態

次に、プラズマ処理方法の第 5 実施形態について説明する。本実施形態のプラズマ処理方法を説明するための概略工程を図 6 に示す。

まず、図 6A に示すように、被処理体となる半導体基体 11 を準備する。そして、この半導体基体 11 上に、例えば、熱酸化法により 2 nm 程度の酸化膜 15 を形成する。さらに、酸化膜 15 上にポリシリコン層を形成した後、フォトリソグラフィ技術を用いてポリシリコン層をゲート電極状に加工し、ポリシリコンゲート電極 19 を形成する。

ポリシリコンゲート電極 19 の形成後、ポリシリコンゲート電極 19 を覆って、酸化膜 15 上の全面を覆って、サイドウォール 17 となる 3 層の絶縁層 17A, 17B, 17C を形成する。絶縁層 17A 及び絶縁層 17C は、例えば TEOS (tetra-ethyl-ortho-silicate) 層を形成する。また、絶縁層 17B は、例えば SiN 層を形成する。

そして、絶縁層 17A, 17B, 17C をエッチバックすることにより、ポリシリコンゲート電極 19 の側壁にサイドウォール 17 を形成する。さらに、ポリシリコンゲート電極 19 及びサイドウォール 17 下を除き、半導体基体 11 上の酸化膜 15 を除去する。

酸化膜 15、ポリシリコンゲート電極 19 及びサイドウォール 17 は、半導体装置に搭載する半導体素子となる構成である。また、半導体基体 11 には、図 6A に示すように汚染金属 12 と結晶欠陥 13 とが存在する。

本実施形態では、サイドウォール 17 の形成後に、ポリシリコンゲート電極 19 と、半導体基体 11 とに同時にプラズマ処理を行う。

【0059】

次に、図 6B に示すように、上述の第 1 実施形態と同様の方法で C 元素と N 元素とを含む混合分子ガスをプラズマ化して、CN ラジカル (CN·) や CN イオン (CN+) 等の CN 活性種を生成する。そして、生成した CN 活性種に、半導体基体 11 の表面、ポリシリコンゲート電極 19、及び、サイドウォール 17 を曝す。

【0060】

この処理により、CN 活性種が半導体基体 11、ポリシリコンゲート電極 19 及びサイドウォール 17 の表面の汚染金属と選択的に反応する。そして、汚染金属と CN 活性種とが安定な金属錯体を形成し、半導体基体 11 から除去される。

また、CN 活性種が、ポリシリコンゲート電極 19 の結晶欠陥と選択的に反応する。さらに、CN 活性種がポリシリコンゲート電極 19、サイドウォール 17 及び酸化膜 15 を透過し、半導体基体 11 表面の結晶欠陥と選択的に反応する。このため、表面にポリシリコンゲート電極 19 及びサイドウォール 17 が形成されている場合にも、半導体基体 11 の表面の結晶欠陥、例えばシリコンの未結合手等の欠陥に CN 活性種が結合し、欠陥を修復することができる。

【0061】

次に、プラズマ処理の際に半導体基体 11 上に形成されるポリマー層 14 を除去する。本実施形態では、ポリシリコンゲート電極 19 及びサイドウォール 17 上にもポリマー層 14 が堆積する。このため、図 6C に示すように、薬液を用いて半導体基体 11 をウェットエッチング処理し、堆積しているポリマー層 14 を除去する。プラズマ処理をポリマー層 14 が形成されない条件で行った場合には、このポリマー層 14 の除去処理は行わなく

10

20

30

40

50

てもよい。そして、最後に、純水を用いて半導体基体 11 の表面を洗浄する。

【0062】

上述のように、サイドウォールを形成した場合にも、ポリシリコンゲート電極及びサイドウォール上から半導体基体 11 の表面をプラズマ処理することで、半導体基体 11 の結晶欠陥を修復することができる。また、半導体基体 11 の結晶欠陥の修復と同時に、形成したポリシリコンゲート電極の結晶欠陥を修復することができる。

この結果、上述の第4実施形態と同様に、ポリシリコンゲート電極の結晶欠陥、及び、ポリシリコンゲート電極とゲート絶縁膜との界面に存在する結晶欠陥を低減することができる。さらに、半導体基体 11 とゲート絶縁膜との界面に存在する結晶欠陥を低減することができる。従って、上述のポリシリコンゲート電極及びゲート絶縁膜を備える半導体装置のリーク電流の低減、トランジスタゲートの I-V 特性の向上、RTS ノイズの低減等が可能となる。

【0063】

また、半導体基体 11 に予めイオン注入により不純物領域を形成し、上述の酸化膜 15、ポリシリコンゲート電極 19 及びサイドウォールを形成した後、本実施形態のプラズマ処理を行ってもよい。これにより、上述の結晶欠陥及び汚染金属が低減にされた MOSFET 等を備える半導体装置を製造することができる。

このように、本実施形態のプラズマ処理では、従来公知の半導体製造工程に適用することで、半導体装置を製造することができる。

【0064】

6. プラズマ処理方法の第6実施形態

次に、プラズマ処理方法の第6実施形態について説明する。本実施形態のプラズマ処理方法を説明するための概略工程を図7に示す。

【0065】

まず、図7Aに示すように、被処理体となる半導体基体 11 を準備する。そして、この半導体基体 11 上に、例えば、熱酸化法により 2 nm 程度の酸化膜 15 を形成する。さらに、酸化膜 15 上にポリシリコン層を形成した後、フォトリソグラフィ技術を用いてポリシリコン層をゲート電極状に加工し、ポリシリコンゲート電極 19 を形成する。

ポリシリコンゲート電極 19 の形成後、ポリシリコンゲート電極 19 を覆って、酸化膜 15 上の全面を覆って、サイドウォール 17 となる 3 層の絶縁層 17A, 17B, 17C を形成する。絶縁層 17A 及び絶縁層 17C は、例えば TEOS (tetra-ethyl-ortho-silicate) 層を形成する。また、絶縁層 17B は、SiN 層を形成する。

そして、絶縁層 17A, 17B, 17C をエッチバックすることにより、ポリシリコンゲート電極 19 の側壁にサイドウォール 17 を形成する。さらに、サイドウォール 17 から露出する酸化膜 15 を除去する。

【0066】

そして、ポリシリコンゲート電極 19 及びサイドウォール 17 を覆って半導体基体 11 の全面に層間絶縁層 18 を形成する。層間絶縁層 18 の形成後、フォトリソグラフィ技術及び異方性エッチングを用いて所定の位置に、半導体基体 11 表面まで貫通する貫通孔 18A を形成する。図7Aでは一例として、サイドウォール 17 の一部が除去される位置に貫通孔 18A を形成している。

【0067】

酸化膜 15、ポリシリコンゲート電極 19 及びサイドウォール 17 は、半導体装置に搭載する半導体素子となる。層間絶縁層 18 の貫通孔 18A 内に導電体を形成することにより、図示しない半導体基体 11 上の配線と層間絶縁層 18 上の配線とを接続することができる。また、半導体基体 11 には、図7Aに示すように汚染金属 12 と結晶欠陥 13 とが存在する。

本実施形態では、層間絶縁層 18 の貫通孔 18A 形成後に、貫通孔 18A の底面に露出する半導体基体 11 の表面にプラズマ処理を行う。

【0068】

10

20

30

40

50

次に、図7Bに示すように、上述の第1実施形態と同様の方法でC元素とN元素とを含む混合分子ガスをプラズマ化して、CNラジカル(CN·)やCNイオン(CN-)等のCN活性種を生成する。そして、生成したCN活性種に、層間絶縁層18、及び、貫通孔18Åの底面に露出する半導体基体11の表面を曝す。

【0069】

この処理により、CN活性種が層間絶縁層18の表面、貫通孔18Åの内面、及び、貫通孔18Å内の半導体基体11の表面の汚染金属と選択的に反応する。そして、汚染金属とCN活性種とが安定な金属錯体を形成し、半導体基体11から除去される。

また、CN活性種が、貫通孔18Åの底面に露出する半導体基体11の表面の結晶欠陥と選択的に反応し、半導体基体11の表面の結晶欠陥、例えばシリコンの未結合手等の欠陥にCN活性種が結合し、欠陥を修復することができる。

【0070】

次に、プラズマ処理の際に半導体基体11上に形成されるポリマー層14を除去する。本実施形態では、層間絶縁層18上、貫通孔18Åの内壁、及び、貫通孔18Åの底面の半導体基体11上にポリマー層14が堆積する。このため、図7Cに示すように、薬液を用いて半導体基体11をウェットエッティング処理し、堆積しているポリマー層14を除去する。プラズマ処理をポリマー層14が形成されない条件で行った場合には、このポリマー層14の除去処理は行わなくてもよい。そして、最後に、純水を用いて半導体基体11の表面を洗浄する。

【0071】

上述のように、層間絶縁層18を形成し、この層間絶縁層18の貫通孔18Åから露出する半導体基体11の表面にも、プラズマ処理による汚染金属と結晶欠陥の低減が可能である。この結果、半導体装置のリーク電流の低減及びI-V特性の向上が可能となる。

【0072】

### 7. プラズマ処理方法の第7実施形態

次に、プラズマ処理方法の第7実施形態について説明する。本実施形態のプラズマ処理方法を説明するための概略工程を図8に示す。

まず、図8Aに示すように、被処理体となる半導体基体11を準備する。この半導体基体11上には、アモルファス層10が形成されている。アモルファス層10は、例えば、半導体装置の製造工程において、シリコン基板を高パワー、高ドーズ条件でエッティング加工した際に、半導体基体11上に堆積する層である。

次に、図8Bに示すようにアモルファス層10を、CDE(Chemical Dry Etching)処理をして除去する。CDE処理は、例えば、 $CF_4/O_2 = 50/50$  sccm、20Paの条件で行う。

【0073】

次に、図8Cに示すように、上述の第1実施形態と同様の方法でC元素とN元素とを含む混合分子ガスをプラズマ化して、CNラジカル(CN·)やCNイオン(CN-)等のCN活性種を生成する。そして、生成したCN活性種に、半導体基体11の表面を曝す。

このとき、CN活性種を用いるプラズマ処理の処理温度は、第1実施形態に示すようにチャンバ壁温度Twが60、ウェハ温度PTが20である。このため、半導体基体11上に、耐熱性の低い材料や部品が形成されている場合にも処理温度が低いため、損傷を与えることなくプラズマ処理が可能となる。

【0074】

次に、プラズマ処理の際に半導体基体11上に形成されるポリマー層14を除去する。Cを含むガスとして、フッ素系のガスを用いた場合、半導体基体11の表面には薄いポリマー層14が形成される。このため、図8Dに示すように、薬液を用いて半導体基体11をウェットエッティング処理し、堆積しているポリマー層14を除去する。プラズマ処理をポリマー層14が形成されない条件で行った場合には、このポリマー層14の除去処理は行わなくてもよい。

最後に、純水を用いて半導体基体11の表面を洗浄する。

10

20

30

40

50

## 【0075】

従来のアモルファス層が堆積した半導体基体11の一般的な処理方法では、アニール処理を行って半導体基体11の結晶性を回復する。しかし、半導体基体11上に耐熱性の低い有機部材や樹脂部材等が形成されている場合には、高温のアニール処理ができない。これに対し、本実施形態のCN活性種を用いるプラズマ処理は、通常の有機部材や樹脂部材等の耐熱温度よりも処理温度が低く、耐熱性の低い部材に損傷を与えることがない。従つて、複数の工程を経て耐熱性の低い材料が形成されている半導体装置にも、本実施形態のプラズマ処理方法を適用することができる。

## 【0076】

## 8. プラズマ処理装置の実施形態

10

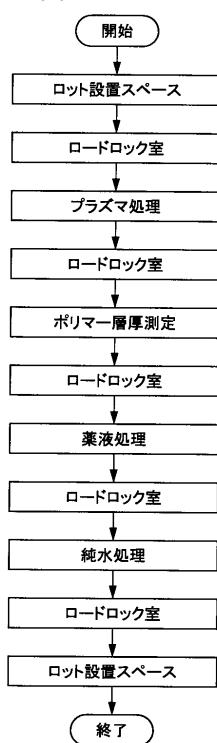

次に、上述のプラズマ処理方法に適用するプラズマ処理装置の実施形態について説明する。図9に本実施形態のプラズマ処理装置の概略構成を示す。また、図10に、図9に示すプラズマ処理装置を用いたプラズマ処理方法の処理フロー図を示す。

## 【0077】

## [ プラズマ処理装置 ]

図9に示すプラズマ処理装置30は、ロット設置スペース31, 36、搬送系（ロードロック室）37、プラズマ処理チャンバ32、ポリマー層厚測定チャンバ33、有機物除去チャンバ34、及び、純水処理チャンバ35から構成される。

## 【0078】

ロット設置スペース31には、処理前の半導体基体が収容されている。ロット設置スペース36には、処理後の半導体基体が収容される。ロット設置スペース31, 36及び各チャンバ間での半導体基体の移動は、ロードロック室37を経由して行われる。また、各チャンバ及びロードロック室37は真空に保たれている。

20

## 【0079】

プラズマ処理チャンバ32は、既知のプラズマ処理チャンバを利用する。プラズマ処理チャンバ32は、例えば、OES（Optical Emission Spectrometry）システム、ガス除去装置、上述のプラズマ処理プロセスのレシピを含むソフトウェア及び制御システムを含んで構成される。

30

ソフトウェアには、上述のプラズマ処理プロセスのレシピとして、トップパワー、バイアスパワー、チャンバ壁温度、ウェハ温度、ガス圧力、ガス流量（比）等の各種条件が格納されている。そして、ソフトウェアのレシピと制御システムとを用いて、プラズマ生成を制御してCN活性種の生成を行う。

また、OESシステムにより、プラズマ処理中のCN発光強度をモニタリングし、発光強度変動に従つて、ソフトウェアと制御システムによりO<sub>2</sub>クリーニングステップを行う。

## 【0080】

プラズマ処理チャンバ32は、毒性の高いガスが使用される、或いは、プラズマチャンバ内でCNガス等の毒性の高いガスが生成されるため、これらのガスの除去装置を備える。

また、プラズマ処理チャンバ32には、図示しないガス供給部が接続されている。ガス供給部は、半導体基体を処理するCN活性種を生成するためのCとNとを含む混合ガスの供給部を含む。また、希釈用のArガスや、プラズマ処理チャンバ32において行われる他の処理で使用されるガスの供給部を含む。

40

## 【0081】

ポリマー層厚測定チャンバ33は、例えば、in-situ測定装置、制御システム及びデータベースを含んで構成される。

ポリマー層厚測定チャンバ33は、例えばXPS（X-ray Photoelectron Spectroscopy）や分光エリプソメトリ等のin-situ測定が可能な測定装置と、in-situ測定装置の制御システムとを備える。また、データベースには、ポリマー層厚と薬液処理時間との関係が格納されている。

50

## 【0082】

有機物除去チャンバ34は、例えば、薬液装置、薬液処理のレシピを含むソフトウェア、制御システム及び廃液装置を含んで構成される。

ソフトウェアには、薬液処理のレシピとして各種処理条件が格納されている。薬液処理の各種条件は、ポリマー層厚測定チャンバ33のデータベースに格納されたポリマー層厚と薬液処理時間との関係から抽出される。そして、ソフトウェアのレシピと制御システムとを用いて、半導体基体上に堆積したポリマー層を除去するための薬液処理を行う。薬液装置は、薬液処理を行うための薬液、例えばH<sub>2</sub>SO<sub>4</sub>、H<sub>2</sub>O<sub>2</sub>、NH<sub>4</sub>OH等を有機物除去チャンバ34に供給する。また、廃液装置により、薬液処理に使用された薬液が回収される。

10

## 【0083】

純水処理チャンバ35は、例えば、薬液装置、純水処理のレシピを含むソフトウェア、制御システム及び廃液装置を含んで構成される。

純水処理チャンバ35で、半導体基体表面の汚れ、異物等を除去するために純水を用いて洗浄する。薬液装置は、半導体基体を洗浄するための純水、及び、半導体基体洗浄用の各種洗浄液等を純水処理チャンバ35に供給する。そして、ソフトウェアに格納されたレシピと制御システムを用いて、半導体基体の洗浄を行う。また、廃液装置により、洗浄に使用された薬液が回収される。

## 【0084】

## [処理フロー]

20

次に、上述の図9に示すプラズマ処理装置30を用いたプラズマ処理方法の処理フローを、図10を用いて説明する。

まず、ロット設置スペース31に置かれた半導体基体は、中央のロードロック室37を通り、プラズマ処理チャンバ32へ送られる。そして、ロット設置スペース31からプラズマ処理チャンバに移送された半導体基体のプラズマ処理を行う。

## 【0085】

CCP、ICP、ECR等を備えるプラズマ処理チャンバ32では、上述のプラズマ処理方法の実施形態と同様に、トップパワー、バイアスパワー、チャンバ壁温度、ウェハ温度、ガス圧力、ガス流量(比)等のレシピに従ってプラズマ生成を制御し、CN活性種による表面処理を行う。

30

## 【0086】

また、プラズマ処理中は、OESシステムによりCN発光強度(例えば、波長387nmの発光)を常にモニタリングし、その発光強度変動に従って処理ウェハ間でO<sub>2</sub>クリーニングステップを自動で行う。例えば、reference強度の20%以上の発光強度変動に対してO<sub>2</sub>クリーニングステップを行う。また、O<sub>2</sub>クリーニングステップは、例えば、O<sub>2</sub>の流量500sccm、トップパワー/バイアスパワー=1000/100Wで1分間行う。

## 【0087】

次に、上述のプラズマ処理後、半導体基体がロードロック室37を通り、ポリマー層厚測定チャンバ33に送られる。そして、ポリマー層厚測定チャンバ33で半導体基体上に堆積したポリマー層の厚さを測定する。ポリマー層厚測定チャンバ33では、実装された膜厚測定機でポリマー層厚をin-situ測定する。そして、ポリマー層の厚さの実測値と、データベースの膜厚-処理時間の関係との比較から、後工程の薬液処理時間を自動決定する。

40

## 【0088】

測定後の半導体基体はロードロック室37を通って有機物除去チャンバ34に送られ、指定された時間で薬液処理される。このチャンバには、処理に必要なH<sub>2</sub>SO<sub>4</sub>、H<sub>2</sub>O<sub>2</sub>、NH<sub>4</sub>OHタンクから薬液が供給され、自動決定された処理時間で薬液処理を行う。

薬液処理後、半導体基体はロードロック室37を通って純水処理チャンバ35に送られ、表面洗浄される。すべての処理が終わった半導体基体はロードロック室37を通り、口

50

ット設置スペース 3 6 に搬送される。

以上の処理フローにより、半導体基体のプラズマ処理を行うことができる。

【0089】

なお、上述の各実施形態におけるプラズマ処理の各条件は、第1実施形態で例示した条件と、同じ条件としてもよく、また、使用するガス種や、処理時間  $t$ 、ガス圧力  $P$ 、チャンバ壁温度  $T_w$  及びウェハ温度  $T$  等の各条件は、適宜変更することができる。プラズマ処理の各種条件は、半導体基体の種類や使用するガス種に応じて、CN活性種による処理効果が高く発揮されるよう最適化する。

また、上述の第2実施形態から第7実施形態によるプラズマ処理方法においても、上述の第1実施形態と同様に、半導体基体に半導体素子等を形成することで、半導体装置の製造方法に適用できる。また、第2実施形態から第7実施形態によるプラズマ処理方法を適用した半導体装置を用いて、第1実施形態と同様に電子機器を構成することができる。

10

【0090】

なお、本開示は以下のような構成も取ることができる。

(1) CとNとを含む混合ガスをプラズマ化してCN活性種を生成し、生成した前記CN活性種により半導体基体の半導体層の表面を処理するプラズマ処理方法。

(2) 前記半導体基体の表面の半導体層を前記CN活性種によりパッシベートする(1)に記載のプラズマ処理方法。

(3) CHF<sub>3</sub>、CH<sub>2</sub>F<sub>2</sub>、C<sub>4</sub>F<sub>8</sub>、C<sub>5</sub>F<sub>8</sub>、CO、C<sub>2</sub>H<sub>5</sub>OH及びCH<sub>3</sub>OHから選ばれる少なくとも1種類以上を含む前記混合ガスを用いる(1)又は(2)に記載のプラズマ処理方法。

20

(4) 半導体基体に加えるバイアスパワーが0W以上50W以下である(1)から(3)のいずれかに記載のプラズマ処理方法。

(5) 前記プラズマ化する際のトップパワーが1000W以上2000W以下である(1)から(4)のいずれかに記載のプラズマ処理方法。

(6) 前記CN活性種により前記半導体基体を処理した後、前記半導体基体上に堆積したポリマー層を薬液により除去する(1)から(5)のいずれかに記載のプラズマ処理方法。

(7) 上記(1)から(6)のいずれかに記載されたプラズマ処理工程と、前記半導体基体に半導体素子を形成する工程とを有する半導体装置の製造方法。

30

(8) 上記(1)から(6)のいずれかに記載されたプラズマ処理を行うプラズマ処理部を備えるプラズマ処理装置。

(9) 前記プラズマ処理部は、前記CN活性種を生成するプラズマ処理条件のレシピを含むソフトウェアを備える(8)に記載のプラズマ処理装置。

(10) 前記プラズマ処理部は、CNガスの除去装置を備える(8)又は(9)に記載のプラズマ処理装置。

【符号の説明】

【0091】

10 アモルファス層、11 半導体基体、12 汚染金属、13 結晶欠陥、14

ポリマー層、15 酸化膜、16 トレンチ、17 サイドウォール、17A, 17B,

17C 絶縁層、18 層間絶縁層、18A 貫通孔、19 ポリシリコンゲート電極、

20 カメラ、21 固体撮像素子、22 光学系、23 シャッタ装置、24 駆動回路、

25 信号処理回路、30 プラズマ処理装置、31, 36 ロット設置スペース、

32 プラズマ処理チャンバ、33 ポリマー層厚測定チャンバ、34 有機物除去チャンバ、

35 純水処理チャンバ、37 搬送系(ロードロック室)

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

---

フロントページの続き

F ターム(参考) 5F140 AA24 BA01 BE07 BF01 BF04 BG10 BG12 BG14 BG37 BG41

BG51 BG53

5F157 AA09 AA28 AA29 AA42 AA46 AB02 AB49 AB51 AC01 AC13

BG32 BG39 BH15 CB03 DB03