(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4612820号

(P4612820)

(45) 発行日 平成23年1月12日(2011.1.12)

(24) 登録日 平成22年10月22日(2010.10.22)

(51) Int.Cl.

H04L 29/10 (2006.01)

F 1

H04L 13/00 309C

請求項の数 11 (全 15 頁)

(21) 出願番号 特願2004-264644 (P2004-264644)

(22) 出願日 平成16年9月10日 (2004.9.10)

(65) 公開番号 特開2006-81032 (P2006-81032A)

(43) 公開日 平成18年3月23日 (2006.3.23)

審査請求日 平成19年9月10日 (2007.9.10)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090273

弁理士 國分 孝悦

森川 健一

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

(72) 発明者 川島 淳

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

(72) 発明者 森村 和彦

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

最終頁に続く

(54) 【発明の名称】通信制御装置及び方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数レイヤのプロトコルのヘッダ生成に必要なヘッダ生成情報を収集し、ヘッダ生成指示及びヘッダ生成情報をフレーム毎に出力するプロトコル制御手段と、

前記プロトコル制御手段から前記ヘッダ生成指示及び前記ヘッダ生成情報を入力されると、複数レイヤのプロトコルのヘッダを並列して1ヘッダ毎に生成し、ヘッダ生成完了通知を出力するヘッダ生成手段と、

前記ヘッダ生成手段から前記ヘッダ生成完了通知を入力されると、前記生成された複数レイヤのプロトコルのヘッダ及びフレーム単位のペイロードをフレームとして合成するヘッダ/ペイロード合成手段と

を有することを特徴とする通信制御装置。

## 【請求項 2】

前記ヘッダ生成手段は、

TCPヘッダを1ヘッダ毎に生成するTCPヘッダ生成手段と、

UDPヘッダを1ヘッダ毎に生成するUDPヘッダ生成手段と、

IPヘッダを1ヘッダ毎に生成するIPヘッダ生成手段と、

MACヘッダを1ヘッダ毎に生成するMACヘッダ生成手段とを有し、

前記プロトコル制御手段は、前記TCPヘッダ生成手段、前記UDPヘッダ生成手段、前記IPヘッダ生成手段及び前記MACヘッダ生成手段にヘッダの生成指示を出力することができる特徴とする請求項1記載の通信制御装置。

10

20

**【請求項 3】**

前記プロトコル制御手段は、前記ヘッダ／ペイロード合成手段が1つ前のフレームとして合成したヘッダを出力した後に、次のフレームのヘッダ生成指示を前記ヘッダ生成手段に出力することを特徴とする請求項1又は2記載の通信制御装置。

**【請求項 4】**

さらに、フレーム単位のペイロードを記憶するためのメモリを有し、

前記プロトコル制御手段は、ペイロードが前記メモリに書き込まれた後に、そのペイロードに対応するヘッダ生成指示を前記ヘッダ生成手段に出力することを特徴とする請求項1又は2記載の通信制御装置。

**【請求項 5】**

さらに、フレーム単位のペイロードを記憶するためのメモリを有し、

前記プロトコル制御手段は、前記ヘッダ／ペイロード合成手段が1つ前のフレームとして合成したヘッダを出力した後、かつ次のペイロードが前記メモリに書き込まれた後に、次のフレームのヘッダ生成指示を前記ヘッダ生成手段に出力することを特徴とする請求項1又は2記載の通信制御装置。

**【請求項 6】**

さらに、前記ヘッダ／ペイロード合成手段により合成されたフレームを送信するフレーム送信手段を有することを特徴とする請求項1～5のいずれか1項に記載の通信制御装置。

**【請求項 7】**

さらに、送信データをフレーム単位のペイロードに分割するペイロード分割手段を有することを特徴とする請求項1～6のいずれか1項に記載の通信制御装置。

**【請求項 8】**

さらに、前記ペイロード分割手段により分割されたフレーム単位のペイロードを記憶するためのメモリを有することを特徴とする請求項7記載の通信制御装置。

**【請求項 9】**

さらに、前記メモリからフレーム単位のペイロードを読み出して前記ヘッダ／ペイロード合成手段に出力するペイロード読み出し手段を有することを特徴とする請求項8記載の通信制御装置。

**【請求項 10】**

さらに、送信データ長を基にフレーム個数及びフレーム長を算出するフレーム個数フレーム長算出手段を有し、

前記ペイロード分割手段は、前記算出されたフレーム個数及びフレーム長を基にペイロードの分割を行うことを特徴とする請求項7～9のいずれか1項に記載の通信制御装置。

**【請求項 11】**

通信制御装置が行う通信制御方法であって、

複数レイヤのプロトコルのヘッダ生成に必要なヘッダ生成情報を収集し、ヘッダ生成指示及びヘッダ生成情報をフレーム毎に出力するプロトコル制御ステップと、

前記ヘッダ生成指示及び前記ヘッダ生成情報が入力されると、複数レイヤのプロトコルのヘッダを並列して1ヘッダ毎に生成し、ヘッダ生成完了通知を出力するヘッダ生成ステップと、

前記ヘッダ生成完了通知が入力されると、前記生成された複数レイヤのプロトコルのヘッダ及びフレーム単位のペイロードをフレームとして合成するヘッダ／ペイロード合成ステップと

を有することを特徴とする通信制御方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、通信制御装置及び方法に関するものである。

**【背景技術】**

10

20

30

40

50

**【 0 0 0 2 】**

パーソナルコンピュータ等でなくとも、機器を直接ネットワークに接続する機会や需要が高まっている。例として携帯端末、プリンタ、カメラ、コピー機、ディスプレイ、ビデオ機器、音響装置などが挙げられる。これらの機器は比較的低価格・低処理能力のCPUを搭載、又は全く搭載していない場合もあり、その様な機器資源を利用しネットワークにおいて標準的に使用されているTCP／UDP／IPといったインターネット標準プロトコルを実現しようとすれば、TCP／UDP／IPのプロトコルスタックを低処理能力CPUで低ビットレート（帯域）ではあるが実現するか、又はTOE（TCP／IPオフロードエンジン）といったプロトコル処理に特化した補助的デバイスを利用する事で比較的広帯域なネットワーク通信を実現するか、の方法しかない。とはいっても機器が扱う情報の量は写真、動画、音楽、いずれにおいても大きくなる一方で、機器のコストを低価格に抑える必要がある、といった背景においてはTOEによるネットワーク通信機能実現のアプローチが今後増加してくることは想像に難くない。10

**【 0 0 0 3 】**

TOE実現（TCP／IPプロトコルスタックのハードウェアによる実現）において、最も簡単にこれを実現する為には、ただ単に今迄ソフトウェアで実現していた方法をそのままハードウェア化すればよいと言う考え方がある。ソフトウェアで実現されているTCP／UDP／IPプロトコルスタックは充分に枯れた方法により実現されており、この考え方は1つの妥当な考え方ではある。しかしソフトウェア（CPU向け）に考案された方法をそのままハードウェア化したときに、それがゲートやレジスタ（フリップフロップ）やメモリといったプリミティブなデバイスで実現される事を考えるとソフトウェアの実現方法がそのままハードウェアの適切な実現方法であるかといえば、違うと言わざるを得ない。ハードウェアは複雑なポインタ処理や、変数の動的生成や消滅、再帰処理、多くのプロセス生成、といった処理方法は苦手であり、ソフトウェアで実現されたTCP／IPプロトコルスタックは複雑なポインタ処理と変数やメモリ領域の動的生成や消滅といった手順が到るところに存在している。20

**【 0 0 0 4 】**

従来手順をそのままハードウェアで実現すると大きく以下の流れになる。（1）アプリケーションデバイスから送信指示された一連の送信データを一時的に連続した共有メモリ領域に保存する。（2）共有メモリに保存された一連の送信データを、最も上位のプロトコル制御ブロックが参照、分割、ヘッダ追加を行い、次のプロトコル制御ブロックに共有メモリのアクセス権利と共に制御を移す。各プロトコル制御ブロックは順次、各々共有メモリの参照、分割、ヘッダ追加を行う。（3）ヘッダとペイロードを連続したメモリ空間に隣接して配置する。ペイロードの全てを連続したメモリ空間に配置できない場合は別のメモリ空間にペイロードのみを配置する。（4）ヘッダと隣接したペイロードや隣接しないペイロード、フレームの連続関係はメモリ制御情報として必要な数だけメモリ内に保存される（一般にmbufと呼ばれる）。

**【 0 0 0 5 】**

即ち、複雑なペイロード分割とペイロードやヘッダの管理情報（mbuf）の生成後にヘッダが生成され、この処理は各プロトコルスタックで各々順次実行される。30

**【 0 0 0 6 】**

また、下記の特許文献1には、TCP／IPをハードウェア的に処理する装置及びその動作方法が記載されている。

**【 0 0 0 7 】**

**【特許文献1】特開2001-268159号公報**

**【発明の開示】****【発明が解決しようとする課題】****【 0 0 0 8 】**

しかし、上記のような手順を踏むと、アプリケーションの転送単位によるTCPセグメント化やIPフラグメント化が必要な場合は、1つ1つのフレームに対する全てのヘッダ40

をメモリに書き込まなければならない。すなわちリンク層に依存する M T U に対して、アプリケーションの転送単位が大きくなるにつれて、分割後に発生するフレームが増加し、そのフレームに付加しなければならないヘッダを書き込むために確保しなければならないメモリ領域が増大するという課題がある。

#### 【0009】

一般的には、メモリ内でヘッダとペイロードをフレーム化して出力する。しかし、アプリケーションの転送単位により T C P のセグメント化や I P のフラグメント化が必要な場合は、一つ一つのフレームに対するヘッダ全てをメモリに書き込まなければならない。

#### 【0010】

本発明の目的は、アプリケーションの転送単位が大きくなることにより送信するフレーム数が増加する場合であっても、ヘッダを書き込むために確保しなければならないメモリ領域の増大を抑止することである。

#### 【課題を解決するための手段】

#### 【0011】

本発明の通信制御装置は、複数レイヤのプロトコルのヘッダ生成に必要なヘッダ生成情報を収集し、ヘッダ生成指示及びヘッダ生成情報をフレーム毎に出力するプロトコル制御手段と、前記プロトコル制御手段から前記ヘッダ生成指示及び前記ヘッダ生成情報が入力されると、複数レイヤのプロトコルのヘッダを並列して1ヘッダ毎に生成し、ヘッダ生成完了通知を出力するヘッダ生成手段と、前記ヘッダ生成手段から前記ヘッダ生成完了通知が入力されると、前記生成された複数レイヤのプロトコルのヘッダ及びフレーム単位のペイロードをフレームとして合成するヘッダ/ペイロード合成手段とを有することを特徴とする。

#### 【0012】

また、本発明の通信制御方法は、複数レイヤのプロトコルのヘッダ生成に必要なヘッダ生成情報を収集し、ヘッダ生成指示及びヘッダ生成情報をフレーム毎に出力するプロトコル制御ステップと、前記ヘッダ生成指示及び前記ヘッダ生成情報が入力されると、複数レイヤのプロトコルのヘッダを並列して1ヘッダ毎に生成し、ヘッダ生成完了通知を出力するヘッダ生成ステップと、前記ヘッダ生成完了通知が入力されると、前記生成された複数レイヤのプロトコルのヘッダ及びフレーム単位のペイロードをフレームとして合成するヘッダ/ペイロード合成ステップとを有することを特徴とする。

#### 【発明の効果】

#### 【0013】

本発明によれば、フレーム単位で複数レイヤのプロトコルのヘッダを並列して生成し、フレーム単位のペイロードと合成するので、アプリケーションの転送単位が大きくなることにより送信フレーム数が増加する場合であっても、フレームに付加しなければならないヘッダを書き込むために確保しなければならないメモリ領域の増大を抑止することができる。

#### 【発明を実施するための最良の形態】

#### 【0014】

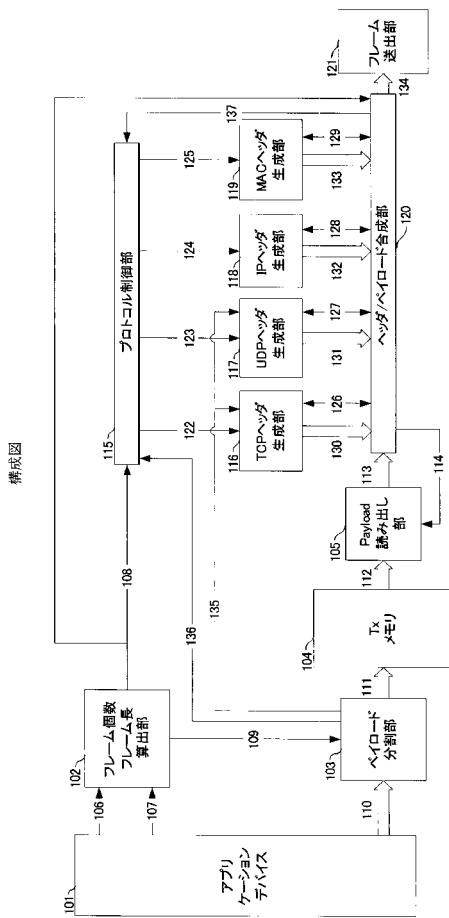

図 1 は、本発明の実施形態による通信制御装置の構成例を示すブロック図である。以下、図 1 を用いてその構成を説明する。

#### 【0015】

#### [アプリケーションデバイス]

アプリケーションデバイス(101)は、送信要求(106)と送信データ長(107)をフレーム個数フレーム長算出部(102)に出力し、送信データ(110)をペイロード分割部(103)に出力する。アプリケーションデバイス(101)には、2つの種類が想定される。1つ目はコンスタントビットレート(単位時間あたりの情報量が一定)のデバイスである。2つ目はバリアブルビットレートのデバイス(単位時間あたりの情報量が一定ではないが、単位時間辺りの情報量は明示される)である。その他にバリアブルビットレートのデバイスからの情報を一時的にバッファし定期的に一定量の情報を出力す

10

20

30

40

50

る様シェーピングするデバイスである場合も想定されるがこれは1つ目の種類のデバイスと同じと見なせる。また、サンプリング周波数で予め規定された量子化ビットレートでRAW情報を出力してくるデバイスも想定できるが、これは1つ目の種類のデバイスと同様に見なすことが出来る。これら全てのアプリケーションデバイス(101)に接続される本実施形態による通信制御装置は、アプリケーションデバイス(101)とのインターフェースにおいて、送信要求(106)、送信データ長(107)、送信データ(110)、を受ける事とする。

#### 【0016】

##### [フレーム個数フレーム長算出部]

フレーム個数フレーム長算出部(102)は、アプリケーションデバイス(101)から入力された送信要求(106)をトリガに、同じく入力された送信データ長(107)を基に送信データを幾つのフレームに分割して出力すべきかを算出する。

10

#### 【0017】

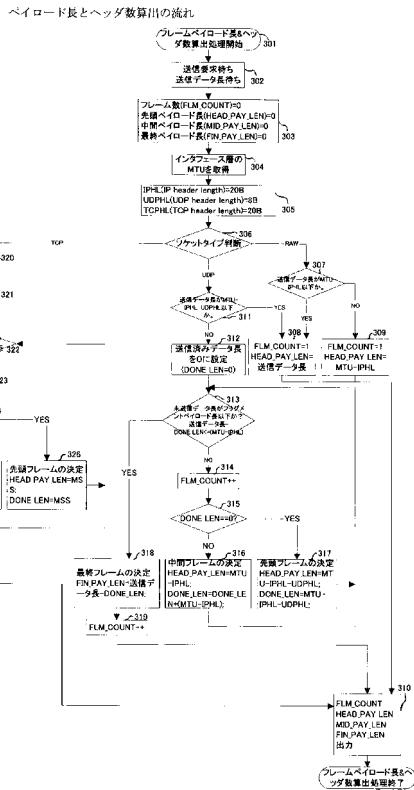

図2のフローチャートを用いて、ペイロード長とヘッダ数算出の流れについて詳説する。フレーム個数フレーム長算出部(102)は、アプリケーションデバイス(101)からの送信要求(106)を受信すると併せて、その一度の送信要求で送信したいデータの長さを送信データ長(107)として受け取る(ステップ301、302)。するとフレーム個数フレーム算出部(以後FFCと呼ぶ)はフレーム数(FLM\_COUNT)、先頭フレームペイロード長(HEAD\_PAY\_LEN)、中間フレームペイロード長(MID\_PAY\_LEN)、最終フレームペイロード長(FIN\_PAY\_LEN)を算出する必要があるが、これらをまず初期化する(ステップ303)。フレームをどの様な長さの単位で送信するかについてはTCP/UDPを想定した場合、インターフェースのMTU又はTCPのMSSが想定されるが、ここではまずインターフェースのMTUを取得する(ステップ304)。また、TCP/UDP/IPから形成されるフレームを扱う場合にフレームのペイロード長を算出する為には各々のプロトコルヘッダの長さを鑑みる必要があるのでIPHL(IP Header Length)及びUDPHL(UDP Header Length)を規定する(ステップ305)。このステップ305では、それぞれ基本のヘッダ長を示してあるが各プロトコルにおいてオプションヘッダを想定する場合はこの場でオプションヘッダ長まで加味したヘッダ長を規定する。次にコネクションの種別についてTCPかUDPか又はRAWであるか、を識別する。コネクション種別は予めFFC(102)にて保持しておく方法とコネクション識別子を基に導出する方法が考えられる(ステップ306)。

20

#### 【0018】

UDPの場合は送信データ長がインターフェース層MTU-IPHL-UDPHL以下であるかを確認する(ステップ311)。そうである場合は1つのフレームに与えられた送信データが全て格納可能であるのでフレーム数1、先頭フレームペイロード長=送信データ長である、とする(ステップ308)。そうでない場合は送信データを複数のフレームに分割する必要がある。この分割数や各ペイロード長を算出する作業は仮にフレームを送信していく場合にどうなるかという事を想定しながら分割作業を進めていく。まず仮の送信済みデータ長(DONE\_LEN)を0とする(ステップ312)。次に未送信データ長がフラグメントペイロード長以下であるかを確認する。これは最終フラグメントであるかという判断をおこなっており、未送信データ長は送信データ長から仮の送信済みデータ長(DONE\_LEN)を減算して求め、これとMTU-IPHLの長さを比較する等という方法が想定できる(ステップ313)。ここまで事前チェックの流れにおいては、初めての比較では未送信データ長がフラグメントペイロード長以下であるということは起き得ない。次にフレーム数(FLM\_COUNT)をインクリメントする(ステップ314)。送信済みデータ長が0であれば(ステップ315)、先頭フレームであると判断されるので先頭フレームのペイロード長はMTU-IPHL-UDPHLであり、仮の送信済みデータ長はMTU-IPHL-UDPHLであると決定される(ステップ317)

30

40

50

。先頭フレームではない場合は中間フレームであるから中間フレーム長を M T U - I P H L、仮の送信済みデータ長 ( D O N E \_ L E N ) を D O N E \_ L E N + ( M T U - I P H L ) とする。これらの後再び未送信データ長がフラグメントペイロード長以下であるか、即ち最終フラグメントであるかを判断し ( ステップ 313 ) 、もし最終フラグメントであれば最終フレームは送信データ長から D O N E \_ L E N を減算する事で求められる ( ステップ 318 ) 。その後最終フラグメントフレームの分のフレーム数をカウントアップ ( F L M \_ C O U N T + + ) し ( ステップ 319 ) 、フレーム数、先頭フレームペイロード長、中間フレームペイロード長、最終フレームペイロード長が決定出力される ( ステップ 310 ) 。

## 【 0019 】

10

コネクション種別が R A W の場合はフレーム数は 1 つで、フレームペイロード長は M T U - I P H L の範囲内に収まるべきであり、もしそうでないとしてもその様に送信データを切り落として送信する事を想定している。又はアプリケーションデバイス ( 101 ) にエラーとして応答を送るという方法も考えられる ( ステップ 308 、 309 ) 。

## 【 0020 】

コネクション種別が T C P の場合はフレーム長は M S S ( マキシマムセグメントサイズ ) が基本となるので取得する ( ステップ 320 ) 。次に仮の送信済みデータサイズ ( D O N E \_ L E N ) をゼロに初期化し ( ステップ 321 ) 、 ( 仮の ) 未送信データ長が M S S 以下であるかをチェックする ( ステップ 322 ) 。もし M S S 以下であれば与えられた送信データは次の 1 セグメントで送信完了できる事が判断できる。もし M S S より大きければフレーム数をインクリメント ( ステップ 323 ) し、先頭セグメントであれば ( この判断は D O N E \_ L E N が 0 であるか否かで行う ) ( ステップ 324 ) 、先頭フレーム長は M S S であり、 D O N E \_ L E N は M S S となる ( ステップ 326 ) 。再び仮の未送信データ長が M S S 以下であるかを確認し、まだ M S S より大きい場合はフレーム数をカウントアップし今度は中間フレームペイロード長を M S S とし送信済みデータ長 D O N E \_ L E N = D O N E \_ L E N + M S S とする ( ステップ 325 ) 。再び未送信データ長が M S S 以下であるかを確認し、もし最終セグメントであると判断されれば最終フレームとして最終フレーム長を送信データ長から D O N E \_ L E N を減算した値とし ( ステップ 327 ) 、最終フレームを送信フレーム数としてカウントする ( ステップ 328 ) 。

20

## 【 0021 】

30

上述の様にフレーム数、先頭フレームペイロード長、中間フレームペイロード長、最終フレームペイロード長が決定出力される ( ステップ 310 ) 。これら 4 つの値をフレーム個数とフレーム長に関する値とし、ペイロード分割部 ( 103 ) とプロトコル制御部 ( 115 ) 及びヘッダ / ペイロード生成部 ( 120 ) に出力する。

## 【 0022 】

## [ ペイロード分割部の分割 ]

ペイロード分割部 ( 103 ) ではフレーム個数フレーム長算出部 ( 102 ) から与えられたフレーム個数とフレーム長に関する入力 ( 109 ) を基にアプリケーションデバイス ( 101 ) から与えられた送信データ ( 110 ) を分割しながらフレームペイロードとしてペイロード T X メモリ ( 104 ) に書き込み保存を行う ( 111 ) 。ペイロード分割部 ( 103 ) は、フレームペイロード書き込みが完了したらプロトコル制御部 ( 115 ) に対しフレームペイロードの送信準備が出来た事を通知する ( 136 ) 。

40

## 【 0023 】

## [ ペイロード分割部のチェックサム ]

ペイロード分割部 ( 103 ) ではフレーム個数フレーム長算出部 ( 102 ) から与えられたフレーム個数とフレーム長に関する入力 ( 109 ) を基にアプリケーションデバイス ( 101 ) から与えられた送信データ ( 110 ) を分割しながらフレームペイロードとしてペイロード T X メモリ ( 104 ) に書き込み保存を行う ( 111 ) 際、フレームペイロードのチェックサムをフレーム毎に求め、 U D P ヘッダ生成部 ( 117 ) 及び、 T C P ヘッダ生成部 ( 116 ) にチェックサム値を伝える ( 135 ) 。

50

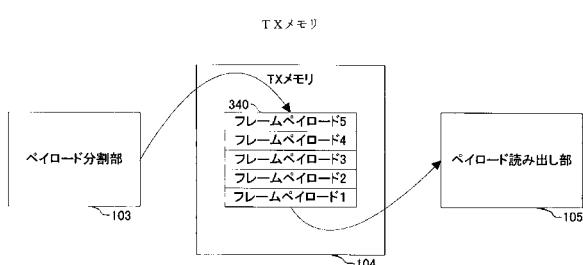

## 【0024】

## [TXメモリ]

TXメモリ(104)では1つの送信要求に伴う一連の送信データを、送信要求毎、フレームペイロード FIFOにフレームペイロードの列として保存している。図3に示す様にTXメモリ(104)内部には1つの送信要求に伴い1つのFIFOが割り当てられ(340)、例えばここでは1つの送信要求による送信データが5つのフレームペイロードから成ることを示している。本図ではフレームペイロード1(先頭フレーム)からフレームペイロード5(最後尾フレーム)がFIFOに蓄えられているがフレーム単位での送信が行われる場合はこの様に5つのフレームが溜まることはない。各々のフレームペイロードはFIFOに挿入された直後にペイロード読み出し部(105)により抜き出され送信される事も考えられる。

10

## 【0025】

## [ペイロード読み出し部]

ペイロード読み出し部(105)ではヘッダ/ペイロード合成部(120)からの、1つのペイロード読み出し指示(114)に対し、送信すべきフレームペイロードを1つ取り出し、ヘッダ/ペイロード合成部(120)へ出力する(113)。

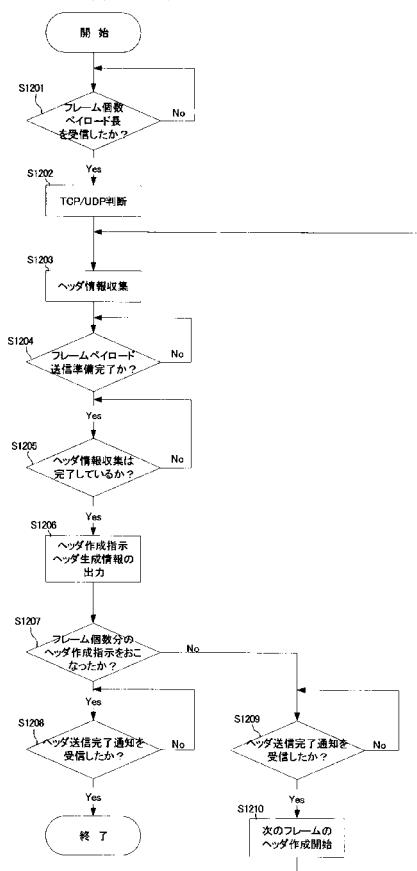

## 【0026】

## [プロトコル制御部]

プロトコル制御部(115)ではフレーム個数フレーム長算出部(102)からの指示により、フレームごとに必要なヘッダを特定してヘッダに必要な情報を収集し、各プロトコルヘッダ生成部(116~119)にヘッダ生成指示及びヘッダ生成情報を通知する(122~125)。図4にプロトコル制御部(115)のフローチャートを示す。ステップS1201においてフレーム個数フレーム長算出部(102)よりフレーム個数、先頭フレームのペイロード長、中間フレームのペイロード長、最終フレームのペイロード長の4つの値(108)を受信したかの判断を行う。もし受信すれば(ステップS1201: Yes)、ステップS1202において送信フレームがTCPなのかUDPなのかを判断し、フレーム送信に必要なプロトコルヘッダを生成するための情報を収集する(ステップS1203)。この時、収集する情報は1つのフレームに付加されるヘッダについてのみ行われる。つまり最初は先頭フレームに付加されるヘッダのみの情報収集を行う。また、収集する各種情報は静的に設定されている場合と動的にテーブル検索を行う場合がある。動的なテーブルとしては、コネクションに付随する宛先IPアドレス、送信元IPアドレス、宛先ポート、送信元ポートを割り出すアドレステーブルや、IPのルーティングテーブルなどが挙げられる。次にペイロード分割部(103)からフレームペイロード送信準備完了通知を受信したかの判断を行う(ステップS1204: Yes)。もし、フレームペイロード送信準備完了通知を受信したら、ステップS1205にてヘッダ情報の収集が終了しているかの判断を行う。ヘッダ情報の収集が終了した場合(ステップS1205: Yes)は、ステップS1206にて送信フレームに必要なヘッダを生成するヘッダ生成部にヘッダ生成指示及びヘッダ生成情報を出力する。ヘッダ生成指示を出力後はステップS1207においてフレーム個数分のヘッダ生成指示を行ったかの判断を行う。もし、フレーム個数分のヘッダ生成指示を行った(ステップS1207: Yes)のなら、ステップS1208においてステップS1206で作成を指示したヘッダのヘッダ送信完了通知をヘッダ/ペイロード合成部(120)から受信するのを待ち、ヘッダ送信完了通知を受信したら1つのデータグラムに対する全てのフレームのヘッダが送信されたとしてプロトコル制御を終了する。ステップS1207においてもしフレーム個数分のヘッダ生成指示を行っていないのならば(S1207: No)、まだ送信すべきフレームを生成しなければならないとして、ステップS1209においてステップS1206で作成を指示したヘッダのヘッダ送信完了通知をヘッダ/ペイロード合成部(120)から受信するのを待ち、ヘッダ送信完了通知を受信したら次のフレームのヘッダ作成を開始する(ステップS1210)。そしてステップS1203に戻る。

20

## 【0027】

30

40

50

**[TCPヘッダ生成部]**

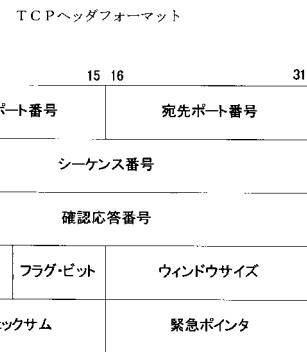

TCPヘッダ生成部(116)ではプロトコル制御部(115)からのヘッダ生成指示及びヘッダ生成情報に基づきヘッダ生成を開始し、ヘッダ生成完了後にヘッダ/ペイロード合成部(120)にTCPヘッダ生成完了通知(126)を行う。TCPヘッダ生成指示をプロトコル制御部(115)から受信したら、プロトコル制御部(115)からTCPヘッダ情報を取得する。TCPヘッダ情報は送信元ポート番号、宛先ポート番号、シーケンス番号、確認応答番号、ヘッダ長、フラグビット、ウィンドウサイズ、緊急ポイント及び擬似ヘッダ用の宛先IPアドレス、送信元IPアドレス、セグメント長(TCPヘッダ長+ペイロード長)である。取得したヘッダ生成情報から擬似ヘッダとチェックサム以外のTCPヘッダを作成する。次にフレームごとのペイロードサムをペイロード分割部(103)より受信し、擬似ヘッダとチェックサム以外のTCPヘッダとペイロードサムからTCPのチェックサムを算出し、チェックサムをTCPヘッダのチェックサムフィールドに設定し、TCPヘッダの生成を完了する。TCPヘッダの生成が完了すると、ヘッダ/ペイロード合成部(120)にTCPヘッダ生成完了通知を行い、TCPヘッダ生成を終了し、プロトコル制御部(115)より次のヘッダ生成指示があるまで待機する。TCPヘッダ生成部(116)で作成するヘッダのフォーマットを図6に、擬似ヘッダフォーマットを図7に示す。

**【0028】**

また、TCPヘッダ生成部(116)はヘッダ/ペイロード合成部(120)からの出力要求(126)を受信すると、生成したTCPヘッダをヘッダ/ペイロード合成部(120)に出力(130)する。

**【0029】**

**[UDPヘッダ生成部]**

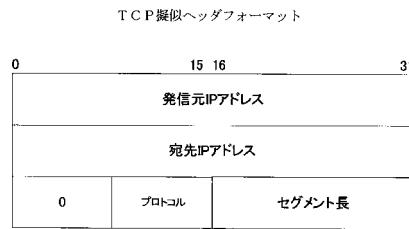

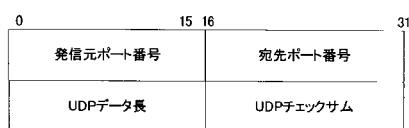

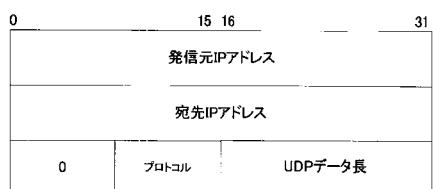

UDPヘッダ生成部(117)ではプロトコル制御部(115)からのヘッダ生成指示及びヘッダ生成情報に基づきヘッダ生成を開始し、ヘッダ生成完了後にヘッダ/ペイロード合成部(120)にUDPヘッダ生成完了通知(127)を行う。UDPヘッダ生成指示をプロトコル制御部(115)から受信したら、プロトコル制御部(115)からUDPヘッダ情報を取得する。UDPヘッダ情報は、送信元ポート番号、宛先ポート番号、UDPデータ長である。取得したヘッダ生成情報から擬似ヘッダとチェックサム以外のUDPヘッダを作成する。次にペイロードサムをペイロード分割部(103)より受信したかの判断を行い、もし受信していれば擬似ヘッダとチェックサム以外のUDPヘッダとペイロードサムの合計からUDPチェックサムを算出し、チェックサムをUDPヘッダのチェックサムフィールドに設定し、UDPヘッダの生成を完了する。UDPヘッダの生成が完了すると、ヘッダ/ペイロード合成部(120)にUDPヘッダ生成完了通知を行い、UDPヘッダ生成を終了する。

**【0030】**

ただし、UDPヘッダのチェックサムはオプションでの対応となっているため、UDPチェックサムを行わない設定にした場合は、プロトコル制御部(115)よりUDPヘッダ情報(送信元ポート番号、宛先ポート番号、UDPデータ長)を取得した時点で、UDPチェックサムフィールドに0を設定し、UDPヘッダ生成完了通知をヘッダ/ペイロード合成部(120)に出力する。

**【0031】**

UDPヘッダ生成部で作成するヘッダのフォーマットを図8に、擬似ヘッダフォーマットを図9に示す。

**【0032】**

また、UDPヘッダ生成部(117)はヘッダ/ペイロード合成部(120)からの出力要求(127)を受信すると、生成したUDPヘッダをヘッダ/ペイロード合成部(120)に出力(131)する。

**【0033】**

**[IPヘッダ生成部]**

10

20

30

40

50

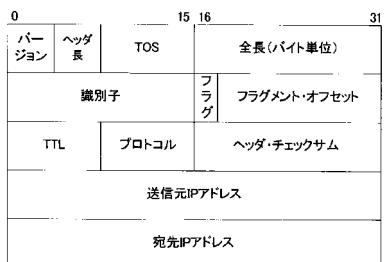

I P ヘッダ生成部(118)ではプロトコル制御部(115)からのヘッダ生成指示及びヘッダ生成情報に基づきヘッダ生成を開始し、ヘッダ生成完了後にヘッダ/ペイロード合成部(120)にI Pヘッダ生成完了通知(128)を行う。I Pヘッダ生成指示をプロトコル制御部(115)から受信したら、プロトコル制御部(115)からI Pヘッダ情報を取得する。I Pヘッダ情報はバージョン、ヘッダ長、TOS、全長、識別子、フラグ、フラグメントオフセット、TTL、プロトコル、送信元I Pアドレス、宛先I Pアドレスである。これらの情報からI Pヘッダのヘッダチェックサムを算出してI Pヘッダを完成させ、ヘッダ/ペイロード合成部(120)にI Pヘッダ生成完了通知を行う。I Pヘッダ生成部で作成するヘッダのフォーマットを図10に示す。

## 【0034】

10

また、I Pヘッダ生成部(118)はヘッダ/ペイロード合成部(120)からの出力要求(128)を受信すると、生成した順番にI Pヘッダをヘッダ/ペイロード合成部(120)に出力(132)する。

## 【0035】

## [MACヘッダ生成部]

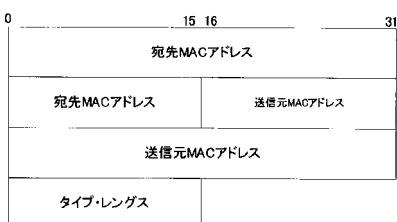

MACヘッダ生成部(119)ではプロトコル制御部(115)からのヘッダ生成指示及びヘッダ生成情報に基づきヘッダ生成を開始し、ヘッダ生成完了後にヘッダ/ペイロード合成部(120)にMACヘッダ生成完了通知(129)を行う。MACヘッダ生成部(119)はプロトコル制御部(115)からMACヘッダ生成指示を受信したら、MACヘッダ情報を取得する。MACヘッダ生成情報は、ヘッダ生成数、送信元MACアドレス、宛先MACアドレス、タイプレンジスである。これらの情報からMACヘッダを完成させ、ヘッダ/ペイロード合成部(120)にMACヘッダ生成完了通知を行う。MACヘッダ生成部で作成するMACヘッダのフォーマットを図11に示す。

20

## 【0036】

また、MACヘッダ生成部(119)はヘッダ/ペイロード合成部(120)からの出力要求(129)を受信すると、生成したMACヘッダをヘッダ/ペイロード合成部(120)に出力(133)する。

## 【0037】

## [ヘッダ/ペイロード合成部]

ヘッダ/ペイロード合成部(120)はフレーム個数フレーム長算出部(102)からのフレーム個数から生成すべきヘッダの種類とその個数を割り出す。次に、各プロトコルヘッダ生成部からのヘッダ完了通知により、送信フレームに必要なヘッダが完了していることを認識し、TCP/I Pの場合はMACヘッダ生成部(119)、I Pヘッダ生成部(118)、TCPヘッダ生成部(116)、ペイロード読み出し部(105)の順に出力要求を行い、ヘッダ及びペイロードを読み出してフレームとして合成し、フレーム送出部(121)に出力する。UDP/I Pの場合は先頭フレームはMACヘッダ生成部(119)、I Pヘッダ生成部(118)、UDPヘッダ生成部(117)、ペイロード読み出し部(105)の順に出力要求を行い、中間、最終フレームはMACヘッダ生成部(119)、I Pヘッダ生成部(118)、ペイロード読み出し部(105)の順に出力要求を行い、ヘッダ及びペイロードを読み出してフレームとして合成しフレーム送出部(121)に出力する。ペイロードを持たないフレームを送信する場合はヘッダのみ読み出して、フレームとして合成し、フレーム送出部(121)に出力する。ヘッダ/ペイロード合成部(120)は、ヘッダをフレーム送出部(121)に出力した時点で、プロトコル制御部(115)にヘッダ送信完了(137)を出力する。

30

## 【0038】

40

## [フレーム送出部]

フレーム送出(送信)部(121)では、ヘッダ/ペイロード合成部(120)から出力されるフレームを通信制御装置外に送信する機能を有する。IEEE802.3に準拠し、プリアンブルの付加、フレームパディング、CRCの生成等を行う。

## 【0039】

50

## &lt; T C P セグメントの送信例 &gt;

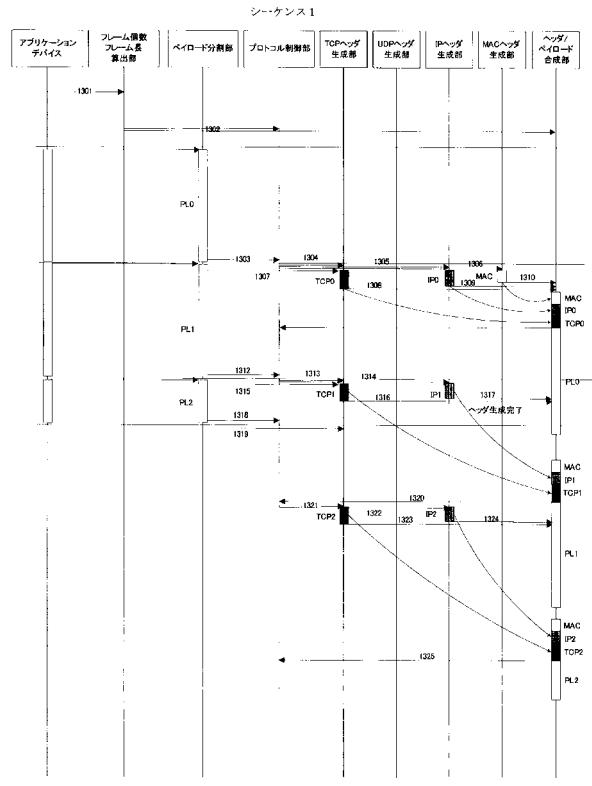

T C P / I P のフレーム送信時に送信データグラムが 3 つのセグメントに分割された場合の例を図 5 に示す。アプリケーションデバイス (101) からの送信指示及び送信データ長 (1301) を受けてフレーム個数フレーム長算出部 (102) は、フレーム個数 (3 個)、先頭フレームのペイロード長 (P L 0 の長さ)、中間フレームのペイロード長 (P L 1 の長さ)、最終フレームのペイロード長 (P L 2 の長さ) をプロトコル制御部 (115) 及びヘッダ / ペイロード合成部 (120) に出力 (1302) する。プロトコル制御部 (115) ではプロトコルタイプを T C P であると判断し、T C P、I P、M A C のヘッダ情報の収集を行う。またペイロード分割部 (103) においてペイロードを T X モリ (104) に書き込んでいき、1 フレーム分 (1 T C P セグメント分) 書き込みが完了すると、プロトコル制御部 (115) に対してフレームペイロード送信準備完了 (1303) を出力する。プロトコル制御部 (115) はフレームペイロード送信準備完了 (1303) を受信するとデータグラムをセグメント化した先頭フレームの T C P、I P、M A C のヘッダを生成するためのヘッダ情報収集が終了しているかを判断し、終了していれば T C P ヘッダ生成部 (116) にヘッダ生成指示及びヘッダ情報 (1304) を、I P ヘッダ生成部 (118) にヘッダ生成指示及びヘッダ情報 (1305) を、M A C ヘッダ生成部 (119) にヘッダ生成指示及びヘッダ情報 (1306) を同時に出力する。ヘッダ生成指示を受信した T C P ヘッダ生成部 (116) はプロトコル制御部 (115) からのヘッダ情報とペイロード分割部 (103) からのペイロードサム (1307) より T C P ヘッダを生成し、ヘッダ / ペイロード合成部 (120) に T C P ヘッダ生成完了 (1308) を出力する。ヘッダ生成指示を受信した I P ヘッダ生成部はプロトコル制御部 (115) からのヘッダ情報から I P ヘッダを生成し、ヘッダ / ペイロード合成部 (120) に I P ヘッダ生成完了 (1309) を出力する。ヘッダ生成指示を受信した M A C ヘッダ生成部 (119) はプロトコル制御部 (115) からのヘッダ情報から M A C ヘッダを生成し、ヘッダ / ペイロード合成部 (120) に M A C ヘッダ生成完了 (1310) をフレーム個数分出力する。ヘッダ / ペイロード合成部 (120) はフレーム個数フレーム長算出部 (102) から受信したフレーム個数 (1302) から 3 つにセグメント化されたフレームの先頭フレームには T C P ヘッダ、I P ヘッダ、M A C ヘッダが必要であることを認識しており、T C P ヘッダ生成完了 (1308)、I P ヘッダ生成完了 (1309)、M A C ヘッダ生成完了 (1310) の全てを受信するとフレームを送信可能な状態であると判断する。ヘッダ / ペイロード合成部 (120) は M A C ヘッダ、I P ヘッダ、T C P ヘッダ、ペイロードと読み出していきフレーム送出部 (121) に先頭フレームを出力する。また、M A C、I P、T C P ヘッダをフレーム送出部 (121) に出力した時点でプロトコル制御部 (115) にヘッダ送信完了 (1311) を出力する。

## 【 0040 】

プロトコル制御部 (115) はヘッダ送信完了 (1311) を受信すると次のフレーム、つまりここでは 3 つにセグメント化されたフレームの中間フレームのヘッダ情報収集を行う。中間フレームに必要なヘッダは先頭と同様に T C P、I P、M A C ヘッダの情報収集を行う。ペイロード分割部 (103) からの次のフレームペイロード送信準備完了 (1312) を受信すると、中間フレームの T C P、I P、M A C のヘッダを生成するためのヘッダ情報収集が終了しているかを判断し、終了していれば T C P ヘッダ生成部 (116) にヘッダ生成指示及びヘッダ情報 (1313) を、I P ヘッダ生成部 (118) にヘッダ生成指示及びヘッダ情報 (1314) を同時に出力する。ヘッダ生成指示を受信した T C P ヘッダ生成部 (116) はプロトコル制御部 (115) からのヘッダ情報とペイロード分割部 (103) からのペイロードサム (1315) より T C P ヘッダを生成し、ヘッダ / ペイロード合成部 (120) に T C P ヘッダ生成完了 (1316) を出力する。ヘッダ生成指示を受信した I P ヘッダ生成部 (118) はプロトコル制御部 (115) からのヘッダ情報から I P ヘッダを生成し、ヘッダ / ペイロード合成部 (120) に I P ヘッダ生成完了 (1317) を出力する。

## 【 0041 】

10

20

30

40

50

ヘッダ/ペイロード合成部(120)はフレーム個数フレーム長算出部(102)から受信したフレーム個数(1302)から3つにセグメント化されたフレームの中間フレームにはTCPヘッダ、IPヘッダ、MACヘッダが必要であることを認識しており、TCPヘッダ生成完了(1316)、IPヘッダ生成完了(1317)を受信するとフレームを送信可能な状態であると判断する。MACヘッダ生成完了については先頭フレームの時にフレーム個数分出力されているため、ヘッダ/ペイロード合成部(120)はこの時点で中間フレームのMACヘッダ生成が完了していると判断している。フレームが送信可能な状態であると判断したヘッダ/ペイロード合成部(120)はMACヘッダ、IPヘッダ、TCPヘッダ、ペイロードと読み出していきフレーム送出部(121)に中間フレームを出力する。また、MAC、IP、TCPヘッダをフレーム送出部に出力した時点でプロトコル制御部(115)にヘッダ送信完了(1320)を出力する。

10

#### 【0042】

プロトコル制御部(115)はヘッダ送信完了(1320)を受信すると次のフレーム、つまりここでは3つにセグメント化されたフレームの最終フレームのヘッダ情報収集を行う。最終フレームに必要なヘッダは先頭、中間と同様にTCP、IP、MACヘッダの情報収集を行う。ペイロード分割部(103)からの次のフレームペイロード送信準備完了(1318)をすでに受信しているので、TCP、IP、MACのヘッダを生成するためのヘッダ情報収集が終了し次第、TCPヘッダ生成部(116)にヘッダ生成指示及びヘッダ情報(1321)を、IPヘッダ生成部(118)にヘッダ生成指示及びヘッダ情報(1322)を同時に出力する。ヘッダ生成指示を受信したTCPヘッダ生成部(116)はプロトコル制御部(115)からのヘッダ情報とペイロード分割部(103)からのペイロードサム(1319)よりTCPヘッダを生成し、ヘッダ/ペイロード合成部(120)にTCPヘッダ生成完了(1323)を出力する。ヘッダ生成指示を受信したIPヘッダ生成部(118)はプロトコル制御部(115)からのヘッダ情報からIPヘッダを生成し、ヘッダ/ペイロード合成部(120)にIPヘッダ生成完了(1324)を出力する。

20

#### 【0043】

ヘッダ/ペイロード合成部(120)はフレーム個数フレーム長算出部(102)から受信したフレーム個数(1302)から3つにセグメント化されたフレームの最終フレームにはTCPヘッダ、IPヘッダ、MACヘッダが必要であることを認識しており、TCPヘッダ生成完了(1323)、IPヘッダ生成完了(1324)を受信するとフレームを送信可能な状態であると判断する。MACヘッダ生成完了については先頭フレームの時にフレーム個数分出力されているため、ヘッダ/ペイロード合成部(120)はこの時点で中間フレームのMACヘッダ生成が完了していると判断している。フレームが送信可能な状態であると判断したヘッダ/ペイロード合成部(120)はMACヘッダ、IPヘッダ、TCPヘッダ、ペイロードと読み出していきフレーム送出部(121)に最終フレームを出力する。また、MAC、IP、TCPヘッダをフレーム送出部に出力した時点でプロトコル制御部(115)にヘッダ送信完了(1325)を出力する。

30

#### 【0044】

以上のように、本実施形態によれば、アプリケーションデバイス(101)から任意の長さの送信データを受信し、サポートするデータリンク層に適切なフレームサイズでフレーム出力する通信制御装置が提供される。プロトコル制御部(101)は、フレーム生成に必要なヘッダ生成情報を収集し、ヘッダ生成指示及びヘッダ生成情報をフレーム毎に出力する。ヘッダ生成手段(116～119)は、プロトコル制御部(115)からヘッダ生成指示及びヘッダ生成情報を入力すると、ヘッダを1ヘッダ毎に生成し、ヘッダ生成完了通知を出力する。ヘッダ/ペイロード合成部(120)は、ヘッダ生成部(116～119)からヘッダ生成完了通知を入力すると、生成されたヘッダ及びフレーム単位のペイロードをフレームとして合成する。プロトコル制御部(115)は、所望のヘッダの生成指示をヘッダ生成部(116～119)に出力することができる。

40

#### 【0045】

TXメモリ(104)は、フレーム単位のペイロードを記憶するためのメモリである。プロトコル制御部(115)は、ヘッダ/ペイロード合成部(120)が1つ前のフレームとして合成したヘッダを出力した後、かつ次のペイロードがTXメモリ(104)に書き込まれた後に、次のフレームのヘッダ生成指示をヘッダ生成部(116～119)に出力する。

#### 【0046】

本実施形態によれば、リンク層に依存するMTUに対して、アプリケーションの転送単位が大きくなるにつれて分割後に発生するフレームが増加しても、フレーム単位でヘッダを生成し送信することで、フレームに付加しなければならないヘッダを書き込むためのメモリ領域を確保する必要がなくなる。

10

#### 【0047】

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されなければならないものである。すなわち、本発明はその技術思想、またはその主要な特徴から逸脱することなく、様々な形で実施することができる。

#### 【図面の簡単な説明】

#### 【0048】

【図1】本発明の実施形態による通信制御装置の構成図である。

【図2】ペイロード長とヘッダ数算出の流れを示すフローチャートである。

【図3】TXメモリを示す図である。

20

【図4】プロトコル制御部のフローチャートである。

【図5】シーケンス1を示す図である。

【図6】TCPヘッダフォーマットを示す図である。

【図7】TCP擬似ヘッダフォーマットを示す図である。

【図8】UDPヘッダフォーマットを示す図である。

【図9】UDP擬似ヘッダフォーマットを示す図である。

【図10】IPヘッダフォーマットを示す図である。

【図11】MACヘッダフォーマットを示す図である。

#### 【符号の説明】

#### 【0049】

30

101 アプリケーションデバイス

102 フレーム個数フレーム長算出部

103 ペイロード分割部

104 TXメモリ

105 ペイロード読み出し部

115 プロトコル制御部

116 TCPヘッダ生成部

117 UDPヘッダ生成部

118 IPヘッダ生成部

119 MACヘッダ生成部

120 ヘッダ/ペイロード合成部

121 フレーム送出部

40

【図1】

【図2】

【図3】

【図4】

プロトコル制御部フロー・チャート

【図5】

【図6】

【図7】

【図8】

UDPヘッダフォーマット

【図9】

UDP擬似ヘッダフォーマット

【図10】

IPヘッダフォーマット

【図11】

MACヘッダフォーマット

---

フロントページの続き

審査官 阿部 弘

(56)参考文献 特開2000-253054(JP,A)

特開2003-046566(JP,A)

特開平06-069957(JP,A)

特開2001-016226(JP,A)

特開2004-215203(JP,A)

特開平11-317762(JP,A)

特開昭63-099651(JP,A)

特開2004-241872(JP,A)

特開2001-339462(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04L 29/10