(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2011년11월09일

(11) 등록번호 10-1081477

(24) 등록일자 2011년11월02일

(51) Int. Cl.

H01L 21/302 (2006.01) H01L 21/306 (2006.01)

H01L 31/042 (2006.01)

(21) 출원번호 10-2008-7001917(분할)

(22) 출원일자(국제출원일자) 2001년11월29일

심사청구일자 2008년02월20일

(85) 번역문제출일자 2008년01월24일

(65) 공개번호 10-2008-0022218

(43) 공개일자 2008년03월10일

(62) 원출원 특허 10-2003-7007263

원출원일자(국제출원일자) 2001년11월29일

심사청구일자 2006년11월27일

(86) 국제출원번호 PCT/AU2001/001546

(87) 국제공개번호 WO 2002/45143

국제공개일자 2002년06월06일

(30) 우선권주장

PR 1748 2000년11월29일 오스트레일리아(AU)

(56) 선행기술조사문헌

US03985579 A1\*

JP07105518 B2

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 36 항

심사관 : 이창용

(54) 태양 전지의 제조를 위한 반도체 제조물

### (57) 요 약

본 발명은 실질적으로 평평한 표면 및 이러한 표면에 대하여 직각으로 두께를 갖는 반도체 웨이퍼의 사용 가능한 표면 구역을 증가시키는 방법이 제공된다. 이러한 방법은, 복수의 스트립으로 웨이퍼를 분할하기 위한 스트립 두께를 선택하는 단계, 상기의 실질적으로 평평한 표면에 대하여 소정의 각도로 웨이퍼를 스트립으로 커팅하기 위한 처리방식을 선택하는 단계 및 이와 같이 선택된 처리방식을 이용하여 각각 스트립을 분리하여 웨이퍼를 스트립으로 커팅하는 단계를 포함하며, 결합된 스트립 두께와 커팅되어 제거된 웨이퍼의 폭은 웨이퍼의 두께보다 작다.

### 대 표 도

## 특허청구의 범위

### 청구항 1

반도체 웨이퍼의 일부분을 포함하는 하나의 프레임 내에 수용되는 복수의 반도체 스트립들의 배열로 구성되는 태양 전지의 제조를 위한 반도체 제조물로서, 각각의 스트립은 슬롯에 의해 인접한 스트립들과 분리되며, 상기 웨이퍼의 두께는 스트립 두께와 슬롯 폭의 합보다 더 크며, 상기 슬롯들은 상기 웨이퍼를 관통하도록 연장된, 태양 전지의 제조를 위한 반도체 제조물.

### 청구항 2

제1항에 있어서,

상기 프레임은 상기 스트립들과 동일한 유형의 반도체로 구성되는, 태양 전지의 제조를 위한 반도체 제조물.

### 청구항 3

제2항에 있어서,

상기 프레임 및 상기 스트립들은 단일의 반도체 기판으로부터 제조되는, 태양 전지의 제조를 위한 반도체 제조물.

### 청구항 4

제3항에 있어서,

상기 기판의 두께는 1 mm인, 태양 전지의 제조를 위한 반도체 제조물.

### 청구항 5

제3항에 있어서,

상기 제조물은 이방성 습식 에칭에 의해 형성되는, 태양 전지의 제조를 위한 반도체 제조물.

### 청구항 6

제1항 내지 제5항 중 어느 한 항에 있어서,

상기 스트립들의 간격은 50  $\mu\text{m}$ 보다 작은, 태양 전지의 제조를 위한 반도체 제조물.

### 청구항 7

제1항 내지 제5항 중 어느 한 항에 있어서,

상기 스트립들 사이의 간격을 유지하기 위한 상호연결부가 존재하는, 태양 전지의 제조를 위한 반도체 제조물.

### 청구항 8

제1항 내지 제5항 중 어느 한 항에 있어서,

상기 스트립들의 두께는 250  $\mu\text{m}$ 보다 작은, 태양 전지의 제조를 위한 반도체 제조물.

### 청구항 9

제1항 내지 제5항 중 어느 한 항에 있어서,

상기 스트립들의 두께는 100  $\mu\text{m}$ 보다 작은, 태양 전지의 제조를 위한 반도체 제조물.

### 청구항 10

제1항 내지 제5항 중 어느 한 항에 있어서,

상기 스트립들의 폭은 1 mm인, 태양 전지의 제조를 위한 반도체 제조물.

**청구항 11**

제1항 내지 제5항 중 어느 한 항에 있어서,

상기 반도체는 실리콘인, 태양 전지의 제조를 위한 반도체 제조물.

**청구항 12**

제1항 내지 제5항 중 어느 한 항에 있어서,

상기 반도체는 다결정(multicrystalline) 실리콘인, 태양 전지의 제조를 위한 반도체 제조물.

**청구항 13**

제1항 내지 제5항 중 어느 한 항에 있어서,

상기 반도체는 싱글 크리스탈(single crystal) 실리콘인, 태양 전지의 제조를 위한 반도체 제조물.

**청구항 14**

제1항 내지 제5항 중 어느 한 항에 있어서,

상기 반도체는 모노크리스탈린(monocrystalline) 실리콘인, 태양 전지의 제조를 위한 반도체 제조물.

**청구항 15**

제1항 내지 제5항 중 어느 한 항에 있어서,

상기 스트립들은 적어도 부분적으로 유전체 물질로 코팅되는, 태양 전지의 제조를 위한 반도체 제조물.

**청구항 16**

제15항에 있어서,

상기 반도체는 싱글 크리스탈(single crystal) 실리콘, 모노크리스탈린(monocrystalline) 실리콘, 멀티크리스탈린(multicrystalline) 실리콘 및 폴리크리스탈린(polycrystalline) 실리콘 중 어느 하나인, 태양 전지의 제조를 위한 반도체 제조물.

**청구항 17**

제15항에 있어서,

상기 유전체는 실리콘 옥사이드(silicon oxide)인, 태양 전지의 제조를 위한 반도체 제조물.

**청구항 18**

제15항에 있어서,

상기 유전체는 실리콘 나이트라이드(silicon nitride)인, 태양 전지의 제조를 위한 반도체 제조물.

**청구항 19**

제1항 내지 제5항 중 어느 한 항에 있어서,

상기 스트립들은 그 표면의 적어도 일부가 도편트(dopant)를 가지고 확산되는, 태양 전지의 제조를 위한 반도체 제조물.

**청구항 20**

제19항에 있어서,

상기 도편트는 봉소(boron)인, 태양 전지의 제조를 위한 반도체 제조물.

**청구항 21**

슬롯들에 의해 적어도 부분적으로 상호 분리되는 복수의 반도체 스트립들을 포함하며, 상기 스트립들은 반도체 웨이퍼의 일부분을 포함하는 하나의 지지 프레임 내에 수용되는, 반도체 제조물로서, 상기 웨이퍼의 두께는 스트립 두께와 슬롯 폭의 합보다 더 크며, 상기 슬롯들은 상기 웨이퍼를 관통하도록 연장된 반도체 제조물.

### 청구항 22

제21항에 있어서,

상기 스트립들은 실리콘 스트립들이며 상기 프레임은 실리콘 프레임인, 반도체 제조물.

### 청구항 23

제21항에 있어서,

상기 프레임은 상기 스트립들과 일체인, 반도체 제조물.

### 청구항 24

제21항에 있어서,

상기 프레임의 폭은 5 mm인, 반도체 제조물.

### 청구항 25

제21항에 있어서,

상기 프레임은 상기 반도체 웨이퍼의 둘레(periphery)를 포함하는, 반도체 제조물.

### 청구항 26

제25항에 있어서,

상기 슬롯들은 그 자신의 길이 전체에 걸쳐 상기 반도체 웨이퍼를 완전히 관통하도록 연장되는, 반도체 제조물.

### 청구항 27

제25항에 있어서,

상기 웨이퍼는 하나의 완전한 웨이퍼이거나 또는 웨이퍼의 일부분인, 반도체 제조물.

### 청구항 28

제25항에 있어서,

상기 슬롯들은 그 자신의 길이 전체에 걸쳐 상기 반도체 웨이퍼를 부분적으로 관통하도록 연장되는, 반도체 제조물.

### 청구항 29

제21항에 있어서,

상기 슬롯들 각각의 폭은 10  $\mu\text{m}$  내지 20  $\mu\text{m}$  사이의 범위에 있는, 반도체 제조물.

### 청구항 30

제25항에 있어서,

상기 슬롯들은 상기 웨이퍼의 표면에 대해 각도를 가지도록 형성되며, 상기 각도는 5° 내지 90°의 범위에 있는, 반도체 제조물.

### 청구항 31

제30항에 있어서,

상기 슬롯들은 상기 웨이퍼의 표면에 대해 각도를 가지도록 형성되며, 상기 각도는 30°, 45°, 60° 및 90° 중

하나인, 반도체 제조물.

### 청구항 32

제21항에 있어서,

인접한 스트립들을 연결하는 적어도 하나의 상호연결부를 더 포함하며, 상기 상호연결부는 스트립인, 반도체 제조물.

### 청구항 33

제32항에 있어서,

상기 상호연결부의 폭은 0.1 mm 인, 반도체 제조물.

### 청구항 34

제32항에 있어서,

인접한 스트립들 사이의 복수의 상호연결부들을 포함하는, 반도체 제조물.

### 청구항 35

제34항에 있어서,

상기 상호연결부들 각각은, 0.1 mm 의 폭과 0.05 mm 의 높이를 가지며, 10 mm 의 간격을 갖는, 반도체 제조물.

### 청구항 36

제32항에 있어서,

상기 상호연결부들은 상기 인접한 스트립들의 길이를 따르는 규칙적인 간격을 가지고 이격된, 반도체 제조물.

### 청구항 37

삭제

## 명세서

### 발명의 상세한 설명

#### 기술 분야

[0001] 본 발명은 태양 전지의 제조를 위한 반도체 제조물에 관한 것이다.

#### 배경 기술

[0002] 거의 모든 반도체 제조공정에 있어서, 일반적인 것은 아니나 초기 기판 웨이퍼의 비용은 최종 처리된 웨이퍼의 비용과 비교된다. 예를 들면, 광발전의 태양 전지 산업은 비용에 대하여 매우 민감하여 일반적으로 초기 실리콘 웨이퍼의 비용은 처리된 웨이퍼 비용의 거의 반을 차지한다. 그러므로, 실리콘 기판이 가능한한 효과적으로 사용되는 것이 매우 중요하다. 이를 기판은 일반적으로 반경이 6 inch 결정체로된 원통형 실리콘을 얇은 조각으로 자름으로써 제조된다. 커팅될 수 있는 가장 얇은 조각은 실리콘의 물리적인 특성에 의하여 결정되며, 6 inch 웨이퍼의 현재 세대에 있어서 일반적으로 300 - 400 $\mu\text{m}$ 이다. 그러나, 차세대 웨이퍼는 200 $\mu\text{m}$ 가 예상된다. 그러나, 6 inch 웨이퍼를 자름으로써 발생되는 커프 로스(kerf loss)는 약 250 $\mu\text{m}$ 이며, 이는 대부분의 가공이 결국 분말로 된다는 것을 의미한다. 그러므로, 반도체의 주어진 단위 부피당 반도체의 사용가능한 평면을 증가시키는 방법 또는 현재의 반도체 제조 공정에 대한 효과적인 대안이 필요하다.

#### 발명의 내용

#### 과제 해결수단

[0003] 제1 관점에 따라, 하나의 프레임 내에 수용되는 반도체 스트립들의 배열로 구성되는, 태양 전지의 제조를 위한

반도체 제조물이 제공된다. 상기 프레임은 상기 스트립들과 동일한 유형의 반도체로 구성될 수 있다. 상기 프레임 및 상기 스트립들은 단일의 반도체 기판으로부터 제조될 수 있다. 상기 기판의 두께는 전형적으로 대략 1 mm 일 수 있다. 상기 제조물은 이방성 습식 에칭에 의해 형성될 수 있다.

상기 반도체 제조물은 상기 스트립들 사이의 간격을 유지하기 위한 상호연결부를 포함할 수 있다. 상기 스트립들의 두께는 50  $\mu\text{m}$  보다 작을 수 있다. 상기 스트립들의 두께는 250  $\mu\text{m}$  보다 작을 수 있다. 상기 스트립들의 두께는 100  $\mu\text{m}$  보다 작을 수 있다. 상기 스트립들의 폭은 전형적은 대략 1 mm 일 수 있다.

상기 반도체는 싱글 크리스탈(single crystal) 실리콘, 모노크리스탈린(monocrystalline) 실리콘, 멀티크리스탈린(multicrystalline) 실리콘 및 폴리크리스탈린(polycrystalline) 실리콘 중 어느 하나일 수 있다.

상기 스트립들은 적어도 부분적으로 유전체 물질로 코팅될 수 있다. 상기 유전체는 실리콘 옥사이드(silicon oxide)일 수 있다. 상기 유전체는 실리콘 나이트라이드(silicon nitride)일 수 있다. 상기 스트립들은 그 표면의 적어도 일부가 도편트(dopant)를 가지고 확산될 수 있다. 상기 도편트는 봉소(boron)일 수 있다. 상기 도편트는 인(phosphorus)일 수 있다.

제2 관점에 따라, 슬롯들에 의해 적어도 부분적으로 상호 분리되는 복수의 반도체 스트립들을 포함하며, 상기 스트립들은 하나의 지지 프레임 내에 수용되는, 반도체 제조물이 제공된다. 상기 스트립들은 실리콘 스트립들이며 상기 프레임은 실리콘 프레임일 수 있다. 상기 프레임은 상기 스트립들과 일체일 수 있다. 상기 프레임의 폭은 대략 5 mm일 수 있다. 상기 프레임은 반도체 웨이퍼의 둘레(periphery)를 포함할 수 있다.

상기 슬롯들은 상기 반도체 웨이퍼를 완전히 통하도록 형성될 수 있다. 상기 웨이퍼는 하나의 완전한 웨이퍼이거나 또는 웨이퍼의 일부분일 수 있다. 상기 슬롯들은 상기 반도체 웨이퍼를 부분적으로 통하도록 형성될 수 있다. 상기 슬롯들 각각의 폭은 10  $\mu\text{m}$  내지 20  $\mu\text{m}$  사이의 범위일 수 있다. 상기 슬롯들은 상기 웨이퍼의 표면에 대해 각도를 가지도록 형성되며, 상기 각도는 5° 내지 90°의 범위일 수 있다. 상기 슬롯들은 상기 웨이퍼의 표면에 대해 각도를 가지도록 형성되며, 상기 각도는 5° 내지 90°의 범위일 수 있다.

인접한 스트립들을 연결하는 적어도 하나의 상호연결부를 더 포함하며, 상기 상호연결부는 스트립일 수 있다. 상기 상호연결부의 폭은 대략 0.1 mm일 수 있다.

상기 반도체 제조물은 인접한 스트립들 사이의 복수의 상호연결부들을 포함할 수 있다. 상기 상호연결부들 각각은, 대략 0.1 mm의 폭과 대략 0.05 mm의 높이를 가지며, 대략 10 mm의 간격을 가질 수 있다. 상기 상호연결부들은 상기 스트립들의 길이를 따르는 규칙적인 간격을 가지고 이격될 수 있다. 상기 스트립들은 얇고 매우 좁을 수 있다.

[0004]

삭제

[0005]

삭제

[0006]

삭제

[0007]

삭제

[0008]

삭제

[0009]

삭제

[0010]

삭제

[0011] 삭제

[0012] 삭제

[0013] 삭제

[0014] 삭제

[0015] 삭제

[0016] 삭제

[0017] 삭제

[0018] 삭제

[0019] 삭제

[0020] 삭제

[0021] 삭제

[0022] 삭제

[0023] 삭제

[0024] 삭제

[0025] 삭제

[0026] 삭제

[0027] 삭제

[0028] 삭제

[0029] 삭제

[0030] 삭제

[0031] 삭제

[0032] 삭제

[0033] 삭제

[0034] 삭제

[0035] 삭제

[0036] 삭제

[0037] 삭제

### 발명의 실시를 위한 구체적인 내용

[0038] 다음에 설명할 도면은 숫자와 같은 참증부호에 의해 인용된다. 도면은 축적에 는 관계없이 단지 개략적으로 나타낸 것이다. 예를 들어, 더 분명하게는 도면은 반드시 슬롯, 스트립, 상호 연결부 및 서술된 방법에 의한 반도체 재료로 형성된 것과 같은 것을 모두 나타내지는 않는다.

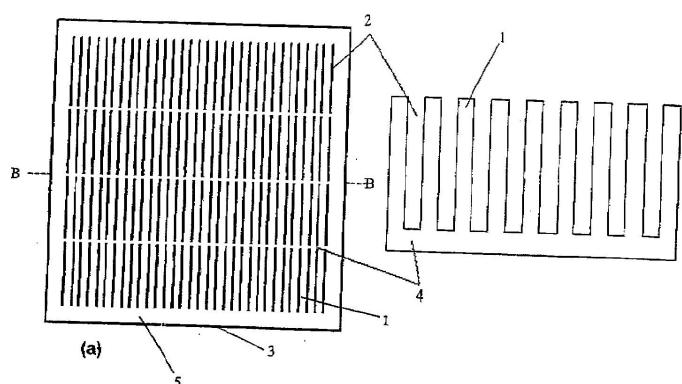

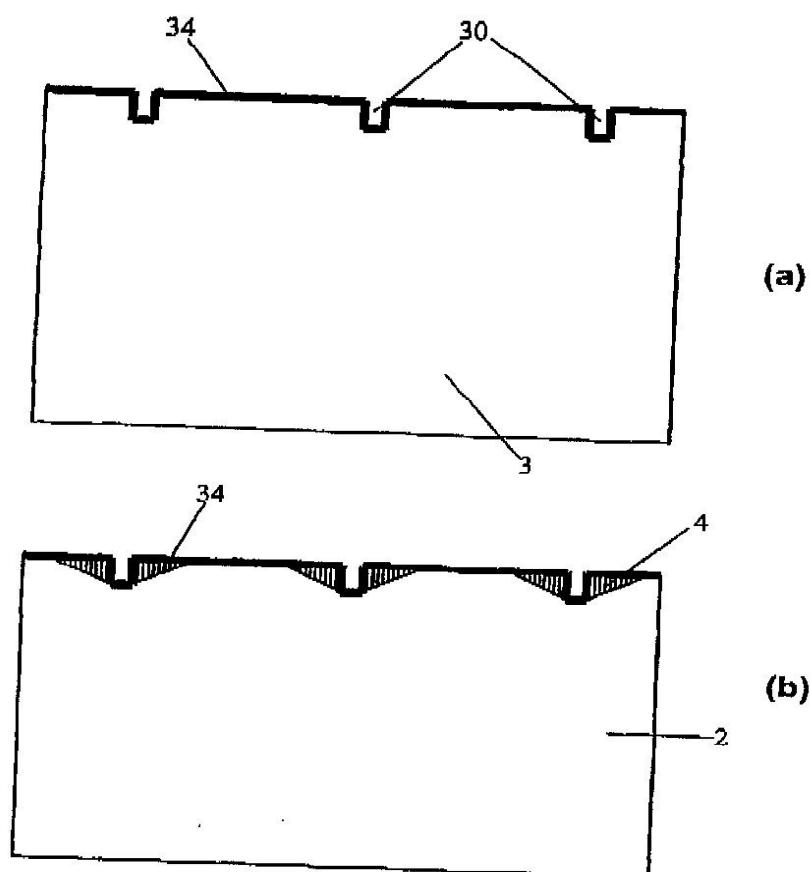

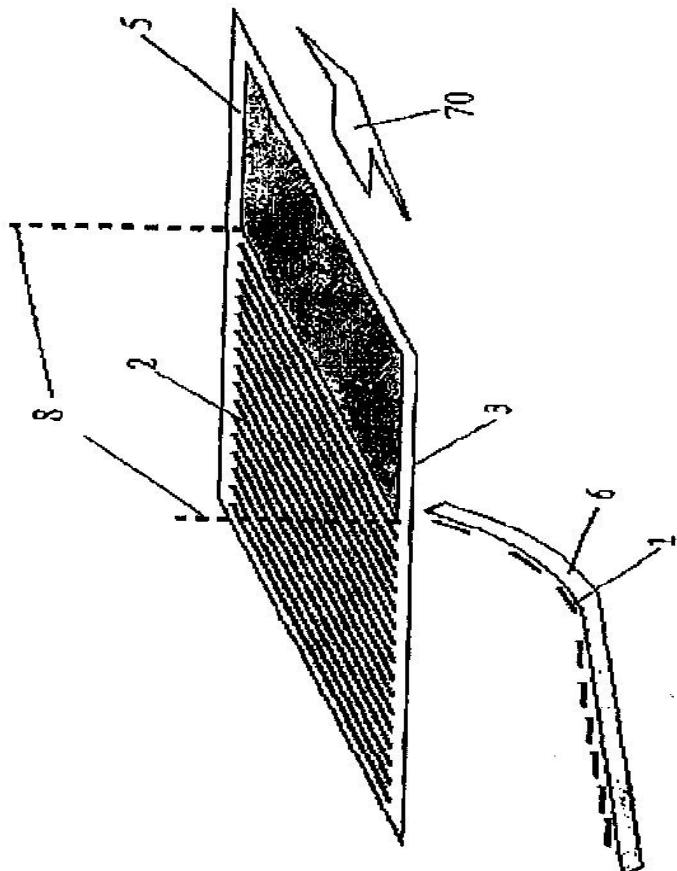

[0039] 도1(a)을 참조하면, 적어도 0.5mm 일반적으로 약 1mm의 두께를 가진 실리콘 웨이퍼(3)는 표준 결정 성장 및 웨이퍼링 기술에 의해 형성된다. 웨이퍼(3)은 다결정 웨이퍼가 사용될수 있지만, 단결정인 것이 바람직하다. 일련의 평행 채널이나 슬롯(2)은 일반적으로 0.05mm의 폭과 0.1mm의 간격을 가지고 웨이퍼(3)에서 형성되며, 실리콘(1)에 약 0.05mm 폭의 얇고 평행한 스트립을 형성한다. 슬롯(2)은 모든 방향의 웨이퍼(3) 모서리로 연장되지는 않으므로, 언커트(uncut)된 실리콘의 프레임(5)은 적소에 스트립(strip)을 고정시키게 된다. 프레임(5)은 일반적으로 각각의 면에서 5mm의 폭을 가진다.

[0040] 슬롯(2)은 좁은 블레이드가 구비된 다이싱 소(dicing saw)로 웨이퍼를 커팅하여 형성된다. 또한, 슬롯(2)은 레이저로 형성될 수도 있다. 예를 들어, 1046nm의 기본 파장이나 2배의 주파수(523nm)에서 작동하는 레조네틱(resonetics) Nd:YLF Q-스위치 레이저가 웨이퍼(3)를 커팅하는데 사용될 수 있다. 다른 시스템, 예를 들어 미국 특허 NO.5,773,791에 개시된 워터젯(water-jet) 레이저 절단 시스템과 같은 시스템도 또한 사용될 수 있다. 또한, 슬롯(2)은 당업자에게 널리 알려진, 수산화 칼륨 용액(KOH)과 같은 습식 이방성 에칭액(wet anisotropic etchant)을 사용하여 형성될 수 있다. 이 경우, 결정성장방향(110)인 단결정 실리콘 웨이퍼를 사용할 필요가 있다. 먼저, 실리콘 이산화물 또는 실리콘 질화물(nitride)과 같은 적절한 에칭 마스크(etch mask)가 웨이퍼(3)의 양측에서 성장되거나 적층된다. 포토리소그래피(photolithography)는 웨이퍼(3)의 일측 표면상의 에칭 마스크에 좁은 스트립을 형성하기 위해 사용되며, 이러한 스트립(stripes)은 일반적으로 0.005mm의 폭과 0.1mm의 간격으로 [1-1-2]의 방향을 따라서 성장한다. 웨이퍼(3)은 에칭 용액에 담가진다. 작업실 온도 또는 그 이상에서 진행되는 에칭에 적당한 용액은 44% w/v 수산화 칼륨의 수성용액이 적절하다.

[0041] 상기와 같은 어떤 방법도 웨이퍼(3)의 일측에서 또는 양측면에서 실시될 수 있으며, 더 두꺼운 웨이퍼도 사용될 수 있다. 예를 들어, 0.5mm의 실리콘을 제거할 수 있는 레이저를 사용할 때, 슬롯의 첫 세트는 1mm 두께 웨이퍼

의 전면에서 만들어진다. 이 웨이퍼는 이후 회전되어, 첫 세트와 정렬된 슬롯의 둘째 세트가 만들어진다. 또한, 슬롯의 양 세트는 샘플의 상부와 하부에 레이저 빔을 정렬시킴으로써 동시에 형성될 수도 있다.

[0042] 만약 다이싱 소나 레이저가 슬롯을 형성하는데 사용된다면, 공정을 가속시키기 위해 동시에 슬롯을 기판(substrate)으로 절단하는 하는 복수의 블레이드나 빔이 구비되는 것이 바람직하다. 예를 들어, 슬롯이 0.1mm의 간격으로 실리콘 웨이퍼 10x10cm상에 형성된다면, 천번의 커팅이 필요하다. 20개의 레이저 빔이 5mm 간격으로 샘플표면에 발사되도록 배열된다면, 각각의 빔은 단지 50번 커팅을 하게 된다.

[0043] 도1(b)는 스트립(1) 및 간격(space;2)을 나타낸 A-A선을 따라 웨이퍼(3)를 절단한, 확대 수직 단면도이다.

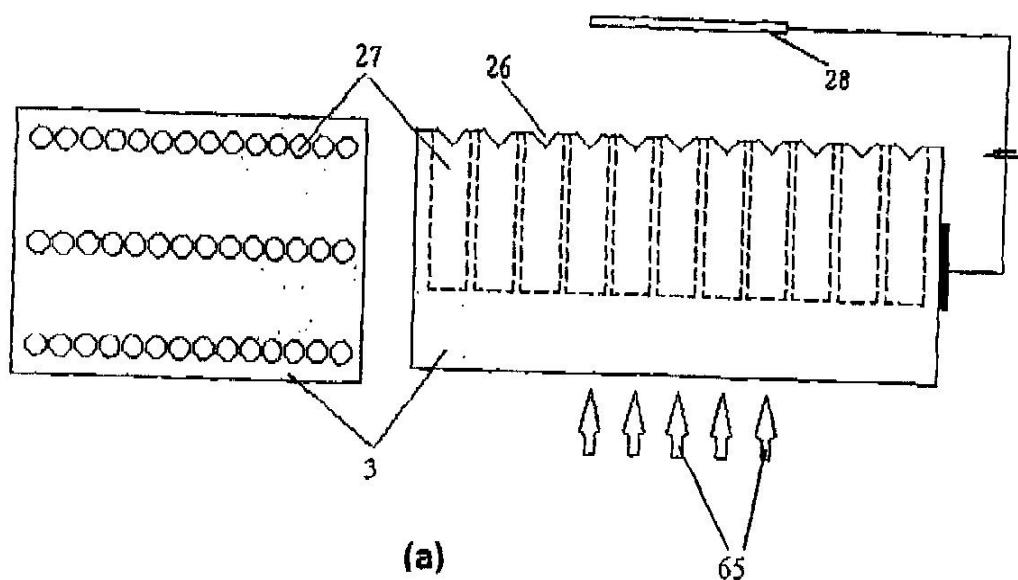

[0044] 도2(a) 및 도2(b)는 광 전기화학에칭(Photo-electrochemical Etching)에 의하여 기판에 슬롯을 형성하는 또 다른 방법을 나타낸다. 광 전기화학에칭은 레만(Lehmann; Journal of the Electrochemical Society, Vol.140, No10, (1993) p.2836)에 의해 고안되었다. 도 2(a)에 도시된 바와 같이, n-타입의 성장방향(100)인 실리콘 웨이퍼(3)가 사용된다. 웨이퍼(3)은 리소그래피 및 KOH 에칭에 의해 인덴트(indent:6)의 배열이 구비된다. 일반적으로 인덴트(26)의 열(row)간 간격은 50 마이크론이지만, 인덴트(26)간 간격이 대체로 5-10 마이크론으로 하여 인덴트(26)는 열을 따라서 배열된다. 웨이퍼(3)은 그 다음 10%의 플루오루화 수소산(hydrofluoric acid)용액과 같은 적당한 에칭액에 담가진다. 광원(65)은 웨이퍼(3)의 후방으로 직접 향하며, 양극 전압(positive bias voltage)이 웨이퍼(3)에 인가된다. 대응전극(28)은 웨이퍼(3)에 인접하여 용액에 위치한다. 이러한 조건하에서 일련의 미세통로(27)가 실리콘 웨이퍼(3)에 연장형성된다. 에칭은 미세통로(27)가 웨이퍼(3)를 관통해 모든 방향으로 연장될 때까지 계속된다.

[0045] 일련의 미세통로(27)가 구비된 실리콘 웨이퍼(3)는 그후, 수산화 칼륨 용액과 같은 실리콘 에칭액에 담가진다. 이로써, 미세통로(27)가 연장된다. 도 2(b)에 도시된 바와 같이, 에칭이 계속되면 미세통로(27)는 웨이퍼(3)을 관통하여 연장되는 슬롯(2)을 형성하도록 합체된다. 이러한 기술에 의하여, 폭이 10마이크론 보다 작은 좁은 슬롯(2)이 형성될 수 있다.

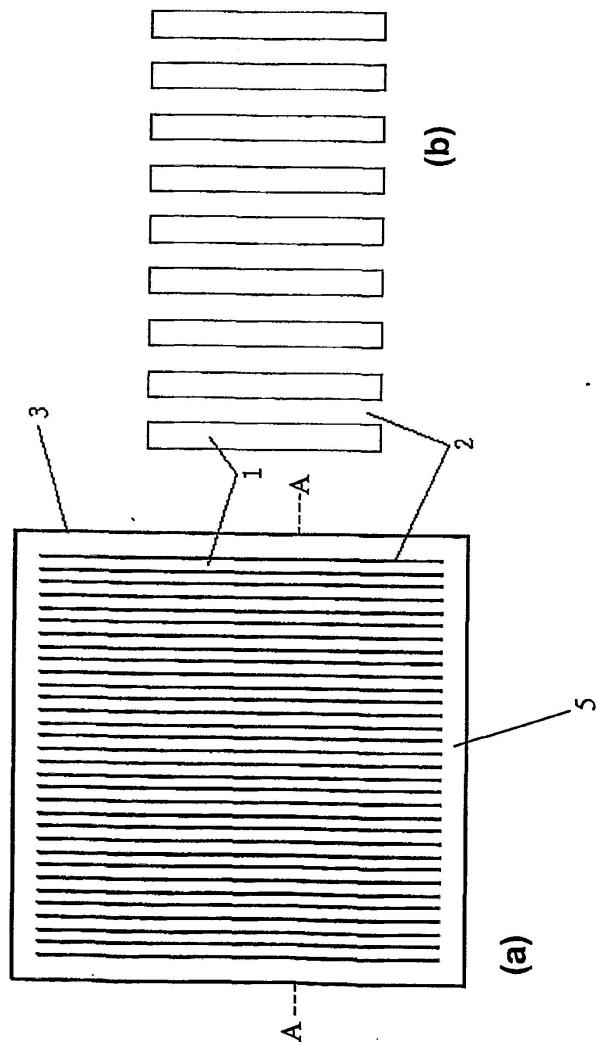

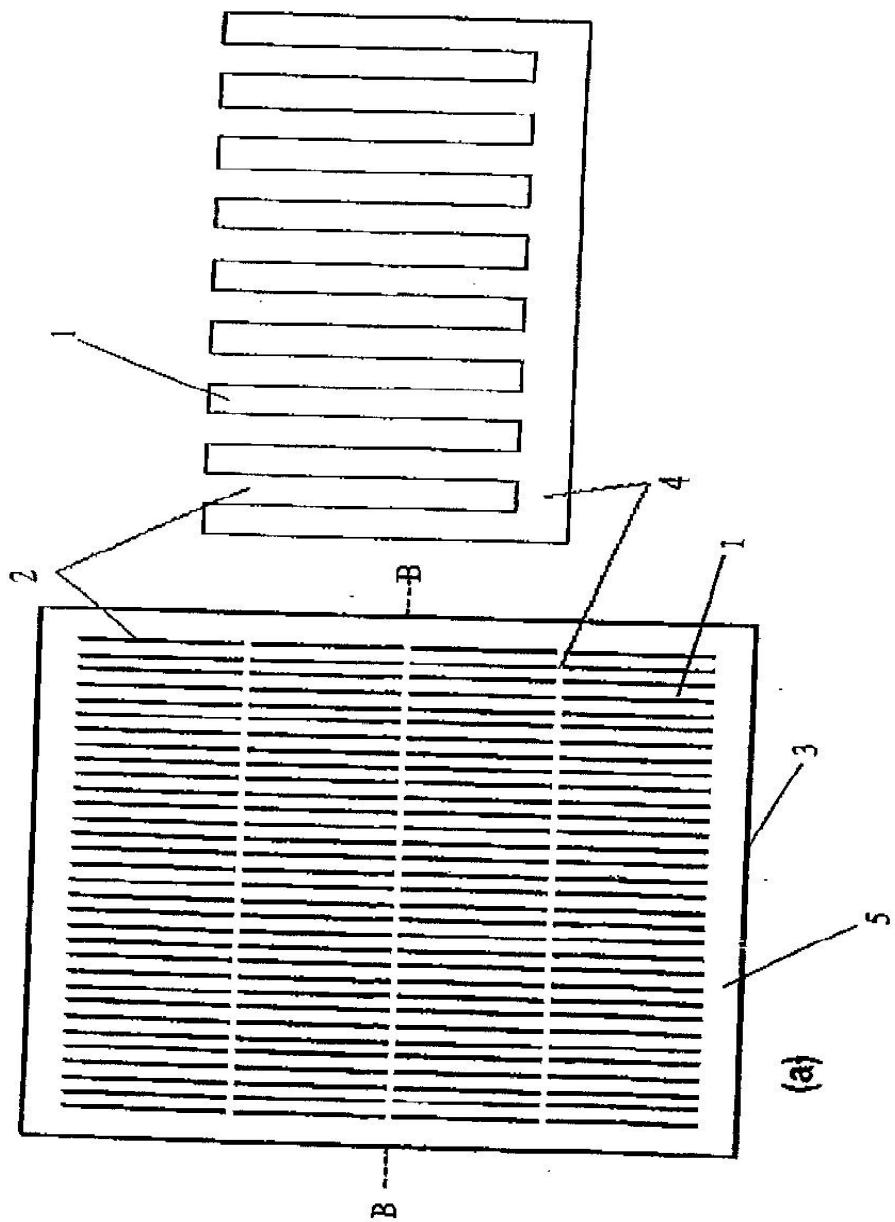

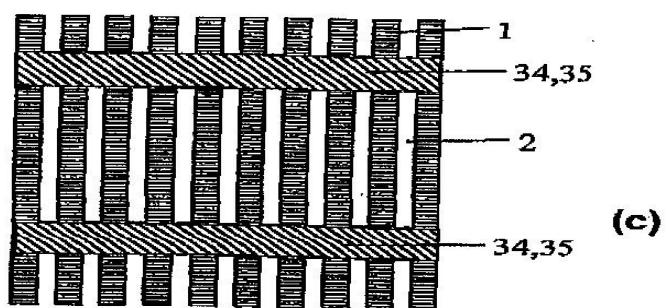

[0046] 제1 내지 제3 실시예에 의한 방법의 다른 형태에 의하면, 슬롯을 따라 일정한 간격으로 슬롯 길이의 대부분에 걸쳐서, 웨이퍼를 관통하는 모든 방향으로 슬롯이 연장되나, 일련의 연결 스트립을 형성하기 위하여 그루브 저면에 약간의 기판이 남도록 슬롯은 완전히 관통하지는 않는다. 이것은 도 3(a) 및 도 3(b)에 나타난다. 도 3(a)는 프레임(5)의 반대면에서 웨이퍼(3)를 가로지르는 연결스트립(4)을 보여주는 웨이퍼(3) 하부를 나타낸 도면으로, 슬롯(2)은 대부분의 길이에 걸쳐서 웨이퍼(3)를 관통하여 연장된다. 도 3(b)는 도 3(a)의 B-B선을 따른 수직단면도이다. 도 3(a)와 도 3(b)에서 나타난 구조는 레이저 제거(ablation) 방법에 의해 제작될 수 있다. 연결스트립(4)은 다른 공정 중 실리콘 스트립(1)의 벤딩 정도를 제한함으로써 슬롯의 폭 변화를 제한한다. 이것은 이하 설명하는 바와 같이, 스트립(1)의 측벽이 확실하게 형성될 수 있도록 한다. 연결 스트립(4)은 일반적으로 0.1mm의 폭, 0.05mm의 높이, 및 10mm의 간격으로 된다.

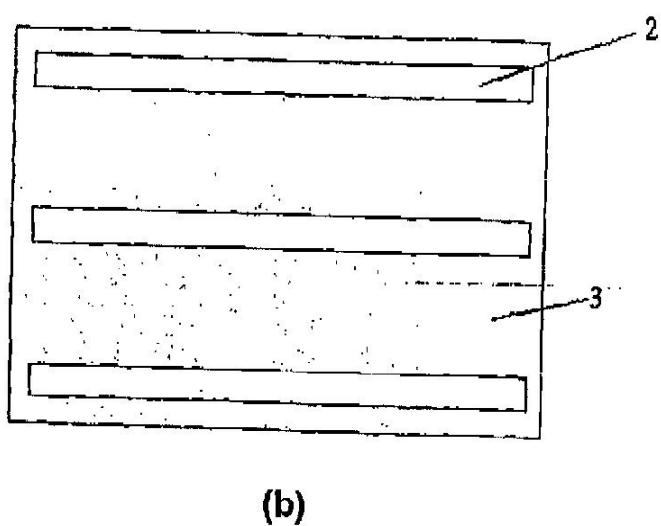

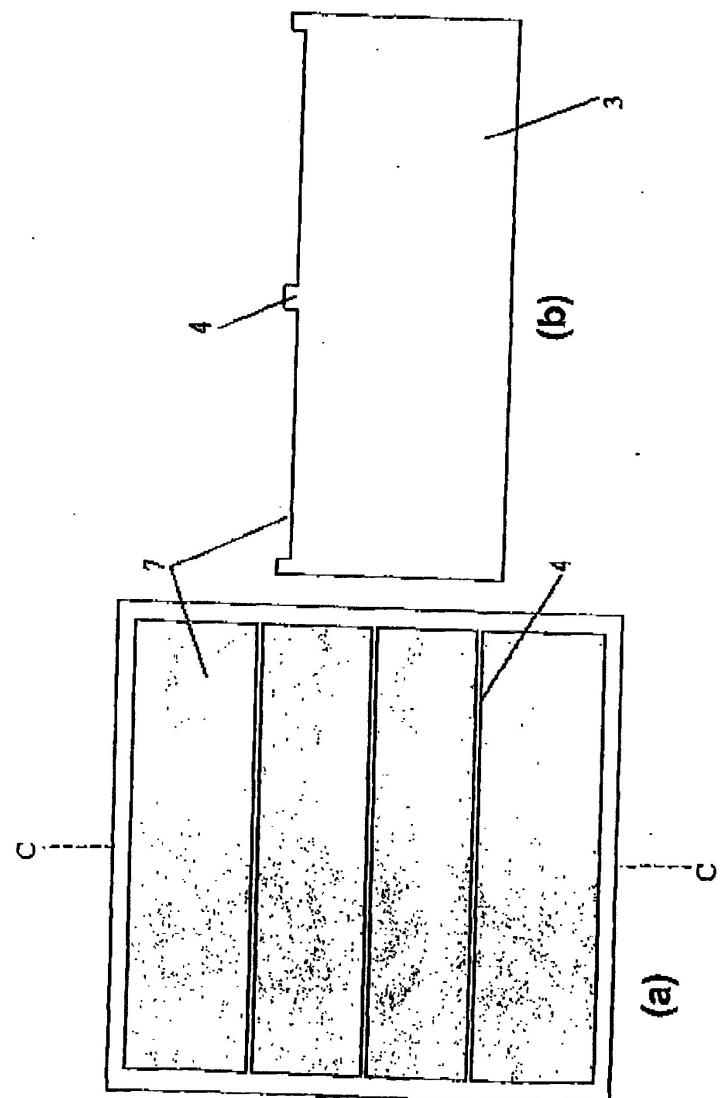

[0047] 제 1내지 제 3실시예에 의한 방법의 또 다른 형태에 의하면, 도 4(a), 4(b) 및 5에 도시된 바와 같이, 트렌치(trench;7)은 화학적 습식에칭, 플라즈마 에칭 또는 넓은 블레이드를 가진 다이싱 소를 사용한 기계적 연마 등 적당한 기술에 의해 실리콘 웨이퍼(3)에 형성된다. 트렌치(7)는 그러한 방법으로 형성되어서 일련의 등간격 연결스트립(4)으로 된다. 트렌치(7)는 일반적으로 0.05mm의 깊이이며 연결스트립(4)은 일반적으로 0.1mm 폭과 10mm 간격으로 형성된다.

[0048] 슬롯(2)은 그후 도 5에서 나타나듯이, 다이싱 소나 KOH 에칭을 사용함으로써 트렌치(7)가 형성되는 웨이퍼(3)의 반대면에서 정면까지 웨이퍼(3)에 형성된다. 슬롯(2)은 연결스트립(4)의 모든 방향으로의 영역이 아닌, 트렌치(7)가 형성되는 영역에서 웨이퍼(3)를 관통하여 모든 방향으로 연장된다. 도 3(a) 및 도 3(b)를 참조하여 상기한 바와 같이, 연결스트립(4)는 실리콘 스트립(1)의 벤딩 정도를 제한하며, 실리콘 스트립(1) 사이의 슬롯(2)의 폭 변화를 제한한다. 웨이퍼의 거의 모든 방향으로 연장되는, 첫 번째 슬롯을 형성함으로써, 슬롯과 트렌치 형성 단계의 순서를 역으로 하는 것이 가능하며, 이후 웨이퍼의 다른면에서 트렌치를 형성하게 된다.

[0049] 본 발명에 따른 또 다른 형성방법은 도 6(a), 6(b) 및 7에 도시된다.

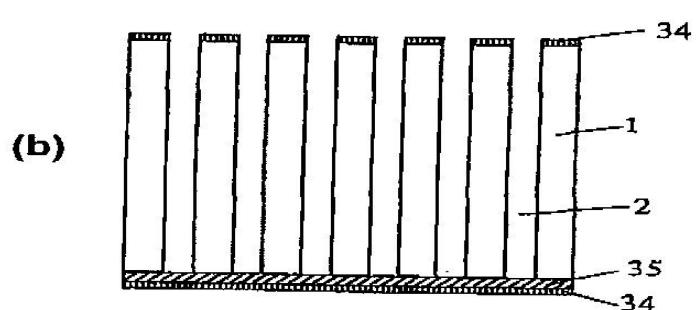

[0050] 도 6(a)는 다이싱 소나 레이저와 같은 적당한 기술에 의해 일련의 얇은 그루브(30)가 형성된 실리콘 웨이퍼(3)의 단면도를 나타낸다. 그루브(30)은 일반적으로 20마이크론의 깊이, 50마이크론의 폭과 10mm의 간격을 가진다. 실리콘 이산화물과 실리콘 질화물과 같은 적당한 에칭마스크(34)는 그후 표면에 적층된다. 이후, 슬롯(2)은 전술한 포토리소그래피 또는 KOH 에칭 방법을 사용하여 웨이퍼(3)에서 에칭된다. 슬롯(2)은 웨이퍼(3)의 정면에서 그루브(30)를 포함하는 반대면까지 에칭된다. 그루브(30)는 슬롯(2)에 직각으로 형성된다. 이로써, 도 6(b)에서

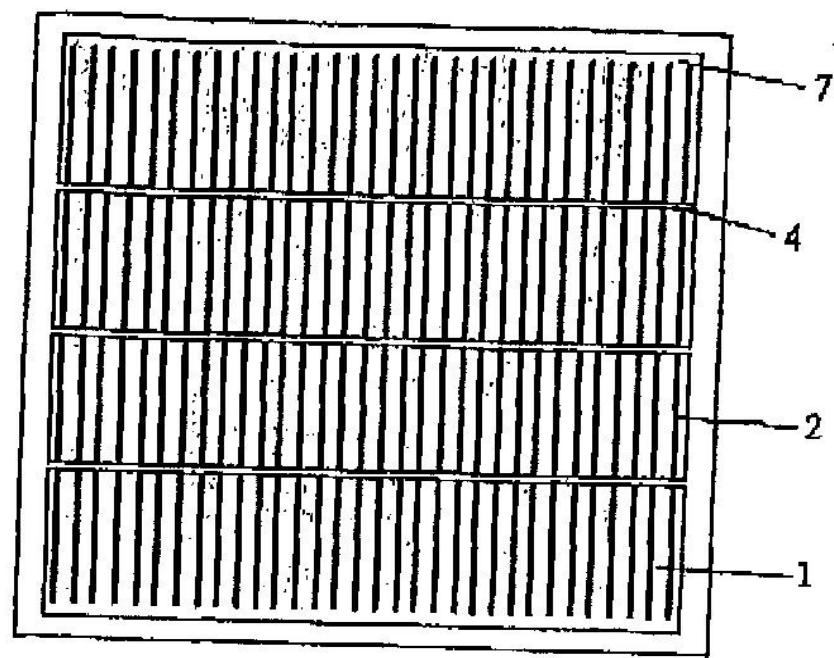

나타나듯이, 에칭과정의 완료후, 후면에 남아있는 실리콘은 연결스트립(4)으로 된다. 연결스트립(4)은 도 6(a)에서 나타난 단면에 직각인 슬롯(2) 중 하나를 관통한 단면이 된다. 연결스트립(4)은 실리콘 스트립(1)의 벤딩 정도를 제한함으로써, 슬롯의 폭 변화를 제한한다. 도 6(b)는 에칭완료후의 구조에 대한 단면도이다. 도7은 그루브(30)을 포함하는 웨이퍼(3)의 측면에서 볼 때, 잔존구조에 대한 평면도이다. 이것은 웨이퍼(3)의 에칭의 결과로 나타난 실리콘 스트립(1)과 슬롯(2)을 보여준다. 실리콘 스트립(1)의 벤딩정도를 제한하는 연결스트립(4)은 등간격으로 존재한다(도면에는 일정부분만 나타남).

[0051] 제1 내지 제3 실시예에 의한 방법의 다른 형태가 도 8(a)내지 8(c)에 도시된다.

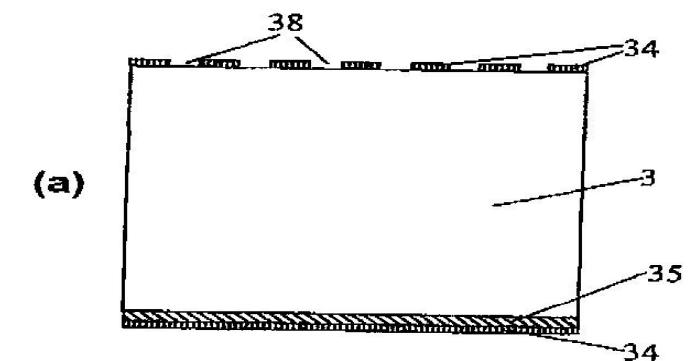

[0052] 도 8(a)는 성장방향(110)인 실리콘 웨이퍼(3)의 일부분을 나타낸 단면도이다. 에칭마스크(34)가 웨이퍼의 양측 표면에 적층된다. 일반적으로 에칭마스크(34)는 다량의 실리콘 이산화물과 실리콘 질화물로 구성되며, 각각의 층은 일반적으로 50-100nm의 두께를 가진다. 에칭마스크(34)는 폭이 좁은 일련의 라인 오프닝(38)을 형성하도록 정면에서 패턴(pattern)화 되며, 라인오프닝을 통하여 실리콘 웨이퍼의 기판(3)이 노출된다. 배면쪽에는 일반적으로 두께가 0.5 - 5 마이크론인 두꺼운 산화물(35)이 에칭마스크(34)가 적층되기 전에 형성된다. 산화물층(35)은 예를 들어 열적 산화, 화학적 증착 또는 스피온글라스(spinon glass)와 같은 다양한 기술에 의해 형성될 수 있다. 산화물은 일련의 산화물 스트립(미도시)을 형성하도록 패턴화되며, 스트립은 평면에서 에칭마스크(34)의 오프닝(38)에 대하여 수직으로 배향된다.

[0053] 도 8(b)는 KOH로 에칭하는 도 8(a)의 구조에 대한 단면도이다. 슬롯(2)은 일련의 실리콘 스트립(1)을 형성하도록 에칭된다. 슬롯(2)은 웨이퍼(3)의 상부표면에서 에칭마스크(34)의 라인오프닝(38)을 통하여 에칭된다. 후방 에칭마스크(34) 하부의 산화물(35)는 비교적 두껍고 산화물(35)은 KOH 에칭용액에 의해 서서히 에칭되므로, 산화물(35)은 에칭과정후 남게 되며 실리콘 스트립(1)사이에 일련의 연결스트립을 생성하게 된다. 연결스트립은 실리콘 스트립(1)의 벤딩정도를 제한함으로써 슬롯의 폭변화도 제한하게 된다.

[0054] 도 8(c)는 도 8(b)의 단면으로 나타난 구조의 평면도이며, 실리콘 스트립(1)과 슬롯(2)을 나타낸다. 등간격으로 에칭마스크(34)와 에칭마스크 하부의 산화물(35)은 연결스트립을 생성하며, 연결스트립은 실리콘 스트립(1)의 벤딩정도를 제한함으로써 슬롯의 폭변화도 제한하게 된다.

[0055] 전술한 구조가 형성된 후, 모든 웨이퍼는 아래에 기술될 태양전지(solar cell)을 형성하기 위해 제조 될 수 있다. 웨이퍼의 후속공정과 지지프레임에서 실리콘 스트립을 분리하기에 앞서, 존재할 수도 있는 연결스트립이 필요하다면 제거된다. 이 과정은 예를 들어 레이저 제거로 실시될 수 있다. 만약 연결스트립이 아주 얇다면 실리콘 스트립이 지지프레임에서 분리될 때 부서지게 되어, 연결스트립의 제거는 불필요할 수도 있다. 이후, 실리콘 스트립은 지지프레임에서 분리되며, 도9에서 나타난 것과 같은 배열수단에 의해 평평하게 안장된다. 도9에서 나타나듯이, 웨이퍼(3)는 프레임(5)에 지지되며 슬롯(2)의 직각 방향(70)을 따라 움직인다. 두 고정 레이저빔(8)은 실리콘 스트립(1)의 어느 한 끝단에서 실리콘을 제거하며, 이러한 결과로 프레임(5)에서 실리콘 스트립이 분리된다. 웨이퍼(3) 하부의 포획기(catcher;6)는 분리된 스트립(1)을 포획하며 적당한 기판위와 경사를 따라서 움직이도록 위치한다. 이러한 배치로 최소한의 조작으로, 상기 스트립(1)이 평평하게 안장되며, 이후 공정을 준비하게 한다.

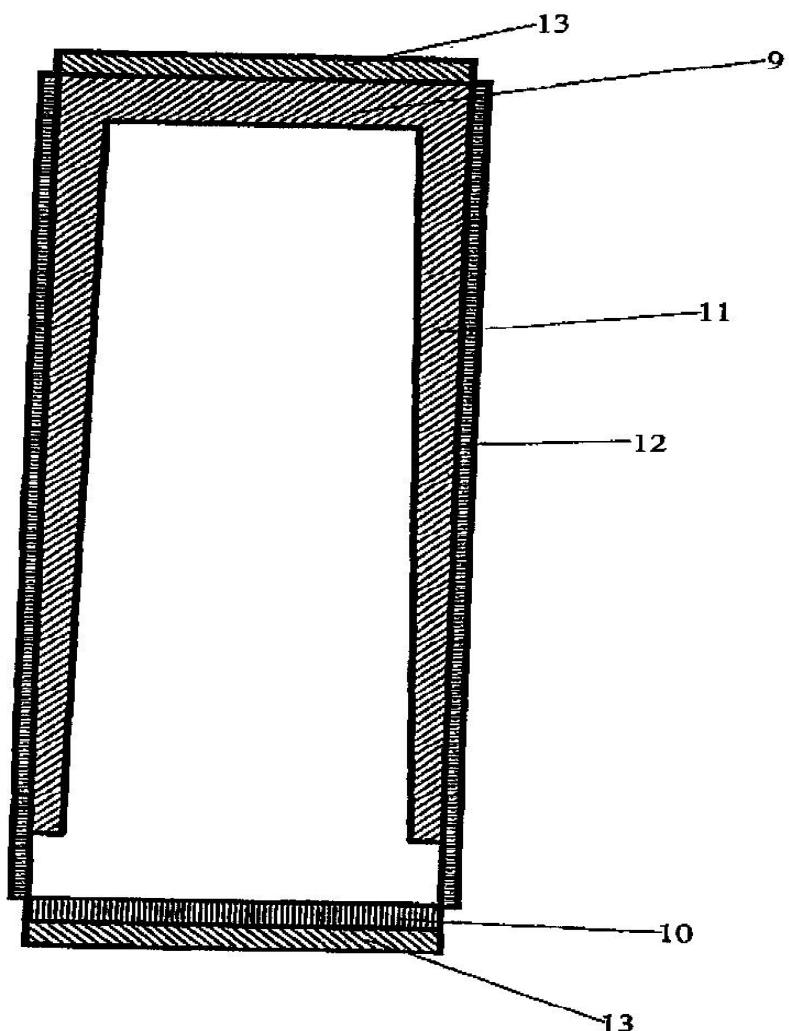

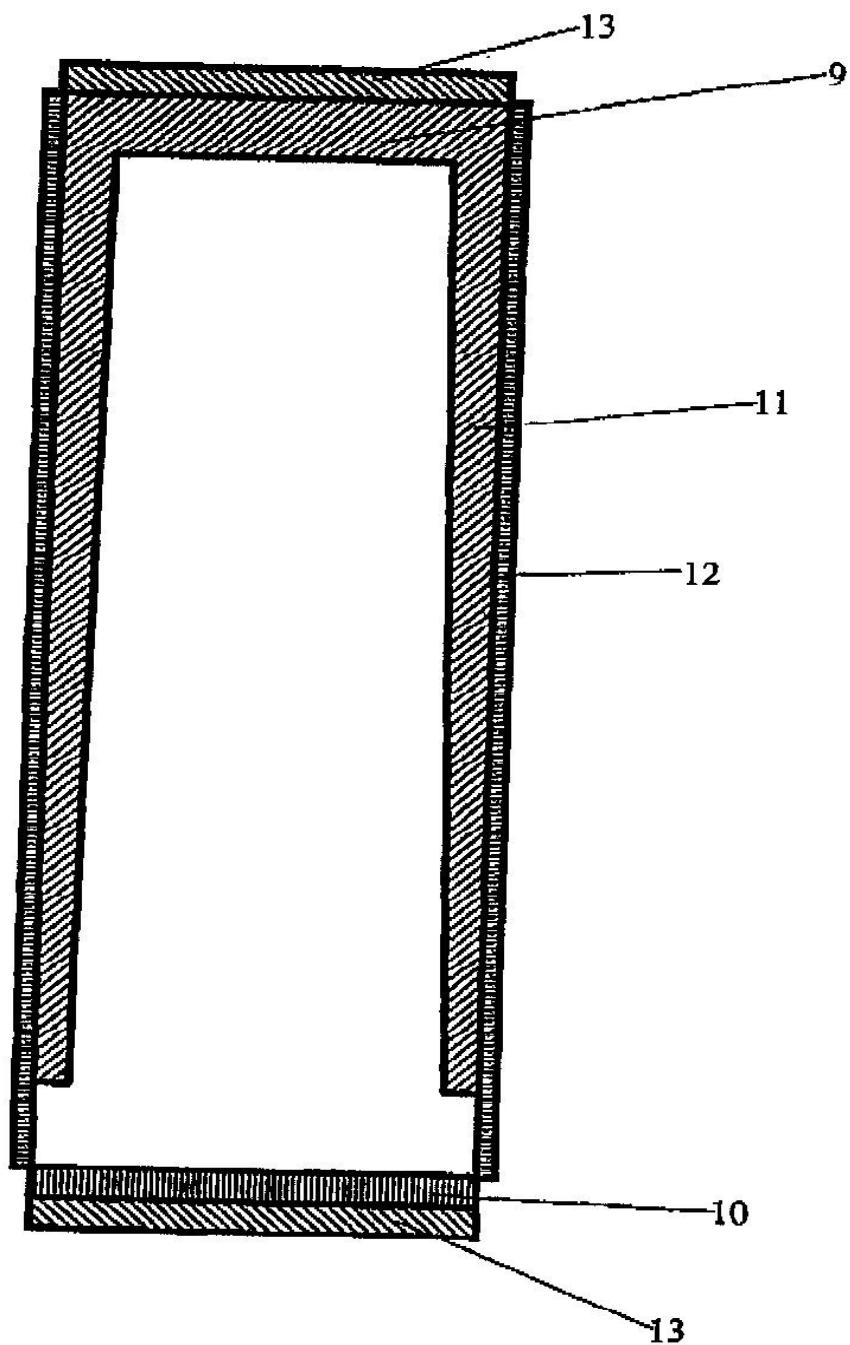

[0056] 태양전지(solar cell)은 도 10에 나타난 후속 공정에 의해 실리콘 스트립(1)으로 제조될 수 있다. 도10은 웨이퍼의 일단에서 고밀도 봉소화산층(10)을 구비하고, 타단에서 고밀도 인화산층(9)을 구비하며, 다른 두 측면에서 저밀도 인화산층(11)을 구비하며, 일반적으로 취득되는 스트립(1)을 예로 나타낸다. 측면은 산화물 층(12)으로 코우팅(증착)된다. 금속성 접촉물(13)은 스트립(1)의 각 끝부분에 적층된다. 스트립(1)은 다음에 기술할 내용에 따라서 제조될 수 있다. 초기 웨이퍼는 저항이 대략 1 ohm-cm로 p-type이다. 고밀도 인화산층(9; 일반적으로 10 ohm/square)은 웨이퍼의 일측면에서 만들어지며, 그 다음은 고밀도 봉소화산층(10; 일반적으로 20 ohm/square)이 반대면에서 만들어진다. 얇은 산화물(약 50 nm)은 웨이퍼의 양측면에서 성장하며, 그후 LPCVD 실리콘 질화물의 얇은 층(약 50nm)이 웨이퍼의 각 측면에 적층된다. 슬롯은 그후 상술한 바와 같이 웨이퍼에서 형성된다. 만약 다이싱 소나 레이저가 사용된다면, 슬롯은 스트립의 측벽을 청소하고 어떠한 잔여 손상도 없애기 위해 작업실 온도에서 20%의 KOH 와 같은 적당한 용액으로 에칭된다.

[0057] 측벽은 적당한 텍스처링으로 가공될 수 있다. 평방 스퀘어당 200ohm 정도의 저밀도 인화산층(11)은 도펜트(dopant)에 노출된 웨이퍼의 양쪽면으로 만들어져서, 측벽은 전체적으로 n-도프(n-doped)로 된다. 그다음은 대략 200nm 두께의 산화물(12)이 노출된 측벽에서 성장한다. 그후, 질화물층은 반응이온 에칭 또는 예를 들어 대략 180° C의 고온 인산과 같은 적당한 질화물 에칭방법을 사용함으로써, 웨이퍼의 전방과 후방에서 벗겨지게 된다. 그때, 질화물 아래의 얇은 산화물은 플루오르화수소산 용액으로 제거된다. 저밀도 인화산층을 덮는 산화

물(12)은 질화물 아래의 산화물보다 훨씬 두꺼우므로, 이러한 예정에 의해 제거되지 않는다. 금속(13)은 측벽 하부의 금속이 최소화하는 방식으로 웨이퍼의 양쪽면에 적층된다. 이것은 예를 들어, 진공증발 시계선(line of sight vacuum evaporation)과 같은 것에 의해 실현될 수 있다.

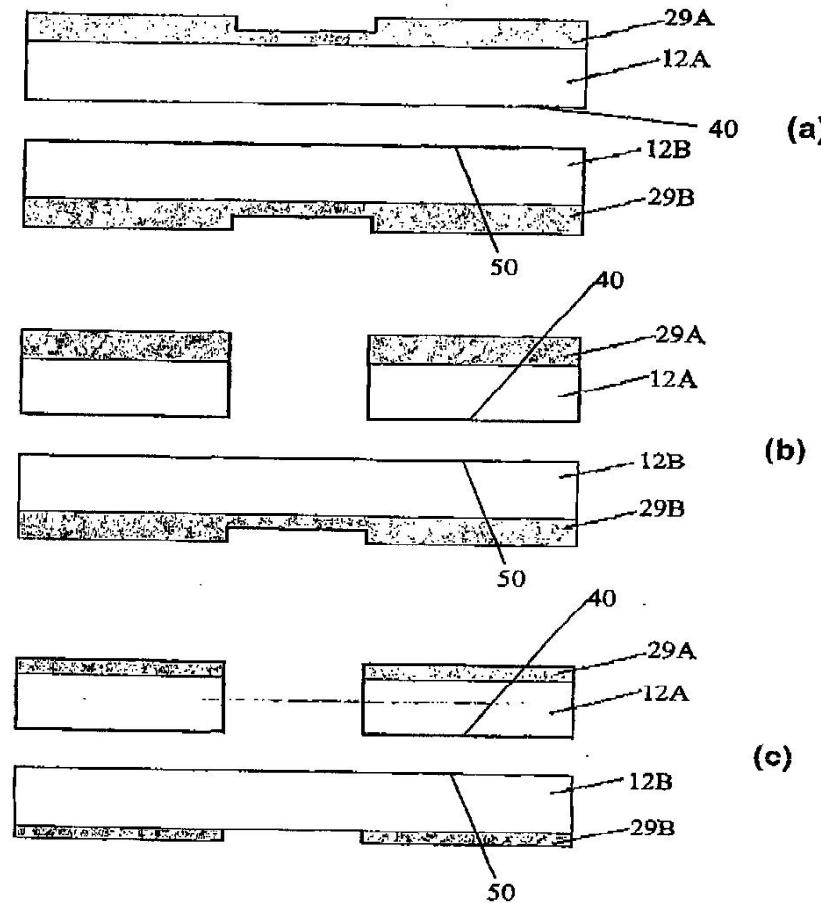

[0058] 도11에 나타나듯이 태양전지를 제조하는 또 다른 공정에 있어서, 인(9)과 봉소(10)가 결정성장방향(110)인 웨이퍼의 전방과 후방면으로 각각 확산되며, 실리콘 이산화물과 실리콘 질화물층은 이미 언급한 바와 같이 웨이퍼의 양 표면에 적층된다. 레이저 제거나 포토리소그래피/예정을 사용함으로써, 방향[1-1-2]를 따라서 진행되는 스트립은 상부 산화물과 질화물층에 노출된다. 그때, 웨이퍼는 그루브가 일반적으로 후방표면이 50 마이크론이내에서 예정될때까지 KOH 용액에 위치한다. 단위 스퀘어당 일반적으로 200ohm의 저밀도 인화산층(11)이 그루브로 만들어지며, 일반적으로 150nm 두께의 산화물(12)이 성장하게 된다. 그때, 그루브를 따라서 배열된 스트립은 상술한 바와 같이, 후방표면의 산화물과 질화물층에서 노출된다. 웨이퍼의 모든 방향으로 연장된 슬롯을 생산하기 위해, 웨이퍼의 후방에서 예정된 새로운 그루브가 전방면에서 생성된 그루브와 결합될때까지 다시 KOH용액에 담가진다. 그때, 얇은 산화물(12)은 아직 산화물로 덮히지 않은 측벽의 단면을 관통하여 성장한다. 그때, 전방과 후방표면의 질화물과 산화물층은 벗겨지고 접촉금속(13)이 전방과 후방표면에 적층된다. 이 셀 구조는 다음의 한 단계 포토리소그래피를 사용함으로써 실현될 수 있다. 전방과 후방표면의 산화물과 질화물 적층 후, 양 표면은 포토레지스트로 코팅되며, 정렬된 스트립 패턴이 양 레지스트 층에서 포토리소그래피에 의하여 형성된다. 이것은 웨이퍼의 상부에 하나, 하부에 다른 하나로, 두 정렬된 마스크가 동시에 노출되도록 배열함으로써, 하나의 노출단계로 실현될 수 있다. 포토레지스트가 현상된 후에, 웨이퍼는 더 늦게 진행되기는 하지만, 실리콘 이산화물뿐만 아니라 실리콘 질화물을 예정하는 완충 HP 용액에 담가진다. 전방표면(40)과 후방표면(50) 각각의 산화물층 12A와 12B 및 질화물층 29A와 29B의 개략적인 도면 12(a)에서 나타나듯이, 질화물층 두께의 절반정도가 예정될때, 웨이퍼가 예정용액에서 제거된다(포토레지스트 층은 미도시). 그때, 후방표면(50)은 예를 들어, 포토레지스트의 추가층(further layer)의 적층으로 더 이상 예정되지 않는다. 도 12(b)에서 나타나듯이 스트립에서 질화물 29A 및 산화물 12A가 완전히 제거될때까지, 웨이퍼는 다시 예정용액에 담가지며 전방표면(40)에 그루브를 형성하도록 KOH 예정이 실시될 수 있다. 후방표면(50)에 스트립 마스크를 형성하기 위해, 웨이퍼는 고온 인산에 담가지며 도12(c)에서 나타나듯이, 부분적으로 예정된 트렌치에서 잔존 질화물이 제거된다. 웨이퍼는 후방표면(50)의 스트립에서 잔존하는 산화물 12B를 제거하기 위해 HF 용액에 담가진다. 이것은, 질화물의 예정률(etch rate)이 산화물의 예정률보다 훨씬 낮기 때문에, 질화물 층에 크게 영향을 미치지 않는다. 그때, 웨이퍼는 실리콘 웨이퍼의 후방표면(50)에서 그루브를 웨이퍼내로 예정하기 위하여, KOH 용액에 담가질 수 있다. 상술한 바와 같이, 스트립은 전방과 후방 실리콘의 예정 앞부분이 서로 만난후 형성된다.

[0059] 일단 웨이퍼가 가공되어 스트립이 각각 분리되면, 스트립은 적당한 기판위에 평평하게 안장된다. 셀은 직렬로 혹은 병렬로, 고정집중광(static concentration)이 사용되는 경우 셀 사이의 틈(gap) 중 어느하나에, 혹은 셀사이의 틈이 없이도, 연결될 수 있다.

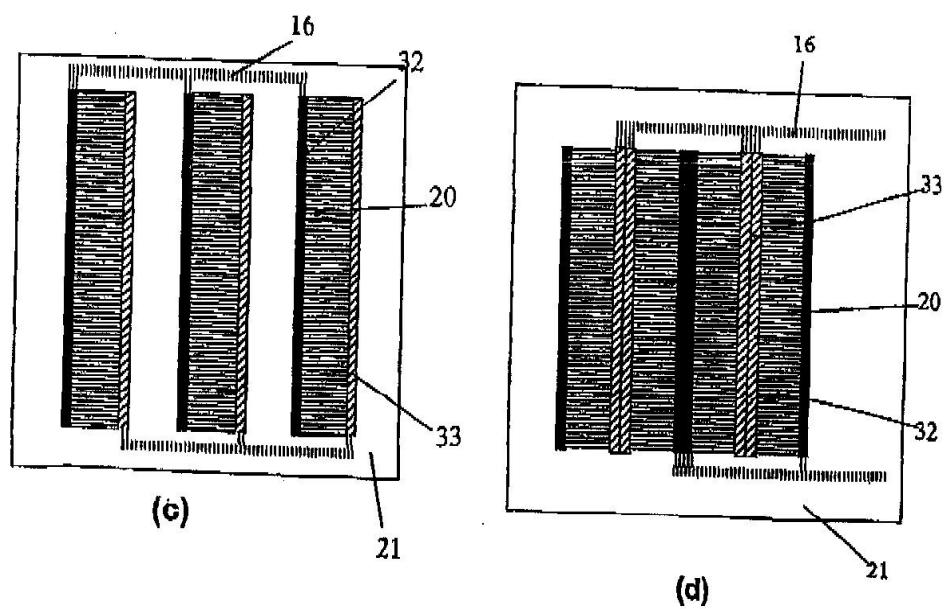

[0060] 도 13(a)는 셀사이의 틈이 없이 직렬연결 되도록 하는 방법을 나타낸다. 셀(20)은 하나의 셀의 p극 접촉부(32)가 인접셀의 n극 접촉부(33)에 인접하게 기판(21)상에 배열된다. 그때, 전기적 연결은 하나의 셀의 p극 접촉부를 다음 셀의 n극 접촉부에 연결하도록 만들어진다.

[0061] 도 13(b)는 셀사이에 틈이 있으며 직렬로 연결된 방법을 나타낸다. 셀(20)은 도면에서 나타나듯이, 기판(21)상에 배열된다. 전기적 전도 트랙(16)은 하나의 셀의 p극 접촉부(32)가 인접셀의 n극 접촉부(33)에 전기적으로 연결되도록 형성된다.

[0062] 도 13(c)는 셀사이에 틈이 있으며 병렬로 연결된 방법을 나타낸다. 셀(20)은 도면에서 나타나듯이, 기판(21)상에 배열된다. 모든 p극 접촉부(32)가 셀의 한쪽 끝부분에 모두 전기적으로 연결되며, 그 반면 모든 n극 접촉부(33)는 셀의 다른쪽 끝부분에 모두 전기적으로 연결되도록 전기적 전도 트랙(16)이 형성된다.

[0063] 도 13(d)는 셀사이에 틈이 없이 병렬로 연결된 방법을 나타낸다. 셀(20)은 도면에서 나타나듯이, 기판(21)상에 배열된다. 매 두번째 셀은 p극 접촉부(32)와 n극 접촉부(33)의 순서가 역으로 되도록 향한다. 전기적 전도 트랙(16)은, 모든 p극 접촉부(32)가 셀의 한쪽 끝부분에 모두 전기적으로 연결되며, 그반면 모든 n극 접촉부(33)는 셀의 다른쪽 끝부분에 모두 전기적으로 연결되도록, 형성된다.

[0064] 가능한 많은 다른 배열뿐만 아니라, 도 13(b)-(d)의 배열은 전기적 전도 트랙이 셀이 장착되는 기판상에 형성되는 것이 필요하다. 트랙은 기판에서 셀이 배치되기 전후로 형성될 수 있다. 만약 트랙이 기판상에서 셀이 배치되기 전에 형성된다면, 트랙은 스크린 프린팅, 금속 증발(metal evaporating) 또는 스퍼터링(sputtering)과 같이 잘 알려진 기술 중 어느 하나를 사용함으로써 형성될 수 있다. 하나의 가능한 접근법은 필요한 트랙을 형성

하도록 기판상에 솔더 페이스트(solder paste)를 스크린 프린트(도포)하는 것이다. 그때 셀은 기판에 위치하며, 기판은 솔더(solder)가 다시 흐르도록 가열되고 셀에 전기적 물리적 접촉부를 형성한다. 만약 트랙이 슬라이버(sliver)의 배치후에 형성된다면, 트랙과 트랙에 대한 셀의 전기적 연결부는 동시에 형성될 수 있다. 전기적 전도 접착물질 및 전기적 전도 잉크를 포함하여, 이미 알려진 어떠한 공정이나 재료도 여기에 사용될 수 있다.

[0065] 각각의 셀이 제조되고 상기한 실시예 중 어느 하나에 따라서 장착된 후, 셀은 사용에 적합한 형태로 패키지화(packaged)되어야 한다.

[0066] 각각의 스트립이 개별 셀이기 때문에, 광 집중기(light concentrator)를 사용하여 각각의 셀이 효율적으로 영역 증가를 하도록 할 수 있다. 각각의 셀에 의해 흡수되는 빛의 양을 증가시키기 위해, 셀은 서로서로 인접하여 배치되지 않고 일정거리로 이격된다. 간격은 각각의 셀 폭의 0-3 배 사이이다. 셀에 두면이 있다는 사실이 장점이 될 수 있다. 즉, 셀은 어느 표면이든지 부딪치는 태양광(sunlight)에 동등하게 반응한다.

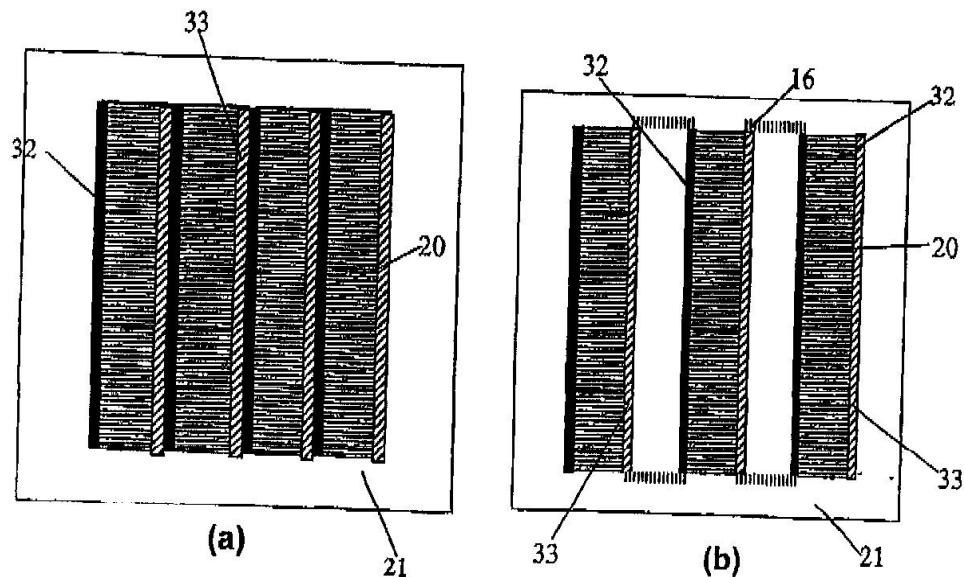

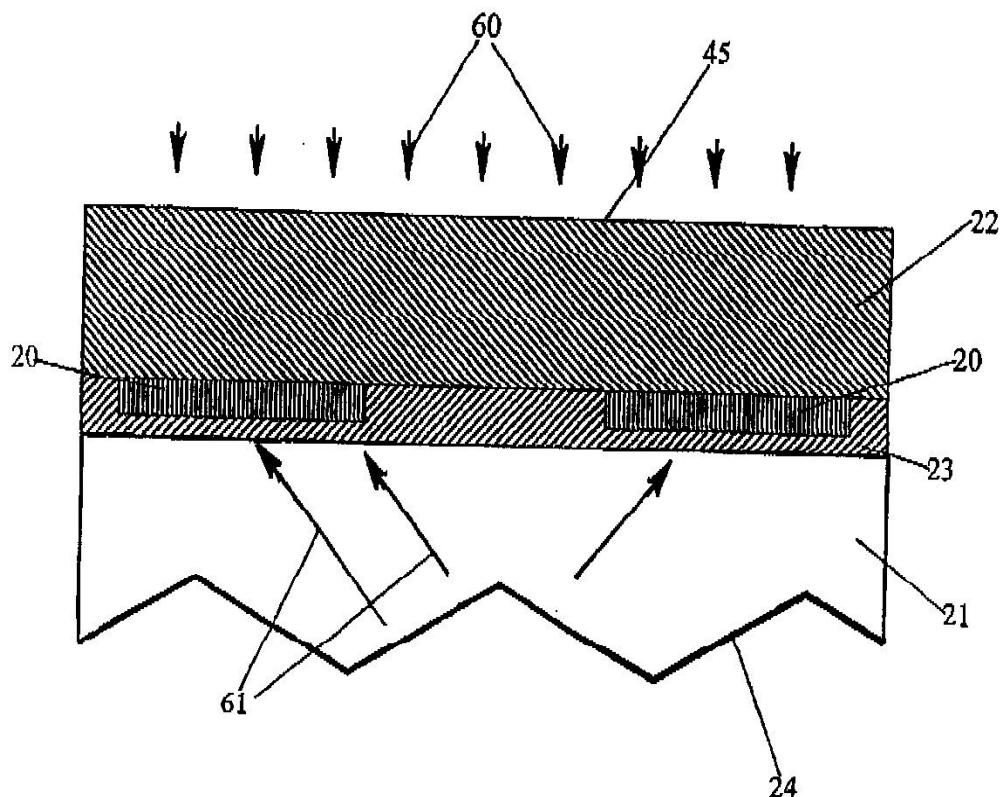

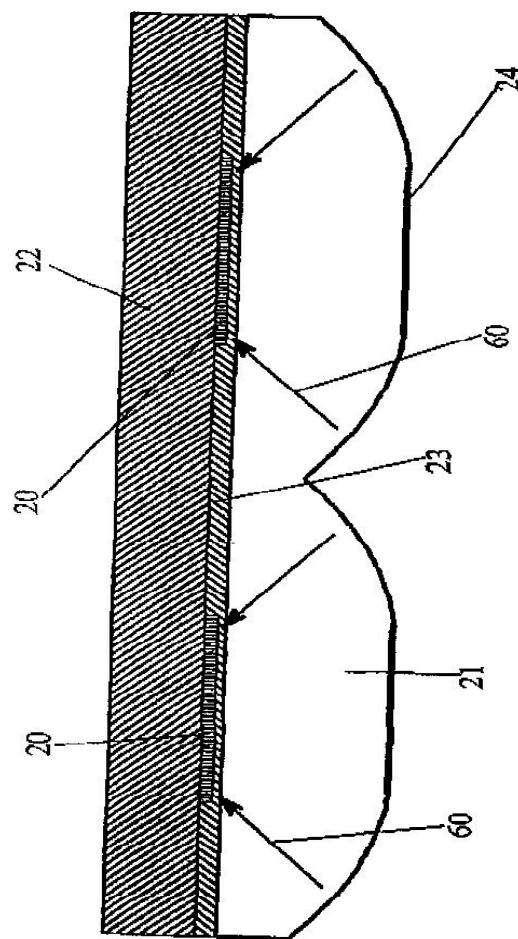

[0067] 도 14는 가능한 집중장치의 구조에 대한 단면도이다. 셀(20)은 적당한 광학 접착물을 사용하여 글라스 상층(22;glass superstrate)에 장착된다. 셀(20)은 직렬과 병렬연결을 적절히 조합하여 서로서로에게 전기적으로 연결된다(미도시). 여기에 유리와 같은 적당히 투명한 기판(21)이 적층되고, 셀(20)과 기판(21) 사이의 공간은, 에틸 비닐 아세테이트(ethyl vinyl acetate ; EVA) 또는 실리콘과 같은 적당한 포턴트(pottant;23)로 채워진다. 기판(21)의 후방표면은 톱니모양이며, 은과 같은 적당한 반사물질로 구성된 반사기(24)는 후방 반사기를 형성하도록 기판에 적층된다. 반사기 구조는 셀(20)과 일렬로 배열되지는 않으며, 셀(20)의 간극과 동일한 주기(period)를 가질 필요도 없다. 바람직하게는, 반사기(24)의 주기는 셀(20)의 간극보다 훨씬 작은 것이 좋다. 셀(20) 사이 간극을 관통하는 태양광(60)은 후방 반사기(24)에 의해 반사되어, 반사광(61)은 셀에 의해 흡수되는 두번째 기회를 가지게 된다. 더우기, 공기-유리의 전방 접촉면(45)에 도달하는 빛은, 만약 빛이 접촉면(45)에서 임계각(critical angle)보다 크게 부딪힌다면, 상층(22)으로 반사되어 되돌아 갈 수 있으며, 따라서 셀(20)에 의해 흡수될 수 있는 또 다른 기회를 가질 수 있다.

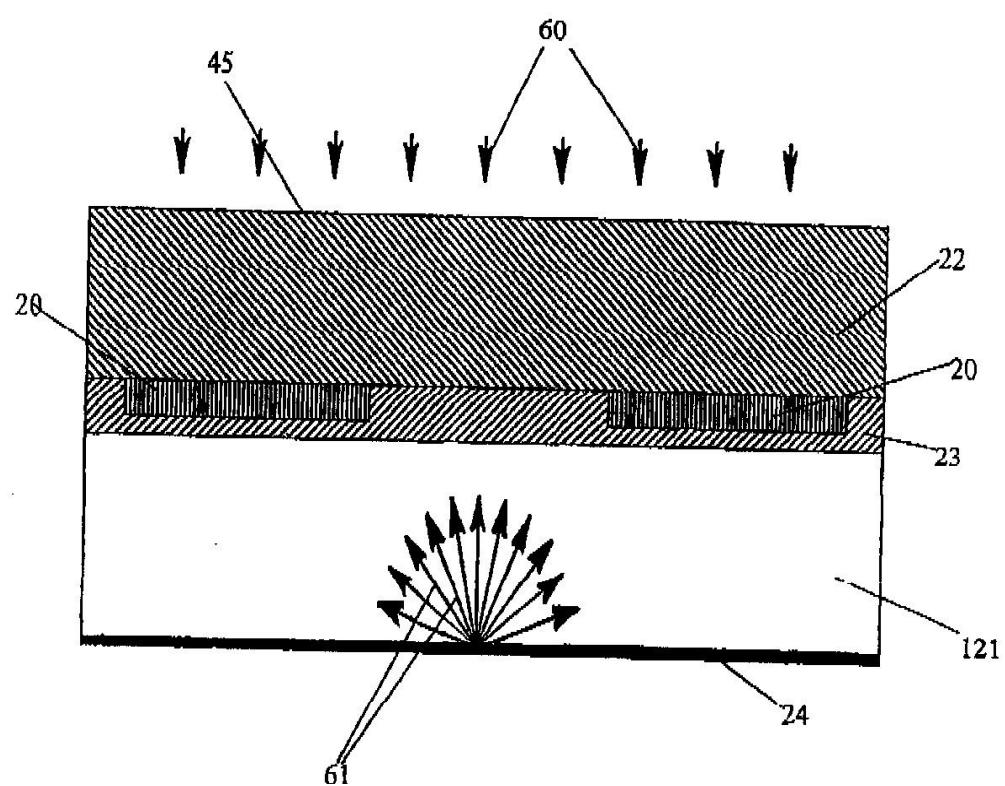

[0068] 도 15는 생각할 수 있는 다른 집중장치의 구조에 대한 단면도이다. 셀(20)은 적당한 광학 접착물질로 글라스 상층(22)에 장착된다. 셀(20)은 직렬과 병렬연결을 적절히 조합하여 서로서로에게 전기적으로 연결된다(미도시). 여기에 유리와 같은 적당히 투명한 기판(21)이 적용되고, 셀(20)과 기판(21) 사이의 공간은, 에틸 비닐 아세테이트(ethyl vinyl acetate ; EVA) 또는 실리콘과 같은 적당한 포턴트(pottant;23)로 채워진다. 적당한 흰색 페이트와 같은 고반사 람베르트(lambertian)(diffuse) 반사기(24)는 후방표면에 적용된다. 셀(20) 사이 간극을 관통하는 태양광(60)은 후방 반사기(24)에 의해 반사되어, 반사광(61)은 셀에 의해 흡수되는 두번째 기회를 가지게 된다. 더우기, 공기-유리의 전방 접촉면(45)에 도달하는 빛은, 만약 빛이 접촉면(45)에서 임계각(critical angle)보다 크게 부딪힌다면, 상층(22)으로 반사되어 되돌아 갈 수 있으며, 따라서 셀(20)에 의해 흡수될 수 있는 또 다른 기회를 가질 수 있다.

[0069] 도 16은 생각할 수 있는 또 다른 집중장치의 구조에 대한 단면도이다. 셀(20)은 적당한 광학 접착물질로 글라스 상층(22)에 장착된다. 셀(20)은 직렬과 병렬연결을 적절히 조합하여 서로서로에게 전기적으로 연결된다(미도시). 여기에 아크릴수지와 같은 적당히 투명한 기판(21)이 적용되고, 셀(20)과 기판(21) 사이의 공간은, 에틸 비닐 아세테이트(ethyl vinyl acetate ; EVA) 또는 실리콘과 같은 적당한 포턴트(pottant;23)로 채워진다. 기판(21)의 후방면은 인젝션 몰딩(injection molding)과 같은 적절한 공정으로 형상화되며, 은과 같은 적당한 반사물질로 구현된다. 이러한 반사기(24)는 셀(20)에 일렬로 배열된다. 반사기(24)는 셀(20) 사이의 간극을 관통하는 대부분의 태양광(60)이 셀(20) 위에서 반사되도록 설계되며, 또한 그러한 곳에 위치한다.

[0070] 실리콘 태양전지의 효율을 극대화하기 위해서는, 실리콘에 흡수되는 1100nm 보다 작은 파장으로 빛의 양을 최대로 하는 것이 중요하다. 흡수된 빛의 양을 감소시킬 수 있는 두가지 메커니즘이 있다. 빛은 실리콘 표면에서 반사될 수 있으며, 또는 실리콘으로 들어가거나 얼마후 흡수되지 않고 다시 실리콘 밖으로 나갈 수 있다. 이러한 두가지 손실 메커니즘은 실리콘 표면을 가공하거나(texturing) 거칠게(roughening) 함으로써 감소될 수 있다. 이것은 광선이 실리콘 표면에 여러번 부딪히게 하는 가능성을 증가시켜 반사손실을 줄이고, 실리콘내로 빛을 제한시켜 흡수손실을 줄이게 한다. 결정성장방향(100)인 단결정 실리콘(single crystal silicon)에 사용될 수 있는 가공기술(texturing technique)은 수산화 칼륨 용액(KOH)과 이소프로필 알콜(isopropyl alcohol; IPA)로 실리콘을 에칭하는 것이다. 이러한 결과로, 표면은 정방형 토대의 피라미드 형태로 덮여진다. 그러나, 이러한 방법은, 스트립의 표면이 결정 성장방향(111)을 가지므로, 실리콘 스트립이 KOH 에칭으로 형성되는 경우에는 사용될 수 없다. 몇몇 다른 가공기술(texturing technique)은 현재 개발중에 있으며, 이러한 기술은 반응 이온 에칭(reactive ion etching; RIE)과 같은 방법을 사용하여 특정한 결정성장방향에 의존하지 않게 된다. 그러나, 이러한

한 기술들은 많은 비용이 소요되거나, 실리콘 표면에서 캐리어(carrier)의 재조합을 증가시키는 등 다른 결점을 드러내고 있다. 더우기, 이러한 기술들은 단지 평판 웨이퍼의 텍스처링(texturing)에 적합하며, 본 발명의 공정 일부로 생산된 스트립 즉 웨이퍼 프레임에 있는 실리콘 스트립의 텍스처링에는 적용될 수 없다.

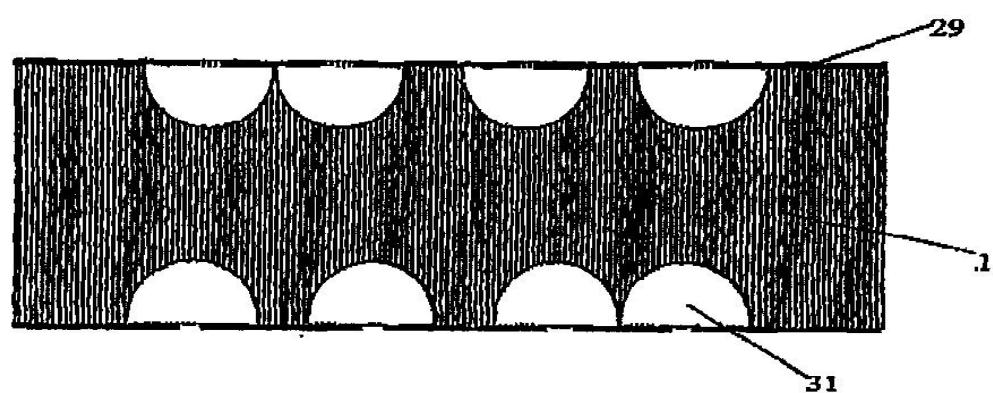

[0071] 도 17은 텍스처링된 실리콘 스트립(1)의 단면도이다. 텍스처링 과정은 다음과 같다. 실리콘 질화물(29)의 얇은 층은 저압 화학 증착(LPCVD)에 의해 실리콘 스트립 기판(1)위에 적층된다. 이러한 기술로 기판 표면에 대하여 실리콘 질화물(29)이 균일하고 등각으로 나타나게 된다. 중요하게는, 실리콘 질화물(29)은 또한 LPCVD에 의해 좁은 채널이나 슬롯 하부 및 상술한 기술(technique) 중 하나에 의해 생성된 실리콘 스트립의 측벽위로 적층된다. 실리콘 질화물의 아주 얇은 층만이 몇몇의 원자층 두께 순서로 적층된다. 그러한 층은 실리콘 기판이 노출되는 몇몇의 구멍(hole)을 보유할 만큼 충분히 얇다. 스트립(1)은 그때 1:50의 플루오르화수소산:질소산의 용액과 같은 적당한 에칭액으로 에칭된다. 작업실 온도에서, 이 용액은 실리콘보다 약 3000배 정도 느리게 실리콘 질화물을 에칭한다. 결과적으로 에칭 구멍(pits;31)은 스트립(1)의 실리콘에서 형성된다. 몇분후에, 대부분의 표면은 수 마이크론 크기까지 에칭 구멍(31)으로 덮이게 된다. 이후 에칭은 종료된다. 에칭공정의 제어는 에칭 시간과 온도를 변화시키거나, 실리콘 질화물의 적층 변수를 변화시킴으로 가능하며, 이러한 적층 변수는 층에서 구멍의 밀도에 영향을 끼칠수 있다. 만약 낮은 에칭온도가 사용되면, 실리콘(1)과 비교하여 실리콘 질화물(29)의 에칭률은 더 낮게 된다. 예를 들어, 0° C에서 에칭용액은 실리콘보다 약 6000배 정도 느리게 실리콘 질화물(29)를 에칭한다. 텍스처 특성을 더 향상시키기 위해, 전술한 텍스처링 공정을 두번 실행하는 것도 가능하다.

[0072] 텍스처링 공정에서 단지 작은양의 실리콘을 소모하기 때문에(각각의 텍스처 표면에서 대략 2-3 마이크론), 텍스처링 기술은 얇은 필름 실리콘 셀에 특히 유용하다. 텍스처링 기술은 임의의 알갱이 크기의 얇은 필름 또는 실리콘 웨이퍼에 적용될 수 있다.

[0073] 수직 측벽을 갖는 그루브를 형성하도록 결정성장방향(110)인 웨이퍼를 에칭하는 것은 광범위하게 문헌에 기재된 바 있다. 수백 마이크론 깊이의 좁은 그루브를 형성하기 위해, 균일한 그루브 깊이와 상당한 에칭률을 유지하는 것은 어려운 것으로 알려져 있다. 이것에 대한 두가지 납득할 만한 이유는, 그루브의 측벽에 부착되어 거품주위에 에칭을 방해하는 수소 거품이 형성되는 것이고, 또 하나는 그루브의 바닥에 신선한 에칭액의 공급이 원활하게 되지 않기 때문이다. 초음파 교반(agitation)과 교란(stirring)과 같이, 에칭률과 그루브 깊이의 균일성을 향상시킬 수 있는 몇가지 방법이 문헌에서 논의되어 왔다. 그러나, 용액의 교란은 그루브 깊이의 에칭상태를 본질적으로 향상시키지는 못하며, 그 반면 초음파 교반은 종종 미세한 형태물을 파괴시킨다.

[0074] 따라서, 아래 상술할 사항은 좁고 깊은 그루브를 에칭하는 새로운 기술에 대한 것이다. 이 기술은 주기적으로 용액에서 웨이퍼를 제거하고 그후 재삽입하는 과정으로 구성된다. 에칭은 일반적인 처리과정에서 5시간 동안 85° C에서 44% 중량의 KOH 용액으로 실시된다. 웨이퍼는 웨이퍼를 고정하는 어셈블리에 일반적으로 수평으로 약 45° 각도로 배치된다. 어셈블리는 웨이퍼를 용액으로 내리며, 웨이퍼는 5분동안 용액에 잠기게 된다. 그후, 웨이퍼는 용액위로 올려지며, 5분동안 이 위치로 놓여지게 된다. 그리고 웨이퍼를 용액속으로 다시 하강시킴으로 사이클이 반복된다.

[0075] 전술한 기술은 초기폭이 10 마이크론인 그루브를 구비한 실리콘 웨이퍼에 적용된다. 5시간 동안의 에칭은 대략 10 마이크론의 측면 에칭이 되어, 최종 그루브의 폭은 20 마이크론이 된다. 5시간 동안의 에칭 마지막에는 깊이 변화가 40 마이크론보다 작게 된다. 그루브 깊이의 최소 및 최대치는 각각 340과 380 $\mu$ m이다. 실험치는 350-360 마이크론 깊이 범위로 60%의 그루브가 에칭되며, 340의 깊이로 15%가 에칭되고, 370-380 마이크론 깊이 범위로 잔존 25%가 에칭되는 것을 나타낸다. 실리콘의 0.5mm 두께부분은 6시간 30분동안 완전히 에칭된다.

## [0076] 구체적인 예

### [0077] 예1- 태양전지의 제조

[0078] 태양전지는 아래와 같은 공정으로 만들어진다. 직경 100mm와 두께 0.8mm, 0.5 Ohm-cm의 봉소로 도프된 부유존(float-zoned) 웨이퍼가 초기 시작물질로 사용된다. 웨이퍼는 어떠한 표면손상을 제거하도록 에칭된다. 인화산은 웨이퍼의 일면(상부면)측으로 대략 50 ohm/square의 판저항으로 확산되며, 그후 봉소가 대략 50 ohm/square로 후방면으로 확산된다. 100nm 두께의 산화물은 양쪽 표면에서 성장하며, 그후 50nm의 실리콘 질화물이 적층된다. 다이싱 소를 사용하여 상부면에서 웨이퍼측으로 절단되며, 또한 실리콘 스트립을 형성하도록 후방표면이 대략 50 마이크론 이내로 연장되어 절단된다. 웨이퍼는 절단과정에서 생긴 어떠한 손상을 제거하기 위해 수산화칼륨 용액으로 에칭된다. 그리고 인(phosphorus)은 대략 100 ohm/square로 그루브로 확산된다. 산화물은 200nm

의 두께로 스트립의 측벽에서 성장한다. 두번째 일련의 절단과정은 다이싱 소로 웨이퍼의 후방으로 절단되며, 이러한 절단은 첫번째 일련의 절단부와 정렬되며, 웨이퍼를 통하여 모든 방향으로 연장되도록 충분한 깊이로 절단된다. 웨이퍼는 절단과정에서의 손상을 제거하도록 다시 수산화 칼륨 용액에 담가진다. 그후, 275nm 두께의 산화물은 새로이 노출된 실리콘 표면에서 성장하며, 측벽 산화물의 두께는 300nm까지 증가한다. 웨이퍼의 전방과 후방의 실리콘 질화물층은 165°C에서 인산을 사용하여 제거된다. 그후 웨이퍼는 산화물이 웨이퍼의 상부와 후방 표면에서 제거될 때까지 10%의 플루오르화수소산 수용액에 담가진다. 이단계에서, 대략 180nm 두께의 산화물은 여전히 실리콘 스트립의 측벽에 존재한다. 이때, 웨이퍼는 금속화된다(metallise). 그후 은(silver)이 대략 4 마이크론의 두께로 접촉부에 전기도금된다. 결국, 실리콘 스트립은 다이싱 소를 사용하여 절단된다. 두께가 100 마이크론 미만에서 250 마이크론까지 범위의 실리콘 스트립은 이런 방법으로 만들어진다.

[0079] 150개의 실리콘 스트립은 직렬로 다음과 같이 함께 연결된다. 스트립은 서로 인접하며 적당한 플레이팅 지그(plating jig)에 위치한다. 또한 스트립은 스트립 어셈블리의 한 모서리를 따라서 은칠(silver paint) 되어서 서로 단락된다(shorted). 그때, 셀은 은으로 도금된다. 이것으로 인해서 은 피복(deposit)은 인접 스트립사이에서 전기적이고 물리적인 연결을 형성하게 된다. 다음의 도금층, 즉 은칠이 된 결과 셀(resulting cell)의 모서리는 다이싱 소로 절단된다. 이러한 셀은 열 활성화 접착물을 사용하여 글라스에 장착된다. 53cm<sup>2</sup> 셀은 이런 방법으로 생산된다. 셀은 92V의 개방회로전압과 10.3mA 전류 및 73%의 필팩터(fill factor)로 13.4%의 효율을 가진다.

#### [0080] 예2- 반사율이 감소하도록 매끄러운 실리콘 표면의 텍스처링(texturing)

[0081] 실리콘 질화물층은 대략 2nm의 두께로 750°C에서 저압 화학 증착법 사용하여 결정성장방향(111)인 매끄러운 실리콘 웨이퍼에 적층된다. 샘플은 웨이퍼에서 절단되어 0°C에서 150초동안 1:50의 플루오르화수소산:질소산 용액에서 에칭된다. 샘플은 1mm두께의 저철(low iron) 글라스 뒤에서 실리콘을 사용하여 캡슐화되며(encapsulated), 샘플의 반사율(reflectance)은 전체 범위에서 분광 측광기(spectrophotometer)를 사용하여 측정된다. 샘플은 900nm에서 11%의 반사율을 가지며, 매끄러운 캡슐화된 실리콘 웨이퍼는 24%의 반사율을 가지고, 역파라미드로 텍스처링된 결정성장방향(100)인 실리콘 샘플은 같은 파장에서 8%의 반사율을 가진다. 이러한 결과는 텍스처링 공정이 실리콘 표면에서의 반사율을 감소시키는데 유효하다는 것을 나타낸다. 또한, 이러한 결과는 텍스처링이 실리콘내에서 빛을 가두는 데(confine) 아주 유효하다는 것을 나타낸다.

#### [0082] 선행기술인 공업용 실리콘 솔라 공정기술에 대한 본 발명에 의한 방법의 장점

[0083] 본 발명의 방법은 종래 방법과 비교할 때, 잉곳(ingot) 물질의 단위길이당 태양전지의 표면적이 더 크게 된다. 예를 들어, 차세대 결정 실리콘(c-Si) 태양전지는 대략 0.2mm의 두께를 가진다. 컬프 로스(Kerf loss)는 대략 0.25mm이며, 따라서 웨이퍼당 소비된 잉곳은 전체두께로 약 0.45mm가 된다. 본 발명에 따라서, 만약 스트립이 1mm 두께의 웨이퍼에서 0.1mm 간격으로 절단되면, 잉곳을 1.25mm 소비하는 동안에 초기 웨이퍼의 면적보다 10배 더 효율적인 표면적을 가지게 된다. 그래서, 동일한 웨이퍼 영역당 소비된 잉곳의 양은 0.125mm가 되며 이득은 3.6 팩터(factor)가 된다.(즉, 0.45/0.125) 웨이퍼 외면 주위에 실리콘 프레임이 구비하는 것은 이러한 이득을 약간 감소시킨다. 이러한 영역이득은 스트립으로 만들어진 태양 전지상으로 향하는 태양광을 집중함으로써 더욱 늘어날 수 있다.

[0084] 본 발명의 방법에는, 솔라 셀 제조공정은 스트립이 웨이퍼에 부착된 상태일 때 실시될 수 있다. 각각의 웨이퍼 공정이 진행중인 동안, 전술한 예를 사용하여 공정중 웨이퍼의 면적이 10배가 되며, 따라서 생산 비용이 감소한다. 일반적으로, 웨이퍼의 두께는 평면 표면적의 순이득을 얻도록, 제거된 실리콘의 폭과 각 스트립 폭의 합보다 더 커야한다.

[0085] 본 발명의 공정에서 자연적으로 모노리식(monolithic) 연결이 결과적으로 나타난다. 이것은 전통적인 셀 연결 공정과 비교할 때, 좀 더 쉽게 자동화 생산을 가능하게 한다. 셀은 또한 바람직하게는 작은 전류장치에 고전압을 일으키며 직렬로 연결될 수 있다.

[0086] 본 발명은 또한 아주 단순하면서도, 2 혹은 그 이상의 팩터(factor)로 태양광을 집중시키는 고효율의 정적 집중기(concentrator) 디자인을 제공한다. 이것은 모듈의 절반 또는 그 미만의 면적에 대해서는 태양전지로 덮혀야 하는 것을 의미한다. 본 발명의 공정에 의해 생산된 태양전지가 종래기술의 태양전지와 비교하여, 왜 더 나은 정

적 집중기 디자인을 제공하는지에 대해 두가지 기본적 이유가 있다.

[0087] 첫 번째 이유는, 본 발명의 공정에 의해 생산된 셀은 양면(bifacial)을 가진다. 즉, 두면은 어느 표면에 부딪히는 태양광에 동일하게 반응한다. 선행기술의 표준 태양전지는 양면이 아니며 오직 한 표면에서 부딪히는 태양광에 반응한다. 따라서 가장 효율적인 정적 집중기 디자인은 양면 셀을 필요로 하게 된다.

[0088] 두 번째 이유는, 본 발명의 공정에 의해 생산된 셀은 전형적으로는 1mm 상태로 매우 폭이 좁을수 있다. 정적 집중기의 높이는 직접적으로 셀의 폭에 비례한다. 웨이퍼에서 만들어진 선행기술의 표준 솔라 셀은 일반적으로 10x10cm<sup>2</sup> 이거나 그보다 더 크게 되고, 따라서 그러한 셀로 만들어진 정적 집중기는 부피가 크게 된다.

[0089] 도면을 참조하여 여기에 기술된 방법의 많은 수정은 관련분야의 당업자의 입장에서는 자명하며, 이러한 것이 본 발명의 범위를 제한하는 것은 아니다.

### 도면의 간단한 설명

[0090] 본 발명의 바람직한 실시예는 아래에 간단히 언급된 도면을 참조하여 단지 일례로서 아래에 기술된다.

[0091] 도1은 본 발명의 바람직한 실시예에 의한, 슬롯이 배치된 실리콘 웨이퍼의 상부(도 1(a)) 및 단면(도 1(b))을 나타낸 개략도.

[0092] 도2(a)는 본 발명에 따른 다른 실시예로 미세통로가 형성된 실리콘 웨이퍼의 평면 및 단면도; 도2(b)는 미세통로를 연결하여 그루브가 형성된 후 도2(a)에서 나타난 실리콘 웨이퍼의 평면도.

[0093] 도3은 바람직한 실시예에 따른, 연결 스트립과 슬롯이 배치된 실리콘 웨이퍼의 바닥( 도3(a)) 및 단면도( 도3(b))의 개략도.

[0094] 도4는 바람직한 실시예에 따른, 얇은 트렌치(trench)가 배치된 실리콘 웨이퍼의 평면도( 도4(a)) 및 단면도( 도4(b))의 개략도.

[0095] 도5는 바람직한 실시예에 따른, 도4에서 나타난 웨이퍼에 슬롯이 배치된 구조를 나타낸 개략적인 평면도.

[0096] 도6(a)은 복수의 얇은 그루브가 형성된 실리콘 웨이퍼의 개략적인 단면도; 도 6(b)는 도6(a)에서 나타난 단면에 직각되며 예칭후의 동일구조를 나타낸 개략적인 단면도.

[0097] 도7은 도6(b)에서 나타난 구조의 평면도.

[0098] 도8(a) 및 도8(b)는 웨이퍼에 슬롯이 형성되기 전후의 성장방향(110)인 실리콘 웨이퍼의 일부를 개략적으로 나타낸 단면도; 도8(c)는 도8(b)의 단면에서 나타난 구조의 개략적인 평면도.

[0099] 도9는 바람직한 실시예에 따른, 레이저수단에 의해 프레임에서 실리콘 스트립을 분리하는 방법을 예시하는 개략도.

[0100] 도10은 본 발명에 따라 제조된 실리콘 스트립 및 태양전지로 제조되는 실리콘 스트립을 개략적으로 나타낸 단면도.

[0101] 도11은 본 발명에 따라 제조된 실리콘 스트립 및 또 다른 태양전지로 제조된 실리콘 스트립을 개략적으로 나타낸 단면도.

[0102] 도12(a), 도12(b) 및 도12(c)는 바람직한 실시예에 따른, 스트립이 형성되는 동안 실리콘 웨이퍼의 전방 및 후방표면을 개략적으로 나타낸 일련의 단면도.

[0103] 도13(a) 내지 도13(d)는 본 발명의 공정에 따라 제조된 실리콘 스트립이 전기적으로 연결된 다양한 방법을 예시하는 개략도.

[0104] 도14는 적당한 기판에 장착되고 스트립상으로 태양광을 집중시키는 광 집중기에 인접한 실리콘 스트립의 개략적인 단면도.

[0105] 도15는 적당한 기판에 장착되고 스트립상으로 태양광을 집중시키는 다른 광 집중기에 인접한 실리콘 스트립의 개략적인 단면도.

[0106] 도16는 적당한 기판에 장착되고 스트립상으로 태양광을 집중시키는 또 다른 광 집중기에 인접하는 실리콘 스트립의 개략적인 단면도.

[0107] 도17은 아래 언급된 표면 텍스처링이 된 실리콘 스트립의 개략도.

### 도면

#### 도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17