(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5072210号

(P5072210)

(45) 発行日 平成24年11月14日(2012.11.14)

(24) 登録日 平成24年8月31日(2012.8.31)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 27/12  | (2006.01) | HO1L 27/12 | B    |

| HO1L 21/02  | (2006.01) | HO1L 29/78 | 627D |

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 624  |

| HO1L 29/786 | (2006.01) | HO1L 29/78 | 619A |

| HO1L 21/20  | (2006.01) | HO1L 21/20 |      |

請求項の数 4 (全 30 頁) 最終頁に続く

(21) 出願番号

特願2005-282204 (P2005-282204)

(22) 出願日

平成17年9月28日 (2005.9.28)

(65) 公開番号

特開2006-135305 (P2006-135305A)

(43) 公開日

平成18年5月25日 (2006.5.25)

審査請求日 平成20年7月2日 (2008.7.2)

(31) 優先権主張番号 特願2004-292546 (P2004-292546)

(32) 優先日 平成16年10月5日 (2004.10.5)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 鶴見 卓也

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 道前 芳隆

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 萩原 周治

最終頁に続く

(54) 【発明の名称】 半導体装置の作製方法

(57) 【特許請求の範囲】

【請求項 1】

第1の基板上に、剥離層を形成し、

前記剥離層上に第1の絶縁膜を形成し、

前記第1の絶縁膜上にp型の不純物領域の半導体層を有する第1の薄膜トランジスタとn型の不純物領域の半導体層を有する第2の薄膜トランジスタとを形成し、

前記第1の薄膜トランジスタと前記第2の薄膜トランジスタとの上に第2の絶縁膜を形成し、

前記第1の絶縁膜と前記第2の絶縁膜との一部を開口し第1の開口領域を形成し、

前記第1の開口領域に、前記剥離層に接するように、前記第1の薄膜トランジスタの半導体層の不純物領域と前記第2の薄膜トランジスタの半導体層の不純物領域とに電気的に接続される導電膜を形成し、

前記導電膜上に第3の絶縁膜を形成し、

前記第1の絶縁膜と前記第2の絶縁膜と前記第3の絶縁膜との一部を開口し第2の開口領域を形成し、

前記第3の絶縁膜上に前記第2の開口領域に合わせて複数の穴が設けられた第2の基板を貼り合わせ、

前記複数の穴を介して、前記第2の開口領域にエッチング剤を導入し、前記剥離層をエッチングし前記第1の基板を剥離することにより、前記導電膜を露出させ、

前記第2の基板が接するようにローラ上に設置し、

10

20

前記ローラを回転させ、前記露出された導電膜にプローブ針を接触させて検査を行い、接着面を備えるベルトコンベアと前記第1の絶縁膜と前記導電膜とを接着し、前記第2の基板を剥離することを特徴とする半導体装置の作製方法。

**【請求項2】**

第1の基板上に、剥離層を形成し、

前記剥離層上に第1の絶縁膜を形成し、

前記第1の絶縁膜上にp型の不純物領域の半導体層を有する第1の薄膜トランジスタとn型の不純物領域の半導体層を有する第2の薄膜トランジスタとを形成し、

前記第1の薄膜トランジスタと前記第2の薄膜トランジスタとの上に第2の絶縁膜を形成し、

10

前記第1の絶縁膜と前記第2の絶縁膜との一部を開口し、

前記開口された領域に、前記剥離層に接するように、前記第1の薄膜トランジスタの半導体層の不純物領域と前記第2の薄膜トランジスタの半導体層の不純物領域とに電気的に接続される導電膜を形成し、

前記導電膜上に第3の絶縁膜を形成し、

前記第3の絶縁膜上に第2の基板を貼り合わせ、

前記剥離層に対して加熱処理を行い、物理的手段を用いて前記第1の基板を剥離することにより、前記導電膜を露出させ、

前記第2の基板が接するようにローラ上に設置し、

前記ローラを回転させ、前記露出された導電膜にプローブ針を接触させて検査を行い、接着面を備えるベルトコンベアと前記第1の絶縁膜と前記導電膜とを接着し、前記第2の基板を剥離することを特徴とする半導体装置の作製方法。

20

**【請求項3】**

第1の基板上に、剥離層を形成し、

前記剥離層上に第1の絶縁膜を形成し、

前記第1の絶縁膜上にp型の不純物領域の半導体層を有する第1の薄膜トランジスタとn型の不純物領域の半導体層を有する第2の薄膜トランジスタとを形成し、

前記第1の薄膜トランジスタと前記第2の薄膜トランジスタとの上に第2の絶縁膜を形成し、

前記第1の絶縁膜と前記第2の絶縁膜との一部を開口し第1の開口領域を形成し、

前記第1の開口領域に、前記剥離層に接するように、前記第1の薄膜トランジスタの半導体層の不純物領域と前記第2の薄膜トランジスタの半導体層の不純物領域とに電気的に接続される導電膜を形成し、

30

前記導電膜上に第3の絶縁膜を形成し、

前記第3の絶縁膜の一部を開口し、コンタクトホールを形成し、

前記コンタクトホールを介して、前記第3の絶縁膜上に前記第1の薄膜トランジスタまたは前記第2のトランジスタと電気的に接続するアンテナを形成し、

前記アンテナ上に第4の絶縁膜を形成し、

前記第1の絶縁膜と前記第2の絶縁膜と前記第3の絶縁膜と前記第4の絶縁膜との一部を開口し第2の開口領域を形成し、

40

前記第3の絶縁膜上に前記第2の開口領域に合わせて複数の穴が設けられた第2の基板を貼り合わせ、

前記複数の穴を介して、前記第2の開口領域にエッチング剤を導入し、前記剥離層をエッチングし前記第1の基板を剥離することにより、前記導電膜を露出させ、

前記第2の基板が接するようにローラ上に設置し、

前記ローラを回転させ、前記露出された導電膜にプローブ針を接触させて検査を行い、接着面を備えるベルトコンベアと前記第1の絶縁膜と前記導電膜とを接着し、前記第2の基板を剥離することを特徴とする半導体装置の作製方法。

**【請求項4】**

第1の基板上に、剥離層を形成し、

50

前記剥離層上に第1の絶縁膜を形成し、

前記第1の絶縁膜上にp型の不純物領域の半導体層を有する第1の薄膜トランジスタと

n型の不純物領域の半導体層を有する第2の薄膜トランジスタとを形成し、

前記第1の薄膜トランジスタと前記第2の薄膜トランジスタとの上に第2の絶縁膜を形

成し、

前記第1の絶縁膜と前記第2の絶縁膜との一部を開口し、

前記開口された領域に、前記剥離層に接するように、前記第1の薄膜トランジスタの半

導体層の不純物領域と前記第2の薄膜トランジスタの半導体層の不純物領域とに電気的に

接続される導電膜を形成し、

前記導電膜上に第3の絶縁膜を形成し、

前記第3の絶縁膜の一部を開口し、コンタクトホールを形成し、

前記コンタクトホールを介して、前記第3の絶縁膜上に前記第1の薄膜トランジスタま

たは前記第2のトランジスタと電気的に接続するアンテナを形成し、

前記アンテナ上に第4の絶縁膜を形成し、

前記第4の絶縁膜上に第2の基板を貼り合わせ、

前記剥離層に対して加熱処理を行い、物理的手段を用いて前記第1の基板を剥離するこ

とにより、前記導電膜を露出させ、

前記第2の基板が接するようにローラ上に設置し、

前記ローラを回転させ、前記露出された導電膜にプローブ針を接触させて検査を行い、

接着面を備えるベルトコンベアと前記第1の絶縁膜と前記導電膜とを接着し、前記第2の

基板を剥離することを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、接触式の検査を行う方法、そのための半導体装置の構造、及びその作製方法に

関する。

【背景技術】

【0002】

現状のICカードは、その表面に接触端子が設けられた接触式ICカード、ICチップの

接続端子を、ある基材上に配置したアンテナの接続端子と接続し、電磁波によりリーダ／

ライタとの通信を行う非接触式ICカード、それらを兼ねたハイブリッド式ICカードに

分類される。

非接触式ICカードは、アンテナを有しており、それを介してリーダ／ライタと無線通信

を可能としている。特に非接触式ICカードは、リーダ／ライタとの通信距離により、密

着型、近接型、近傍型、マイクロ波型に分類される（特許文献1参照）。

【特許文献1】特開2003-76969号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

上記特許文献1に記載のICカードに実装されるICチップは、シリコンウェハから形成

されている。そのため、薄型状商品に実装する場合、凹凸が生じてしまった。

【0004】

またこのようなチップの不良検査では、アンテナを実装している場合、接触式の検査を行

うことが難しかった。これはチップが完成すると、チップ表面には端子が露出していない

からである。接触式の検査は、非接触式と比べて、精度が高く、検査装置も簡単なもので

あるため、使用することが望まれていた。

【0005】

そこで本発明は、不良を検査しやすくするため、接触式検査方法を提供し、そのための新

たな構成であり、非常に薄型のチップ、及び該チップの作製方法を提供することを課題と

する。

**【課題を解決するための手段】****【0006】**

上記課題を鑑み本発明は、基板上に薄膜半導体膜及び配線を有するチップを形成し、該基板を剥離すると、配線の一部が露出され、該配線に対して接触式の検査をおこなうことを特徴とする。またそのためのチップの新たな構造やその作製方法を特徴とする。

**【0007】**

なお本発明の新たな構成を有するチップを半導体装置と呼ぶ。半導体装置とは、半導体特性を利用した装置全般を指す。

**【0008】**

具体的な本発明の構成は、基板上に、剥離層を介して半導体膜を形成し、半導体膜上に絶縁膜を形成し、絶縁膜の一部を開口し、開口された領域に、剥離層に接するように、配線を形成し、剥離層に対して加熱処理を行い、基板を剥離することにより、配線を露出させることを特徴とする半導体装置の作製方法である。10

**【0009】**

別の本発明の構成は、基板上に、剥離層を介して半導体膜を形成し、半導体膜上に絶縁膜を形成し、絶縁膜の一部を開口し、開口された領域に、剥離層に接するように、配線を形成し、絶縁膜の一部に溝を形成して、剥離層を露出させ、溝にエッチング剤を導入して剥離層を除去することにより、配線を露出させることを特徴とする半導体装置の作製方法である。

**【0010】**

別の本発明の構成は、基板上に、剥離層を介して半導体膜を形成し、半導体膜上に絶縁膜を形成し、絶縁膜の一部を開口し、開口された領域に、剥離層に接するように、配線を形成し、剥離層に対して加熱処理を行い、基板を剥離することにより、配線を露出させ、露出された配線にプローブ針を接触させて検査を行うことを特徴とする半導体装置の検査方法である。20

**【0011】**

別の本発明の構成は、基板上に、剥離層を介して半導体膜を形成し、半導体膜上に絶縁膜を形成し、絶縁膜の一部を開口し、開口された領域に、剥離層に接するように、配線を形成し、絶縁膜の一部に溝を形成して、剥離層を露出させ、溝にエッチング剤を導入して剥離層を除去することにより、配線を露出させ、露出された配線にプローブ針を接触させて検査を行うことを特徴とする半導体装置の検査方法である。30

**【0012】**

別の本発明の構成は、基板上に設けられた半導体膜と、半導体膜が有する不純物領域と、半導体膜上に設けられた絶縁膜と、絶縁膜の開口領域に設けられた、不純物領域に接続される配線と、を有し、配線は、半導体膜より下の領域まで設けられていることを特徴とする半導体装置である。

**【0013】**

本発明の半導体装置は、通信方法により、接触型と、非接触型に分けることができる。接触型の場合、端子を介して、情報を送受信する装置と通信する。そのため、接触型の場合、アンテナを実装する必要はない。このような接触型の半導体装置の用途は、カード、集積回路（L S I）、メモリ等がある。40

**【0014】**

また非接触型の場合、無線を用いて、情報を送受信する装置と通信する。そのため、非接触型の場合、アンテナを実装する必要がある。このような、無線により通信するものを無線チップともいう。無線チップの用途は、個体の識別に用いる無線タグ、記憶装置としての無線メモリ、医療に用いる医療用無線チップ等がある。

**【発明の効果】****【0015】**

本発明のチップにおいて、基板を剥離すると、配線が露出される。そこで、プローブ針を用いて、無線チップの検査を行うことができる。接触式の検査は、非接触式と比べて、精50

度が高く、検査装置も簡便なものであるため好ましい。

【発明を実施するための最良の形態】

【0016】

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

【0017】

10

(実施の形態1)

本実施の形態では、物理的手段を用いた剥離法によって、チップを作製する工程について説明する。

【0018】

20

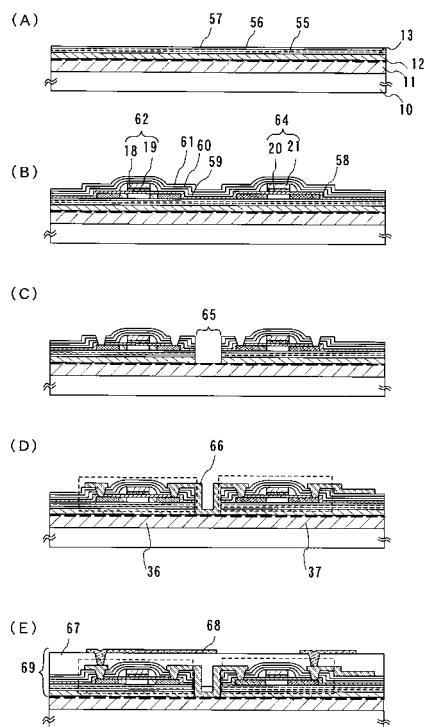

まず図1(A)に示すように第1の基板10を代表とする絶縁表面上に、剥離層として、金属膜11を形成する。なお、第1の基板10は後の剥離工程に耐えうる剛性を有していればよく、例えばバリウムホウケイ酸ガラスや、アルミノホウケイ酸ガラスなどのガラス基板、石英基板等が挙げられる。またその他基板としては、ポリエチレン-テレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルファン(PES)に代表されるプラスチックや、アクリル等の可撓性を有する合成樹脂からなる基板が挙げられる。また、ステンレスなどの金属または半導体基板などの表面に酸化珪素や窒化珪素などの絶縁膜を形成した基板なども用いることができる。

【0019】

金属膜としては、W、Ti、Ta、Mo、Nd、Ni、Co、Zr、Zn、Ru、Rh、Pd、Os、Irから選ばれた元素または前記元素を主成分とする合金材料若しくは化合物材料からなる単層、或いはこれらの積層を用いることができる。金属膜は、金属をターゲットして用いるスパッタリング法を用いて作製することができる。なお金属膜の膜厚は、10nm～200nm、好ましくは50nm～75nmとする。

【0020】

30

なお金属膜11に、窒素や酸素等の元素を添加してもよい。例えば、金属膜11に窒素や酸素をイオン注入して形成することができる。また、金属膜11の代わりに、窒化された金属膜、つまり窒化金属膜を用いても構わない。例えば、成膜室を窒素や酸素雰囲気とし、金属をターゲットして用いるスパッタリング法により、窒化金属膜を形成することができる。また、ターゲットとして窒化金属を用いて、窒化金属膜を形成することができる。

【0021】

このとき、金属膜に上記金属の合金(例えば、WとMoとの合金:  $W_xMo_{(1-x)}$ )を用いる場合、成膜室内に第1の金属(W)及び第2の金属(Mo)といった複数のターゲットを配置して、金属の合金を形成することができる。または、第1の金属(W)と第2の金属(Mo)との合金のターゲットを配置して形成することもできる。

【0022】

40

このように形成される金属膜により、後の剥離工程の条件を決定することができる。例えば、金属の合金を用いた場合、合金の各金属の組成比を制御することにより、加熱処理の温度、更には加熱処理の要否を制御することができる。このようにして、プロセスマージンを広げることができる。

【0023】

その後、金属膜11上に被剥離層を形成する。この被剥離層は金属膜11上の膜、酸化膜12から上に設けられる膜を合わせて指す。

【0024】

酸化膜12は、スパッタリング法やCVD法により酸化珪素膜、窒化珪素膜、窒素を有する酸化珪素膜等を形成すればよい。なお酸化膜12の膜厚は、金属膜11の約2倍以上で

50

あることが望ましい。ここでは、シリコンターゲットを用いたスパッタリング法により、酸化珪素膜を 150 nm ~ 200 nm の膜厚として形成する。

【0025】

なお本発明において、酸化膜 12 を形成するときに、金属膜 11 上に当該金属を有する金属酸化物 13 が形成される（図中点線で記載する）。金属酸化物 13 の膜厚は、0.1 nm ~ 1 μm、好ましくは 0.1 nm ~ 100 nm、更に好ましくは 0.1 nm ~ 5 nm となるように形成すればよい。金属酸化物 13 は剥離層として機能する。

【0026】

また上記以外の金属酸化物 13 の作製方法は、硫酸、塩酸或いは硝酸を有する水溶液、硫酸、塩酸或いは硝酸と過酸化水素水とを混同させた水溶液又はオゾン水で処理することによって、薄い酸化膜が形成されるときに作製することができる。更に他の方法としては、酸素雰囲気中でのプラズマ処理や、酸素含有雰囲気中で紫外線照射することによりオゾンを発生させて酸化処理を行ったり、クリーンオーブンを用い 200 ~ 350 度に加熱して薄い酸化膜を形成するときに作製することもできる。

10

【0027】

また酸化膜 12 上に、金属膜 11 や基板 10 からの不純物やゴミの侵入を防ぐため酸化珪素膜、窒化珪素膜、窒素を有する酸化珪素膜等の絶縁膜を、下地膜として設けると好ましい。本実施の形態では、窒素を有する酸化珪素膜（SiON）55、酸素を有する窒化珪素膜（SiNO）56、窒素を有する酸化珪素膜（SiON）57 を順に積層して、下地膜とする。なおこれら絶縁膜は連続性膜することができる、その場合、界面が明確とならないこともある。そのため、図中では界面を点線で示す。

20

【0028】

その後図 1 (B) に示すように、半導体膜を形成し、所定の形状にパターニング（加工）する。半導体膜は、40 nm ~ 170 nm の膜厚を有し、非常に薄型である。また半導体膜は、珪素を有する、又はゲルマニウムを有する材料から形成することができる。また半導体膜は、非晶質半導体、非晶質状態と結晶状態とが混在したセミアモルファス半導体（SAS とも表記する）、及び結晶性半導体のいずれの状態を有してもよい。なお SAS は、非晶質半導体中に 0.5 nm ~ 20 nm の結晶粒を観察することができる微結晶半導体が含まれる。

30

【0029】

本実施の形態では、非晶質半導体膜を形成し、加熱処理により結晶化された結晶性半導体膜を形成する。加熱処理とは、加熱炉、レーザー照射、若しくはレーザー光の代わりにランプから発する光の照射（以下、ランプアーニールと表記する）、又はそれらを組み合わせて用いることができる。

【0030】

レーザー照射を用いる場合、連続発振型のレーザビーム（CW レーザビーム）やパルス発振型のレーザビーム（パルスレーザビーム）を用いることができる。レーザビームとしては、Ar レーザー、Kr レーザー、エキシマレーザー、YAG レーザー、Y<sub>2</sub>O<sub>3</sub> レーザー、YVO<sub>4</sub> レーザー、YLF レーザー、YAlO<sub>3</sub> レーザー、ガラスレーザー、ルビーレーザー、アレキサンドライドレーザー、Ti : サファイヤレーザー、銅蒸気レーザーまたは金蒸気レーザーのうち一種または複数種から発振されるものを用いることができる。このようなレーザビームの基本波、及び当該基本波の第 2 高調波から第 4 高調波のレーザビームを照射することで、大粒径の結晶を得ることができる。例えば、Nd : YVO<sub>4</sub> レーザ（基本波 1064 nm）の第 2 高調波（532 nm）や第 3 高調波（355 nm）を用いることができる。このときレーザーのエネルギー密度は 0.01 ~ 100 MW / cm<sup>2</sup> 程度（好ましくは 0.1 ~ 10 MW / cm<sup>2</sup>）が必要である。そして、走査速度を 10 ~ 2000 cm / sec 程度として照射する。

40

【0031】

なお連続発振の基本波のレーザビームと連続発振の高調波のレーザビームとを照射するようにしてよいし、連続発振の基本波のレーザビームとパルス発振の高調波のレーザビーム

50

ムとを照射するようにしてもよい。複数のレーザビームを照射することにより、エネルギーを補うことができる。

【0032】

またパルス発振型のレーザビームであって、半導体膜がレーザー光によって溶融してから固化するまでに、次のパルスのレーザー光を照射できるような発振周波数でレーザーを発振させるレーザビームを用いることもできる。このような周波数でレーザビームを発振させることで、走査方向に向かって連続的に成長した結晶粒を得ることができる。具体的なレーザビームの発振周波数は10MHz以上であって、通常用いられている数十Hz～数百Hzの周波数帯よりも著しく高い周波数帯を使用する。

【0033】

なお、希ガスや窒素などの不活性ガス雰囲気中で上記レーザーを照射するようにしてもよい。これにより、レーザビームの照射による半導体表面の荒れを抑えたり、平坦性を高めることができ、界面準位密度のばらつきによって生じる閾値電圧のばらつきを抑えることができる。

【0034】

またSiH<sub>4</sub>とF<sub>2</sub>、又はSiH<sub>4</sub>とH<sub>2</sub>を用いて微結晶半導体膜を形成し、その後上記のようなレーザー照射をおこなって結晶化してもよい。

【0035】

その他の加熱処理として、加熱炉を用いる場合、非晶質半導体膜を500～550で2～20時間かけて加熱する。このとき、徐々に高温となるように温度を500～550の範囲で多段階に設定するとよい。最初の低温加熱工程により、非晶質半導体膜の水素等が出てくるため、結晶化の際の膜荒れを低減する、所謂水素だしを行なうことができる。さらに、結晶化を促進させる金属元素、例えばNiを非晶質半導体膜上に設けると、加熱温度を低減することができ好ましい。さらに加えて上記のようなレーザー照射を行ってもよい。

【0036】

但し、金属元素を形成する場合、半導体素子の電気特性に悪影響を及ぼすことが懸念されるので、該金属元素を低減又は除去するためのゲッタリング工程を施す必要が生じる。例えば、非晶質半導体膜をゲッタリングシンクとして金属元素を捕獲するよう工程を行なえばよい。

【0037】

また直接被形成面に、結晶性半導体膜を形成してもよい。この場合、GeF<sub>4</sub>、又はF<sub>2</sub>等のフッ素系ガスと、SiH<sub>4</sub>、又はSi<sub>2</sub>H<sub>6</sub>等のシラン系ガスとを用い、熱又はプラズマを利用して直接被形成面に、結晶性半導体膜を形成することができる。このように直接結晶性半導体膜を形成する場合であって、高温処理が必要となるときは、耐熱性の高い石英基板を第1の基板10に用いるとよい。

【0038】

その後、半導体膜を覆うように、ゲート絶縁膜58として機能する絶縁膜を形成する。絶縁膜には、酸化珪素膜、窒化珪素膜、窒素を有する酸化珪素膜等を用いることができる。

【0039】

ゲート絶縁膜58を介して、半導体膜上にゲート電極62、64として機能する導電膜を形成する。導電膜は、単層構造であっても、積層構造であってもよく、Ta、W、Ti、Mo、Al、Cuから選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料で形成することができる。本実施の形態では、第1の導電膜18、20として膜厚が10～50nm、例えば30nmの窒化タンタル膜を形成し、第2の導電膜19、21として膜厚200～400nm、例えば370nmのタンゲステン膜を順次形成する。

【0040】

その後、ゲート電極62、64の側面に絶縁物を形成し、サイドウォールとして機能させる。サイドウォールにより、不純物形成領域の有無やその大きさ、さらにその不純物濃度を制御することができる。不純物領域の大きさ、チャネル形成領域が微細化するにつれ短

10

20

30

40

50

チャネル効果を防ぐことができる。本実施の形態では、第1の半導体膜は、サイドウォール下方に形成される低濃度不純物領域及び高濃度不純物領域を有し、第2の半導体膜は高濃度不純物領域のみを有する構成とする。低濃度不純物領域を有し、該低濃度不純物領域がゲート電極と重ならない構造を LDD (Lightly Doped Drain) 構造といい、高濃度不純物領域のみを有する構造をシングルドレイン構造と表記する。また低濃度不純物領域がゲート電極を重なる場合、その構造を GOLD (Gate-drawn Overlapped LDD) 構造を表記する。

#### 【0041】

その後、半導体膜、ゲート電極 62、64、ゲート絶縁膜 58 等を覆って、絶縁膜を形成する。絶縁膜は無機材料、又は有機材料から形成することができ、単層構造であっても、積層構造であってもよい。積層構造を用いる場合、無機材料を積層したり、有機材料を積層することができる。また無機材料と有機材料とを積層してもよく、有機材料を用いて平坦性を高め、無機材料により不純物の侵入を防ぐことができる。有機材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテン、シロキサン、ポリシラザンを用いることができる。シロキサンは、シリコン (Si) と酸素 (O) との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基（例えばアルキル基、芳香族炭化水素）が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。またポリシラザンとは、珪素 (Si) と窒素 (N) の結合を有するポリマー材料を含む液体材料を出発原料として形成される絶縁膜である。

10

#### 【0042】

本実施の形態では、プラズマ CVD 法を用いた連続成膜により、窒素を有する酸化珪素膜 (SiON) 59、酸素を有する窒化珪素膜 (SiNO) 60、窒素を有する酸化珪素膜 (SiON) 61 を順に積層して、下地膜とする。このように窒素を有する絶縁膜を用いると、不純物汚染を防止することができる。なお本実施の形態では、SiON 59 を形成した後、加熱処理（例えば 400 ~ 570、具体的には 550 で 4 時間）を行い、SiNO 60、SiON 61 を順に形成する。

20

#### 【0043】

その後、400 ~ 500、例えば 410 で 1 時間の加熱処理を行い、絶縁膜 59、60、61 が有する水素を拡散し、半導体膜中のタングリングボンドを低減させる。この加熱処理により、金属酸化物 13 の状態に変化が生じことがある。その結果、第1の基板の剥離を簡便に行わせることができうる。

30

#### 【0044】

なお本実施の形態では、半導体膜を有する薄膜トランジスタ (TFT) を用いる場合で説明したが、シリコンウェハを用いたトランジスタ、有機 TFT、薄膜ダイオード、シリコンの PIN 接合からなる光電変換素子等を形成してもよい。

#### 【0045】

その後図 1 (C) に示すように、不純物領域に配線を接続するための開口領域を形成する。本発明では、開口領域の一部を、金属膜 11 が露出するように、または露出する直前で止めるように形成することを特徴とする。

40

このような開口領域は、ドライエッチング法、ウェットエッチング法、レーザー照射により形成することができる。例えば、ウェットエッチング法を用いる場合、フッ酸系のエッチャントを用いて、開口領域を形成することができる。

#### 【0046】

次いで、図 1 (D) に示すように、配線 66 として機能する導電膜を形成する。導電膜は、アルミニウム (Al)、チタン (Ti)、モリブデン (Mo)、タングステン (W) もしくはシリコン (Si) の元素からなる膜又はこれらの元素を用いた合金膜を用いればよい。本実施の形態では、チタン膜 / アルミニウム - シリコン合金膜 / チタン膜 (Ti / Al - Si / Ti) をそれぞれ積層したのち、所望の形状にパターニング及びエッチングして配線 66 を形成する。このとき、配線 66 の膜厚は、段切れしないように、開口領域の

50

深さを考慮して決めることができる。また配線 6 6 を形成後、加熱処理を行い、金属酸化物の状態に変化を与えてよい。本実施の形態では、350 で1時間の加熱処理を行う。

#### 【0047】

このように配線 6 6 まで形成された状態を薄膜トランジスタとし、本実施の形態ではn型の薄膜トランジスタ36、p型の薄膜トランジスタ37を形成する。このような薄膜トランジスタにより、チップが有する論理回路等を作製することができる。チップが有する論理回路等は、昇圧電源回路、復調回路、変調回路、メモリインターフェース、メモリが挙げられる。無線通信を可能とする無線チップの場合、加えてアンテナ回路を有する。

#### 【0048】

次いで図1(E)に示すように、配線 6 6 を覆って、絶縁膜 6 7 を形成する。絶縁膜は、単層構造であっても、積層構造であってもよく、無機材料、又は有機材料、若しくは無機材料と有機材料との積層構造から形成することができる。有機材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテン、シロキサン、ポリシラザンを用いることができる。本実施の形態ではシロキサンを用いて、絶縁膜 6 7 を形成する。

10

#### 【0049】

その後、絶縁膜 6 7 に開口部を形成し、配線 6 6 と接続される導電膜 6 8 を形成する。導電膜 6 8 はその一部をアンテナとして用いることができる。アンテナとなる導電膜は、スパッタリング法等に加えて、スクリーン印刷法、液滴吐出法等のフォトリソグラフィー法を不要とする方法で作製することができる。また導電膜 6 8 の材料は、アルミニウム(A1)、チタン(Ti)、モリブデン(Mo)、タングステン(W)もしくはシリコン(Si)の元素からなる膜又はこれらの元素を用いた合金膜を用いればよい。このようにアンテナを形成し、無線通信を可能とした無線チップを形成することができる。

20

#### 【0050】

以上のように形成された酸化膜 1 2 より上に設けられた膜をあわせて、被剥離層 6 9 となる。

#### 【0051】

この段階で、金属酸化物 1 3 の状態に変化を与えるため、加熱処理を行ってもよいが、有機材料からなる絶縁膜や、配線材料の耐熱性を考慮する必要がある。なお本実施の形態では、絶縁膜 5 9 、 6 0 、 6 1 を形成後の加熱処理により、金属酸化物 1 3 の状態に変化を与えることができる。

30

#### 【0052】

なお加熱処理は、半導体装置の作製と兼用させて工程数を低減させてもよい。例えば、非晶質半導体膜を結晶化させるための、加熱炉やレーザー照射を用いて、結晶性半導体膜を形成すると同時に、金属酸化物 1 3 への変化を生じさせることもできる。

#### 【0053】

また図2(A)に示すように、被剥離層 6 9 に、第1の接着機能を有する材料(接着剤)70を用いて第2の基板 7 1 を固定する。

#### 【0054】

40

人間の手等によって、剥離する場合、第2の基板 7 1 は第1の基板 1 0 よりも剛性の高い基板を用いることが好ましい。またローラ等の装置を用いて、力を加えて剥離する場合、第2の基板 7 1 は、ローラに巻くことができる柔軟性を有する基板が好ましい。

#### 【0055】

第1の接着剤 7 0 は、ある処理によって接着性が低くなり、剥離可能な接着剤、例えば紫外線により接着性が低くなり剥離することが可能な紫外線剥離型接着剤、熱により接着性が低くなり剥離することが可能な熱剥離型接着剤、水により粘着性が低くなり剥離することが可能な水溶性接着剤を用いることができる。具体的な材料として、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、メラミン樹脂、ウレタン樹脂、シリコン樹脂等の樹脂材料を用いることができる。また、ベンゾシクロブテン、パリレン、フレア

50

、ポリイミドなどの有機材料、シロキサン系ポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料等の絶縁膜が挙げられる。そして、上記粘着剤のいずれかを有する両面テープ、又は上記粘着剤のいずれかを有するフィルム（例えばホットメルトフィルム）を使用することができる。

## 【0056】

第2の基板71には、ポリカーボネート、ポリアリレート、ポリエーテルスルファン、ポリエチレンテレフタレート、ポリエチレンナフタレート等のプラスチック基板、ポリテトラフルオロエチレン基板又はセラミック基板等の膜厚の薄い基板や可撓性のある（フレキシブルな）基板（以下、このような基板をフィルム基板と表記する）を用いることができる。

10

## 【0057】

なお金属酸化物13の状態に変化を与えるための加熱処理は、第2の基板71を固定した後に行なっても構わない。有機材料からなる絶縁膜や、配線材料の耐熱性を考慮する必要がある。

## 【0058】

上記した接着剤材料は、保護膜としての機能も奏すことができる。そのため、被剥離層69の側面に、接着剤材料を設けてもよい。

## 【0059】

このような状態で、第1の基板10を、物理的手段を用いて剥離する。物理的手段とは、ローラの回転、人間の手、ノズルから吹付けられるガスの風圧、超音波等の比較的小さな力で引き剥がす手段が挙げられる。本実施の形態では、ローラの回転により第1の基板10及び第2の基板71間に力を加えて、剥離する。

20

## 【0060】

このとき金属酸化物の層内、又は金属酸化物の両面、つまり金属酸化物13と金属膜11との界面或いは酸化膜12と金属酸化物13との界面で剥がれる。こうして、被剥離層69を、第1の基板10から剥離することができる。

## 【0061】

このように高温プロセスは第1の基板10を用いて行い、その後第2の基板71に転置することにより、耐熱性の低い基板材料を第2の基板71に用いることができる。

30

## 【0062】

このとき、第1の基板10、及び第2の基板71のいずれか、又は両者の外側に補助基板を設けた後、剥離してもよい。補助基板により、剥離を簡便なものとすることができる。補助基板としては、例えば石英基板を用いることができる。

## 【0063】

補助基板を設ける場合、第2の基板71の材料のうち、強度の弱いフィルム基板を用いやすい。

## 【0064】

なお本発明は、必ずしも第2の基板が必要にならない。例えば、絶縁膜70を形成した後、第2の基板71を貼り合わせることなく、第1の基板を剥離することができる。

40

## 【0065】

次いで図2(B)に示すように、第1の基板10を剥離すると、配線66が露出される。すなわち、配線66は半導体膜や下地膜より下の領域まで設けられているため、露出することができる。そこで、プローブ針80を用いて、チップ、具体的には論理回路等の検査を行うことができる。このとき、金属酸化物13は、配線66とプローブ針80とが接触できる程度で点在していれば、問題とならない。また本発明は、配線が露出することを特徴としており必ずしもプローブ針を用いて検査を行う必要はない。例えば、露出した配線に、検査装置に接続されたFPC(flexible printed circuit)を貼って検査を行っても構わない。

## 【0066】

チップが完成すると、表面に配線が露出されない構成となる。例えば、図2(C)に示す

50

ように、チップはラミネート（貼り合わせ）加工されるため、表面に配線が露出されない。そのため、接触式の検査を行うことが難しかった。しかし、本発明のように開口領域65に配線66を形成することにより、第1の基板10を剥離すると、配線66を露出することができ、このときチップに対して接触式の検査を行うことができる。接触式の検査は、非接触式と比べて、精度が高く、検査装置も簡便なものであるため好ましい。

#### 【0067】

その後、チップを所望の形状に分断し、図2(C)に示すように、貼り合わせ加工を施し、両面を樹脂フィルム81で覆い、チップ完成させる。

#### 【0068】

なお、チップの作製方法は上記に限定されず、さらに第3の基板へ転置してもよい。例えば、図3(A)に示すように、剥離した被剥離層69を、第2の接着剤73により転置体となる第3の基板72に貼り付ける。第3の基板72としては、ポリカーボネート、ポリアリレート、ポリエーテルスルファン、ポリエチレンテレフタレート、ポリエチレンナフタレート等のプラスチック基板、ポリテトラフルオロエチレン基板又はセラミック基板等のフィルム基板を用いることができる。第2の接着剤73としては、紫外線により接着性が高くなる紫外線硬化接着剤、熱により粘着性が高くなる熱硬化接着剤を用いることができる。具体的な材料は、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、メラミン樹脂、ウレタン樹脂、シリコン樹脂等の樹脂材料を用いることができる。また、ベンゾシクロブテン、パリレン、フレア、ポリイミドなどの有機材料、シロキサン系ポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料が挙げられる。そして、上記接着剤等のいずれかを有する両面テープを使用することができる。なお、第3の基板72の表面に接着機能がある場合、第2の接着剤73は使用しなくてもよい。

10

#### 【0069】

このような接着剤材料を用いて、被剥離層69の側面まで覆ってもよい。

#### 【0070】

次いで、第1の接着剤70を除去し、第2の基板71を剥がす。第1の接着剤を剥がすために、紫外線照射を照射したり、加熱したり、水洗したりすればよい。また更に、アルゴンガス及び酸素ガスを用いたプラズマクリーニングやベルクリン洗浄を行って、表面をきれいにすると好ましい。

20

#### 【0071】

その後、図3(B)に示すように、保護膜74を用いて被剥離層69を覆う。保護膜74としては、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、メラミン樹脂、ウレタン樹脂、シリコン樹脂等の樹脂材料を用いることができる。また、ベンゾシクロブテン、パリレン、フレア、ポリイミドなどの有機材料、シロキサン系ポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料等を用いて形成してもよい。保護膜74の形成は、スクリーン印刷法や液滴吐出法によって形成することができる。

#### 【0072】

その後好ましくは、図3(C)に示すように貼り合わせ加工を施し、両面を樹脂フィルム81で多い、薄膜トランジスタを有するチップを完成させる。

30

#### 【0073】

また完成されたチップにおいて、貼り合わせ加工を施す前に、その側面の周囲に、エポキシ樹脂等の有機樹脂を充填してもよい。その結果、チップは、貼り合わせ加工前であっても、外部から保護され、持ち運びしやすい形態となる。

#### 【0074】

なお無線チップに本発明を適用する場合、アンテナを一体形成する場合に限定されず、アンテナを外付けして実装してもよい。外付けするアンテナは、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルファン(PES)、塩化ビニリデン、塩化ビニル樹脂等の別の基板上にスパッタリング法、スクリーン印

40

50

刷法、液滴吐出法等により形成される。アンテナが形成される基板には、フィルム基板を用いることができる。そして、配線 6 6 又は導電膜 6 8 にバンプを設け、外付けするアンテナをバンプに接続すればよい。またさらに、露出された配線を介して、アンテナを外付けしてもよい。

#### 【 0 0 7 5 】

本発明のチップは、第 3 の基板 7 2 、つまりフィルム基板上に形成されている。また  $0.2 \mu\text{m}$  以下、代表的には  $40 \text{ nm} \sim 170 \text{ nm}$  、好ましくは  $50 \text{ nm} \sim 150 \text{ nm}$  の膜厚の半導体膜を能動領域として有する。そのため、軽量化、薄型化を高めることができる。その結果、実装させる商品のデザイン性を損ねることがない。またフレキシブル性に富むため、チップの耐衝撃性を高めることができる。また曲面や異形形状な商品にチップを実装することができる。 10

#### 【 0 0 7 6 】

なお本実施の形態において、第 3 の基板 7 2 を転置体とした場合を示したが、これに限定されない。例えば、第 3 の基板の代わりに、直接商品へ転置することも可能である。例えば、ラベル紙やタグ台紙に直接転置し、チップが実装された商品ラベルやタグを作製することができる。商品ラベルやタグを作製する場合、無線チップを用いると無線通信を用いて商品管理ができるため好ましい。無線チップを用いたタグを、無線タグと呼ぶ。

#### 【 0 0 7 7 】

このような剥離方法を用いることより、大型基板に多数チップを形成する場合であっても、全面に剥離でき、歩留まりよく、チップを形成することができる。 20

#### 【 0 0 7 8 】

なお本発明は、チップ完成前に、接触式の検査を行うことができればよく、チップの作製方法、特に剥離方法には限定されない。但し本実施の形態のような剥離方法を用いることにより、TFT 完成後にレーザー照射することができないため、TFT 等に負荷をかけることがなく好ましい。また本実施の形態のような剥離方法では、第 1 の基板 1 0 、第 2 の基板等を再利用することができるため好ましい。その結果、更に安価なフィルム基板を使用するためコストを抑えたチップを提供することができる。

#### 【 0 0 7 9 】

さらにこのような矩形上の基板からチップを形成する場合、円形のシリコンウェハからチップを取り出す場合と比較して、母体基板形状に制約がない。そのため、チップの生産性を高め、大量生産を行うことができる。 30

#### 【 0 0 8 0 】

例えば、直径 12 インチのシリコンウェハを用いた場合と、 $730 \times 920 \text{ mm}^2$  のガラス基板を用いた場合とで取り数等を比較する。前者のシリコン基板の面積は約  $73000 \text{ mm}^2$  であるが、後者のガラス基板の面積は約  $672000 \text{ mm}^2$  であり、ガラス基板はシリコン基板の約 9.2 倍に相当する。後者のガラス基板の面積は約  $672000 \text{ mm}^2$  では、基板の分断により消費される面積を無視すると、1 mm 四方のチップが約 672000 個形成できる計算になり、該個数はシリコン基板の約 9.2 倍の数に相当する。そしてチップの量産化を行なうための設備投資は、 $730 \times 920 \text{ mm}^2$  のガラス基板を用いた場合の方が直径 12 インチのシリコン基板を用いた場合よりも工程数が少なくて済むため、額を 3 分の 1 で済ませることができる。 40

#### 【 0 0 8 1 】

その結果、チップのコストを削減できる。単価が非常に低いチップは、単価コストの削減により非常に大きな利益を生むことができる。

#### 【 0 0 8 2 】

また本発明のチップは、シリコンウェハから形成されるチップと比較して、電波吸収の心配がなく、高感度な信号の受信を行なうことができる。

#### 【 0 0 8 3 】

さらに本発明のチップは、シリコンウェハを有さないため、透光性を有することができる。その結果、実装品の印字面に実装しても、デザイン性を損ねることがない。 50

## 【0084】

本発明の無線チップは、アンテナにより電力、又は信号を得ることができる。アンテナが実装されている本発明の無線チップは、非接触型チップと呼ぶことができる。なお、アンテナは実装せずに、接続端子を形成した接触型チップ、非接触型及び接触型とを混在したハイブリッド型チップがあるが、本実施の形態で示した接触式の検査方法は、非接触型チップ以外の、接触型チップ、及びハイブリッド型チップのいずれにも適用することができる。

## 【0085】

## (実施の形態2)

本実施の形態では、上記実施の形態と異なる方法により剥離し、チップを作製する工程について説明する。

10

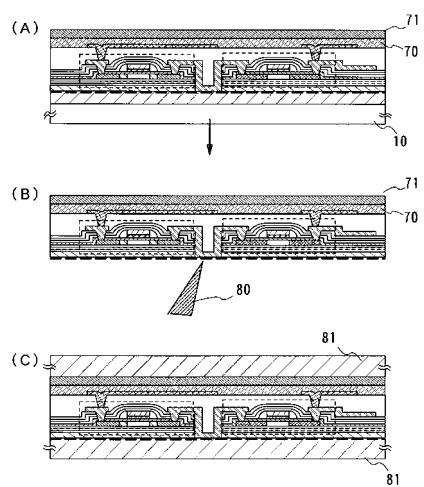

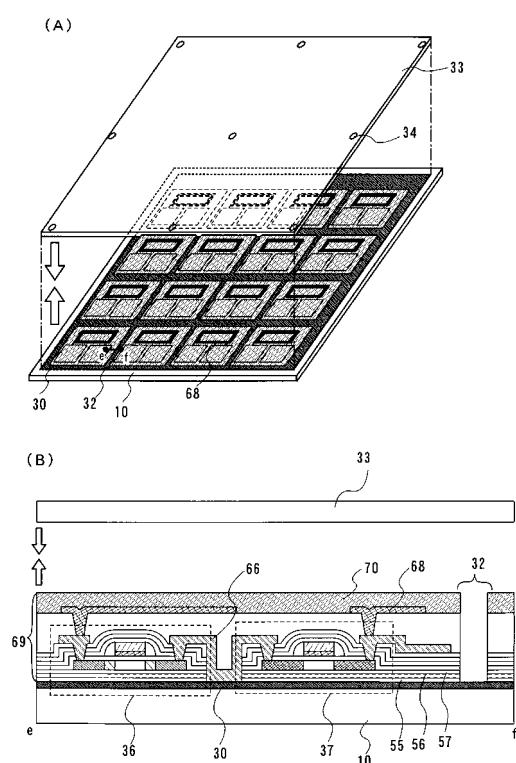

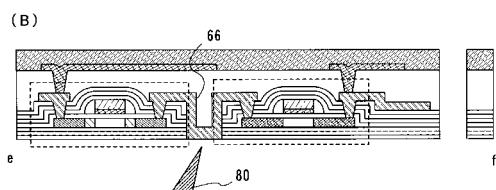

## 【0086】

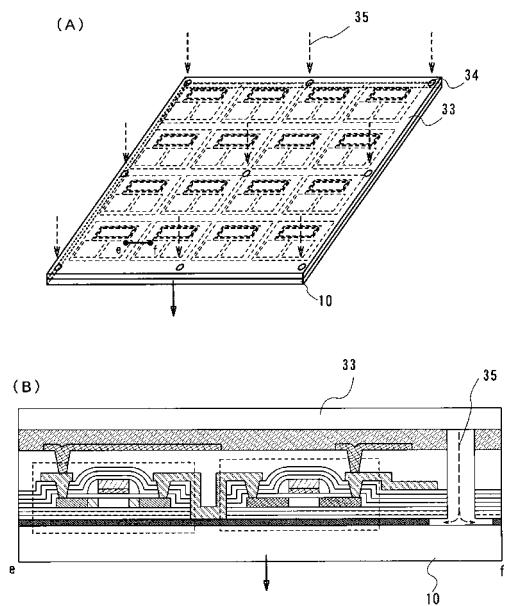

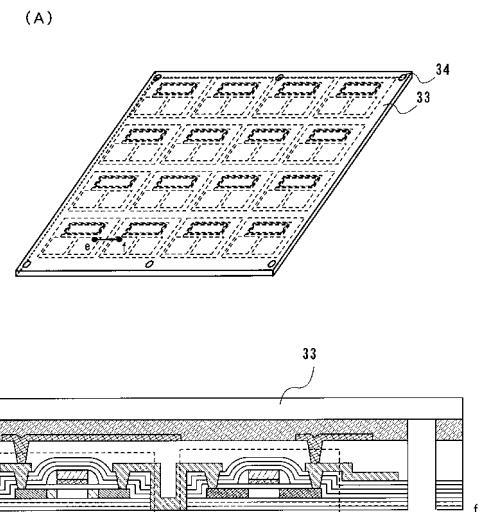

図4(A)、図4(A)のe-fの拡大された断面図を示す図4(B)に示すように、第1の基板10上に、剥離層30を介して半導体膜を形成する。半導体膜は、40nm~170nmの膜厚を有し、非常に薄型である。このような半導体膜を有する薄膜トランジスタを、上記実施の形態と同様に形成し、配線66まで形成されたn型の薄膜トランジスタ36、p型の薄膜トランジスタ37を作製する。

## 【0087】

本発明では、配線66を形成するための開口領域の一部を、剥離層30が露出するよう<sup>20</sup>に、または露出する直前で止めるように形成することを特徴とする。このような開口領域は、ドライエッチング法、ウェットエッチング法、レーザー照射により形成することができることは、上記実施の形態と同様である。

## 【0088】

また剥離層30上に形成される下地膜は、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)(x、y=1、2...)等の酸素、又は窒素を有する絶縁膜の単層構造、又はこれらの積層構造を有するとよい。これら下地膜は、後に剥離層30をエッチングするための材料に対し、剥離層30との十分な選択比がとれるため、正確な剥離を行うことができる。

## 【0089】

本実施の形態では、窒素を有する酸化珪素膜(SiON)55、酸素を有する窒化珪素膜(SiNO)56、窒素を有する酸化珪素膜(SiON)57を順に積層して下地膜とする。

30

これは、第1の基板10等からの不純物拡散を考えると、酸素を有する窒化珪素膜(SiNO)のように窒素含有率の高い絶縁膜を用いると好ましいが、当該SiNOは剥離層30、や半導体膜との密着性が低いことが懸念される。そこで、密着性を高めるために、SiONを設けている。

## 【0090】

このような薄膜トランジスタ36、37により、チップが有する論理回路等を作製することができる。チップが有する論理回路等は、昇圧電源回路、復調回路、変調回路、メモリインターフェース、メモリが挙げられる。無線チップの場合、加えてアンテナ回路がある<sup>40</sup>。

## 【0091】

また配線66を覆って設けられた絶縁膜67、絶縁膜67の開口部に設けられ、配線66に接続される導電膜68も、上記実施の形態と同様に形成する。導電膜68はアンテナとして機能することができる。

## 【0092】

その後、第1の接着剤であって、保護膜としても機能する絶縁膜70を形成する。具体的な材料として、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、メラミン樹脂、ウレタン樹脂、シリコン樹脂等の樹脂材料を用いることができる。また、ベンゾシクロブテン、パリレン、フレア、ポリイミドなどの有機材料、シロキサン系ポリマー等

40

50

の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料が挙げられる。

【0093】

剥離層30としては、珪素を有すればよく、その構造は、非晶質半導体、非晶質状態と結晶状態とが混在したセミアモルファス半導体(SAS)、及び結晶性半導体のいずれでもよい。これらの剥離層30は、スパッタリング法、又はプラズマCVD法等によって形成することができ、その膜厚は、30nm~1μmとすればよく、成膜装置の薄膜形成限界が許容すれば、30nm以下とすることも可能である。また剥離層30として、実施の形態1で述べた金属膜を用いることもできる。

【0094】

また剥離層30には、リンやボロン等の元素を添加してもよい。さらに加熱等により当該元素を活性化させてもよい。元素を添加したり、活性化させることにより、剥離層の反応速度、つまりエッチングレートを改善することができる。

【0095】

本実施の形態では、剥離層に30nm~1μm、好ましくは30nm~50nmの膜厚を有する非晶質珪素膜を用いるが、上述したその他の材料を用いても構わない。

【0096】

また剥離層30より上に形成される、半導体膜、絶縁膜等を合わせて被剥離層69とする。なお、被剥離層69の最上層には、保護膜が形成されていると好ましい。保護膜としては、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、メラミン樹脂、ウレタン樹脂、シリコン樹脂等の樹脂材料を用いることができる。また、ベンゾシクロブテン、パリレン、フレア、ポリイミドなどの有機材料、シロキサン系ポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料が挙げられる。

【0097】

このとき剥離層を選択的に形成してもよい。例えば、第1の基板10上に格子状に形成したり、第1の基板10の周囲は形成しないようにする。剥離層30が形成されない領域があることにより、後に剥離層を除去しても、被剥離層69がばらばらになることがなく、その後の移動に便利である。これは剥離層を除去しても剥離層30が形成されない領域で、被剥離層69と第1の基板10とが一体化されているためである。

【0098】

また、薄膜トランジスタが有する半導体膜に対して、加熱処理を行う場合、剥離層30への影響があると考えられる。例えば、加熱炉を用いる場合や、レーザー照射、特に532nmの波長を用いる場合、剥離層30までそのエネルギーが到達することがある。その結果、剥離層30の状態に変化が生じ、例えば結晶化があることがある。このような剥離層30の結晶化状態によっても、反応速度を制御することができる。

【0099】

一方、剥離層30へレーザーによるエネルギーを到達させないように、下地絶縁膜の構造を選択することもできる。例えば、下地絶縁膜の材料、膜厚、積層順を選択することにより、レーザーエネルギーが到達しなくなる。

【0100】

また薄膜トランジスタが有する半導体膜は、シリコンウェハから形成されるチップと比べて多くの水素を有する。具体的には、水素を $1 \times 10^{19} \sim 1 \times 10^{22} / \text{cm}^3$ 、好ましくは $1 \times 10^{19} \sim 5 \times 10^{20} / \text{cm}^3$ 有するように形成することができる。この水素により、半導体膜中の欠陥を緩和する、所謂欠陥のターミネート効果を奏すことができる。加えて水素により、チップが有する論理回路等の柔軟性を高めることができる。

【0101】

さらに、パターニングされた半導体膜がチップにおいて占める面積の割合を、1~30%とすることで、曲げ応力による薄膜トランジスタの破壊や剥がれを防止することができる。このように、薄膜トランジスタを用いてチップを形成すると、好ましい。

10

20

30

40

50

## 【0102】

その後、チップ間ににおいて、被剥離層69に溝32を形成する。溝32は、ダイシング、スクライビング又はマスクを利用したエッティング等によって形成することができる。溝の形状は、円状（所謂穴に相当）、矩形状（所謂スリットに相当）等とすることができますが、これに限定されない。例えば、溝の幅を異ならせててもよい。具体的には、上方から見たとき、チップ上に形成される溝の幅より、チップ間の上に形成される溝の幅を狭くする。その結果、チップ間の切断をしやすくすることができる。

## 【0103】

ダイシングの場合には、ダイシング装置（ダイサー）を用いるブレードダイシング法が一般的である。ブレードとは、ダイヤモンド砥粒を埋め込んだ砥石で、その幅は約30～50μmであり、このブレードを高速回転させることにより、被剥離層69の一部を分離する。スクライビングの場合には、ダイヤモンドスクライビング法とレーザスクライビング法等がある。エッティングの場合には、露光、現像工程によりマスクパターンを形成し、ドライエッティング、ウェットエッティング等により溝32を形成することができる。ドライエッティングにおいては、大気圧プラズマ法を用いてもよい。

10

## 【0104】

なお溝32は必ずしも、チップ間に形成する必要はなく、薄膜トランジスタ間に形成してもよい。またチップ間の溝と、薄膜トランジスタ間の溝とを合わせて使用してもよい。その結果、剥離層30の除去に要する時間を短縮することができる。

20

## 【0105】

このような第1の基板に、第2の基板33を貼り合わせる。このとき、絶縁膜70の接着性により貼り合わせることができる。また第2の基板33は、溝32の位置に合わせて穴34が設けられている。穴34の形状は、溝32により決めることができ、円状（所謂穴に相当）、矩形状（所謂スリットに相当）とすることができます。第2の基板33としては、ポリカーボネート、ポリアリレート、ポリエーテルスルファン、ポリエチレンテレフタレート、ポリエチレンナフタレート等のプラスチック基板、ポリテトラフルオロエチレン基板又はセラミック基板等のフィルム基板を用いることができる。

## 【0106】

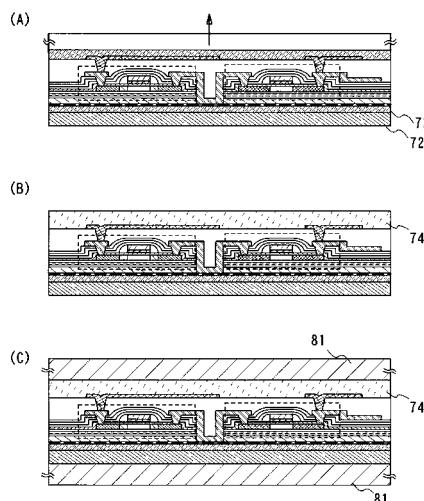

この状態で、図5に示すように剥離層30を除去する。また図5（A）は上面図、図5（B）は図5（A）のe-fの断面図を示す。

30

## 【0107】

まず、剥離層30を除去するエッティング剤35を、溝32へ導入する。エッティング剤35としては、フッ化ハロゲンを含む気体又は液体を使用することができる。例えばフッ化ハロゲンとして $C_1F_3$ （三フッ化塩素）を使用することができる。なお、 $C_1F_3$ は、塩素を200以上でフッ素と反応させることにより、 $C_1_2(g) + 3F_2(g) \rightarrow 2C_1F_3(g)$ の過程を経て生成することができる。また $C_1F_3$ は、反応空間の温度によっては液体の場合もある（沸点11.75）。このような液体を用いたエッティングを行う場合、フッ化ハロゲンを含む液体として、例えばHFを用いてウェットエッティングを採用することもできる。その他のフッ化ハロゲンを含む気体として、 $C_1F_3$ 等に窒素を混合したガスを用いてもよい。

40

## 【0108】

また、剥離層30をエッティングし、下地膜となる絶縁膜55、56、57、及びその他の絶縁膜のいずれかもエッティングしないようなエッティング剤であれば、 $C_1F_3$ に限定されるものでなく、またフッ化ハロゲンに限定されるものでもない。例えば、 $CF_4$ 、 $SF_6$ 、 $NF_3$ 、 $F_2$ 等のフッ素を含む気体をプラズマ化して用いることもできる。その他のエッティング剤として、テトラメチルアンモニウムハイドロオキサイド（TMAH）のような強アルカリ溶液を用いてもよい。

## 【0109】

さらに、 $C_1F_3$ 等のフッ化ハロゲンを含む気体によって化学的に除去する場合、選択的にエッティングされる材料を剥離層30として用い、エッティングされない材料を下地膜とな

50

る絶縁膜 55、56、57として用いるという条件に従うならば、剥離層及び下地絶縁膜の組合せは、上記材料に限定されるものではない。

【0110】

本実施の形態では、複数の第1の基板10に対して一度に処理することのできる減圧CVD装置を用い、エッティング剤：ClF<sub>3</sub>（三フッ化塩素）ガス、温度：350、流量：300 sccm、気圧：6 Torr (798 Pa)、時間：3 hの条件で剥離層30を除去する。但し本発明のエッティング条件は、これに限定されるものではない。このような、減圧CVD装置により、チップの生産性をより高めることができる。

【0111】

また減圧CVD装置は、ガス導入管よりClF<sub>3</sub> 35が導入され、排気管より不要なガスが排気される。このとき、剥離層30が形成されない領域があると、その領域で第1の基板10とチップとが一体化されているため、排気管へ吸い込まれる懼がなく好ましい。このように一体化されると、その後の移動に素子が飛散することなく便利である。

【0112】

さらに減圧CVD装置は加熱手段を設けてもよい。加熱手段により処理温度を100～300とすると剥離層とエッティング剤の反応速度を高めることができる。その結果、エッティング剤の使用量を少なくすることができ、処理時間を短縮することもできる。

【0113】

このように、エッティング剤35により、剥離層30を徐々に後退させて、第1の基板10を剥離することができる。

10

20

【0114】

なお本実施の形態で用いるClF<sub>3</sub>は、珪素を選択的にエッティングする特性があるため、珪素を有する剥離層30を選択的に除去することができる。さらに下地膜となる絶縁膜55、56、57には酸素、又は窒素を有する絶縁膜を用いるため、剥離層30との反応速度の差が大きく、薄膜トランジスタを保護しつつ、剥離層30を容易に除去することができる。また本実施の形態では、薄膜トランジスタの上面や側面は、層間絶縁膜67、ゲート絶縁膜58、絶縁膜70等で覆われているため、薄膜トランジスタがエッティング剤35と反応することを防止できる。

【0115】

このように高温プロセスは第1の基板10を用いて行い、その後第2の基板33に転置することにより、耐熱性の低い基板材料を第2の基板33に用いることができる。

30

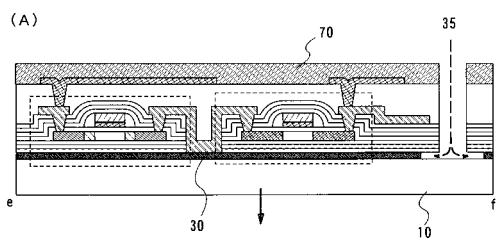

【0116】

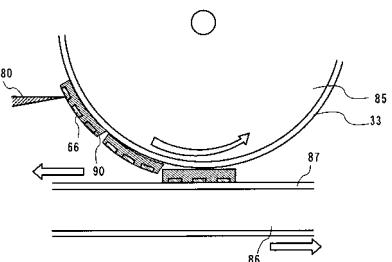

剥離層30を後退させて、第1の基板10を剥離すると、図6に示すように配線66が露出する。すなわち、配線66は半導体膜や下地膜より下の領域まで設けられているため、露出することができる。また図6(A)は上面図、図6(B)は図6(A)のe-fの断面図を示す。ここで、プローブ針80を用いて、チップ、具体的には論理回路等の検査を行うことができる。本発明のように開口領域65に配線66を形成することにより、第1の基板10を剥離すると、配線66を露出することができ、このときチップに対して接触式の検査を行うことができる。接触式の検査は、非接触式と比べて、精度が高く、検査装置も簡便なものであるため好ましい。また本発明は、配線が露出することを特徴としており必ずしもプローブ針を用いて検査を行う必要はない。例えば、露出した配線に、検査装置に接続されたFPC(flexible printed circuit)を貼って検査を行っても構わない。

40

【0117】

その後、チップを所望の形状に分断し、図2(C)に示すように貼り合わせ加工を施し、両面を樹脂フィルム81で覆い、チップを完成させる。

【0118】

また図7に示すように、検査と、貼り合わせ加工を一連作業として行うことができる。第2の基板33をローラ85に設置し、白抜矢印方向に回転させる。このとき配線66が露出しているため、プローブ針80を用いて、チップ90の検査を行うことができる。検査

50

終了後、良品と判断されたチップは、分断される。具体的には、ベルトコンベア86の表面に接着面を備える手段87を設けておき、白抜矢印方向に移動させ、第2の基板33からチップを剥離する。接着面を備える手段87としては、シリコーンゴム、パーフロロエラストマー、フルオンアフラス、テフロン（登録商標）（ポリテトラフルオロエチレンとも記す）ゴム等を使用することができる。特に、パーフロロエラストマー、フルオンアフラスは、耐熱性、耐薬品性の高く好ましい。このとき、接着面を備える手段87の接着強度は、第2の基板33が張り合わされている接着強度より高くなるように設定する。

【0119】

剥離層30が形成されない領域で、被剥離層69と第1の基板10とが一体化されている場合、ローラ85に設置したのち、第1の基板10を剥がすとよい。このとき、簡便に剥がせるように、剥離層30が形成されない領域の大きさを制御する。また、第2の基板33に形成する穴34を円状や矩形状とすることにより、被剥離層69と第2の基板33とが一体化されており、ばらばらになることを防止できる。このように被剥離層69がばらばらにならず、このように一体化されていることにより、ローラ85への設置が簡便になる。

10

【0120】

その後、チップ90は、ベルトコンベア86に乗せられ、貼り合わせ加工を施すことができる。

【0121】

このように、チップの検査、貼り合わせ加工を一連作業で行うことにより、生産性を高めることができる。また接触式の検査は、非接触式と比べて、精度が高く、検査装置も簡便なものであるため好ましい。

20

【0122】

また、剥離された第1の基板10、第2の基板33は再利用することができる。その結果、チップの低コスト化を達成することができる。再利用する場合、溝32を形成するためのダイシングやスクライビング等において、第1の基板10に傷が生成されないように制御するのが望ましい。しかし、傷が生成された場合であっても、塗布法や液滴吐出法によつて有機樹脂や無機膜を形成し、平坦化処理を行なうことができる。なお液滴吐出法とは、導電膜や絶縁膜などの材料が混入された組成物の液滴（ドットとも表記する）を選択的に吐出（噴出）する方法であり、その方式によっては、インクジェット法とも呼ばれる。

30

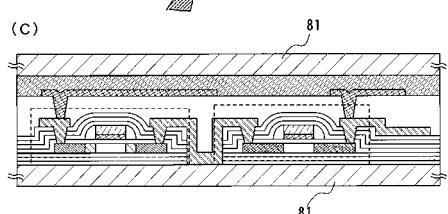

【0123】

また第2の基板33を用いずに、チップを形成する場合を説明する。図8（A）に示すように、絶縁膜70を形成した後、溝32を形成し、エッチング剤35を導入する。そして剥離層30を後退させて、第1の基板10を剥離する。なお絶縁膜70の具体的な材料として、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、メラミン樹脂、ウレタン樹脂、シリコン樹脂等の樹脂材料を用いることができる。また、ベンゾシクロブテン、パリレン、フレア、ポリイミドなどの有機材料、シロキサン系ポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料が挙げられる。

【0124】

40

そして第1の基板10を剥離すると、図8（B）に示すように配線66が露出する。そこで、プローブ針80を用いて、接触式の検査を行うことができる。

【0125】

その後、図8（C）に示すように、貼り合わせ加工を施し、両面を樹脂フィルム81で覆い、チップを完成させる。

【0126】

このように、第2の基板33を用いずにチップを形成すると、溝32と、穴34との位置あわせの制約がなく好ましい。

【0127】

さらに第2の基板33を用いずに第1の基板を剥離する場合、ローラに絶縁膜70を粘着

50

させ、ローラの回転力を用いて第1の基板を剥離することができる。

【0128】

また第2の基板33を用いない場合であっても、溝32の形状によって、絶縁膜70により被剥離層69全体が一体化されている。そのため、図7に示すような、検査と、貼り合わせ加工を一連作業として行うことができる。

【0129】

このように完成されたチップにおいて、貼り合わせ加工を施す前に、その側面の周囲に、エポキシ樹脂等の有機樹脂を充填してもよい。その結果、チップは、貼り合わせ加工前であっても、外部から保護され、持ち運びしやすい形態となる。

【0130】

このような無線チップは、アンテナを一体形成する場合に限定されず、アンテナを外付けして実装してもよい。この場合、配線66又は導電膜68と接続するようにバンプを設け、外付けするアンテナをバンプに接続すればよい。またさらに、露出された配線を介して、アンテナを外付けしてもよい。

【0131】

本発明のチップは、第3の基板72、つまりフレキシブル基板上に形成されている。また0.2μm以下、代表的には40nm～170nm、好ましくは50nm～150nmの膜厚の半導体膜を能動領域として有する。そのため、軽量化、薄型化を高めることができる。その結果、実装させる商品のデザイン性を損ねることがない。またフレキシブル性に富むため、チップの耐衝撃性を高めることができる。また曲面や異形形状な商品にチップを実装することができる。

10

【0132】

なお本実施の形態において、第3の基板72を転置体とした場合を示したが、これに限定されない。例えば、第3の基板の代わりに、直接商品へ転置することも可能である。例えば、ラベル紙やタグ台紙に直接転置し、チップが実装された商品ラベルやタグを作製することができることは、上記実施の形態1と同様である。

【0133】

このような剥離方法を用いることより、大型基板に多数チップを形成する場合であっても、全面に剥離でき、歩留まりよく、チップを形成することができる。

【0134】

なお本発明は、チップ完成前に、接触式の検査を行うことができればよく、チップの作製方法、特に剥離方法には限定されない。但し本実施の形態のような剥離方法を用いることにより、TFT完成後にレーザー照射することができないため、TFT等に負荷をかけることがなく好ましい。また本実施の形態のような剥離方法では、第1の基板10、第2の基板等を再利用することができるため好ましい。その結果、更に安価なフィルム基板を使用するためコストを抑えたチップを提供することができる。

20

【0135】

さらにこのような矩形上の基板からチップを形成する場合、円形のシリコンウェハからチップを取り出す場合と比較して、母体基板形状に制約がない。そのため、チップの生産性を高め、大量生産を行うことができる。

30

【0136】

例えば、直径12インチのシリコンウェハを用いた場合と、730×920mm<sup>2</sup>のガラス基板を用いた場合とで取り数等を比較する。前者のシリコン基板の面積は約73000mm<sup>2</sup>であるが、後者のガラス基板の面積は約672000mm<sup>2</sup>であり、ガラス基板はシリコン基板の約9.2倍に相当する。後者のガラス基板の面積は約672000mm<sup>2</sup>では、基板の分断により消費される面積を無視すると、1mm四方のチップが約672000個形成できる計算になり、該個数はシリコン基板の約9.2倍の数に相当する。そしてチップの量産化を行なうための設備投資は、730×920mm<sup>2</sup>のガラス基板を用いた場合の方が直径12インチのシリコン基板を用いた場合よりも工程数が少なくて済むため、額を3分の1で済ませることができる。

40

50

**【 0 1 3 7 】**

その結果、チップのコストを削減できる。単価が非常に低いチップは、単価コストの削減により非常に大きな利益を生むことができる。

**【 0 1 3 8 】**

また本発明のチップは、シリコンウェハから形成されるチップと比較して、電波吸収の心配がなく、高感度な信号の受信を行なうことができる。

**【 0 1 3 9 】**

さらに本発明のチップは、シリコンウェハを有さないため、透光性を有することができる。その結果、実装品の印字面に実装しても、デザイン性を損ねることがない。

**【 0 1 4 0 】**

本発明の無線チップは、アンテナにより電力、又は信号を得ることができる。

アンテナが実装されている本発明の無線チップは、非接触型チップと呼ぶことができる。なお、アンテナは実装せずに、接続端子を形成した接触型チップ、非接触型及び接触型とが混在したハイブリッド型チップがあるが、本実施の形態で示した接触式の検査方法は、非接触型チップ以外の、接触型チップ、及びハイブリッド型チップのいずれにも適用することができる。

**【 0 1 4 1 】****( 実施の形態 3 )**

本実施の形態では、上記実施の形態を組み合わせた方法により、チップを作製する工程について説明する。

**【 0 1 4 2 】**

例えば、剥離層 30 に金属膜、及び珪素を有する膜を積層して用いることができる。その結果、両者の剥離条件のいずれかを満たせばよいこととなり、プロセスマージンを広げることができる。

**【 0 1 4 3 】**

また、剥離層 30 に金属膜を用い、ダイシング等により溝 32 を形成する。そして、溝に金属膜のみをエッチングするエッチング剤を導入して、第 1 の基板 10 を剥離することができる。

**【 0 1 4 4 】**

このように、実施の形態 1 と実施の形態 2 とは自由に組み合わせることができる。

**【 0 1 4 5 】****( 実施の形態 4 )**

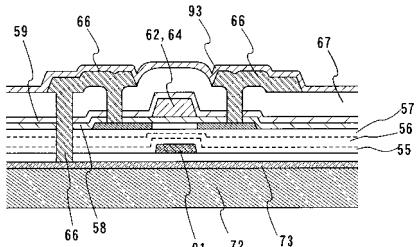

本実施の形態では、上記実施の形態で示した薄膜トランジスタと異なる構成の薄膜トランジスタについて詳述する。

**【 0 1 4 6 】**

薄膜トランジスタの構成は、上記実施の形態で示したように半導体膜上にゲート電極 62 、 64 が設けられたトップゲート型以外に、半導体膜を挟んで上下にゲート電極（上部ゲート電極、及び下部ゲート電極と表記する）が設けられたデュアルゲート型を用いることができる。本実施の形態では、接着剤 73 を介して第 3 の基板 72 に貼り付けられたデュアルゲート型の薄膜トランジスタの構成を、図 9 を用いて説明する。

**【 0 1 4 7 】**

まず、下部ゲート電極 91 として機能する導電膜を形成する。導電膜は、金属又は一導電型の不純物を添加した多結晶半導体で形成することができる。金属を用いる場合は、タンゲステン (W) 、モリブデン (Mo) 、チタン (Ti) 、タンタル (Ta) 、アルミニウム (Al) などを用いることができる。下部ゲート電極 91 は、マスク、例えばレジストマスクを用いて、所定の形状にエッチングする。このとき、微細な下部ゲート電極を形成するため、酸素プラズマにより細められたレジストマスクを用いてエッチングしてもよい。

**【 0 1 4 8 】**

そして、下地膜として機能する絶縁膜を形成する。本実施の形態では、窒素を有する酸化

10

20

30

40

50

珪素膜(SiON)55、酸素を有する窒化珪素膜(SiNO)56、窒素を有する酸化珪素膜(SiON)57を順に積層するが、これに限定されない。例えば、酸素を有する窒化珪素膜(SiNO)からなる単層構造を用いてもよい。下地膜により、第3の基板72や接着剤73からの不純物、下部ゲート電極91からの金属の、半導体膜への拡散を防止することができる。

【0149】

次に、所定の形状を有する半導体膜、半導体膜を覆って設けられたゲート絶縁膜58、上部ゲート電極62、64として機能する導電膜を順に設ける。これらの材料や作製方法は、上記実施の形態を参照することができる。

【0150】

なお、上部ゲート電極62、64を所定の形状にパターニングするためのレジストマスクを形成する。このとき、下部ゲート電極91を用いた裏面露光により所定の形状を有するレジストマスクを形成することができる。そして、当該レジストマスクを用いて、パターニングすることができる。このように、下部ゲート電極を用いてレジストマスクを露光することにより、上部ゲート電極の位置合わせの制約を緩和することができる。

【0151】

なお、上記実施の形態に示したように、上部ゲート電極62、64を積層構造とする場合、上部ゲート電極の下層電極をパターニングするときに、下部ゲート電極91を用いて露光されたレジストマスクを用いる。その後、上層電極を形成する。

【0152】

その後、上部ゲート電極62、64を用いて、半導体膜に不純物元素を添加する。このとき、上記実施の形態のようにサイドウォールとして機能する絶縁物を設け、低濃度不純物領域の大きさ等を制御することができる。

【0153】

また上部ゲート電極62、64を積層構造とする場合、上層電極を用いて、低濃度不純物領域を形成することができる。このとき、低濃度不純物領域は、下層電極と重なるため、GOLD構造となる。

【0154】

そして、下部ゲート電極91と、上部ゲート電極62、64を別に制御するため、それぞれに配線を接続する。まず、下部ゲート電極91に接続される配線を設けるため、上部ゲート電極62、64の一部を除去してコンタクトホールを形成する。上部ゲート電極62、64が下層電極と、上層電極との積層構造の場合、下層電極の一部を除去する。

【0155】

なお下部ゲート電極91と、上部ゲート電極62、64と同じように制御する場合、上記のように上部ゲート電極62、64の一部を除去する必要はない。下部ゲート電極91上に設けられるゲート絶縁膜58にコンタクトホールを形成し、当該コンタクトホールに直接上部ゲート電極62、64を形成すればよい。

【0156】

その後、ゲート電極を覆って、絶縁膜59、67を形成する。絶縁膜59、67は、無機材料、又は有機材料から形成することができる。また上記実施の形態に示すように絶縁膜59以外の絶縁膜を積層してもよい。また絶縁膜67によって、平坦性を高める場合、絶縁膜67は有機材料を用いると好ましい。

【0157】

その後、絶縁膜59、67、ゲート絶縁膜47に開口領域を形成し、不純物領域と接続する配線66として機能する導電膜を形成する。その後、配線66を覆って絶縁膜93を設けることができる。絶縁膜93は、無機材料又は有機材料から形成することができる。また積層構造であっても、単層構造であってもよい。

【0158】

このとき、開口領域の一部は、下部ゲート電極91と同一層までエッチングする。そのため、第1の基板10を剥離後、配線66が露出し、接触式の検査を行うことができる。

10

20

30

40

50

## 【0159】

配線 6 6 に、さらに接続される導電膜 6 8 を形成してもよい。アンテナは、配線 6 6 、又は導電膜 6 8 を用いて、形成することができる。

## 【0160】

このようにして下部ゲート電極 9 1 を有するデュアルゲート型の薄膜トランジスタを、チップの論理回路に適用することができる。下部ゲート電極 9 1 は、上部ゲート電極 6 2 、6 4 と別に制御することができる。そのため、ゲート電極が微細な薄膜トランジスタを形成する場合、上部ゲート電極にオフとなる信号を入力するときに電流が流れてしまうことがあっても、下部ゲート電極 9 1 を制御することにより、正確にオフ状態とすることができます。その結果、低消費電力化を図ることができる。

10

## 【0161】

具体的には、N型の薄膜トランジスタ 3 6 をデュアルゲート型とする場合、下部ゲート電極 9 1 に対する負のバイアス電圧の印加は、しきい値電圧を高めることによって、リーク電流を減少させることができる。また、正のバイアス電圧の印加は、しきい値電圧を下げることによって、チャネル形成領域に電流が流れやすくすることができる。従って、デュアルゲート型の薄膜トランジスタは、より高速化、若しくはより低電圧で動作することができます。

## 【0162】

本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

20

## 【0163】

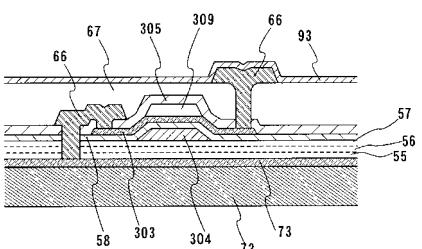

## (実施の形態 5 )

本実施の形態では、上記実施の形態と異なる TFT の構成について説明する。

## 【0164】

図 1 0 は、半導体膜下方にゲート電極を有するボトムゲート型の薄膜トランジスタを示す。なお本実施の形態において、接着剤 7 3 を介して第 3 の基板 7 2 に貼り付けられた状態のボトムゲート型の薄膜トランジスタを説明する。

30

## 【0165】

接着剤 7 3 を介して第 3 の基板 7 2 に貼り付けられたボトムゲート型薄膜トランジスタは、下地膜上にゲート電極 3 0 4 として機能する導電膜が設けられている。本実施の形態では、下地膜として、窒素を有する酸化珪素膜 (SiON) 5 5 、酸素を有する窒化珪素膜 (SiNO) 5 6 、窒素を有する酸化珪素膜 (SiON) 5 7 を順に積層するが、これに限定されない。例えば、酸素を有する窒化珪素膜 (SiNO) からなる単層構造を用いてもよい。

## 【0166】

ゲート電極 3 0 4 は、単層構造であっても、積層構造であってもよく、Ta、W、Ti、Mo、Al、Cu から選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料で形成することができる。なお、その後の工程において加熱処理を施す場合、W のように、耐熱性の高い材料を用いるとよい。さらには耐熱性を高めるため陽極酸化法を用いて、ゲート電極 3 0 4 の周りに絶縁物を形成してもよい。

40

## 【0167】

その後、ゲート絶縁膜 5 8 として機能する絶縁膜、半導体膜を形成する。半導体膜は、非晶質半導体、SAS を用いると好ましいが、結晶性半導体膜を用いてもよい。例えば非晶質半導体膜を形成後、加熱処理を施し結晶性半導体膜を形成することができる。このとき、ゲート電極の耐熱性を考慮する必要がある。

## 【0168】

その後半導体膜上に、チャネル保護膜 3 0 9 として機能する絶縁膜を形成する。チャネル保護膜 3 0 9 により、半導体膜がエッチングされることを防止することができ好ましいが、必ずしもチャネル保護膜 3 0 9 は必要ではない。

## 【0169】

その後、これらを覆って絶縁膜 3 0 5 を形成する。絶縁膜 3 0 5 は無機材料、又は有機材

50

料から形成することができる。本実施の形態では、半導体膜への不純物等汚染を防止することを考え、窒素を有する酸化珪素膜( SiON )を用いて絶縁膜305を形成する。

#### 【0170】

そして、半導体膜に接続する配線66を形成するため、開口領域を形成する。本実施の形態では、一方の配線66のみを形成する。このとき、開口領域の一部は、下地膜までエッチングする。そのため、第1の基板10を剥離後、配線66が露出し、接触式の検査を行うことができる。

#### 【0171】

またコンタクト抵抗を下げるため、n型を有する半導体膜を、配線66と、半導体膜との接続箇所に設けてもよい。

10

#### 【0172】

その後、絶縁膜67を設ける。絶縁膜67は、無機材料、又は有機材料から形成することができる。平坦性を高めるためには有機材料を用いるとよい。

#### 【0173】

そして他方の配線66を形成するため、絶縁膜67、305に開口領域を形成する。このとき、開口領域の一部を、下地膜までエッチングすることができる。その結果、第1の基板10を剥離後、配線66が露出し、接触式の検査を行うことができる。

#### 【0174】

その後、配線66、絶縁膜67を覆うように、絶縁膜93を形成する。絶縁膜93は、無機材料、又は有機材料から形成することができるが、不純物等の汚染を防止することを考え、窒素を有する酸化珪素膜( SiON )を用いて絶縁膜93を形成する。

20

#### 【0175】

このような構造を有するボトムゲート型薄膜トランジスタを、チップの論理回路に適用することができる。

#### 【0176】

なお、チップの論理回路に用いられる薄膜トランジスタは、上記実施の形態のようなトップゲート型、デュアルゲート型であっても、ボトムゲート型であってもよい。またトップゲート型と、ボトムゲート型、デュアルゲート型をそれぞれ組み合わせて用いてもよい。

#### 【0177】

本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

30

#### 【0178】

(実施の形態6)

本実施の形態では、多層配線構造について説明する。

#### 【0179】

チップのように小さな面積に、論理回路を形成する場合、回路同士、薄膜トランジスタ同士を接続する配線を多層構造とすると集積化でき、好ましい。本実施の形態では、トップゲート型の薄膜トランジスタを用いて、多層配線構造について説明する。

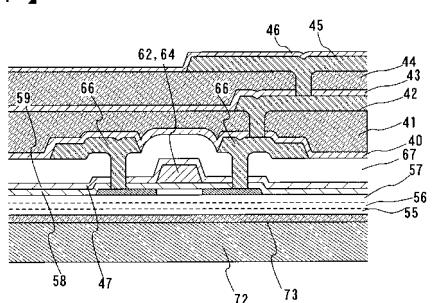

#### 【0180】

図11には、配線66と接続される配線42、配線42に接続される配線45が積層される薄膜トランジスタを示す。配線66、42、45の材料は、上記実施の形態と同様に、アルミニウム( Al )、チタン( Ti )、モリブデン( Mo )、タングステン( W )もしくはシリコン( Si )の元素からなる膜又はこれらの元素を用いた合金膜を用いればよい。

40

#### 【0181】

このとき、配線間に設けられる絶縁膜は、無機材料、又は有機材料から形成することができる、絶縁膜単層構造であっても、積層構造であってもよいが、好ましくは無機材料と、有機材料の積層構造とするとよい。本実施の形態では、配線66、配線42間に設けられる絶縁膜40に、窒素を有する酸化珪素膜( SiON )を用い、絶縁膜41にシリコンを用いることができる。これら無機材料により、不純物等の汚染防止をはかり、有機材料により平坦性を高めることができる。同様に、配線42、配線45間に設けられる絶縁膜4

50

3に、窒素を有する酸化珪素膜(SiON)を用い、絶縁膜44にシロキサンを用いることができる。

【0182】

このような積層構造を有する絶縁膜の構成は、多層配線構造に好適である。

【0183】

本実施の形態は、上記実施の形態と自由に組み合わせることができる。

【0184】

(実施の形態7)

本実施の形態では、積層された薄膜トランジスタ構造について説明する。

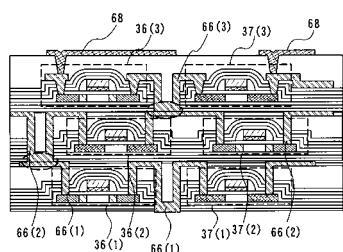

【0185】

第1の基板10を剥離後、配線66が露出するため、これらを積層することが簡便となる。例えば、図12には、薄膜トランジスタ36、37を3つ積層した構造を示す。各層の薄膜トランジスタを36(1)、36(2)、36(3)、及び37(1)、37(2)、37(3)とし、それぞれの配線を66(1)、66(2)、66(3)とする。

10

【0186】

接触式の検査を得て、論理回路に分断された薄膜トランジスタは、配線66を介して積層される。このとき、配線66が露出しているため、接続するためのバンプ、ワイヤボンディングを不要とすることができます。

【0187】

そのため、上部の薄膜トランジスタに向けて、論理回路領域を小さくする必要がなく、高集積化を達成することができます。

20

【0188】

また第3の層には、配線66(3)と接続される導電膜68を形成する。導電膜68はアンテナとして機能することができる。なお導電膜68は第3の層に形成することに限定されず、第1の層、第2の層に形成してもよい。

【0189】

このように配線66を露出することにより、積層された薄膜トランジスタを簡便に作製することができる。

【0190】

このような積層された薄膜トランジスタ構造は、各層にセンサー機能を持たせ、複合センサー装置に適用できる。例えば、第1層目の薄膜トランジスタを用いて圧力センサーを形成し、第2層目の薄膜トランジスタを用いて温度センサーを形成し、第3層目の薄膜トランジスタを用いてフォトセンサーを形成することができる。

30

【0191】

特に多層配線構造で示したように、配線66に接して形成される絶縁膜には、無機材料と有機材料とが積層した構造を用いるとよい。

【0192】

またさらに、露出された配線を介して、アンテナを貼り付けてもよい。

【0193】

本実施の形態は、上記実施の形態と自由に組み合わせることができる。

40

【0194】

(実施の形態8)

本実施の形態では、貼り合わせ加工された無線チップの断面図について説明する。

【0195】

無線チップは、アンテナより電源を供給するため、電源の安定化が難しく、消費電力を極力抑制することが必要である。仮に、消費電力が増加すると、電磁波を入力する必要があるため、リーダライタの消費電力の増加、他の装置や人体への悪影響、無線チップとリーダライタとの通信距離に制約が生じるなどの不都合が生じる。

【0196】

そこで、本実施の形態では、消費電力を抑制することが可能とするため、デュアルゲート

50

構造の薄膜トランジスタを用いて無線チップを形成することを特徴とする。

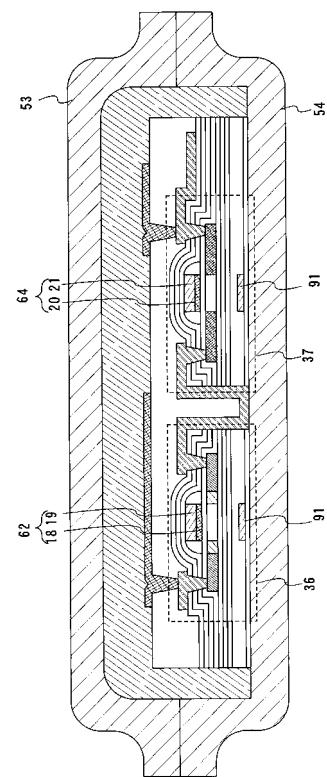

【0197】

図13には、下部ゲート電極91と上部ゲート電極62を含むN型の薄膜トランジスタ36と、下部ゲート電極91と上部ゲート電極64を含むP型の薄膜トランジスタ37を示す。

【0198】

また無線チップに対して貼り合わせ加工を行って、論理回路等を構成する薄膜トランジスタを、第1の基体53と第2の基体54により封止する。このようにして、第1の基体53と第2の基体54により封止された無線チップが完成する。

【0199】

上記の通り、下部ゲート電極91に印加するバイアス電圧を制御することで、薄膜トランジスタ36、37のしきい値電圧を変えて、リーク電流を減少させ、その結果、無線チップ自体の消費電力を抑制することができる。従って、暗号処理などの複雑な処理を行っても、電源が不安定になることがなく、電源の安定化を実現する。また、電磁波を入力する必要がなく、リーダライタとの通信距離を改善することができる。なお、バイアス電圧の印加は、専用の制御回路を設けて、アンテナを介した電源の状態によって切り換えるといい。

10

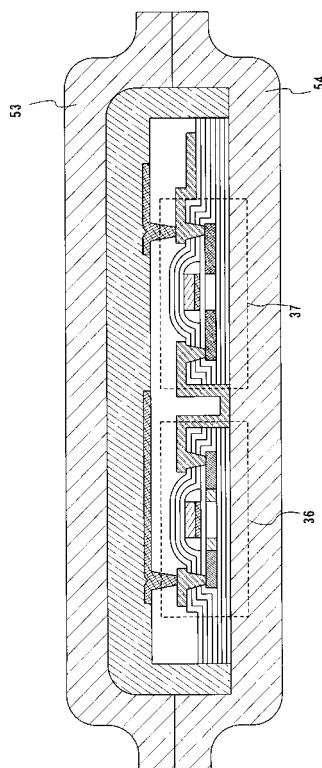

【0200】

なおデュアルゲート構造の薄膜トランジスタを用いる場合を説明したが、図14に示すように、シングルゲート構造の薄膜トランジスタを用いてもよい。図14には、シングルゲート構造のN型の薄膜トランジスタ36、及びP型の薄膜トランジスタ37を示す。

20

【0201】

なお図14において、薄膜トランジスタ、アンテナ、及び保護層までの厚みは、20μm～40μmであり、第1の基体53及び第2の基体54のそれぞれの膜厚は、15μm～35μmである。

【0202】

本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

【0203】

なお接触型チップの場合、図13、図14において、アンテナを形成しない構成とすればよい。但し、接触型チップは、接続端子を露出しておくため、貼り合わせ加工のとき、その領域を開口しておく。

30

【0204】

(実施の形態9)

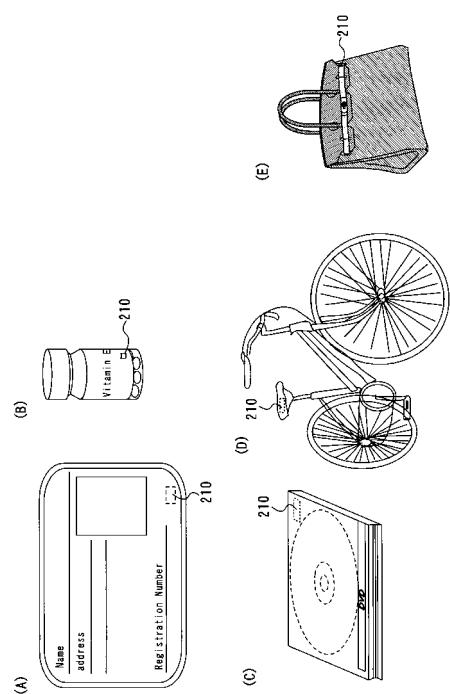

本発明のチップの用途は広範にわたり、あらゆる商品に実装することができる。例えば、紙幣、硬貨、有価証券類、無記名債券類、証書類（運転免許証や住民票等、図15（A）参照）、包装用容器類（包装紙やボトル等、図15（B）参照）、記録媒体（DVDソフトやビデオテープ等、図15（C）参照）、乗物類（自転車等、図15（D）参照）、装身具（鞄や眼鏡等、図15（E）参照）、食品類、衣類、生活用品類、電子機器等に貼り付けて使用することができる。電子機器とは、液晶表示装置、EL表示装置、テレビジョン装置（単にテレビ、テレビ受像機、テレビジョン受像機とも呼ぶ）、コンピュータ、及び携帯電話機等を指す。このように電子機器に貼り付ける場合、チップにより電子機器の機能を補助することができる。特にコンピュータや携帯電話機にチップを貼り付ける場合、メモリ機能の補助をすることができる。このようなチップであって、無線通信を行うものを無線メモリと呼ぶ。またこのようなチップは、コンピュータや携帯電話機に差し込んで使用するため、接続端子を有する接触型であってもよい。

40

【0205】

チップは、商品の表面に貼ったり、商品に埋め込んだりして、商品に固定することができる。例えば、本なら表紙の厚紙に埋め込んだり、有機樹脂からなるパッケージなら当該有機樹脂に埋め込んだりする。また、紙幣、硬貨、有価証券類、無記名債券類、証書類等なら、表面に貼り付けたり、埋め込んだりする。上記に挙げた商品のうち、例えば、包装用

50

容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等にチップを設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。このように商品に埋め込む場合、無線通信を行う無線チップを用いると好ましい。

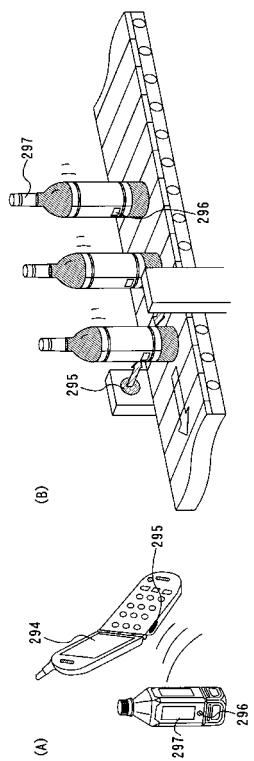

#### 【0206】

また、チップを、物の管理や流通のシステムに応用することで、システムの高機能化を図ることができる。例えば、表示部294を含む携帯端末の側面にリーダライタ295を設けて、商品297の側面にチップ296を設ける場合が挙げられる（図16（A）参照）。この場合、リーダライタ295にチップ296をかざすと、表示部294に商品297の原材料や原産地、流通過程の履歴等の情報が表示されるシステムになっている。また、別の例として、ベルトコンベアの脇にリーダライタ295を設ける場合が挙げられる（図16（B）参照）。この場合、商品297には、チップが実装されたラベルが貼られており、の検品を簡単に行うことができる。このようにリーダライタにかざす場合、無線通信を行う無線チップを使用する。

#### 【0207】

またさらに、チップは動物の管理にも使用することができる。例えば、家畜等にチップを埋め込み、健康状態等を管理することができる。またペットの首輪等にチップを貼り付け、迷子のときの現在地を把握することもできる。このような動物管理に用いる場合、無線通信を行う無線チップを使用する。

#### 【0208】

また医療にチップを用いることができる。このようなチップは、無線通信を行う無線チップを用いると好ましい。医療に用いる無線チップを医療用無線チップと呼ぶ。

#### 【0209】

また接触型チップは、カードに搭載することができる。また、集積回路（LSI）の機能を補助するため、端子を介して接触型チップを実装してもよい。

#### 【0210】

本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

#### 【図面の簡単な説明】

#### 【0211】

【図1】本発明のチップの作製工程を示した図である

【図2】本発明のチップの作製工程を示した図である

【図3】本発明のチップの作製工程を示した図である

【図4】本発明のチップの作製工程を示した図である

【図5】本発明のチップの作製工程を示した図である

【図6】本発明のチップの作製工程を示した図である

【図7】本発明のチップの検査工程を示した図である

【図8】本発明のチップの作製工程を示した図である

【図9】本発明のチップが有する薄膜トランジスタの構成を示した図である

【図10】本発明のチップが有する薄膜トランジスタの構成を示した図である

【図11】本発明のチップが有する薄膜トランジスタの構成を示した図である

【図12】本発明の薄膜トランジスタを積層した構成を示した図である

【図13】本発明のチップの断面を示した図である

【図14】本発明のチップの断面を示した図である

【図15】本発明のチップを実装した商品を示した図である

【図16】本発明のチップを実装した商品を示した図である

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

|                          |                 |

|--------------------------|-----------------|

| (51)Int.Cl.              | F I             |

| G 0 6 K 19/07 (2006.01)  | G 0 6 K 19/00 H |

| G 0 6 K 19/077 (2006.01) | G 0 6 K 19/00 K |

(56)参考文献 特開平11-026734 (JP, A)

特開2004-214281 (JP, A)

特開2003-100450 (JP, A)

特開2001-015721 (JP, A)

特開昭62-219954 (JP, A)

特開平11-020360 (JP, A)

特開2003-174153 (JP, A)

特開平04-178633 (JP, A)

## (58)調査した分野(Int.Cl., DB名)

|         |                       |

|---------|-----------------------|

| H 0 1 L | 2 7 / 1 2             |

| H 0 1 L | 2 1 / 0 2             |

| G 0 6 K | 1 9 / 0 0 - 1 9 / 1 8 |

| H 0 1 L | 2 1 / 2 0             |

| H 0 1 L | 2 1 / 3 3 6           |

| H 0 1 L | 2 9 / 7 8 6           |