(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-294867

(P2005-294867A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

H01L 33/00

H01S 5/323

F 1

H01L 33/00

H01S 5/323

テーマコード(参考)

5FO41

5F173

審査請求 有 請求項の数 8 O L (全 14 頁)

(21) 出願番号 特願2005-186712 (P2005-186712)

(22) 出願日 平成17年6月27日 (2005.6.27)

(62) 分割の表示 特願2001-121689 (P2001-121689)

の分割

原出願日 平成13年4月19日 (2001.4.19)

(71) 出願人 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(74) 代理人 100122884

弁理士 角田 芳末

(74) 代理人 100113516

弁理士 磯山 弘信

(72) 発明者 菊池 剛志

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 奥山 浩之

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

最終頁に続く

(54) 【発明の名称】窒化物半導体素子の製造方法及び窒化物半導体素子

## (57) 【要約】

【課題】 活性層とその後に積層する窒化物半導体層の成長温度に起因する活性層の劣化等の問題を解決し、発光特性などの素子特性の優れた窒化物半導体素子を製造する方法を提供する。

【解決手段】 基体10上に気相成長した活性層13がInを含む混晶であり、前記活性層13のIn組成率がX(%)とされ、その気相成長後に積層される全ての窒化物半導体層の成長温度T( )が(1080 - 4.27 X)以下の温度とすることにより、活性層13中での例えばIn-Nのボンドが切断されることによる窒素空孔の発生やIn金属化などの問題が未然に防止され該活性層の結晶性を良好に保つことできる。

【選択図】

図1

**【特許請求の範囲】****【請求項 1】**

基体上に気相成長した活性層が In を含む混晶であり、

前記活性層の In 組成率が X ( % ) とされ、

その気相成長後に積層される全ての窒化物半導体層の成長温度 T ( ) が ( 1 0 8 0 - 4

. 2 7 X ) 以下の温度とされる

ことを特徴とする窒化物半導体素子の製造方法。

**【請求項 2】**

前記気相成長後に積層される全ての窒化物半導体層の成長温度 T ( ) は、 ( 9 8 0 -

4 . 2 7 X ) 以下の温度であることを特徴とする請求項 1 に記載の窒化物半導体素子の製

造方法。 10

**【請求項 3】**

第 1 の窒化物半導体層と、

該第 1 の窒化物半導体層上に積層される活性層と、

前記第 1 の窒化物半導体層と反対導電型とされ前記活性層上に積層される第 2 の窒化物

半導体層とを有し、

前記第 2 の窒化物半導体層は、成長温度が 9 0 0 以下とされ、且つ平坦化面を呈する

厚みを有する

ことを特徴とする窒化物半導体素子。

**【請求項 4】**

前記第 2 の窒化物半導体層は 5 0 n m 以上の厚みを有することを特徴とする請求項 3 に

記載の窒化物半導体素子。 20

**【請求項 5】**

前記第 2 の窒化物半導体層は 1 0 0 n m 以上の厚みを有することを特徴とする請求項 3 に

記載の窒化物半導体素子。 30

**【請求項 6】**

前記第 2 の窒化物半導体層が p 型であることを特徴とする請求項 3 に記載の窒化物半導

体素子。

**【請求項 7】**

前記第 2 の窒化物半導体層が n 型であることを特徴とする請求項 3 に記載の窒化物半導

体素子。 30

**【請求項 8】**

前記窒化物半導体層は窒化ガリウム層であることを特徴とする請求項 3 に記載の窒化物

半導体素子。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は窒化ガリウム系化合物半導体などの窒化物半導体を基体上に成長させて製造す

る窒化物半導体素子の製造方法に関し、特に半導体発光ダイオードや半導体レーザーなど

の半導体発光素子を製造する窒化物半導体素子の製造方法及び窒化物半導体素子に関する

。 40

**【背景技術】****【0 0 0 2】**

GaN、AlGaN、GaInNなどの窒化物(ナイトライド)系 III-V族化合物半導体は、その禁制帯幅が 1 . 8 eV から 6 . 2 eV に亘っており、赤色から紫外線の発光が可能な発光素子の実現が理論上可能であるため、近年、注目を集めている。

**【0 0 0 3】**

この窒化物系 III-V族化合物半導体により発光ダイオード(LED)や半導体レーザーを製造する場合には、GaN、AlGaN、GaInNなどを多層に積層し、発光層(活性層)を n 型クラッド層および p 型クラッド層によりはさんだ構造を形成する必要が 50

ある。このような発光ダイオードまたは半導体レーザーとして、発光層を GaInN / GaN 量子井戸構造または GaInN / AlGaN 量子井戸構造としたものがある。

#### 【0004】

この GaInN / GaN 量子井戸構造または GaInN / AlGaN 量子井戸構造を形成する場合には、良好な結晶性を得るために、障壁層である GaN 層または AlGaN 層は 1000 度の高温で成長させ、井戸層である GaInN 層は 700 から 800 度の低温で成長させる必要がある。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0005】

しかしながら、井戸層である GaInN 層を 700 から 800 度以下の低温で成長させた後、成長温度を 1000 度に上昇させて障壁層である GaN 層または AlGaN 層を成長させると、下地の GaInN 層が劣化し、発光強度が低下してしまうという問題が生ずる。これは、窒化ガリウム系化合物半導体では一般的に混晶の組成に応じて成長温度が異なっており、通常組成 10 ~ 20 % の InGaN は 700 から 800 度で成長されるが、GaN の最適な成長温度は 1000 度以上である。このため、例えば InGaN 層の後に GaN 層を成長する場合には、GaN の最適な成長温度を適用すると InGaN 層は成長温度よりも高い温度にさらされることになり、活性層の結晶性が低下する。この要因としては InGaN 層中で In - N のボンドが切断されることによる窒素空孔の発生と In 金属化などが挙げられる。また低温で積層した層に p-n 接合など有する場合には n 型もしくは p 型不純物原子の拡散などにより特性が著しく悪化する。以上は、GaInN 層の劣化についてであるが、同様な劣化は、In を含む窒化物系 III - V 族化合物半導体層全般に起こり得るものである。

#### 【0006】

従って、InGaN 層を活性層として n 型 GaN 層上に、活性層、p 型 GaN 層を積層して作製される半導体発光デバイス (LED、LD) の場合には、InGaN 層からなる活性層形成後に p 型 GaN 層もしくは AlGaN 層を成長するため活性層の劣化が発生する。特に活性層と p 型 GaN 層の成長温度差が大きくなる長波長発光 (可視光) デバイスの作製には性能劣化が顕著に現れる。

#### 【0007】

このような活性層より上層の成長層の成長温度に起因する問題を解決するための 1 つの技術として、膜厚が 10 から 40 nm 程度の GaN キャップ層を低温で形成する方法が知られており、このような技術は特開平 10 - 32349 号公報に記載されている。ところが、GaN キャップ層だけを低温とした場合でも、その後に成長する層の成長温度が高い場合、同様な InGaN 層からなる活性層の劣化という問題は再度生ずることになり、さらに有効な解決策が模索されているのが現状である。

#### 【0008】

さらに、活性層保護を目的として活性層形成後の膜の成長温度を下げた場合、一般に窒化ガリウム系化合物半導体は最適な成長温度よりも低い温度では成長ピットを生じやすく、例えば、基本的に n 型 GaN、InGaN 活性層、p 型 GaN をこの順で積層した半導体発光デバイスでは p 型 GaN 層を 950 度で成長すると成長ピットを生じやすく、リーク電流の増加につながる。これに対して p 型 GaN 層を 1000 度以上で成長すると成長ピットのない平坦な膜となるが、上記の理由で活性層の劣化につながることになる。

#### 【0009】

本発明は上述の技術的な課題に鑑み、活性層とその後に積層する窒化物半導体層の成長温度に起因する従来の問題を解決し、発光特性などの素子特性の優れた窒化物半導体素子を得ることができる窒化物半導体素子の製造方法及び窒化物半導体素子を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0010】

10

20

30

40

50

本発明による窒化物半導体素子の製造方法は、基体上に気相成長した活性層がInを含む混晶であり、前記活性層のIn組成率がX(%)とされ、その気相成長後に積層される全ての窒化物半導体層の成長温度T( )が(1080-4.27X)以下の温度とされることを特徴とし、より好ましくは(980-4.27X)以下の温度とされることを特徴とする。

#### 【0011】

本発明製造方法によれば、活性層の成長後に積層される全ての窒化物半導体層の成長温度T( )は、活性層がInを含む混晶であってIn組成率がX(%)とされる場合に、そのIn組成率の一次関数を上限とするような挙動を示すことが実験データより得られている。すなわち、その実験データに基づき算出したところ、そのような1次関数は(1080-4.27X)で示されることが示されており、活性層の成長後に積層される全ての窒化物半導体層の成長温度T( )を(1080-4.27X)以下、より好ましくは(980-4.27X)以下とすることで、活性層の劣化を効果的に抑制することが可能である。

#### 【0012】

また、本発明の窒化物半導体素子は、第1の窒化物半導体層と、該第1の窒化物半導体層上に積層される活性層と、前記第1の窒化物半導体層と反対導電型とされ前記活性層上に積層される第2の窒化物半導体層とを有し、前記第2の窒化物半導体層の成長温度が900以下とされ、且つ前記第2の窒化物半導体層は平坦化面を呈する膜厚を有することを特徴とする。

#### 【0013】

この窒化物半導体素子によれば、活性層形成後に形成される第2の窒化物半導体層の成長において、900以下で成長する層を挿入することで平坦な膜を成長する。この第2の窒化物半導体層の平坦化面を呈する膜厚は、一例として50nm以上であり、望ましくは100nm以上である。窒化物半導体層を窒化ガリウム層とする場合、一般に950程度で成長される窒化ガリウム層は成長ピットを生じやすいが、逆にさらに低い900以下の低温で成長させた場合では、II族原子の表面拡散長の短くなるため成長ピットの少ない平坦な膜となる。このためデバイスを作製した場合にリーク電流などの低減を実現できる。

#### 【発明を実施するための最良の形態】

#### 【0014】

本発明の好適な実施形態について図面を参照しながら説明する。

本発明の第1の実施形態の窒化物半導体素子の製造方法は、基体上に活性層を第1の成長温度で気相成長し、その気相成長後に積層される全ての窒化物半導体層の成長温度を前記第1の成長温度から250高い温度以下、すなわち、本実施形態では、活性層の成長温度を基準として、それ以降に積層される全部の層の成長温度を活性層の成長温度から250高温を上限とし、より好ましくは150高い温度以下とする。

#### 【0015】

この方法によれば、活性層形成後に積層される全ての層の成長温度が活性層を形成するための第1の成長温度から250高い温度以下、より好ましくは150高い温度以下とされ、活性層中での例えばIn-Nのボンドが切断されることによる窒素空孔の発生やIn金属化などが未然に防止されて、活性層の結晶性を良好に維持することが可能となる。

例えば活性層を650で成長した場合には900より高い温度には上げずに、各層を形成する。その上限よりも成長温度が高い場合には活性層が熱的に安定ではないため、活性層に劣化が生ずる。

#### 【0016】

また、基体上に活性層を気相成長し、その気相成長後に積層される全ての窒化物半導体層の成長温度T( )は、活性層の発光波長を(nm)とした場合に(1350-0.75)以下の温度であることを特徴とし、より好ましくは(1250-0.75)以

10

20

30

40

50

下の温度とされる。

#### 【0017】

この方法によれば、活性層の成長後に積層される全ての窒化物半導体層の成長温度T( )は、活性層の発光波長を (nm)とした場合にその発光波長の一次関数を上限とするような挙動を示すことが、実験データより得られており、その実験データに基づく1次関数は (1350 - 0.75) である。従って、活性層の成長後に積層される全ての窒化物半導体層の成長温度T( )を (1350 - 0.75) 以下とすることで、より好ましくは (1250 - 0.75) 以下の温度とすることで活性層の劣化を効果的に抑制することが可能である。

#### 【0018】

活性層はInを含む混晶とすることができる、代表的な材料はInGaN層である。Inを含むInGaNなどの混晶では長波長ほどInの組成が高く（また、低温で成長され）、In-NのボンドはGa-Nのボンドと比較して熱的に不安定なため、その後の成長温度を低くすることが好ましい。InGaN層で活性層を構成した場合の窒化物半導体素子の発光波長域は、370nm以上640nm以下とされる。ここで、窒化物半導体素子は主に発光ダイオード若しくは半導体レーザーなどの発光素子を含むものである。

#### 【0019】

##### [第1の実施形態]

次に、図1乃至図3を参照しながら、本実施形態の窒化物半導体素子の製造方法について説明する。

#### 【0020】

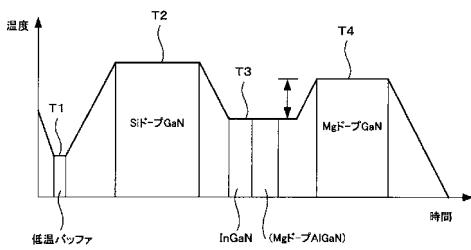

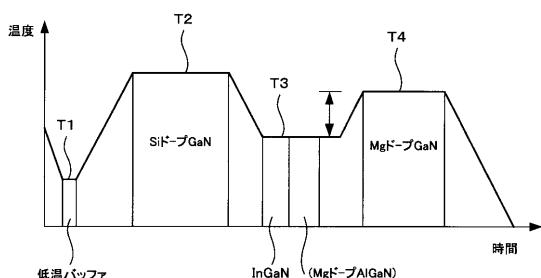

図1は本製造方法における成長温度の変化を示す図であり、低温バッファ層の形成時に成長温度T1（例えば約500）であったものが、シリコンドープのn型GaN層を形成する際に成長温度T2（例えば約1020）に昇温される。次いで、トリメチルガリウムの供給をいったん停止し、引き続き成長温度をT3（例えば約730）まで降温しながらキャリアガスをすべて窒素ガスに切り替えて、Ga原料としてトリメチルガリウム、In原料としてトリメチルインジウムを供給して30のInGaNからなる活性層を形成する。

#### 【0021】

このInGaNからなる活性層の形成後、成長温度T3で連続してマグネシウムドープのAlGaNを形成し、その後、成長温度T4（例えば900）まで昇温しマグネシウムドープのp型GaNを形成している。

#### 【0022】

この成長温度の変化のグラフからも明らかなように、活性層であるInGaNの成長温度T3とその後に形成されるマグネシウムドープのp型GaNの成長温度T4の差（T4-T3）は、250を下回る170に過ぎず、従来のGaNの最適温度とされる1020ではマグネシウムドープのp型GaNは形成されていない。また、マグネシウムドープのp型GaNは活性層の形成後に成長される層の中で最も高温で成長される層であり、その他の活性層以後の各層はマグネシウムドープのp型GaNの成長温度T4よりは低い温度で形成されている。このため活性層以後の全部の層は活性層の成長温度から250

高温を上限とする範囲内に収まっており、活性層中での例えばIn-Nのボンドが切断されることによる窒素空孔の発生やIn金属化などが未然に防止されて、活性層の結晶性を良好に維持することが可能となり、発光効率を改善することができる。

#### 【0023】

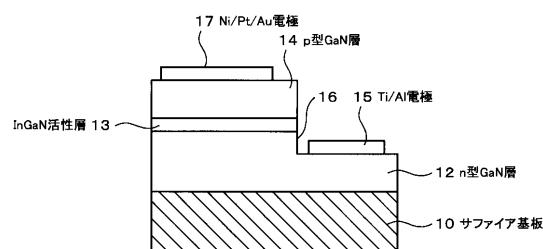

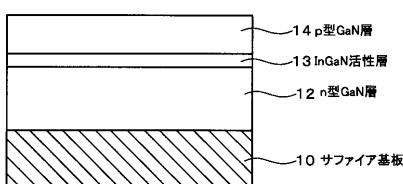

このような本実施形態の製造方法について、さらに図2、図3を参照しながらデバイス構造を用いて説明する。

先ず、図示しない有機金属気相成長装置内に2インチのサファイア基板10を設置し、反応炉内にキャリアガスとして例えばH<sub>2</sub>とN<sub>2</sub>との混合ガスを流し、例えば1050で20分間熱処理を行うことによりそのサファイア基板10の表面をサーマルクリーニングする。次いで、基板温度を例えば510（T1）に下げた後、反応炉内にN原料とし

てのアンモニア ( $\text{NH}_3$ ) および Ga 原料としてのトリメチルガリウム (TMGa、Ga ( $\text{CH}_3$ )<sub>3</sub>) を供給し、正面を c 面とするサファイア基板 10 上に GaN バッファ層を成長させる。このような GaN バッファ層を形成した後、1020 (T2) でシリコン (Si) ドープの n 型 GaN 層 12 を 3  $\mu\text{m}$  成長させる。シリコンの原料はシランガスである。

#### 【0024】

トリメチルガリウムの供給をいったん停止し、引き続き成長温度を 730 (T3) まで降温しながらキャリアガスをすべて窒素ガスに切り替えて、Ga 原料としてトリメチルガリウム、In 原料としてトリメチルインジウムを供給して 30 の InGaN からなる InGaN 活性層 13 を n 型 GaN 層 12 上に積層する。

10

#### 【0025】

成長温度を 730 (T3) として InGaN 活性層 13 を形成した後、図 1 のようにマグネシウムドープの AlGaN 層形成することもできるが、AlGaN 層を形成しなくとも良い。その後、Ga 原料としてトリメチルガリウムと Mg 原料としてメチルシクロペントジエニルマグネシウムを供給しながら昇温し、900 (T4) でマグネシウムドープの p 型 GaN 層 14 を 200 nm 成長する。このマグネシウムドープの p 型 GaN 層 14 の成長温度である 900 (T4) が InGaN 活性層 13 の成長温度 730 (T3) から 250 以内の範囲であり、窒素空孔の発生や In 金属化などが未然に防止され、活性層の結晶性を良好に維持することが可能となり、発光効率を改善することができる。従来の製法では GaN の最適な成長温度である 1020 でマグネシウムドープの GaN を成長しており、活性層の成長温度よりもかなり高温であるため活性層に In 金属の析出が発生し、発光ダイオードの発光効率が悪いなどの問題が生じていたが、本実施形態によってこのような問題が解決されることになり、発光効率が向上する。

20

#### 【0026】

マグネシウムドープの p 型 GaN 層 14 の成長後、800 窒素ガス中のアニールを行い、図 3 に示すように、p 型 GaN 層 14、InGaN 活性層 13、n 型 GaN 層 12 の一部を除去して溝 16 を形成し、その溝 16 によって露出した n 型 GaN 層 12 に Ti / Al 電極 15 からなる n 側電極、p 型 GaN 層 14 に Ni / Pt / Au 電極 17 からなる p 側電極をそれぞれ形成 N して半導体発光ダイオードを完成する。

30

#### 【0027】

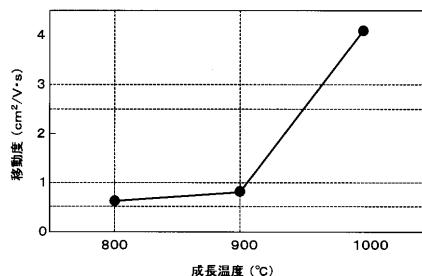

本実施形態では活性層成長温度を活性層 13 の成長温度に対して 250 以内 (900 - 730 = 170) に抑えたため、活性層 13 に In 金属の析出は見られず、発光効率が向上する。通常マグネシウムドープの GaN はキャリア濃度が同一になるような条件で成長しても、図 4 に示すように結晶性の低下による移動度 (mobility) の低下が生ずる。すなわち、成長温度が 900 以下では移動度があまり高くはならないことになり、その結果、素子の抵抗は高くなり、動作電圧は上昇することになる。しかしながら本実施形態では、注入電流に対する発光効率は結果的に上昇しており、デバイス特性が改善されることになる。

30

#### 【0028】

なお、本実施形態では、本発明を GaN 系半導体発光素子の製造に適用した場合について説明したが、この発明は GaN 系電界効果トランジスタ (FET) などの GaN 系電子走行素子の製造に適用してもよい。また、上述の各 GaN 層の代りに Al<sub>x</sub>Ga<sub>1-x</sub>N 層などを適宜用いることも可能である。

40

#### 【0029】

##### [第 2 の実施形態]

本実施形態は第 1 の実施形態とほぼ同様の構造を有する GaN 系半導体発光素子を製造する方法の例であり、製造される GaN 系半導体発光素子の発光波長と活性層形成後に積層する窒化物半導体層の成長温度の関係に基づき、前記成長温度を選択して GaN 系半導体発光素子を製造する方法を示す例である。

#### 【0030】

50

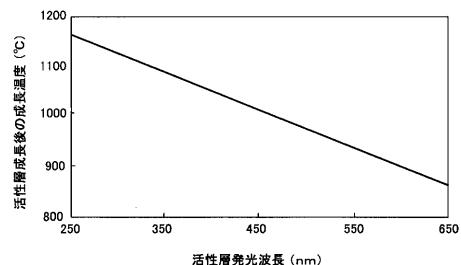

まず、本実施形態の技術的思想の根底に在るGaN系半導体発光素子の発光波長と活性層形成後に積層する窒化物半導体層の成長温度の関係について説明する。この関係は、本件発明者らが行った測定データより明らかとなった関係である。ここで測定について説明すると、前述の第1の実施形態のGaN系発光ダイオードと同様な構造あってn型GaN層、InGaN活性層、p型GaN層からなる発光ダイオード構造を活性層の成長条件を変更しながら形成し、その発光波長が異なるようにいくつかの素子を形成した。すなわち、InGaN活性層の発光波長が470nmとなるように成長した場合、その後のp型GaN層をすべて950以下で成長した場合には活性層中のIn金属の析出はなく顕著な発光効率の低下は見られなかつたが、1020まで昇温してp型GaN層を成長した場合には活性層中にIn金属の析出が発生し、注入電流に対しての発光効率は低下した。これは主に析出したIn金属を介して発光に寄与しない無効電流が発生するためと考えられる。InGaN活性層の発光波長が470nmである場合、このような効率の低下の発生する温度はほぼ1000であった。また、発光波長が525nmとなるように成長した場合には、効率の低下しないp型GaNの成長温度の上限は950であった。さらにInGaN活性層の発光波長を成長400nmとなるように成長した場合には1020で成長しても顕著な効率の低下は見られなかつた。

10

## 【0031】

以上の測定データをプロットしたグラフが図5である。図5は活性層形成後に積層するp型GaN層の成長温度の上限と活性層の発光波長の関係を示す図である。図5に示すように、活性層形成後に積層するp型GaNの成長温度の上限と活性層の発光波長の関係は線形な関係であり、活性層の気相成長後に積層される全ての窒化物半導体層の成長温度T( )は、活性層の発光波長を( nm )とした場合に( 1350 - 0.75 )以下の温度とすることで、活性層の劣化が抑制されることになる。

20

## 【0032】

この窒化物半導体層の成長温度T( )と発光波長( nm )の間の関係を基礎に発光ダイオードを作成する場合、発光波長( nm )が予め決められている場合には、その発光波長に基づき活性層の劣化が発生しないような活性層の気相成長後に積層される全ての窒化物半導体層の成長温度T( )を設定することができ、最終的に発光効率の優れた素子を製造できることになる。

30

## 【0033】

## [第3の実施形態]

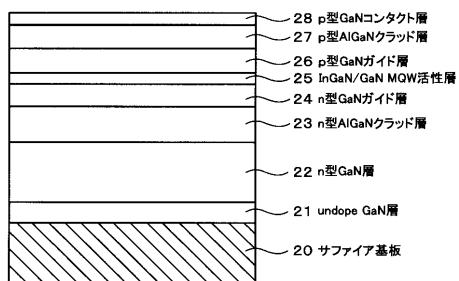

本実施形態は活性層がInの混晶からなるGaN系半導体レーザーの例であり、図6及び図7を参照しながらその製造方法について説明する。

## 【0034】

先ず、第1の実施形態と同様にして、例えば1050でC面を正面とするサファイア基板20のサーマルクリーニングを行った後、例えば510の成長温度でGaNバッファ層若しくはAlNバッファ層を成長させる。このようなGaNバッファ層を形成した後、成長温度を約1020まで上昇させた後、アンドープのGaN層21を1μm、シリコン(Si)ドープのn型GaN層22を3μm成長させる。シリコンの原料はシランガスである。

40

## 【0035】

シリコン(Si)ドープのn型GaN層22を形成した後、反応炉内にN原料としてのNH<sub>3</sub>およびGaN原料としてのトリメチルガリウム(TMGa、Ga(CH<sub>3</sub>)<sub>3</sub>)に加えてAl原料としてのトリメチルアルミニウム(TMA1、Al(CH<sub>3</sub>)<sub>3</sub>)を供給し、n型AlGaNクラッド層23を成長させる。

## 【0036】

次に、反応炉内へのトリメチルガリウム(TMGa)およびトリメチルアルミニウム(TMA1)の供給を停止し、NH<sub>3</sub>の供給はそのまま続けながら、成長温度を例えば700~850(例えば、720)に下げた後、反応炉内に再びトリメチルガリウム(TMGa)を供給してn型GaNガイド層24を成長させる。次に、成長温度をそのまま7

50

00～850に保持した状態で、反応炉内にN原料としてのNH<sub>3</sub>に加えてGa原料としてのトリメチルガリウム(TMGa)およびIn原料としてのトリメチルインジウム(TMIIn)を供給する状態と、In原料としてのトリメチルインジウム(TMIIn)の供給を止めながらGa原料としてのトリエチルガリウム(TEGa)の供給を続ける状態とを繰り返して、活性層25をInGaN(30)/GaN(50)の3周期程度の多重量子井戸(MQW)構造にする。ここで活性層25のIn組成は例えば約15%に設定される。

#### 【0037】

このような多重量子井戸(MQW)構造の活性層25を形成した後、NH<sub>3</sub>の供給はそのまま続けながら、成長温度を例えば700～850(例えば、720)に維持し、反応炉内に再びトリメチルガリウム(TMGa)を供給してマグネシウムドープのp型GaNガイド層26を成長させる。反応炉内にN原料としてのNH<sub>3</sub>およびGa原料としてのトリメチルガリウム(TMGa)に加えてAl原料としてのトリメチルアルミニウム(TMA1)を供給し、p型AlGaNクラッド層27を成長させ、さらにトリメチルアルミニウム(TMA1)の供給を停止しながらGa原料としてのトリメチルガリウム(TMGa)とN原料としてのNH<sub>3</sub>を供給してp型GaNコンタクト層28を形成する。

#### 【0038】

ここで、活性層25以降の成長層であるp型GaNガイド層26、p型AlGaNクラッド層27、及びp型GaNコンタクト層28はそれぞれの成長温度T( )は(1080-4.27X)以下の温度に制御されている。すなわち、前述のように活性層25のIn組成率が15(%)であることから、上記関係式に基づいて約1016よりも低い温度に制御される。より詳しくは、p型GaNガイド層26、p型AlGaNクラッド層27は約720程度とされ、さらにp型GaNコンタクト層28は約900に制御され、それぞれ上限値である約1016(=1080-4.27X)よりも低い成長温度であるために、これらp型半導体層は活性層中の例えばIn-Nのボンドが切断されることによる窒素空孔の発生やIn金属化などが未然に防止されて、活性層の結晶性を良好に維持することが可能となり、発光効率を改善することができる。

#### 【0039】

この成長温度T( )の上限は、Inの組成比Xについて(1080-4.27X)となる関係で示されるが、Inの組成比Xが高いほうがより低温で成長する必要性が高く、経験値としてこのようなInの組成比Xについて(1080-4.27X)となる関係が得られている。

#### 【0040】

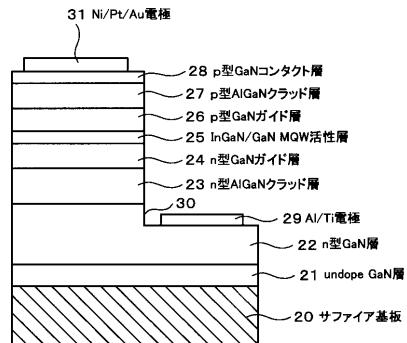

p型GaNガイド層26、p型AlGaNクラッド層27、及びp型GaNコンタクト層28の各p型窒化物半導体層を形成した後、図7に示すように、溝30を形成してn型窒化物半導体層であるn型GaN層22の面を露出し、その現れたn型GaN層22の面上にn側電極としてAl/Ti電極29が形成され、最上層のp型GaNコンタクト層28上にはNi/Pt/Au電極31が形成される。

#### 【0041】

このような構造を有する本実施形態にかかるGaN系半導体レーザーは、多重量子井戸(MQW)構造を有する活性層25よりも後のp型GaNガイド層26、p型AlGaNクラッド層27、及びp型GaNコンタクト層28はそれぞれ成長温度がInの組成比Xに基づく上限以下であるため、活性層の劣化が未然に防止されることになり発光効率を高めることができる。

#### 【0042】

#### [第4の実施形態]

本実施形態は、第1の実施形態と同様な層構造を有するが、活性層の後で成長される窒化物半導体層の成長温度を900以下としその窒化物半導体層は平坦化面を呈する厚みを有することを特徴とする。

#### 【0043】

10

20

30

40

50

先ず、第1の実施形態と同様に、図示しない有機金属気相成長装置内にサファイア基板を設置し、反応炉内にキャリアガスとして例えばH<sub>2</sub>とN<sub>2</sub>との混合ガスを流し、例えば1050で20分間熱処理を行うことによりそのサファイア基板の表面をサーマルクリーニングする。次いで、基板温度を例えば510に下げた後、反応炉内にN原料としてのアンモニア(NH<sub>3</sub>)およびGa原料としてのトリメチルガリウム(TMGa、Ga(CH<sub>3</sub>)<sub>3</sub>)を供給し、サファイア基板上にGaNバッファ層を成長させる。このようなGaNバッファ層を形成した後、1020でアンドープのGaN層を1μm、シリコン(Si)ドープのn型GaN層を3μm成長させる。シリコンの原料はシランガスである。

## 【0044】

次にトリメチルガリウムの供給を一旦停止し、引き続き成長温度を730まで降温しながらキャリアガスをすべて窒素ガスに切り替えて、Ga原料としてトリメチルガリウム、In原料としてトリメチルインジウムを供給して30のInGaNからなるInGaN活性層をn型GaN層上に積層する。

## 【0045】

このようなInGaN活性層を形成した後、Ga原料としてトリメチルガリウムとMg原料としてメチルシクロペニタジエニルマグネシウムを供給しながら昇温し、約800でマグネシウムドープのp型GaN層を200nm成長する。この成長温度約800は、従来の製造方法と比較すると十分に低い温度であり、この成長温度ではGa原子の表面拡散長が短いためGaN層は一様に堆積し、平坦面を呈する膜として観察される。低温の成長であるため、このp型GaN層はキャリア濃度が10<sup>18</sup>cm<sup>-3</sup>程度になるよう成長しても950で成長したものと比較して移動度が低く(図4)、動作電圧は若干向上しているが、電流注入の均一性もよくリーク電流も減少している。結果として、注入電流に対する発光効率は向上することになる。なお活性層の発光波長は470nmとされる。

## 【0046】

一方、成長温度約800と言うようかなりの低温ではなく、p型GaN層をすべて950で成長した場合では、活性層のIn析出はみられなかったものの、GaNの最適な成長温度である1000以上よりも低いため、表面は6つのS面から構成される逆六角錐形状の成長ピットで覆われる現象が生じ、なかにはp型GaN層の膜厚とほぼ等しい200nm程度の深さを有するピットもInGaN活性層から発生して、作製されたデバイスではこのピット部に電流が集中し、電流注入の均一性は悪く、またリーク電流に発生することが確認されている。

## 【0047】

従って、成長温度約800としながら表面にピットなどの生じない平坦面を呈する厚みで窒化物半導体層を形成することで、素子特性の優れた半導体発光素子を製造できることになる。すなわち、活性層以降に成長ピットの生じ難い低温成長層を一層でも挿入することで成長ピットによるリーク電流の発生を抑制することができ、例えばGaNの場合、1000以上では成長ピットの少ない平坦ステップフロー成長を示すが、それより低い温度では6つのS面からなる逆六角錐形状の成長ピットが多くなる。しかし、さらに成長温度を上げるとIII族原子の表面拡散長が短くなるため逆に成長ピットは低減される。この低温の成長温度では点欠陥などの点で結晶性は悪化し例えれば抵抗成分は増大することもあるが、平坦化面が形成されているためデバイス作成時のリーク電流を効果的に抑制することができるうことになる。

## 【0048】

## [第5の実施形態]

本実施形態の窒化物半導体素子は、低温で成長され且つ平坦面を呈する半導体層が活性層の後の層の一部に形成される例である。

## 【0049】

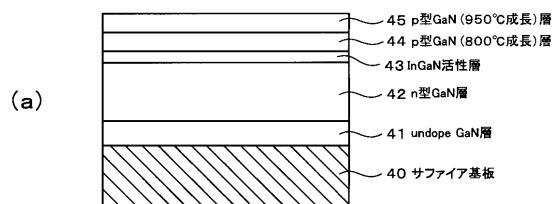

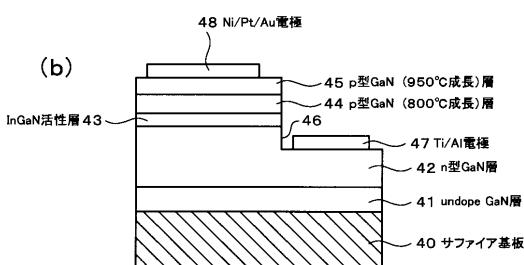

図8の(a)に示すように、第1の実施形態と同様に、図示しない有機金属気相成長裝

置内にサファイア基板40を設置し、例えば1050で20分間熱処理を行うことによりそのサファイア基板40の表面をサーマルクリーニングし、基板温度を例えば510に下げた後、反応炉内にN原料としてのアンモニア( $\text{NH}_3$ )およびGa原料としてのトリメチルガリウム(TMGa、 $\text{Ga}(\text{CH}_3)_3$ )を供給して、サファイア基板上にGaNバッファ層を成長させる。

#### 【0050】

このようなGaNバッファ層を形成した後、1020でアンドープのGaN層41を $1\text{ }\mu\text{m}$ 、シリコン(Si)ドープのn型GaN層42を $3\text{ }\mu\text{m}$ 成長させる。シリコンの原料はシランガスである。次にトリメチルガリウムの供給を一旦停止し、引き続き成長温度を730まで降温しながらキャリアガスをすべて窒素ガスに切り替えて、Ga原料としてトリメチルガリウム、In原料としてトリメチルインジウムを供給して30のInGaNからなるInGaN活性層43をn型GaN層42上に積層する。

10

#### 【0051】

このようなInGaN活性層43を形成した後、Ga原料としてトリメチルガリウムとMg原料としてメチルシクロペントジエニルマグネシウムを供給しながら昇温し、約800でマグネシウムドープのp型GaN層44を $100\text{ nm}$ 成長させ、次いで、約950でマグネシウムドープのp型GaN層45をさらに $100\text{ nm}$ 成長させる。

#### 【0052】

成長温度約800では、第4の実施形態と同様に、Ga原子の表面拡散長が短いためGaN層は一様に堆積し、平坦面を呈する膜が形成される。このp型GaN層44はキャリア濃度が $10^{18}\text{ cm}^{-3}$ 程度になるように成長され電流注入の均一性もよくリーク電流も減少する。このp型GaN層44の上に形成される成長温度約950のp型GaN層45では、ピットが発生するものの、各ピットは950で成長したGaN層45の膜厚 $100\text{ nm}$ 程度の深さしかなく、全て800で成長した場合(第4の実施形態)と比較しても顕著な発光効率の低下とはならない。本件発明者らが行った実験データによても、全て800で成長した場合(第4の実施形態)と比較しても顕著な発光効率の低下とはならないことが確かめられており、このように電極と接する層を高温とすることで電極との接触抵抗を減少でき、動作電圧はp型GaNをすべて800で成長した場合よりも低減できることが確認されている。

20

#### 【0053】

このような約950でマグネシウムドープのp型GaN層45をさらに $100\text{ nm}$ 成長させた後、図8の(b)に示すように、溝46を形成してn型窒化物半導体層であるn型GaN層42の面を露出し、その現れたn型GaN層42の面にn側電極としてAl/Ti電極47が形成され、最上層のp型GaN層45上にはNi/Pt/Au電極48が形成されて、半導体発光ダイオードが完成する。

30

#### 【0054】

本実施形態の窒化物半導体素子では、活性層形成後の窒化物半導体層を低温成長ながら平坦化面を呈する膜とそれよりは成長温度の高い膜との組み合わせでとなる構造しており、ピットの発生を防止して電流の集中やリーク電流の発生を防止しながら、且つ電極との接触抵抗を減少できることになる。

40

#### 【0055】

#### [第6の実施形態]

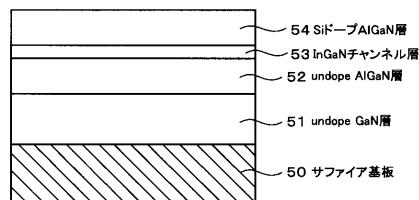

本実施形態は、活性層が電界効果型トランジスタのチャンネル層に適用される電界効果型トランジスタの例である。

#### 【0056】

その構造は、図9に示すように、第1の実施形態と同様に、図示しない有機金属気相成長装置内にサファイア基板50を設置し、例えば1050で20分間熱処理を行うことによりそのサファイア基板50の表面をサーマルクリーニングし、基板温度を例えば510に下げた後、反応炉内にN原料としてのアンモニア( $\text{NH}_3$ )およびGa原料としてのトリメチルガリウム(TMGa、 $\text{Ga}(\text{CH}_3)_3$ )を供給して、サファイア基板上に

50

GaNバッファ層を成長させる。

【0057】

このようなGaNバッファ層を形成した後、1020でアンドープのGaN層51を2μm形成し、さらにガスをトリメチルアルミニウムを含むように切り換えてアンドープのAlGaN層52を2μm形成する。

【0058】

次にトリメチルガリウムの供給を一旦停止し、引き続き成長温度を800まで降温しながらキャリアガスをすべて窒素ガスに切り替えて、Ga原料としてトリメチルガリウム、In原料としてトリメチルインジウムを供給して30のInGaNからなるInGaNチャンネル層53をアンドープのAlGaN層52上に積層する。このときのInの組成率は例えば10%とされる。10

【0059】

このようなInGaNチャンネル層53を形成した後、Ga原料としてトリメチルガリウム、Al原料としてトリメチルアルミニウム、更にSi原料としてシランを供給しながら昇温し、約1040以下でシリコンドープのAlGaN層54を成長させて、素子を形成する。

【0060】

この電界効果型トランジスタは、InGaNチャンネル層53部分が電界効果型トランジスタ(FET)のチャンネル層として機能し、この部分にゲート電極を絶縁膜を介して形成し、所要のゲート電圧を印加することでInGaN活性層53部分を走行する電子(キャリア)を制御し、それによってトランジスタの増幅機能を発揮することが可能である。特に、InGaNチャンネル層53を形成した後のシリコンドープAlGaN層54の成長温度は、約1040以下であり、チャンネル層53の成長温度に対して250以内(1040 - 800 = 240)に抑えられているため、チャンネル層として機能するInGaNチャンネル層53にIn金属の析出などは見られず、デバイス特性が改善されることになる。20

【0061】

上述したように、本発明の窒化物半導体素子の製造方法及び窒化物半導体素子によれば、活性層の成長温度や発光波長に対して、その後に積層する層の成長温度を低減することで活性層の劣化の少ないデバイスが実現できる。特に低い成長温度を必要とする長波長(例えば450nm以下)で発光するデバイスの場合は活性層におけるIn金属の析出などを抑制することができ、発光効率の改善などの性能の向上を実現できる。30

【0062】

また、本発明の窒化物半導体素子によれば、特に活性層形成後に900以下で成長する平坦化面を呈する層を挿入することで、単に成長温度を下げただけでは発生しやすい成長ピットの影響を低減でき、注入電流の均一性の向上やリーク電流の抑制を実現できることになる。

【図面の簡単な説明】

【0063】

【図1】本発明の第1の実施形態の窒化物半導体素子の製造方法における窒化物半導体層の成長温度の時間変化を示すグラフである。40

【図2】本発明の第1の実施形態の窒化物半導体素子の製造方法における工程断面図であって、p型GaN層の形成までの工程断面図である。

【図3】本発明の第1の実施形態の窒化物半導体素子の製造方法における工程断面図であって、電極層の形成までの工程断面図である。

【図4】GaN系半導体素子の窒化物半導体層の成長温度と移動度の関係を示すグラフである。

【図5】GaN系半導体素子の活性層の発光波長と活性層成長後の成長温度の関係を示すグラフである。

【図6】本発明の第3の実施形態の窒化物半導体素子の製造方法における工程断面図であ50

って、p型GaNコンタクト層の形成までの工程断面図である。

【図7】本発明の第3の実施形態の窒化物半導体素子の製造方法における工程断面図であって、電極層の形成までの工程断面図である。

【図8】本発明の第5の実施形態の窒化物半導体素子を製造した場合における工程断面図であって、(a)はp型GaN層の形成までの工程断面図であり、(b)は電極層の形成までの工程断面図である。

【図9】本発明の第6の実施形態の窒化物半導体素子の断面図である。

#### 【符号の説明】

##### 【0064】

- 10, 20, 40, 50 サファイア基板

- 21, 41, 51 アンドープのGaN層

- 12, 22, 42 n型GaN層

- 13, 43 InGaN活性層

- 14, 44, 45 p型GaN層

- 23 n型AlGaNクラッド層

- 24 n型GaNガイド層

- 25 InGaN/GaN活性層

- 26 p型GaNガイド層

- 27 p型AlGaNクラッド層

- 28 p型GaNコンタクト層

- 52 アンドープのAlGaN層

- 53 InGaNチャンネル層

- 54シリコンドープのAlGaN層

10

20

20

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 土居 正人

東京都品川区北品川 6 丁目 7 番 35 号 ソニー株式会社内

(72)発明者 大畠 豊治

東京都品川区北品川 6 丁目 7 番 35 号 ソニー株式会社内

F ターム(参考) 5F041 AA44 CA04 CA05 CA34 CA40 CA46 CA65

5F173 AH22 AH44 AP06 AQ12 AR82 AR96