(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-5569

(P2004-5569A)

(43) 公開日 平成16年1月8日(2004.1.8)

(51) Int.C1.<sup>7</sup>

G06F 15/80

G06T 15/00

F 1

G06F 15/80

G06T 15/00 100A

テーマコード(参考)

5B080

審査請求 未請求 請求項の数 10 O L (全 31 頁)

|              |                              |          |                                                                                                                  |

|--------------|------------------------------|----------|------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2003-104747 (P2003-104747) | (71) 出願人 | 398038580<br>ヒューレット・パッカード・カンパニー<br>HEWLETT-PACKARD COMPANY<br>アメリカ合衆国カリフォルニア州パロアルト ハノーバー・ストリート 3000<br>110000039 |

| (22) 出願日     | 平成15年4月9日 (2003.4.9)         | (72) 発明者 | 特許業務法人アイ・ピー・エス<br>ダニエル・エヌ・エモット<br>アメリカ合衆国コロラド州フォート・コリーンズ・エヌ・カントリー・ロード 11・5<br>524                                |

| (31) 優先権主張番号 | 10/147763                    | (74) 代理人 | F ターム(参考) 5B080 AA14 AA15 BA03 CA01 CA03<br>CA04 FA02 FA03 FA17 GA02<br>GA11 GA22                                |

| (32) 優先日     | 平成14年5月16日 (2002.5.16)       |          |                                                                                                                  |

| (33) 優先権主張国  | 米国(US)                       |          |                                                                                                                  |

(54) 【発明の名称】データおよび命令の流れを少なくとも1つの機能ユニットに配向 (direct) するシステムおよび方法

## (57) 【要約】

【課題】データおよび命令の流れを少なくとも1つの機能ユニットに配向する。

【解決手段】複数のノードを定義するシステムにおいて、各ノードの一部を形成するキューネットワークマネージャ(QNM)を提供する。QNMは、複数のノードの間での相互通信をサポートする、ネットワークへのインターフェースと、ノード内の機能ユニットにメッセージを渡すように構成されるインターフェースと、メッセージおよびプログラム可能命令のうちの少なくとも一方を格納するように構成されるランダムアクセスメモリ(RAM)と、プログラム可能命令の内容に基づいて、機能ユニットの動作態様を制御するように構成されるロジックとを備える。

【選択図】

図5

**【特許請求の範囲】****【請求項 1】**

複数のノード(402、404、406、408)を規定する構成要素のシステムにおいて、各ノード(402、404、406、408)の一部を形成する待ち行列ネットワークマネージャ(QNM)(582)であって、

前記複数のノード(402、404、406、408)間の相互通信をサポートする、ネットワークへのインターフェース(504)と、

前記ノード内の機能ユニット(522、524)にメッセージを渡すように構成されるインターフェース(508)と、

メッセージ(512)およびプログラム可能命令(514)のうちの少なくとも一方を格納するように構成されるランダムアクセスメモリ(RAM)(510)と、

前記プログラム可能命令(514)の内容に基づいて、機能ユニットの動作態様を制御するように構成されるロジック(540)と

を備えるQNM。

**【請求項 2】**

前記機能ユニット(522、524)の動作態様を制御するように構成されるロジックは、前記RAM(510)に格納された前記プログラム可能命令(514)を評価するよう

に構成される実行ユニット(540)を該QNM(582)内に備える

請求項1記載のQNM。

**【請求項 3】**

少なくとも1つの実行ユニット(540、542)をさらに備え、該実行ユニット(540、542)はそれぞれ、機能動作を行うように構成される

請求項1記載のQNM。

**【請求項 4】**

前記プログラム可能命令(514)は、少なくとも1つの実行ユニット(540、542)の動作を制御するように動作可能である

請求項3記載のQNM。

**【請求項 5】**

リモートノード(402、404、406)からプログラム可能命令(514)を受け取り、該プログラム可能命令(514)を前記RAMに格納するロジック(530)をさらに備える

請求項1記載のQNM。

**【請求項 6】**

前記機能ユニットは、メッセージ生成機能ユニット(524)である

請求項1記載のQNM。

**【請求項 7】**

前記機能ユニットは、メッセージ消費側機能ユニット(522)である

請求項1記載のQNM。

**【請求項 8】**

前記システムは、コンピュータグラフィックスシステムである

請求項1記載のQNM。

**【請求項 9】**

前記少なくとも1つのメッセージ(512)は、前記少なくとも1つの機能ユニット(522、524)に対する命令を含む

請求項1記載のシステム。

**【請求項 10】**

複数のノード(402、404、406、408)を規定する構成要素のシステムにおいて、データおよび命令の流れを少なくとも1つの機能ユニット(522、524)に配向する方法であって、

第1のインターフェースを通してリモートノード(402、404、406)からプログラ

10

20

30

40

50

ム可能命令を受け取ること(612)と、

前記プログラム可能命令(514)をランダムアクセスメモリ(RAM)(510)に格納すること(614)と、

前記プログラム可能命令(514)の内容を用いることであって、実行ユニット(540)、542)の動作を構成すること(616)と

を含む方法。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、コンピュータグラフィックスシステムに関し、特に、データおよび命令の流れ

を少なくとも1つの機能ユニットに配向する新規のシステムおよび方法に関する。 10

##### 【0002】

##### 【従来の技術】

コンピュータグラフィックスシステムは一般に、二次元映像表示画面にオブジェクトの図形表示を表示するために使用される。

現在のコンピュータグラフィックス表示システムは、高精細表現を提供し、様々な用途に

使用されている。

コンピュータグラフィックス表示システムは一般に、中央演算処理装置(CPU)、シス

テムメモリ、グラフィックスマシン、および映像表示画面を備える。

##### 【0003】

通常のコンピュータグラフィックス表示システムでは、表示画面に示されるオブジェクト

がグラフィックスプリミティブに分解される。

プリミティブは、グラフィックス表示の基本成分であって、点、線、ベクトル、およびポ

リゴン(たとえば、三角形および四角形)を含むことができる。

通常は、ハードウェア/ソフトウェア手法が実行されて、表示画面に表示される1つまたは複数のオブジェクトのビューを表すグラフィックスプリミティブをレンダリング、すな

わち描画する。

##### 【0004】

通常、レンダリングされる三次元オブジェクトのプリミティブは、プリミティブデータに

関してホストCPUによって定義される。 30

たとえば、プリミティブが三角形の場合、ホストコンピュータはその頂点のX、Y、およ

びZ座標でプリミティブを定義できる。

特定の用途では、付加的なプリミティブデータを使用することができる。

レンダリングハードウェアは、各々のプリミティブを表示する表示画面ピクセルを計算す

るためにプリミティブデータを補間する。

##### 【0005】

グラフィックスマシンは、ジオメトリアクセラレータ、ラスタライザ、フレームバッファ

コントローラ、およびフレームバッファを一般に備える。

グラフィックスマシンは、テキスチャマッピングハードウェアを備える場合もある。

ジオメトリアクセラレータは、表示されるビューを構成するプリミティブを定義する頂点

データをホストCPUから受け取る。 40

知られているように、ジオメトリアクセラレータの動作は、非常に計算集約的である。

三次元(3D)グラフィックスディスプレイの1フレームは、数十万程度のプリミティブ

を含みうる。

最新技術のパフォーマンスを実現するために、ジオメトリアクセラレータは、1秒当たり

数億もの浮動小数点計算を行うように求められることがある。

さらに、ホストコンピュータとグラフィックスハードウェアとの間で転送されるデータの

量は、非常に多い。

ホストコンピュータからジオメトリアクセラレータに転送されるさらなるデータとしては

、照度パラメータ、クリッピングパラメータ、およびグラフィックス表示の生成に必要な

50

任意の他のパラメータが含まれる。

【0006】

知られているように、ラスタライザは、図またはオブジェクトを表すデータを受け取り、次いで図のピクセル様表現を提供する。

同じく知られているように、テキスチャマッピングには、テキスチャの1つまたは複数の点要素（テクセル）を、テキスチャがマッピングされているオブジェクトの表示部分の各点要素（ピクセル）に適用することが含まれる。

テキスチャマッピングハードウェアには、従来、テキスチャマップのテクセルが、オブジェクトを表す表示画面上のピクセルに対応する様様を示す情報が提供される。

テキスチャマップの各テクセルは、二次元テキスチャマップ上の位置を特定するSおよびT座標によって定義することができる。 10

各ピクセルについて、それをマッピングする、対応するテクセル（1つまたは複数）にテキスチャマップからアクセスし、これを、表示画面上のテキスチャオブジェクトを表すためにピクセルごとに生成される最終的な赤、緑、青（RGB）値に組み込む。

知られているように、二次元テキスチャマップにさらに、一次元、三次元、さらには他の次元のテキスチャマップもまた知られている。

この点に関し、二次元テキスチャマップは、例示目的だけのために示されるものである。

【0007】

オブジェクトプリミティブの各ピクセルは、オブジェクトのあらゆるビューについてテキスチャマップの単一テクセルと1対1に対応してマッピングされない場合もあることを理解されたい。 20

たとえば、オブジェクトは、表示画面上に表されるビューポートに近いほど、大きく見える。

オブジェクトが表示画面上で大きく見えるほど、テキスチャの表現はより詳細になる。

このように、オブジェクトが表示画面のかなり大きな部分を消費する場合、多数のピクセルが表示画面上のオブジェクトを表現するために使用され、そのオブジェクトを表す各ピクセルをテキスチャマップの単一ピクセルと1対1の対応でマッピングすることができるか、または単一テクセルを複数のピクセルにマッピングすることができる。

しかし、オブジェクトが表示画面上で比較的小さな部分を占める場合、そのオブジェクトを表現するにははるかに少ない数のピクセルが使用され、テキスチャがより荒く表される結果になり、各ピクセルを複数のテクセルにマッピングすることができる。 30

テキスチャがオブジェクトの小さな部分にマッピングされる場合、各ピクセルを複数のテクセルにマッピングすることが可能である。

結果得られるテクセルデータが、2つ以上のテクセルにマッピングされる各ピクセルについて計算され、通常、そのピクセルにマッピングされるテクセルの平均を表す。

【0008】

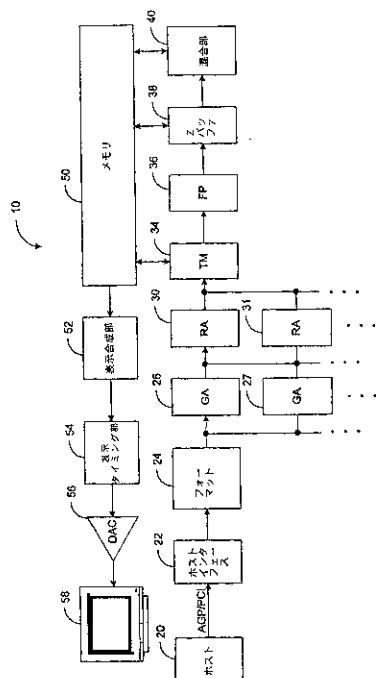

従来のグラフィックスシステムをより具体的に示すために、図1を参照する。

図1は、既知のグラフィックスパイプライン10を示す図である。

最初に、図1に示すグラフィックスパイプライン10を図示する様々な代替の様式があり、図1の図は、例示だけのために提示されることに留意されたい。 40

【0009】

図示のように、ホストコンピュータ20は通常、AGP（加速グラフィックスポート）バスまたはPCI（周辺コンポーネント相互接続）バス等の高速バスを介してグラフィックスハードウェアと通信する。

ホストインターフェース22は通常、高速バスとインターフェースするグラフィックスハードウェアのフロントエンドに設けられる。

ホストインターフェース22の下流に、フォーマットブロック24が設けられる。

1つまたは複数のジオメトリアクセラレータ26および27、ならびに1つまたは複数のラスタライザ30および31がフォーマットブロック24の下流に設けられる。

各ジオメトリアクセラレータによって生み出される、または生成される情報は、すべての 50

下流ラストライザに同報通信される。

ジオメトリアクセラレータおよびラストライザの動作、ならびにこういった複数の構成要素を操作する方法／構成は既知であるため、本明細書において述べる必要はない。

#### 【0010】

ラストライザ30および31の下流には、テキスチャマッピングハードウェア34、フラグメントプロセッサ36、Zバッファ38、および混合ハードウェア40がある。

これら構成要素それぞれの機能および動作は既知であるため、本明細書において述べる必要はない。

しかし、知られているように、テキスチャマッピングハードウェアシステムは通常、レンダリング中のオブジェクトに関連付けられたテキスチャを表すデータを格納するローカルメモリサブシステム50を含む。

#### 【0011】

テキスチャマッピングハードウェアの下流には、表示合成部52、表示タイミング部54、デジタル／アナログ変換器（D A C）56、およびディスプレイ58を含むサブシステムがある。

知られているように、表示合成ハードウェア52は、異なるオブジェクト／プリミティブ層を処理して、表示する所与のピクセルの色を決定する。

#### 【0012】

図1のもののようなグラフィックスパイプライン10の一般的なアーキテクチャおよびデータフローと一致して、多重／並列ラストライザおよび多重／並列テキスチャマッピングサブシステムを備え、各ラストライザおよびテキスチャマッピング構成要素が専用ローカルメモリと通信する従来技術によるシステムが知られている。

#### 【0013】

ラストライズ処理ハードウェアおよびテキスチャマッピングハードウェアを組み合わせた他のシステムも知られている。

かかるシステムでは、多重／並列結合ラストライザ／テキスチャマッピングサブシステムがあり得る。

かかるシステムは通常、各ラストライザ／テキスチャマッピング構成要素ごとに専用メモリを備えていた。

知られているように、かかるシステムは、ディスプレイをセグメント化し、ディスプレイの部分部分を、処理のために異なるラストライザ／テキスチャマッピング構成要素に専用としていた。

しかし、セグメントの境界に延出するプリミティブを処理するために、この種の並列性を実施するシステムはしばしば、テキスチャマップおよび他のデータを別個のメモリにまたがって複製するため、容量および帯域双方に問題が生じた。

換言すれば、先に述べたテキスチャマップは分離することができない。

むしろ、テキスチャデータは、分離されたディスプレイセグメントまたは領域それぞれに複製される。

帯域の問題は、データがメモリから検索される（すなわち、バースト読み取り）際の粒度によってさらに悪化した。

#### 【0014】

##### 【発明が解決しようとする課題】

本発明は、データおよび命令の流れを少なくとも1つの機能ユニットに配向するシステムおよび方法を広く対象とする。

#### 【0015】

##### 【課題を解決するための手段】

複数のノードを定義するシステムの構成要素の一実施形態において、各ノードの一部を形成するキューネットワークマネージャ（Q N M）を提供する。

本実施形態では、Q N Mは、複数のノードの間での相互通信をサポートする、ネットワークへのインターフェースと、ノード内の機能ユニットにメッセージを渡すように構成される

10

20

30

40

50

インターフェースと、メッセージおよびプログラム可能命令のうちの少なくとも一方を格納するように構成されるランダムアクセスメモリ( RAM )と、プログラム可能命令の内容に基づいて、機能ユニットの動作態様を制御するように構成されるロジックとを備える。

【 0 0 1 6 】

複数のノードを定義するシステムの構成要素の別の実施形態では、データおよび命令の流れを少なくとも 1 つの機能ユニットに配向する方法を提供する。

本方法は、第 1 のインターフェースを通して、リモートノードからプログラム可能命令を受け取ることと、プログラム可能命令をランダムアクセスメモリ( RAM )に格納することと、プログラム可能命令の内容を用いて、機能ユニットの動作を構成することとを含む。

【 0 0 1 7 】

本明細書に組み込まれ、本明細書の一部をなす添付図面は、本発明のいくつかの態様を示すと共に、説明と併せて、本発明の原理を説明する役割を果たすものである。

【 0 0 1 8 】

【発明の実施の形態】

本発明の特定の中心的な特徴および態様を考察する前に、まず、本発明が存在して動作する環境の説明を参照する。

この点に関して、本発明は、ノードが、通信リンクを介して相互通信する機能ユニットを含む独特なノードアーキテクチャに存在し動作する。

以下の考察から分かるように、このノードアーキテクチャの独特的な設計は、帯域集約的な動作環境において特に効率的なパフォーマンスを提供する。

さらに、本明細書に述べる実施形態では、通信リンクは直列リンクである。

しかし、本発明の範囲および精神に矛盾せずに他の( すなわち、非直列 )通信リンクも実施し得ることが分かろう。

さらにまた、本発明の特定の態様については、すぐ下に述べるシステム環境と併せて考察する。

しかし、これら本発明の特徴については、本発明が存在し動作する環境を考察した後に明確にする。

【 0 0 1 9 】

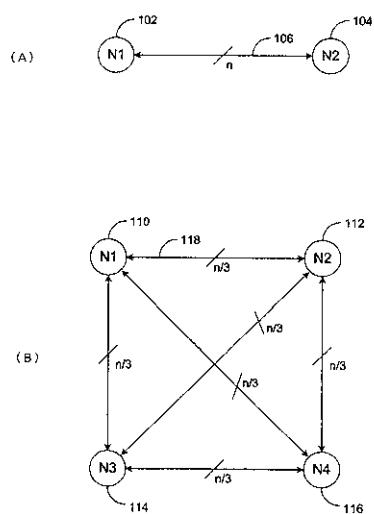

図 2 ( A ) を参照して、2 つのノード 102 および 104 を有するシステムを示す。

2 つのノード 102 および 104 は、複数の直列リンク 106 を介して相互に通信する。

直列リンクの数は、直列リンクの速度およびシステムの帯域要件に応じて、システムごとに異なり得る。

上述したように、テキスチャマッピングは、グラフィックスシステムに高いメモリ帯域要求を課す。

したがって、コンピュータグラフィックスシステムのようなシステムでは、より低い帯域のシステムよりも一般により多くの通信リンク 106 が望まれる。

【 0 0 2 0 】

図 2 ( B ) を参照して、4 つのノード 110 、 112 、 114 、および 116 を有するシステムを示す。

図 2 ( A ) の 2 ノードシステムのように、4 つのノード 110 、 112 、 114 、 116 は、複数の直列リンク( たとえば、 118 )を介して相互に通信する。

しかし、4 ノードシステムでは、任意の 2 つの所与のノードを相互接続する直列リンクの数は低減する。

この点に関し、システムがより多くの機能処理ノードに分割されるほど、ノードのそれぞれの間の相互接続に必要な直列リンクは少なくなる。

図 2 ( A ) および図 2 ( B ) に提示する抽象的な例では、図 2 ( A ) の 2 ノードシステムのシステム帯域のサポートに  $n$  個の直列リンクが必要であるならば、数学的に  $n / 3$  個の直列リンクが図 2 ( B ) の 4 ノードシステムにおけるノードのそれぞれの間の相互接続に使用される。

【 0 0 2 1 】

10

20

30

40

50

本発明を理解するために、図2(A)および図2(B)から、帯域集約的な処理システムは機能ノードに分割することが可能であるため、システム全体の機能を実行するように協働するように機能ノードが設計されることが観察される。

さらに、機能ユニットは複数の直列リンクを介して相互に通信する。

【0022】

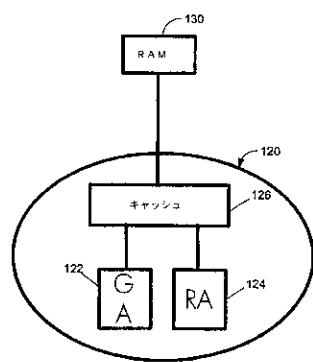

この基本的なアーキテクチャを要約したが、次に、グラフィックス処理システムの機能ユニットの1つの可能な構造を示す図面、および機能ユニットが相互に通信してデータを転送し、それぞれの動作機能を協働して実行する全体的な方法を参照する。

この点に関し、高性能グラフィックス処理システムに使用可能なノード120を示す図3を参照する。

図示のように、かかるノード120は、統合されたジオメトリアクセラレータ122、ラスタライザ124、およびキャッシュ126を備えることができる。

ジオメトリアクセラレータ122、ラスタライザ124、およびキャッシュ126の一般的な機能動作は、既知のシステムのものと同様である。

したがって、この機能動作を本明細書において説明する必要はない。

【0023】

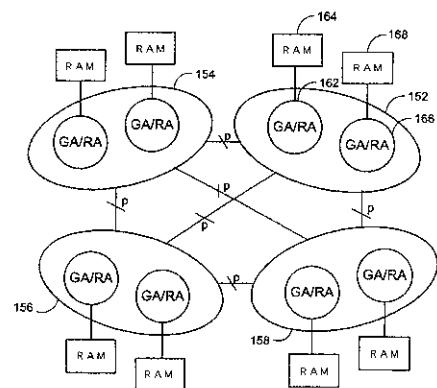

次に、所与のグラフィックス処理システム内にあることができる相互接続された複数のノードを示す図4を参照する。

図4は、ノードの作成がチップの分化に殆ど依存しないことを示す。

代わりに、チップの統合およびチップの分割は、ピンカウント、統合の経済性、スケーラビリティ(拡張性)粒度等の要因によって導かれる。

スケーラビリティ粒度に関しては、チップ当たり1つのノードがある場合、システムは一度に1つのノードでスケーリング(拡張縮小)可能なことが分かろう。

しかし、チップ当たり4つのノードがある場合、システムは、好ましくは、一度に4つのノードでスケーリング可能である。

図には、4個のチップ152、154、156、および158を示す。

各チップは2つのノードを含む。

たとえば、チップ152は、ノード162および166を含む。

ノード162はRAM164と通信し、ノード166はRAM168と通信する。

したがって、かかる実施形態は、2つのノードの増分でスケーリング可能である。

【0024】

図4はまた、チップ152とは別個のものとしてRAM要素164および168を示す。

一実施形態では、別個の専用RAMデバイスがノードごとに存在しうる。

かかる手法は、より細かい粒度を提供し、よりよい効率をもたらすとともに、内部機能設計の複雑さを低減する。

しかし、別の実施形態(図示せず)では、単一のRAMデバイスを利用することができる。

しかし、かかる実施形態の単一RAMデバイスは、個々の区分が個々のノードに割り当たられるように分割することが可能である。

個々のノードに対して、単一のメモリデバイスを割り当てるか、それとも単にメモリデバイスの区分を割り当てるかについての設計上の判断は、帯域要件等様々な設計に固有の考慮事項に基づいて行うことができる。

さらに別の実施形態では、接続ノードと同じチップにRAMを組み込んでもよい。

【0025】

図4にさらに示すように、各ノードは複数(p)の直列リンクを通して他のノードに接続される。

先に述べたように、各種ノードを相互接続する直列リンクの数は帯域要件によって導き出されるため、システムごとに異なりうる。

所与のグラフィックスシステムでは、これら機能の並列性によって得られるパフォーマンスを強化するために、いくつかのジオメトリアクセラレータ/ラスタライザ(GA/RA)

) ノードが設けられる。

ノードによっては、これら機能、またはこれら機能の少なくとも一部を他の機能とグループ化することが可能なものもある。

【0026】

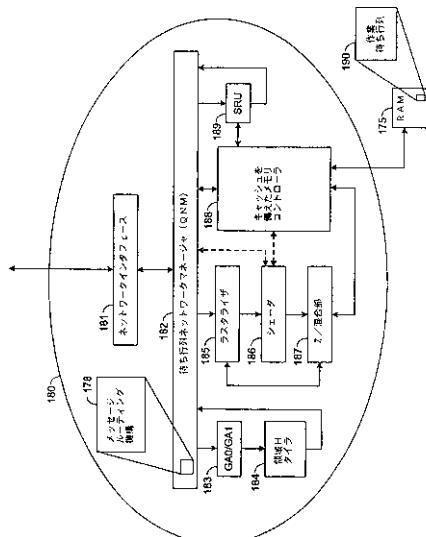

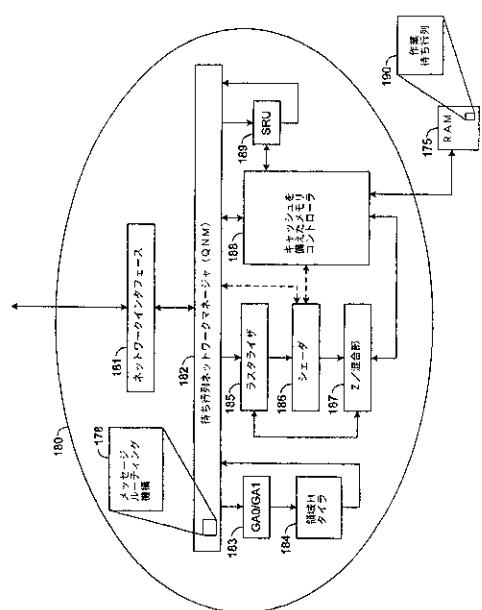

次に、好ましい実施形態のノードをより詳細に示す図5を参照する。

この図では、ノード180は特に、階層タイラ184と共にジオメトリアクセラレータ183を備えることができ、これらは共に正確な領域選択を行うために設けられる。

パラメトリック補間を有する階層ラスタライザ185、シェーダ186、およびz/z混合部187の各要素は、簡単なハードウェアが多くのパラメータを補間できるようにする。好ましくは、シェーダ186は、パラメトリックテキスチャリングをサポートし、z/z混合部187はz検定をサポートする。

【0027】

ノード180に対してローカルなRAM175を管理するために、オンボードキャッシュを有するメモリコントローラ188も設けられる。

画面リフレッシュユニット(SRU)189も図示される。

SRU189は、表示合成機能を含み、画面にRGB値を合成するように動作する。

上記要約した構成要素184、185、186、および187の一般的な機能および動作は一般に既知であり、当業者には理解されるはずである。

したがって、本明細書において説明する必要はない。

【0028】

図5は、ネットワークインターフェース181および待ち行列ネットワークマネージャ(QNM)182も示す。

QNM182は、作業待ち行列(後述)を操作するとともに、ノード180の機能ユニット(1つまたは複数)にデータおよび命令の流れを配向するようにプログラムされたプロセッサである。

後述するように、QNM182のプログラム可能性により、本発明により構築されるシステムの汎用性が増す。

【0029】

ネットワークインターフェース181は単に、ノードネットワーク内の他のノードを相互接続する複数の直列リンクにノード180をインターフェースする回路である。

QNM182は、作業待ち行列190(後述)の使用を通して、異なるノード/機能ユニットを共にインターフェースするように設計される。

この点に関して、QNM182は、並列機能ユニットに配向するために作業待ち行列190を区分化し照合する。

特定の直列リンクに到来するパケットのIDは、そのパケットを特定の論理作業待ち行列190に関連付ける。

作業待ち行列190はローカルなRAM175に格納され、QNM182は、好ましくは、マルチスレッドをサポートするように設計される。

スレッドへの資源の区分化は、特定の用途用にプログラマによって決定される。

【0030】

最後に、図5は、QNM182の一部であるルーティング(routing:経路選択)機構178を示す。

ルーティング機構178は、メッセージを各種ノードにルーティングする役割を担う。より詳細に後述するように、各メッセージは、メッセージの宛先である宛先ノードのIDを含む。

確立されたルーティング技術およびアルゴリズムをルーティング機構178内で実施して、介在するノードに到来するメッセージを向きを変え(redirection)転送することができる。

かかるルーティングアルゴリズムは既知のものであるため、本明細書では説明を省略する。

10

20

30

40

50

## 【0031】

図5の要素についての上記説明は、グラフィックス処理システムにおいて可能な1つのノード設計の高レベル例示の提供のみを意図する。

しかし、本発明は、特定のノード設計に制限されない、すなわち依存しない。

さらに、グラフィックス処理分野における当業者は、図5に関連付けて大まかに述べた要素の動作を認識し、理解するであろう。

したがって、本明細書では、さらなる説明は省略する。

## 【0032】

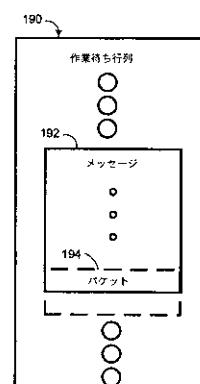

次に、図6を参照する。

図6は、各種ノードの機能動作を制御するために使用される作業待ち行列190を示すブロック図である。 10

本質的に、作業待ち行列は論理的な FIFOである。

第1のノードが第2のノードの動作を引き起こすために、第1のノードは、第2のノードに連絡され作業待ち行列190に配置されるメッセージまたはメッセージシーケンスを生成する。

第2のノードは後に、作業待ち行列内のそのメッセージを処理するときに、第1のノードによって要求、すなわち特定される動作を実行する。

この点に関し、作業待ち行列190は複数のメッセージ192を含む。

一般に、メッセージは、ノード上にある機能ユニットへのコマンドまたは命令である。

データパケット194も示される。 20

データパケットとは、メッセージを連絡するために使用される機構であり、通信リンクを介してやりとりされる最小量のデータである。

## 【0033】

待ち行列190およびメッセージがとりうる様々な形態があるが、好ましい実施形態の範囲および精神と一致して、好ましい実施形態のこれら待ち行列およびメッセージの形態を以下の表1ないし表6により完全に示す。

## 【0034】

以下の表1は、本発明の一実施形態によるメッセージのための作業待ち行列メッセージフォーマットを示す。

以下の表1および表2に示すように、メッセージは、2つの基本フォーマットのうちの1つで一般に提供することができる。 30

第1のフォーマット（ビット31を0に設定することによって定義される）では、最初にデータワードカウントおよびメッセージ内容の識別子を含む、1～128のコピーレントワードを可能にする。

第2のフォーマット（ビット31を1に設定することによって定義される）は2ワード長であり、一度に1ピクセルずつの二次元（2D）サーフェスのDirectDraw（直接描画）アクセスをサポートする。

## 【0035】

## 【表1】

| Work Queue Message |    |            |   |      |         |   |   |   |         |   |   |           |           |   |   |   |   |

|--------------------|----|------------|---|------|---------|---|---|---|---------|---|---|-----------|-----------|---|---|---|---|

| 作業待ち行列メッセージ        |    |            |   |      |         |   |   |   |         |   |   |           |           |   |   |   |   |

| M                  | S  | B          |   |      |         |   |   |   |         |   |   |           |           |   | L | S | B |

| 3                  | 3  | 2          | 2 | 2    | 2       | 2 | 2 | 2 | 2       | 2 | 2 | 1         | 1         | 1 | 1 | 1 | 0 |

| 1                  | 0  | 9          | 8 | 7    | 6       | 5 | 4 | 3 | 2       | 1 | 0 | 9         | 8         | 7 | 6 | 5 | 4 |

| 0                  | rw | Data Count |   | Type | Data[1] |   |   |   | Command |   |   |           |           |   |   |   |   |

|                    |    | データカウント    |   | タイプ  | Data[1] |   |   |   | コマンド    |   |   |           |           |   |   |   |   |

| *** Data DataCount |    |            |   |      |         |   |   |   |         |   |   |           |           |   |   |   |   |

| 1                  | rw | Byte       |   |      |         |   |   |   |         |   |   | UAddressY | UAddressX |   |   |   |   |

|                    |    | Enable     |   |      |         |   |   |   |         |   |   | UアドレスY    | UアドレスX    |   |   |   |   |

|                    |    | バイトイネーブル   |   |      |         |   |   |   |         |   |   | Data      | データ       |   |   |   |   |

40

50

## 【0036】

以下の表2は、表1のメッセージフィールドの全体的な動作または内容を定義する。

## 【0037】

## 【表2】

| フィールド           | ビット   | 機能                                                                                                      |

|-----------------|-------|---------------------------------------------------------------------------------------------------------|

| Pc              | 31    | メッセージを2つの種類に分ける<br>1 - Pixel 1ピクセルちょうどのデータワードがメッセージにつく<br>0 - Command データカウントワードがメッセージにつくのを可能にする        |

| rw              | 30    | 読み取り書き込み選択: 0 - 書き込み、1 - 読み取り                                                                           |

| Data Count      | 29:23 | バッファリングされたメッセージにつく [0..127] を含むデータワードを指定する                                                              |

| Type<br>(タイプ)   | 22:20 | 8つのメッセージタイプから1つを選択、8つのメッセージタイプのうちの4つは独立して説明される<br>0 - 状態 5 - ジオメトリ頂点 7 - QNM<br>2 ~ 4 - 予約 6 - ラスタライザ頂点 |

| Command         | 19:0  | タイプによって指定される空間内の演算子および物理レジスタを選択する                                                                       |

| Uaddress<br>X/Y | 23:0  | 拡張末バッファアドレス空間により $8K \times 2K$ Direct Draw サーフェスへのアクセスが許容される                                           |

| Byte Enable     | 29:26 | バイトイネーブル: 1は変更可能であり、[31:24]、[23:16]、[15:8]、[7:0]に対応する                                                   |

| Data            | 31:0  | コンテキスト依存データ                                                                                             |

Data Count: データカウント

Command: コマンド

UaddressX/Y: UアドレスX/Y

Data: データ

10

20

## 【0038】

表1に示すように、3ビットがメッセージタイプを定義する。

表2に示すように、これら3ビットの値がゼロの場合、メッセージは「状態」タイプメッセージである。

状態タイプメッセージは、機能ユニットタイプが機能ユニットの内部レジスタにアクセスするために使用することができる。

「状態」タイプメッセージの構造およびフォーマットを以下の表3に提示する。

## 【0039】

## 【表3】

| State Message |    |            |   |   |                 |   |                 |   |   |   |   |   |   |   |   | L |   |

|---------------|----|------------|---|---|-----------------|---|-----------------|---|---|---|---|---|---|---|---|---|---|

| 状態メッセージ       |    |            |   |   |                 |   |                 |   |   |   |   |   |   |   |   | S |   |

| M             | S  | B          |   |   |                 |   |                 |   |   |   |   |   |   |   | B | L |   |

| 3             | 3  | 2          | 2 | 2 | 2               | 2 | 2               | 2 | 2 | 2 | 1 | 1 | 1 | 1 | 1 | S | L |

| 1             | 0  | 9          | 8 | 7 | 6               | 5 | 4               | 3 | 2 | 1 | 0 | 9 | 8 | 7 | 6 |   |   |

| 0             | rw | Data Count |   | 0 | Category Select |   | Register Select |   |   |   |   |   |   |   |   |   |   |

|               |    | データカウント    |   |   | カテゴリ選択          |   | レジスタ選択          |   |   |   |   |   |   |   |   |   |   |

|               |    |            |   |   |                 |   |                 |   |   |   |   |   |   |   |   |   |   |

|               |    | カテゴリ選択     |   |   | Data            |   | データ             |   |   |   |   |   |   |   |   |   |   |

30

40

## 【0040】

表3に示すように、状態タイプメッセージ内にて定義される様々なフィールドがある。これらフィールドの動作または内容を表4において以下に定義する。

## 【0041】

## 【表4】

| フィールド   | ビット       | 機能                                                                                                                         |

|---------|-----------|----------------------------------------------------------------------------------------------------------------------------|

| r w     | 3 0       | 読み取り書き込み選択: 0-書き込み、1-読み取り                                                                                                  |

| データカウント | 2 9 : 2 3 | バッファリングされたメッセージにつく [0.. 127] を含むデータワードを指定する                                                                                |

| カテゴリ選択  | 1 9 : 1 5 | アクセスするレジスタのカテゴリを選択する<br>0×00-映像表示 0×08-ラスタライザ 0×12-ホストインターフェース<br>0×04-ジオメトリ 0×09-フレームバッファ 0×13-BIN C<br>0×07-シェーダ 0×10-共有 |

| レジスタ選択  | 1 4 : 0   | カテゴリ内でアクセスするレジスタを選択する                                                                                                      |

| データ     | 3 1 : 0   | コンテキスト依存データ                                                                                                                |

10

## 【0042】

QNM182に配向される作業待ち行列メッセージは、QNM182ファイルアドレス空間内で実行される作業待ち行列ルーチンによってオペランド解析され解釈される。こういったルーチンは、QNM182の振る舞いに影響を及ぼしうる内容の有無についてすべてのメッセージを自由に調べることができる。

好ましくは、1つのメッセージタイプがQNM182の単独使用のために確保される。このメッセージタイプは、QGOメッセージ（表5がQGOメッセージのメッセージ構造を示す）と呼ばれ、作業待ち行列インタプリタ（図10参照）が、メッセージ内で示されたレジスタファイルロケーションに実行点を変更するために使用する。

これは、QNM内で複雑な演算を行うコンパクトかつ効率的な方法を提供する。

そのロケーションにおけるメッセージリストがおそらく、作業待ち行列インタプリタへの復帰（return：リターン）を行う（The message list... work queue interpreter.）。

## 【0043】

QGOに含められる付加的なデータワードの利用は、呼び出されたルーチンの機能である。

さらに、作業待ち行列レスポンダは、データカウントをさらにパディングして、直列リンクネットワーク上のパケットフレーミングに適合することができる。

## 【0044】

## 【表5】

20

30

| M |   | QGO Message |   |   |     |   |                       |   |   |   |   |   |   |   |   |   |   |   |   |   |   | L |   |

|---|---|-------------|---|---|-----|---|-----------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S |   | QGOメッセージ    |   |   |     |   |                       |   |   |   |   |   |   |   |   |   |   |   |   |   |   | S |   |

| B |   |             |   |   |     |   |                       |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B |   |

| 3 | 3 | 2           | 2 | 2 | 2   | 2 | 2                     | 2 | 2 | 2 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

| 1 | 0 | 9           | 8 | 7 | 6   | 5 | 4                     | 3 | 2 | 1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 9 | 8 |

| 0 | 0 | Data Count  |   | 7 | Ind |   | Register File Address |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 0 |

データカウント

レジスタファイルアドレス

40

## 【0045】

表5に示すように、QGOタイプメッセージ内で定義される様々なフィールドがある。これらフィールドのうちの特定のものの動作または内容を表6において以下に定義する。

## 【0046】

## 【表6】

| フィールド        | ビット  | 機能                                                                               |

|--------------|------|----------------------------------------------------------------------------------|

| レジスタファイルアドレス | 15:0 | QNMにとってローカルの記憶装置の64Kアドレス空間内のワードロケーションを指定する。<br>レゾリューション後のアドレスは、QNMメッセージリストの最初である |

| Ind          | 18   | 指定レジスタファイルアドレスに含まれる値を介しての間接レゾリューション                                              |

## 【0047】

間接アドレス指定は、ポインタを介して生成側（producer）と利用側（consumer）との分離をもたらすことができる。

10

QGOメッセージは、メッセージを受け取っている機能ユニットに新しいメッセージタイプを合成する能力を有する。

QNM182は、QGOメッセージを使用して、新しいメッセージを作業待ち行列インタプリタに挿入することができる。

QGOメッセージはなんらかのサブルーチンへのポインタであるため、プログラマは、所与の機能ユニットに予め定義されていない新しいコマンドを作成するためにこれを使用することができる。

## 【0048】

QNMのレジスタファイル内において、別のメッセージセットを使用して、QNM182の振る舞いを実施することができる。

20

バッファリングされた作業待ち行列QGOメッセージも有効なQNMメッセージであることができる。

QNM182は、直列リンクのネットワークを介してすべてのノードのローカルな記憶装置に読み取りアクセスすることができ、またそれ自体のノード180のローカルな記憶装置175に読み取り／書き込みアクセスすることができる。

自由に使用可能なように記憶装置の一部を割り当ててもよく、またサブルーチンメッセージにより、指定情報をローカルな記憶装置175からロードし、またそこから格納するよう明示的に指示することもできる。

## 【0049】

QNM182は、高度に動的な多数の待ち行列およびスタック構造を管理することも可能である。

30

構造の数により、レジスタファイル空間の固定部分をそれぞれに確保することは望ましくない。

また、機能ユニット間の相互作用のダイナミクスにより、任意所与の瞬間に最も多くのデータを含む構造がシフトするものと予想される。

したがって、ストレージの動的割り当てをサポートする機構を含めることができる。

## 【0050】

本発明の教示により構築されるグラフィックスシステムの基本要素の高レベルの構造および動作について述べたが、システムは、テキスチャマップおよびジオメトリアクセラレータ等、ノード内に含まれる機能ユニットが、ポイントツーポイント直列リンクを備えるノードからなるルータベースのネットワークを介して通信する新規のアーキテクチャを有することを理解されたい。

40

直列リンクは、発信ノードがネットワーク上の応答ノードのローカル記憶空間からデータパケットを戻すように要求するための媒体を確立する。

ローカル記憶空間は、物理的なRAMであっても、またはキャッシュおよび待ち行列等、そのRAMの仮想表現であってもよい。

直接リンクを持たないノードは、中間ノードを介してQNM182によってルーティングされる。

好みの実施形態では、リモートノードのローカルメモリ空間への書き込みは許されない。

50

代わりに、資源および作業は、ノードのローカル空間への書き込みだけが必要なように分散される。

#### 【0051】

作業またはデータをどのようにシステムのノードに分散可能かを説明するために、S R U 189を考える。

S R Uは、様相(画面解像度(display resolution)、フロントバッファ選択等)の変更を除き、作業待ち行列によって導かれない連続プロセスである。

合成プロセスは、ディスプレイを表す画像サーフェスの空間的局所性に基づいて区分化される。

このプロセスは、それぞれの空間的局所性から独立して、複数の画像サーフェスにアクセスすることができる。 10

ディスプレイに位置合わせされたサーフェスは、同じ空間的局所性を有することができる。

ディスプレイをアップデートするプロセスは、ディスプレイドライバのロケーションに対してローカルである。

この点において、ディスプレイに単一のドライバのみがあることが好ましい。

これにより、実際のディスプレイ上のピクセルの位置合わせに伴う問題が回避される。

ディスプレイアップデートプロセスでは、適正なノードから合成画像にアクセスする。

#### 【0052】

ジオメトリアクセラレータに関しては、作業は、各種ジオメトリアクセラレータの間で均衡のとれた作業負荷が維持されるように、システム内の各種ジオメトリアクセラレータに分散することができる。 20

既知のように、ジオメトリアクセラレータによって演算されるデータは、画面座標ではなくユーザ座標にある。

したがって、空間的局所性に基づいてジオメトリアクセラレータ間に作業を分割しないほうが好ましい。

しかし、ロードバランスに基づいてデータを分割することが可能である。

#### 【0053】

この点において、各種ジオメトリエンジンは一般に、アイドルになるときかまたは作業が必要なとき、それぞれの作業待ち行列をホストインターフェースQ N Mからポーリングする。 30

ホストインターフェースQ N Mは、このポーリングアクティビティを監視して、どのジオメトリアクセラレータがより暇であるかを判断し、付加的なプリミティブをそういったジオメトリアクセラレータに割り当てることができる。

このようにして、ホストインターフェースQ N Mは、最も効率的に作業負荷を平衡化するように、各種ジオメトリアクセラレータに作業を分散させることができる。

本明細書においてさらに考察するように、作業の順序が維持される限り、「ラウンドロビン」様式で、または他の方法でこの作業を分散させることができる。

#### 【0054】

ラスタライザに関しては、作業を、ジオメトリアクセラレータにより実行された後、空間的局所性に基づいて分散させることができる。 40

すなわち、ジオメトリアクセラレータがデータに対するそれぞれの作業を完了した後に、そのデータを画面空間に投影することができる。

作業を画面空間に投影すると、階層タイラ184が、どのラスタライザがディスプレイ(画面空間)の特定のエリアに関連しているかを判定することができ、画面空間投影に基づいて、作業をラスタライザに適宜配向することができる。

#### 【0055】

テキスチャマッピングに関しては、ピクセル、またはさらにサブピクセルレベルに対するテキスチャパラメータを計算した後、個々のテクセルの空間的局所性を決定することができる。 50

一般に、テキスチャの空間的局所性と画像の空間的局所性との間に相関はない。

【0056】

作業は、好ましくは、画像の空間的局所性、より古典的なFIFO格納手段を通してのパイプラインパラメータによって示されるノードに分配されて、空間的局所性から独立したテクセルサンプルを読み出す機能を有するテキスチャマッピングを提供する。

【0057】

機能ユニットが別のユニットにおいて一連のアクションを行うために、メッセージシーケンスが生成され、実施ノードのローカル記憶空間に書き込まれる。

好ましい実施形態では、また上述のように、メッセージは、指示されたアクションの実行に使用されるデータワードが続くコマンドワードからなる一連の32ビットワードである。

影響を受ける機能ユニットは、同意されたロケーションからシーケンスを消費し、メッセージを意図されるように解釈する。

メッセージシーケンスは、作業待ち行列と呼ばれ、これについても上述した。

機能ユニットは、それぞれの入力において作業待ち行列を消費し、それぞれの出力において作業待ち行列を生成する。

この点において、生成側ノードは、それ自体のローカルメモリ空間に作業待ち行列を生成する。

対照的に、消費側ノードは、データ、命令、または他の情報（必要に応じて）を生成側のメモリから引き出す。

このようにして、コピーレンジが簡略化された様で維持される。

消費側が、まだ準備できていないデータまたは情報を要求する場合、そのデータまたは情報は消費側に戻されず（データまたは情報が生成側によって生成されるまで）、よって消費側がストールすることを理解されたい。

【0058】

実行機能ユニットおよび影響を受ける機能ユニットは、同じ物理ノード内にある必要がない。

プログラム可能なポインタは、明示ノードのローカル記憶空間内の待ち行列に空間を指定し、生成側と消費側とを分離できるようにする。

独立して生成側ポインタおよび消費側ポインタを指定することで、新しい機能ユニットを古いユニットについての知識なしで挿入できるようにすることによってスケーラビリティが向上する。

機能ユニットは、FIFO様インターフェースを介して待ち行列にアクセスし、ノード格納アドレスの管理はQNMによって行われる。

【0059】

例として、機能ユニットによるメッセージの実行は、作業待ち行列に明示的に提供されない情報を必要とする場合がある。

たとえば、あるアクションは、テキスチャが貼り付けられた三角形プリミティブのレンダリング、またはDACを通しての画像を表す情報のシーケンシングができる。

機能ユニットは、そのノードのメモリサブシステムインターフェースへの専用インターフェースを介して、またはQNM182への専用ポートを介して、必要な情報を直接要求する。

たとえば、図5のシェーダ186は、メモリコントローラ188と直接通信することができるか、あるいは、QNM182への専用ポートを介して通信することができ、QNM182は、シェーダ186に/からのデータがローカルであるか、それともリモートであるかを判断することができる。

メモリサブシステムは、どのノードのローカルストレージが情報を含むかを判断し、リモートノードにある場合はネットワークへのインターフェース上に要求を発信し、リモートノードにない場合はそれ自体のローカル記憶装置インターフェースに対するアクセスを始める。

応答が戻る待ち時間を補償するために、複数の要求を発信することも可能である。

10

20

30

40

50

## 【0060】

QNMに待ち行列ポインタを変更する能力を与えることで、作業待ち行列パラダイムにおけるフロー制御が行われる。

たとえば、一連の生成側から消費側作業待ち行列を得ることが望ましい場合がある。

QNM内に含まれるレジスタファイルに格納されているルーチンにアクセスするメッセージクラスでQNMの能力を増強することで、あるクラスのユニットの「ラウンドロビン」シーケンシング等（以下に提示する例では、複数のジオメトリアクセラレータの出力のシーケンシング等）多種多様な有用な振る舞いを作成することが可能であり、またはコンテキストをローカル記憶空間に保存かつ／または再格納することが可能である。

さらに、QNMのすべての振る舞いは、結果としてより高レベルのルーチンにアクセス可能な、メッセージ待ち行列の内容を転送し解釈するルーチンによって決められる。 10

予想される正確な振る舞いは、好ましくは、QNMにプログラムされる実施によって決定される。

## 【0061】

このパラダイムの使用についての単純な例示を提供するために、作業待ち行列を介して通信する機能ユニットの概念を示す図7を手短に参照する。

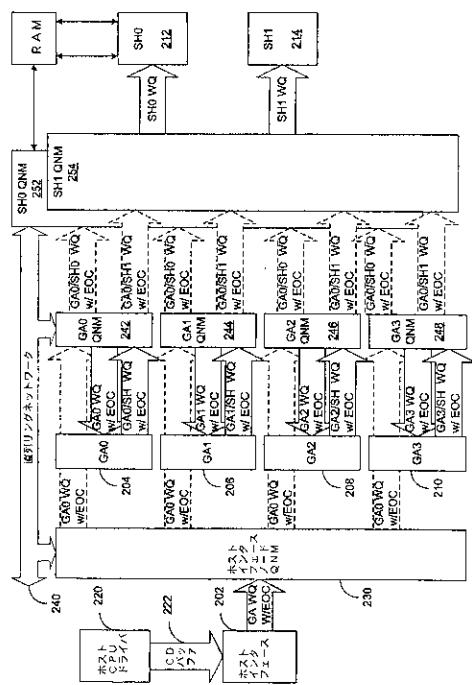

具体的に、図7は、ホストインターフェース202、4つのジオメトリアクセラレータ（GA）204、206、208、および210、ならびに2つのシェーダ212および214を示す。

ホスト上のデバイスドライバ220は、コマンド／データバッファの形態のメッセージ22をI/Oバスに書き込み、ホストインターフェース202がこれを、ホストインターフェースQNM230に書き込まれる作業待ち行列メッセージに翻訳する。 20

図示の実施形態では、全ての4つの描画プリミティブが完成した後に、常に、ホストインターフェースQNM230は、EOC（End-Of-Chunk）メッセージを合成してロードバランシングを行う。

EOCメッセージは、エンドオブチャンク（本明細書においてさらに考察する）を行うQGOメッセージ（上述）である。

## 【0062】

破線の矢印は、デバイス間の論理的な通信を表すことを理解されたい。

かかるデバイス間の実際の通信は、好ましくは、直接ではなく、むしろ直列リンクのネットワークを介して、また各ノードのQNMを通して行われる。 30

## 【0063】

QNM230は、作業待ち行列（QNMにとってローカルなメモリにおいて）をオペランド解析するパワーアップ後に開始されるメッセージリストを実行し、状態メッセージをすべてのジオメトリアクセラレータ作業待ち行列に分配し、次のEOCまで、1つのジオメトリアクセラレータ作業待ち行列に作業メッセージを分配する。

このEOCは、「ラウンドロビン」シーケンスから次のジオメトリアクセラレータを選択することができるサブルーチンメッセージリストを呼び出し、アクティブなジオメトリアクセラレータ作業待ち行列にシェーダEOCを合成する。

各ジオメトリアクセラレータ204、206、208、および210は、それぞれの作業待ち行列を消費し、シェーダ212および214に作業待ち行列を生成する。 40

ジオメトリアクセラレータによって直接実行可能ではないメッセージは、その出力に伝播されるが、他は、新しいシェーダメッセージの合成につながる描画プリミティブを表す。QNMは、シェーダ作業待ち行列を解析するパワーアップの後、開始される他のメッセージリストをも実行し、すべてのシェーダ作業待ち行列に状態メッセージを分配し、メッセージに含まれる空間情報によって指示されるように各シェーダ作業待ち行列に作業メッセージを分配する。

## 【0064】

図示のように、ネットワーク240との通信は各種QNMによって行われる。

たとえば、ホストインターフェースQNM230は、ジオメトリアクセラレータ204、2 50

06、208、および210の作業待ち行列メッセージをネットワーク240に連絡する。

ジョメトリアクセラレータ204、206、208、および210の各QNM242、244、246、および248にて、これら作業待ち行列メッセージをネットワーク240から受け取る。

#### 【0065】

概念上、任意の数の機能ユニットがノード内に存在しうるが、各機能ユニットは独立して、それぞれの作業待ち行列を生成し消費する。

所与のノードに存在する機能ユニットの実際の数は、QNM内で必要な資源を決め、ネットワーク上の帯域消費に貢献する。

10

入出力の帯域は、好ましくは、ネットワークのノード部分上の利用可能な帯域を越えず、さらなる生成側および消費側にサービスを提供可能な場合であっても、QNMの複雑性に事実上上限を設ける。

異種混在ノードクラスセットでは、機能ユニットタイプの異方性分布を許し、新しいタイプの機能ユニットのネットワークへの導入を容易にするため、スケーラビリティが向上する。

#### 【0066】

複数の機能ユニットは、各機能ユニットの通信シーケンス順が、他の機能ユニットから独立して維持されるため、デッドロックなしで同時に動作することができる。

好ましくは、ネットワーク240上の通信粒度は、十分に細かいため、どの機能ユニットも他の機能ユニットのネットワークへのアクセスを大幅に遅らせることがない。

代わりに、利用不可能なパケットへの所与の要求を発した特定の機能ユニットのみがストールする。

他のシーケンスは、ネットワーク240に沿って独立して継続する。

作業待ち行列は、応答なしで発信を無期限に取り残すことのないように終わる構造を有する。

上記EOC等の機構を利用する待ち行列は、先を読み、到来するEOCについて警告する役割を果たすQNMメッセージを挿入することによって、待ち行列の論理的終わりまたは待ち行列間の遷移を越えて要求を発信しないようにするルーチンを生成側QNMおよび消費側QNMに含む。

#### 【0067】

機能ユニット間で動作を同期させるという浸透したニーズもまた、待ち行列の概念で実現可能である。

同期させる各ユニットは、単純にリターンである短い待ち行列を生成する。

この文脈において、リターンは単純に、指定されたアドレスから検索される内容のないパケットであり、戻り値について解釈または実行はない。

単一の指定ユニットは、各待ち行列を順番に消費するためにジャンプする。

最後の待ち行列の検索に成功した場合、各ユニットに待ち行列を生成する。

生成は本質的に、同時に完了し、各機能ユニットが消費を完了し、それぞれの作業待ち行列を略同期して継続することが可能である。

#### 【0068】

作業待ち行列生成に関して、1つの機能ユニットにて生成されたメッセージシーケンスは、複数のユニットによって消費されるシーケンスに分化することができる。

シーケンスは、すべてのターゲットユニットに複製すべき部分（状態）、およびターゲットユニットのサブセットが処理すべき部分（作業）を含むことができる。

状態部分は、最適化可能な部分（同じメッセージの初期書き込みを除去可能）および最適化不可能な部分にさらに分けることができる。

作業部分のターゲットは、その内容によって予め決めることができるか、または空の作業部分を受け取る「ラウンドロビン」シーケンスにおいて最初に利用可能な中間ユニットによって動的に決めることができる。

10

20

30

40

50

## 【0069】

区分化するシーケンスで最適化可能な状態が見つかる場合は常に、アクティブ状態として保存され、すべての機能ユニットにマークが付けられる。

ビットアレイとしてレジスタファイルワードを操作するメッセージにより、これらアクションが容易になる。

ターゲットとする作業待ち行列に作業を配置すべき場合は常に、マークの付いたすべてのアクティブ状態は、作業待ち行列にまず配置される。

このようにして、作業を有する機能ユニットは、作業メッセージ間ですべての状態遷移を受け取ることなく、アクティブ状態を有するようになる。

## 【0070】

さらに、適当な機能ユニット入力または出力における作業待ち行列を処理するQNMメッセージを導入することによって、生成側、消費側、および／またはネットワーク240の帯域に対してより効率的なシーケンスの特定が可能である。

たとえば、頂点データ（たとえば、X、Y、Z、R、G、B、アルファ、S、T等の座標および値）の異なる部分をノードに通信するために複数の連続メッセージを使用した場合、単一メッセージパケットを、単一パケットでこのすべてのデータを送信するように構築することができる。

これにより、複数のメッセージでやりとりされる「ヘッダ」情報の量が削減される。

## 【0071】

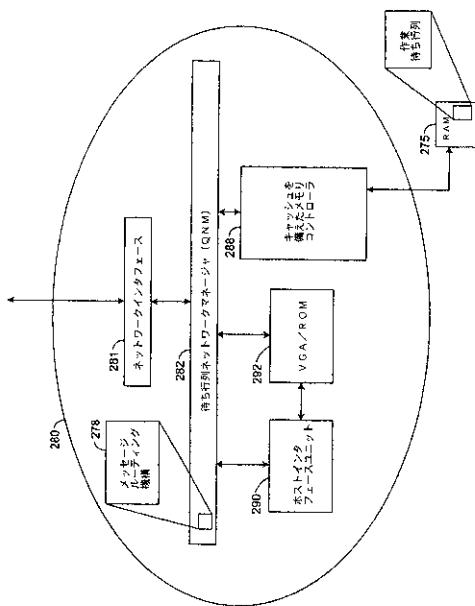

次に、図5のノード180と同様であるが、異なる機能ユニットを有するノード280を示す図8を手短に参照する。

この点に関して、図5は、コンピュータグラフィックスシステムにおいて特定のグラフィックス処理機能を実行するノード180を示した。

図5のノードのように、図8に示すノード280は、ネットワークインターフェース281、QNM282、メモリコントローラ288、メッセージルーティング機構278、および専用RAM275を備える。

ノード280は、ホストインターフェースユニット290およびVGA/ROM292も示す。

## 【0072】

このノード280またはこのようなノードは、ホストコンピュータとの他のノードの初期化および通信を調整するように動作する。

機能ユニット290は、ホストインターフェースとしての役割を果たし、ホストと通信するように動作する。

スタートアップすると、システム内の他のノードは、ノード290と通信して命令を受け取ることができる。

すなわち、スタートアップすると、他のノード（消費側）は、ホストインターフェース290からそれぞれのセットアップおよび構成情報を読み取って得ることができる。

この初期通信中、その他のノードには、それぞれの作業待ち行列を読み出す場所について命令することができる。

## 【0073】

VGA/ROM292とラベルの付いたブロックは、QNM282およびホストインターフェースユニット290の双方と通信することが可能である。

VGA/ROM292は、本発明のグラフィックスシステムおよびドライバが表示の制御を得る前に、グラフィックスBIOS（基本入出力サービス）と通信することによってグラフィックス初期化を行うことができる。

ホストと初期化および通信を、ノード290を通して行う特定の方法は、本発明に対する制限ではなく、当業者により実施可能である。

## 【0074】

好ましい実施形態の一態様は、分散共有メモリとして見ることができる。

共有または統合メモリシステムは既知であり、メモリシステムが複数のサブシステムまた

は機能 / 処理ユニットによって共有される。

分散メモリシステムもまた既知であり、メモリが各種機能 / 処理ユニットによる使用のために分散される。

上述した分散共有メモリ態様は、共有手法および分散手法の双方からの利点を生かすものである。

まず、分散帯域（メモリ帯域ボトルネックの回避）等、分散メモリシステムからの特定の利点を提供する。

同時に、メモリ資源の共有を可能にすることによって、複数のメモリ装置間でのデータの複製を回避する。

好ましい実施形態では、メモリ装置への書き込みアクセスが、関連するノードの機能ユニットによってしか行うことができないように、メモリ装置へのアクセスは制限される。 10

しかし、読み取りアクセスはすべてのノードに許可される。

この制約により、複雑なコヒーレンシ方式を実施する必要がなくなる。

#### 【0075】

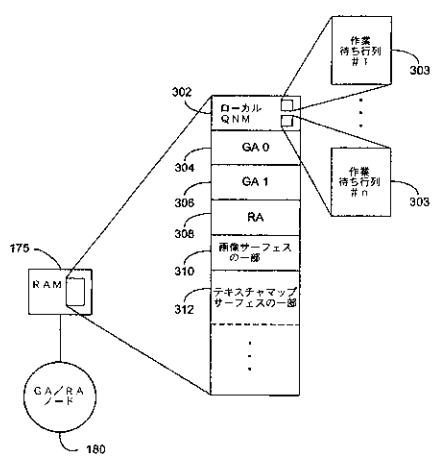

次に、図5に示すもののようなグラフィックスノードが使用しうる潜在的なメモリセグメント化方式の一例を示す図9を参照する。

しかし、本発明の範囲および精神に一致して他の多数のセグメント化方式を使用可能なことを理解されたい。

図9に示す実施形態では、グラフィックス処理機能を実行するノード180にとってローカルなメモリ175は、いくつかの専用セグメントを含むことができる。 20

1つのセグメント302は、ローカルノード180のQNM182（図5）専用である。

空間に格納可能な他のデータおよび情報の中でもとりわけ、この専用メモリ空間302は、複数の作業待ち行列303を含むことができる。

この点に関して、QNM182は、消費ノードに作業待ち行列を生成する生産ノードとして機能する。

これと併せて、消費ノードは、これら作業待ち行列303から読み出すことが可能である。

#### 【0076】

メモリ175の他のメモリセグメントは、第1のジオメトリアクセラレータのためのセグメント304、第2のジオメトリアクセラレータのためのセグメント306、ラスタライザのためのセグメント308、画像サーフェスの一部を含むセグメント310、テキスチャサーフェスの一部を含むセグメント312を含むことができる。 30

ジオメトリアクセラレータセグメントおよびラスタライザセグメントに関して、これら構成要素が「消費側」として機能する場合、メモリセグメントは作業待ち行列を格納する必要はない（作業待ち行列を格納する必要があるのは生成側構成要素のみであるため）。

本発明の統合メモリ構造により、テキスチャサーフェスを分化し、複数のノードにまたがって格納することが可能である。

テキスチャサーフェスを表示中の画像に空間的にマッピングすることは容易ではない範囲において、これは特に独特である。

#### 【0077】

したがって、システムは、各種ノードのメモリのセグメント化に基づいて作業待ち行列を変更する機構を含む。

この機構は、メモリセグメント化に関連する機能ユニットに応じて異なる。

先に述べたように、ホストインターフェースは、各種ノードのジオメトリアクセラレータの間でロードバランシングが行われるように作業をジオメトリアクセラレータに分散させる機構（特に図示せず）を含むことができる。

空間的局所性（たとえば、メモリセグメント化）に基づいて各種ラスタライザに作業に分散させる別の機構（たとえば、階層タイラ184）を使用することも可能である。

#### 【0078】

図示の実施形態（たとえば、図5）では、メモリ装置はノードが割り当てられ、ノードに 50

関連付けられる。

各ノードは、データを処理する少なくとも1つの機能ユニットを含む。

かかるシステムアーキテクチャには、特にコンピュータグラフィックス環境において多くの利点がある。

これら利点のいくつかとしては、統合されたサーフェス定義を提供すること、複数のメモリにテキスチャを複製することなくテキスチャの共有が可能であること、画像サーフェスがテキスチャを定義可能であること、コンピュータグラフィックスカード内にディスプレイリストの分散格納が可能であること、すべてのジオメトリアクセラレータがディスプレイリストにアクセス可能であること、グラフィックスシステムがスケーリングされる際のテキスチャ帯域のスケーラビリティ、および大きなメモリ構成のサポートが挙げられる。

大きなメモリ構成のサポートに関して、かかる構成は、テキスチャマッピング、アンチエイリアシング、およびディスプレイリスト格納に強化されたサポートを提供する。

#### 【0079】

既知のように、ディスプレイリストは、グラフィックスハードウェアに対してローカルに格納されるグラフィックスプリミティブのリストである。

ディスプレイリストの実施および使用は既知であり、グラフィックスハードウェアの速度がホストCPUよりも高速であったときに開発された。

進化してCPUの速度が向上し、ディスプレイリストの使用および実施が減り始めた。

しかし、グラフィックスハードウェアの速度および能力は、再び大半のホストCPUよりも優れたものとなりつつあり、ディスプレイリストの使用および実施がより望ましくなってきている。

本発明の分散共有メモリ構造は、ディスプレイリストの実施を単純なことにすることを理解されたい。

#### 【0080】

好ましい実施形態の一様によれば、共通アクセス可能なメモリを介して各種機能ノードの間でメッセージを受け渡すシステムおよび方法が提供される。

この点に関して、「メッセージ」なる用語は広義に解釈される。

ある文脈では、メッセージは単純に、渡されるかまたは共有される情報を含むことができる。

別の文脈では、メッセージは、消費側機能ユニットが消費可能な作業待ち行列に関連する。

たとえば、作業は、コンピュータグラフィックスのセグメント上でそれぞれ動作する、異なるノードの複数のジオメトリアクセラレータに割り当てることができる。

生成側であるジオメトリアクセラレータは、出力をそれぞれの自身のローカルメモリに「生成」する。

しかし、ラスタライザのQNMは、複数のジオメトリアクセラレータの各出力を検索し、ラスタライザに関連するノードのメモリ空間に作業待ち行列を形成し、この作業待ち行列はラスタライザによって消費される。

#### 【0081】

別の文脈では、好ましい実施形態の構造は、システムの素早い拡張を容易にする、または実現する。

一例として、ジオメトリアクセラレータとラスタライザ（二次補間回路等）との動作の間に機能的に挿入される機能ユニットを追加したいものと仮定する。

この機能ユニットを含む別個のノードを追加することができる。

この機能ユニットのQNMは、複数のジオメトリアクセラレータの各出力を検索し、新しい機能ユニットが消費する作業待ち行列を形成することができる。

そして、新しい機能ユニットはそれ自体の出力を生成することができ、ラスタライザ（1つまたは複数）がこの出力を検索し、演算を行う。

かかるハードウェアの拡張は、他のハードウェアを変更することなく、単純なソフトウェアアップデートにより、システムによって独自に実現可能であることが理解されよう。

10

20

30

40

50

## 【0082】

図6に併せて考察したように、第1のノードが第2のノードの動作を引き起こすために、第1のノードは、第2のノードに連絡され、第2のノードの作業待ち行列190に配置されるメッセージまたはメッセージシーケンスを生成する。

第2のノードは後に、作業待ち行列内のそのメッセージを処理するときに、第1のノードによって要求される、すなわち特定される動作を実行する。

この点に関し、作業待ち行列190は複数のメッセージ192を含む。

一般に、メッセージは、ノード上にある機能ユニットへのコマンドまたは命令である。

データパケット194も示される。

データパケットとは、メッセージを通信するために使用される機構であり、通信リンクを介してやりとりされる最小量のデータである。 10

## 【0083】

QNM182に配向される作業待ち行列メッセージは、QNM182ファイルアドレス空間内で実行される作業待ち行列ルーチンによってオペランド解析され解釈される。

こういったルーチンは、QNM182の振る舞いに影響を及ぼし得る内容がないかすべてのメッセージを自由に調べることができる。

上述したように、QGOメッセージタイプは、QNM182の単独使用のために確保される。

作業待ち行列インタプリタ440(図10参照)が、メッセージ内で示されたレジスタファイルロケーションに実行点を変更するためにQGOメッセージを使用する。 20

これは、QNM内で複雑な演算を行うコンパクトかつ効率的な方法を提供する。

その位置におけるメッセージリストがおそらく、作業待ち行列インタプリタへの復帰(return:リターン)を行う(The message list at that location may well effect a return to the work queue interpreter.)。

## 【0084】

QGOに含められる付加的なデータワードの利用は、呼び出されたルーチンの機能である。

さらに、作業待ち行列レスポンダは、データカウントをさらにパディングして、直列リンクネットワーク上のパケットフレーミングに適合することができる。 30

上述したように、間接アドレス指定により、ポインタ430(図10参照)を介して生成側と消費側とを分離することができる。

## 【0085】

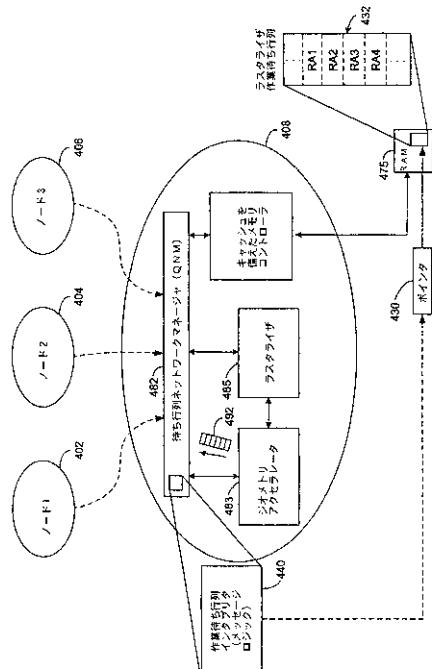

メッセージ受け渡しの特定の態様を上述したが、これら態様について、図10を参照してさらに説明する。

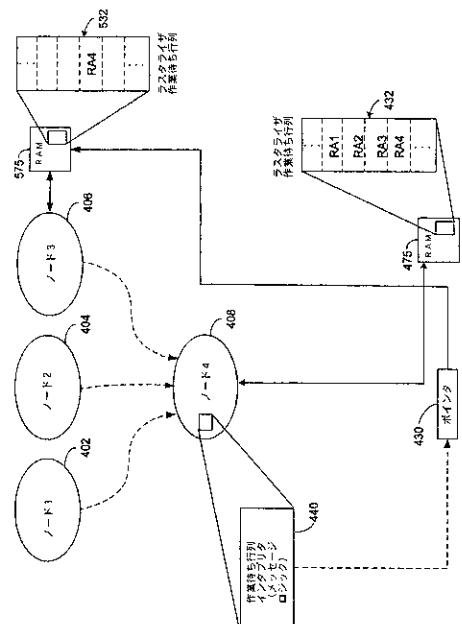

図10は、複数のノード402、404、406、および408を有するシステム400を示す図である。

もちろん、付加的なノード(図示せず)が存在してもよい。

簡単および例示のために、ノード402、404、406、および408の各々が、図5に示すノード180と併せて示した各種機能ユニットを備えるものと仮定する。

これら機能ユニットの一部のみがノード408に示されており、ノード402、404、および406には示されていない。

ジオメトリアクセラレータおよびラスタライザの動作の上流において、ホストから送信されたグラフィックスデータストリームが解析され、ジオメトリアクセラレータによる処理のために、各種ノード402、404、406、および408にセグメント化される。

各ノードはそれぞれのローカルメモリにのみ書き込むため、ジオメトリアクセラレータの出力結果は、各ノード内のRAMに保存される。

次いで、ノード408は、ラスタライザ485に作業待ち行列を形成するにあたり、各種ジオメトリアクセラレータの結果を検索する。

もちろん、ラスタ化プロセスを各種ノードに分割してもよい。

20

30

40

50

しかし、簡単のために、1つのかかるラストライザノードのみを示す。

【0086】

4つのラストライザがある、図示の場合のような状況では、各ジオメトリアクセラレータからの結果をラストライザのうちの1つまたは複数に分散させなければならない。

図示のように、メッセージ492は、ジオメトリアクセラレータ483から生成し、作業待ち行列インタプリタ440によって解釈することができ、作業待ち行列インタプリタ440が、どのラストライザがメッセージを処理する必要があるかを判断する。

ローカルメモリ475（または他のどこか）に格納され、ラストライザ作業待ち行列432のデータ宛先を指すことが可能な一連のポインタ430を使用することにより、QNM482は、ノード408内のラストライザ485、ならびにノード402、404、および406内のラストライザに作業待ち行列432を容易に構築することができる。 10

【0087】

同様にして、QNM482は、追加の機能ユニットのシステム400への挿入を容易にサポートすることが可能である。

上述したように、例示として、補間機能実行のために新しい機能ユニットを挿入したいものと仮定する。

さらに、この機能ユニットは、ジオメトリアクセラレータとラストライザとの間に機能的に挿入されるものと仮定する。

ポインタは、挿入される機能ユニットによって生成されるデータのソースを反映するよう 20に更新することができるため、ポインタベースのシステムを使用すると、追加の機能ユニットを容易に挿入することができる。

作業待ち行列インタプリタ440を使用して、この特徴を推進することもできる。

【0088】

図10と同様の図である図11を手短に参照する。

しかし、ノード408の内部構成要素は図から省かれている。

さらに、ノード406に関連する作業待ち行列532が示される。

特に、ラストライザ作業待ち行列432および532は、とりわけ、各ノード406および408のジオメトリアクセラレータからの内容を含み、ラストライザ485（図10）が計算を行うとき（メッセージ制御を介して）、作業待ち行列インタプリタ（またはポインタロジック）440は、必要な情報を得るために、必要に応じて作業待ち行列432、作業待ち行列532、または別の作業待ち行列を指すようにポインタの値を制御する。 30

この点に関して、消費側機能ユニット（たとえば、ラストライザ）はリモートノードからデータを得ることができる。

そのため、ポインタは、ローカルRAM475内のロケーションを指す必要はなく、リモートRAM575内のロケーションを指すことができる。

【0089】

上記から分かるように、実際、作業待ち行列を消費側に供給するように働くQNMは、ポインタ変更を指示するメッセージが複数の生成側からの作業待ち行列部分の検索開始まで待たない可能性が高い。

待つ場合、変更発生時に新しい生成側からパイプラインを充填する不必要的待ち時間が発生し得る。 40

代わりに、ポインタが「ラウンドロビン」様式で変化することを知った上で待ち時間を隠すようにQNMを構成することができる。

メッセージによりサブルーチン等へのポインタ変更を命令しなければならない場合であっても、インテリジェントな生成側はその変更を予見し、新しいポインタの値を予示するメッセージを送信し、メッセージストリームにおける適宜ポイントにて制御フローの変更をトリガする。

【0090】

本発明により構築されるシステムおよび方法の好ましい動作環境、ならびに共通メモリを通してシステムのノード間でメッセージを受け渡すために設けられる構成要素について述 50

べたが、次に、QNMの内部構造および動作を参照する。

先に述べたように、QNMは、相互通信ネットワークから各種ノードの機能ユニット（消費側および生成側の双方）へのデータおよび命令の流れを調整または配向する。

QNM482の物理的および機能的な構造を図10に示す。

【0091】

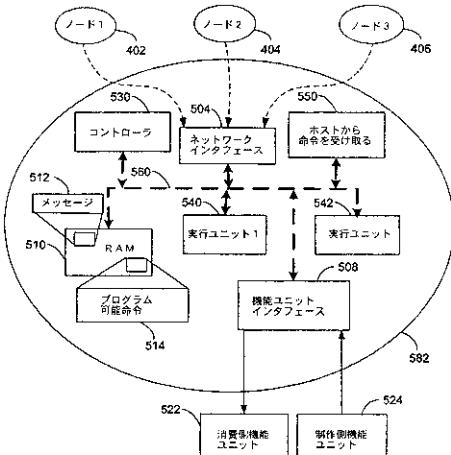

次に、本発明の一実施形態により構築されQNM582の機能および特徴を実施する特定の内部構成要素を示すブロック図である図12を参照する。

この点に関して、本発明の重要な特徴は、プログラム可能なQNMの設計および実施である。

この文脈にて使用する「プログラム可能」なる用語は、QNM582を含むノードに命令を渡すことによって、ホスト、あるいは他のリモートコンピュータまたはノードが制御可能な機能性を有するQNMの実施を指す。

図12の図中の各種ブロックは、本発明の範囲および精神に合致してハードウェア、ファームウェア、またはソフトウェアで実施し得るロジックまたは機能ユニットを表すこと 10 を理解されたい。

好ましくは、QNMは、特定用途向け集積回路（ASIC）の一部であり、このASICは、さらなる特徴および構成要素を同様に実現することができる。

【0092】

図12に示すように、QNM582の中心には、RAM510、複数の実行ユニット540および542、ならびにプログラム可能コントローラ等の制御機構530がある。

実行ユニット540および542は一般に、ALU（論理演算装置）や他の同様のデバイス等、比較的単純なタスクを実行するように設計された構成要素である。

図示のように、RAM510は、特に、メッセージ512およびプログラム可能命令514（他のノードから受け取る）を格納する空間を含む。

本発明の実施形態によれば、プログラム可能命令514は、明確な、すなわち特定の機能を実行するように実行ユニット540および542を構成するために使用することができる。

この点に関して、実行ユニット540および542は、過度に単純な設計においてではあるが、異なる様々なタスクを実行するように特に構成可能な汎用設計を有することができる。

プログラム可能命令514は、各種命令ユニット540および542の特定化された動作を制御または構成するために使用することができる。

【0093】

図12には、ネットワークインターフェース504および機能ユニットインターフェース508を含むインターフェースも示す。

一実施形態では、これらインターフェースは、それ自体特に設計することができる。

別の実施形態では、これらインターフェース504および508は、それ自体プログラム可能に構成することができる。

この点に関して、インターフェース504および508は、実行ユニット540および542のような、インターフェースとして一意に構成された実行ユニットとして見ることができる。

最も単純な形態では、インターフェース504および508は、単にFIFO（先入れ先出し）デバイスであり得る。

【0094】

コントローラ530は、QNM582内の各種装置の全体の動作を制御し調整するように構成可能なロジックである。

例として、ホストコンピュータ等のリモートノードが、特定のプログラム可能命令をQNM582に連絡した場合、これら命令はネットワークインターフェース504を通して受け取られ、RAM510内に格納される。

コントローラ530は、プログラム可能命令514を評価し、それに従って作用するよう

10

20

30

40

50

に構成可能である。

たとえば、プログラム可能命令が、実行ユニット 540 の構成が、受け取ったメッセージ 512 の特定部分またはフィールドに対して復号化動作を行うように命令するものである場合、コントローラ 530 は、プログラム可能命令 514 に従って実行ユニット 540 の構成を制御するように構成することができる。

【0095】

プログラム可能命令 514 の形態およびフォーマットは様々であり得ることを理解されたい。

一実施形態では、プログラム可能命令 514 は単一の命令であってもよい。

別の実施形態では、プログラム可能命令 514 は、1つまたは複数の実行ユニット 540 および 542 の動作の構成に使用されるコードのより複雑なセグメントを含むことができる。

【0096】

図 12 には、リモートノードから命令または他の情報を受け取り、確実に情報が RAM 510 に適宜配向されるように構成されるロジックを表すブロック 550 も示す。

コントローラ 530 とは別個に示すが、実施形態によっては、ロジック 550 はプログラム可能コントローラ 530 に組み込まれ得ることを理解されたい。

【0097】

QNM582 内の各種機能ユニットおよび装置を相互接続するように示す破線 560 は単に、これら装置間の通信ネットワークを表すことをさらに理解されたい。

この通信ネットワーク 560 は、QNM582 内の装置の特定の実施に応じて様々な形態または実施態様を探ることができる。

したがって、図 12 における破線 560 は、必ずしも、各種装置間の直接接続として見るべきではなく、別様に言えば、本発明に対する制限として解釈すべきではない。

【0098】

図 12 は、機能ユニットインターフェース 508 と、QNM582 外にある各種機能ユニット 522 および 524 との間の相互通信も示す。

先に述べたように、計算システム内のノードは各種機能ユニットを含む。

機能ユニットによっては、生成側（すなわち、作業待ち行列を生成する）であるものも、また消費側（すなわち、作業待ち行列を消費する）であるものもある。

機能ユニット 508 は、各タイプの機能ユニット（すなわち、消費ユニット 522 および制作側機能ユニット 524 の双方）と通信して図 11 に示されている。

もちろん、実際の実施では、機能ユニットインターフェース 508 は、各インターフェースが単一の機能ユニットのみとインターフェースするように、複数の機能ユニットインターフェースに区分化することができる。

図 12 に示す実施形態は、比較的高レベルの構成要素のみを示すことを理解されたい。

【0099】

QNM482 の本発明のプログラム可能性に関して、受け取られ、RAM510 に格納されるプログラム可能命令は、特定のタスク、機能、または動作を実行するように QNM582 内の実行ユニットを構成するために利用可能なことを理解されたい。

好ましくは、これらタスク、機能、または動作は、QNM582 を通して渡されるメッセージ 512 に対して行われる。

一実施形態では、実行ユニット（たとえば、実行ユニット 540）は、動作して RAM 510 内に含まれるプログラム可能命令（単数または複数）を評価し、ふさわしい動作（すなわち、プログラム可能命令によって定義される動作）を実行するように特別に構成することができる。

一実施形態では、かかる命令（1つまたは複数の関連メッセージからの内容に結び付けられる）は、他の実行ユニットの動作を構成する構成情報を提供することができる。

【0100】

このプログラム可能性およびメッセージ受け渡しプロセスを通してサポートし得る機能お

10

20

30

40

50

および動作は種々様々であることが理解されよう。

たとえば、一実施形態では、MOVEメッセージを利用して、レジスタファイルアドレス空間内の演算子からデータを取得して、レジスタファイルアドレス空間を有するオペランド宛先にコピーする柔軟な機構を提供することができる。

複数のワードは連続アドレスからのものであってもよく、または、単一の間接アドレスを介して、構造内のインデックスに関連付けられたワードを指定することもできる。

【 0 1 0 1 】

別の実施形態では、MOVE LISTメッセージは、オペランドおよび演算子の間接アドレスの埋め込みリストを可能にする明示制御を提供することができる。

以下の表 7 に、かかるMOVE LIST (またはMVList) メッセージの例示的なフォーマットを提供する。 10

もちろん、他のメッセージおよび命令フォーマットも、本発明の範囲および精神に一致して提供することができる。

( 0 1 0 2 )

【表7】

| フィールド       | ビット  | 機能                                                                                                           |

|-------------|------|--------------------------------------------------------------------------------------------------------------|

| オペレーションカウント | 14:8 | フレキシブル：当業者により理解されるように定義される                                                                                   |

| オペレータカウント   | 6:0  | フレキシブル：当業者により理解されるように定義される                                                                                   |

| オペランドカウント   |      | フレキシブル：当業者により理解されるように定義される                                                                                   |

| MOP         | 2:2  | 0・MV-演算子からオペランドをロード<br>1・QGOレジスタファイルに格納されているサブルーチンにジャンプ；W<br>Qメッセージと同じ                                       |

| S           | 1:9  | オペランド間接アドレスもしくは完全なRFアドレスの構造／インデックス部分を選択。ind $\equiv$ 1かつindirect_address[31] $\equiv$ 0である場合かつその場合に限って当てはまる。 |

| S           | 1:7  | オペランド間接アドレスもしくは完全なRFアドレスの構造／インデックス部分を選択。ind $\equiv$ 1かつindirect_address[31] $\equiv$ 0である場合かつその場合に限って当てはまる。 |

| k           | 1:6  | k=0埋め込み演算子ワードは定数；演算子は間接規則子                                                                                   |

【 0 1 0 3 】

「演算カウント」、「オペランドデータカウント」、および「演算子データカウント」フィールドは、メッセージデータカウントから独立している。

オペランドカウントは、存在する場合、メッセージデータカウントと演算子カウントとの差によって推論することができる。

指定されない、すなわち 0 の場合には、デフォルトで 1 にすることができる。

1つの演算は、上述したように拡張される一連のオペランドに個々に適用される指示関数である。

指示されたように拡張される一連の演算子は、指示された演算回数を終えるために必要な分だけ繰り返すことができる。

アドレスがデータカウント > 1 を有し、かつアドレスが間接アドレスを参照する場合、データカウント連続アドレスを読み取って、データカウント間接アドレスにアクセスすることができる。

## 【0104】

ここでも、上記メッセージ構造は制限ではなく、機能は当業者によって理解される様々な方法で実施し得ることを当業者は理解するであろう。

## 【0105】

別の実施形態では、JUMPメッセージおよび関数を提供することができる。

かかるJUMPメッセージは、オペランドの最初のワードに対してプール条件を評価し、真の場合には、演算子ワードにより指示されるアドレスで置換するか、あるいは範囲 [-128..127] の埋め込み符号付き定数を附加することによって、スレッドプログラムカウンタを変更することができる。

以下の表8に、かかるJUMPメッセージの1つのフォーマットを示す。

10

## 【0106】

## 【表8】

| J{ZER NEG POS TRU NZR NNG NPS } |   |   |   |   |       |   |     |   |   |   |   |                 |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

|---------------------------------|---|---|---|---|-------|---|-----|---|---|---|---|-----------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|

| M                               | S | B |   |   |       |   |     |   |   |   |   |                 |   |   |   |   |   |   |   |   |   |   |   |   |   |   | L | S | B |   |   |  |

| 3                               | 3 | 2 | 2 | 2 | 2     | 2 | 2   | 2 | 2 | 2 | 1 | 1               | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |   |   |   |  |

| 1                               | 0 | 9 | 8 | 7 | 6     | 5 | 4   | 3 | 2 | 1 | 0 | 9               | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 1                               |   | 0 |   |   | JmpOP | S | Ind |   | 0 |   |   | Operand RF Addr |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

| 1                               |   | 0 |   |   | JmpOP | S | Ind | S | 1 |   |   | Operand RF Addr |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

| 1                               |   | 1 |   |   | JmpOP | S | Ind | S | k |   |   | Operand RF Addr |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

|                                 |   |   |   |   |       |   |     |   |   |   |   |                 |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

Operand RF Addr: オペランドRFアドレス

Signed Constant: 符号付き定数

Indirect Jump Addr: 間接ジャンプアドレス

Constant or Indirect: 定数または間接

AND Mask: ANDマスク

20

| フィールド | ビット   | 機能                                                                                                                                                                                                                                                                                                                                         |

|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JmpOP | 22:20 | ジャンプは、[-32..31] [-128..127] の範囲に関係する。最上位マスク解除ビットは符号。<br>0. J ZER-オペランドがゼロ ( $\equiv 0$ ) の場合にジャンプ<br>1. J NEG-オペランドが負 ( $< 0$ ) の場合にジャンプ<br>2. J POS-オペランドが正 ( $> 0$ ) の場合にジャンプ<br>3. J TRU-常にジャンプ<br>4. J NZR-オペランドが非ゼロ ( $\neq 0$ ) の場合にジャンプ<br>5. J NNG-オペランドが負ではない ( $\geq 0$ ) の場合にジャンプ<br>6. J NPS-オペランドが正ではない ( $\leq 0$ ) の場合にジャンプ |

30

## 【0107】

2つ以上の埋め込みデータワードが含まれる場合、JUMPは、JUMPテーブル（以下の表9参照）を形成することができ、JUMPテーブルは、選択されるオペランド解析規則および単一ワードアクションメッセージのリストである。

これは、メッセージヘッダのオペランド解析を容易にする。

オペランド解析規則は、オペランドワードの一部を選択して、指定範囲内にあるかどうかをチェックする。

範囲内にある場合、オペランドワードの第2の部分に対してオフセットおよびクランピングが行われ、JUMPテーブルに索引付けられる。

一実施形態では、enable = (range0 (operand & mask0) range1); select = (operand & mask2) - range2; if (enable && (select range3)) execute\_table[select]; otherwise execute\_table[range3 + 1]; operation\_table[select]において、selectは、mask2内の0に対応するあらゆるビットを右シフトすることによって統合される。

DataCountは、(range3 - range2 + 2) であることができる。

40

50

【 0 1 0 8 】

【表9】

| M | JUMP Table    |       |   |     |      |                        |   |   |   |                     |   |   |   |           |   |   |   |   | L |

|---|---------------|-------|---|-----|------|------------------------|---|---|---|---------------------|---|---|---|-----------|---|---|---|---|---|

| S | JUMP テーブル     |       |   |     |      |                        |   |   |   |                     |   |   |   |           |   |   |   |   | S |

| B |               |       |   |     |      |                        |   |   |   |                     |   |   |   |           |   |   |   |   | B |

| 3 | 3             | 2     | 2 | 2   | 2    | 2                      | 2 | 2 | 2 | 2                   | 2 | 1 | 1 | 1         | 1 | 1 | 1 | 1 | 1 |

| 1 | 0             | 9     | 8 | 7   | 6    | 5                      | 4 | 3 | 2 | 1                   | 0 | 9 | 8 | 7         | 6 | 5 | 4 | 3 | 2 |

| 1 | Data Count >1 | TblOP | S | ind | Jind | Operand RF Addr        |   |   |   | Operator RF Address |   |   |   |           |   |   |   |   |   |

|   | データカウント       |       |   |     |      | Message_w_0DC[0]       |   |   |   |                     |   |   |   | 演算子RFアドレス |   |   |   |   |   |

|   |               |       |   |     |      | Message_w_0DC[range]   |   |   |   |                     |   |   |   |           |   |   |   |   |   |

|   |               |       |   |     |      | Message_w_0DC[range+1] |   |   |   |                     |   |   |   |           |   |   |   |   |   |

Operand RF Addr: オペランドRFアドレス

## フィールド ビット

| Field | Bits              | Function 機能                                                 |         |          |            |       |        |        |  |

|-------|-------------------|-------------------------------------------------------------|---------|----------|------------|-------|--------|--------|--|

| TbIOP | 22:20             | Executes 1 word message (dc=0) selected by indicated rules. |         |          |            |       |        |        |  |

|       |                   | mask 0                                                      | range 0 | range1   |            | mask2 | range2 | range3 |  |

| 0     | T                 | 0                                                           | 0       | 0        | $2^m$      | op[0] | 0      | mask2  |  |

| 1     | $\neq$<br>0       | op[0]                                                       | 1       | $\sim 0$ | $2^m$      | op[1] | 0      | mask2  |  |

| 2     | $\equiv$          | op[0]                                                       | op[1]   | range0   | $2^m$      | op[2] | 0      | mask2  |  |

| 3     | $\leftrightarrow$ | op[0]                                                       | op[1]   | op[2]    | $2^m$      | op[3] | 0      | mask2  |  |

| 4     | $\leftrightarrow$ | op[0]                                                       | op[1]   | op[2]    | 1          | 0     | 0      | 0      |  |

| 5     | T                 | 0                                                           | 0       | 0        | $\leq 2^m$ | op[0] | op[1]  | op[2]  |  |

| 6     | $\equiv$          | op[0]                                                       | op[1]   | range0   | $\leq 2^m$ | op[2] | op[3]  | op[4]  |  |

| 7     | $\leftrightarrow$ | op[0]                                                       | op[1]   | op[2]    | $\leq 2^m$ | op[3] | op[4]  | op[5]  |  |

Excutes 1 word message (dc=0) selected by indicated rules.

指示される規則に従って選択される1ワードメッセージ (dc=0) を実行

注: 「m」=mask2に設定されるビット数

【 0 1 0 9 】

演算子は、示すように連續レジスタファイルアドレスにおけるワードのリストを関連付けることができ、共通関数の演算子を効率的に使用するために、非関連演算子は示すデフォルト値とことができる。

〔 0 1 1 0 〕

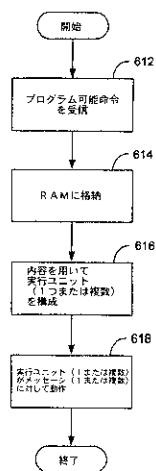

次に、本発明の一態様によるQNMのトップレベルの動作を示すフローチャートである図13を手短に参照する。

この点に関して、QNMは、ホスト等のリモートノードからプログラム可能命令（またはプログラム可能命令セット）を受け取るように構成される（ステップ612）。

次に、このプログラム可能命令（単数または複数）は、Q N M内のRAMに格納される（ステップ614）。

次いで、このプログラム可能命令の内容を使用して、特定のタスク、動作、または機能を実行するように Q N M 内の 1 つまたは複数の実行ユニットを構成することができる（ステップ 6 1 6 ）。

構成されると、実行ユニットは後に、Q N Mを通して渡されるメッセージに対してこれら指定のタスク、機能、および動作を行う（ステップ 6 1 8）。

QNMに送信されるプログラム可能命令の内容を変化させることにより、実行ユニットを介してのQNMの機能または演算を制御可能に再構成できることが理解されよう。

## 【図面の簡単な説明】

【図 1】従来技術によるコンピュータグラフィックスシステムのブロック図である。

【図 2】図 2 ( A ) および図 2 ( B ) は、機能ノードが直列リンクを通して相互接続された本発明による高レベルノードアーキテクチャを示す図である。

【図 3】ジオメトリアクセラレータと、ラスタライザと、ローカルRAMと通信するキャッシュとを含む機能ノードを示す図である。

【図 4】本発明の一実施形態によるマルチチップアーキテクチャでのノード構成を示す図である。

【図 5】本発明の一実施形態の單一ノードにて実現可能な様々な機能要素を示す図である。

【図 6】機能ユニットの演算の制御に使用される作業待ち行列を示すブロック図である。

【図 7】4つの並列ジオメトリアクセラレータおよび2つのシェーダを有するノードグラフィックスシステムを通しての例示的な作業待ち行列フローを示す図である。

【図 8】図 5 のノードと同様であるが、異なる機能ユニットを有するノードを示す図である。

【図 9】図 5 に示すものと同様のグラフィックスノードが使用可能な潜在的なメモリセグメント化方式の一例を示す図である。

【図 10】図 5 のノードと同様の複数のノードを有するシステムを示すと共に、ノード間のメッセージの受け渡しの概念を示す図である。

【図 11】図 5 のノードと同様の複数のノードを有するシステムを示すと共に、異なるノードを有する複数の作業待ち行列を示す図である。

【図 12】待ち行列ネットワークマネージャの特定の内部構成要素および機能特徴を示す図である。

【図 13】本発明の一実施形態により構築された待ち行列ネットワークマネージャのトップレベルの動作を示すフローチャートである。

## 【符号の説明】

2 0 . . . ホスト、

2 2 . . . ホストインターフェース、

2 4 . . . フォーマット、

3 8 . . . Zバッファ、

4 0 . . . 混合部、

5 0 . . . メモリ、

5 2 . . . 表示合成部、

5 4 . . . 表示タイミング部、

1 2 6 . . . キャッシュ、

1 7 8 . . . メッセージルーティング機構、

1 8 1 . . . ネットワークインターフェース、

1 8 2 . . . 待ち行列ネットワークマネージャ ( Q N M )

1 8 4 . . . 領域 H タイラ、

1 8 5 . . . ラスタライザ、

1 8 6 . . . シェーダ、

1 8 7 . . . Z / 混合部、

1 8 8 . . . キャッシュを備えたメモリコントローラ、

1 9 0 . . . 作業待ち行列、

1 9 2 . . . メッセージ、

1 9 4 . . . パケット、

2 0 2 . . . ホストインターフェース、

2 2 0 . . . ホストCPUドライバ、

2 2 2 . . . C / D バッファ、

2 3 0 . . . ホストインターフェースノード Q N M、

10

20

30

40

50

2 4 0 . . . 直列リンクネットワーク、

2 8 1 . . . ネットワークインターフェース、

2 9 0 . . . ホストインターフェースユニット、

1 8 0 . . . G A / R A ノード、

4 0 2 . . . ノード 1、

4 3 0 . . . ポインタ、

4 3 2 . . . ラスタライザ作業待ち行列、

4 4 0 . . . 作業待ち行列インターフェース (メッセージロジック)、

4 8 3 . . . ジオメトリアクセラレータ、

4 8 5 . . . ラスタライザ、

5 0 8 . . . 機能ユニットインターフェース、

5 1 4 . . . プログラム可能命令、

5 2 2 . . . 消費側機能ユニット、

5 2 4 . . . 制作側機能ユニット、

5 3 0 . . . コントローラ、

5 4 0 . . . 実行ユニット 1、

10

【図 1】

【図 2】

【図3】

【 四 4 】

【図5】

【 四 6 】

【図7】

【図8】

【図9】

【図10】

【図 1-1】

【図 1-2】

【図 1-3】