(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4197234号

(P4197234)

(45) 発行日 平成20年12月17日(2008.12.17)

(24) 登録日 平成20年10月10日(2008.10.10)

|              |                          |

|--------------|--------------------------|

| (51) Int.Cl. | F 1                      |

| HO 1 S 5/022 | (2006.01) HO 1 S 5/022   |

| HO 4 B 10/04 | (2006.01) HO 4 B 9/00 Y  |

| HO 4 B 10/06 | (2006.01) HO 1 L 31/02 C |

| HO 4 B 10/14 | (2006.01)                |

| HO 4 B 10/26 | (2006.01)                |

請求項の数 14 (全 31 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2002-84164 (P2002-84164)    |

| (22) 出願日     | 平成14年3月25日 (2002.3.25)        |

| (65) 公開番号    | 特開2003-258363 (P2003-258363A) |

| (43) 公開日     | 平成15年9月12日 (2003.9.12)        |

| 審査請求日        | 平成16年12月7日 (2004.12.7)        |

| (31) 優先権主張番号 | 特願2001-399654 (P2001-399654)  |

| (32) 優先日     | 平成13年12月28日 (2001.12.28)      |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000006013<br>三菱電機株式会社<br>東京都千代田区丸の内二丁目7番3号 |

| (74) 代理人  | 100089118<br>弁理士 酒井 宏明                     |

| (72) 発明者  | 渡辺 敏明<br>東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内       |

審査官 土屋 知久

最終頁に続く

(54) 【発明の名称】光通信器

## (57) 【特許請求の範囲】

## 【請求項 1】

底板に複数の突起が形成され、該複数の突起を当接させることによって複数のピン接続孔が形成された外部基板上に着座される筐体と、

前記筐体の底板から間隔をおいて支持されるように筐体内に収容され、光信号を入力もしくは出力するための回路デバイスおよび該回路デバイスに接続される基板線路を有する基板と、

該基板の下面に突設されて複数並べられ、一方端が前記基板線路に接続され、他方端が外部基板に形成された前記ピン接続孔に挿通固定される複数のインターフェースピンと、

を備えた光通信器において、

前記基板と同じ材料または基板と同程度の誘電率を有するとともに複数のピン貫通孔が形成され、前記基板の底面から前記外部基板までの間隔とほぼ等しい高さを有し、前記複数のピン貫通孔に前記複数のインターフェースピンが挿通される誘電体ブロックを備え、

前記筐体の底板に誘電体ブロックが挿通されるプロック貫通孔を設け、

前記複数のインターフェースピンが挿通された誘電体ブロックを、前記基板の底面から前記外部基板までの空間に介在させたことを特徴とする光通信器。

## 【請求項 2】

上記インターフェースピンは、信号ピンと、該信号ピンの周囲を囲む複数のグランドピンを含むことを特徴とする請求項 1 に記載の光通信器。

## 【請求項 3】

前記誘電体ブロックにおけるインターフェースピンが挿通されるピン貫通孔の周囲には、接地導体に接続された複数の第1のグランドスルーホールが形成されていることを特徴とする請求項1に記載の光通信器。

**【請求項4】**

上記信号ピンは、10GHzと同等もしくはそれ以上の速度の信号が伝送されることを特徴とする請求項2に記載の光通信器。

**【請求項5】**

前記基板には、前記複数のインターフェースピンの一方端が挿入される複数のピン孔が形成され、

前記基板のピン孔と前記外部基板のピン接続孔に挿通されるインターフェースピンの両端部は、前記誘電体ブロックで覆われたピンの部分の径よりも小さいことを特徴とする請求項1に記載の光通信器。 10

**【請求項6】**

前記グランドスルーホールに接続される接地導体は、前記誘電体ブロックにおける前記基板との当接面および前記誘電体ブロックにおける前記外部基板との当接面のうちの少なくとも一方に形成されることを特徴とする請求項3に記載の光通信器。

**【請求項7】**

前記インターフェースピンの誘電体ブロックに覆われた部分の特性インピーダンスは、略50であることを特徴とする請求項5に記載の接続体。

**【請求項8】**

前記基板は、前記誘電体ブロックにおけるインターフェースピンが挿通されるピン貫通孔の周囲に配置される複数の第1のグランドスルーホールと電気的に接続される複数の第2のグランドスルーホールを有することを特徴とする請求項3に記載の光通信器。 20

**【請求項9】**

前記基板には、前記複数のインターフェースピンの一方端が挿入される複数のピン孔が形成され、前記基板のピン孔に挿通されるインターフェースピンの端部は、前記誘電体ブロックで覆われたピンの部分の径よりも小さいものであり、

前記第2のグランドスルーホールは、前記第1のグランドスルーホールよりも前記インターフェースピンの中心軸側に近い側に配設されることを特徴とする請求項8に記載の光通信器。 30

**【請求項10】**

前記回路デバイスは、光半導体素子と、前記光半導体素子を駆動する電気回路とを含むことを特徴とする請求項1~9のいずれか一つに記載の光通信器。

**【請求項11】**

前記半導体素子がレーザダイオードまたは光変調器であり、前記電気回路がレーザダイオードまたは光変調器を駆動するドライバICであることを特徴とする請求項10に記載の光通信器。

**【請求項12】**

前記半導体素子がフォトダイオードであり、前記電気回路が前記フォトダイオードからの信号を再生する受信回路ICであることを特徴とする請求項10に記載の光通信器。 40

**【請求項13】**

隣接するインターフェースピン間に位置する第1のグランドスルーホールが隣接するインターフェースピンで共用されるように第1のグランドスルーホールを配置したことを特徴とする請求項3に記載の光通信器。

**【請求項14】**

複数の信号ピンおよび複数のグランドピンを交互に一列に配置し、前記誘電体ブロックにおける信号ピンが挿通されるピン貫通孔の周囲には、接地導体に接続された複数の第1のグランドスルーホールが形成され、

前記基板は、前記誘電体ブロックにおける複数の第1のグランドスルーホールと電気的に接続される複数の第2のグランドスルーホールを有することを特徴とする請求項2に記 50

載の光通信器。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

この発明は、インターフェースピンを介して信号伝送を行う光通信器に関するものである。

【0002】

【従来の技術】

光送受信器は、送信するデータ信号を電気信号から光信号に変換し、送信用の光ファイバを介して光信号を送信するとともに、受信用の光ファイバを介して光信号を受信し、受信した光信号を電気信号として再生するものである。この種の光送受信器を外部機器である上位システム装置（光伝送装置とも呼ばれる）の基板に取り付ける場合、コネクタを使わずに、筐体の底面から下向きに突出した複数のインターフェースピンを用いて上位システム装置のシステム基板に接続することで、電気的なインターフェースが取られる。インターフェースピンは、電源電圧、制御信号、高速パルス信号、高速クロック信号などの電源、クロック、信号を授受するのに利用される。なお、上位システム装置は、デジタルデータ信号を生成し、生成したデジタルデータ信号を複数の光送受信器に分配して送ったり、複数の送受信器から伝送されてきたデータ信号に対して種々の処理を行う。

10

【0003】

近年、光ファイバを介して光信号を伝送する光通信システムにおいては、インターネットの普及に伴なう通信トラフィックの増大に応えるため、光信号の伝送速度の高速化が目覚しく、光送／受信器においてもその伝送速度が2.5Gb/sから10Gb/sへと移行しつつあり、現在、40Gb/sの伝送速度の実現に向けて研究開発が進められている。これに伴ない、光送受信器の扱う信号の伝送速度についても、高速化が要求されている。

20

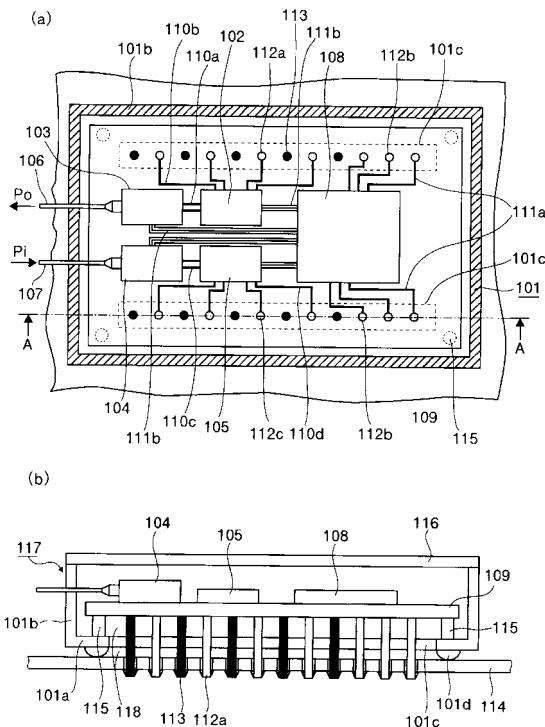

【0004】

図27に、従来の光送受信器の概略構成と、システム基板と光送受信器との間のインターフェース構造を示す。図27(a)は上蓋を外した状態の上面図、図27(b)はA-A線側断面図である。この図27は、2.5Gb/sのデータレートで信号伝送を行う光送受信器117の一例を示すものである。

【0005】

30

図27において、筐体101は、厚さ0.5～1mm程度の金属製の板材を、4方に折り曲げて成形されている。四角形状をした筐体101の底面101aの周囲4個所に筐体の側面を成す側壁101bが立設され、また底面101aの端部近傍には、インターフェース用の長孔101cが設けられている。さらに、筐体101の底面101aの裏面部には、突起101dが3箇所以上設けられている。複数の突起101dがシステム基板114に当接することによって、筐体101をシステム基板114に安定に着座させる。

【0006】

図27に示す光送受信器117では、基板109が筐体101内に収納され、筐体101の上面には上部の開口を覆う上蓋116が接合されている。基板109には、LDドライバ102と、レーザダイオード(LD)が設けられたLDモジュール103と、フォトダイオード(PD)が設けられたPDモジュール104と、PLL回路やデータ識別生成回路等を含む受信回路105と、電源回路や各種制御装置等を含む制御回路108とが搭載されている。LDモジュール103には送信用光ファイバ106が接続され、PDモジュール104には受信用光ファイバ107が接続されている。基板109は、筐体101の底面101aに立設された基板保持部材115によって支持されている。

40

【0007】

基板109には、基板線路110a(送信側)、110b(送信側)、110c(受信側)、110d(受信側)，111a，111bが形成されている。基板線路111aは低速用のインターフェースピン(図中のグレーの丸)112bと制御回路108とを接続するものであり、基板線路111bはLDドライバ102、LDモジュール103、PDモ

50

ジュー<sup>ル</sup> 1 0 4 および受信回路 1 0 5 のそれぞれと、制御回路 1 0 8 とを接続するものである。基板線路 1 1 0 a (送信側)、1 1 0 b (送信側)、1 1 0 c (受信側)、1 1 0 d (受信側)は、高周波信号を含むデータ信号やクロック信号を伝送することが可能なものである。また、基板 1 0 9 には、高周波信号を含むデータ信号やクロック信号を伝送することのできる 4 本～1 0 本程度の高速用のインターフェースピン (白丸) 1 1 2 a (送信側)、1 1 2 c (受信側) と、低周波の制御信号や、直流電圧が供給される低速用のインターフェースピン 1 1 2 b と、接地用のグランドピン (黒丸) 1 1 3 が接続固定されている。これらのインターフェースピン 1 1 2 a～1 1 2 c およびグランドピン 1 1 3 を介して、基板 1 0 9 が上位システム装置に設けられたシステム基板 1 1 4 に接続され、これにより光送受信器 1 1 7 と上位システム装置が信号の授受を行うことができる。

10

#### 【 0 0 0 8 】

ここで、インターフェースピン 1 1 2 及びグランドピン 1 1 3 は、基板 1 0 9 の長辺側の各端部に直線的に 1 列ずつ配置されており、筐体 1 0 1 に形成されたインターフェース用の長孔 1 0 1 c から下方に突出している。これらの各ピン 1 1 2、1 1 3 がシステム基板 1 1 4 に設けられたピン穴に挿入され、半田付けされることによって、コネクタを使うことなしに、基板 1 0 9 およびシステム基板 1 1 4 を接続することができる。

#### 【 0 0 0 9 】

また、基板保持部材 1 1 5 は、筐体 1 0 1 の底面 1 0 1 a の 4 隅に配置されている。各基板保持部材 1 1 5 は、一端が基板 1 0 9 に接合され、他端が筐体 1 0 1 の底面 1 0 1 a に固定されている。したがって、基板 1 0 9 と筐体 1 0 1 の底面 1 0 1 a との間に、数 mm の隙間が設けられている。この基板保持部材 1 1 5 は、基板 1 0 9 の裏面のパターン配線が金属製の筐体 1 0 1 の底面 1 0 1 a に接触しないようにするために、設けている。

20

#### 【 0 0 1 0 】

従来の光送受信器は次のように動作する。システム基板 1 1 4 から、インターフェースピン 1 1 2 a を通じて、2.5Gb/sのデータ信号 (パルス信号) 及び 2.5GHz のクロック信号が入力され、これらの信号は、基板線路 1 1 0 b を介して LD ドライバ 1 0 2 に伝送される。また、インターフェースピン 1 1 2 b および基板線路 1 1 1 a を通じて制御回路 1 0 8 に電源電圧や制御信号が供給される。

#### 【 0 0 1 1 】

30

LD ドライバ 1 0 2 は、2.5Gb/sのデータ信号及び 2.5GHz のクロック信号に基いて、LD モジュール 1 0 3 を駆動するための変調信号 Im (パルス信号) を生成する。LD ドライバ 1 0 2 で生成された変調信号 Im は、基板線路 1 1 0 a を介して LD モジュール 1 0 3 に伝送される。また、制御回路 1 0 8 は、LD ドライバ 1 0 2、LD モジュール 1 0 3、PD モジュール 1 0 4、及び受信回路 1 0 5 に対し、基板線路 1 1 1 b を介して直流電圧を供給したり、これら各機器のモニタを行う。これによって、LD モジュール 1 0 3 の LD が発光して、強度変調された光信号が出射される。出射された光信号は光ファイバ 1 0 6 の端面に入射されて、光ファイバ 1 0 6 内を光信号 Po が伝播される。

#### 【 0 0 1 2 】

また、PD モジュール 1 0 4 は、光ファイバ 1 0 7 を介して光信号 Pi を受信し、内蔵された PD で光信号を電流信号に光電変換した後、内蔵されたプリアンプによって電流信号を電圧信号に変換し、変換した電圧信号を基板線路 1 1 0 c を介して受信回路 1 0 5 に送信する。受信回路 1 0 5 は、PD モジュール 1 0 4 から送出された電圧信号に基いてクロックを抽出するとともに、データ信号を再生する。受信回路 1 0 5 で再生されたデータ信号及びクロック信号は、基板線路 1 1 0 d からインターフェースピン 1 1 2 c の一端に入力され、インピーダンス変換される。インターフェースピン 1 1 2 c の一端に入力された信号は、インターフェースピン 1 1 2 c を伝わって他端に接続されたシステム基板 1 1 4 に入力される。

40

#### 【 0 0 1 3 】

上記従来の光送受信器は、光信号の伝送速度の高速化に伴ない、次のような問題が発生す

50

る。

#### 【0014】

例えば、光送受信器とシステム基板114との間で、2.5Gb/sよりもレートの高い10Gb/sのデータ信号や、2.5GHzよりもレートの高い10GHzのクロック信号が送受信される場合には、基板線路110bとインターフェースピン112aの特性インピーダンス(一般に50Ω)あるいは基板線路110dとインターフェースピン112cの特性インピーダンス(一般に50Ω)を合わせておかないと、伝送特性が劣化し、高速信号を伝送することができないという問題がある。

#### 【0015】

従来の光送受信器においては、基板保持部材115の高さ、筐体101の底板101aの厚み、筐体101に設けられた突起101dの高さによって、基板109とシステム基板114との間に、2~5mm程度の空隙(ギャップ部)118が生じている。10

#### 【0016】

この空隙118の存在によって、基板109とシステム基板114との間に空気層が介在し、インターフェースピンの特性インピーダンスを基板線路110b, 110dの特性インピーダンス(一般に50Ω)に合わせることが、現実的には困難となっている。

#### 【0017】

したがって、従来の光送受信器では、10Gb/s程度以上の高速なデータ信号や、10GHz程度以上の高速なクロック信号を伝送する場合、伝送特性が劣化するという問題があった。この伝送特性の劣化は、ビットレートが2.5Gb/s程度のデータ信号までは、光送受信器を実用化する上で許容できる速度であるが、10Gb/s程度になると、伝送特性の劣化が顕著になり、無視し得なくなる。20

#### 【0018】

なお、インターフェースピンではなく、特性インピーダンスが管理されたインターフェースコネクタ(同軸コネクタなど)や、導波管等を用いた接続線路を使用すれば、電気的には好ましいインピーダンス特性が得られるが、データ信号とクロック信号の伝送に必要とされる接続線路の数は、4~10本程度必要であり、このような接続線路の使用は、インターフェース装置の大型化や、コストアップなどを招き、安価で大量設置が要求される光送受信器にとっては、現実的なものではない。

#### 【0019】

【発明が解決しようとする課題】30

このように従来の光送受信器では、10Gb/s程度のデータ信号や、10GHz程度のクロック信号をインターフェースピンで伝送させる場合、基板線路とインターフェースピンとの特性インピーダンスを合わせることが困難であるという問題点があった。

#### 【0020】

この発明は上記に鑑みてなされたもので、簡単且つ安価な構成によって基板線路とインターフェースピンとの特性インピーダンスを合わせることができ、データ信号、クロック信号の高速伝送を可能とする光通信器を得ることを目的とする。

#### 【0021】

【課題を解決するための手段】40

上記目的を達成するため、この発明では、底板に複数の突起が形成され、該複数の突起を当接させることによって複数のピン接続孔が形成された外部基板上に着座される筐体と、前記筐体の底板から間隔をおいて支持されるように筐体内に収容され、光信号を入力もしくは出力するための回路デバイスおよび該回路デバイスに接続される基板線路を有する基板と、該基板の下面に突設されて複数並べられ、一方端が前記基板線路に接続され、他方端が外部基板に形成された前記ピン接続孔に挿通固定される複数のインターフェースピンと、を備えた光通信器において、前記基板と同じ材料または基板と同程度の誘電率を有するとともに複数のピン貫通孔が形成され、前記基板の底面から前記外部基板までの間隔とほぼ等しい高さを有し、前記複数のピン貫通孔に前記複数のインターフェースピンが挿通される誘電体ブロックを備え、前記筐体の底板に誘電体ブロックが挿通されるブロック

貫通孔を設け、前記複数のインターフェースピンが挿通された誘電体ブロックを、前記基板の底面から前記外部基板までの空間に介在させたことを特徴とする。

#### 【0042】

##### 【発明の実施の形態】

以下に添付図面を参照して、この発明にかかる光通信器の好適な実施の形態を詳細に説明する。

#### 【0043】

##### 実施の形態1.

この発明の実施の形態1においては、光送受信器に設けられた基板20と、上位システム装置のシステム基板21との間の空隙23に誘電体ブロック22を配置し、インターフェースピン12a, 12cの特性インピーダンスを、基板線路10a, 10bの特性インピーダンスに整合させるインターフェース構造を用いることによって、インターフェースピン12a, 12cを介在させて、10Gb/sのデータ伝送および10GHzのクロック伝送を具現化するものである。 10

#### 【0044】

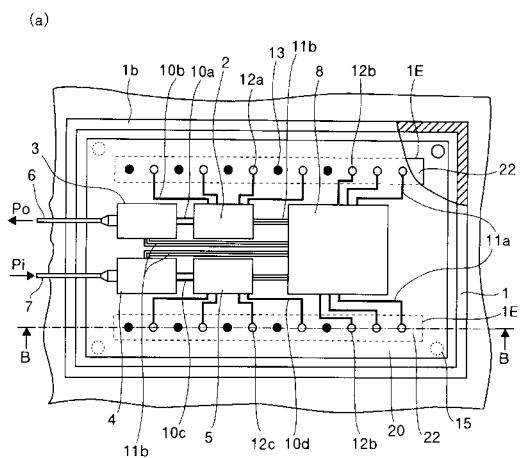

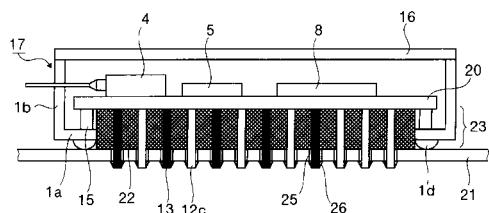

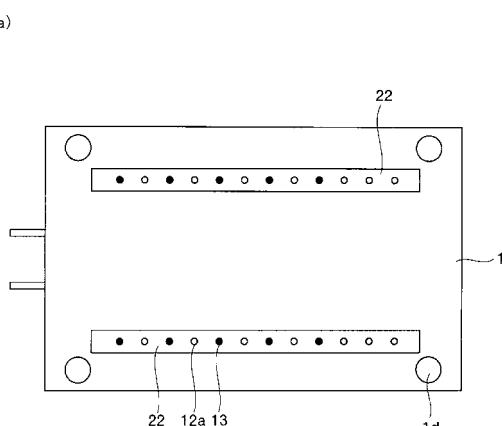

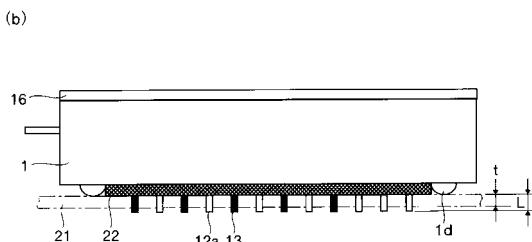

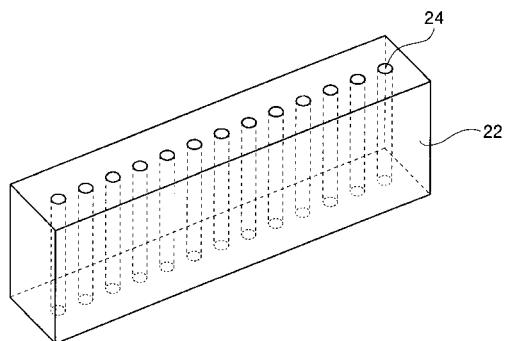

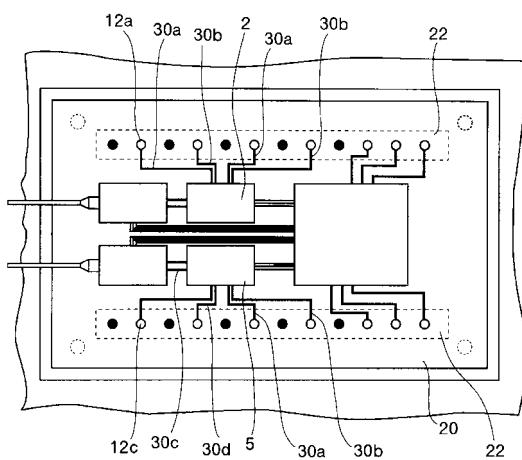

図1はこの発明の実施の形態1における光送受信器とシステム基板との接続構造を示す構成図であり、図1(a)は上蓋を外した状態の上面図、図1(b)はB-B線の側断面図である。また、図2はシステム基板21と接続される前の実施の形態1の光送受信器を示す図であり、図2(a)は下面図、図2(b)は側面図である。また、図3は誘電体ブロックの斜視図である。 20

#### 【0045】

図1および図2において、光送受信器17の筐体1は、厚さ0.5~1mm程度の金属製の板材を、4方に折り曲げて成形されている。四角形状をした筐体1の底面1aの周囲4箇所には、筐体の側面を成す側壁1bが立設されており、さらに、筐体1の底面1aの裏面には、突起1dが3箇所以上(この場合は4個)設けられている。複数の突起1dがシステム基板21に当接することによって、筐体1をシステム基板21に安定に着地させる。この突起1dは、ゴムなどの弾性体やバネ性を有する金属部品であっても良い。筐体1の底面1aには、後述する誘電体ブロック22を下方に突出させるための四角形状の孔1eが形成されている。 30

#### 【0046】

この光送受信器17においては、基板20が筐体1内に収納され、筐体1の上面には上部の開口を覆う上蓋16が接合されている。基板20には、LDドライバ2と、レーザダイオード(LD)が設けられたLDモジュール3と、フォトダイオード(PD)が設けられたPDモジュール4と、PLL回路やデータ識別生成回路等を含む受信回路5と、電源回路や各種制御装置等を含む制御回路8とが搭載されている。LDモジュール3には送信用光ファイバ6が接続され、PDモジュール4には受信用光ファイバ7が接続されている。基板20は、筐体1の底面1aに立設された基板保持部材15によって支持されている。基板保持部材15は、筐体1の底面1aの4隅に配置されている。各基板保持部材15は、一端が基板20に接合され、他端が筐体1の底面1aに固定されている。 40

#### 【0047】

基板20には、基板線路10a(送信側)、10b(送信側)、10c(受信側)、10d(受信側), 11a, 11bが形成されている。基板線路11aは低速用のインターフェースピン(グレーの丸)12bと制御回路8とを接続するものであり、基板線路11bはLDドライバ2、LDモジュール3、PDモジュール4および受信回路5のそれぞれと、制御回路8とを接続するものである。基板線路10a(送信側)、10b(送信側)、10c(受信側)、10d(受信側)は、高周波信号を含むデータ信号やクロック信号を伝送することが可能なものであり、例えば差動伝送線路で構成される。

#### 【0048】

また、基板20には、高周波信号を含むデータ信号やクロック信号を伝送することができる4本~10本程度の高速用のインターフェースピン(白丸)12a(送信側), 12c 50

(受信側)と、低周波の制御信号や、直流電圧が供給される低速用のインターフェースピン12bと、接地用のグランドピン(黒丸)13が接続固定されている。これらのインターフェースピン12a～12cおよびグランドピン13を介して、基板20が上位システム装置に設けられたシステム基板21に接続され、これにより光送受信器17と上位システム装置が信号の授受を行うことが可能となる。

#### 【0049】

インターフェースピン12aは基板線路10bを介してLDドライバ2に接続され、インターフェースピン12cは基板線路10dを介して受信回路5に接続されている。インターフェースピン12bは基板線路11aを介して制御回路8と接続される。これらインターフェースピン12a、12b、12cは、同一形状を成し、その本数は合わせて数十本程度になる。10

#### 【0050】

ここで、インターフェースピン12及びグランドピン13は、基板20の長辺側の各端部に直線的に1列ずつ配置されており、基板20から下方に垂直に突出している。これら2列のインターフェースピン12及びグランドピン13を挿入して、これらのピン12, 13周囲を覆うために、基板20の裏面には、直方体形状で上下面が平坦な一对の誘電体ブロック22が固定されている。誘電体ブロック22には、図3に示すように、インターフェースピン12およびグランドピン13の挿入用の複数の孔24が設けられており、これらの孔24に、インターフェースピン12およびグランドピン13が挿入される。インターフェースピン12およびグランドピン13が孔24に挿入された状態で、誘電体ブロック22の上面が基板20の裏面に接合される。また、各インターフェースピン12およびグランドピン13は、誘電体ブロック22が基板20の下面に当接した状態で、誘電体ブロック22の下面から垂直に僅かに突出するようにしている。その突出した長さLは、システム基板21の板厚tよりも長い(図2(b)参照)。20

#### 【0051】

インターフェースピン12がシステム基板21に設けられたインターフェースピン12の挿入用の孔25に挿入されると、誘電体ブロック22の下面是システム基板21の上面に当接する。すなわち、誘電体ブロック22の高さ寸法は、基板20の下面とシステム基板21の上面との間のギャップ部23に対応している。また、システム基板21の孔25の内周には導体がメタライズされており、この導体がシステム基板21に形成された基板線路に接続されている。インターフェースピン12がシステム基板21に挿入された状態で、インターフェースピン12は半田26によってシステム基板21の孔25に半田接合される。半田26はシステム基板21の下側に盛られて、インターフェースピン12の先端部周辺を接合し、これによって光送受信器17をシステム基板21に固定することができる。30

#### 【0052】

上記実施の形態1の光送受信器17は、インターフェースピン12を介して10Gb/sデータ信号、及び10GHzクロック信号が次のように伝送される。

#### 【0053】

##### [送信器動作]

まず、送信器動作を行う場合、システム基板21から送信された10Gb/sデータ信号及び10GHzクロック信号は、インターフェースピン12aに入力される。これらの信号は、インターフェースピン12aから基板線路10bに伝送される。40

#### 【0054】

光送受信器17の基板20とシステム基板21との間には、基板20と同じ材料、あるいは基板20と同程度の誘電率を有する誘電体ブロック22(例えば、誘電率=4.3の樹脂材料(例えばBTレジン))が配置されている。これによって、インターフェースピン12aの特性インピーダンスが、基板線路10bの特性インピーダンスと概ね合致し、10Gb/sデータ信号及び10GHzクロック信号は、伝送特性の劣化が抑えられて基板線路10bに伝送される。この伝送された信号はLDドライバ2に入力される。50

## 【0055】

L D ドライバ 2 は、入力された 1 0 Gb/s データ信号及び 1 0 GHz クロック信号に基いて、L D モジュール 3 を駆動するための、所定の振幅に調整された 1 0 Gb/s の変調信号 I m (パルス信号) を生成する。L D ドライバ 2 で生成された変調信号 I m は、基板線路 1 0 a を介して L D モジュール 3 に伝送される。また、制御回路 8 は、L D ドライバ 2 、L D モジュール 3 、P D モジュール 4 、及び受信回路 5 に対し、基板線路 1 1 b を介して直流電圧を供給したり、これら各機器のモニタを行う。L D モジュール 3 は、変調信号 I m と制御回路 8 から供給される直流電圧 I b (バイアス信号) を重畠し、この重畠された信号に基いて、内部に設けられた L D を駆動する。これによって、L D モジュール 3 の L D が発光して、強度変調された光信号が出射される。この出射された光信号は光ファイバ 6 の端面に入射されて、光ファイバ 6 内を光信号 P o が伝播される。

10

## 【0056】

## [受信器動作]

次に、光送受信器 1 7 が、システム基板 2 1 に対して 1 0 Gb/s データ信号及び 1 0 GHz クロック信号を出力する場合について説明する。

## 【0057】

この場合、光ファイバ 7 から P D モジュール 4 に入力された光信号 P i は、P D モジュール 4 に内蔵された P D によって電流信号に変換され、また内蔵されたプリアンプで電圧信号に変換されて出力される。この出力された電圧信号は、基板線路 1 0 c を介して受信回路 5 に入力される。受信回路 5 は、P D モジュール 4 から送出された電圧信号の振幅を調整し、内部に設けられた P L L 回路の動作によって、P D モジュール 4 から送出された電圧信号からクロックを抽出し、また、内部に設けられた識別再生回路によってデータ信号を識別し、1 0 Gb/s データ信号及び 1 0 GHz クロック信号を再生する。この再生されたデータ信号及びクロック信号が基板線路 1 0 d に出力される。基板線路 1 0 d は、この信号をインターフェースピン 1 2 c に出力する。

20

## 【0058】

基板 2 0 とシステム基板 2 1 との間のギャップ部 2 3 には、基板 2 0 と同じ材料、あるいはシステム基板 2 1 と同程度の誘電率を有する誘電体ブロック 2 2 が充填されている。これによって、基板線路 1 0 d とインターフェースピン 1 2 c との特性インピーダンスが概ね合致し、1 0 Gb/s データ信号、及び 1 0 GHz クロック信号は伝送特性の劣化が抑えられた状態で、データ信号及びクロック信号がシステム基板 2 1 まで伝送される。

30

## 【0059】

ここで、実施の形態 1 によるインターフェース構造と従来のインターフェース構造との違いを説明するために、図 2 7 に示した従来のインターフェース構造によるインピーダンス特性の劣化について説明する。

## 【0060】

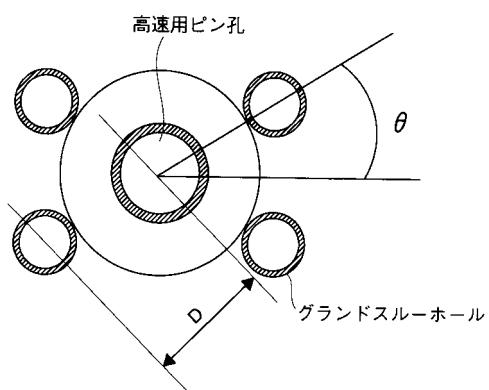

図 2 7 の従来のインターフェース構造では、インターフェースピン 1 1 2 の周囲には空隙が設けられ、インターフェースピン 1 1 2 の周囲は空気 (誘電率 ;  $\epsilon = 1$  ) で覆われている。このため、例えばインターフェースピン 1 1 2 a (または 1 1 2 c ) とグランドピン 1 1 3 のピッチ D が 2 . 5 4 mm 、各ピンの直径 d が 1 . 2 7 mm である場合、下式 (1) によれば、特性インピーダンス Z が 1 0 4  $\Omega$  程度となる。したがって、この場合のインターフェースピン 1 1 2 a (または 1 1 2 c ) の特性インピーダンス Z は、基板線路 1 1 0 b , 1 1 0 d の特性インピーダンス ( 5 0  $\Omega$  ) に一致しなくなる。

40

## 【0061】

このため、1 0 Gb/s のデータ信号や、1 0 GHz のクロック信号の伝送特性が劣化し、伝送できなくなる。

## 【数 1】

$$Z = \frac{207}{\sqrt{\epsilon}} \bullet \log \left( 1.59 \bullet \frac{D}{d} \right) \dots \dots \text{式 (1)}$$

但し、 $\epsilon$  は誘電体ブロックの誘電率である。

#### 【0062】

これに対し、図 1 に示したこの実施の形態 1 によるインターフェース構造では、光送受信器 17 の基板 20 とシステム基板 21 間のギャップ部 23 に、光送受信器 17 の基板 20 と同じ材料、あるいは基板 20 と同程度の誘電率を有する誘電体ブロック 22 ( 例えれば  $\epsilon = 4.3$  の樹脂材料 ( 例えれば B T レジン ) ) を充填するため、式 ( 1 ) によると、特性インピーダンスが  $Z = 50$  となり、伝送特性の劣化を抑えることができる。 10

#### 【0063】

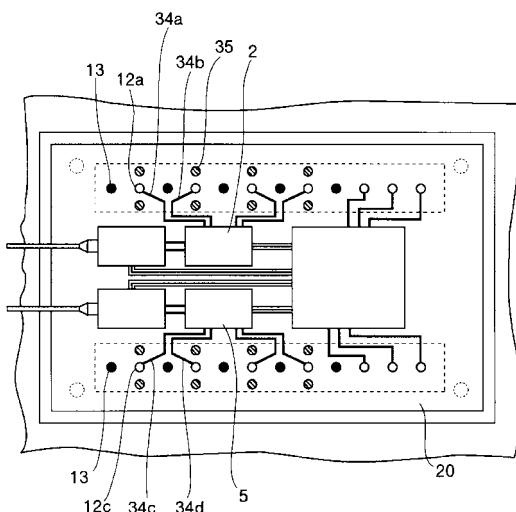

図 4 は、図 1 に示す実施の形態 1 の変形態様を示す平面図である。この変形態様においては、高速用のインターフェースピン 12a と LD ドライバ 2 とを接続する基板線路 30a, 30b と、高速用のインターフェースピン 12c と受信回路 5 とを接続する基板線路 30c, 30d を夫々正相、逆相の信号が伝送される差動線路としている。

#### 【0064】

このため、基板 20 上を伝送される信号がノイズに対して強くなり、インターフェースピン 12a と LD ドライバ 2 との間の信号伝送、あるいはインターフェースピン 12c と受信回路 5 との間の信号伝送によって、LD ドライバ 2 での信号処理でノイズの影響を受けたりあるいはシステム基板 21 での信号処理でのノイズの影響を受けることをさらに抑えることができる。なお、上述した各基板線路は、説明の都合上、基板表面に配置されているかの如く図示されているが、この配置や配線パターン形式に限定されるものではなく、例えば、多層基板の内層に設けるようにしてもよい。 20

#### 【0065】

実施の形態 2 。

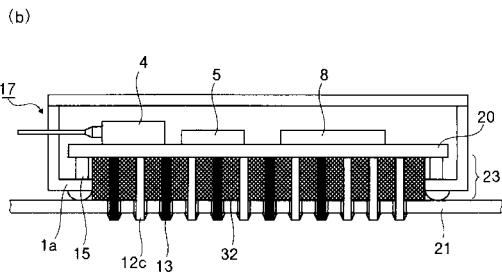

つぎに、図 5 および図 6 を用いてこの発明の実施の形態 2 について説明する。図 5 は実施の形態 2 における光送受信器とシステム基板との接続構造を示す構成図であり、図 5 ( a ) は蓋を外した状態の上面図、図 5 ( b ) は C - C 断面図である。図 5 において、図 1 に示す実施の形態 1 と同じ機能を達成する構成要素についての説明は省略する。 30

#### 【0066】

実施の形態 2 による光送受信器のインターフェース構造においては、基板 20 と上位システム基板 21 との間のギャップ部 23 に所定の誘電体ブロック 32 を配置するとともに、10Gb/s データ信号及び 10GHz クロック信号が通過するインターフェースピンの周囲に複数のグランドピン 31 を設け、これによりインターフェースピンと基板線路との特性インピーダンスを整合させ、10Gb/s データ信号及び 10GHz クロック信号の伝送の際の伝送特性の劣化を抑制するようにしている。

#### 【0067】

かかる実施の形態 2 の構成において、10Gb/s データ信号及び 10GHz クロック信号は次のように伝送される。 40

#### 【0068】

まず、光送受信器 17 がシステム基板 21 に対して 10Gb/s データ信号及び 10GHz クロック信号を伝送する場合は、受信回路 5 が 10Gb/s データ信号、及び 10GHz クロック信号を出力する。この出力信号が基板線路 10d に伝送されて、さらにインターフェースピン 12c に伝送される。

#### 【0069】

また、光送受信器 17 がシステム基板 21 から 10Gb/s データ信号、及び 10GHz クロック信号を受信する場合は、システム基板 21 からの 10Gb/s データ信号、10GHz クロック信号は、インターフェースピン 12a を介して基板 20 に入力される。さらに、インターフェースピン 12a から基板線路 10b に伝送路が変換された後、信号は基板 20 内を 50

伝送される。

**【 0 0 7 0 】**

ここで、この実施の形態 2においては、光送受信器の基板 20とシステム基板 21との間のギャップ部 23に、基板 20と同じ材料か、あるいは基板 20と同程度かさらにはそれよりも少し小さい誘電率を有する誘電体ブロック 32を配置して、基板線路 10とインターフェースピン 12aの特性インピーダンスを整合させている。これによって、10Gb/sデータ信号及び10GHzクロック信号は、伝送特性の劣化が抑えられて、インターフェースピン 12aから基板線路 10bへ伝送される。伝送された信号は LD ドライバ 2に入力される。

**【 0 0 7 1 】**

ここで、各インターフェースピン 12a(または 12c)が直線的に配置されている場合、一般に特性インピーダンスが基板線路より高くなりやすく、インターフェースピン 12a(または 12c)のピン径 d がピン間のピッチ D に比べて小さいと、ギャップ部 23を誘電体ブロック 32で充填しても、特性インピーダンスを基板線路の値に合わせることが困難になる場合がある。

**【 0 0 7 2 】**

したがって、この実施の形態 2においては、インターフェースピン 12a、12cの隣りのグランドピン 13の他に、インターフェースピン 12a、12cの周囲に複数のグランドピン 31を追加し、基板線路 10bとの特性インピーダンスを合わせるようにしている。

**【 0 0 7 3 】**

これによって、10Gb/sデータ信号、及び10GHzクロック信号は、伝送特性の劣化が抑えられて基板 20まで伝送される。これは、インターフェースピン 12a、12cのピン径 d がピン間のピッチ D に比べて小さいときに、特に有効である。

**【 0 0 7 4 】**

ピンのピッチ D = 2.54mm、ピンの直径 d = 1.27mm、特性インピーダンスを Z = 50 に指定して、インターフェースピン 12 の隣りにのみグランドピン 13 がある場合を考えると、下式(2)により誘電率 = 4.33 の誘電体ブロック 32 が必要になる。

**【 0 0 7 5 】**

それに対して、インターフェースピン 12 の隣りのグランドピン 13 の他に、インターフェースピン 12 の周囲に複数(この場合 4本)のグランドピン 31を追加した場合には、下式(3)が適用され、この場合、誘電率 = 3.1mm の誘電体ブロック 32 でよい。なお、各インターフェースピン 12 の周囲を囲むように、各インターフェースピンから等距離に 6本のグランドピン 31を配置した場合は、下の式を近似式として用いることができ、よりグランド能力を強化することができる。

**【 数 2 】**

$$d = \frac{D \bullet 1.59}{10^{\left( Z \bullet \frac{\sqrt{\epsilon}}{207} \right)}} \quad \dots \dots \text{式 (2)}$$

**【 数 3 】**

$$d = \frac{1.14 \bullet \sqrt{2}}{10^{\left( Z \bullet \frac{\sqrt{\epsilon}}{173} \right)}} \bullet D \quad \dots \dots \text{式 (3)}$$

但し、式(3)において、D はインターフェースピン 12 とグランドピン 31とのピッチである。

10

20

30

40

50

**【 0 0 7 6 】**

誘電体ブロック 3 2 を挟んだだけの場合と、誘電体ブロック 3 2 を挟んだ上でインターフェースピン 1 2 の周囲にグランドピン 3 1 を設けた場合の、どちらであっても、特性インピーダンスを  $Z = 50 \Omega$  にできるが、インターフェースピン 1 2 の周囲にグランドピン 3 1 を追加した場合の方が、ギャップ部 2 3 に充填する誘電体ブロック 3 2 の誘電率を下げることができるため、誘電体ブロックの基板コストを下げることが出来、より効果的である。

**【 0 0 7 7 】**

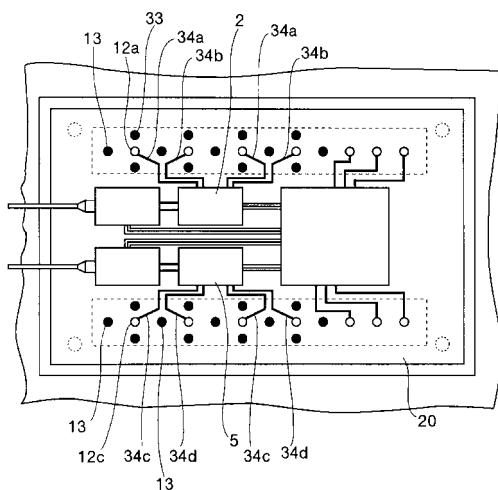

図 6 は、図 5 に示す実施の形態 2 の変形態様を示す平面図である。この変形態様においては、高速用のインターフェースピン 1 2 a と LD ドライバ 2 とを接続する基板線路 3 4 a , 3 4 b と、高速用のインターフェースピン 1 2 c と受信回路 5 とを接続する基板線路 3 4 c , 3 4 d とを、夫々正相、逆相の信号が伝送される差動線路としている。10

**【 0 0 7 8 】**

このため、基板 2 0 上を伝送される信号がノイズに対して強くなり、インターフェースピン 1 2 a と LD ドライバ 2 との間の信号伝送、あるいはインターフェースピン 1 2 c と受信回路 5 との間の信号伝送によって、LD ドライバ 2 での信号処理でノイズの影響を受けたりあるいはシステム基板 2 1 での信号処理でのノイズの影響を受けることをさらに抑えられることがある。

**【 0 0 7 9 】**

なお、図 6 の場合、インターフェースピン 1 2 a , 1 2 c の周囲に、グランドピン 1 3 とグランドピン 3 3 を共用して、等距離に 4 本のグランドピンを配置するようにしているが、差動線路 3 4 が対称を成して V 字形状に分かれ、それぞれのインターフェースピン 1 2 a , 1 2 c に接続される構成上、この方が望ましい。20

**【 0 0 8 0 】**

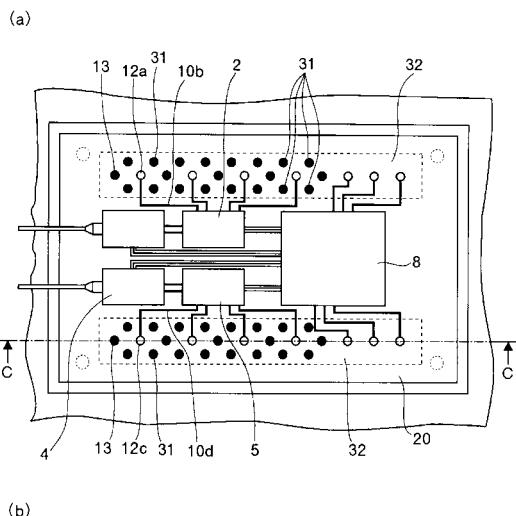

実施の形態 3 .

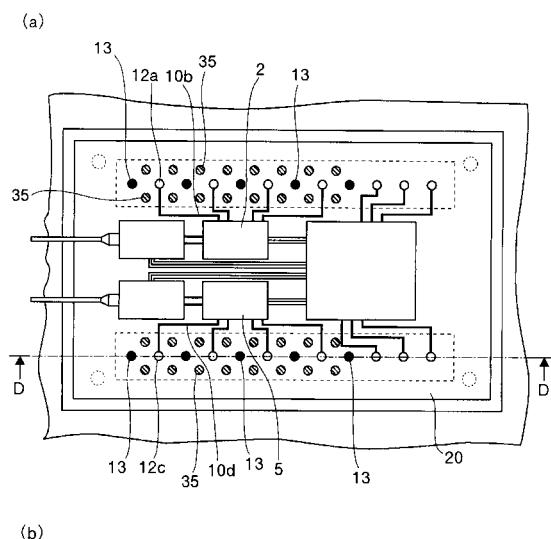

つぎに、図 7 および図 8 を用いてこの発明の実施の形態 3 について説明する。図 7 は実施の形態 3 における光送受信器とシステム基板との接続構造を示す構成図であり、図 7 ( a ) は蓋を外した状態の上面図、図 7 ( b ) は D - D 断面図である。図 7 において、図 1 に示す実施の形態 1 または図 5 に示す実施の形態 2 と同じ機能を達成する構成要素についての説明は省略する。30

**【 0 0 8 1 】**

実施の形態 3 においては、基板 2 0 とシステム基板 2 1 との間のギャップ部 2 3 に所定の誘電体ブロック 3 6 を配置するとともに、10Gb/sデータ信号及び10GHzクロック信号が通過するインターフェースピン 1 2 a , 1 2 c の周囲に、基板内層の接地導体に接続されている複数のグランドスルーホール 3 5 を配置し、これによりインターフェースピンと基板線路との特性インピーダンスを整合させ、10Gb/sデータ信号及び10GHzクロック信号の伝送の際の伝送特性の劣化を抑制する。

**【 0 0 8 2 】**

かかる実施の形態 3 の構成において、10Gb/sデータ信号及び10GHzクロック信号は次のように伝送される。40

**【 0 0 8 3 】**

まず、光送受信器 1 7 がシステム基板 2 1 に対して 10Gb/sデータ信号及び10GHzクロック信号を伝送する場合は、受信回路 5 が 10Gb/sデータ信号及び10GHzクロック信号を出力する。この出力信号が基板線路 1 0 d に伝送されて、さらにインターフェースピン 1 2 c に伝送される。

**【 0 0 8 4 】**

光送受信器 1 7 の基板 2 0 とシステム基板 2 1 の間のギャップ部 2 3 には基板 2 0 と同じ材料、あるいは基板 2 0 と同程度の誘電率を有する誘電体ブロック 3 6 を充填する。ここで、インターフェースピン 1 2 が直線状に配置されている場合、一般にインターフェースピン 1 2 の特性インピーダンスが基板線路より高くなりやすく、インターフェースピン 1

10

20

30

40

50

2のピン径がピン間のピッチに比べて小さいと、ギャップ部23を誘電体ブロック36で充填しても、特性インピーダンスを基板線路の値に合わせることが困難になる場合がある。

#### 【0085】

そこで、この実施の形態3においては、インターフェースピン12の周囲に複数のグランドスルーホール35を追加し、これら複数のグランドスルーホール35を基板上または基板内のベタグランドパターンと接続する。これにより、インターフェースピン12と基板線路10と特性インピーダンスを合わせる。したがって、10Gb/sデータ信号10GHzクロック信号は伝送特性の劣化が抑えられ、10Gb/sデータ信号10GHzクロック信号が特性劣化することなくシステム基板21まで伝送される。なお、グランドスルーホール35の高さは、誘電体ブロック36の高さと略同等である。10

#### 【0086】

次に、光送受信器17が10Gb/sデータ信号及び10GHzクロック信号をシステム基板21から受信する場合、システム基板21から伝送された10Gb/sデータ信号及び10GHzクロック信号が、インターフェースピン12aを介して基板20に伝送される。この信号は、インターフェースピン12aから基板線路10bに伝送線路が変換された後、基板20内を伝送される。

#### 【0087】

光送受信器17の基板20とシステム基板21との間には、基板20と同じ材料、あるいは基板20と同程度の誘電率を有する誘電体ブロックを充填し、さらにインターフェースピン12の周囲に複数のスルーホール35を追加しており、インターフェースピン12と基板線路10bとの特性インピーダンスが整合されている。したがって、10Gb/sデータ信号、及び10GHzクロック信号は、伝送特性の劣化が抑えられて基板線路10bに伝送される。伝送された信号はLDドライバ2に入力される。20

#### 【0088】

この実施の形態3では、スルーホールを用いてグランドを構成するため、実施の形態2と比べてよりコストを下げることができる。

#### 【0089】

図8は、図7に示す実施の形態3の変形態様を示す平面図である。この変形態様においては、高速用のインターフェースピン12aとLDドライバ2とを接続する基板線路34a, 34bと、高速用のインターフェースピン12cと受信回路5とを接続する基板線路34c, 34dとを、夫々正相、逆相の信号が伝送される差動線路としている。30

#### 【0090】

このため、基板20上を伝送される信号がノイズに対して強くなり、インターフェースピン12aとLDドライバ2との間の信号伝送、あるいはインターフェースピン12cと受信回路5との間の信号伝送によって、LDドライバ2での信号処理でノイズの影響を受けたりあるいはシステム基板21での信号処理でのノイズの影響を受けることをさらに抑えることができる。

#### 【0091】

実施の形態4。40

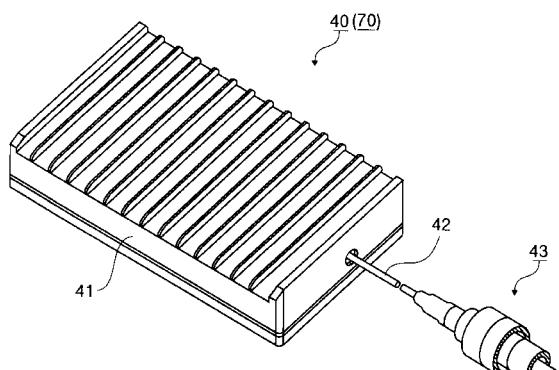

つぎに、図9～図19を用いてこの発明の実施の形態4について説明する。この実施の形態4は、光送信の機能のみを1つの筐体カバー内に搭載した光送信器40に関するものである。すなわち、この実施の形態4では、別体とした光送信器および光受信器のうちの光送信器を示している。

#### 【0092】

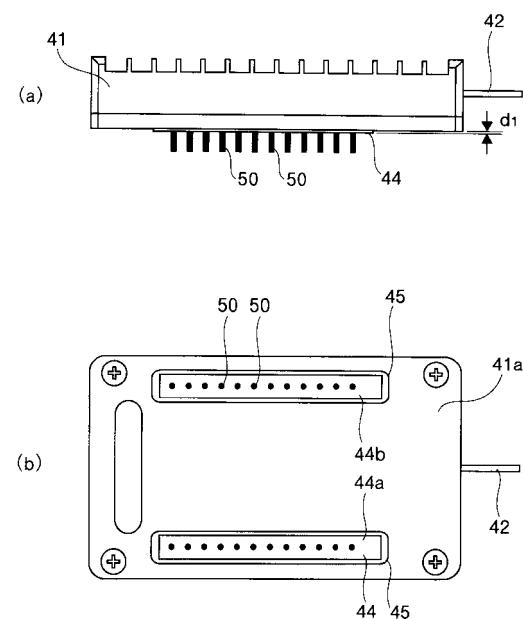

図9は光送信器40の外観構成を示す斜視図である。また、図10(a)は、光送信器40の外観構成を示す正面図であり、図10(b)がその下面図である。この光送信器40は上板にヒートシンクが取り付けられた金属製の矩形状の筐体カバー(ケース)41に、先の実施の形態1などに示した基板、誘電体ブロックなどが内蔵されている。ケース41の前面板から送信用光ファイバ42が突出されている。この送信用光ファイバ42にFC50

コネクタ（F01 単芯光ファイバに相当）、SCコネクタ（F04 単芯光ファイバに相当）などの光コネクタ43が接続される。ケース41の下板41aには、一対の誘電体ブロック44が挿入される一対の長孔45が下板41aの長辺側の端縁部に形成されている。図10(a)に示すように、ケース41の下面から長孔45を介して一対の誘電体ブロック44a, 44bが僅かの寸法d1(この場合は0.5mm)だけ下方に突出している。各誘電体ブロック44a, 44bからは、夫々12本のピン50が下方に突出している。

#### 【0093】

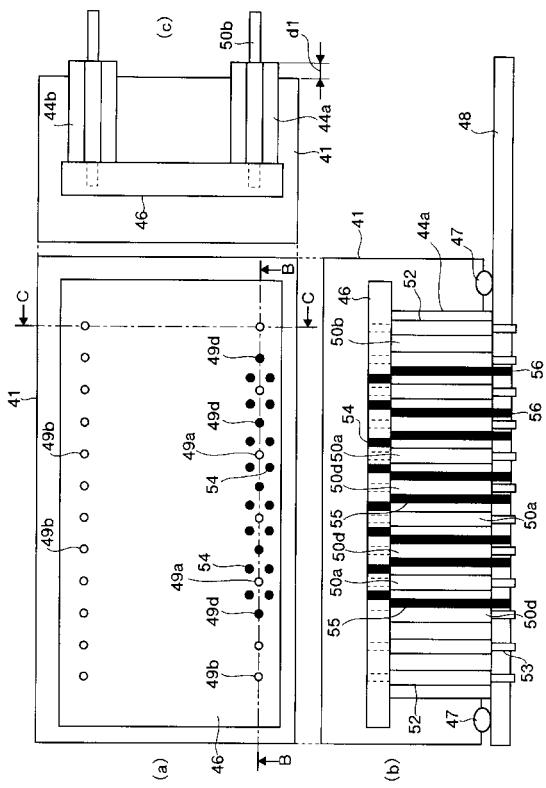

図11は、光送信器40とシステム基板48との接続構造を示す概略図であり、図11(a)はケース41の上板を外した状態の上面図、図11(b)はB-B断面図、図11(c)はC-C断面図である。また、図12は、内部基板46に、複数のピン50が挿入された一対の誘電体ブロック44a, 44bを装填した基板ユニットを示すものである。10

#### 【0094】

図11において、内部基板46(実施の形態1~3の基板20に対応)は、先の実施の形態1と同様、基板保持部材15(図示せず)によってケース41に支持固定されている。内部基板46には、前述したLDドライバと、レーザダイオード(LD)が設けられたLDモジュールと、電源回路や各種制御装置等を含む制御回路などのICが搭載されている。。

#### 【0095】

ケース41の下板41aの裏面には、弾性体あるいは金属などから成る複数の突起47が設けられている。複数の突起47がシステム基板48に当接することによって、ケース41をシステム基板48(実施の形態1~3のシステム基板21に対応)に安定に着座させている。このように、この実施の形態4の光送信器40においては、光送信器40とシステム基板48とは、複数の突起47と、誘電体ブロック44a, 44bの底面とで当接している。突起47が存在しない場合、ケース41の重量が全て誘電体ブロック44a, 44bを介して内部基板46に直接かかるようになり、これらの構造物の機械的強度に問題があるときには、突起47を削除しないほうがいい。しかし、ケース41、誘電体ブロック44、内部基板46間の機械的強度が強固な場合は、突起47を省略した構成としてもよい。20

#### 【0096】

内部基板46には、2個の誘電体ブロック44に設けられる12本のピン50(50a, 50b, 50d)が圧入固定される12個のピン孔49a, 49b, 49dが長辺側の各端縁部に形成されている。これらピン孔は、ほぼ等間隔に形成されている。30

#### 【0097】

図11(a)において、紙面の下方側に形成された4個の高速用ピン孔(白丸)49aには、前述した高周波信号を含むデータ信号(2本)やクロック信号(2本)を伝送するとのできる4本の高速用のインターフェースピン50aの一方の端部が圧入固定される。低速用ピン孔(グレー丸)49bには、低周波の制御信号や、直流電圧を供給するための低速用のインターフェースピン50bの一方の端部が圧入固定される。グランドピン孔(黒丸)49dには、接地用のグランドピン50dの一方の端部が圧入固定される。40

#### 【0098】

図11(a)において、下側に形成される12個のピン孔配列は、左側から見ると次のような順序になる。

- 2個の低速用ピン孔(グレー丸)49b

- 1個のグランドピン孔(黒丸)49d

- 1個の高速用ピン孔49a

- 1個のグランドピン孔(黒丸)49d

- 1個の高速用ピン孔49a

- 1個のグランドピン孔(黒丸)49d

- 1個の高速用ピン孔49a

- 1個のグランドピン孔(黒丸)49d

50

20

30

40

50

1 個の高速用ピン孔 4 9 a

1 個のグランドピン孔（黒丸）4 9 d

2 個の低速用ピン孔（グレー丸）4 9 b

#### 【 0 0 9 9 】

また、内部基板 4 6 には、各高速用ピン孔 4 9 a の周囲に、特性インピーダンスを整合するための 4 個のグランドスルーホール 5 4 が夫々形成されている。

#### 【 0 1 0 0 】

図 11 ( a )において、上側に形成される 12 個のピン孔配列には、低速用ピン孔（グレー丸）4 9 b とグランドピン孔（黒丸）4 9 d とが適宜混在されるが、本発明において特に重要でないので、全て低速用ピン孔（グレー丸）4 9 b として図示した。 10

#### 【 0 1 0 1 】

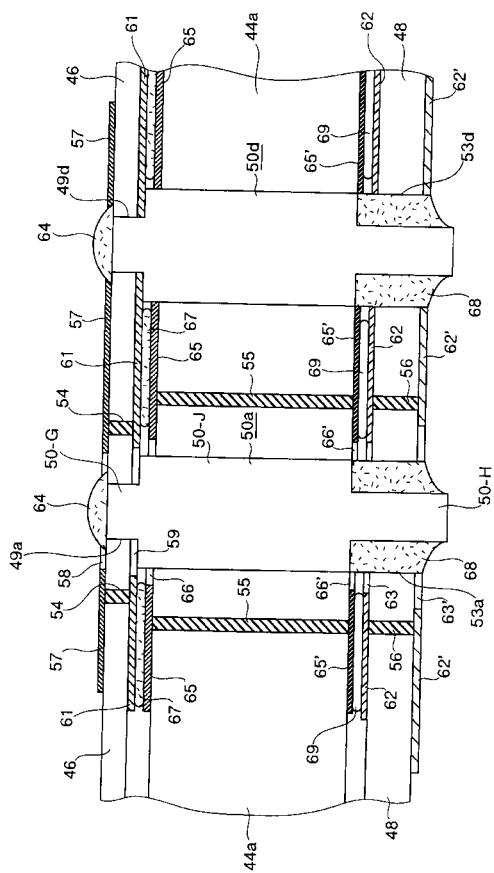

つぎに、各誘電体ブロック 4 4 a , 4 4 b には、高速用インターフェースピン 5 0 a , 低速用インターフェースピン 5 0 b およびグランドピン 5 0 d を挿入するための 12 個の孔 5 2 が夫々設けられており、これらの孔 5 2 に上記内部基板 4 6 でのピン配列に対応する並びで、高速用インターフェースピン 5 0 a 、低速用インターフェースピン 5 0 b およびグランドピン 5 0 d の太径部が挿入される。従って、各誘電体ブロック 4 4 a , 4 4 b でのピン数は、図 12 にも示すように、12 本となる。誘電体ブロック 4 4 a には、高速用インターフェースピン 5 0 a の周囲に、4 個のグランドスルーホール 5 5 が夫々形成されている。

#### 【 0 1 0 2 】

なお、各高速用インターフェースピン 5 0 a の全ての箇所での特性インピーダンス 5 0 を満足させるために、信号ピン 5 0 の径 d に応じて、グランドスルーホール 5 5 と高速用インターフェースピン 5 0 a とのピッチ間隔 D を変化させている。すなわち、誘電体ブロック 4 4 a , 4 4 b にはピン 5 0 の太径部が挿入され、また内部基板 4 6 にはピン 5 0 の細径の端部が挿入されるので、先の式(3)に従って、誘電体ブロック 4 4 a でのピン 5 0 と各グランドスルーホール 5 5 とのピッチを、内部基板 4 6 におけるピン 5 0 とグランドスルーホール 5 4 とのピッチよりも長く設定している。 20

#### 【 0 1 0 3 】

図 11 からも判るように、誘電体ブロック 4 4 a , 4 4 b は、ケース 4 1 の下面から僅かの寸法 d 1 だけ下方に突出している。ピン 5 0 の基板動作時の環境条件は、0 ~ 70 であり、またピン 5 0 の材質としては、内部基板 4 6 のピン孔 4 9 に圧入するのに適した材料が好ましい。ピン 5 0 には、金メッキが施されている。 30

#### 【 0 1 0 4 】

つぎに、システム基板 4 8 には、上記一対の誘電体ブロック 4 4 a , 4 4 b に内蔵される 12 本のピン 5 0 を挿入するための 12 個のピン孔 5 3 の列が 2 列形成されている。各ピン 5 0 の下端部は、誘電体ブロック 4 4 a , 4 4 b がシステム基板 4 8 に当接した状態のとき、システム基板 4 8 の下面から垂直に僅かに突出するような、長さに設定している。システム基板 4 8 においても、内部基板 4 6 と同様、高速用のインターフェースピン 5 0 a の他方の端部が挿入される 4 つのピン孔 5 3 の周囲には、4 個のグランドスルーホール 5 6 が夫々形成されている。システム基板 4 8 においては、各グランドスルーホール 5 6 の位置を誘電体ブロック 4 4 でのグランドスルーホール 5 5 の位置とほぼ同じ位置とする。その理由は後述する。 40

#### 【 0 1 0 5 】

このような誘電体ブロック 4 4 a , 4 4 b のピン 5 0 を介して内部基板 4 6 とシステム基板 4 8 が電気的に接続されることで、光送信器 4 0 と上位システム装置が信号の授受を行うことが可能となる。

#### 【 0 1 0 6 】

つぎに、内部基板 4 6 、誘電体ブロック 4 4 a , ピン 5 0 、システム基板 4 8 の詳細について順に説明する。

#### 【 0 1 0 7 】

10

20

30

40

50

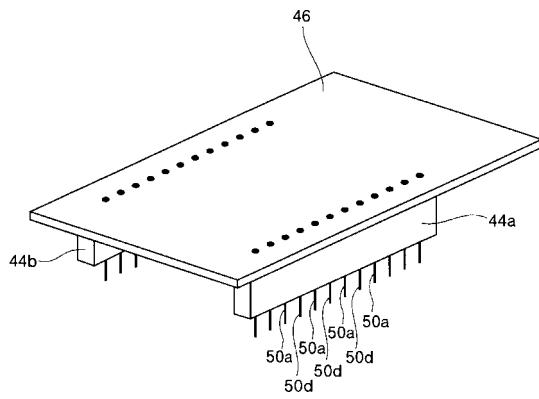

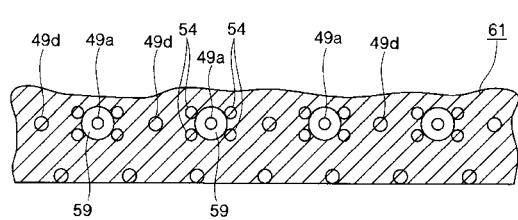

まず、図13および図14を用いて内部基板46について説明する。図13は内部基板46のおもて面を示す一部平面図であり、図14は内部基板46の裏面（誘電体ブロック44a, 44bとの当接面側）を示す一部平面図である。図13および図14においては、4個の高速用ピン孔49aの周辺部分の詳細について示している。

#### 【0108】

図13および図14に示すように、4個の高速用ピン孔49aの周囲には、前述したように、4個のグランドスルーホール54が夫々形成されている。図13に示すように、内部基板46のおもて面には、これら各グランドスルーホール54および5個のグランドピン孔49dを含むようにあってかつ4個の高速用ピン孔49aを避けるようにベタグランドパターン57（ハッチング部分）が形成されている。高速用ピン孔49aの周りには、その後の各ピン50に対する半田付けの際に、半田とベタグランドパターン57との接触を防ぐために、ソルダレジスト58が形成されている。10

#### 【0109】

内部基板46の裏面も同様であり、内部基板46の裏面には、図14に示すように、各グランドスルーホール54および5個のグランドピン孔49dを含みかつ4個の高速用ピン孔49aを避けるようにベタグランドパターン61（ハッチング部分）が形成されている。高速用ピン孔49aの周りには、ソルダレジスト59が形成されている。

#### 【0110】

4つの高速用ピン孔49aは、この場合、左から順に、正相のデータ信号用、逆相のデータ信号用、正相のクロック信号用、逆相のクロック信号用となっている。これら4つの高速用ピン孔49aは、基板線路を介してLDドライバ60に接続されている。LDドライバ60は、前述したように、入力されたデータ信号、クロック信号に基いて、LDモジュール（図示せず）を駆動するための変調信号Im（パルス信号）を生成する。20

#### 【0111】

この場合、LDドライバ60と4つの高速用ピン孔49aとの間の基板線路は、差動伝送線路90としている。差動伝送線路90は、ノイズ対策のために互いを出来るだけ近接させて電磁結合を発生させるようにしたものである。一方、高速用インターフェースピン50aは、シングルエンド（不平衡型）伝送路である。このため、これら高速用インターフェースピン50aが挿入される高速用ピン孔49aの間は、信号干渉が発生しないよう或る程度の間隔を確保する必要がある。30

#### 【0112】

したがって、差動伝送線路90と2組の高速用インターフェースピン50aとの間の接続部としてのパターン線路91は、間隔を大きく離すと共に、特性インピーダンスが50に近づくように、パターン幅drを差動伝送線路90のパターン幅dsよりも大きく（dr > ds）している。

#### 【0113】

なお、この場合、配線パターン線路91をほぼ直角に曲げているが、Y字形状などを利用して両者の間隔を徐々に離隔するようにしてもよい。また、パターン幅の変更の仕方も、反射特性の劣化が生じない限り急に細くなるようにしてもよいし、反射特性の劣化が生じる場合は徐々に細くなるようにしてもよい。また、グランドパターン57は、配線パターン線路91と接触しないようにU字型の切欠きを有している。40

#### 【0114】

また、配線パターン線路91の途中（図中Qの箇所）には、バイアス電圧をカットするためのコンデンサが設けられている。これらのコンデンサは、LDドライバ60に用いるバイアス電圧と、各線路の接続先であるシステム基板48上のICとのバイアス電圧との違いを考慮して挿入されており、これらコンデンサによってバイアス電圧をカットして電圧振幅信号をLDドライバ60に出力するようにしている。このため、両者のバイアス電圧が同じであれば、これらのコンデンサは不要である。

#### 【0115】

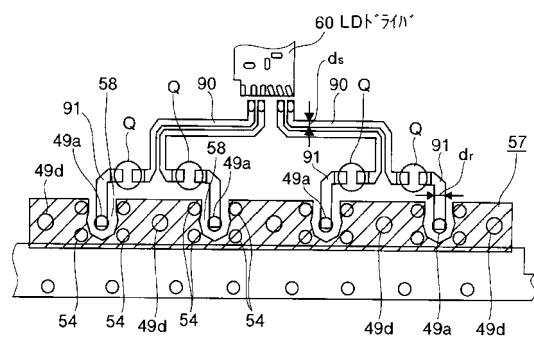

つぎに、図15を用いて、高速用インターフェースピン50aを内包している誘電体ブロ50

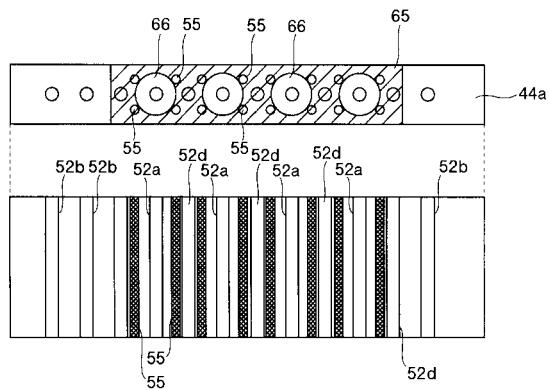

ック44aについて説明する。図15に示すように、誘電体ブロック44aには、4本の高速用インターフェースピン50aを挿入するための4個の高速用ピン孔52a, 3本の低速用インターフェースピン50bを挿入するための3個の低速用ピン孔52b, 5本のグランドピン50dを挿入するための12個のグランドピン孔52dが夫々設けられている。4個の高速用ピン孔52aの周囲には、前述したように、4個のグランドスルーホール55が夫々形成されている。

#### 【0116】

誘電体ブロック44aの上面および下面には、各グランドスルーホール55および5個のグランドピン孔52dを含むようにあってかつ4個の高速用ピン孔52aを避けるようにベタグランドパターン65(ハッチング部分)が形成されている。誘電体ブロック44aの上面および下面において、高速用ピン孔52aの周りには、その後の各ピン50aに対する半田付けの際に、半田とベタグランドパターン65との接触を防ぐために、ソルダレジスト66が形成されている。なお、各ピン孔52a, 52b, 52dは、キリ穴1.0mmとし、グランドスルーホール55は、0.6mmとしている。

10

#### 【0117】

誘電体ブロック44としては、たとえば次のような寸法を設定する。以下では、中心の高速用ピン孔52aとその周りのグランドスルーホール55とのピッチPmとして2種類設定している。また、筐体ケース41とシステム基板48の間に間隙を設け、この間隙に部品を配置する場合と、配置しない場合とで、2種類の長さの誘電体ブロック44を想定している。

20

#### 【0118】

ピッチPmが1.8mmまたは2.1mmで、間隙に部品配置しない場合、

高さ×幅×長さ(mm)は2.5×4.0×35.0

であり、

ピッチPmが1.8mmまたは2.1mmで、間隙に部品配置する場合、

高さ×幅×長さ(mm)は6.5×4.0×35.0

である。

#### 【0119】

この場合の、誘電率は、ピッチPmが1.8mmの場合は、3.75で、ピッチPmが2.1mmのときは、4.7となる。これらの誘電率は、先の(3)式に基づいて求めることができる。

30

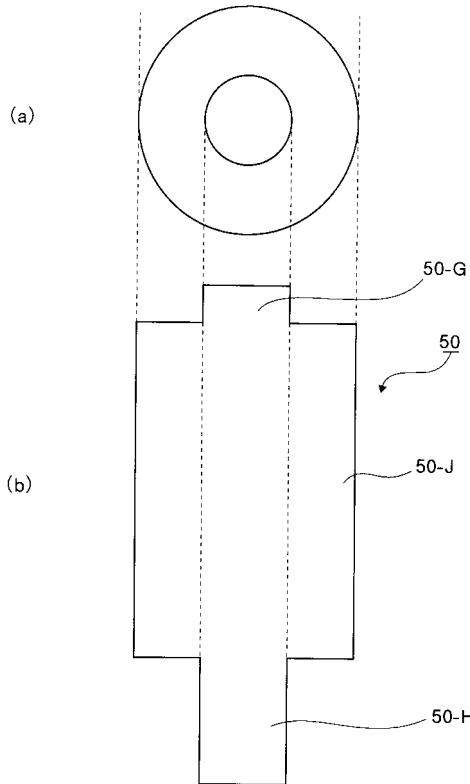

#### 【0120】

つぎに、図16を用いてピン50について説明する。内部基板46とシステム基板48を電気的に接続するためのピン50は、内部基板46のピン孔49に挿入される一方の端部50-Gおよびシステム基板48のピン孔に挿入される他方の端部50-Hが、誘電体ブロック44に挿入される部分(太径部)50-Jに比べ小径となっている。また、内部基板46に挿入される一方の端部50-Gのほうが他方の端部50-Hに比べ長さが短く設定されている。

#### 【0121】

ピン50の寸法は、例えば、つぎのように設定される。一方の端部50-Gは、径が0.46mm~0.51mmのテーパ形状で、高さが1.6mmである。他方の端部50-Hは、径が0.46mmで、高さが2.5mmである。なお、端部50-Gは端部50-Hより僅かに大径となっている。また、太径部50-Jは、長さが2.0mm~10mmであり、その径は、0.8mmである。筐体ケース41とシステム基板48の間に間隙を設け、この間隙に部品を配置する場合は、ピン50の太径部50-Jの長さが長く設定され、例えば6.5mmとする。また、前記間隙に特に部品を配置しない場合は、ピン50の太径部50-Jの長さは、例えば2.5mmとする。

40

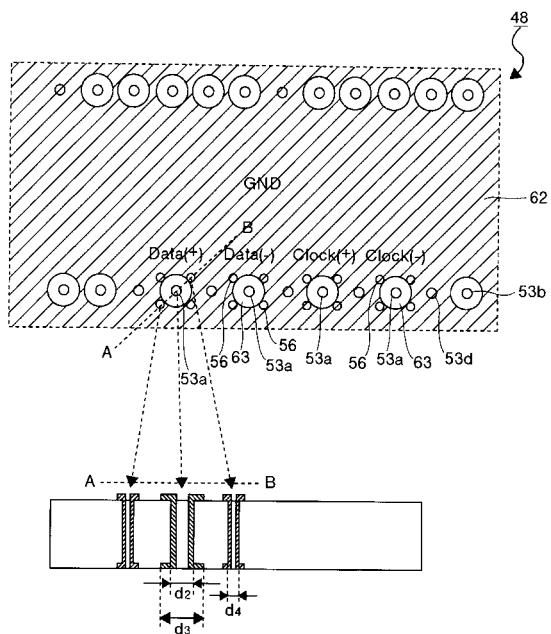

#### 【0122】

つぎに、図17に従ってシステム基板48について説明する。図17に破線で囲んだ領域は、システム基板48の全ての領域のうちの光送信器40を搭載する領域を示している。

50

この破線で囲んだ光送信器搭載領域に関しては、信号ピンが挿入されるピン孔以外の全ての領域あるいは信号ピンに接続される配線パターン部分を除く誘電体ブロック44a, 44bと当接する領域をおもて面および裏面ともベタグランド62とする。なお、コストなどを考慮した場合は、前者の全ての領域をベタグランドとするほうが好ましい。

#### 【0123】

図17に示すように、光送信器搭載領域の紙面下側には、誘電体ブロック44aに内蔵される12個のピン50が挿入される12個のピン孔53（高速用ピン孔53a, 低速用ピン孔53b, グランドピン孔53d）が形成されている。4個の高速用ピン孔53aの周囲には、前述したように、4個のグランドスルーホール56が夫々形成されている。高速用ピン孔53aや他のピン孔の周りには、その後の各ピン50に対する半田付けの際に、半田とベタグランドパターン62との接触を防ぐために、ソルダレジスト63が形成されている。このソルダレジスト63は、図中では円形としているが、ピンと接続される配線パターンが通過する部分では、図13に示すようにU字状となっていてもよい。

10

#### 【0124】

4つの高速用ピン孔49aは、この場合、左から順に、正相のデータ信号用、逆相のデータ信号用、正相のクロック信号用、逆相のクロック信号用となっている。このシステム基板48において、4個の高速用ピン孔53aの外形d2は、0.8mmとし、そのランクサイズd3は1.0mmとする。

#### 【0125】

すなわち、高速用ピン孔53aの外形d2は、高速用インターフェースピン50aの太径部50-Jの径とほぼ同じにしており、この0.8mmの外径をもつピン孔53aの周壁面と高速用インターフェースピン50aの0.46mmの径をもつ端部50-Hとの隙間に半田を充填することにより、高速用インターフェースピン50aの0.46mmの端部50-Hの径を高速用インターフェースピン50aの太径部50-Jの径と実質的に同じになるようにしておき、これによりこの部分の特性インピーダンスも50に保つようしている。

20

#### 【0126】

また、グランドスルーホール56の外径d4は0.6mmとする。高速用ピン孔53aとグランドスルーホール56とのピッチとしては、誘電体ブロック44aと同様、1.8mmまたは2.1mmの2種類が設定されている。

30

#### 【0127】

図18は、内部基板46、誘電体ブロック44aおよびシステム基板48における高速用ピン孔とその周りの4個のグランドスルーホールとの配置関係を示すものである。高速用ピン孔とグランドスルーホールとのピッチDは、特性インピーダンスを50に保つために所定値（この場合は、1.8mmまたは2.1mmの2種類）に設定されている。この設定ピッチを保ちつつ、かつインピーダンス特性を劣化させることなく、誘電体ブロック44aの幅を狭くしたり、各基板46, 48の実装密度を向上させることが要求される場合は、高速用ピン孔の並びに沿った線と、高速用ピン孔とグランドスルーホールを結ぶ直線とのなす角度θをインピーダンス特性にとって理想的な45°にするのではなく、θ=30°前後の値に設定すればよい。このようなθ=30°前後の値に設定すれば、インピーダンス特性に対する要求を満足させつつ誘電体ブロック44aの幅を狭くし、また各基板46, 48の実装密度を向上させることが可能となる。

40

#### 【0128】

つぎに、図19に従って、ピン50による内部基板46、誘電体ブロック44aおよびシステム基板48の接続構造を説明する。図19には、1本の高速用インターフェースピン50aと1本のグランドピン50dが示されている。

#### 【0129】

図19を用いて、まず内部基板46とピン50との接続構造について述べる。内部基板46のピン孔49a, 49dに対し、各ピン50a, 50dの端部50-Gが圧入されることにより内部基板46とピン50とが接続固定される。さらに、各ピン50a, 50dの

50

端部 50 - G の表面に半田 64 が付けられることで、内部基板 46 とピン 50 とが接続固定される。内部基板 46 のおもて面及び裏面の高速用ピン孔 49a の周囲には、半田 64 を盛るのに十分な大きさの領域を除いてソルダレジスト 58, 59 が形成されている。

#### 【 0130 】

このように内部基板 46 とピン 50 とを圧入および半田による固定構造とすることで、機械的な接続構造をより強固にしている。これは、内部基板 46 とピン 50 とを半田のみによる接続構造とすると、システム基板 48 の発熱が大きい場合、システム基板 48 からの熱がピン 50 を伝わって内部基板 46 の半田 64 に伝わり、内部基板 46 とピン 50 との接続強度が弱まるなどを防止するためである。なお、この熱が半田 64 に加わって、ピン 50 と配線パターン線路 91 との半田接続が切断されないように、ピン 50 から内部基板 46、誘電体ブロック 44 へ充分に熱が拡散するようにしつつシステム基板 48 の半田条件を適当な条件に設定しておく。

#### 【 0131 】

ピン 50 は、ピン孔に対する高さ方向への位置決めのために、その両端部を細径としている。また、前述したように、圧入接続を採用するためには、内部基板 46 のピン孔 49a, 49d としては、ピン 50 の細径の端部にほぼ一致する径を選択する必要がある。このため、高速用インターフェースピン 50a の端部 50 - G の部分の金属部分の径は他の部分よりも細くなり、他の部分とインピーダンスが異なるようになる。そこで、先の式(3)に従って、この部分のピンとグランドスルーホール 54 とのピッチを他の部分のピッチよりも短く設定することで、この部分の特性インピーダンスも 50 に保つようにしている。

#### 【 0132 】

内部基板 46 に形成されたグランドスルーホール 54 は、内部基板 46 のおもて面に形成されたベタグランドパターン 57 および裏面に形成されたベタグランドパターン 61 に接続されている。なお、グランドピン 50d に関しては、グランドピン 50d の端部自体が直接ベタグランドパターン 57 およびベタグランドパターン 61 に接続されている。

#### 【 0133 】

誘電体ブロック 44 に形成されたグランドスルーホール 55 も、誘電体ブロック 44 のおもて面に形成されたベタグランドパターン 65 および裏面に形成されたベタグランドパターン 65' に接続されている。これらベタグランドパターン 65, 65' は、ソルダレジスト 66, 66' によって高速用インターフェースピン 50a とは接触しないようになっている。誘電体ブロック 44 においても、グランドピン 50d に関しては、グランドピン 50d 自体が直接ベタグランドパターン 65, 65' に接続されている。

#### 【 0134 】

内部基板 46 の裏面のベタグランドパターン 61 と、誘電体ブロック 44 の上面のベタグランドパターン 65 とは半田 67 によって接合される。一方、誘電体ブロック 44 の下面のグランドパターン 65' にはソルダレジスト 69 が塗布されており、これにより、システム基板 48 側の配線パターン構造が不明のときに、システム基板 48 との予期せぬ電気的接触を防止している。

#### 【 0135 】

つぎにシステム基板 48 とピン 50 との接続構造について述べる。システム基板 48 と各ピン 50a, 50d との接合は半田 68 のみによって行われる。前述したように、高速用ピン孔 53a の外形 d2 は、高速用インターフェースピン 50a の太径部 50 - J の径とほぼ同じにしており、このピン孔 53a の周壁面と高速用インターフェースピン 50a の端部 50 - H との隙間に半田を充填させることにより、高速用インターフェースピン 50a の端部 50 - H の径を、太径部 50 - J の径と実質的に同じになるようにしてあり、これによりこの部分のインピーダンスを太径部と同じ 50 としている。

#### 【 0136 】

システム基板 48 に形成されたグランドスルーホール 56 は、システム基板 48 のおもて面に形成されたベタグランドパターン 62 および裏面に形成されたベタグランドパターン

10

20

30

40

50

62'に接続されている。システム基板48のおもて面及び裏面の高速用ピン孔53aの周囲には、ソルダレジスト63, 63'が形成されている。グランドピン50dに関しては、グランドピン50d自体がベタグランドパターン62およびベタグランドパターン62'に直接接続されている。

#### 【0137】

なお、誘電体ブロック44aの下面のグランドパターン65'およびシステム基板48の上面のグランドパターン62を、半田によって接合するようにしてもよい。また、システム基板48の表裏面に形成されるグランドパターン62, 62'を省略しても良い。また、システム基板48に挿入されるピン50の端部50-Hを太径部と同じ寸法の径にする場合は、この場合でも半田が充填される隙間を確保する必要があるので、グランドスルーホール56を、誘電体ブロック44aでのグランドスルーホール55の配置位置に比べ外側に配置するようにして、この部分のインピーダンスを他と同じにすればよい。10

#### 【0138】

このようにこの実施の形態4によれば、高速用インターフェースピンの特性インピーダンスが基板線路に整合され、これにより高速なデータ伝送またはクロック伝送を実現する光送信器を提供することができる。

#### 【0139】

実施の形態5.

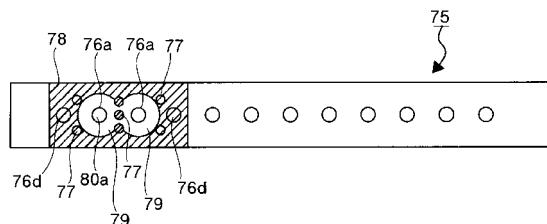

つぎに、図9を参照するとともに、図20～図23を用いてこの発明の実施の形態5について説明する。この実施の形態5は、光受信の機能のみを1つの筐体カバー内に搭載した光受信器70(図9参照)に関するものである。光受信器70においても、前述した光送信器40同様、内部基板と、誘電体ブロックと、内部基板とシステム基板とを接続するピンとから構成されている。ただし、光受信器70は、勿論内部基板に搭載されているICが光送信器40のものとは異なることの他に、光受信器70の場合には、内部基板上の受信回路から内部基板上の伝送線路およびピンを介して伝送される高速信号が正相および逆相のデータ信号の2本のみである。すなわち、この実施の形態5の光受信器では、クロック信号をシステム基板に送信してはいない。したがって、光受信器70については、主にこの正相および逆相の2本のデータ信号に関する構成について説明する。20

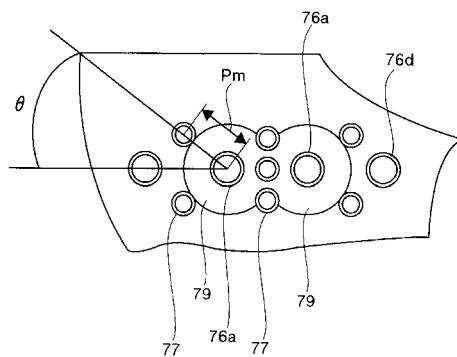

#### 【0140】

図20は、光受信器70の誘電体ブロック75の平面図を示すものである。図21はその一部拡大図である。誘電体ブロック75には、12本のピン孔が形成され、12本のピンが挿入される。そのうちの2本が正相および逆相のデータ信号に用いられる。30

#### 【0141】

誘電体ブロック75には、2本の高速用インターフェースピン80aを挿入するための2個の高速用ピン孔76aが設けられる。2個の高速用ピン孔76aに対し外側に隣接するピン孔は、グランドピン用のグランドピン孔76dである。2個の高速用ピン孔76aの周囲には、5個のグランドスルーホール77が夫々形成されている。ただし、2個の高速用ピン孔76aの間に3個のグランドスルーホール77は、2つの高速用インターフェースピン80aの特性インピーダンス調整のために共用されるグランドとなる。また、2個の高速用ピン孔76aの中心を結ぶ直線上に、1個のグランドスルーホール77を配し、これにより、2本の高速用インターフェースピン80aを伝送される信号の相互干渉を防止している。40

#### 【0142】

また、図21に示すように、高速用ピン孔同士を結ぶ直線と、高速用ピン孔とグランドスルーホールを結ぶ直線とのなす角度を30°前後の値に設定することで、インピーダンス特性に対する要求を満足させつつ誘電体ブロック75の幅を狭くして、実装密度を向上させている。

#### 【0143】

誘電体ブロック75の上面および下面には、各グランドスルーホール77および2個のグランドピン孔76dを含むようにかつ2個の高速用ピン孔76aを避けるようにグランド

10

20

30

40

50

パターン 7 8 (ハッチング部分)が形成されている。高速用ピン孔 7 6 a の周りには、ソルダレジスト 7 9 が形成されている。

【 0 1 4 4 】

各ピン孔 5 2 a , 5 2 b , 5 2 は、キリ穴 1 . 0 mm とし、グランドスルーホール 5 5 は、0 . 6 mm としている。

【 0 1 4 5 】

誘電体ブロック 7 5 としては、光送信器 4 0 の誘電体ブロック 4 4 と同様次のような寸法を設定する。中心の高速用ピン孔 7 6 a とその周りのグランドスルーホール 7 7 とのピッチを P m とする。

【 0 1 4 6 】

ピッチ P m が 1 . 8 mm または 2 . 1 mm で、筐体ケースとシステム基板との間隙に部品配置しない場合、

高さ × 幅 × 長さ (mm) は 2 . 5 × 4 . 0 × 3 5 . 0

であり、

ピッチ P m が 1 . 8 mm または 2 . 1 mm で、その間隙に部品配置する場合、

高さ × 幅 × 長さ (mm) は 6 . 5 × 4 . 0 × 3 5 . 0

である。

【 0 1 4 7 】

この場合の、誘電率は、ピッチ P m が 1 . 8 mm の場合は、3 . 7 5 で、ピッチ P m が 2 . 1 mm のときは、4 . 7 となる。但し、特性インピーダンス (5 0 ) を満足する誘電率に対して ± 1 . 3 程度の誘電率を選択すれば良く、例えば、P m = 1 . 8 mm で、3 . 4 8 に誘電率を設定しても良い。

【 0 1 4 8 】

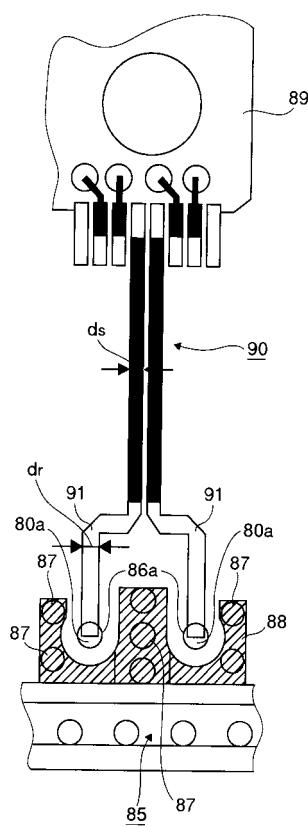

図 2 2 は、光受信器 7 0 に搭載される内部基板 8 5 における 2 つの高速用インターフェースピン 8 0 a の近傍の配線パターンを示す平面図である。

【 0 1 4 9 】

誘電体ブロック 7 5 に形成された 2 つの高速用ピン孔 7 6 a およびその周りの 5 つのグランドスルーホール 7 7 に対応するように、内部基板 8 5 にも、2 つの高速用ピン孔 8 6 a と 5 つのグランドスルーホール 8 7 が形成されている。5 つのグランドスルーホール 8 7 を囲むようにベタグランドパターン 8 8 が形成されている。

【 0 1 5 0 】

この 2 本の高速用ピン孔 7 6 a に挿入される 2 つの高速用インターフェースピン 8 0 a は、内部基板 8 5 上の基板線路を介して受信回路 I C 8 9 に接続される。受信回路 I C 8 0 は、P D モジュールから送出された電圧信号の振幅を増幅調整し、その電圧信号を基板線路を介して 2 本の高速用インターフェースピン 8 0 a に出力する。

【 0 1 5 1 】

受信回路 I C 8 9 の正相および逆相の 2 本の出力信号は、差動伝送線路 9 0 に出力される。一方、高速用インターフェースピン 8 0 a は、シングルエンド (不平衡型) 伝送路である。このため、これら高速用インターフェースピン 8 0 が挿入される高速用ピン孔 8 6 a の間は、信号干渉が発生しないように或る程度の間隔を確保する必要がある。したがって、差動伝送線路 9 0 と 2 組の高速用インターフェースピン 8 0 a との間の接続部としてのパターン線路 9 1 は、間隔を離すと共に、特性インピーダンスが 5 0 に近づくように、パターン幅 d r を差動伝送線路 9 0 のパターン幅 d s よりも大きく (d r > d s) している。なお、この場合も、配線パターン線路 9 1 をほぼ直角に曲げているが、Y 字形状などをを利用して両者の間隔を徐々に離隔するようにしてよい。また、パターン幅の変更の仕方も、急に細くなるようにしてよいし、徐々に細くなるようにしてよい。なお、シングルエンド伝送路の高速用インターフェースピン 8 0 a を介して伝送されたデータは、システム基板において、シングルエンド伝送路のままあるいは差動伝送線路に戻されて伝送される。

【 0 1 5 2 】

10

20

30

40

50

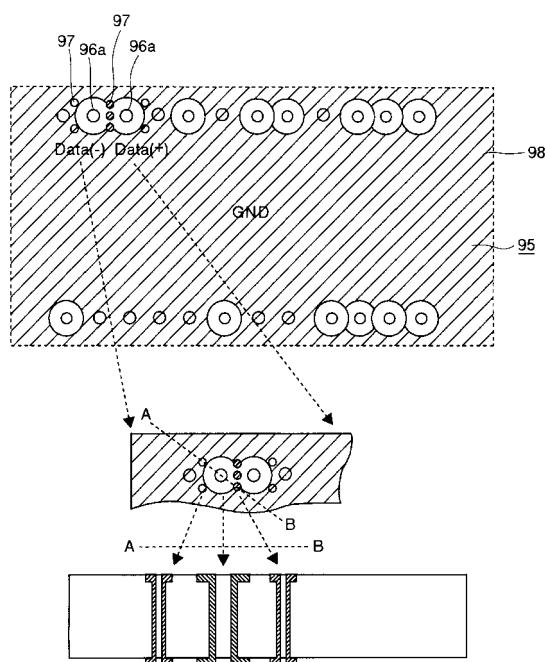

図23は、光受信器が接続されるシステム基板95を示す図である。図23に破線で囲んだ領域は、システム基板95の全ての領域のうちの光受信器70を搭載する光受信器搭載領域を示している。

#### 【0153】

システム基板95にも、誘電体ブロック75に形成された2つの高速用ピン孔76aおよびその周りの5つのグランドスルーホール77に対応するように、2つの高速用ピン孔96aと5つのグランドスルーホール97が形成されている。破線で囲んだ光受信器搭載領域に関しては、信号ピンが挿入されるピン孔以外の全ての領域あるいは信号ピンに接続される配線パターン部分を除く誘電体ブロックと当接する領域をおもて面および裏面ともベタグランド98とする。なお、コストなどを考慮した場合、前者の全ての領域をベタグランドとするほうが好ましい。10

#### 【0154】

このようにこの実施の形態5によれば、高速用インターフェースピンの特性インピーダンスが基板線路に整合され、これにより高速なデータ伝送またはクロック伝送を実現する光受信器を提供することができる。なお、光受信器70は、データ信号を送信する2本のピンの他に、クロック信号を伝送する2本のピンを設けてもよく、この場合は内部に設けられたPLL回路の動作によって、PDモジュールから送出された電圧信号からクロックを抽出し、また内部に設けられた識別再生回路によってデータ信号を識別し、再生されたデータ信号を基板線路を介して2本の高速用インターフェースピン80aに出力する。20

#### 【0155】

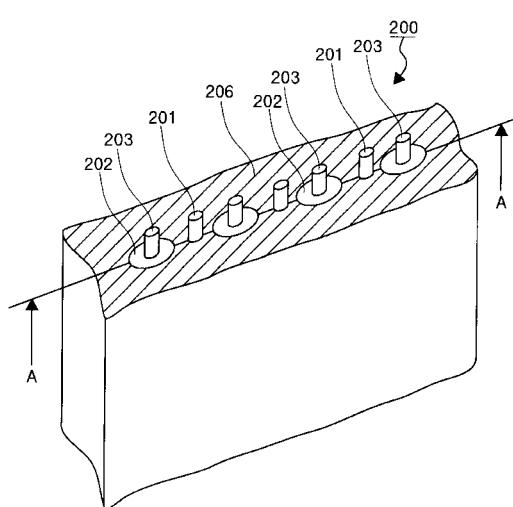

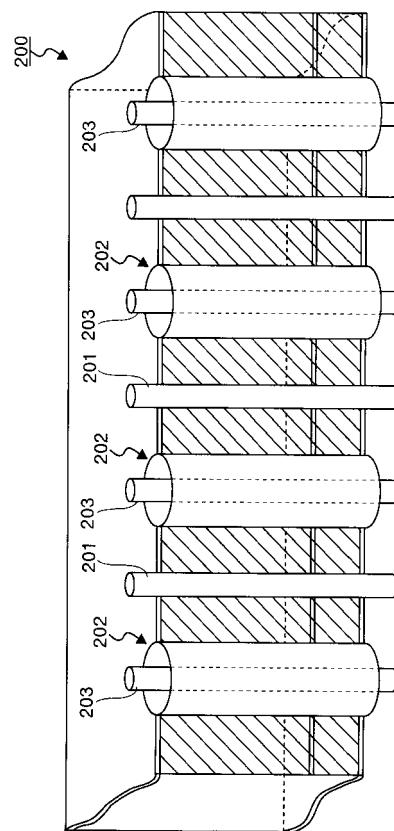

実施の形態6。

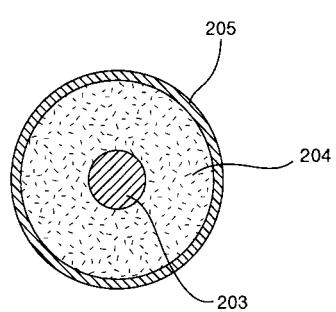

つぎに、図24～図26を用いてこの発明の実施の形態6について説明する。図24は実施の形態6の誘電体ブロック200の一部を示す斜視図であり、図25は図24のA-A断面図であり、図26は高速信号用ピン部分の平面図である。

#### 【0156】

この実施の形態6においては、先の実施の形態のように信号用ピンの周りに間欠的にグランドスルーホールを配置するのではなく、信号用ピンの全周囲にグランド用の金属パターンを形成するようにしている。

#### 【0157】

図24および図25において、誘電体ブロック200には、グランドピン201と、これらグランドピン201の間に配設される4つの高速用インターフェース線路202とが内蔵される。高速用インターフェース線路202は、図26に示すように、中心に配置される高速信号用インターフェースピン203と、その周りの誘電体204と、誘電体204の周囲に配置されるグランド用の金属パターン205とから構成される。誘電体ブロック200の上面及び下面には、ベタグランドパターン206が信号ピン203および誘電体204の部分を除いて一様に形成されている。30

#### 【0158】

このような誘電体ブロック200の高速用インターフェース線路202を製造するには、つぎのような2つの製法(A)(B)がある。

##### (A) 第1製法

- ・孔を形成する。

- ・孔の内周面を金属メッキし、グランド用の金属パターン205を形成する。

- ・孔の中に中央にピン挿入用の孔が空いた誘電体204を流し込む。

- ・誘電体204の中にピン203を入れる。

##### 【0159】

##### (B) 第2製法

- ・孔を形成する。

- ・孔の内周面を金属メッキし、グランド用の金属パターン205を形成する。

- ・ピン203を入れる

- ・ピン203と金属パターン205との間に溶融している誘電体を流し込む。

10

20

30

40

50

**【 0 1 6 0 】**

このようにこの実施の形態 6 によれば、信号用ピンの周りに間欠的にグランドスルーホールを配置するのではなく、信号用ピンの全周囲にグランド用の金属パターンを形成しているので、よりグランドが強化され、特性インピーダンスの安定化に寄与する。

**【 0 1 6 1 】**

なお、上記の実施の形態 1 ~ 6 においては、信号ピンを誘電体ブロック 44a, 44b から突出させているが、どちらか一端側または両端とも突出しないように構成しても良い。突出させない場合は、例えば、バンプによりピンの端面を基板側に接続すればよい。

**【 0 1 6 2 】****【発明の効果】**

10

以上説明したように、この発明にかかる光送受信器によれば、ギャップ部に誘電体ブロックを設け、基板線路との特性インピーダンスを合わせるようにしたので、より高速なデータ信号またはクロック信号を伝送させることができる。また、インターフェースピンの周囲に複数のグランドピンまたはグランドスルーホールを設け、基板線路との特性インピーダンスを合わせるようにしたので、より高速なデータ信号またはクロック信号を、より低い誘電率の誘電体ブロックを充填することによって、伝送させることができる。

**【 0 1 6 3 】**

つぎの発明にかかる接続体によれば、誘電体ブロックにピン及び該ピンの周囲に形成されるグランドスルーホールを内蔵させ、該ピンによって第 1 及び第 2 の基板を電気接続するようになっているので、特性インピーダンスが改善され、これにより第 1 及び第 2 の基板間で、高速なデータ伝送またはクロック伝送を実現することができる。

20

**【 0 1 6 4 】**

つぎの発明にかかる基板ユニットによれば、ピン及び該ピンの周囲に形成される第 1 のグランドスルーホールを有する接続体と、前記ピンが圧入されるピン孔と、このピン孔の周囲であって前記第 1 のグランドスルーホールと電気的に接続される第 2 のグランドスルーホールとを有する基板とを備えているので、特性インピーダンスが改善され、前記基板及び他の基板間で高速なデータ伝送またはクロック伝送を実現することができる。

**【 0 1 6 5 】**

つぎの発明にかかる光送信器によれば、複数の信号ピン、グランドピン及び信号ピンの周囲に形成される複数の第 1 のグランドスルーホールを有する接続体と、前記ピンが圧入されるピン孔、信号ピン用のピン孔の周囲に配置される第 2 のグランドスルーホールおよび前記信号ピン用のピン孔に接続される基板配線を有する基板と、前記基板上に搭載されるレーザダイオードと、前記レーザダイオードと前記基板配線に接続されるドライバ IC を備えているので、基板線路と信号ピンとの特性インピーダンスが整合され、これにより高速なデータ伝送またはクロック伝送を実現することができる。

30

**【 0 1 6 6 】**

つぎの発明にかかる光受信器によれば、2 本の高速用インターフェースピン、グランドピン及び高速用インターフェースピンの周囲に形成される複数の第 1 のグランドスルーホールを有する接続体と、前記ピンが圧入されるピン孔、高速用インターフェースピン用のピン孔の周囲に配置される第 2 のグランドスルーホールおよび前記高速用インターフェースピン用のピン孔に接続される基板配線を有する基板と、前記基板上に搭載されるフォトダイオードと、前記フォトダイオードと前記基板配線に接続される受信回路 IC を備えているので、基板線路と信号ピンとの特性インピーダンスが整合され、これにより高速なデータ伝送またはクロック伝送を実現することができる。

40

**【 0 1 6 7 】**

つぎの発明にかかる半導体装置によれば、誘電体ブロックのピンの周り、第 1 および第 2 の基板のピン孔の周りにグランドスルーホールを形成するとともに、第 2 の基板におけるピン孔の習癖面とピンとの隙間に半田などの金属を充填するようにしたので、特性インピーダンスが改善され、第 1 及び第 2 の基板間で高速なデータ伝送またはクロック伝送を実現することができる。

50

**【図面の簡単な説明】**

【図 1】 この発明の実施の形態 1 の光送受信器モジュールを示す図であり、(a) はその平面図、(b) はその B - B 断面図である。

【図 2】 この発明の実施の形態 1 の光送受信器モジュールのピン配列を示す図であり、(a) はその平面図、(b) はその B - B 断面図である。

【図 3】 この発明の実施の形態 1 の光送受信器モジュールに用いられる誘電体ブロックを示す斜視図である。

【図 4】 この発明の実施の形態 1 の光送受信器モジュールの変形態様を示す平面図である。

【図 5】 この発明の実施の形態 2 の光送受信器モジュールを示す図であり、(a) はその平面図、(b) はその B - B 断面図である。 10

【図 6】 この発明の実施の形態 2 の光送受信器モジュールの変形態様を示す平面図である。

【図 7】 この発明の実施の形態 3 の光送受信器モジュールを示す図であり、(a) はその平面図、(b) はその B - B 断面図である。

【図 8】 この発明の実施の形態 3 の光送受信器モジュールの変形態様を示す平面図である。

【図 9】 この発明の実施の形態 4 の光送信器の外観構成を示す斜視図である。

【図 10】 この発明の実施の形態 4 の光送信器を示す図であり、(a) はその正面図、(b) はその下面図である。 20

【図 11】 この発明の実施の形態 4 の光送信器の内部構成を示す図であり、(a) はその平面図、(b) はその縦断面図、(c) はその横断面図である。

【図 12】 この発明の実施の形態 4 の光送信器に用いられる基板ユニットを示す斜視図である。

【図 13】 この発明の実施の形態 4 の光送信器に用いられる内部基板の部分平面図である。

【図 14】 この発明の実施の形態 4 の光送信器に用いられる内部基板の部分下面図である。

【図 15】 この発明の実施の形態 4 の光送信器に用いられる誘電体ブロックを示す平面図および断面図である。 30

【図 16】 この発明の実施の形態 4 の光送信器に用いられるピンを示す図であり、(a) はその上面図、(b) はその正面図である。

【図 17】 この発明の実施の形態 4 の光送信器に用いられるシステム基板を示す平面図および断面図である。

【図 18】 この発明の実施の形態 4 の光送信器に用いられるシステム基板を示す一部拡大平面図である。

【図 19】 この発明の実施の形態 4 の光送信器の内部ユニットの接続構造を示す断面図である。

【図 20】 この発明の実施の形態 5 の光受信器に用いられる誘電体ブロックを示す平面図である。 40

【図 21】 この発明の実施の形態 5 の光受信器に用いられる誘電体ブロックの高速用インターフェースピンの周囲の構造を示す一部拡大平面図である。

【図 22】 この発明の実施の形態 5 の光受信器に用いられる内部基板の一部拡大平面図である。

【図 23】 この発明の実施の形態 5 の光受信器に用いられるシステム基板を示す平面図、断面図である。

【図 24】 この発明の実施の形態 6 の誘電体ユニットを示す斜視図である。

【図 25】 この発明の実施の形態 6 の誘電体ユニットを示す一部断面図である。

【図 26】 この発明の実施の形態 6 の誘電体ユニットの高速用インターフェースピンの構造を示す断面図である。 50

【図27】 従来技術を示す図であり、(a)は平面図、(b)はそのA-A断面図である。

【符号の説明】

1 筐体、2 LDドライバ、3 LDモジュール、4 PDモジュール、5 受信回路、6 送信用光ファイバ、7 受信用光ファイバ、8 制御回路、10a~10d 基板線路、11a, 11b 基板線路、12a, 12c 高速用インターフェースピン、13 グランドピン、15 基板保持部材、17 光送受信器、20 基板、21 システム基板、22 誘電体ブロック、23 ギャップ部(空隙)、31 グランドピン、32 誘電体ブロック、33 グランドピン、34 差動線路、35 グランドスルーホール、36 誘電体ブロック、40 光送信器、41 筐体(ケース)、42 送信用光ファイバ、43 光コネクタ、44a, 44b 誘電体ブロック、46 内部基板、48 システム基板、49a 高速用ピン孔、50a 高速用インターフェースピン、54~56 グランドスルーホール、60 LDドライバ、70 光受信器、75 誘電体ブロック、76d グランドピン孔、76a 高速用ピン孔、80a 高速用インターフェースピン、85 内部基板、90 差動伝送線路、91 パターン線路、95 システム基板、200 誘電体ブロック、201 グランドピン、202 高速用インターフェース線路、203 高速信号用インターフェースピン、204 誘電体、205 金属パターン、206 ベタグランドパターン。

10

【図1】

(a)

【図2】

(a)

(b)

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図15】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

---

フロントページの続き

(51)Int.Cl. F I

H 0 4 B 10/28 (2006.01)

H 0 1 L 31/0232 (2006.01)

(56)参考文献 特開平09-260693 (JP, A)

特開平05-074532 (JP, A)

特開2000-082826 (JP, A)

特開平04-306901 (JP, A)

特開平08-037047 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01S 5/00- 5/50

H01R 9/03- 9/11

H01R 12/04-12/08

H01R 12/32-12/38

H04B 10/00-10/28

H04J 14/00-14/08

G02B 6/12- 6/14

G02B 6/26

G02B 6/30- 6/34

G02B 6/42