(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6302231号

(P6302231)

(45) 発行日 平成30年3月28日(2018.3.28)

(24) 登録日 平成30年3月9日(2018.3.9)

(51) Int.Cl.

B 41 J 2/14 (2006.01)

F 1

B 41 J 2/14 6 1 1

B 41 J 2/14 2 0 1

請求項の数 14 (全 16 頁)

(21) 出願番号 特願2013-257396 (P2013-257396)

(22) 出願日 平成25年12月12日 (2013.12.12)

(65) 公開番号 特開2015-112817 (P2015-112817A)

(43) 公開日 平成27年6月22日 (2015.6.22)

審査請求日 平成28年8月1日 (2016.8.1)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】記録素子基板、記録ヘッド及び記録装置

## (57) 【特許請求の範囲】

## 【請求項 1】

吐出を行うための吐出素子と、第1電圧が供給される第1ノードに電気的に接続されたドレイン端子、第2電圧が供給される第2ノードに電気的に接続されたゲート端子、並びに、前記吐出素子に電気的に接続されたソース端子及びバックゲート端子を含むMOSトランジスタと、前記吐出素子と接地ノードとの間の電流経路に配されたスイッチ手段と、前記MOSトランジスタの前記ソース端子及び前記バックゲート端子にアノードが接続され、前記MOSトランジスタの前記ゲート端子にカソードが接続されている第1のダイオードと、前記MOSトランジスタの前記ゲート端子にアノードが接続され、前記MOSトランジスタの前記ソース端子及び前記バックゲート端子にカソードが接続されている第2のダイオードと、を含むことを特徴とする吐出素子基板。

## 【請求項 2】

吐出を行うための吐出素子と、第1電圧が供給される第1ノードに電気的に接続されたドレイン端子、第2電圧が供給される第2ノードに電気的に接続されたゲート端子、並びに、前記吐出素子に電気的に接続されたソース端子及びバックゲート端子を含むMOSトランジスタと、前記吐出素子と接地ノードとの間の電流経路に配されたスイッチ手段と、

10

20

前記MOSトランジスタの前記ドレイン端子にアノードが接続され、前記MOSトランジスタの前記ゲート端子にカソードが接続されている第1のダイオードと、

前記MOSトランジスタの前記ゲート端子にアノードが接続され、前記MOSトランジスタの前記ソース端子及び前記バックゲート端子にカソードが接続されている第2のダイオードと、

を含むことを特徴とする吐出素子基板。

## 【請求項3】

吐出を行うための吐出素子と、

第1電圧が供給される第1ノードに電気的に接続されたドレイン端子、第2電圧が供給される第2ノードに電気的に接続されたゲート端子、並びに、前記吐出素子に電気的に接続されたソース端子及びバックゲート端子を含むMOSトランジスタと、

前記吐出素子と接地ノードとの間の電流経路に配されたスイッチ手段と、

前記MOSトランジスタの前記ソース端子及び前記バックゲート端子にアノードが接続され、前記MOSトランジスタの前記ゲート端子にカソードが接続されている第1のダイオードと、

前記MOSトランジスタの前記ゲート端子にアノードが接続され、前記MOSトランジスタの前記ドレイン端子にカソードが接続されている第2のダイオードと、

を含むことを特徴とする吐出素子基板。

## 【請求項4】

吐出を行うための吐出素子と、

第1電圧が供給される第1ノードに電気的に接続されたドレイン端子、第2電圧が供給される第2ノードに電気的に接続されたゲート端子、並びに、前記吐出素子に電気的に接続されたソース端子及びバックゲート端子を含むMOSトランジスタと、

前記吐出素子と接地ノードとの間の電流経路に配されたスイッチ手段と、

前記MOSトランジスタの前記ドレイン端子にアノードが接続され、前記MOSトランジスタの前記ゲート端子にカソードが接続されている第1のダイオードと、

前記MOSトランジスタの前記ゲート端子にアノードが接続され、前記MOSトランジスタの前記ドレイン端子にカソードが接続されている第2のダイオードと、

を含むことを特徴とする吐出素子基板。

## 【請求項5】

前記MOSトランジスタはソースフォロワ動作を行う

ことを特徴とする請求項1乃至4のいずれか1項に記載の吐出素子基板。

## 【請求項6】

前記スイッチ手段は、ドレイン端子が前記吐出素子に接続され、ソース端子が接地ノードに接続された第2のMOSトランジスタを含む

ことを特徴とする請求項1乃至5のいずれか1項に記載の吐出素子基板。

## 【請求項7】

前記第1のダイオードの数量と、前記第2のダイオードの数量とは、前記第1ノードに供給されるべき前記第1電圧と前記第2ノードに供給されるべき前記第2電圧との大小関係に基づいて定められた

ことを特徴とする請求項1乃至6のいずれか1項に記載の吐出素子基板。

## 【請求項8】

前記第2のダイオードの数量は、前記第1のダイオードの数量よりも大きい

ことを特徴とする請求項1乃至6のいずれか1項に記載の吐出素子基板。

## 【請求項9】

吐出を行うための吐出素子と、

第1電圧が供給される第1ノードに電気的に接続されたドレイン端子、第2電圧が供給される第2ノードに電気的に接続されたゲート端子、並びに、前記吐出素子に電気的に接続されたソース端子及びバックゲート端子を含むMOSトランジスタと、

前記吐出素子と接地ノードとの間の電流経路に配されたスイッチ手段と、

10

20

30

40

50

前記第2ノードの電位を検出する検出部と、

前記検出部からの検出結果に基づいて、前記MOSトランジスタの前記ソース端子及び前記バックゲート端子と、前記接地ノードとを電気的に接続する第2のスイッチ手段と、を備える

ことを特徴とする吐出素子基板。

【請求項10】

吐出を行うための吐出素子と、

第1電圧が供給される第1ノードに電気的に接続されたドレイン端子、第2電圧が供給される第2ノードに電気的に接続されたゲート端子、並びに、前記吐出素子に電気的に接続されたソース端子及びバックゲート端子を含むMOSトランジスタと、

10

前記吐出素子と接地ノードとの間の電流経路に配されたスイッチ手段と、

前記第2ノードの電位を検出する検出部と、

前記検出部からの検出結果に基づいて前記スイッチ手段を導通状態にする制御部と、を備える

ことを特徴とする吐出素子基板。

【請求項11】

前記MOSトランジスタおよび前記スイッチ手段は、それぞれNMOSトランジスタであり、

前記検出部は、

抵抗素子と、

20

前記第1ノードに接続されたソース端子、前記第2ノードに接続されたゲート端子、および、前記抵抗素子に接続されたドレイン端子を有するPMOSトランジスタと、を含むことを特徴とする請求項9または請求項10に記載の吐出素子基板。

【請求項12】

前記MOSトランジスタはDMOSトランジスタで構成されている

ことを特徴とする請求項1乃至11のいずれか1項に記載の吐出素子基板。

【請求項13】

請求項1乃至12のいずれか1項に記載の吐出素子基板と、

前記吐出素子に対応して設けられ、前記吐出素子に電流が流れたことに応答して液体を吐出する吐出口と、を備える

30

ことを特徴とする吐出ヘッド。

【請求項14】

請求項13に記載の吐出ヘッドと、

前記吐出ヘッドを駆動する吐出ヘッドドライバと、を備える

ことを特徴とする液体吐出装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、記録素子基板、記録ヘッド及び記録装置に関する。

40

【背景技術】

【0002】

インクジェット方式の記録装置は、記録媒体に対して記録を行う記録ヘッドを備える。記録ヘッドは記録素子基板を備えており、該記録素子基板は、記録素子と、該記録素子を駆動するための駆動トランジスタとを有する。記録素子を通電するための第1電圧と、駆動トランジスタを制御するための第2電圧とは、個別に供給される。この構成によると、記録を行うことによって第1電圧の電源ノードで電位変動が生じた場合でも、当該電位変動による記録特性への影響を小さくすることが可能である。

【先行技術文献】

【特許文献】

50

## 【0003】

【特許文献1】特開2010-155452号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0004】

ところで、例えば記録ヘッドが適切に記録装置に装着されていない場合や、記録装置で誤動作が生じた場合など、上述の第1電圧および第2電圧を含む複数の電圧のうちの第2電圧が供給されていないといった事態が生じうる。この場合の第2電圧を供給するための電源ノードは不定（例えば0[V]）になる。

## 【0005】

第2電圧を供給する電源ノードの電圧が例えば0[V]になると、上述の駆動トランジスタのソースとゲートとの間には過電圧が生じうる。このことは、該駆動トランジスタの絶縁破壊をもたらしうる。

## 【0006】

本発明の目的は、駆動トランジスタの絶縁破壊を防ぐのに有利な技術を提供することにある。

## 【課題を解決するための手段】

## 【0007】

本発明の一つの側面は、吐出を行うための吐出素子と、第1電圧が供給される第1ノードに電気的に接続されたドレイン端子、第2電圧が供給される第2ノードに電気的に接続されたゲート端子、並びに、前記吐出素子に電気的に接続されたソース端子及びバックゲート端子を含むMOSトランジスタと、前記吐出素子と接地ノードとの間の電流経路に配されたスイッチ手段と、前記MOSトランジスタの前記ソース端子及び前記バックゲート端子にアノードが接続され、前記MOSトランジスタの前記ゲート端子にカソードが接続されている第1のダイオードと、前記MOSトランジスタの前記ゲート端子にアノードが接続され、前記MOSトランジスタの前記ソース端子及び前記バックゲート端子にカソードが接続されている第2のダイオードと、を含む吐出素子基板に関する。

また、本発明の別の側面は、吐出を行うための吐出素子と、第1電圧が供給される第1ノードに電気的に接続されたドレイン端子、第2電圧が供給される第2ノードに電気的に接続されたゲート端子、並びに、前記吐出素子に電気的に接続されたソース端子及びバックゲート端子を含むMOSトランジスタと、前記吐出素子と接地ノードとの間の電流経路に配されたスイッチ手段と、前記第2ノードの電位を検出する検出部と、前記検出部からの検出結果に基づいて前記スイッチ手段を導通状態にする制御部と、を備える吐出素子基板に関する。

## 【発明の効果】

## 【0008】

本発明によれば、駆動トランジスタの絶縁破壊を防ぐのに有利である。

## 【図面の簡単な説明】

## 【0009】

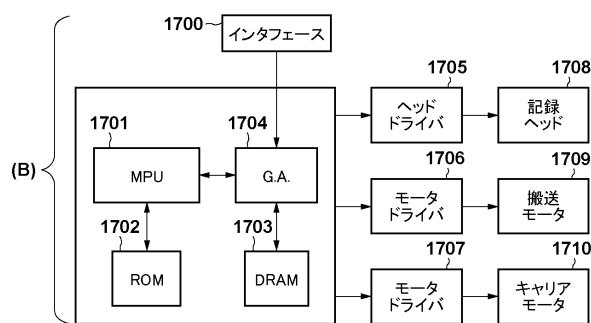

【図1】記録装置の構成例を説明する図。

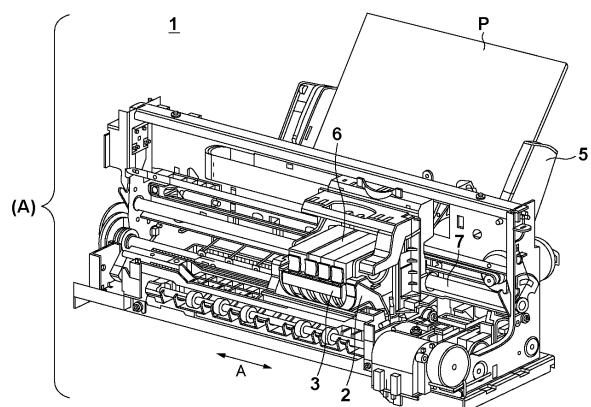

【図2】記録素子基板の構成例を説明する図。

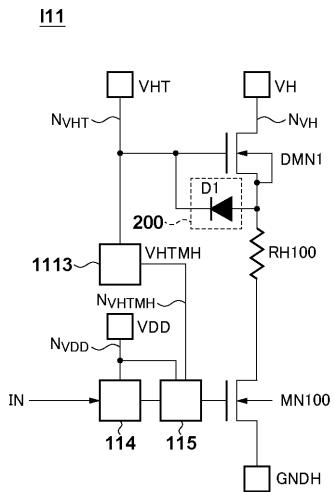

【図3】電圧生成部およびレベルシフタの構成例を説明する図。

【図4】高耐圧MOSトランジスタの構造の一例を説明する図。

【図5】記録素子基板の構成例を説明する図。

【図6】記録素子基板の構成例を説明する図。

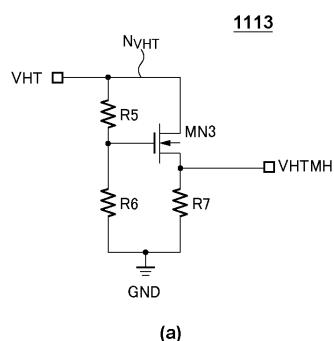

【図7】検出部の構成例を説明する図。

【図8】記録素子基板の回路構成例を説明する図。

【図9】記録素子基板の回路構成例を説明する図。

【図10】記録素子基板の回路構成例を説明する図。

## 【発明を実施するための形態】

10

20

30

40

50

## 【0010】

## (記録装置の構成例)

図1を参照しながら、インクジェット方式の記録装置の構成例を述べる。記録装置は、例えば、記録機能のみを有するシングルファンクションプリンタでもよいし、記録機能、FAX機能、スキャナ機能等の複数の機能を有するマルチファンクションプリンタでもよい。また、記録装置は、カラーフィルタ、電子デバイス、光学デバイス、微小構造物等を所定の記録方式で製造する製造装置をも含みうる。

## 【0011】

図1の(A)は、記録装置PAの外観構成の一例を示す斜視図である。記録装置PAは、インクを吐出して記録を行う記録ヘッド3をキャリッジ2に搭載し、キャリッジ2を矢印A方向に往復移動させて記録を行う。記録装置PAは、プリント用紙などの記録媒体Pを、給紙機構5を介して給紙し、記録位置まで搬送する。記録装置PAは、その記録位置において記録ヘッド3から記録媒体Pにインクを吐出することにより記録を行う。

10

## 【0012】

キャリッジ2には、記録ヘッド3の他、例えば、インクカートリッジ6が搭載される。インクカートリッジ6は、記録ヘッド3に供給するインクを貯留する。インクカートリッジ6は、キャリッジ2に対して着脱自在になっている。また、記録装置PAは、カラー記録が可能である。そのため、キャリッジ2には、マゼンタ(M)、シアン(C)、イエロ(Y)、ブラック(K)のインクをそれぞれ収容する4つのインクカートリッジが搭載されている。これら4つのインクカートリッジは、それぞれ独立して着脱可能である。

20

## 【0013】

記録ヘッド3は、インクを吐出するためのインク吐出口(ノズル)を有し、また、ノズルに対応して設けられた電気熱変換体(ヒータ)を備える記録素子基板を具備する。ヒータには記録信号にしたがうパルス電圧が印加され、パルス電圧が印加されたヒータによる熱エネルギーによってインク内で気泡が生じ、当該ヒータに対応するノズルからインクが吐出される。

## 【0014】

図1の(B)は、記録装置PAのシステム構成を例示している。記録装置PAは、インターフェース1700、MPU1701、ROM1702、RAM1703及びゲートアレイ1704を有する。インターフェース1700には記録信号が入力される。ROM1702は、MPU1701が実行する制御プログラムを格納する。RAM1703は、前述の記録信号や記録ヘッド1708に供給された記録データ等、各種データを保存する。ゲートアレイ1704は、記録ヘッド1708に対する記録データの供給制御を行い、また、インターフェース1700、MPU1701、RAM1703の間のデータ転送の制御を行う。

30

## 【0015】

また、記録装置PAは、記録ヘッドドライバ1705、並びにモータドライバ1706及び1707、搬送モータ1709、キャリアモータ1710をさらに有する。記録ヘッドドライバ1705は記録ヘッド1708を駆動する。モータドライバ1706及び1707は搬送モータ1709及びキャリアモータ1710をそれぞれ駆動する。搬送モータ1709は記録媒体を搬送する。キャリアモータ1710は記録ヘッド1708を搬送する。

40

## 【0016】

インターフェース1700に記録信号が入力されると、この記録信号は、ゲートアレイ1704とMPU1701の間で所定の形式の記録データに変換されうる。この記録データにしたがって各機構が所望の動作を行い、このようにして上述の記録が為される。

## 【0017】

## (第1実施形態)

図2～4を参照しながら第1実施形態を述べる。なお、本明細書では、特に断りがない限り、「電圧」は、接地ノードの電位を基準としたときの電位差であるとして述べる。ま

50

た、通常、「接地ノード」は 0 [V] に固定される。

【0018】

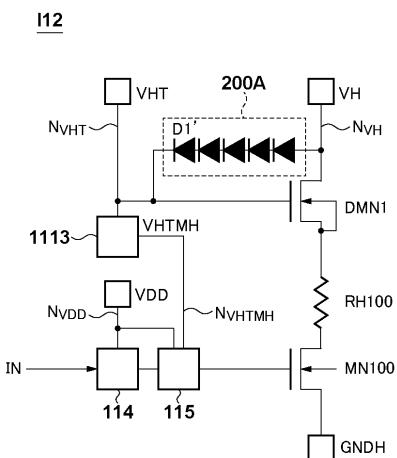

図2は、本実施形態の記録素子基板I11の構成例を示している。記録素子基板I11は、ヒータRH100と、NMOSトランジスタDMN1と、NMOSトランジスタMN100と、ユニット200と、を備えている。また、記録素子基板I11は、信号処理部114と、レベルシフタ115と、電圧生成部1113と、をさらに備えている。

【0019】

ヒータRH100と、トランジスタDMN1及びMN100とは、第1電圧VH（例えば24～32[V]）を受ける電源ノードN<sub>VH</sub>と、接地ノード（GNDH）との間に、電流経路を形成することができるよう、直列に配されている。

10

【0020】

トランジスタDMN1には高耐圧MOSトランジスタが用いられる。トランジスタDMN1のドレイン端子は、電源ノードN<sub>VH</sub>に接続されている。トランジスタDMN1のゲート端子は、第2電圧VHT（例えば24～32[V]）を受ける電源ノードN<sub>VHT</sub>に接続されている。トランジスタDMN1のソース端子およびバックゲート端子は、ヒータRH100の一方の端に接続されている。電圧VHTは、電圧VHとは異なる電源電圧であり、記録動作による電圧VHの電位変動の影響を受けにくい。トランジスタDMN1は、この電圧VHTをゲート端子で受けてソースフォロワ動作を行い、ヒータRH100に定電流を供給する。

【0021】

20

トランジスタMN100には、トランジスタDMN1と同様に、高耐圧MOSトランジスタが用いられる。トランジスタMN100のドレイン端子は、ヒータRH100の他方の端に接続されており、ソース端子およびバックゲート端子は、接地ノードに接続されている。トランジスタMN100は、信号処理部114からの信号を、レベルシフタ115を介してゲート端子で受け、該信号に応答して導通状態または非導通状態になるスイッチ手段である。トランジスタMN100が導通状態になることによって、ヒータRH100が駆動され（通電し）、発熱する。

【0022】

なお、ここでは、トランジスタMN100としてNMOSトランジスタを用いた構成を例示したが、トランジスタMN100には他の公知のスイッチ手段が用いられてもよい。

30

【0023】

ユニット200は、後述するように、トランジスタDMN1のソース端子およびバックゲート端子とゲート端子との間を電気的に接続するように配されている。

【0024】

信号処理部114には、ロジック用の電源電圧である第3電圧VDD（例えば3.3～5[V]）が供給され、信号処理部114は、記録装置PA本体からの記録データにしたがう信号を、レベルシフタ115を介してトランジスタMN100に出力する。

【0025】

電圧生成部1113は、電圧VHTを受けて第4電圧VHTMHを生成し（又は、電圧VHTを電圧VHTMHに変換する電圧変換部として機能し）、電圧VHTMHをレベルシフタ115に供給する。

40

【0026】

図3(a)は、電圧生成部1113の構成例を示している。電圧生成部1113は、抵抗素子R5及びR6と、トランジスタMN3及び抵抗素子R7とが、電源ノードN<sub>VHT</sub>と接地ノード（GND）との間に、それぞれ電流経路を形成するように配されうる。この構成によると、電圧VHTの抵抗素子R5及びR6による分圧電圧がトランジスタMN3のゲートに入力され、当該分圧電圧に応じた電圧VHTMHが出力される。

【0027】

なお、例えばノイズ対策のため、電圧VHに対応する接地ノードとしてのGNDHと、電圧VHTに対応する接地ノードとしてのGNDとは区別して設けられうるが、他の対策

50

が講じられていれば、GNDH及びGNDは共通の接地ノードでもよい。

【0028】

レベルシフタ115には、電圧VDD及びVHTMHが供給される。レベルシフタ115は、信号処理部114からの信号を、電圧VDDの電位レベルから電圧VHTMHの電位レベルにレベルシフトして出力する。

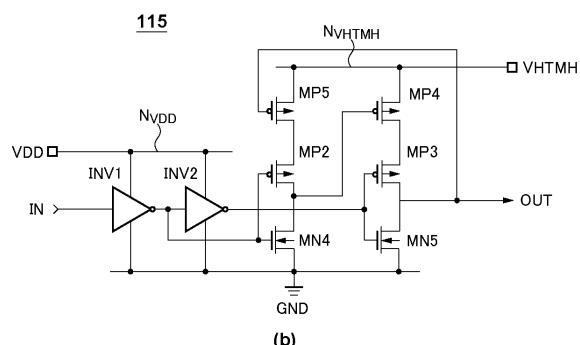

【0029】

図3(b)は、レベルシフタ115の構成例を示している。レベルシフタ115は、インバータINV1及びINV2と、NMOSトランジスタMN4及びMN5と、PMOSトランジスタMP2～MP5とを用いて構成されうる。インバータINV1は、信号処理部114からの出力を受け、インバータINV2に出力する。NMOSトランジスタMN4及びMN5並びにPMOSトランジスタMP2～MP5は、インバータINV1及びINV2の出力を受けて、信号処理部114からの信号について、電位レベルのレベルシフトを行う回路部を形成する。具体的には、トランジスタMP5、MP2及びMN4は電圧VHTMHの電源ノードN<sub>VHTMH</sub>と接地ノードとの間に電流経路を形成するように配されている。トランジスタMP4、MP3及びMN5は、電圧VHTMHの電源ノードN<sub>VHTMH</sub>と接地ノードとの間に電流経路を形成するように配されている。トランジスタMP2及びMN4のゲートはインバータINV1の出力を受ける。トランジスタMP3及びMN5のゲートはインバータINV2の出力を受ける。また、トランジスタMP2とMN4との間のノードは、トランジスタMP4のゲートに接続される。トランジスタMP3とMN5との間のノードは、トランジスタMP5のゲートに接続されている。

10

20

【0030】

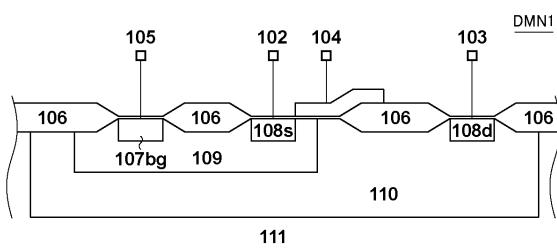

ここで、図4を参照しながら、トランジスタDMN1に用いられる高耐圧MOSトランジスタの例として、Nチャネル型のDMOSトランジスタの構造を述べる。DMOSトランジスタの構造は、公知の半導体製造プロセスを用いて形成されうる。P型半導体領域111を含む基板にN型半導体領域110が形成されており、N型半導体領域110の中にはP型半導体領域109が設けられている。P型半導体領域109の中には高濃度P型領域107bgが設けられている。P型半導体領域109の中には高濃度N型領域108sが設けられている。N型半導体領域110の中のP型半導体領域109から離れた位置には高濃度N型領域108dが設けられている。基板上にはフィールド酸化膜106やゲート絶縁膜を含む絶縁膜が設けられている。また、P型半導体領域109とN型半導体領域110との境界領域には、フィールド酸化膜106及びゲート絶縁膜を介してゲート電極が設けられている。端子102はソース端子に対応し、端子103はドレイン端子に対応し、端子104はゲート端子に対応し、端子105はバックゲート端子(バルク端子)に対応している。

30

【0031】

この構造によると、ドレイン領域に対応するN型領域108dからゲート電極およびチャネルへの電界が緩和され、高耐圧MOSトランジスタとして機能しうる。また、この構造によると、ソース及びバックゲートと接地ノードとが電気的に分離され、ヒータRHにヒータ電流が流れることによってトランジスタDMN1のソース電位が上がったときの基板バイアス効果の影響が低減される。トランジスタDMN1のソース電位は、トランジスタDMN1の閾値電圧をV<sub>T</sub>として、(VHT-V<sub>T</sub>)程度になる。ゲート-ソース間の電位差はV<sub>T</sub>程度であり、該ゲート-ソース間での絶縁破壊は生じない。

40

【0032】

上述の通り、ヒータRHに適切に電流が供給されている間は、トランジスタDMN1のソースは(VHT-V<sub>T</sub>)程度の高電位状態である。この状態で、電圧VHは適切に記録素子基板I11に供給されているが、電圧VHTが記録素子基板I11へ適切に供給されなくなった場合について考える。電圧VHTが供給されていない場合、電源ノードN<sub>VH-T</sub>の電位は不定状態となる。該電位が、例えば0[V]になったときには、トランジスタDMN1のゲートの電位は、ほぼ0[V]になる。ここで、トランジスタMN100が非導通状態のとき、トランジスタDMN1のソースは電位が高い状態に維持される。このこ

50

とは、トランジスタ DMN1 のソースに蓄積された電荷の放電経路が実質的に存在しないことによる。その結果、トランジスタ DMN1 のゲート ソース間で過電圧が生じ、該ゲート ソース間での絶縁破壊が生じうる。

【0033】

なお、電圧 VHT が供給されていない場合には、通常、電源ノード N<sub>VHT</sub> の電位は基板を介して接地ノードの電位と等しくなりうるが、当該電位の不定状態を回避するため、例えば抵抗値の大きい抵抗素子を用いて電源ノード N<sub>VHT</sub> をプルダウン固定してもよい。

【0034】

そこで、本実施形態では、ユニット 200 として、例えばダイオード D1 が、トランジスタ DMN1 のソース端子およびバックゲート端子とゲート端子との間を電気的に接続するように配されている。ダイオード D1 は、アノードがトランジスタ DMN1 のソース端子およびバックゲート端子に接続され、カソードがトランジスタ DMN1 のゲート端子（又は電源ノード N<sub>VHT</sub>）に接続されている。

【0035】

ダイオード D1 に順方向電圧よりも大きいバイアスが印加されたとき、具体的には、アノードの電位がカソードの電位よりも所定値（例えば 0.6 [V]）を超えて大きくなつたときには、ダイオード D1 では順方向電流が流れる。この順方向電流による電荷の移動により、トランジスタ DMN1 のソース電位が下がり、その結果、トランジスタ DMN1 のゲート ソース間の電位差が小さくなる。

【0036】

即ち、ユニット 200 は、電源ノード N<sub>VHT</sub> の電位がトランジスタ DMN1 のソースの電位よりも所定値を超えて小さいときに、トランジスタ DMN1 のゲート ソース間の電位差を小さくする電位差調整部として機能しうる。ユニット 200 によると、電圧 VHT が適切に供給されていない場合でも、トランジスタ DMN1 のゲート ソース間での絶縁破壊が生じるおそれが低減される。よって、本実施形態によると、駆動トランジスタの絶縁破壊を防ぐのに有利である。

【0037】

本実施形態では、ユニット 200 として、1 つのダイオード D1 を用いた場合を例示したが、記録素子基板 I11 の仕様等に基づいて、2 以上のダイオード D1 が直列に接続された多段ダイオードが用いられてもよい。

【0038】

例えば、ダイオード D1 の段数ないし数量は、例えば、トランジスタ DMN1 の耐圧（絶縁破壊が生じうる電圧）と、個々のダイオードの順方向電圧（例えば 0.6 [V]）と、に基づいて決定されればよい。具体的には、ダイオード D1 の段数を n としたとき、トランジスタ DMN1 のゲート ソース間の電位差は  $0.6 \times n$  [V] 程度に抑えられる。よって、段数 n は、 $0.6 \times n$  [V] が上記耐圧を超えないように決められればよい。トランジスタ DMN1 のソースの電位は、トランジスタ DMN1 のゲートの電位と、トランジスタ DMN1 の閾値電圧 V<sub>T</sub> としたがい。ダイオード D1 の数量は、順方向電圧の合計がトランジスタ DMN1 のソース ゲート間の電位差よりも大きくなるように、ダイオード個々の順方向電圧に基づいて選択されればよい。

【0039】

なお、以上では、ダイオード D1 を用いた構成を例示して本実施形態を述べたが、同様の機能を有する構成を採ればよく、この構成に限られるものではない。例えば、ダイオード D1 の代わりにダイオード接続されたトランジスタが用いられてもよいし、バイポーラトランジスタが用いられてもよい。

【0040】

（第 2 実施形態）

前述の第 1 実施形態では、トランジスタ DMN1 のソース端子およびバックゲート端子とゲート端子との間を接続するように配されたユニット 200 を例示したが、本発明はこ

10

20

30

40

50

の構成に限られるものではなく、他の構成を探ってもよい。

【0041】

図5は、本実施形態の記録素子基板I12の構成例を示している。記録素子基板I12は、ユニット200の代わりに、トランジスタDMN1のドレイン端子とゲート端子との間を接続するように配されたユニット200Aを備えている。ユニット200Aは、直列に接続された5段ダイオードD1'を含む。ダイオードD1'は、アノードがトランジスタDMN1のドレイン端子に接続されており、カソードがトランジスタDMN1のゲート端子に接続されている。なお、ここではダイオードD1'の段数n=5としたが、この段数nは、前述のとおり、記録素子基板I12の仕様等に基づいて、適宜、決定されればよい。

10

【0042】

例えば、段数nは、記録装置PAによる記録動作時における電源ノードN<sub>VH</sub>の電位変動量に基づいても決定されうる。例えば、電圧VHとVHTとの電圧値が互いに等しい電源電圧を用いる構成において、電源ノードN<sub>VH</sub>の電位変動量が1[V]よりも大きくなると予想される場合には、段数nを2より大きくすればよい。これにより、記録動作時における電源ノードN<sub>VH</sub>の電位変動による電源ノードN<sub>VHT</sub>への影響を低減しつつ、上述の絶縁破壊を防ぐことも可能になる。また、例えば、VH>VHTとなる電源電圧を用いる構成では、段数nは、0.6×n[V]が(VH-VHT)を超えるように決められればよい。

【0043】

20

本実施形態によると、段数n=5であるため、トランジスタDMN1のゲートドレイン間の電位差が、0.6×5=3[V]よりも大きくなった場合に、電源ノードN<sub>VH</sub>からN<sub>VHT</sub>に順方向電流が流れる。これによりトランジスタDMN1のゲート電位が大きくなり、その結果、ゲートソース間の電位差が小さくなる。よって、本実施形態によつても、第1実施形態と同様の効果が得られる。

【0044】

(第3実施形態)

前述の第1～第2実施形態では、少なくとも1つのダイオードを含むユニット200ないし200Aを用いた構成を例示したが、本発明はこの構成に限られるものではなく、他の構成を探ってもよい。

30

【0045】

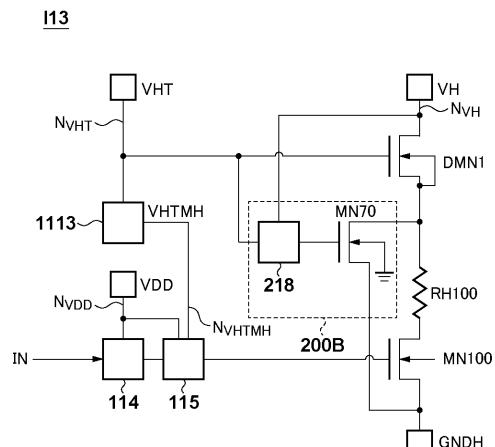

図6は、本実施形態の記録素子基板I13の構成例を示している。記録素子基板I13は、検出部218とNMOSトランジスタMN70とを含むユニット200Bを備えている。

【0046】

検出部218は、電源ノードN<sub>VHT</sub>の電位を検出する。具体的には、検出部218は、電圧VHを受けて電圧VHTをモニタする。検出部218は、検出結果をトランジスタMN70に出力する。

【0047】

トランジスタMN70には、前述の高耐圧MOSトランジスタが用いられる。トランジスタMN70のドレイン端子は、トランジスタDMN1とヒータRH100との間のノードに接続されており、トランジスタMN70のソース端子は、接地ノード(GNDH)に接続されている。トランジスタMN70は、検出部218からの検出結果をゲートで受けて、該検出結果に応じて導通状態または非導通状態になる。

40

【0048】

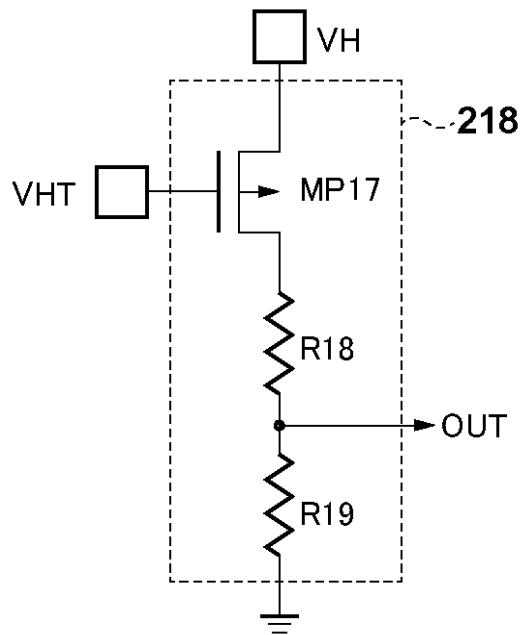

図7は、検出部218の構成例を示している。検出部218は、PMOSトランジスタMP17と、抵抗素子R18及びR19とを含む。トランジスタMP17と、抵抗素子R18及びR19とは、電流経路を形成できるように互いに直列に配されている。具体的には、トランジスタMP17は、ドレイン端子が電源ノードN<sub>VH</sub>に接続されており、ソース端子が抵抗素子R18の一方の端に接続されている。抵抗素子R18の他方の端は、抵

50

抗素子 R 1 9 の一方の端に接続され、また、抵抗素子 R 1 9 の他方の端は接地ノード ( G N D H ) に接続されている。

【 0 0 4 9 】

トランジスタ M P 1 7 のゲート端子は電源ノード  $N_{V_{H_T}}$  に接続されている。電圧  $V_{H_T}$  が供給されている場合には、トランジスタ M P 1 7 は非導通状態になり、検出部 2 1 8 は、 L o w レベルを出力する。前述のトランジスタ M N 7 0 は、該 L o w レベルを受けて非導通状態になる。

【 0 0 5 0 】

一方、電圧  $V_{H_T}$  が供給されていない場合には、トランジスタ M P 1 7 は導通状態になり、検出部 2 1 8 は、抵抗素子 R 1 8 と R 1 9 との分圧電圧を出力する。トランジスタ M N 7 0 は、該分圧電圧を受けて導通状態になり、これによって、トランジスタ D M N 1 のソース電位が下がる。その結果、トランジスタ D M N 1 のゲート ソース間の電位差が小さくなる。

【 0 0 5 1 】

トランジスタ M P 1 7 にもゲート絶縁膜に過電圧が印加されうるため、トランジスタ M P 1 7 には、ゲート絶縁膜の膜厚が十分に大きい P M O S トランジスタ等、高耐圧 M O S トランジスタが用いられる。製造コストを低減するため、例えば、トランジスタ D M N 1 を形成する際のフィールド酸化膜 1 0 6 がゲート絶縁膜として用いられてもよいし、又は、層間絶縁膜がゲート絶縁膜として用いられてもよい。

【 0 0 5 2 】

以上、本実施形態によっても、第 1 実施形態等と同様の効果が得られる。

【 0 0 5 3 】

( 第 4 実施形態 )

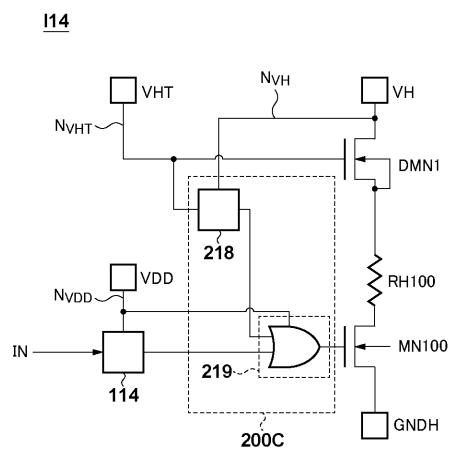

図 8 は、本実施形態の記録素子基板 I 1 4 の構成例を示している。記録素子基板 I 1 4 は、検出部 2 1 8 と論理和回路 2 1 9 とを含むユニット 2 0 0 C を備えている。論理和回路 2 1 9 には電圧  $V_{D D}$  が供給され、論理和回路 2 1 9 は、信号処理部 1 1 4 からの信号と、検出部 2 1 8 からの信号とを受けて、その結果をトランジスタ M N 1 0 0 に出力する。

【 0 0 5 4 】

電圧  $V_{H_T}$  が供給されている場合には、検出部 2 1 8 のトランジスタ M P 1 7 は非導通状態になり、検出部 2 1 8 は、 L o w レベルを出力する。よって、論理和回路 2 1 9 は信号処理部 1 1 4 からの信号を出力し、該信号に基づく記録動作が適切に為される。

【 0 0 5 5 】

一方、電圧  $V_{H_T}$  が供給されていない場合には、検出部 2 1 8 のトランジスタ M P 1 7 は導通状態になり、検出部 2 1 8 は、抵抗素子 R 1 8 と R 1 9 との分圧電圧を出力する。該分圧電圧を受けた論理和回路 2 1 9 は H i レベルを出力し、トランジスタ M N 1 0 0 は導通状態になる。これによって、トランジスタ D M N 1 のソース電位が下がる。その結果、トランジスタ D M N 1 のゲート ソース間の電位差が小さくなる。

【 0 0 5 6 】

本実施形態では、検出部 2 1 8 と論理和回路 2 1 9 とを含むユニット 2 0 0 C の構成を例示した。しかしながら、論理和回路 2 1 9 の代わりに、他の論理回路を組み合わせた構成が採られてもよいし、検出部 2 1 8 の検出結果を受けてトランジスタ M N 1 0 0 を制御する制御部が設けられてもよい。

【 0 0 5 7 】

本実施形態では、レベルシフタ 1 1 5 を用いていないが、本実施形態においても、必要に応じてレベルシフタ 1 1 5 を用いた構成が採られることは言うまでもなく、この構成に限られるものではない。例えば、前述の第 1 実施形態等では、記録動作時に接地ノード ( G N D H ) の電位が変動しうることから、トランジスタ M N 1 0 0 が、信号処理部 1 1 4 からの信号を、レベルシフタ 1 1 5 を介してゲート端子で受ける構成とした。しかしながら、例えば、接地用の電源配線パターンの幅を大きくし、配線抵抗を十分に小さくする

10

20

30

40

50

ことによって、本実施形態のようにレベルシフタ 115 を用いない構成にすることも可能である。

【0058】

(第5実施形態)

前述の第1～第4実施形態では、電圧VHTが供給されていない場合に、ユニット200等を用いて、トランジスタDMN1のゲート～ソース間の電位差を小さくする様子を示した。しかしながら、電圧VHTは適切に記録素子基板に供給されたが、電圧VHが供給されない場合も考えられる。この場合にも対応可能な構成として、図9を参照しながら本実施形態の記録素子基板を述べる。

【0059】

10

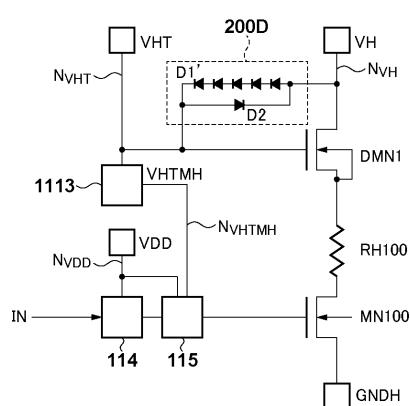

図9は、本実施形態の記録素子基板I15の構成例を示している。記録素子基板I15は、双方向ダイオードを含むユニット200Dを備えるという点で、第2実施形態(図5参照)の記録素子基板I12と異なる。ユニット200Dは、5段ダイオードD1'(第2実施形態と同様)の他、第2のダイオードD2をさらに含んでおり、ダイオードD1' とD2とが双方向ダイオードを形成している。

【0060】

ダイオードD2は、アノードがトランジスタDMN1のゲート端子に接続されており、カソードがトランジスタDMN1のドレイン端子に接続されている。

【0061】

20

例えば、電圧VHが供給されない場合には、電源ノードN<sub>VH</sub>の電位は不定状態(例えば0[V])となる。そのため、トランジスタDMN1のドレイン電位は不定になり、例えばドレイン電位が0[V]のときはチャネル電位ないしソース電位も0[V]になりうる。一方、トランジスタDMN1のゲートには電圧VHTが供給されるため、駆動トランジスタのゲート～ソース基板間で過電圧が生じ、絶縁破壊をもたらしうる。

【0062】

ここで、ユニット200DのダイオードD2に、順方向電圧よりも大きいバイアスが印加されたときには、ダイオードD2では順方向電流が流れる。この順方向電流により、電源ノードN<sub>VH</sub>の電位が大きくなり(即ち、トランジスタDMN1のドレイン電位が大きくなり)、その結果、トランジスタDMN1のゲート～ソース間の電位差が小さくなる。

【0063】

30

よって、本実施形態によると、前述の第1実施形態等と同様の効果が得られる他、電圧VHが供給されない場合においても駆動トランジスタの絶縁破壊を防ぐのに有利である。

【0064】

本実施形態では、双方向ダイオードとして、5段のダイオードD1'(N<sub>VH</sub>側がアノード、N<sub>VHT</sub>側がカソード)と、1段のダイオードD2(N<sub>VHT</sub>側がアノード、N<sub>VH</sub>側がカソード)と、を例示した。しかしながら、これらの段数は、前述(第1～第2実施形態)と同様で、記録素子基板I15の仕様等に基づいて、適宜、決定されればよい。例えば、これらの段数は、供給されるべき電源電圧VHとVHTとの大小関係に基づいて定められてもよい。具体的には、ダイオードD1'の段数をn1とし、ダイオードD2の段数をn2として、n1=n2としてもよい。また、VH>VHTとなる電源電圧を用いる構成では、n1>n2とすればよい。また、VH<VHTとなる電源電圧を用いる構成では、n1<n2とすればよい。

40

【0065】

また、本実施形態では、ダイオードD2について、アノードがトランジスタDMN1のゲート端子に接続され、カソードがトランジスタDMN1のドレイン端子に接続された構成を例示した。しかしながら、本発明はこの構成に限られるものではなく、ダイオードD2のカソードはトランジスタDMN1のソース端子およびバックゲート端子に接続されてもよいし、該ダイオードD2は、他の実施形態に適用されてもよい。

【0066】

(応用例)

50

以上の各実施形態では、説明を容易にするため、ヒータR H 1 0 0と、該ヒータR H 1 0 0に対応するトランジスタD M N 1と、該ヒータR H 1 0 0を通電させるためのトランジスタM N 1 0 0と、を1つずつ示した。実際には、記録動作は、複数のヒータを所定の駆動方式（例えば、時分割駆動方式）にしたがって駆動することによって為されうる。

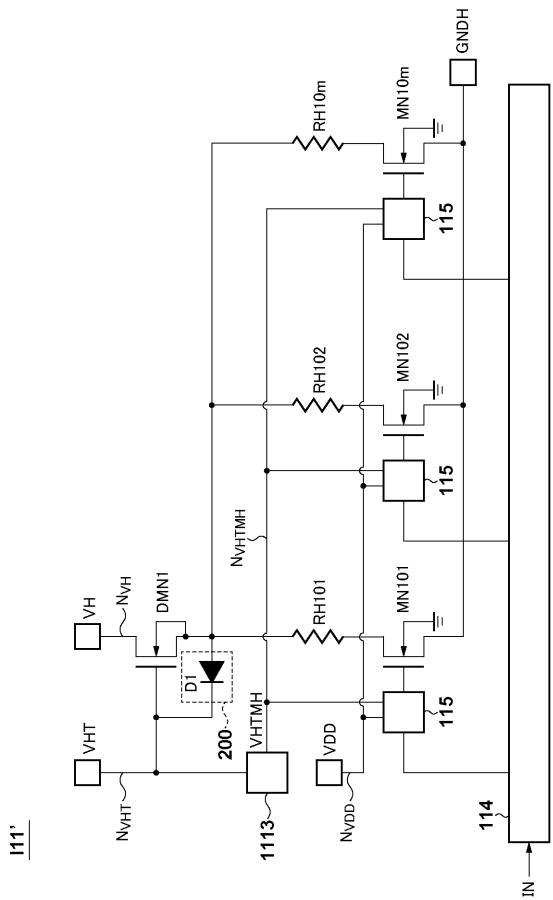

#### 【0067】

図10は、第1実施形態（図4参照）で述べた構成に基づいて、m個のヒータR H 1 0 1～R H 1 0 mが配列された記録素子基板I 1 1'の構成例を示している。記録素子基板I 1 1'は、ヒータR H 1 0 1～R H 1 0 mの他、トランジスタD M N 1と、ヒータR H 1 0 1～R H 1 0 mに対応するように配され、対応するヒータを駆動するためのm個のトランジスタM N 1 0 1～1 0 mと、を備えている。トランジスタD M N 1のソース端子は、ヒータR H 1 0 1～R H 1 0 mの一方の端に共通に接続されている。トランジスタD M N 1は、ソースフォロワ動作を行い、ヒータR H 1 0 1～R H 1 0 mのいずれかに定電流を供給する。この構成により、ヒータR H 1 0 1～R H 1 0 mのいずれかが駆動される。

#### 【0068】

前述のユニット200は、トランジスタD M N 1のソース端子およびバックゲート端子とゲート端子との間を電気的に接続するように配されている。

#### 【0069】

ヒータR H 1 0 1～R H 1 0 mと、1つのトランジスタD M N 1と、ヒータR H 1 0 1～R H 1 0 mとを含む上記グループを1つの単位として、2以上のグループを形成する場合も、同様にして記録素子基板を構成すればよい。即ち、各グループにおいて、ユニット200は、トランジスタD M N 1のソース端子およびバックゲート端子とゲート端子との間を電気的に接続するように配される。

#### 【0070】

##### （その他）

以上、いくつかの好適な実施形態を述べたが、本発明はこれらに限られるものではなく、記録素子基板の仕様等に応じて変更が可能であり、他の実施形態によっても為されうる。例えば、上記各実施形態で例示された各ユニット（ユニット200等の他、レベルシフタ115等の機能ユニットを含む）は、各々が同様の機能を有する構成を採ればよく、本発明はこれらの構成に限られるものではない。その他、例えば、以上の各実施形態では、記録素子としてヒータ（電気熱変換体）を用いた構成が示されたが、圧電素子を用いた記録方式その他の公知の記録方式が採られてもよい。また、例えば、各パラメータ（電圧の値など）は仕様に応じて変更されうるし、当該変更に合せて、各々が適切に動作するよう各ユニットの構成は変更されうる。

【図1】

【図2】

【図3】

【図4】

【図5】

【 図 6 】

【 四 7 】

【図8】

【 四 9 】

【図10】

---

フロントページの続き

(72)発明者 高木 誠

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 亀田 宏之

(56)参考文献 特開2010-155452 (JP, A)

特開2003-053973 (JP, A)

特開2007-173444 (JP, A)

特開2007-234718 (JP, A)

米国特許出願公開第2006/0072260 (US, A1)

(58)調査した分野(Int.Cl., DB名)

B41J 2/01 - 2/215