(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5013654号

(P5013654)

(45) 発行日 平成24年8月29日(2012.8.29)

(24) 登録日 平成24年6月15日(2012.6.15)

(51) Int.Cl.

G06F 12/00 (2006.01)

F 1

G06F 12/00 514 E

G06F 12/00 514 M

請求項の数 26 (全 21 頁)

(21) 出願番号 特願2003-330455 (P2003-330455)

(22) 出願日 平成15年9月22日 (2003.9.22)

(65) 公開番号 特開2004-288150 (P2004-288150A)

(43) 公開日 平成16年10月14日 (2004.10.14)

審査請求日 平成18年8月21日 (2006.8.21)

審判番号 不服2009-25159 (P2009-25159/J1)

審判請求日 平成21年12月18日 (2009.12.18)

(31) 優先権主張番号 10/390667

(32) 優先日 平成15年3月19日 (2003.3.19)

(33) 優先権主張国 米国(US)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路129

129, Samsung-ro, Yeon

gton-gu, Suwon-si, G

yeonggi-do, Republic

of Korea

(74) 代理人 100086368

弁理士 萩原 誠

(72) 発明者 ジンーアイオン リー

大韓民国キョンギード スウォンーシ パ

ルダルーク ヨントンードン シンナムジ

ル ミジュアパート652-1006

最終頁に続く

(54) 【発明の名称】フラッシュファイルシステム

## (57) 【特許請求の範囲】

## 【請求項1】

フラッシュファイルシステムであって、

フラッシュメモリと、

前記フラッシュメモリとホストシステムとの間をインターフェースするサブシステムと

、

を備え、

前記サブシステムが、

前記ホストシステムとインターフェースするホストシステムインターフェースと、

キャッシュメモリシステムと、

を有し、

前記キャッシュメモリシステムは、一定数のデータユニットの記憶容量を有するとともに、前記ホストシステムインターフェースを通じて前記ホストシステムから受信した論理アドレスに基づいて、前記ホストシステムインターフェースを通じて前記ホストシステムに（又はから）伝送するためのデータを記憶し、データは前記論理アドレスに関連して記憶され、また、

前記サブシステムはさらに、

前記キャッシュメモリシステムから受信した論理アドレスを、フラッシュメモリの物理アドレスにマッピングするフラッシュ変換階層ユニットと、

前記フラッシュメモリとインターフェースするフラッシュメモリインターフェースと、

を備え、

前記フラッシュ変換階層ユニットは物理アドレステーブルと論理アドレステーブルとを記憶し、

前記物理アドレステーブルは、

論理アドレスをインデックスとし、

各論理アドレスに対応する物理アドレスを示し、

前記論理アドレスと前記物理アドレスとの関連が有効であるか否かを示し、

前記論理アドレステーブルは、

物理アドレスをインデックスとし、

各物理アドレスに対応する論理アドレスを示し、

前記物理アドレスと前記論理アドレスとの関連が有効であるか否かを示し、

各物理アドレスに対し、フラッシュメモリのこの部分が消去されたか否かを示し、

前記フラッシュメモリインターフェースは、

前記フラッシュ変換階層ユニットから受信した物理アドレスに基づいて、前記キャッシュメモリシステムから前記フラッシュメモリにデータを伝送し、また、

前記フラッシュ変換階層ユニットから受信した物理アドレスに基づいて、前記フラッシュメモリから前記キャッシュメモリシステムにデータを伝送することを特徴とするフラッシュファイルシステム。

#### 【請求項 2】

請求項 1 に記載のフラッシュファイルシステムにおいて、

前記サブシステムがフラッシュメモリの物理的構成から独立したマッピングフォーマットを有することを特徴とするフラッシュファイルシステム。

#### 【請求項 3】

請求項 1 に記載のフラッシュファイルシステムにおいて、

前記マッピングフォーマットはホストシステムのデータ伝送ユニットと同じサイズであることを特徴とするフラッシュファイルシステム。

#### 【請求項 4】

請求項 3 に記載のフラッシュファイルシステムにおいて、

前記マッピングフォーマットはホストシステムのクラスタサイズを有することを特徴とするフラッシュファイルシステム。

#### 【請求項 5】

請求項 4 に記載のフラッシュファイルシステムにおいて、

前記マッピングフォーマットのサイズが 4 KB であることを特徴とするフラッシュファイルシステム。

#### 【請求項 6】

請求項 1 に記載のフラッシュファイルシステムにおいて、

前記キャッシュメモリシステムは、前記ホストシステムにより要求されたデータがキャッシュメモリシステムに常駐している場合、フラッシュメモリにアクセスせずに、ホストシステムに伝送するデータを出力することを特徴とするフラッシュファイルシステム。

#### 【請求項 7】

請求項 6 に記載のフラッシュファイルシステムにおいて、

前記キャッシュメモリシステムは、

一定数のデータ伝送ユニットの記憶容量を有するバッファメモリと、

ルックアップテーブルメモリと、

を備え、また、

前記ルックアップテーブルメモリは前記バッファメモリの各データユニットと関連のエントリを有し、

各エントリが、関連データユニットの論理アドレスとデータユニットでのデータの有効/無効を示すことを特徴とするフラッシュファイルシステム。

#### 【請求項 8】

10

20

30

40

50

請求項 7 に記載のフラッシュファイルシステムにおいて、

前記各エントリが、データユニット中のどのデータ部分がホストシステムによって変更

されたデータを含むのかを示すことを特徴とするフラッシュファイルシステム。

**【請求項 9】**

請求項 7 に記載のフラッシュファイルシステムにおいて、

前記各エントリが、全データユニットがホストシステムによって変更されたデータを含

むか否かを示すことを特徴とするフラッシュファイルシステム。

**【請求項 10】**

請求項 1 に記載のフラッシュファイルシステムにおいて、

前記論理アドレステーブルが、少なくともエラー補正コードデータを含む各物理アドレ

スインデックスに関連するその他のフィールドを含むことを特徴とするフラッシュファイ

ルシステム。 10

**【請求項 11】**

請求項 1 に記載のフラッシュファイルシステムにおいて、

前記フラッシュ変換階層ユニットが、

マッピングテーブルキャッシュと、

データのデータユニットの論理アドレスを含む前記マッピングテーブルキャッシュ内の

各エントリと、

前記データのデータユニットと関連する物理アドレスと、

前記論理アドレスと前記物理アドレスとの関連が有効であるか否かを示す有効性インジ

ケータと、

前記物理アドレスと関連する前記フラッシュメモリの一部分が消去されたか否かを示す

消去インジケータと、

を記憶することを特徴とするフラッシュファイルシステム。 20

**【請求項 12】**

フラッシュファイルシステムであって、

フラッシュメモリと、

前記フラッシュメモリとホストシステム間をインターフェースするサブシステムと、

を備え、

前記サブシステムがキャッシュメモリシステムを含み、また、

前記キャッシュメモリシステムは、

前記ホストシステムにより用いられる論理アドレスに従って前記フラッシュメモリに伝

送するデータを記憶し、

前記ホストシステムにより要求されたデータが前記キャッシュメモリシステム内に常駐

している場合に、前記フラッシュメモリにアクセスせずに、前記ホストシステムにデータ

を伝送するための出を行い、データは前記論理アドレスに関連して記憶され、

前記サブシステムが、

前記ホストシステムから受信した論理的アドレスをフラッシュメモリの物理アドレスに

マッピングするフラッシュ変換階層ユニットを有し、 30

前記フラッシュ変換階層ユニットは、物理アドレステーブル及び論理アドレステーブル

を記憶し、

前記物理アドレステーブルは、

論理アドレスをインデックスとし、

各論理アドレスに対応する物理アドレスを示し、

前記論理アドレスと前記物理アドレスとの関連が有効であるか否かを示し、

前記論理アドレステーブルは、

物理アドレスをインデックスとし、

各物理アドレスに対応する論理アドレスを示し、

前記物理アドレスと前記論理アドレスとの関連が有効であるか否かを示し、

各物理アドレスに対して前記フラッシュメモリのこの部分が消去されたか否かを示すこ 40

50

とを特徴とするフラッシュファイルシステム。

【請求項 1 3】

請求項1 2に記載のフラッシュファイルシステムにおいて、

前記キャッシュメモリシステムは、

一定数のデータユニットの記憶容量を有するバッファメモリと、

ルックアップテーブルメモリと、

を備え、前記ルックアップテーブルメモリが、

前記バッファメモリ内の各データユニットと関連するエントリと、

関連するデータユニットの論理アドレス及びデータユニットにおいてデータが有効であるか否かを示すエントリと、

を有することを特徴とするフラッシュファイルシステム。

10

【請求項 1 4】

請求項1 3に記載のフラッシュファイルシステムにおいて、

前記各エントリが、前記データユニット内のどのデータ部分が、前記ホストシステムにより変更されたデータを含むのかを示すことを特徴とするフラッシュファイルシステム。

【請求項 1 5】

請求項1 3に記載のフラッシュファイルシステムにおいて、

前記各エントリが、全データユニットが前記ホストシステムにより変更されたデータを含むか否かを示すことを特徴とするフラッシュファイルシステム。

【請求項 1 6】

請求項1 2に記載のフラッシュファイルシステムにおいて、

前記論理アドレステーブルが、少なくともエラー補正コードデータを含む各物理アドレスインデックスに関連するその他のフィールドを含むことを特徴とするフラッシュファイルシステム。

20

【請求項 1 7】

請求項1 2に記載のフラッシュファイルシステムにおいて、

前記フラッシュ変換階層ユニットが、

マッピングテーブルキャッシュと、

データのデータユニットの論理アドレスを含む前記マッピングテーブルキャッシュ内の各エントリと、

前記データのデータ伝送ユニットと関連する物理アドレスと、

前記論理アドレスと物理アドレスとの関連が有効であるか否かを示す有効性インジケータと、

前記物理アドレスと関連するフラッシュメモリの一部分が消去されたか否かを示す消去インジケータと、

を記憶することを特徴とするフラッシュファイルシステム。

30

【請求項 1 8】

フラッシュメモリのためのフラッシュファイル方法であって、

ホストシステムから受信した論理アドレスに基づくキャッシュメモリシステムにおいて、データを前記ホストシステムに（又は、から）伝送するために記憶する段階であって、前記キャッシュメモリシステムは、一定数のデータユニットの記憶容量を有し、かつ前記論理アドレスに関連して伝送するために前記データを記憶する段階と、

40

前記キャッシュメモリシステムから受信した論理アドレスをフラッシュメモリの物理アドレスにマッピングする段階と、

前記フラッシュメモリとインターフェースして、書き込みモードのマッピング段階から受信した物理アドレスに基づいてキャッシュメモリシステムからフラッシュメモリへデータを伝送する段階と、

読み出しモードでマッピング段階から受信した前記物理アドレスに基づいて前記フラッシュメモリから前記キャッシュメモリシステムにデータを伝送する段階と、

を備え、

50

物理アドレステーブルと論理アドレステーブルとを記憶し、

前記物理アドレステーブルは、

論理アドレスをインデックスとし、

各論理アドレスに対応する物理アドレスを示し、

前記論理アドレスと前記物理アドレスとの関連が有効であるか否かを示し、

前記論理アドレステーブルは、

物理アドレスをインデックスとし、

各物理アドレスに対応する論理アドレスを示し、

前記物理アドレスと論理アドレスとの対応関係が有効であるか否かを示し、

各物理アドレスに対し前記フラッシュメモリのこの部分が消去されたか否かを示し、 10

前記物理及び論理アドレステーブルに基づいたマッピング動作を実行するマッピング段階を備えることを特徴とするフラッシュファイル方法。

**【請求項 19】**

請求項18に記載のフラッシュファイル方法において、

前記マッピング段階で用いられたマッピングフォーマットはフラッシュメモリの物理的構成から独立していることを特徴とするフラッシュファイル方法。

**【請求項 20】**

請求項18に記載のフラッシュファイル方法において、

前記マッピング段階で用いられたマッピングフォーマットは、前記ホストシステムのデータ伝送ユニットと同一サイズであることを特徴とするフラッシュファイル方法。 20

**【請求項 21】**

請求項19に記載のフラッシュファイル方法において、

前記マッピングフォーマットは前記ホストシステムのクラスタサイズを有することを特徴とするフラッシュファイル方法。

**【請求項 22】**

請求項18に記載のフラッシュファイル方法において、

前記ホストシステムにより要求されたデータが前記キャッシュメモリシステムに常駐している場合に、前記フラッシュメモリにアクセスせずに前記ホストシステムにデータを伝送するために出力を行う段階を含むことを特徴とするフラッシュファイル方法。

**【請求項 23】**

請求項18に記載のフラッシュファイル方法において、

マッピングテーブルキャッシュと、

データのデータユニットに対する論理アドレスを含む前記マッピングテーブルキャッシュ内の各エントリと、

データのデータユニットと関連する物理アドレスと、

前記論理アドレスと物理アドレスとの対応関係が有効であるか否かを示す有効性インジケータと、

物理アドレスに対応するフラッシュメモリの一部分が消去されたか否かを示す消去インジケータと、

を記憶し、 40

前記マッピング段階が、前記物理アドレステーブルと、前記論理アドレステーブルと、前記マッピングテーブルキャッシュとに基づいたマッピング動作を実行することを特徴とするフラッシュファイル方法。

**【請求項 24】**

フラッシュメモリのためのフラッシュファイル方法であって、

ホストシステムの使用する論理アドレスに従って、キャッシュメモリシステムにおいてデータをフラッシュメモリに伝送するために記憶し、データは前記論理アドレスに関連して記憶され、

物理アドレステーブルと論理アドレステーブルとを記憶し、

前記物理アドレステーブルが論理アドレスをインデックスとし、前記論理アドレスと物 50

理アドレスの関連の有効／無効を示し、

前記論理アドレステーブルが物理アドレスをインデックスとし、前記物理アドレスと論理アドレスの関連の有効／無効を示し、

各物理アドレスに対し、前記フラッシュメモリのこの部分が消去されたか否かを示し、さらに、

前記ホストシステムから受信した論理アドレスを、前記物理及び論理アドレステーブルに基づいた前記フラッシュメモリの物理アドレスにマッピングし、

前記ホストシステムにより要求されたデータが前記キャッシュメモリシステムに常駐している場合に、フラッシュメモリにアクセスせずにデータをホストシステムに伝送するために出力することを特徴とするフラッシュファイル方法。 10

#### 【請求項 2 5】

請求項2 4に記載のフラッシュファイル方法において、

前記記憶段階が、前記キャッシュメモリシステムのバッファメモリ内に、フラッシュメモリに伝送するデータを記憶し、

前記バッファメモリは一定数のデータユニットの記憶容量を有しており、

前記出力段階が、前記バッファメモリの各データユニットに関連するエントリを有するルックアップテーブルメモリにアクセスして、前記バッファメモリからホストシステムに伝送するデータを出力し、

各エントリが、関連するデータユニットの論理アドレスとデータユニットでデータが有効であるか否かを示すことを特徴とするフラッシュファイル方法。 20

#### 【請求項 2 6】

請求項2 5に記載のフラッシュファイル方法において、

マッピングテーブルキャッシュと、

データのデータユニットの論理アドレスを含む前記マッピングテーブルキャッシュ内に各エントリと、

データのデータユニットと関連する物理アドレスと、

前記論理アドレスと物理アドレスの関連の有効／無効を示す有効性インジケータと、

前記物理アドレスに関連する前記フラッシュメモリの一部分が消去されたか否かを示す消去インジケータと、

を記憶しており、 30

前記マッピング段階が、前記物理アドレステーブル、前記論理アドレステーブル及び前記マッピングテーブルキャッシュに基づいたマッピング動作を実行することを特徴とするフラッシュファイル方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0 0 0 1】

本発明は電子記憶装置の分野に関するもので、より詳細には、フラッシュメモリとファイルシステムとに関する。

##### 【背景技術】

##### 【0 0 0 2】

近年、フラッシュメモリが用いられる範囲は益々拡大している。これは、フラッシュメモリに記憶された情報は、フラッシュメモリに電源が供給されなくても保持されるためである。また、フラッシュメモリはソリッドステート装置であり、携帯用コンピュータやデジタルスチルカメラなどの携帯用デバイスに非常に有用である。フラッシュメモリの消費電力は少なく、ハードディスクなど、様々な形態の磁気記憶媒体と比較してショックに強い。

##### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0 0 0 3】

フラッシュメモリには、NAND型とNOR型の2つの型がある。NOR型のフラッシュメモリは 40

50

ランダムアクセスを提供するが、生産コストが高い。反対に、NAND型フラッシュメモリは比較的安価であるが、書き出し操作が非効率的であるという問題を抱えている。

#### 【0004】

フラッシュメモリの一部に以前データがプログラムされていた（すなわち書き込まれていた）ことがある場合、フラッシュメモリのその一部にデータを再プログラム（すなわち上書き）するには、書き込み可能にするための消去操作を行う必要がある。この書き込み前の消去、すなわちEBW処理は非効率的である上、フラッシュメモリの寿命を制限する。

#### 【0005】

フラッシュメモリはトランジスタメモリセルである。このトランジスタメモリセルは、ホットエレクトロン、ソース注入、トンネルを通じてプログラム可能であるとともに、ファウラー・ノルドハイムトンネルメカニズムを通じて消去可能である。このようなメモリセルのプログラム及び消去を行うには、フローティングゲートを囲む誘電体を通過するための電流が必要とされる。よって、いつかは誘電体が劣化してしまうので、こうした型のメモリが有する消去・書き込み周期の回数は限られる。

#### 【0006】

EBW問題を緩和させるために、いくつかの技術が提案してきた。その一つの方法は、論理又は仮想アドレス方式を用いることである。例えば、ホストシステムが読み出し又は書き込み操作の論理アドレスをフラッシュメモリに提供すると、この論理アドレスはフラッシュメモリの物理アドレスにマッピングされる。この過程の間、データはフラッシュメモリの物理的空き領域に書き込まれる。そうすれば、消去操作を実行する必要がない。この技術は、物理アドレスに対して論理アドレスのマッピングテーブルを保持することを含む。通常、このマッピング操作には、変換とマッピング操作の両方が必要である。例えば、ホスト装置はクラスタと呼ばれる4KBのユニットデータに基づいた論理アドレスを供給することになる。言い換えれば、コンピュータなど、ホスト装置のファイルシステムは、クラスタサイズフォーマットを有する。

#### 【0007】

しかし、フラッシュメモリの物理アドレスはデータユニットに基づいて定められる。このユニットは一般的に16KB以上であり、一度に消去される可能性がある。また、従来のフラッシュメモリシステムにおけるフラッシュメモリのコントローラにより用いられるファイルシステムは、フラッシュメモリの物理的構造に基づいている。その結果、論理アドレスを物理アドレスにマッピングするためには、ホスト装置ファイルシステムをフラッシュメモリのファイルシステムに変換する作業も必要となる。

#### 【0008】

フラッシュメモリのためのマッピング情報は、フラッシュメモリを内蔵する装置に電源が供給されないときにも保持されていなければならない。フラッシュメモリ自体にこの情報を記憶することによって、フラッシュメモリの記憶容量が減少する。その結果、フラッシュメモリの構造は取り扱い困難なものになってしまう。

#### 【0009】

また、こうした従来のシステムにおけるフラッシュメモリのコントローラは、インターフェース構造を含む。インターフェース構造は、ホストインターフェース機能とフラッシュメモリインターフェース機能とを一体化させてるので、フラッシュメモリにおける変更や、ホストインターフェースにおける変更、あるいはインターフェース構造の一部分における変更には、フラッシュメモリシステム全体の再設計が必要となる。

#### 【0010】

本発明によるフラッシュファイルシステムは階層構造を有する。この階層構造は、フラッシュファイルシステム全体を再設計せずに、ホストシステム、フラッシュメモリ又はフラッシュファイルシステムの一部分を再設計することを可能にする。従って、本発明のフラッシュファイルシステムは特定の用途に対して極めてフレキシブルで、且つ容易に適用することができる。

10

20

30

40

50

**【課題を解決するための手段】****【0011】**

本発明の一実施例によるフラッシュファイルシステムは、フラッシュメモリとフラッシュメモリサブシステムを含む。フラッシュメモリサブシステムは、ホストシステムインターフェースと、キャッシングメモリシステムと、フラッシュ変換階層(FTL)部、及びフラッシュメモリインターフェースを含む。ホストシステムインターフェースはホストシステムとインターフェースする。キャッシングメモリシステムは一定数のデータユニットの記憶容量を有し、ホストシステムインターフェースを通じてホストシステムに(又はから)伝送するデータを記憶する。フラッシュ変換階層ユニットは、ホストシステムインターフェースとキャッシングメモリシステムを通じてホストシステムから受信された論理アドレスを、フラッシュメモリの物理アドレスにマッピングする。フラッシュメモリインターフェースはフラッシュメモリとインターフェースし、フラッシュ変換階層ユニットから受信した物理アドレスに基づいて、キャッシングメモリシステムからフラッシュメモリにデータを伝送するとともに、フラッシュ変換階層ユニットから受信した物理アドレスに基づいて、フラッシュメモリからキャッシングメモリにデータを伝送する。

**【0012】**

他の一実施例において、キャッシングメモリシステムは、ホストシステムが使用する論理アドレスに従ってフラッシュメモリに伝送するデータを記憶し、ホストシステムに要求されたデータがキャッシングメモリシステムに常駐している場合には、フラッシュメモリにアクセスせずにホストシステムに伝送するデータを出力する。また、他の実施例においては、キャッシングメモリシステムは、ホストシステムと同一のファイルシステムを用いる。従って、キャッシングメモリシステムにおいては、ホストシステムから受信した論理アドレスの変換は必要とされない。

**【0013】**

また、他の実施例において、フラッシュ変換階層ユニットはホストシステムと同じファイルシステムを用いる。従って、ホストシステムの受信した論理アドレスをフラッシュメモリの物理アドレスにマッピングするとき、フラッシュ変換階層ユニット(FTL)は、ホストシステムの論理アドレスを一つのマッピングフォーマット又はファイルシステムから別のマッピングフォーマット又はファイルシステムに変換する必要がない。より具体的には、フラッシュメモリサブシステムのファイルシステム及びマッピングフォーマットは、ホストシステムのファイルシステム及びマッピングフォーマットと同じデータユニットサイズに基づいている。従って、マッピングフォーマットは、フラッシュメモリの物理的構成からは独立している。一実施例においては、ファイルシステムとマッピングフォーマットは4KBのクラスタに基づいている。

**【0014】**

さらに他の実施例においては、フラッシュ変換階層ユニットは、物理アドレステーブルと論理アドレステーブルとを含む。物理アドレステーブルは論理アドレスをインデックスとし、各論理アドレスに対応する物理アドレスを示すとともに、論理アドレスと物理アドレスとの対応関係が有効であるか否かを示す。論理アドレステーブルは物理アドレスをインデックスとし、各物理アドレスに対応する論理アドレスを示すと共に、物理アドレスと論理アドレスとの対応関係が有効であるか否かを示す。また、各物理アドレスに対しては、フラッシュメモリのその部分が消去されたか否かが示される。論理アドレステーブルはさらに、エラー補正コード(ECC)データなどのデータを記憶するその他のフィールドを含む。

**【発明の効果】****【0015】**

本発明によるフラッシュファイルシステムは階層的構成を有し、これによってフラッシュファイルシステム全体を再設計することなく、ホストシステム、フラッシュメモリ又はフラッシュファイルシステムの一部分だけを再設計できるようになっている。従って、本発明のフラッシュファイルシステムは極めてフレキシブルで、且つ特定の応用例に容易に適

用することができる。

【0016】

キャッシュメモリシステムはホストシステムと同一のファイルシステムを用いるため、キャッシュメモリシステムにおいてはホストシステムから受信した論理アドレスの変換が要求とされない。

【0017】

さらに、FTLはホストシステムと同一のファイルシステムを用いる。結果的に、ホストシステムが受信した論理アドレスをフラッシュメモリの物理アドレスにマップする際、FTLは、ホストシステムの論理アドレスを一つのマッピングフォーマット又はファイルシステムから他のマッピングフォーマット又はファイルシステムに変換する必要がない。より具体的には、フラッシュメモリサブシステム14のファイルシステム及びマッピングフォーマットは、ホストシステムのファイルシステム及びマッピングフォーマットと同一のデータユニットサイズに基づいている。従って、マッピングフォーマットは、フラッシュメモリ6の物理的構成からは独立している。

【発明を実施するための最良の形態】

【0018】

本発明の実施形態について、以下に図面を用いて詳しく説明する。図面の対応する部分には同じ符号を付する。

【0019】

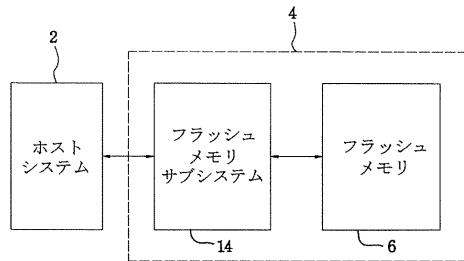

図1は、本発明の一実施例によるフラッシュファイルシステム4に連結されたホストシステム2を示す。図示したように、フラッシュファイルシステム4はフラッシュメモリサブシステム14に連結されたフラッシュメモリ6を含む。フラッシュメモリ6はNAND型フラッシュメモリである。フラッシュメモリサブシステム14は、ホストシステム2とフラッシュメモリ6との間のインターフェースとなる。

【0020】

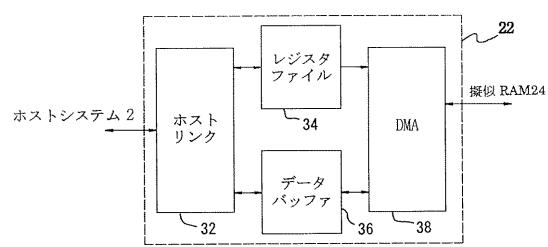

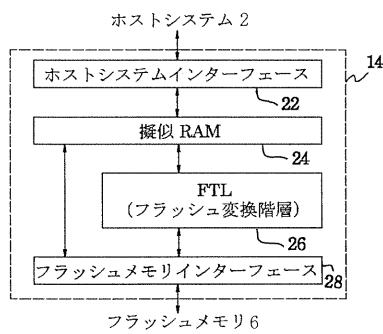

図2はフラッシュメモリサブシステム14の詳細図である。図示したように、フラッシュメモリサブシステム14は階層的構成を有する。その結果、フラッシュメモリ6又はホストシステム2を再設計する場合、フラッシュメモリサブシステム14全体を再設計する必要がなくなる。すなわち、図示したように、フラッシュメモリサブシステム14は、ホストシステム2とインターフェースするホストシステムインターフェース22を含む。擬似RAM24はホストシステムインターフェース22に連結され、キャッシングの一形態として動作するとともに、フラッシュメモリ6に書き込まれるデータとフラッシュメモリ6から読み出されるデータを一時的に記憶する。フラッシュ変換階層ユニット(FTL)26は、ホストシステム2から受信した論理アドレスを、フラッシュメモリ6の物理アドレスにマッピングする。フラッシュメモリインターフェース28は、擬似RAM24より受信したデータをFTL26により供給されたアドレスでフラッシュメモリ6に書き込み、FTL26により供給されたアドレスでフラッシュメモリ6からデータを読み込むことによって、フラッシュメモリ6とインターフェースする。

【0021】

以下、フラッシュメモリサブシステム14の各階層を詳しく説明する。

【0022】

ホストシステムインターフェース

ホストシステムインターフェース22はインターフェースプロトコルに従いホストシステム2とインターフェースする。インターフェースプロトコルとしては、多くの公知プロトコルを適用可能である。本発明は、コンパクトフラッシュ(登録商標)のような並列プロトコルと、マルチメディアカード(MMC)、SD(Secure Digital)、及びメモリスティックのような直列プロトコルの全てに適用可能である。また、さらに多目的なインターフェースを用いることも可能である。

【0023】

図3は、本発明によるホストシステムインターフェース22の一実施例を示す。図示し

10

20

30

40

50

たように、ホストリンク32はホストシステム2と通じている。ホストリンク32は特定のホストインターフェースタイミングプロトコルを含む。ホストリンク32を再設計するだけで、本発明によるホストシステムインターフェース22を用いる多様なインターフェースプロトコルを支援することができる。周知のように、レジスタファイル34はホストシステムインターフェース22の状態と動作パラメータとを記憶する。ホストシステム2に(又はから)伝送されるデータは、データバッファ36によりホストシステムインターフェース22に一時的に記憶される。データバッファ36は、ホストリンク32と直接メモリアクセス(DMA)38とに連結されている。DMA38はレジスタファイル34にも連結されており、ホストシステム2からフラッシュメモリサブシステム14の下位層に入力/出力要求を伝達する。特に、DMA38はデータバッファ36に記憶されたライト要求及び関連データを擬似RAM24に伝達するか、又はリード要求に従って擬似RAM24からデータを読み出し、そのデータをデータバッファ36に記憶する。

#### 【0024】

一実施例によると、DMA38は $512\text{ビット} \times n_s$ ( $n_s = 1, 2, 4, 8, 16$ )でデータを伝送し、従来の磁気ディスク記憶装置システムに由来するホストインターフェース方式を支援する。DMA38とホストリンク32との間のデータ伝送効率を高めるため、データバッファ36は $n \times$ バス幅の構成を有する。ここで、 $n$ はデータバッファ36のFI F0の寸法で、 $2, 4, 8, 16 \dots$ に等しく、そのバス幅は $8, 16, 32, 64 \dots$ に等しい。

#### 【0025】

##### 擬似RAM24

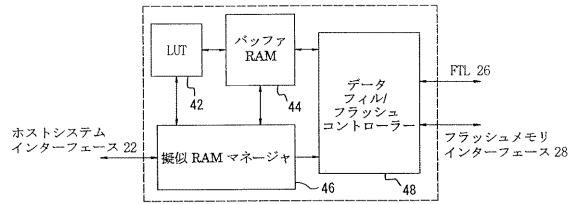

擬似RAM24は、ホストシステムインターフェース22が標準的なRAMに類似する形態でデータにアクセスできるようにする。図4に示されるように、擬似RAM24は、フラッシュメモリ6より読み出されたか又は書き込まれた最新のデータを記憶するバッファRAM44を含む。バッファRAM44に対応するルックアップテーブル(LUT)42は、バッファRAM44に記憶されているデータのディレクトリを保持する。データがフラッシュメモリ6に書き込まれるとき、又はフラッシュメモリ6から読み出されるとき、データファイル/フラッシュコントローラ48は、バッファRAM44とフラッシュメモリサブシステム14の下位層との間でインターフェースとして機能する。擬似RAMマネージャ46は、ホストシステムインターフェース22から受信したリード及びライト要求に基づいて、LUT42、バッファRAM44及びデータファイル/フラッシュコントローラ48の動作をコントロールする。

#### 【0026】

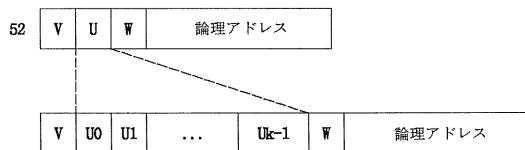

図5はLUT42に記憶されたディレクトリエントリのフィールド構成を示す。LUT42は、バッファRAM44に記憶された各データユニットのためのエントリ52を含む。本発明の一実施例においては、バッファRAM44に記憶されたデータユニットは、ホストシステム2でファイルシステムの基礎を形成するデータユニットと同一である。以下の記述からわかるように、フラッシュメモリサブシステム14は、ホストシステム2のファイルシステムと同じデータユニットに基づいたファイルシステムを採用している。例えば、本発明の一実施例において、ホストシステム2はクラスタと呼ばれる4KBのデータユニットを基本とするファイルシステムを有する。従って、バッファRAM44はクラスタユニット単位でデータを記憶し、LUT42は各クラスタのためのエントリ52を含む。以下により詳しく説明するように、バッファRAM44のファイルシステムはホストシステム2の使用しているファイルシステムと適合しているため、ホストシステム2からフラッシュメモリサブシステム14に供給される論理アドレスは、変換されることなくバッファRAM44から(又はバッファRAMに)直接データを読み出したり書き込んだりするのに用いられることがある。言い換えれば、フラッシュメモリサブシステム14のマッピングフォーマットはホストシステム2のそれと同一である。従って、フラッシュメモリサブシステム14のマッピングフォーマットとファイルシステムとは、フラッシュメモリ6の物理的構成からは独立している。

10

20

30

40

50

## 【0027】

図5を参照すると、LUT4\_2においてエントリ5\_2は、バッファRAM4\_4内の対応するデータユニットの論理アドレス、有効フィールドV、更新フィールドU及び書き込みフィールドWを含む。有効フィールドVは、エントリ5\_2の論理アドレスに対応するデータが有効であるかどうかを示す。更新フィールドUはバッファRAMでデータがホストシステム2により更新されたか否かを示す。実施例において、更新フィールドUはkサブフィールド(U0-Uk-1)から構成される。ここで、kはデータのサブユニットを示す。例えば、フラッシュメモリ6は通常それぞれ512バイトのページ又はセクタに編成される。ページサイズによってバッファRAM4\_4に記憶されたデータユニットのサイズを分割すると、k個のデータサブユニットが得られる。バッファRAM4\_4に記憶されたデータユニットを4KBのクラスタとする例に戻り、フラッシュメモリ6がそれぞれ512バイトのページに編成されたと仮定すると、更新フィールドUは8つ(即ち、k=8)のサブフィールド(U0-U7)から構成される。更新された各サブフィールド(U0-U7)は、バッファRAM4\_4に記憶されたデータのサブユニットが更新されたか否かを示す。

10

## 【0028】

書き込みフィールドWは、バッファRAM4\_4に記憶されたデータユニット内の全てのサブユニットが更新されたか否かを示す。上記の例を前提とすると、U0-Uk-1が全て1に設定されて、対応するサブユニットが更新されたことを示す場合、書き込みフィールドWもやはり1に設定される。以下に詳述するように、擬似RAMマネージャ4\_6は書き込みフィールドWを監視して、バッファRAM4\_4からフラッシュメモリ6にデータを書き込むタイミングを決定する。

20

## 【0029】

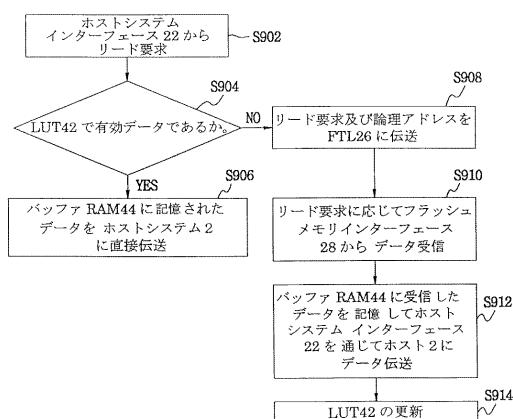

図6は、リード要求をホストシステムインターフェース2\_2から受信する場合の擬似RAM2\_4の動作を示す。図示したように、S9\_0\_2において、擬似RAMマネージャ4\_6はホストシステムインターフェース2\_2からリード要求を受信する。ホストシステム2から伝送されたリード要求には、論理アドレスが含まれている。続いて、擬似RAMマネージャ4\_6はLUT4\_2にアクセスし、LUT4\_2が(i)受信した論理アドレスと同一の論理アドレスを有するエントリ5\_2を含むか否かを判断するとともに、(ii)その論理アドレスの有効性フィールドVが、バッファRAM4\_4内にある対応するデータが有効であることを示すか否かを判断する(S9\_0\_4)。

30

## 【0030】

擬似RAMマネージャ4\_6が、バッファRAM4\_4に記憶されたデータが有効であると判断すると、擬似RAMマネージャ4\_6はバッファRAM4\_4から有効データを読み出し、ホストシステムインターフェース2\_2を通じてこのデータをホストシステム2に直接送る(S9\_0\_6)。従って、この方法において擬似RAM2\_4はフラッシュメモリ6に対してキャッシュの形で動作し、一層効率的な読み出し動作を行うことが可能になる。

## 【0031】

S9\_0\_4において、受信した論理アドレスに対して有効なエントリ5\_2を見つけることにRAMマネージャ4\_6が失敗すると、擬似RAMマネージャ4\_6はデータファイル/フラッシュコントローラ4\_8を制御し、FTL2\_6を通じてリード要求を伝送する(S9\_0\_8)。リード要求はホストシステムインターフェース2\_2から受信した論理アドレスを含む。以下詳細に説明するように、FTL2\_6は論理アドレスをフラッシュメモリ6の物理アドレスにマップして、この物理アドレスをリード要求と一緒にフラッシュメモリインターフェース2\_8に供給する。フラッシュメモリインターフェース2\_8は受信した物理アドレスとリード要求とに基づいてフラッシュメモリ6からデータを読み出し、読み出されたデータをデータファイル/フラッシュコントローラ4\_8に返す。従って、S9\_1\_0において、データファイル/フラッシュコントローラ4\_8はリード要求に応じてフラッシュメモリにインターフェース2\_8からデータを受信する。次いで、受信したデータはバッファRAM4\_4に記憶され、ホストシステムインターフェース2\_2を通じてホストシステム2に送られる(S9\_1\_2)。

40

。

50

## 【0032】

受信したデータをバッファRAM44に記憶する際、擬似RAMマネージャ46はLUT42を更新し(S914)、新しく記憶されたデータのエントリ52を含ませる。エントリ52はリード要求と共に受信した論理アドレスを含み、有効性フィールドVは有効データを示すよう設定され(例えばV=1)、更新フィールドU及び書き込みフィールドWには未更新データが設定される(例えば、U0-Uk-1=0やW=0)。

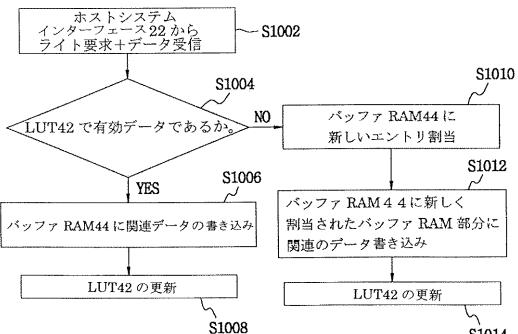

## 【0033】

次に、ライト要求をホストシステムインターフェース22から受信したときの擬似RAM24の動作について、図7を参照して説明する。S1002に示すように、擬似RAMマネージャ46は、ホストシステムインターフェース22を通じてホストシステム2からライト要求とデータを受信する。ライト要求に含まれるのは、受信したデータを書き込むための論理アドレスである。続いて、擬似RAMマネージャ46はLUT42にアクセスし、論理アドレスと同じ論理アドレスをエントリ52が有するか否か、そして、その論理アドレスの有効フィールドVが有効データを示すか否かを判断する(S1004)。受信した論理アドレスに適合する有効な論理アドレスを擬似RAMマネージャ46が見つけた場合、擬似RAMマネージャ46は受信したデータをバッファRAM44内に書き込み(S1006)、エントリ52の対応する更新サブフィールドを更新する(S1008)。

## 【0034】

S1004において、受信した論理アドレスに適合する有効な論理アドレスが見つからない場合、擬似RAMマネージャ46はバッファRAM44で新しいエントリを作成し(S1010)、受信したデータをバッファRAM44に書き込む(S1012)。バッファRAM44に新しいエントリを作成することは、LUT42に無効のエントリ52を設置することを含む。フラッシュメモリサブシステム14が最初に動作を開始するとき、LUT42の各エントリ52は無効のものとして初期化される。しかし、一定時間経過後であれば、LUT42に含まれるエントリが全部有効となる場合もある。このようにして、新しいエントリ52を作成する必要ができた場合、LUT42は更新サブフィールドセットを持たないエントリ52を設置し、このエントリ52に対応するバッファRAM44にデータを書き込む。(i)有効なエントリが存在しない場合、また、(ii)無効且つ未更新のエントリが存在する場合、バッファRAMマネージャ46は、データファイル/フラッシュコントローラ48にバッファRAM44の一部又は全てを放出するよう指示する。これは、放出されたバッファRAM44の内容を、フラッシュメモリ6に書き込むことを意味する。すると、放出されたデータに対応するエントリ52は、書き込み動作が実行される無効エントリとして設定される。続いて、擬似RAMマネージャ46はLUT42を更新し、新しく書き込まれたデータの新しいエントリ52を反映する(S1014)。新しいエントリ52はライト要求とともに受信した論理アドレスを含み、有効性ビットは有効なデータを示すように設定され、また、更新フィールドは更新データを示すように設定される。例えば、データのクラスタ全てが書き込まれるのであれば、書き込みフィールドWは、完全に更新されたエントリ52を示すようにセットされる(例えばW=1)。それ以外の場合、書き込みフィールドは、エントリ52が完全に更新されてはいないことを示すように設定される。

## 【0035】

上述したように、擬似RAMマネージャ46はLUT42のエントリ52を監視する。エントリが書き込みフィールドWを有し、その書き込みフィールドWが、バッファRAM44において完全に更新されたデータユニットを示す場合、擬似RAMマネージャ46はデータファイル/フラッシュコントローラ48に指示を送り、フラッシュメモリ6にデータが書き込まれるようにする。特に、この指示に応答して、データファイル/フラッシュコントローラ48は、ライト要求とそれに対応する論理アドレスとをFTL26に送るとともに、関連データをフラッシュメモリインターフェース28に送る。以下に詳しく説明するように、FTL26は受信した論理アドレスを物理アドレスにマップし、物理アドレスはライト要求と一緒にフラッシュメモリインターフェース28に供給される。次いで、フラッシュメモリインターフェース28は受信した物理アドレスを用いて受信したデータをフラッシュメモリ6

10

20

30

30

40

50

に書き込む。

【0036】

フラッシュ変換階層ユニット(FTL)26

読み出し及び書き込み動作のため、FTL26は、受信した論理アドレスを物理アドレスにマップする。フラッシュメモリ6のようなNAND型フラッシュメモリで書き込み動作をする前には、データ消去が必要とされる。このデータ消去は非効率性を引き起こす。マッピング動作は、この非効率性を緩和するために実行される。また、FTL26はホストシステム2が使用したものと同一のファイルシステムを採用する。これによって、ホストシステム2から受信した論理アドレスの変換をすることなく、論理アドレスから物理アドレスへの直接のマッピングが可能になる。例えれば、ホストシステムがデータユニットとしてクラスタに基づいたファイルシステムを使用するのであれば、FTL26の論理アドレスもクラスタに基づく。従って、FTL26は、フラッシュメモリ6の物理的構成から独立して設計される。10

【0037】

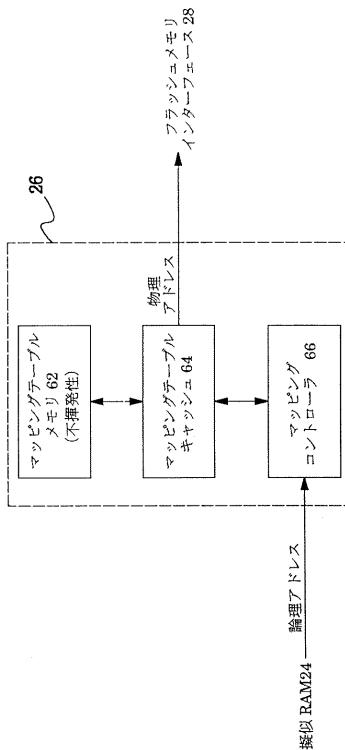

図8は、本発明によるFTL26の他の実施例を示す。図示したように、FTL26はマッピングテーブルメモリ62を含む。これは、実施例においては、NOR型フラッシュメモリのような不揮発性メモリである。マッピングテーブルメモリ62は、物理アドレステーブルと論理アドレステーブルとを含む。なお、論理アドレステーブルについては、図9と関連して以下に詳しく説明する。物理アドレステーブルは論理アドレスを物理アドレスにマップするためのもので、論理アドレステーブルは物理アドレスを論理アドレスにマップするためのものである。20

【0038】

図8にさらに示したように、FTL26はマッピングテーブルキャッシュ64を含む。マッピングテーブルキャッシュ64は、マッピングテーブルメモリ62に対してキャッシュとして動作するので、論理及び物理アドレスを互いにマップする際に、より高い効率性を提供することができる。マッピングテーブルメモリ62とマッピングテーブルキャッシュ64とは、マッピングコントローラ66によって制御され、擬似RAM24からリード及びライト要求を受信する。

【0039】

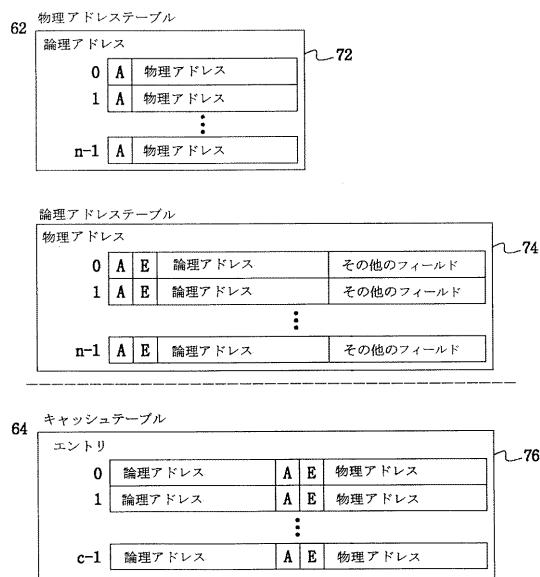

図9に、マッピングテーブルメモリ62とマッピングテーブルキャッシュ64とを詳しく示す。図示したように、マッピングテーブルメモリ62は、物理アドレステーブル72と論理アドレステーブル74とを含む。物理アドレステーブル72は使用可能な論理アドレスによってインデックスされる。言い換えれば、物理アドレステーブルの各エントリは、使用可能な論理アドレスにそれぞれ対応する。論理アドレスと対応する各アドレスは、割当フィールドAと物理アドレスフィールドとを含む。割当フィールドAは物理アドレスが論理アドレスと対応しているか否かを示し、物理アドレスフィールドは対応する物理アドレスを示す。30

【0040】

論理アドレステーブル74は使用可能な物理アドレスをインデックスとする。すなわち、論理アドレステーブル74の各エントリは、フラッシュメモリ6の使用可能な物理アドレスにそれぞれ対応する。論理アドレステーブル74の各エントリは、割当フィールドA、消去フィールドE、論理アドレスフィールド及びその他のフィールドを含む。割当フィールドAは、論理アドレスが物理アドレスと対応しているか否かを示す。消去フィールドEは、対応する物理アドレスが現在消去されているか否かを示す。論理アドレスフィールドは、物理アドレスに対応する論理アドレスを含み、その他のフィールドはエラー補正コードECCデータなどのデータを記憶する。40

【0041】

図9にさらに示したように、マッピングテーブルキャッシュ64のキャッシュテーブル76は複数のエントリを含む。各エントリは、論理アドレスフィールド、割当フィールドA、消去フィールドE、及び物理アドレスフィールドを含む。論理アドレスフィールドは、50

物理アドレスフィールドの物理アドレスに対応する論理アドレスのアクセスタグを含む。割当フィールドAは、論理アドレスと物理アドレスとの間の対応関係が有効であるか否かを示し、消去フィールドは、物理アドレスフィールドの物理アドレスが現在消去されているか否かを示す。

#### 【0042】

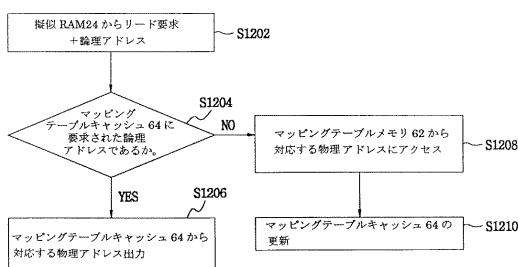

図10は、擬似RAM24からリード要求が受信される場合のFTL26の動作を示す。S1202に示すように、マッピングコントローラ66は擬似RAM24からリード要求と論理アドレスとを受信する。これに応じてマッピングコントローラ66はマッピングテーブルキャッシュ64にアクセスし、キャッシュテーブル76がエントリ内に受信した論理アドレスのタグ部分を含むか否か、そして、受信した論理アドレスと物理アドレスとの間に有効な対応関係が存在するか否かを判断する(S1204)。キャッシュテーブル76において受信した論理アドレスと物理アドレスとの間に有効な対応関係が存在するのであれば、マッピングコントローラ66はマッピングテーブルキャッシュ64に、対応する物理アドレスとリード要求とをフラッシュメモリインターフェース28へ出力する(S1206)。

#### 【0043】

受信した論理アドレスがキャッシュテーブル76の物理アドレスと対応していないのであれば、マッピングテーブルキャッシュ64は物理アドレステーブル72から受信した論理アドレスに対応する物理アドレスにアクセスする(S1208)。即ち、マッピングテーブルキャッシュ64は受信した論理アドレスをインデックスとして用いて、対応する物理アドレス72を得る。何らかの理由によって、論理アドレスが対応関係の無効な物理アドレスを含む場合(A=0)、受信した論理アドレスに対応する有効なデータは存在しないことになる。また、エラー状態がマッピングコントローラ66によって擬似RAM24に返される。このエラーは、ホストシステムインターフェース22を通じてホストシステム2に伝達される。

#### 【0044】

マッピングテーブルキャッシュ64は、物理アドレスをフラッシュメモリインターフェース28に出力するだけでなく、キャッシュテーブル76を更新して、受信した論理アドレスを含ませた後、物理アドレスをキャッシュテーブル76のエントリとして出力する。その際、マッピングテーブルキャッシュ64は、論理アドレステーブル74にもアクセスし、対応する物理アドレスの消去インジケータEの状態を取得する。

#### 【0045】

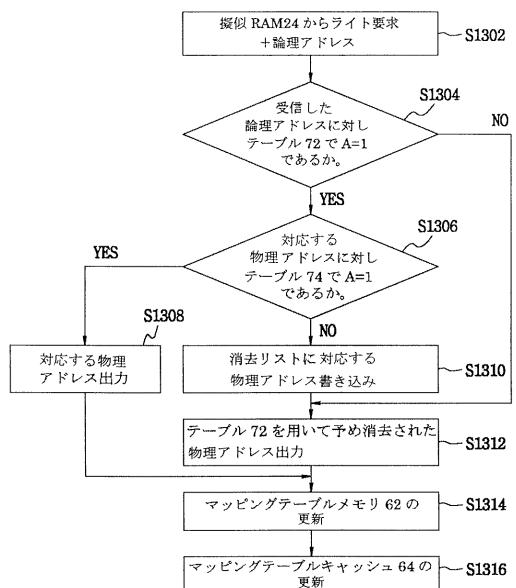

次に、図11を参照して、RAM24から受信したライト要求に関するFTL26の動作を説明する。図示したように、マッピングコントローラ66は擬似RAM24からライト要求、論理アドレス及び関連データを受信する(S1302)。マッピングコントローラ66は、マッピングテーブルキャッシュ64を通じてマッピングテーブル62にアクセスし、論理アドレステーブル72から、受信した論理アドレスが物理アドレスと対応しているか否かを判断する(S1304)。

#### 【0046】

すなわち、マッピングコントローラ66は、受信した論理アドレスをインデックスとして用い、エントリのA=1が受信した論理アドレスに対応するか否かを判断する。対応するのであれば、マッピングコントローラは物理アドレステーブル72から対応する物理アドレスにアクセスし、S1306で、検索した物理アドレスに対応するフラッシュメモリ6の一部分が消去されたか否かを判断する。特に、マッピングコントローラ66は、検索した物理アドレスをインデックスとして用いて、論理アドレステーブルで物理アドレスに対応する消去フィールドEが1であるかを判断する。その結果がE=1の場合は、論理アドレスと物理アドレスとの間の対応関係が有効であり、物理アドレスは消去状態にあって、書き込み動作が実行可能であることを示す。そして、マッピングコントローラ66はマッピングテーブルキャッシュ64に、検索した物理アドレスとライト要求とをフラッシュメモリインターフェース28に出力するよう命令する(S1308)。

## 【0047】

マッピングテーブルキャッシュ64が検索した物理アドレスを有していないのであれば、マッピングコントローラ66は物理アドレステーブル72に指示して、検索した物理アドレスを出力させる。また、マッピングコントローラ66はマッピングテーブルメモリ62を更新するとともに(S1314)、マッピングテーブルキャッシュを更新する(S1316)。特に、論理アドレステーブル74では、割当フィールドが設定され(例えばA=1)、出力物理アドレスに対応する消去フィールドEが変更されて、物理アドレスが現在消去されていないことを示す。また、受信した論理アドレスは論理アドレスフィールドに入力される。物理アドレステーブル72において、受信した論理アドレスの割当フィールドが設定され、出力物理アドレスは物理アドレスフィールドに入力される。キャッシュテーブル76に、物理アドレスに対応する受信した論理アドレスのエントリが存在するのであれば、類似の変更がなされる。キャッシュテーブル76にこのようなエントリが存在しないのであれば、エントリが作成される。

## 【0048】

S1306で検索した物理アドレスに対してE=1でない場合、検索した物理アドレスに対応するフラッシュメモリ6の記憶域は消去されていない。従って、書き込み前の消去動作が実行されない限り、この記憶域にデータを書き込むことはできない。そのため、マッピングコントローラ66は検索した物理アドレスを消去リスト上に載せる(S1310)。消去リストとは、消去する物理アドレスのリストである。この消去は定期的に行ってもよいし、効率性に影響を与えないイベント駆動時(例えば、プロセシングリソースやフラッシュメモリ6の読み出し/書き込み時)に行ってもよい。

## 【0049】

次に、マッピングコントローラ66は論理アドレステーブル74にアクセスし、消去状態の物理アドレスを見つける(S1312)。この物理アドレスは、ライト要求とともにフラッシュメモリインターフェース28に出力される。そして、マッピングコントローラ66はマッピングテーブルメモリ62とマッピングテーブルキャッシュ64とを更新する(S1314、S1316)。マッピングテーブルメモリ62を更新する際、物理アドレステーブル72を以下のように変更する。

## 【0050】

まず、受信した論理アドレスの割当フィールドAが設定されていない場合には設定し、論理アドレスの割当を示す。次に、受信した論理アドレスの物理アドレスフィールドに出力物理アドレスを入力する。論理アドレステーブル74で、受信した論理アドレスに以前対応していた物理アドレスの割当フィールドAを設定し(A=0)、物理アドレスが論理アドレスと対応しないことを示す。また、論理アドレステーブル74では、出力物理アドレスのエントリを以下のように変更する。割当フィールドを設定して割当を示し(A=1)、消去フィールドを設定して非消去状態を示す(E=0)。受信した論理アドレスは論理アドレスフィールドに入力する。マッピングテーブルキャッシュ64を更新する際には、受信した論理アドレス及び出力物理アドレスのエントリを作成するか、あるいは論理又は物理アドレスを含む任意のエントリ(または、更新されて無効となったことを示すエントリ)を上書きする。

## 【0051】

S1304に戻って説明すると、受信した論理アドレスの物理アドレステーブル72でA=1でなければ、論理アドレスには物理アドレスが割当てられていない。すると、処理はS1312まで行われ、そこから先は上述されたように進行する。

## 【0052】

図12は、FTL26がライト要求を処理する前後の物理アドレステーブル72と論理アドレステーブル74との一部分を示したものである。図12のテーブル1102と1104とは、ライト要求を受ける前の物理アドレステーブル72と論理アドレステーブル74とをそれぞれ示す。また、テーブル1106と1108とは、ライト要求を処理した後の物理アドレステーブル72と論理アドレステーブル74とをそれぞれ示す。図12に示し

た例では、ライト要求は論理アドレス # 0 に新しいデータを書き込む。図 11 に対応して上述した過程に従うと、S1304において、マッピングコントローラ 66 は、論理アドレス # 0 に対し A=1 を決定する(図 12 の 1102 参照)。それに合わせ、マッピングアドレスは、論理アドレス # 0 に対応する物理アドレスの消去状態を判断する(S1306)。図 12 の 1102 に示したように、論理アドレス # 0 に対応する物理アドレスは、物理アドレス # 31 である。また、同図の 1104 に示したように、物理アドレス # 31 の消去状態は 0 であり、消去されていないことを示す。従って、マッピングコントローラ 66 は、消去状態の新しい物理アドレスを見つける(S1308)。

#### 【0053】

図 12 を再度参照すると、マッピングコントローラ 66 は物理アドレス # 32 の位置を確認する。物理アドレス # 32 は、図 12 の 1104 に示したように消去状態にある。10

従って、S1308において、マッピングテーブルキャッシュ 64 すなわち物理アドレステーブル 72 からの物理アドレス出力は、物理アドレス # 32 である。

#### 【0054】

S1314において、マッピングコントローラ 66 はマッピングテーブルメモリ 62 を更新する。図 12 の 1106 にある物理アドレステーブル 72 は更新され、物理アドレス # 32 が論理アドレス # 0 と対応することを示す。図 12 の 1108 にある論理アドレステーブル 74 に対応して、物理アドレス # 31 の割当フィールド A は変更され、割当を示さない。物理アドレス # 32 の割当フィールド A は変更され、物理アドレスが割当てされることを示す。物理アドレス # 32 の消去状態は変更され、物理アドレス # 32 が消去状態ではないことを示す。また、物理アドレス # 32 に対応して論理アドレス # 0 が書き込まれる。20

#### 【0055】

##### フラッシュメモリインターフェース

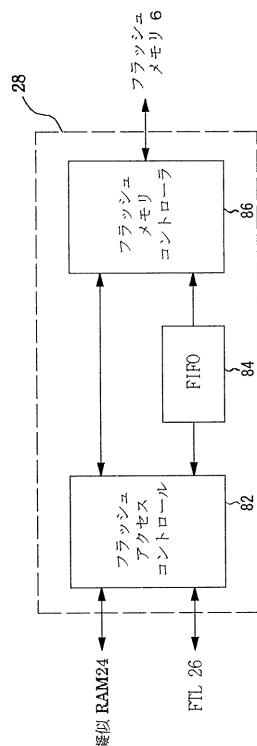

図 13 は、フラッシュメモリサブシステム 14 の最下位層であるフラッシュメモリインターフェース 28 を示す。具体的には、フラッシュメモリインターフェース 28 は、フラッシュメモリ 6 にデータを直接書き込んだり、フラッシュメモリ 6 からデータを直接読み出したりする。これは周知の通りである。

#### 【0056】

図 13 に示したように、フラッシュメモリインターフェース 28 は、フラッシュアクセスコントロール 82 とフラッシュメモリコントローラ 86 とを含む。フラッシュアクセスコントロール 82 は、フラッシュメモリサブシステム 14 の上位層とのインターフェースとして機能する。また、フラッシュメモリコントローラ 86 はフラッシュメモリ 6 との直接インターフェースとして機能する。フラッシュアクセスコントロール 82 とフラッシュメモリコントローラ 86 との間に配置されるのは、データ FIFO 84 である。これは、フラッシュアクセスコントロール 82 とフラッシュメモリコントローラ 86 との間で伝送するデータを記憶する。30

#### 【0057】

フラッシュアクセスコントロール 82 は、インターフェースとしての役割を果たす際に、データや命令ハンドシェイク信号を処理する。また、ECCの結果や、以前に書き込まれたECC値などを記憶するレジスタを含む。これは周知の通りである。フラッシュアクセスコントロール 82 の受信したライト又はリード要求がフラッシュメモリコントローラ 86 に直接伝送される一方で、書き込み動作の間に受信したデータは FIFO 84 を通じてフラッシュメモリコントローラ 86 に供給される。さらに、フラッシュアクセスコントロール 82 は、リード及びライト要求に対応して、フラッシュメモリコントローラ 86 に論理アドレスを直接供給する。40

#### 【0058】

フラッシュメモリコントローラ 86 は、フラッシュメモリコントロール信号を送出して読み出し(書き込み)プログラムと消去動作とを実行する。本発明の一実施例では、フラッシュメモリコントローラ 86 は、フラッシュメモリサブシステムと連結したフラッシュ50

メモリ 6 に依存しており、最も効率的な方法で動作するよう設計されている。また、効率を高めるために、FIFO 8 4 は  $n \times b$  s ビットのサイズを有するように構成される。ここで、n は FIFO の寸法を、b s はバスサイズを表す。

【 0 0 5 9 】

フラッシュメモリインターフェース 2 8 の構成及び動作は周知である。従って、簡潔にするために、この装置の構成と動作に対するさらに詳しい説明は省略する。

【 産業上の利用可能性 】

【 0 0 6 0 】

本発明は、上記説明のフラッシュファイルシステムに限定されず、様々なメモリ管理システムに利用することができる。

10

【 図面の簡単な説明 】

【 0 0 6 1 】

【図 1】本発明の一実施例によるフラッシュファイルシステムに連結したホストシステムのブロック図である。

20

【図 2】図 1 のフラッシュメモリサブシステムの詳細なブロック図である。

【図 3】図 2 のホストシステムインターフェースの詳細なブロック図である。

【図 4】図 2 の擬似RAMの詳細なブロック図である。

【図 5】図 4 でルックアップテーブルに記憶されたディレクトリエントリのフィールド構成図である。

【図 6】図 4 の擬似RAMにより実行される読み出し過程のフローチャートである。

20

【図 7】図 4 の擬似RAMにより実行される書き込み過程のフローチャートである。

【図 8】図 2 のフラッシュ変換階層ユニットの詳細なブロック図である。

【図 9】図 8 のマッピングテーブルメモリとマッピングテーブルキャッシュの詳細なブロック図である。

【図 10】図 8 のFTLにより実行される読み出し過程のフローチャートである。

【図 11】図 9 のFTLにより実行される書き込み過程のフローチャートである。

【図 12】書き込み動作例の前後のマッピングテーブルメモリ部分を示したブロック図である。

【図 13】図 2 のフラッシュメモリインターフェースの詳細なブロック図である。

30

【 符号の説明 】

【 0 0 6 2 】

- 2 ホストシステム

- 4 フラッシュファイルシステム

- 6 フラッシュメモリ

- 14 フラッシュメモリサブシステム

- 22 ホストシステムインターフェース

- 26 フラッシュ変換階層ユニット

- 28 フラッシュメモリインターフェース

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

【図 1 2】

| <Before> |     |        |        |

|----------|-----|--------|--------|

| 物理アドレス   | A   | 物理アドレス | 論理アドレス |

| #0       | 1   | #31    |        |

| ...      | ... | ...    |        |

| ...      | ... | ...    |        |

| <After> |     |     |        |

|---------|-----|-----|--------|

| 物理アドレス  | A   | E   | 論理アドレス |

| ...     | ... | ... | ...    |

| #31     | 1   | 0   | #0     |

| #32     | 0   | 1   | #1     |

| ...     | ... | ... | ...    |

1106

【図 1 3】

1108

| 物理アドレス | A   | E   | 論理アドレス | その他のアドレス | アドレス |

|--------|-----|-----|--------|----------|------|

| ...    | ... | ... | ...    | ...      | ...  |

| #31    | 1   | 0   | #0     | ...      | ...  |

| #32    | 0   | 1   | #1     | ...      | ...  |

| ...    | ... | ... | ...    | ...      | ...  |

1104

---

フロントページの続き

合議体

審判長 和田 志郎

審判官 甲斐 哲雄

審判官 山田 正文

(56)参考文献 特開平6 - 215589 (JP, A)

特開平1 - 288940 (JP, A)

小林 修, フラッシュEEPROM外部記憶装置向け使用環境整う, 日経エレクトロニクス, 日本, 日経BP社, 1994年 4月11日, 第605号, p. 75~83

(58)調査した分野(Int.Cl., DB名)

G06F 12/00

G06F 3/06