(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7164497号**

**(P7164497)**

(45)発行日 令和4年11月1日(2022.11.1)

(24)登録日 令和4年10月24日(2022.10.24)

(51)国際特許分類

|                        |     |              |         |

|------------------------|-----|--------------|---------|

| H 01 L 29/78 (2006.01) | F I | H 01 L 29/78 | 6 5 2 K |

| H 01 L 29/06 (2006.01) |     | H 01 L 29/06 | 3 0 1 F |

| H 01 L 29/41 (2006.01) |     | H 01 L 29/06 | 3 0 1 V |

| H 01 L 29/12 (2006.01) |     | H 01 L 29/44 | L       |

| H 01 L 21/336(2006.01) |     | H 01 L 29/44 | Y       |

請求項の数 10 (全17頁) 最終頁に続く

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2019-152836(P2019-152836) |

| (22)出願日  | 令和1年8月23日(2019.8.23)        |

| (65)公開番号 | 特開2021-34543(P2021-34543A)  |

| (43)公開日  | 令和3年3月1日(2021.3.1)          |

| 審査請求日    | 令和3年9月15日(2021.9.15)        |

|          |                                                 |

|----------|-------------------------------------------------|

| (73)特許権者 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号           |

| (73)特許権者 | 317011920<br>東芝デバイス＆ストレージ株式会社<br>東京都港区芝浦一丁目1番1号 |

| (74)代理人  | 100108062<br>弁理士 日向寺 雅彦                         |

| (74)代理人  | 100168332<br>弁理士 小崎 純一                          |

| (74)代理人  | 100146592<br>弁理士 市川 浩                           |

| (74)代理人  | 100157901<br>弁理士 白井 達哲                          |

| (74)代理人  | 100172188                                       |

最終頁に続く

(54)【発明の名称】 半導体装置

**(57)【特許請求の範囲】****【請求項1】**

第1電極と、

前記第1電極の上に設けられ、前記第1電極と電気的に接続された第1導電形の第1半導体領域と、

前記第1半導体領域の上に設けられた第2導電形の第2半導体領域と、

前記第2半導体領域の上に選択的に設けられた第1導電形の第3半導体領域と、

前記第1電極から前記第1半導体領域に向かう第1方向に垂直な第2方向において、前記第1半導体領域の一部、前記第2半導体領域、及び前記第3半導体領域と並ぶ第1絶縁部と、

前記第1絶縁部中に設けられ、前記第2方向において前記第1半導体領域と対向する部分を有する第2電極と、

前記第1絶縁部中に設けられ、前記第2方向においてゲート絶縁層を介して前記第2半導体領域と対向し、前記第2電極と電気的に分離されたゲート電極と、

前記第1絶縁部と連なり、前記第1方向における長さが前記第1半導体領域と前記第2電極との間の前記第1絶縁部の厚さよりも長く、前記第2方向における長さが前記第1絶縁部の厚さの2倍よりも短い第2絶縁部と、

前記第2半導体領域及び前記第3半導体領域の上に設けられ、前記第2半導体領域、前記第3半導体領域、及び前記第2電極と電気的に接続された第3電極と、

を備えた半導体装置。

**【請求項 2】**

前記第1電極と前記第1半導体領域との間に設けられた第1導電形の第4半導体領域をさらに備え、

前記第4半導体領域における第1導電形の不純物濃度は、前記第1半導体領域における第1導電形の不純物濃度よりも高く、

前記第2絶縁部の下端は、前記第1方向において前記第4半導体領域から離れている請求項1記載の半導体装置。

**【請求項 3】**

前記第2絶縁部の前記第2方向における長さは、下方に向かうほど短い請求項1又は2に記載の半導体装置。

10

**【請求項 4】**

前記第1絶縁部、前記第2絶縁部、前記ゲート電極、及び前記第2電極のそれぞれは、前記第2方向において複数設けられ、

前記第1半導体領域は、

前記第2方向において隣り合う前記第1絶縁部同士の間に位置する第1部分と、

前記第2方向において隣り合う前記第2絶縁部同士の間に位置する第2部分と、

を有し、

前記第2部分の前記第2方向における長さは、前記第1部分の前記第2方向における長さよりも長い請求項1～3のいずれか1つに記載の半導体装置。

**【請求項 5】**

前記第1絶縁部、前記第2絶縁部、前記ゲート電極、及び前記第2電極のそれぞれは、さらに、前記第1方向に垂直であり且つ前記第2方向と交差する第3方向において複数設けられ、

前記第2絶縁部の前記第3方向における長さは、前記第1絶縁部の厚さの2倍よりも短い請求項4記載の半導体装置。

20

**【請求項 6】**

前記第1半導体領域は、

前記第3方向において隣り合う前記第1絶縁部同士の間に位置する第3部分と、

前記第3方向において隣り合う前記第2絶縁部同士の間に位置する第4部分と、

を有し、

前記第4部分の前記第3方向における長さは、前記第3部分の前記第3方向における長さよりも長い請求項5記載の半導体装置。

30

**【請求項 7】**

前記第2絶縁部にボイドが設けられた請求項1～6のいずれか1つに記載の半導体装置。

**【請求項 8】**

前記第1絶縁部及び前記第2絶縁部は、酸化シリコンを含む請求項1～7のいずれか1つに記載の半導体装置。

**【請求項 9】**

前記第2電極の前記第1方向における長さに対する、前記第2絶縁部の前記第1方向における前記長さの比は、0.5以上2.0以下である請求項1～8のいずれか1つに記載の半導体装置。

40

**【請求項 10】**

前記第2電極の前記第2方向における長さに対する、前記第2絶縁部の前記第2方向における前記長さの比は、0.5以上2.0以下である請求項1～9のいずれか1つに記載の半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明の実施形態は、半導体装置に関する。

**【背景技術】**

50

**【0002】**

Metal Oxide Semiconductor Field Effect Transistor (MOSFET)などの半導体装置は、電力変換等の用途に用いられている。半導体装置のオン抵抗は、低いことが望ましい。

**【先行技術文献】****【特許文献】****【0003】**

**【文献】**特開2010-147475号公報

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

本発明が解決しようとする課題は、オン抵抗を低減できる半導体装置を提供することである。

**【課題を解決するための手段】****【0005】**

実施形態に係る半導体装置は、第1電極と、第1導電形の第1半導体領域と、第2導電形の第2半導体領域と、第1導電形の第3半導体領域と、第1絶縁部と、第2電極と、ゲート電極と、第2絶縁部と、第3電極と、を有する。前記第1半導体領域は、前記第1電極の上に設けられ、前記第1電極と電気的に接続されている。前記第2半導体領域は、前記第1半導体領域の上に設けられている。前記第3半導体領域は、前記第2半導体領域の上に選択的に設けられている。前記第1絶縁部は、前記第1電極から前記第1半導体領域に向かう第1方向に垂直な第2方向において、前記第1半導体領域の一部、前記第2半導体領域、及び前記第3半導体領域と並んでいる。前記第2電極は、前記第1絶縁部中に設けられ、前記第2方向において前記第1半導体領域と対向する部分を有する。前記ゲート電極は、前記第1絶縁部中に設けられ、前記第2方向においてゲート絶縁層を介して前記第2半導体領域と対向し、前記第2電極と電気的に分離されている。前記第2絶縁部は、前記第1絶縁部と連なる。前記第2絶縁部の前記第1方向における長さは、前記第1半導体領域と前記第2電極との間の前記第1絶縁部の厚さよりも長い。前記第2絶縁部の前記第2方向における長さは、前記第1絶縁部の厚さの2倍よりも短い。前記第3電極は、前記第2半導体領域及び前記第3半導体領域の上に設けられ、前記第2半導体領域、前記第3半導体領域、及び前記第2電極と電気的に接続されている。

**【図面の簡単な説明】****【0006】**

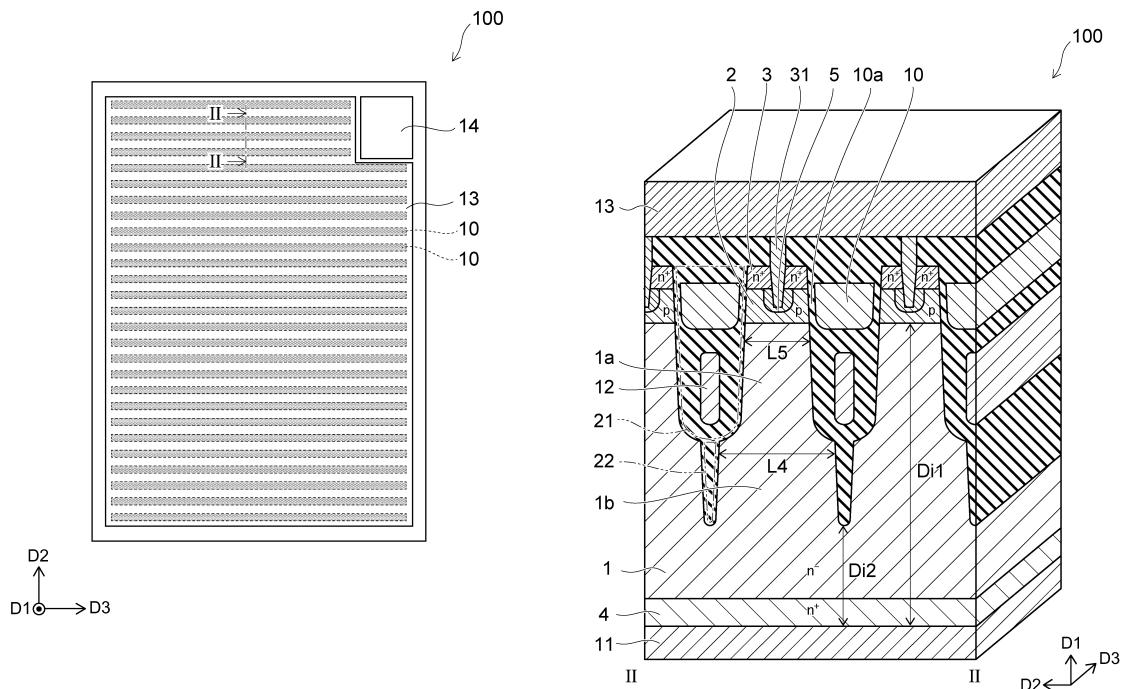

**【図1】**第1実施形態に係る半導体装置を表す平面図である。

**【図2】**図1のII-II断面を含む斜視断面図である。

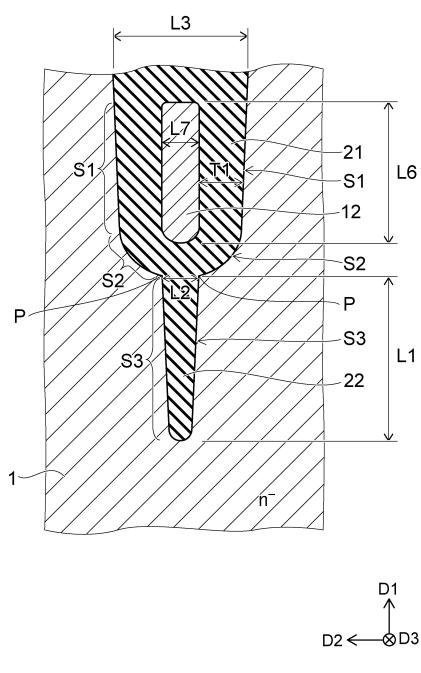

**【図3】**図2のフィールドプレート電極近傍を拡大した断面図である。

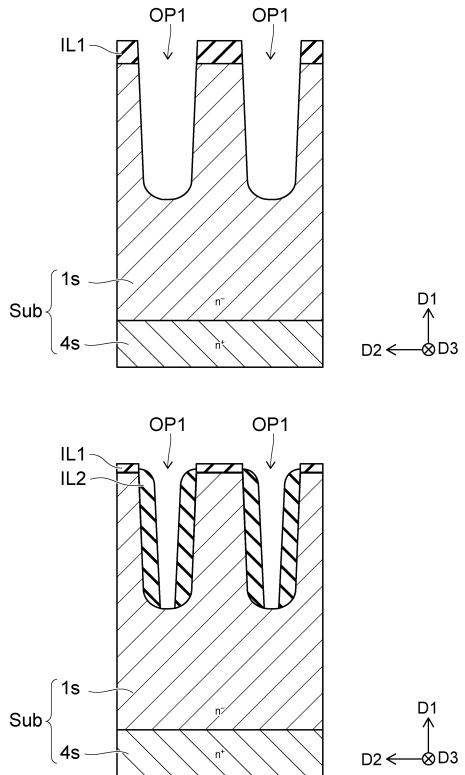

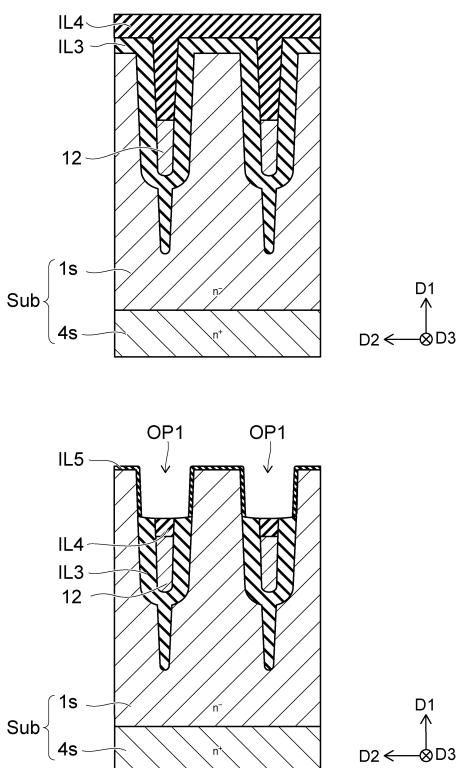

**【図4】**第1実施形態に係る半導体装置の製造工程を表す工程断面図である。

**【図5】**第1実施形態に係る半導体装置の製造工程を表す工程断面図である。

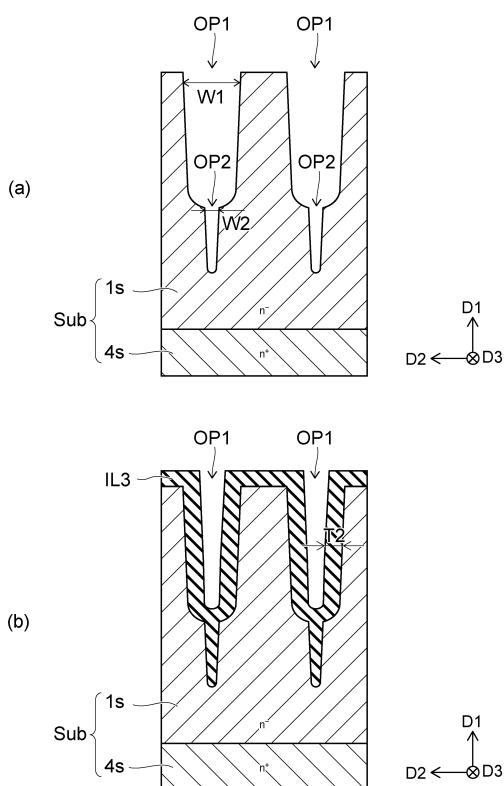

**【図6】**第1実施形態に係る半導体装置の製造工程を表す工程断面図である。

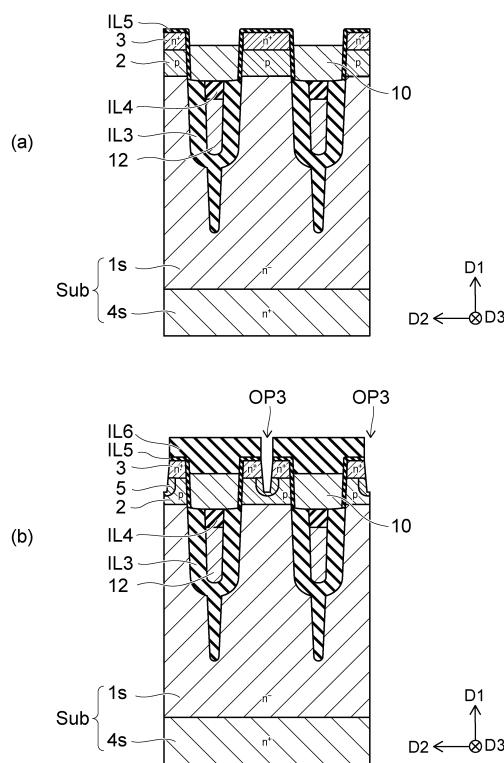

**【図7】**第1実施形態に係る半導体装置の製造工程を表す工程断面図である。

**【図8】**第1実施形態に係る半導体装置の製造工程を表す工程断面図である。

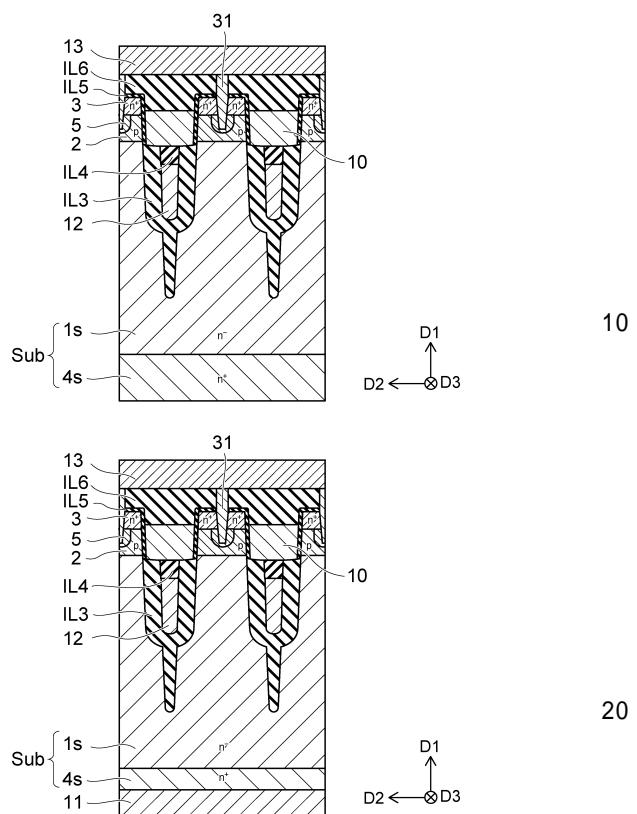

**【図9】**第1実施形態の第1変形例に係る半導体装置の一部を表す斜視断面図である。

**【図10】**第1実施形態の第2変形例に係る半導体装置の一部を表す斜視断面図である。

**【図11】**第2実施形態に係る半導体装置を表す平面図である。

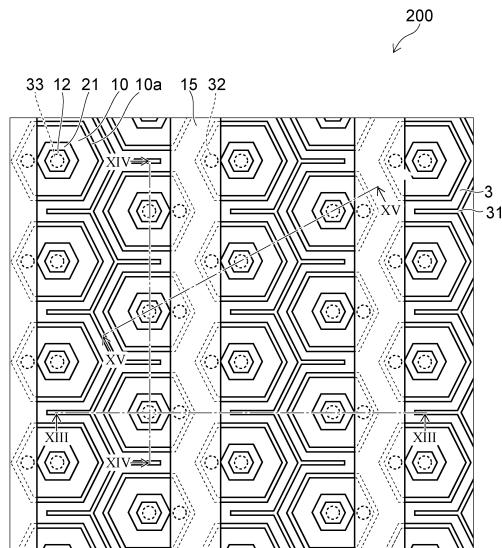

**【図12】**図11の部分XIIを表す平面図である。

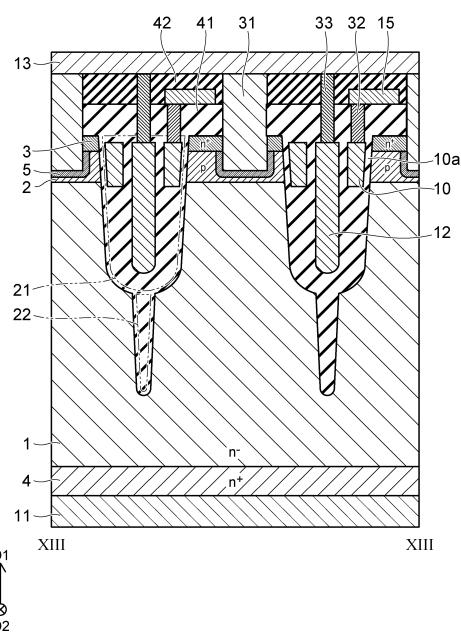

**【図13】**図12のXIII-XIII断面図である。

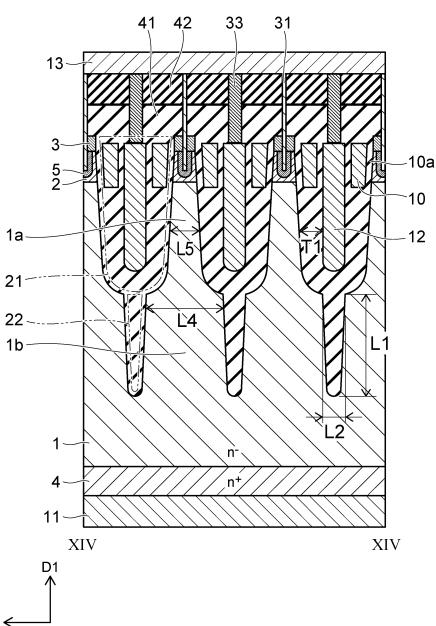

**【図14】**図12のXIV-XIV断面図である。

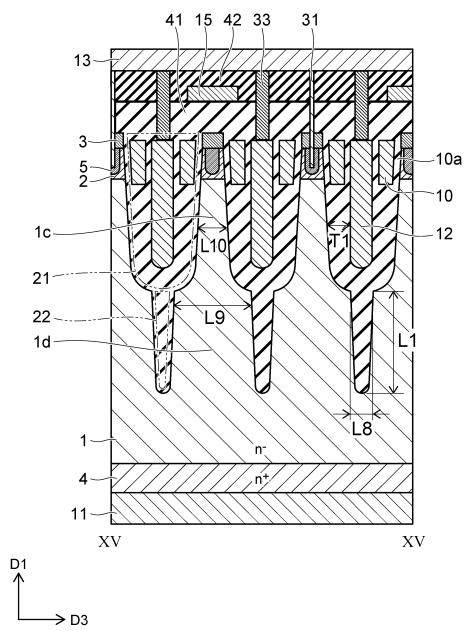

**【図15】**図12のXV-XV断面図である。

**【発明を実施するための形態】****【0007】**

10

20

30

40

50

以下に、本発明の各実施形態について図面を参照しつつ説明する。

図面は模式的または概念的なものであり、各部分の厚みと幅との関係、部分間の大きさの比率などは、必ずしも現実のものと同一とは限らない。同じ部分を表す場合であっても、図面により互いの寸法や比率が異なって表される場合もある。

本願明細書と各図において、既に説明したものと同様の要素には同一の符号を付して詳細な説明は適宜省略する。

以下の説明及び図面において、 $n^+$ 、 $n^-$ 及び $p^+$ 、 $p$ の表記は、各不純物濃度の相対的な高低を表す。すなわち、「+」が付されている表記は、「+」及び「-」のいずれも付されていない表記よりも不純物濃度が相対的に高く、「-」が付されている表記は、いずれも付されていない表記よりも不純物濃度が相対的に低いことを示す。これらの表記は、それぞれの領域に $p$ 形不純物と $n$ 形不純物の両方が含まれている場合には、それらの不純物が補償しあった後の正味の不純物濃度の相対的な高低を表す。

10

以下で説明する各実施形態について、各半導体領域の $p$ 形と $n$ 形を反転させて各実施形態を実施してもよい。

#### 【0008】

##### (第1実施形態)

図1は、第1実施形態に係る半導体装置を表す平面図である。

図2は、図1のII-II断面を含む斜視断面図である。

第1実施形態に係る半導体装置は、例えばMOSFETである。図1及び図2に表したように、第1実施形態に係る半導体装置100は、 $n^-$ 形(第1導電形)ドリフト領域1(第1半導体領域)、 $p$ 形(第2導電形)ベース領域2(第2半導体領域)、 $n^+$ 形ソース領域3(第3半導体領域)、 $n^+$ 形ドレイン領域4、 $p^+$ 形コンタクト領域5、ゲート電極10、ドレイン電極11(第1電極)、FP電極12(第2電極)、ソース電極13(第3電極)、ゲートパッド14、第1絶縁部21、第2絶縁部22、及び接続部31を有する。

20

#### 【0009】

以下の各実施形態の説明では、第1方向D1、第2方向D2、及び第3方向D3を用いる。ドレイン電極11から $n^-$ 形ドリフト領域1に向かう方向を第1方向D1とする。第1方向D1に垂直な一方向を、第2方向D2とする。第1方向D1に垂直であり、第2方向D2と交差する方向を、第3方向D3とする。また、説明のために、ドレイン電極11から $n^-$ 形ドリフト領域1に向かう方向を「上」と言い、その反対方向を「下」と言う。これらの方向は、ドレイン電極11と $n^-$ 形ドリフト領域1との相対的な位置関係に基づき、重力の方向とは無関係である。

30

#### 【0010】

図1に表したように、半導体装置100の上面には、ソース電極13及びゲートパッド14が設けられている。ソース電極13とゲートパッド14は、互いに電気的に分離されている。図1では、ソース電極13の下に設けられたゲート電極10がドットを付して表されている。図1に表したように、ゲート電極10は第2方向D2において複数設けられ、各ゲート電極10が第3方向D3に延びている。この例では、第3方向D3は、第2方向D2に対して垂直である。

40

#### 【0011】

図2に表したように、半導体装置100の下面には、ドレイン電極11が設けられている。ドレイン電極11の上には、 $n^+$ 形ドレイン領域4を介して $n^-$ 形ドリフト領域1が設けられている。 $n^-$ 形ドリフト領域1は、 $n^+$ 形ドレイン領域4を介してドレイン電極11と電気的に接続されている。 $p$ 形ベース領域2は、 $n^-$ 形ドリフト領域1の上に設けられている。 $n^+$ 形ソース領域3及び $p^+$ 形コンタクト領域5は、 $p$ 形ベース領域2の上に選択的に設けられている。

#### 【0012】

第1絶縁部21は、第2方向D2において、 $n^-$ 形ドリフト領域1の一部、 $p$ 形ベース領域2、及び $n^+$ 形ソース領域3と並んでいる。ゲート電極10及びFP電極12は、第

50

1 絶縁部 2 1 中に設けられている。FP 電極 1 2 は、第 2 方向 D 2 において n<sup>-</sup> 形ドリフト領域 1 と対向している。ゲート電極 1 0 は、FP 電極 1 2 の上に設けられている。ゲート電極 1 0 は、第 2 方向 D 2 において、第 1 絶縁部 2 1 の一部であるゲート絶縁層 1 0 a を介して、p 形ベース領域 2 と対向している。半導体装置 1 0 0 では、ゲート電極 1 0 は、ゲート絶縁層 1 0 a を介して n<sup>-</sup> 形ドリフト領域 1 の一部及び n<sup>+</sup> 形ソース領域 3 の一部とさらに対向している。ゲート電極 1 0 と FP 電極 1 2との間には、第 1 絶縁部 2 1 の一部が設けられている。これにより、ゲート電極 1 0 と FP 電極 1 2 は、互いに電気的に分離されている。

#### 【 0 0 1 3 】

第 2 絶縁部 2 2 は、第 1 絶縁部 2 1 の下に設けられ、第 1 絶縁部 2 1 と連なっている。FP 電極 1 2 は、第 1 絶縁部 2 1 の中にのみ設けられている。すなわち、FP 電極 1 2 は、第 2 絶縁部 2 2 の中には設けられていない。

#### 【 0 0 1 4 】

ソース電極 1 3 は、n<sup>+</sup> 形ソース領域 3 、p<sup>+</sup> 形コンタクト領域 5 、及びゲート電極 1 0 の上に設けられ、n<sup>+</sup> 形ソース領域 3 、p<sup>+</sup> 形コンタクト領域 5 、FP 電極 1 2 と電気的に接続されている。半導体装置 1 0 0 では、1 つの p 形ベース領域 2 の上に、1 つの p<sup>+</sup> 形コンタクト領域 5 及び 2 つの n<sup>+</sup> 形ソース領域 3 が設けられている。p<sup>+</sup> 形コンタクト領域 5 は、n<sup>+</sup> 形ソース領域 3 よりも下方に位置している。接続部 3 1 の一部は、第 2 方向 D 2 において、n<sup>+</sup> 形ソース領域 3 同士の間に位置する。n<sup>+</sup> 形ソース領域 3 及び p<sup>+</sup> 形コンタクト領域 5 は、接続部 3 1 を介して、ソース電極 1 3 と電気的に接続されている。p 形ベース領域 2 は、p<sup>+</sup> 形コンタクト領域 5 及び接続部 3 1 を介してソース電極 1 3 と電気的に接続されている。ゲート電極 1 0 は、ソース電極 1 3 とは電気的に分離され、ゲートパッド 1 4 と電気的に接続されている。

#### 【 0 0 1 5 】

例えば、p 形ベース領域 2 、n<sup>+</sup> 形ソース領域 3 、p<sup>+</sup> 形コンタクト領域 5 、ゲート電極 1 0 、FP 電極 1 2 、第 1 絶縁部 2 1 、及び第 2 絶縁部 2 2 は、第 2 方向 D 2 において複数設けられ、それぞれが、第 3 方向 D 3 に延びている。また、n<sup>-</sup> 形ドリフト領域 1 は、第 1 部分 1 a 及び第 2 部分 1 b を有する。第 1 部分 1 a は、第 2 方向 D 2 において隣り合う第 1 絶縁部 2 1 同士の間に位置する。第 2 部分 1 b は、第 2 方向 D 2 において隣り合う第 2 絶縁部 2 2 同士の間に位置する。複数の第 1 部分 1 a と複数の第 1 絶縁部 2 1 が、第 2 方向 D 2 において交互に設けられている。複数の第 2 部分 1 b と複数の第 2 絶縁部 2 2 が、第 2 方向 D 2 において交互に設けられている。

#### 【 0 0 1 6 】

図 3 は、図 2 の FP 電極 1 2 近傍を拡大した断面図である。

図 3 に表したように、第 2 絶縁部 2 2 の第 1 方向 D 1 における長さ L 1 は、n<sup>-</sup> 形ドリフト領域 1 と FP 電極 1 2 との間の第 1 絶縁部 2 1 の厚さ T 1 よりも長い。また、第 2 絶縁部 2 2 の第 2 方向 D 2 における長さ L 2 は、厚さ T 1 の 2 倍よりも短い。長さ L 2 が第 1 方向 D 1 において変化している場合、第 2 方向 D 2 において最も長い部分の長さを、長さ L 2 として用いる。

#### 【 0 0 1 7 】

第 1 絶縁部 2 1 と第 2 絶縁部 2 2 の境界は、例えば以下のように定めることができる。

第 1 絶縁部 2 1 は、一対の側面 S 1 及び一対の湾曲面 S 2 を有する。第 2 絶縁部 2 2 は、一対の側面 S 3 を有する。側面 S 1 は、第 1 方向 D 1 に沿う。すなわち、側面 S 1 の第 1 方向 D 1 に対する傾きは、側面 S 1 の第 2 方向 D 2 に対する傾きよりも小さい。湾曲面 S 2 の上端は、第 1 方向 D 1 に沿い、側面 S 1 と連なる。湾曲面 S 2 の下端は、第 2 方向 D 2 に沿い、側面 S 3 と連なる。すなわち、湾曲面 S 2 の第 1 方向 D 1 に対する傾きは、下方に向かうほど、大きくなっている。一方、側面 S 3 の上端の第 1 方向 D 1 に対する傾きは、側面 S 3 の上端の第 2 方向 D 2 に対する傾きよりも小さい。従って、湾曲面 S 2 と側面 S 3 との間には、第 1 方向 D 1 に対する傾きが第 2 方向 D 2 に対する傾きよりも小さくなる点 P が存在する。一対の湾曲面 S 2 と一対の側面 S 3 との間で、それぞれ点 P を求

10

20

30

40

50

める。これらの点 P を結んで得られる面を、第 1 絶縁部 2 1 と第 2 絶縁部 2 2 の境界と定義できる。第 2 絶縁部 2 2 の長さ L 1 は、この境界を基準にして求めることができる。

#### 【 0 0 1 8 】

第 2 絶縁部 2 2 の長さ L 2 が厚さ T 1 の 2 倍より短いと、長さ L 2 は、第 1 絶縁部 2 1 の第 1 方向 D 1 における長さ L 3 よりも短い。このため、n<sup>-</sup> 形ドリフト領域 1 については、図 2 に表したように、第 2 部分 1 b の第 2 方向 D 2 における長さ L 4 が、第 1 部分 1 a の第 2 方向 D 2 における長さ L 5 よりも長い。長さ L 4 及び L 5 のそれぞれが第 1 方向 D 1 において変化している場合、第 2 方向 D 2 において最も長い部分の長さを、それぞれ長さ L 4 及び L 5 として用いる。

#### 【 0 0 1 9 】

半導体装置 1 0 0 の動作について説明する。

ソース電極 1 3 に対してドレイン電極 1 1 に正電圧が印加された状態で、ゲート電極 1 0 に閾値以上の電圧を印加する。これにより、p 形ベース領域 2 にチャネル（反転層）が形成され、半導体装置 1 0 0 がオン状態となる。電子は、チャネルを通ってソース電極 1 3 からドレイン電極 1 1 へ流れる。その後、ゲート電極 1 0 に印加される電圧が閾値よりも低くなると、p 形ベース領域 2 におけるチャネルが消滅し、半導体装置 1 0 0 がオフ状態になる。

#### 【 0 0 2 0 】

半導体装置 1 0 0 がオフ状態に切り替わると、ソース電極 1 3 に対してドレイン電極 1 1 に印加される正電圧が増大する。正電圧の増大により、第 1 絶縁部 2 1 と n<sup>-</sup> 形ドリフト領域 1 との界面から n<sup>-</sup> 形ドリフト領域 1 に向けて、空乏層が広がる。この空乏層の広がりにより、半導体装置 1 0 0 の耐圧を高めることができる。又は、半導体装置 1 0 0 の耐圧を維持したまま、n<sup>-</sup> 形ドリフト領域 1 における n 形不純物濃度を高め、半導体装置 1 0 0 のオン抵抗を低減できる。

#### 【 0 0 2 1 】

半導体装置 1 0 0 の各構成要素の材料の一例を説明する。

n<sup>-</sup> 形ドリフト領域 1 、 p 形ベース領域 2 、 n<sup>+</sup> 形ソース領域 3 、 n<sup>+</sup> 形ドレイン領域 4 、及び p<sup>+</sup> 形コンタクト領域 5 は、半導体材料として、シリコン、炭化シリコン、窒化ガリウム、またはガリウムヒ素を含む。半導体材料としてシリコンが用いられる場合、n 形不純物として、ヒ素、リン、またはアンチモンを用いることができる。p 形不純物として、ボロンを用いることができる。

ゲート電極 1 0 及び F P 電極 1 2 は、ポリシリコンなどの導電材料を含む。導電材料には、不純物が添加されていても良い。

第 1 絶縁部 2 1 及び第 2 絶縁部 2 2 は、酸化シリコンなどの酸化物系の絶縁材料を含む。

ドレイン電極 1 1 、ソース電極 1 3 、及びゲートパッド 1 4 は、アルミニウム又は銅などの金属を含む。

接続部 3 1 は、タンゲステンなどの金属を含む。

#### 【 0 0 2 2 】

第 1 実施形態に係る半導体装置 1 0 0 の製造方法の一例を説明する。

図 4 ~ 図 8 は、第 1 実施形態に係る半導体装置の製造工程を表す工程断面図である。図 4 ~ 図 8 は、第 1 方向 D 1 及び第 2 方向 D 2 に平行な断面における製造工程を表す。

#### 【 0 0 2 3 】

n<sup>+</sup> 形半導体層 4 s と、n<sup>-</sup> 形半導体層 1 s と、を有する半導体基板 S u b を用意する。n<sup>-</sup> 形半導体層 1 s の上に絶縁層 I L 1 を形成し、フォトリソグラフィにより絶縁層 I L 1 をパターニングする。絶縁層 I L 1 をマスクとして用いて、n<sup>-</sup> 形半導体層 1 s の一部を除去し、図 4 ( a ) に表したように開口 O P 1 を形成する。開口 O P 1 は、第 2 方向 D 2 において複数形成され、各開口 O P 1 が第 3 方向 D 3 に延びている。

#### 【 0 0 2 4 】

熱酸化により、複数の開口 O P 1 の内面に沿って、複数の絶縁層 I L 2 をそれぞれ形成する。反応性イオンエッティング ( R I E ) などの異方性エッティングにより、開口 O P 1 の

側面に設けられた絶縁層 I L 2 を残しつつ、開口 O P 1 の底部に設けられた絶縁層 I L 2 を除去する。これにより、図 4 ( b ) に表したように、開口 O P 1 の底部にて n<sup>-</sup> 形半導体層 1 s が露出する。

#### 【 0 0 2 5 】

絶縁層 I L 1 及び I L 2 をマスクとして用いて、開口 O P 1 の底部に露出した n<sup>-</sup> 形半導体層 1 s を除去する。これにより、図 5 ( a ) に表したように、開口 O P 1 の底部に、開口 O P 2 が形成される。開口 O P 2 の幅 ( 第 2 方向 D 2 における寸法 ) W 2 は、開口 O P 1 の幅 W 1 よりも狭い。また、開口 O P 2 の幅 W 2 は、後に形成される絶縁層 I L 3 の厚さ T 2 の 2 倍よりも狭い。

#### 【 0 0 2 6 】

絶縁層 I L 1 及び I L 2 を除去する。これにより、絶縁層 I L 1 及び I L 2 に覆われていた n<sup>-</sup> 形半導体層 1 s の表面が露出する。熱酸化により、図 5 ( b ) に表したように、n<sup>-</sup> 形半導体層 1 s の表面に沿って絶縁層 I L 3 を形成する。絶縁層 I L 3 は、化学気相堆積 ( C V D ) により形成しても良い。上述した通り、開口 O P 2 の幅 W 2 は、絶縁層 I L 3 の厚さ T 2 の 2 倍よりも狭い。このため、開口 O P 2 の両側面から第 2 方向 D 2 に沿って形成される絶縁層 I L 3 により、開口 O P 2 が埋め込まれる。絶縁層 I L 3 の厚さ T 2 は、図 3 に表した第 1 絶縁部 2 1 の厚さ T 1 と対応し、厚さ T 1 と実質的に同じである。

#### 【 0 0 2 7 】

絶縁層 I L 3 の上に、複数の開口 O P 1 を埋め込む導電層を形成する。例えば、導電層は、不純物が添加されたポリシリコンを含む。導電層の上面を後退させ、それぞれの開口 O P 1 の内側に F P 電極 1 2 を形成する。図 6 ( a ) に表したように、絶縁層 I L 3 の上に、複数の F P 電極 1 2 を覆う絶縁層 I L 4 を形成する。

#### 【 0 0 2 8 】

絶縁層 I L 3 及び I L 4 の上面を後退させる。これにより、n<sup>-</sup> 形半導体層 1 s の表面の一部及び p 形ベース領域 2 の表面が露出する。熱酸化により、図 6 ( b ) に表したように、露出した n<sup>-</sup> 形半導体層 1 s の表面に沿って絶縁層 I L 5 を形成する。

#### 【 0 0 2 9 】

絶縁層 I L 5 の上に、複数の開口 O P 1 を埋め込む導電層を形成する。例えば、導電層は、不純物が添加されたポリシリコンを含む。導電層の上面を後退させ、それぞれの開口 O P 1 の内側にゲート電極 1 0 を形成する。n<sup>-</sup> 形半導体層 1 s の表面に p 形不純物をイオン注入し、p 形ベース領域 2 を形成する。このとき、ゲート電極 1 0 の下端は、n<sup>-</sup> 形半導体層 1 s と p 形ベース領域 2 との界面よりも下方に位置する。p 形ベース領域 2 の表面に n 形不純物をイオン注入し、図 7 ( a ) に表したように、n<sup>+</sup> 形ソース領域 3 を形成する。

#### 【 0 0 3 0 】

絶縁層 I L 5 の上に、複数のゲート電極 1 0 を覆う絶縁層 I L 6 を形成する。絶縁層 I L 6 、絶縁層 I L 5 、n<sup>+</sup> 形ソース領域 3 、及び p 形ベース領域 2 のそれぞれの一部を除去し、p 形ベース領域 2 に達する開口 O P 3 を形成する。複数の開口 O P 3 を通して、複数の p 形ベース領域 2 に p 形不純物をそれぞれイオン注入し、図 7 ( b ) に表したように、複数の p<sup>+</sup> 形コンタクト領域 5 を形成する。

#### 【 0 0 3 1 】

絶縁層 I L 6 の上に、タンゲステンを含む金属層を形成し、複数の開口 O P 3 を埋め込む。この金属層の上面を後退させることで、複数の n<sup>+</sup> 形ソース領域 3 及び複数の p<sup>+</sup> 形コンタクト領域 5 とそれ接続された複数の接続部 3 1 が形成される。絶縁層 I L 6 及び複数の接続部 3 1 の上に、アルミニウムを含む金属層を形成する。この金属層をパテニングすることで、図 8 ( a ) に表したソース電極 1 3 と、不図示のゲートパッド 1 4 と、が形成される。

#### 【 0 0 3 2 】

n<sup>+</sup> 形半導体層 4 s が所定の厚さになるまで、n<sup>+</sup> 形半導体層 4 s の裏面を研削する。その後、図 8 ( b ) に表したように、n<sup>+</sup> 形半導体層 4 s の裏面にドレイン電極 1 1 を形

10

20

30

40

50

成する。以上の工程により、図 1 ~ 図 3 に表した半導体装置 100 が製造される。

#### 【 0 0 3 3 】

上述した製造工程において、各構成要素の形成には、化学気相堆積 ( CVD ) 又はスパッタリングを用いることができる。各構成要素の一部の除去には、ウェットエッチング、ケミカルドライエッチング ( CDE ) 、又は反応性イオンエッチング ( RIE ) を用いることができる。各構成要素の上面の後退には、ウェットエッチング、CDE、又は化学機械研磨 ( CMP ) を用いることができる。

#### 【 0 0 3 4 】

第 1 実施形態の効果を説明する。

第 1 実施形態に係る半導体装置 100 は、第 1 絶縁部 21 の下において、第 1 絶縁部 21 と連なる第 2 絶縁部 22 を有する。第 1 絶縁部 21 及び第 2 絶縁部 22 は、図 5 ( a ) に表したように、半導体の熱酸化又は酸化物の CVD により形成される。これらの方法により形成された第 1 絶縁部 21 及び第 2 絶縁部 22 は、圧縮応力を有する。このため、第 1 絶縁部 21 及び第 2 絶縁部 22 を形成した際、第 1 絶縁部 21 同士の間、及び第 2 絶縁部 22 同士の間に位置する n- 形半導体層 1s に、第 1 絶縁部 21 及び第 2 絶縁部 22 の圧縮応力によって、第 1 方向 D1 に引っ張り応力が加わる。この引っ張り応力は、半導体装置 100 の製造が完了した後も残存する。この結果、図 2 に表した半導体装置 100 において、第 1 絶縁部 21 同士の間、及び第 2 絶縁部 22 同士の間に位置する n- 形ドリフト領域 1 には、引っ張りひずみが生じる。

半導体装置 100 がオン状態のとき、キャリアは第 1 方向 D1 に沿って流れる。換言すると、引っ張りひずみは、キャリアが流れる方向に沿って生じる。キャリアが流れる方向に沿って引っ張りひずみが生じると、キャリアの移動度が向上する。すなわち、n- 形ドリフト領域 1 に引っ張りひずみが生じることで、半導体装置 100 のオン抵抗を低減できる。例えば、第 1 絶縁部 21 及び第 2 絶縁部 22 の両方が設けられることで、第 1 絶縁部 21 のみしか設けられていない場合に比べて、n- 形ドリフト領域 1 のより広い範囲に引っ張りひずみを発生させることができる。

#### 【 0 0 3 5 】

第 2 絶縁部 22 の第 1 方向 D1 における長さ L1 は、n- 形ドリフト領域 1 と FP 電極 12 との間の第 1 絶縁部 21 の厚さ T1 よりも長い。これにより、第 2 絶縁部 22 同士の間ににおいて n- 形ドリフト領域 1 に生じるひずみを大きくできる。例えば、長さ L1 が厚さ T1 よりも短いと、第 2 絶縁部 22 から離れた領域では、十分な引っ張りひずみが生じず、キャリアの移動度の向上が小さい。

また、第 2 絶縁部 22 が設けられていると、第 1 絶縁部 21 よりも下方の領域において、電流が流れる経路が狭くなる。半導体装置 100 では、第 2 絶縁部 22 の第 2 方向 D2 における長さ L2 が、厚さ T1 の 2 倍よりも短い。このため、n- 形ドリフト領域 1 の第 2 部分 1b の長さ L4 を、n- 形ドリフト領域 1 の第 1 部分 1a の長さ L5 よりも長くできる。これにより、第 2 絶縁部 22 が設けられている場合でも、第 2 絶縁部 22 同士の間ににおける電流経路の幅が狭くなることを抑制できる。

すなわち、上述した長さ L1 、長さ L2 、及び厚さ T1 の関係によれば、第 2 絶縁部 22 に起因した引っ張りひずみに基づくオン抵抗の低減の効果を、第 2 絶縁部 22 を設けることによるオン抵抗の増加の効果よりも大きくできる。従って、第 1 絶縁部 21 のみしか設けられていない場合に比べて、半導体装置 100 のオン抵抗を低減できる。

#### 【 0 0 3 6 】

さらに、長さ L2 が厚さ T1 の 2 倍よりも短いと、図 5 ( b ) に表したように、第 1 絶縁部 21 の一部を形成すると同時に、第 2 絶縁部 22 を形成できる。これにより、半導体装置 100 をより容易に製造できるようになる。

#### 【 0 0 3 7 】

第 2 絶縁部 22 の下端が n+ 形ドレイン領域 4 に達するように、第 2 絶縁部 22 が設けられていても良い。好ましくは、第 2 絶縁部 22 の下端は、図 2 に表したように、第 1 方向 D1 において n+ 形ドレイン領域 4 から離れている。第 2 絶縁部 22 が n+ 形ドレイン

10

20

30

40

50

領域4から離れていると、第2絶縁部22よりも下方において、電流経路の幅がより広くなる。また、第2絶縁部22の形成が容易となり、半導体装置100の歩留まりを向上できる。

#### 【0038】

以下は、好ましい寸法比の一例である。

F P電極12の第1方向D1における長さL6（図3に示す）に対する長さL1の比は、0.5以上2.0以下である。F P電極12の第2方向D2における長さL7に対する長さL2の比は、0.5以上2.0以下である。ドレイン電極11とp形ベース領域2との間の第1方向D1における距離Di1（図2に示す）に対する、ドレイン電極11と第2絶縁部22との間の第1方向D1における距離Di2の比は、0.1以上0.5以下である。

10

#### 【0039】

長さL6に対する長さL1の比については、比が小さすぎると、発生するひずみが小さくなり、オン抵抗の低減効果が小さくなる。一方で、比が大きすぎると、電流経路の幅が狭くなり、電流経路が狭小になる。この結果、オン抵抗が増加する。

長さL7に対する長さL2の比については、比が小さすぎると、発生するひずみが小さくなり、オン抵抗の低減効果が小さくなる。一方で、比が大きすぎると、電流経路が狭小になり、オン抵抗が増加する。

距離Di1に対する距離Di2の比については、比が小さすぎると、電流経路が狭小となり、オン抵抗が増加する。一方で、比が大きすぎると、発生するひずみが小さくなり、オン抵抗の低減効果が小さくなる。

20

#### 【0040】

長さL6に対する長さL1の比、長さL7に対する長さL2の比、及び距離Di1に対する距離Di2の比の少なくともいずれかが、上述した範囲にあることで、電流経路の狭小化に起因したオン抵抗の増加に対する、引っ張りひずみに起因したオン抵抗の低減の割合を、より大きくできる。これにより、半導体装置100のオン抵抗をさらに低減することができる。また、3つの比の全てが上述した範囲にあることで、オン抵抗をより一層低減できる。

#### 【0041】

##### （第1変形例）

30

図9は、第1実施形態の第1変形例に係る半導体装置の一部を表す斜視断面図である。

図9に表した半導体装置110では、複数の第2絶縁部22の少なくとも一部に、ボイドVが設けられている。ボイドVは、第2絶縁部22の内部に存在する空洞である。例えば、ボイドVの第1方向D1における寸法は、ボイドVの第2方向D2における寸法よりも長い。ボイドVは、第1方向D1に沿って線状に設けられていても良い。

#### 【0042】

ボイドVが設けられていると、第2絶縁部22からn-形ドリフト領域1に加わる応力が緩和される。例えば、ボイドVが大きいほど、応力がより緩和される。ボイドVを第2絶縁部22に設けることで、n-形ドリフト領域1に加わる応力を調整できる。

#### 【0043】

ボイドVを形成するためには、例えば、図5(a)に表した工程において、絶縁層IL3をCVDにより形成する。このとき、成膜条件を供給律速よりの条件にすることで、開口OP2の上端付近における酸化物の堆積速度を、開口OP2の中部における酸化物の堆積速度よりも大きくできる。この結果、開口OP2の内部に材料が完全に堆積していない状態で、開口OP2の上端が閉塞される。これにより、開口OP2内に設けられた絶縁層IL3の内部にボイドVを形成できる。

40

#### 【0044】

ただし、より小さな第2絶縁部22によって、より大きなひずみをn-形ドリフト領域1に発生させるためには、第2絶縁部22にボイドVが無いことが好ましい。ボイドVの形成を抑制するためには、開口OP2の側面が第1方向D1に対して傾斜していることが

50

好みしい。開口OP2の側面を傾斜させることで、開口OP2の内部に材料が完全に堆積していない状態で、開口OP2の上端が閉塞することを抑制できる。開口OP2の側面が第1方向D1に対して傾斜している場合、第2絶縁部22の第2方向D2における長さは、下方に向かうほど短くなる。

#### 【0045】

##### (第2変形例)

図10は、第1実施形態の第2変形例に係る半導体装置の一部を表す斜視断面図である。

図10に表した半導体装置120では、1つの第1絶縁部21の下に、複数の第2絶縁部22が設けられている。複数の第2絶縁部22は、第3方向D3において互いに離れている。このため、半導体装置120がオン状態のとき、第3方向D3において隣り合う第2絶縁部22同士の間をキャリアが移動できる。

10

#### 【0046】

第2変形例に係る半導体装置120によれば、半導体装置100に比べて、第1絶縁部21の下方における電流経路の幅をより広くできる。このため、第2変形例によれば、オン抵抗をより低減できる。

#### 【0047】

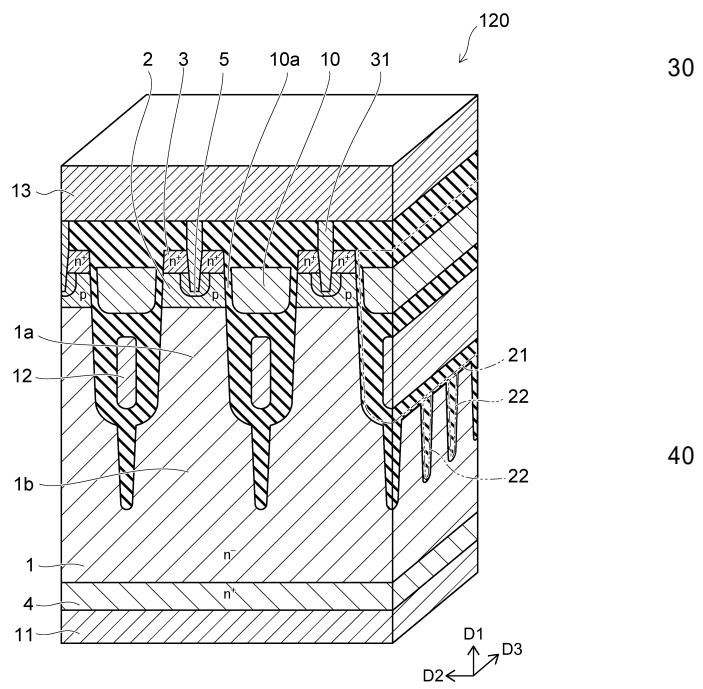

##### (第2実施形態)

図11は、第2実施形態に係る半導体装置を表す平面図である。

図12は、図11の部分XIIを表す平面図である。図12では、ソース電極13、絶縁層41、及び絶縁層42が省略されている。

20

図13は、図12のXIII-XIII断面図である。図14は、図12のXIV-XIV断面図である。図15は、図12のXV-XV断面図である。

第2実施形態に係る半導体装置200は、半導体装置100と比べて、ゲート配線層15、接続部32、接続部33、絶縁層41、及び絶縁層42をさらに有する。

#### 【0048】

図12～図15に表したように、半導体装置200では、ゲート電極10、FP電極12、第1絶縁部21、及び第2絶縁部22が、第2方向D2及び第3方向D3において複数設けられている。図12に表したように、第1方向D1から見たときのゲート電極10の形状は、環状である。FP電極12は、ゲート電極10の内側に位置する。p形ベース領域2、n<sup>+</sup>形ソース領域3、及びp<sup>+</sup>形コンタクト領域5は、第2方向D2及び第3方向D3において、各第1絶縁部21の周りに設けられている。

30

#### 【0049】

図13に表したように、ゲート配線層15は、ゲート電極10の上に絶縁層41を介して設けられている。接続部32は、ゲート電極10とゲート配線層15との間に設けられ、ゲート電極10とゲート配線層15を電気的に接続している。ソース電極13は、ゲート配線層15の上に絶縁層42を介して設けられている。接続部33は、FP電極12とソース電極13との間に設けられ、FP電極12とソース電極13とを電気的に接続している。接続部31は、ゲート配線層15が設けられていない位置において、n<sup>+</sup>形ソース領域3及びp<sup>+</sup>形コンタクト領域5をソース電極13と電気的に接続している。

#### 【0050】

図12に表したように、ゲート配線層15は、第3方向D3において複数設けられ、各ゲート配線層15は、第2方向D2に延びている。各ゲート配線層15は、第2方向D2に並んだゲート電極10の上に設けられ、第2方向D2に並んだゲート電極10と電気的に接続されている。図13に表したように、ソース電極13は、複数のゲート配線層15の上に絶縁層42を介して設けられている。

40

#### 【0051】

ゲートパッド14は、例えば図11に表したように、絶縁層42の上に設けられ、ソース電極13から離れている。ゲート配線層15とゲートパッド14は、絶縁層42を貫通する不図示の接続部により、互いに電気的に接続される。又は、ゲートパッド14は、絶縁層41の上に設けられていても良い。この場合、ゲートパッド14は、ソース電極13

50

よりも下方に位置する。

#### 【0052】

図14に表したように、半導体装置200においても、第2絶縁部22の第1方向D1における長さL1は、n-形ドリフト領域1とFP電極12との間の第1絶縁部21の厚さT1よりも長い。第2絶縁部22の第2方向D2における長さL2は、厚さT1の2倍よりも短い。また、図15に表したように、第2絶縁部22の第3方向D3における長さL8は、厚さT1の2倍よりも短い。

#### 【0053】

n-形ドリフト領域1は、図14及び図15に表したように、第1部分1a～第4部分1dを有する。第1部分1aは、第2方向D2において隣り合う第1絶縁部21同士の間に位置する。第2部分1bは、第2方向D2において隣り合う第2絶縁部22同士の間に位置する。第3部分1cは、第3方向D3において隣り合う第1絶縁部21同士の間に位置する。第4部分1dは、第3方向D3において隣り合う第2絶縁部22同士の間に位置する。

第2部分1bの第2方向D2における長さL4は、第1部分1aの第2方向D2における長さL5よりも長い。第4部分1dの第3方向D3における長さL9は、第3部分1cの第3方向D3における長さL10よりも長い。

#### 【0054】

第2実施形態によれば、ゲート電極10が、第2方向D2及び第3方向D3において複数設けられている。この構造によれば、半導体装置200がオン状態のとき、各ゲート電極10の周囲にチャネルが形成される。このため、半導体装置100に比べて、単位面積あたりのチャネルの面積を増大させることができ、オン抵抗をさらに低減できる。

#### 【0055】

さらに、第1実施形態と同様に、第1絶縁部21の下に第2絶縁部22が設けられることで、第2絶縁部22同士の間のn-形ドリフト領域1に引っ張りひずみを発生させることができる。また、長さL1は、厚さT1よりも長い。長さL2及びL8のそれぞれは、厚さT1の2倍よりも短い。この関係によれば、第2絶縁部22による引っ張りひずみに基づくオン抵抗の低減の効果を、第2絶縁部22を設けることによるオン抵抗の増加の効果よりも大きくできる。従って、第1絶縁部21のみしか設けられていない場合に比べて、半導体装置200のオン抵抗を低減できる。

また、長さL2及びL8のそれぞれが厚さT1の2倍よりも短いと、第2絶縁部22の形成が容易となり、半導体装置200の歩留まりを向上できる。

#### 【0056】

以上で説明した各実施形態における、各半導体領域の間の不純物濃度の相対的な高低については、例えば、SCM(走査型静電容量顕微鏡)を用いて確認することが可能である。なお、各半導体領域におけるキャリア濃度は、各半導体領域において活性化している不純物濃度と等しいものとみなすことができる。従って、各半導体領域の間のキャリア濃度の相対的な高低についても、SCMを用いて確認することができる。また、各半導体領域における不純物濃度については、例えば、SIMS(二次イオン質量分析法)により測定することが可能である。

#### 【0057】

以上、本発明のいくつかの実施形態を例示したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更などを行うことができる。これら実施形態やその変形例は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。また、前述の各実施形態は、相互に組み合わせて実施することができる。

#### 【符号の説明】

#### 【0058】

1 n-形ドリフト領域、 1a 第1部分、 1b 第2部分、 1c 第3部分、 1d

10

20

30

40

50

第4部分、1 s n<sup>-</sup>形半導体層、2 p形ベース領域、3 n<sup>+</sup>形ソース領域、4 n<sup>+</sup>形ドレイン領域、4 s n<sup>+</sup>形半導体層、5 p<sup>+</sup>形コンタクト領域、10 ゲート電極、10a ゲート絶縁層、11 ドレイン電極、12 フィールドプレート電極、13 ソース電極、14 ゲートパッド、15 ゲート配線層、21 第1絶縁部、22 第2絶縁部、31～33 接続部、41, 42 絶縁層、100, 110, 120, 200 半導体装置、I L 1～I L 6 絶縁層、O P 1～O P 3 開口、S 1 側面、S 2 湾曲面、S 3 側面、Sub 半導体基板、V ボイド

【図面】

【図1】

【図2】

10

20

30

40

50

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 1 1】

D<sub>2</sub>

D<sub>1</sub> →

D<sub>3</sub>

【図 1 2】

10

D<sub>2</sub>

D<sub>1</sub> →

D<sub>3</sub>

20

【図 1 3】

【図 1 4】

30

40

50

【図15】

10

20

30

40

50

---

フロントページの続き

(51)国際特許分類

| F I                  |

|----------------------|

| H 01 L 29/78 6 5 2 F |

| H 01 L 29/78 6 5 2 M |

| H 01 L 29/78 6 5 2 P |

| H 01 L 29/78 6 5 2 Q |

| H 01 L 29/78 6 5 2 T |

| H 01 L 29/78 6 5 3 C |

| H 01 L 29/78 6 5 8 F |

弁理士 内田 敬人

(74)代理人 100197538

弁理士 竹内 功

(72)発明者 西脇 達也

東京都港区芝浦一丁目1番1号 東芝デバイス&amp;ストレージ株式会社内

審査官 上田 智志

(56)参考文献 特開2013-58575 (JP, A)

特開2009-54638 (JP, A)

米国特許出願公開第2012/0319199 (US, A1)

米国特許出願公開第2007/0138544 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

H 01 L 21/336, 29/06, 29/12,

29/41, 29/78