(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-180583

(P2011-180583A)

(43) 公開日 平成23年9月15日(2011.9.15)

(51) Int.Cl.

**G02F 1/1368 (2006.01)**

**G09F 9/30 (2006.01)**

**G09F 9/00 (2006.01)**

F 1

GO2F 1/1368

GO9F 9/30 338

GO9F 9/30 349Z

GO9F 9/00 366A

テーマコード(参考)

2H092

5C094

5G435

審査請求 未請求 請求項の数 8 O L (全 36 頁)

(21) 出願番号 特願2011-21175 (P2011-21175)

(22) 出願日 平成23年2月2日 (2011.2.2)

(31) 優先権主張番号 特願2010-24643 (P2010-24643)

(32) 優先日 平成22年2月5日 (2010.2.5)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

F ターム(参考) 2H092 JA26 JB05 JB07 JB13 JB56

KA08 KB25 KB26 LA01 NA07

NA26 PA06 PA09

5C094 AA06 AA10 BA03 BA14 BA43

CA19 DA13 EA04 ED15 FA01

FA02 FB02 FB12 FB14 FB15

5G435 AA02 AA03 BB12 CC09 EE49

FF13 HH12 HH13 HH14

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】反射型液晶表示装置において、隣接する画素間にあって、画素電極が設けられていない間隙は、画素に占める表示領域の割合、所謂開口率の低下を招く。その結果、表示画像のコントラスト、及び明るさが損なわれてしまうという問題があった。表示画像のコントラストが高く、また表示画像が明るい液晶表示装置を提供することを課題とする。

【解決手段】液晶表示装置の画素電極の端部を、隣接する画素電極の端部に絶縁層を挟んで重ねて設け、隣接する画素間にある間隙を狭め、画素に占める表示領域の割合を高めればよい。

【選択図】図4

**【特許請求の範囲】****【請求項 1】**

絶縁層と、

それぞれ独立したスイッチング素子とそれぞれ電気的に接続する第1の画素電極及び第2の画素電極と、

前記第1の画素電極及び前記第2の画素電極に対向する対向電極と、

前記第1の画素電極及び前記第2の画素電極と対向電極の間に液晶層を有し、

前記第2の画素電極の端部が、前記絶縁層を介して前記第1の画素電極の端部の上に重ねて設けられている液晶表示装置。

**【請求項 2】**

さらに着色された絶縁層を有し、前記着色された絶縁層は前記第2の画素電極の端部から延在して第1の画素電極の上面に重なる請求項1記載の液晶表示装置。

**【請求項 3】**

前記着色された絶縁層が前記第1の画素電極の上面に重なる前記第2の画素電極の側面を覆う請求項2記載の液晶表示装置。

**【請求項 4】**

前記スイッチング素子に、酸化物半導体を有するトランジスタを用いる請求項1乃至請求項3のいずれかに記載の液晶表示装置。

**【請求項 5】**

第1の絶縁層と、第2の絶縁層と、

それぞれ独立したスイッチング素子とそれぞれ電気的に接続する第1の画素電極、第2の画素電極及び第3の画素電極と、

前記第1の画素電極、前記第2の画素電極及び前記第3の画素電極に対向する対向電極と、

前記第1の画素電極、前記第2の画素電極及び前記第3の画素電極と対向電極の間に液晶層を有し、

前記スイッチング素子に酸化物半導体を有するトランジスタを用い、

前記第2の画素電極を挟んで、第1の画素電極と、第2の画素電極と、第3の画素電極は隣接し、

前記第2の画素電極の一方の端部が、前記第1の絶縁層を介して前記第1の画素電極の端部の上に重ねて設けられ、

前記第2の画素電極の他方の端部が、前記第2の絶縁層を介して前記第3の画素電極の端部の下に重ねて設けられている液晶表示装置。

**【請求項 6】**

第1の絶縁層と、第2の絶縁層と、

それぞれ独立したスイッチング素子とそれぞれ電気的に接続する第1の画素電極、第2の画素電極及び第3の画素電極と、

前記第1の画素電極、前記第2の画素電極及び前記第3の画素電極に対向する対向電極と、

前記第1の画素電極、前記第2の画素電極及び前記第3の画素電極と対向電極の間に液晶層を有し、

前記スイッチング素子に酸化物半導体を有するトランジスタを用い、

前記第2の画素電極を挟んで、第1の画素電極と、第2の画素電極と、第3の画素電極は隣接し、

前記第2の画素電極の一方の端部が、前記第1の絶縁層を介して前記第1の画素電極の端部の上に重ねて設けられ、

前記第2の画素電極の他方の端部が、前記第2の絶縁層を介して前記第3の画素電極の端部の上に重ねて設けられている、液晶表示装置。

**【請求項 7】**

第1の絶縁層と、第2の絶縁層と、

10

20

30

40

50

それぞれ独立したスイッチング素子とそれぞれ電気的に接続する第1の画素電極、第2の画素電極及び第3の画素電極と、

前記第1の画素電極、前記第2の画素電極及び前記第3の画素電極に対向する対向電極と、

前記第1の画素電極、前記第2の画素電極及び前記第3の画素電極と対向電極の間に液晶層を有し、

前記スイッチング素子に酸化物半導体を有するトランジスタを用い、

前記第2の画素電極を挟んで、第1の画素電極と、第2の画素電極と、第3の画素電極は隣接し、

前記第2の画素電極の一方の端部が、前記第1の絶縁層を介して前記第1の画素電極の端部の下に重ねて設けられ、

前記第2の画素電極の他方の端部が、前記第2の絶縁層を介して前記第3の画素電極の端部の下に重ねて設けられている、液晶表示装置。

#### 【請求項8】

前記酸化物半導体を有するトランジスタと電気的に接続するフォトセンサと、

前記画素電極を同一基板上に有し、

前記フォトセンサを囲うブラックマトリクスを有する請求項5乃至請求項7のいずれかに記載の液晶表示装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は反射型の表示装置に関する。特に外光を反射する画素電極を複数配置した液晶表示装置に関する。

##### 【背景技術】

##### 【0002】

情報化社会の発達に伴い、電話、コンピュータ、デジタルカメラなど携帯型情報機器が広く用いられるようになっている。これらの携帯型情報機器の重量、並びに大きさは、携帯が可能である範囲に収めなければならないという制約がある。特に、バッテリーは重量、大きさ共に情報機器に占める割合が大きいため、その容量には限りがある。

##### 【0003】

限られた容量のバッテリーを用いて、長時間の利用が可能な携帯型情報機器を提供するには、消費電力が少ない部品や装置をもって構成する必要がある。例えば、消費電力が少ない表示装置としては、反射型の液晶表示装置をその例に挙げることができる。

##### 【0004】

反射型液晶表示装置はバックライトを用いず、外光を利用して表示を行うため消費電力が小さい。反射型の液晶表示装置の一例としては、例えば反射電極に低屈折率材料からなるテクスチャ構造体を設け、その上に高屈折率材料からなる光反射膜を形成する表示装置が考案されている（特許文献1）。

##### 【先行技術文献】

##### 【特許文献】

##### 【0005】

【特許文献1】特開2000-2875号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0006】

反射型の液晶表示装置は入射する外光を利用して表示を行うため、隣接する画素間にあって、画素電極が設けられていない間隙は、画素に占める表示領域の割合、所謂開口率の低下を招く。その結果、表示画像のコントラスト、及び明るさが損なわれてしまうという問題があった。

##### 【0007】

10

20

30

40

50

本発明は、このような技術的背景のもとでなされたものである。したがって、その目的の一つは、表示画像のコントラストが高く、また表示画像が明るい液晶表示装置を提供することである。

【課題を解決するための手段】

【0008】

上記目的を達成するために、液晶表示装置の画素電極の端部を、絶縁層を挟んで隣接する画素電極の端部に重ねて設け、隣接する画素間にある間隙を狭め、画素に占める表示領域の割合を高めればよい。

【0009】

すなわち本発明の一態様は、絶縁層と、それぞれ独立したスイッチング素子と電気的に接続する第1の画素電極及び第2の画素電極と、第1の画素電極及び第2の画素電極に対向する対向電極と、第1の画素電極及び第2の画素電極と対向電極の間に液晶層を有する。さらに、第2の画素電極の端部が、絶縁層を介して第1の画素電極の端部の上に重ねて設けられている、液晶表示装置である。

【0010】

また本発明の一態様は、上記の絶縁層が第2の画素電極の端部から延在して第1の画素電極の上面に重なり、かつ着色された上記の液晶表示装置である。

【0011】

また本発明の一態様は、第1の画素電極の上面に重なる第2の画素電極の側面を上記の絶縁層が覆う上記の液晶表示装置である。

【0012】

また本発明の一態様は、スイッチング素子に酸化物半導体を有するトランジスタを用いる上記の液晶表示装置である。

【0013】

また本発明の一態様は、第1の絶縁層と、第2の絶縁層と、それぞれ独立したスイッチング素子と電気的に接続する第1の画素電極、第2の画素電極及び第3の画素電極と、第1の画素電極、第2の画素電極及び第3の画素電極に対向する対向電極と、第1の画素電極、第2の画素電極及び第3の画素電極と対向電極の間に液晶層を有する。さらに、上記のスイッチング素子に酸化物半導体を有するトランジスタを用い、第2の画素電極を挟んで、第1の画素電極と、第2の画素電極と、第3の画素電極は隣接し、第2の画素電極の一方の端部が、第1の絶縁層を介して第1の画素電極の端部の上に重ねて設けられ、第2の画素電極の他方の端部が、第2の絶縁層を介して第3の画素電極の端部の下に重ねて設けられている、液晶表示装置である。

【0014】

また本発明の一態様は、第1の絶縁層と、第2の絶縁層と、それぞれ独立したスイッチング素子と電気的に接続する第1の画素電極、第2の画素電極及び第3の画素電極と、第1の画素電極、第2の画素電極及び第3の画素電極に対向する対向電極と、第1の画素電極、第2の画素電極及び第3の画素電極と対向電極の間に液晶層を有する。さらに、上記のスイッチング素子に酸化物半導体を有するトランジスタを用い、第2の画素電極を挟んで、第1の画素電極と、第2の画素電極と、第3の画素電極は隣接し、第2の画素電極の一方の端部が、第1の絶縁層を介して第1の画素電極の端部の上に重ねて設けられ、第2の画素電極の他方の端部が、第2の絶縁層を介して第3の画素電極の端部の上に重ねて設けられている、液晶表示装置である。

【0015】

また、本発明の一態様は、第1の絶縁層と、第2の絶縁層と、それぞれ独立したスイッチング素子と電気的に接続する第1の画素電極、第2の画素電極及び第3の画素電極と、第1の画素電極、第2の画素電極及び第3の画素電極に対向する対向電極と、第1の画素電極、第2の画素電極及び第3の画素電極と対向電極の間に液晶層を有する。さらに、上記のスイッチング素子に酸化物半導体を有するトランジスタを用い、第2の画素電極を挟んで、第1の画素電極と、第2の画素電極と、第3の画素電極は隣接し、第2の画素電極の

10

20

30

40

50

一方の端部が、第1の絶縁層を介して第1の画素電極の端部の下に重ねて設けられ、第2の画素電極の他方の端部が、第2の絶縁層を介して第3の画素電極の端部の下に重ねて設けられている、液晶表示装置である。

【0016】

また、本発明の一態様は、酸化物半導体を有するトランジスタと電気的に接続するフォトセンサと、画素電極を同一基板上に有し、フォトセンサと、画素電極の間にブラックマトリクスを有する上記液晶表示装置である。

【0017】

なお、本明細書において、オフ電流とは、トランジスタがオフ状態のときに、ソース電極とドレイン電極の間に流れる電流をいう。例えば、N型のトランジスタの場合には、ゲート電圧がトランジスタの閾値電圧よりも低いときにソース電極とドレイン電極との間に流れる電流である。

10

【発明の効果】

【0018】

本発明によれば、表示画像のコントラストが高く、また表示画像が明るい液晶表示装置を提供できる。

【図面の簡単な説明】

【0019】

【図1】実施の形態に係わる画素部を説明する図。

20

【図2】実施の形態に係わる画素部の作製工程を説明する図。

【図3】実施の形態に係わる画素部を説明する上面図。

【図4】実施の形態に係わる画素部を説明する図。

【図5】実施の形態に係わる画素部を説明する図。

【図6】実施の形態に係わる画素部の作製工程を説明する図。

20

【図7】実施の形態に係わる画素部の作製工程を説明する図。

【図8】実施の形態に係わる画素部を説明する上面図。

【図9】実施の形態に係わる画素部を説明する上面図。

【図10】実施の形態に係わる画素部を説明する図。

【図11】実施の形態に係わる液晶表示装置を説明するブロック図。

30

【図12】実施の形態に係わる液晶表示装置を説明する等価回路図。

【図13】実施の形態に係わるフォトセンサの駆動回路の概略図

【図14】実施の形態に係わる液晶表示装置を説明するタイミングチャート。

【図15】実施の形態に係わる液晶表示装置を説明する図。

【図16】実施の形態に係わる液晶表示装置を説明する図。

【図17】実施の形態に係わる画素部を説明する図。

【図18】酸化物半導体層を含むトランジスタ及びその作製方法の一例を説明する図。

30

【図19】酸化物半導体によって作製されたトランジスタのVg - Id特性の一例を示すグラフ。

【図20】酸化物半導体によって作製されたトランジスタのVg - Id特性の内、オフ状態の特性を説明するためのグラフ。

40

【図21】ソース - ドレイン電圧Vとオフ電流Iとの関係を表すグラフ。

【発明を実施するための形態】

【0020】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0021】

50

## (実施の形態 1)

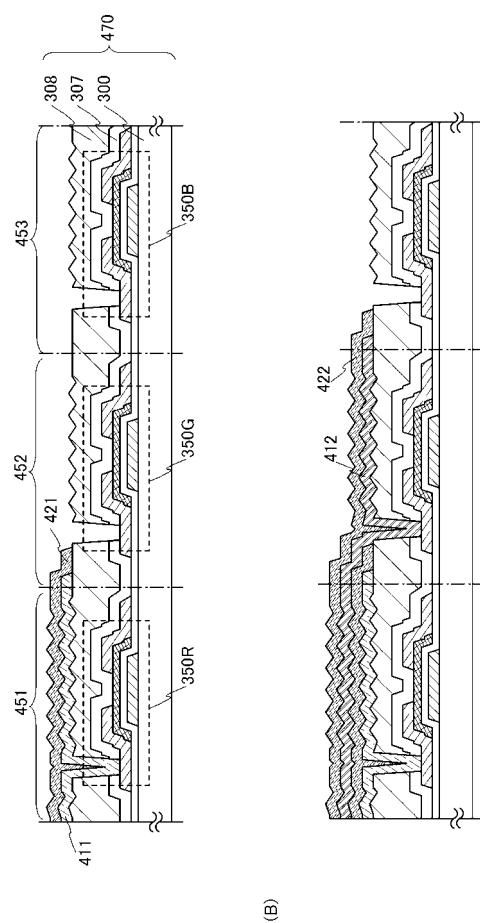

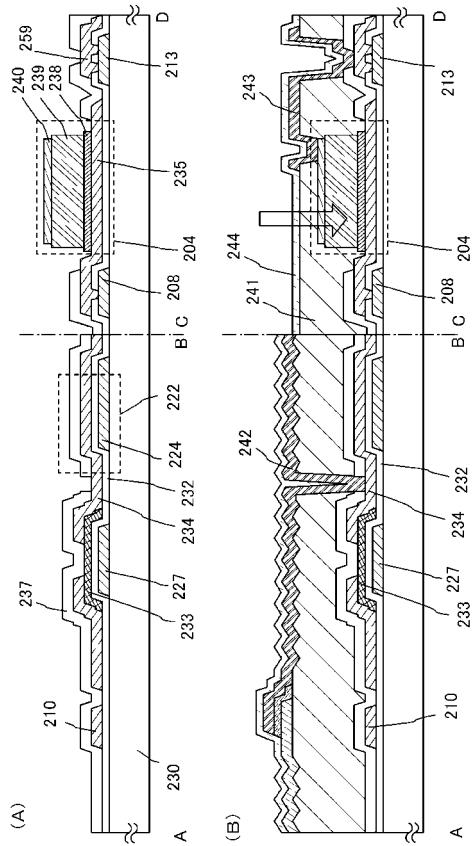

本実施の形態では、絶縁層を間に挟んで、液晶表示装置の画素電極の端部を隣接する画素電極の端部に重ねて設ける構成を、図1を用いて説明する。また、その作製方法を、図2を用いて説明する。

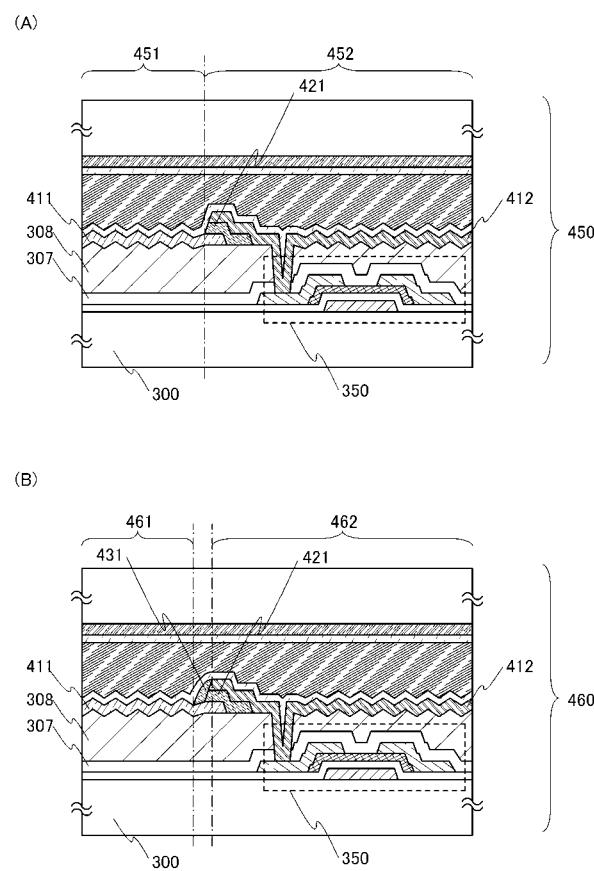

## 【0022】

本実施の形態で例示する液晶表示装置の隣接する二つの画素電極の構成について、断面図を用いて説明する。図1(A)に液晶表示装置450の第1の画素451と、第2の画素452が隣接する部分を示す。

## 【0023】

液晶表示装置450は第1の画素451、及び第2の画素452を含む複数の画素を有する。第1の画素451は第1の画素電極411を有し、第2の画素452は第2の画素電極412を有する。なお、第1の画素電極411、及び第2の画素電極412は基板300に設けた絶縁層308上に設けられ、第1の画素電極411及び第2の画素電極412上には配向膜414が設けられている。また、対向基板408は一方の面に対向電極403と対向電極403上に配向膜404を備える。液晶層405は配向膜414と配向膜404に接して、基板300と対向基板408の間に挟持されている。

10

## 【0024】

図1(A)に示す絶縁層308の表面にある凹凸は、不規則な形態の凹凸構造、所謂テクスチャ構造を模式的に表している。第1の画素電極411、及び第2の画素電極412は、テクスチャ構造を有する絶縁層308上に設けられているため、下地のテクスチャ構造が表面に現れる。その結果、当該画素電極に入射する光は乱反射し、第1の画素電極411、及び第2の画素電極412は巨視的には概ね白色に見える。なお、白色に見える画素電極を用いて液晶の配向を制御することで、コントラストを高めることができる。

20

## 【0025】

第1の画素電極411は図示されていないトランジスタのソース電極又はドレイン電極と電気的に接続され、第2の画素電極412はトランジスタ350のソース電極又はドレイン電極と電気的に接続されている。なお、トランジスタ350は画素452のスイッチング素子として機能する。トランジスタ350を含む画素トランジスタは基板300上に形成され、該画素トランジスタを覆う絶縁層307、及び絶縁層308上に、第1の画素電極411、及び第2の画素電極412が設けられている。

30

## 【0026】

第2の画素電極412の端部は、絶縁層421を介して第1の画素電極411の端部に重ねて設けられている。絶縁層421は第1の画素電極411と第2の画素電極412の電気的な接続を防止する。

## 【0027】

隣接する二つの画素電極を重ねて設ける構成とすると、表示装置に対峙する方向から見て、二つの画素電極の間に隙間が見えなくなる。その結果、それぞれの画素に占める画素電極の面積の割合を大きくできる。このような構成の画素電極を有する表示装置は、明るく、コントラストに優れた表示画像を表示できる。

40

## 【0028】

また、図1(A)に図示した構成とは異なる液晶表示装置460の画素電極の構成について説明する。液晶表示装置460の第1の画素461と第2の画素462の隣接部分を図1(B)に示す。

## 【0029】

第1の画素461、及び第2の画素462は同一の基板300上に設けられ、第1の画素461は第1の画素電極411を有し、第2の画素462は第2の画素電極412を有する。第2の画素電極412の端部は、絶縁層421を介して第1の画素電極411の端部に重ねて設けられている。絶縁層421は第1の画素電極411と第2の画素電極412の電気的な接続を防止する。

## 【0030】

50

また、液晶表示装置 460 の第 2 の画素電極 412 の側面は、第 1 の画素電極 411 上に設けた絶縁層 431 に覆われている。なお、絶縁層 431 は、ブラックマトリクスとして機能する層、例えば着色材料を含む着色層を用いて形成することが好ましい。また、絶縁層 431 を有すること以外は、液晶表示装置 460 は液晶表示装置 450 と同じ構成を有する。

#### 【0031】

隣接する第 1 の画素電極 411 と第 2 の画素電極 412 の側面の間に強い電界が発生すると、当該領域に位置する液晶の配向が乱れる場合がある。液晶表示装置 460 に設けられた第 2 の画素電極 412 の側面を覆う絶縁層 431 は、第 1 の画素電極 411 と第 2 の画素電極 412 の側面の間に生じる電界を緩和する。その結果、液晶の配向の乱れが生じにくくなり、表示画像の品質が向上する。また、ブラックマトリクスとして機能する層を絶縁層 431 に用いると、表示画像の暗い領域、所謂シャドー部の光学濃度を高めることができ、シャドー部の階調を豊かに再現することができる。

10

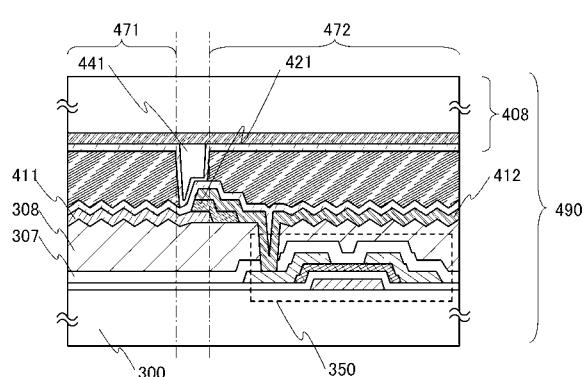

#### 【0032】

また、図 1 (A)、並びに図 1 (B) に図示した構成と異なる液晶表示装置 490 の画素電極の構成について説明する。液晶表示装置 490 の第 1 の画素 471 と第 2 の画素 472 の隣接部分を図 17 に示す。

#### 【0033】

第 1 の画素 471、及び第 2 の画素 472 は同一の基板 300 上に設けられ、第 1 の画素 471 は第 1 の画素電極 411 を有し、第 2 の画素 472 は第 2 の画素電極 412 を有する。第 2 の画素電極 412 の端部は、絶縁層 421 を介して第 1 の画素電極 411 の端部に重ねて設けられている。絶縁層 421 は第 1 の画素電極 411 と第 2 の画素電極 412 の電気的な接続を防止する。

20

#### 【0034】

また、液晶表示装置 490 の第 1 の画素電極 411 と第 2 の画素電極 412 が重なる領域に、スペーサ 441 が設けられている。スペーサ 441 は、例えば誘電体材料を用いて対向基板 408 と基板 300 の間に設ければよく、具体的には対向基板 408 側に有機樹脂を用いて形成することができる。また、スペーサ 441 はブラックマトリクスとして機能する層、例えば着色材料を含む着色層を用いて形成することもできる。なお、スペーサ 441 を有すること以外は、液晶表示装置 490 は液晶表示装置 450 と同じ構成を有する。

30

#### 【0035】

前述の通り、隣接する第 1 の画素電極 411 と第 2 の画素電極 412 の側面の間に強い電界が発生すると、当該領域に位置する液晶の配向が乱れる場合がある。液晶表示装置 490 においては、当該領域にスペーサ 441 が配置されており、液晶の配向の乱れを抑止できる。

#### 【0036】

次に、図 1 (B) に例示する本発明の一態様の画素電極を、スイッチング素子が形成された基板上に作製する方法を、図 2 を用いて説明する。

40

#### 【0037】

基板 300 上に形成するスイッチング素子は特に限定されない。例えばトップゲート構造、又はボトムゲート構造のトランジスタなどを用いることができる。また、トランジスタはチャネル形成領域が一つ形成されるシングルゲート構造でも、二つ形成されるダブルゲート構造もしくは三つ形成されるトリプルゲート構造であっても良い。また、チャネル領域の上下にゲート絶縁層を介して配置された 2 つのゲート電極層を有する、デュアルゲート型でもよい。一例として、ボトムゲート型のトランジスタ 350 を適用する場合について、図 2 に示す。なお、スイッチング素子としては、オフ電流が低減された酸化物半導体層を有するトランジスタが特に好適である。オフ電流が低減された酸化物半導体層を有するトランジスタを画素トランジスタに用いることにより、例えば静止画像を表示する期間に表示素子の書き換え頻度を低減することにより、電力の消費が抑制された表示装置を提

50

供できる。

【0038】

トランジスタ350上に絶縁層307を形成する。絶縁層370としては、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などの無機絶縁膜を用いることができる。また、絶縁層307は複数の絶縁膜を積層して形成してもよい。例えば、前述の無機絶縁膜に重ねて窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、窒化酸化アルミニウム膜などの無機絶縁膜を用いることができる。なお、上記無機絶縁膜はスパッタリング法などを用いて形成することができる。

【0039】

また、絶縁層307上に絶縁層308を設ける。絶縁層308としては、例えば感光性有機樹脂を用いることができる。スピンドルコート法などを用いて、絶縁層307上に感光性有機樹脂層を形成し、フォトマスクを用いてトランジスタ350のソース電極又はドレイン電極に達する開口部を設けるための露光をはじめにおこない、次いで、別のフォトマスクを用いて絶縁層308の表面にテクスチャ構造を形成するための露光を行い、現像して絶縁層308を形成する。

10

【0040】

次に、第1の画素電極411を絶縁層308上に形成する。第1の画素電極411に用いることができる導電膜としては、可視光を反射する電極であればよく、例えばAl、Ag、またはこれらの合金、例えばNdを含むアルミニウム、Ag-Pd-Cu合金等をその例に挙げることができる。なお、上記導電膜はスパッタリング法、真空蒸着法などを用いて形成することができる。次いで、フォトマスクを用いて形成したレジストマスクを用いて不要な部分を除去し、第1の画素電極411を形成する。

20

【0041】

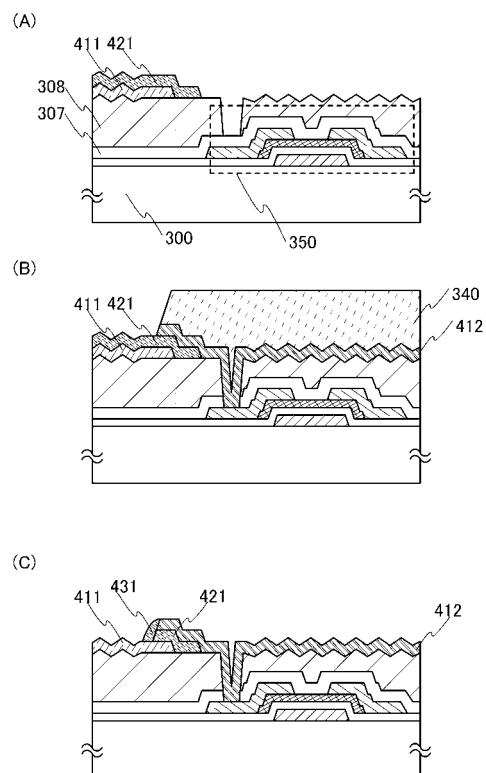

次に、絶縁層421となる絶縁膜を第1の画素電極411を覆って設ける。絶縁層421に用いることができる材料としては絶縁性であれば良く、例えば、酸化シリコン、酸化窒化シリコン、酸化アルミニウム、または酸化窒化アルミニウム、窒化シリコン、窒化アルミニウム、窒化酸化シリコン、窒化酸化アルミニウムなどの無機材料や、ポリイミド、アクリル、ベンゾシクロブテン等の有機材料を用いることができる。なお、上記無機材料を用いた絶縁膜はスパッタリング法、ゾルゲル法などを用いて形成することができ、上記有機材料を用いた絶縁膜はスピンドルコート法や印刷法などを用いて形成することができる。次いで、レジストマスクを用いるなどして不要な部分を除去し、第1の画素電極411を覆う絶縁層421を形成する。この段階までの断面図を図2(A)に示す。

30

【0042】

次に、第2の画素電極412を絶縁層421、及び絶縁層308上に形成する。第2の画素電極412となる導電膜は第1の画素電極411と同様の方法を用いて形成する。次いで、フォトマスクを用いて形成したレジストマスク340を用いて不要な部分を除去し、第2の画素電極412を形成する。なお、第1の画素電極411上に設けた絶縁層421は、エッティングストップとして働き、このエッティング工程から第1の画素電極411を保護する。この段階までの断面図を図2(B)に示す。

40

【0043】

次いで、同じレジストマスク340を用いて絶縁層421の不要な部分を除去し、その後レジストマスク340を取り除くと、図1(A)に例示する本発明の一態様の画素電極を作製できる。

【0044】

また、第1の画素電極411上の第2の画素電極412の側面を覆うように、絶縁層431を形成する。絶縁層431は絶縁層421に用いることができる材料を適用して形成する。絶縁層431の形成方法としては、絶縁膜を成膜した後にレジストマスクを用いてエッティングする方法の他、絶縁層431をフォトレジストで形成してもよい。また、印刷法、インクジェット法を用いて形成することもできる。この段階までの断面図を図2(C)に示す。

50

## 【0045】

以上の工程を経て、絶縁層421を間に挟んで、第1の画素電極411の端部に隣接する第2の画素電極412を重ねて設け、第1の画素電極411上にある第2の画素電極412の側面を絶縁層431で覆う構成を有する、液晶表示装置の画素電極を作製できる。

## 【0046】

本実施の形態で例示した液晶表示装置は、隣接する二つの画素電極を重ねて設ける構成を有する。このような構成の画素電極を設けた表示装置は、表示装置に対峙する方向から見て、二つの画素電極の間に隙間が見えない。その結果、それぞれの画素に占める画素電極の面積の割合を大きくできる。このような構成の画素電極を有する表示装置は、明るく、コントラストに優れた表示画像を表示できる。

10

## 【0047】

また、本実施の形態で例示した第1の画素電極の上面に重なる第2の画素電極の側面を覆う絶縁層を設ける構成が適用された液晶表示装置は、液晶の配向の乱れが生じにくくなり、高品質な画像を表示できる。また、ブラックマトリクスとして機能する層を、該側面を覆う絶縁層に用いると、表示画像の暗い領域、所謂シャドー部の光学濃度が高まり、シャドー部の階調再現性を豊かにできる。

## 【0048】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

20

## 【0049】

## (実施の形態2)

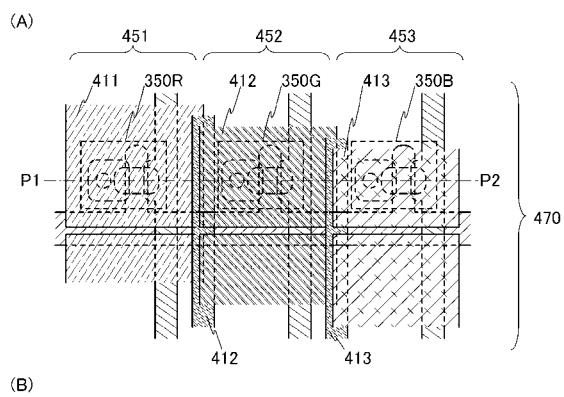

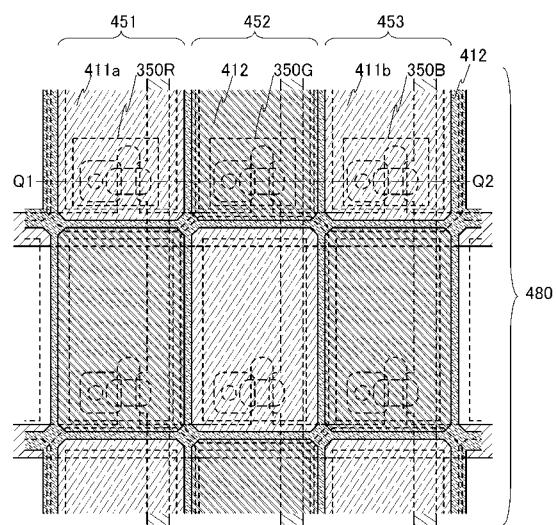

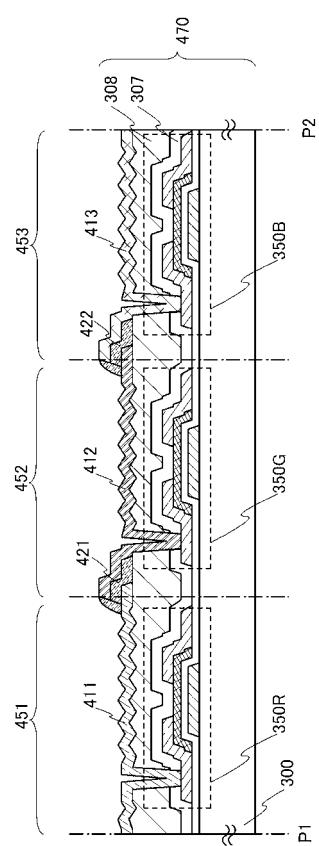

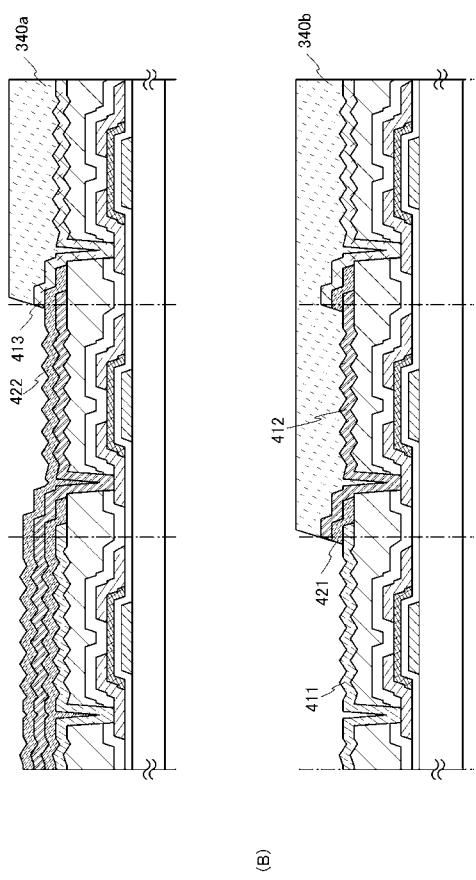

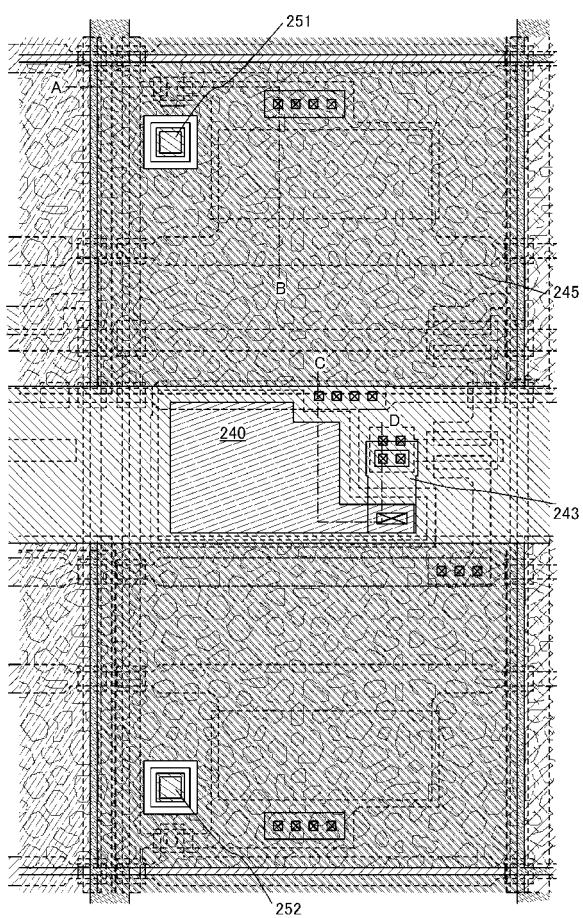

本実施の形態では、3つ以上の隣接する画素電極を有する表示装置において、絶縁層を挟んで、互いの端部を重ねて設ける構成について図3、乃至図7を用いて説明する。

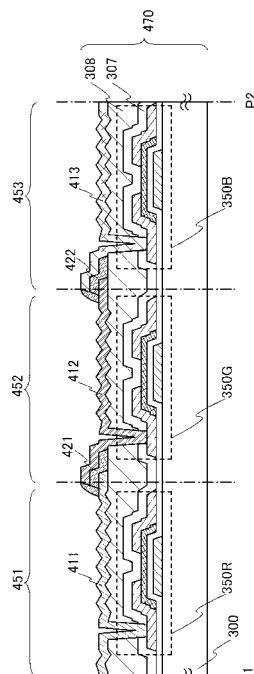

## 【0050】

本実施の形態で例示する液晶表示装置470の画素部の上面図を図3(A)に示す。液晶表示装置470は、第1の画素451、第2の画素452、及び第3の画素453を有する。第1の画素451は、第1の画素電極411と第1のトランジスタ350Rを有し、第2の画素452は、第2の画素電極412と第2のトランジスタ350Gを有し、第3の画素453は、第3の画素電極413と第3のトランジスタ350Bを有する。

30

## 【0051】

また、図3(A)の切断線P1-P2における液晶表示装置470の断面図を図4に示す。液晶表示装置470は、同一基板300上に3つのトランジスタ(350R、350G、及び350B)を有し、該トランジスタを覆う絶縁層307と絶縁層307を覆う絶縁層308を有する。第1の画素電極411、第2の画素電極412、及び第3の画素電極413は絶縁層308上に設けられている。

## 【0052】

また、絶縁層307、及び絶縁層308の開口部を介して、第1の画素電極411とトランジスタ350Rのソース電極またはドレイン電極が電気的に接続され、第2の画素電極412とトランジスタ350Gのソース電極またはドレイン電極が電気的に接続され、第3の画素電極413とトランジスタ350Bのソース電極またはドレイン電極が電気的に接続されている。

40

## 【0053】

また、第2の画素電極412の一方の端部が、第1の絶縁層421を間に挟んで第1の画素電極411の上に重ねて設けられ、第2の画素電極412の他方の端部が、第2の絶縁層422を間に挟んで第3の画素電極413の下に重ねて設けられている。

## 【0054】

なお、このように2つの画素電極の間に配置された画素電極の一方の端部を隣接する画素電極の端部の上に重ね、他方の端部を隣接するもう一方の画素電極の端部の下に重ねる構成は、3つの画素電極が配置される場合に限定されない。例えば、4つの画素電極が一列に配置される場合についても適用できる。具体的には、4つの画素電極のそれぞれの左側

50

の端部が、その左隣の画素電極の右側の端部の上に重ねて設けられた構成であってもよい。

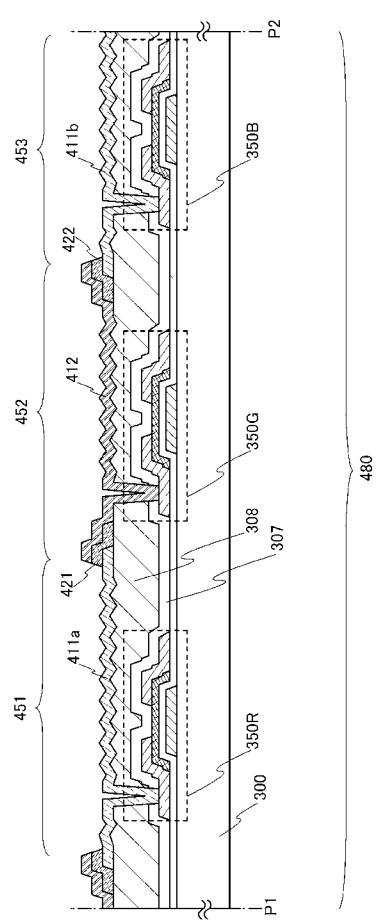

【0055】

次に、図3(A)とは異なる画素電極の構成について説明する。液晶表示装置480の上面図を図3(B)に示す。液晶表示装置480は、第1の画素451、第2の画素452、及び第3の画素453を有する。第1の画素451は、第1の画素電極411aと第1のトランジスタ350Rを有し、第2の画素452は、第2の画素電極412と第2のトランジスタ350Gを有し、第3の画素453は、第3の画素電極411bと第3のトランジスタ350Bを有する。

【0056】

図3(B)の切断線Q1-Q2における液晶表示装置480の断面図を図5に示す。液晶表示装置480は、同一基板300上に3つのトランジスタ(350R、350G、及び350B)を有し、該トランジスタを覆う絶縁層307と、該絶縁層307を覆う絶縁層308を有する。第1の画素電極411a、第2の画素電極412、及び第3の画素電極411bは絶縁層308上に設けられている。

【0057】

また、絶縁層307、及び絶縁層308の開口部を介して、第1の画素電極411aとトランジスタ350Rのソース電極またはドレイン電極が電気的に接続され、第2の画素電極412とトランジスタ350Gのソース電極またはドレイン電極が電気的に接続され、第3の画素電極411bとトランジスタ350Bのソース電極またはドレイン電極が電気的に接続されている。

【0058】

また、第2の画素電極412の一方の端部が、第1の絶縁層421を間に挟んで第1の画素電極411aの上に重ねて設けられ、第2の画素電極412の他方の端部が、第2の絶縁層422を間に挟んで第3の画素電極411bの上に重ねて設けられている。

【0059】

なお、このように2つの画素電極の間に配置された画素電極の端部を、隣接する画素電極の端部の上に重ねる構成は、画素電極が3つ以上連なる場合にも適用できる。

【0060】

また、2つの画素電極の間に配置された画素電極の端部を隣接する画素電極の端部の下に重ねる構成としてもよい。言い換えると、4つ以上の画素電極を並べる場合、2つの画素電極の間に配置された画素電極の端部を隣接する画素電極の端部の上に重ねる構成と、隣接する画素電極の端部の下に重ねる構成を交互に設けることができる。

【0061】

次に、液晶表示装置470の画素部の作製方法の一例を、図6及び図7を用いて説明する。液晶表示装置470の画素部は、実施の形態1とほぼ同様な方法を用いて作製できる。

【0062】

基板300に、トランジスタ(350R、350G、及び350B)と、トランジスタのソース電極又はドレイン電極に達する開口部を有する絶縁層(307、及び308)を設ける。次いで、実施の形態1に説明した方法を用いて絶縁層308上に第1の画素電極411を形成し、第1の画素電極411上に第1の絶縁層421を形成する。この段階までの断面図を図6(A)に示す。

【0063】

同様にして第2の画素電極412と第2の絶縁層422を図6(B)に示すように形成し、第3の画素電極413となる導電膜を他の画素電極と同様に形成する。次いで、レジストマスク340aを形成し、レジストマスク340aを用いて不要な部分を除去し、第3の画素電極413を形成する。この段階までの断面図を図7(A)に示す。

【0064】

さらに、同じレジストマスク340aを用いて第2の絶縁層422の不要な部分をエッチングして除去する。次いで、第2の画素電極412となる導電膜上にレジストマスク34

10

20

30

40

50

0 b を形成し、レジストマスク 3 4 0 b を用いて第 1 の画素電極 4 1 1 と第 1 の絶縁層 4 2 1 の不要な部分を除去して、液晶表示装置 4 7 0 の画素部を形成する。

【 0 0 6 5 】

また、図 3 ( B )、及び図 5 に例示す液晶表示装置 4 8 0 の画素部を作製する方法の一例を、図 5 を参照しながら説明する。

【 0 0 6 6 】

基板 3 0 0 に、トランジスタ ( 3 5 0 R、3 5 0 G、及び 3 5 0 B ) と、トランジスタのソース電極又はドレイン電極に達する開口部を有する絶縁層 ( 3 0 7、及び 3 0 8 ) を設ける。次いで、絶縁層 3 0 8 上に導電膜を形成し、フォトマスクを用いて形成したレジストマスクを使って第 1 の画素電極 4 1 1 a と第 3 の画素電極 4 1 1 b を形成する。

10

【 0 0 6 7 】

次いで、第 1 の画素電極 4 1 1 a と第 3 の画素電極 4 1 1 b を覆う絶縁膜を成膜し、レジストマスクを用いて当該絶縁膜の不要な部分をエッチングして除去する。なお、ここで用いるレジストマスクは、第 1 の画素電極 4 1 1 a と第 3 の画素電極 4 1 1 b の端部からその外側に延在し、後に第 1 の絶縁層 4 2 1、及び第 2 の絶縁層 4 2 2 になる部分を覆ってこれらをエッチング液から保護する形状を有するものとする。

【 0 0 6 8 】

従って、第 1 の画素電極 4 1 1 a、又は第 3 の画素電極 4 1 1 b と重なる部分の絶縁層は除去されないで残るため、当該絶縁層は第 1 の絶縁層 4 2 1、及び第 2 の絶縁層 4 2 2 とは異なる形状を有する。

20

【 0 0 6 9 】

次に、当該レジストマスクを除去し、第 2 の画素電極 4 1 2 となる導電膜を成膜し、その上にフォトマスクを用いてレジストマスクを形成する。次いで当該レジストマスクを使用して、不要な部分をエッチングして除去し、第 2 の画素電極 4 1 2 を形成する。

【 0 0 7 0 】

さらに第 2 の画素電極 4 1 2 を形成する際に用いたレジストマスクを用いて、第 1 の画素電極 4 1 1 a、又は第 3 の画素電極 4 1 1 b と重なる絶縁層の不要な部分をエッチングして除去して、第 1 の絶縁層 4 2 1、及び第 2 の絶縁層 4 2 2 を形成する。

【 0 0 7 1 】

図 3 ( B )、及び図 5 に例示した 2 つの画素電極の間に配置された画素電極の端部を、隣接する画素電極の端部の上に重ねる構成は、画素電極を二回に分けて形成すれば良く、比較的簡便に作製することができる。なお、2 つの画素電極の間に配置された画素電極の端部を、隣接する画素電極の端部の下に重ねる構成であっても、同様に比較的簡便に作成することができる。

30

【 0 0 7 2 】

絶縁層を挟んで、隣接する 3 つ以上の画素電極が端部を重ねて設ける構成とすると、表示装置に対峙する方向から見て、画素電極の間に間隙が見えなくなる。その結果、それぞれの画素に占める画素電極の割合を大きくできる。このような構成の画素電極を有する表示装置は、明るく、コントラストに優れた表示画像を表示できる。

【 0 0 7 3 】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【 0 0 7 4 】

( 実施の形態 3 )

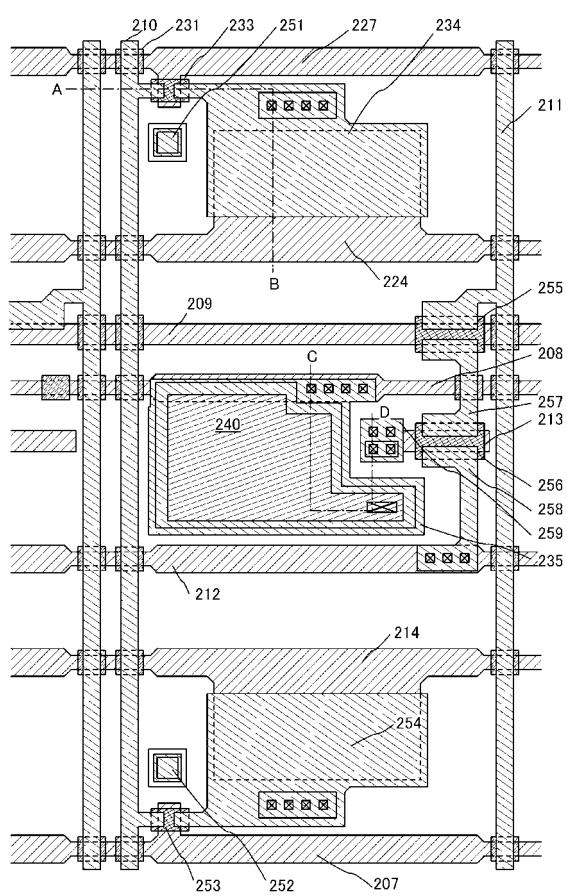

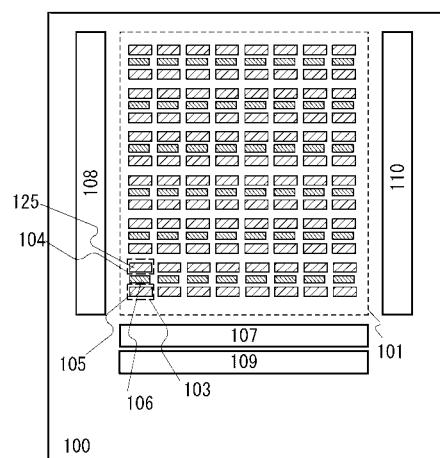

本実施の形態では、実施の形態 1 及び実施の形態 2 で例示した画素電極を有し、さらにフォトセンサとしてフォトダイオードを同一基板上に設ける液晶表示装置について、図 8 乃至図 10 を用いて説明する。

【 0 0 7 5 】

図 8 は、画素上面図の一例である。また、フォトダイオードの電極を形成する前の状態を示している。なお、図 8 中の鎖線 A - B で切断した断面図、及び鎖線 C - D で切断した断

40

50

面図が図10(A)にそれぞれ対応している。

【0076】

次に、本実施の形態で例示する液晶表示装置の作製方法について、図8を主に用いて、図10と共に説明する。まず、基板230上に導電膜を形成した後、1枚目の露光マスクを用いる第1のフォトリソグラフィ工程により、ゲート電極を含むゲート信号線207、213、227、容量配線224、フォトダイオードリセット信号線208、読み出し信号線209、フォトセンサ基準信号線212を形成する。なお、本実施の形態では基板230としてガラス基板を用いる場合について説明する。

【0077】

下地膜となる絶縁膜を基板230と導電膜との間に設けてもよい(図10参照)。下地膜は、基板230からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

【0078】

また、導電膜は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

【0079】

次いで、これらの配線を覆う絶縁層を形成し、2枚目の露光マスクを用いる第2のフォトリソグラフィ工程により、選択的にエッチングを行い、後に形成される配線が交差する部分にのみ絶縁層231を形成する。本実施の形態では、絶縁層231は膜厚600nmの酸化窒化珪素膜を用いる。

【0080】

次いで、ゲート絶縁層232及び酸化物半導体膜を形成し(図10参照)、3枚目の露光マスクを用いる第3のフォトリソグラフィ工程により、ゲート絶縁層232を介してゲート信号線207、213、227及び読み出し信号線209とそれぞれ重なる第1の酸化物半導体層233、第2の酸化物半導体層253、第3の酸化物半導体層255、及び第4の酸化物半導体層256を形成する。本実施の形態では、ゲート絶縁層232として膜厚100nmの酸化窒化珪素膜を用い、酸化物半導体層として膜厚25nmのIn-Ga-Zn-O膜を用いる。

【0081】

また、第1の酸化物半導体層233、第2の酸化物半導体層253、第3の酸化物半導体層255、及び第4の酸化物半導体層256は、化学式 $In_xMO_3$  ( $ZnO$ )<sub>m</sub> ( $m > 0$ )で表記される酸化物薄膜を用いることができる。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及びCoなどがある。また、上記酸化物薄膜にSiO<sub>2</sub>を含んでもよい。

【0082】

また、酸化物薄膜をスパッタリング法で作製するためのターゲットとしては、例えば、組成比として、 $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 1$  [mol数比]の酸化物ターゲットを用い、In-Ga-Zn-O膜を成膜する。また、このターゲットの材料及び組成に限定されず、例えば、 $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 2$  [mol数比]の酸化物ターゲットを用いてもよい。なお、ここで、例えば、In-Ga-Zn-O膜とは、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物膜、という意味であり、その化学量論比はとくに問わない。

【0083】

次いで、酸化物半導体層に第1の加熱処理を行う。この第1の加熱処理によって酸化物半導体層の脱水化または脱水素化を行うことができる。第1の加熱処理の温度は、400以上750以下、または400以上基板の歪み点未満とする。本実施の形態では、R-TA(Rapid Thermal Anneal)装置を用い、窒素雰囲気下で650

10

20

30

40

50

、6分の加熱処理を行った後、大気に触れることなく、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れないように酸化物半導体層の成膜室に移動させて酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層を得る。

## 【0084】

次いで、4枚目の露光マスクを用いる第4のフォトリソグラフィ工程により、ゲート絶縁層232を選択的に除去して、ゲート信号線213に達する開口と、フォトダイオードリセット信号線208に達する開口を形成する(図10参照)。

## 【0085】

次いで、ゲート絶縁層232、及び酸化物半導体層上に、導電膜を形成する。導電膜としては、例えば、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素を成分とする金属膜、または上述した元素の窒化物を成分とする合金膜か、上述した元素を組み合わせた合金膜等を用いることができる。そして、5枚目の露光マスクを用いる第5のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行って、ビデオデータ信号線210、フォトセンサ出力信号線211、電極層234、235、254、257、258、259を形成する。

10

## 【0086】

なお、図8に示す第1の酸化物半導体層233を有するトランジスタは、電極層234をソース電極層またはドレイン電極層とするトランジスタであり、画素のスイッチング素子となる。また、図10に示すように、電極層234は、ゲート絶縁層232を誘電体とし、容量配線224と保持容量222を形成する。また、図8に示す第2の酸化物半導体層253を有するトランジスタは、電極層254をソース電極層またはドレイン電極層とするトランジスタであり、画素のスイッチング素子となる。

20

## 【0087】

また、図8に示す第3の酸化物半導体層255を有するトランジスタは、電極層257をソース電極層またはドレイン電極層とするトランジスタであり、フォトセンサを構成する一要素となる。

30

## 【0088】

また、図8に示す第4の酸化物半導体層256を有するトランジスタは、電極層257または電極層258をソース電極層またはドレイン電極層とするトランジスタである。また、図10(A)に示すように、当該トランジスタのゲート信号線213は、電極層259と電気的に接続している。

## 【0089】

次いで、不活性ガス雰囲気下、または酸素ガス雰囲気下で第2の加熱処理(好ましくは200以上400以下、例えば250以上350以下)を行う。本実施の形態では、窒素雰囲気下で300、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層の一部(チャネル形成領域)が絶縁層と接した状態で加熱される。

## 【0090】

次いで保護絶縁層となる絶縁層237を形成し、6枚目の露光マスクを用いる第6のフォトリソグラフィ工程により、電極層235に達する開口、電極層234に達する開口、電極層259に達する開口を形成する。

40

## 【0091】

次いで、プラズマCVD法により、p層238、i層239、及びn層240を積層成膜する。本実施の形態では、p層238として膜厚45nmのボロンを含む微結晶シリコン膜を用い、i層239として膜厚400nmのアモルファスシリコン膜を用い、n層240として膜厚80nmのリンを含む微結晶シリコン膜を用いる。そして、7枚目の露光マスクを用いる第7のフォトリソグラフィ工程により、電極層235と接して重なる領域のみを残して除去する。この段階までの断面図が図10(A)であり、その上面図が図8に相当する。

## 【0092】

50

次いで感光性有機樹脂層を形成し、8枚目の露光マスクで開口となる領域を露光し、9枚目の露光マスクで凹凸となる領域（テクスチャ構造を有する領域）を露光し、現像して部分的に凹凸を有する絶縁層241を形成する第8のフォトリソグラフィ工程を行う。

【0093】

次いで、第1の画素電極、第2の画素電極、及び第3の画素電極を作製する。本実施の形態では、図3（A）、図4、図6、及び図7を用いて実施の形態2で説明した方法を適用するものとし、ここでは詳細な図面を用いずに説明する。

【0094】

具体的には、第1の画素電極となる反射性を有する導電膜を成膜し、10枚目の露光マスクを用いる第9のフォトリソグラフィ工程を行う。次いで、第1の画素電極となる導電膜を覆い、第1の絶縁層となる絶縁層を成膜し、11枚目の露光マスクを用いる第10のフォトリソグラフィ工程を行う。

10

【0095】

次に、第2の画素電極となる反射性を有する導電膜を成膜し、12枚目の露光マスクを用いる第11のフォトリソグラフィ工程を行う。次いで、第2の画素電極となる導電膜を覆い、第2の絶縁層となる絶縁層を成膜し、13枚目の露光マスクを用いる第12のフォトリソグラフィ工程を行う。

【0096】

次に、第3の画素電極となる反射性を有する導電膜を成膜し、14枚目の露光マスクを用いる第13のフォトリソグラフィ工程を行い、第3の画素電極と第2の絶縁層を形成する。次いで、15枚目の露光マスクを用いる第14のフォトリソグラフィ工程を行い、第2の画素電極、第1の絶縁層、第1の画素電極を形成する。また、接続電極層243を画素電極と共に形成する（図9参照）。接続電極層243は、フォトダイオード204とゲート信号線213を電気的に接続する。

20

【0097】

なお、反射性を有する導電膜としてはAl、Ag、またはこれらの合金、例えばNdを含むアルミニウム、Ag-Pd-Cu合金等を用いる。そして、第9のフォトリソグラフィ工程後に第3の加熱処理、本実施の形態では、窒素雰囲気下250℃、1時間を行う。

【0098】

以上の工程により、図10（B）に示すように同一基板上に絶縁層を挟んで隣接する反射電極の端部と端部を重ねる反射電極層242と、反射電極層242と電気的に接続するトランジスタと、ゲート信号線213と接続電極層243を介して電気的に接続するフォトダイオード204とを合計15枚の露光マスクを用い、合計14回のフォトリソグラフィ工程によって作製することができる。

30

【0099】

そして反射電極層242を覆う配向膜244を形成する。この段階での断面図が図10（B）に相当する。こうしてアクティブマトリクス基板が作製できる。

【0100】

そして、このアクティブマトリクス基板と貼り合わせる対向基板を用意する。対向基板には、フォトセンサの受光部を囲むように遮光層（ブラックマトリクスとも呼ぶ）と透光性を有する導電膜を形成し、さらに有機樹脂を用いた柱状スペーサを形成する。そして、最後に配向膜で覆う。

40

【0101】

この対向基板を、シール材を用いてアクティブマトリクス基板と貼り合わせ、一対の基板間に液晶層を挟持する。なお、対向基板の遮光層は、反射電極層242及びフォトダイオードの感光領域に重ならず、フォトダイオードの周囲を囲う様に設ける。また、対向基板に設けられた柱状スペーサは、電極層251、252と重なるように位置合わせを行う。柱状スペーサは、電極層251、252と重ねることで一対の基板の間隔を一定に保持する。なお、電極層251、252は、電極層234と同一工程で形成することができるため、マスク数を増やすことなく設けることができる。

50

## 【0102】

こうして貼り合わせた一対の基板における画素の上面図が図9に相当する。また、反射電極層242は、凹凸を有する感光性有機樹脂層上に設けられているため、図9に示すようなランダムな平面模様を有する。感光性有機樹脂層の表面形状を反映させて反射電極層242の表面にも凹凸を設け、鏡面反射となることを防いでいる。なお、図9において反射電極層242の凹部245も示しており、凹部245の周縁は、反射電極層の周縁よりも内側に位置し、凹部245の下方の感光性有機樹脂層は他の領域よりも薄い膜厚となっている。

## 【0103】

また、必要があれば、対向基板の外光が入射する面に、位相差を調節するための位相差フィルムや、偏光機能を有するフィルムや、反射防止板や、カラーフィルタなどの光学フィルムを設けてもよい。

## 【0104】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

## 【0105】

## (実施の形態4)

本実施の形態では、絶縁層を間に挟んで、画素電極の端部を隣接する画素電極の端部に重ねて設ける構成を有し、当該画素電極、並びにフォトセンサを同一基板上に有する液晶表示装置について、その駆動方法について説明する。

## 【0106】

実施の形態3で説明した画素電極、並びにフォトセンサを同一基板上に有する表示パネルの一例について、図11を参照して説明する。表示パネル100は、画素回路101、表示素子制御回路、及びフォトセンサ制御回路を有する。画素回路101は、行列方向にマトリクス状に配置された複数の画素103、104及びフォトセンサ106を有する。画素104、103は、1つの表示素子をそれぞれ有する。本実施の形態では、画素103と画素104の間に、1つのフォトセンサ106を配置し、フォトセンサの数が画素数の半分とする例を示したが特に限定されず、フォトセンサの数が画素数と同じになるよう、画素間にそれぞれ1つのフォトセンサを有する構成としてもよく、フォトセンサの数が画素数の3分の一となる構成としてもよい。

## 【0107】

表示素子105は、トランジスタ、保持容量、及び液晶層を有する液晶素子などを有する。トランジスタは、保持容量への電荷の注入もしくは保持容量からの電荷の排出を制御する機能を有する。保持容量は、液晶層に印加する電圧に相当する電荷を保持する機能を有する。液晶層に電圧を印加することで偏光方向が変化することを利用して、液晶層を透過する光の明暗(階調)を作ることで、画像表示が実現される。液晶層を透過する光には、外光(太陽光または照明光)によって液晶表示装置の表面から照射される光を用いる。

## 【0108】

本実施の形態の液晶素子は、絶縁層を間に挟んで画素電極の端部を隣接する画素電極の端部に重ねて設ける構成を有する。その結果、隣接する画素との間に生じる間隙を小さくでき、外光を反射する画素面積を大きく確保することができる。また、表示素子とフォトセンサを同一基板上に設ける構成においては、表示素子の画素電極の面積が制限されてしまうため、隣接する画素との間に生じる間隙を小さくできる構成は特に好適である。

## 【0109】

また、表示素子制御回路は、表示素子105を制御するための回路であり、ビデオデータ信号線などの信号線(「ソース信号線」ともいう。)を介して表示素子105に信号を入力する表示素子駆動回路107と、走査線(「ゲート信号線」ともいう。)を介して表示素子105に信号を入力する表示素子駆動回路108を有する。

## 【0110】

例えば、走査線側の表示素子駆動回路108は、特定の行に配置された画素が有する表示

10

20

30

40

50

素子を選択する機能を有する。また、信号線側の表示素子駆動回路 107 は、選択された行の画素が有する表示素子に任意の電位を与える機能を有する。なお、走査線側の表示素子駆動回路 108 により高電位を印加された表示素子では、トランジスタが導通状態となり、信号線側の表示素子駆動回路 107 により与えられる電荷が供給される。

【0111】

また、フォトセンサ 106 は、フォトダイオードなど、受光することで電気信号を発する機能を有する受光素子と、トランジスタとを有する。

【0112】

フォトセンサ制御回路は、フォトセンサ 106 を制御するための回路であり、フォトセンサ出力信号線、フォトセンサ基準信号線等の信号線側のフォトセンサ読み出し回路 109 と、走査線側のフォトセンサ駆動回路 110 を有する。走査線側のフォトセンサ駆動回路 110 は、特定の行に配置された画素が有するフォトセンサ 106 に対して、後述するリセット動作と選択動作とを行う機能を有する。また、信号線側のフォトセンサ読み出し回路 109 は、選択された行の画素が有するフォトセンサ 106 の出力信号を取り出す機能を有する。

10

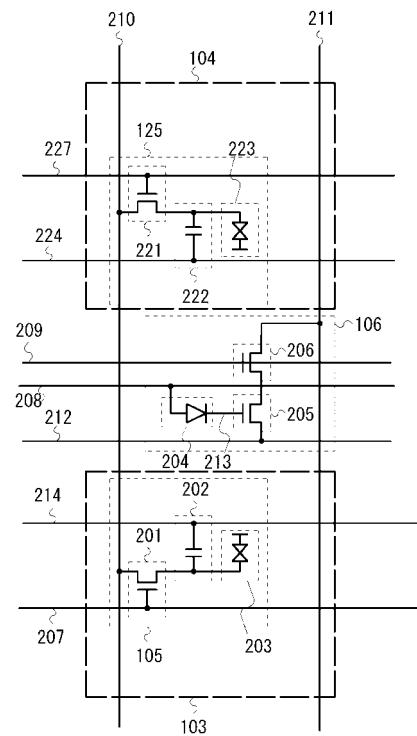

【0113】

本実施の形態では、画素 103 と、フォトセンサ 106 と、画素 104 の回路図について、図 12 を用いて説明する。画素 103 は、トランジスタ 201、保持容量 202 及び液晶素子 203 を有する表示素子 105 を有する。また、フォトセンサ 106 は、フォトダイオード 204、トランジスタ 205 及びトランジスタ 206 を有する。また、画素 104 は、トランジスタ 221、保持容量 222 及び液晶素子 223 を有する表示素子 125 を有する。

20

【0114】

トランジスタ 201 は、ゲートがゲート信号線 207 に、ソース又はドレインの一方がビデオデータ信号線 210 に、ソース又はドレインの他方が保持容量 202 の一方の電極と液晶素子 203 の一方の電極に電気的に接続されている。保持容量 202 の他方の電極は、容量配線 214 に電気的に接続され、一定の電位に保たれている。また、液晶素子 203 の他方の電極は一定の電位に保たれている。液晶素子 203 は、一対の電極と、該一対の電極の間の液晶層を含む素子である。

30

【0115】

トランジスタ 201 は、ゲート信号線 207 に電位 "H" が印加されると、ビデオデータ信号線 210 の電位を保持容量 202 と液晶素子 203 に印加する。保持容量 202 は、印加された電位を保持する。液晶素子 203 は、印加された電位により、光の透過率を変更する。

【0116】

フォトダイオード 204 は、一方の電極がフォトダイオードリセット信号線 208 に、他方の電極がトランジスタ 205 のゲートに電気的に接続されている。トランジスタ 205 は、ソース又はドレインの一方がフォトセンサ基準信号線 212 に、ソース又はドレインの他方がトランジスタ 206 のソース又はドレインの一方に電気的に接続されている。トランジスタ 206 は、ゲートが読み出し信号線 209 に、ソース又はドレインの他方がフォトセンサ出力信号線 211 に電気的に接続されている。

40

【0117】

また、トランジスタ 221 は、ゲートがゲート信号線 227 に、ソース又はドレインの一方がビデオデータ信号線 210 に、ソース又はドレインの他方が保持容量 222 の一方の電極と液晶素子 223 の一方の電極に電気的に接続されている。保持容量 222 の他方の電極は、容量配線 224 に電気的に接続され、一定の電位に保たれている。また、液晶素子 223 の他方の電極は一定の電位に保たれている。液晶素子 223 は、一対の電極と、該一対の電極の間の液晶層を含む素子である。

【0118】

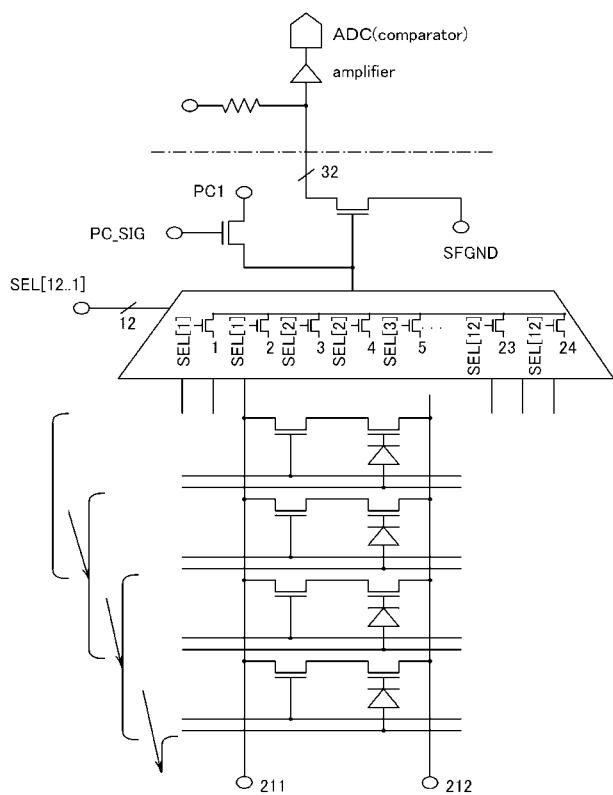

次に、フォトセンサ読み出し回路 109 の構成の一例について、図 12 及び図 13 を用い

50

て説明する。一例として、表示部は、1024行768列の画素で構成され、表示素子は各行各列の画素に1個、フォトセンサは2行各列の画素間に1個、を有する構成とする。すなわち、表示素子は1024行768列、フォトセンサは512行768列で構成される。また、フォトセンサ出力信号線は2列を1組として表示装置外部に出力する例を示す。すなわち、2行2列の画素4個に挟まれるフォトセンサ計2個から出力を1個取得する。

#### 【0119】

図12は、画素の回路構成で、2行1列分の2つの画素と、1つのフォトセンサを示している。表示素子を1画素に1個、フォトセンサを2画素間に1個、有する。図13は、フォトセンサ読み出し回路109の回路構成で、説明のため、一部のフォトセンサも示している。

10

#### 【0120】

図13に示すように、フォトセンサの走査線駆動回路は、同時に画素4行分に相当するフォトセンサ2行分を駆動し、選択行を画素2行分に相当するフォトセンサ1行分ずつシフトさせていく駆動方法を行う例を考える。ここで、各行のフォトセンサは、フォトセンサの走査線駆動回路に2回、連続して選択されることになる。このような駆動方法を用いることで、フォトセンサによる撮像のフレーム周波数を向上させることができることになる。特に、大型の表示装置の場合に有利である。なお、フォトセンサ出力信号線211には、同時に2行分のフォトセンサの出力が重畠されることになる。また、選択行のシフトを512回繰り返すことで、全フォトセンサを駆動することができる。

20

#### 【0121】

フォトセンサ読み出し回路109は、図13に示すように、画素24列に1個ずつセレクタを有する。セレクタは、表示部におけるフォトセンサ出力信号線211について2列分を1組とする12組から1組を選択して出力を取得する。すなわち、フォトセンサ読み出し回路109全体で、セレクタを32個有し、同時に32個の出力を取得する。各々のセレクタによる選択を12組全てに対して行うことで、フォトセンサ1行分に相当する合計384個の出力を取得することができる。セレクタによる12組の選択を、フォトセンサの走査線駆動回路が選択行をシフトさせる都度行うことで、全フォトセンサの出力を得ることができる。

30

#### 【0122】

本実施の形態では、図13に示すように、信号線側のフォトセンサ読み出し回路109は、アナログ信号であるフォトセンサの出力を表示装置外部に取り出し、表示装置外部に設けたアンプを用いて増幅した後にA/D変換器を用いてデジタル信号に変換する構成を考える。勿論、表示装置と同一基板上にA/D変換器を搭載し、フォトセンサの出力をデジタル信号に変換した後、表示装置外部に取り出す構成とすることも可能である。

#### 【0123】

また、個々のフォトセンサの動作は、リセット動作、累積動作、及び選択動作を繰り返すことで実現される。リセット動作とは、フォトダイオードリセット信号線208の電位を”H”とする動作である。リセット動作を行うと、フォトダイオード204が導通し、トランジスタ205のゲートが接続されたゲート信号線213の電位が”H”となる。

40

#### 【0124】

また、累積動作とは、リセット動作の後にフォトダイオードリセット信号線208の電位を”L”にする動作である。また、選択動作とは、累積動作の後に読み出し信号線209の電位を”H”にする動作である。

#### 【0125】

累積動作時に、フォトダイオード204に照射する光が強いほど、トランジスタ205のゲートが接続されたゲート信号線213の電位が下がり、トランジスタ205のチャネル抵抗が増大する。そのため、選択動作時に、トランジスタ206を介してフォトセンサ出力信号線211に流れる電流は小さくなる。一方、累積動作時に、フォトダイオード204に照射する光が弱いほど、選択動作時に、トランジスタ206を介してフォトセンサ出

50

力信号線 211 に流れる電流は大きくなる。

【0126】

本実施の形態においては、全フォトセンサのリセット動作、累積動作、及び選択動作を実行することで、外光の局所的陰影を検出することができる。また、検出した陰影について適宜画像処理などを行うことにより、指やペンなどが表示装置に接触した位置を知ることができる。あらかじめ、接触した位置に対応する操作、例えば文字入力であれば文字の種類を規定しておくことで、所望の文字の入力を行うことができる。

【0127】

なお、本実施の形態における表示装置では、フォトセンサにより外光の局所的陰影を検出する。そのため、指やペンなどが表示装置に物理的に接触しなくとも、非接触で近接することにより陰影が形成されれば検出が可能である。以下、指やペンなどが表示装置に接触するとは、非接触で近接することも含むものとする。

10

【0128】

上記構成により、表示部 1032 にタッチ入力機能を持たせることができる。

【0129】

タッチ入力を行う際には、キーボードのような静止画を一部に含む画像を表示し、表示されたキーボードの所望の文字の位置に指やペンを接触することで、入力を行う構成の表示装置とすると操作性が向上する。このような表示装置を実現する場合には、次のようにして、表示装置における消費電力を著しく低減することが可能である。すなわち、表示部の静止画を表示する第 1 画面領域については、静止画を表示した後は、当該領域の表示素子への電力の供給を停止し、その後もその静止画を視認可能な状態を長時間維持することが有効である。そして、表示部の残りの第 2 画面領域については、例えば、タッチ入力による入力結果を表示する。第 2 画面領域の表示画像の更新を行う時以外の期間では表示素子制御回路を非動作とすることで、電力の節約ができる。このような制御を可能にする駆動方法について、以下説明する。

20

【0130】

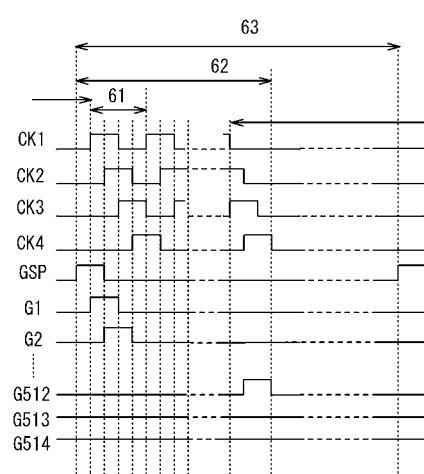

例えば、表示素子が 1024 行 768 列で配置された表示部を有する表示装置における、走査線駆動回路のシフトレジスタのタイミングチャートについて図 14 に示す。図 14 中の期間 61 はクロック信号の 1 周期期間 (64.8 μsec) であり、期間 62 は第 2 画面領域に相当する表示素子の第 1 行から第 512 行まで書き込むまでに要する期間 (8.36 msec) であり、期間 63 は 1 フレーム期間 (16.7 msec) にそれぞれ相当する。

30

【0131】

ここで、走査線駆動回路のシフトレジスタは、第 1 のクロック信号 CK1 ~ 第 4 のクロック信号 CK4 で動作する 4 相クロック形式のシフトレジスタとする。また、第 1 のクロック信号 CK1 ~ 第 4 のクロック信号 CK4 は、互いに 4 分の 1 周期期間ずつずれた信号とする。スタートパルス信号 GSP を電位 "H" とすると、第 1 行目のゲート信号線 G1 ~ 第 512 行目のゲート信号線 G512 は、4 分の 1 周期期間ずつ遅れながら順に電位 "H" となる。また、各ゲート信号線は、2 分の 1 周期期間電位 "H" となり、連続する行の 2 つのゲート信号線は、各々 4 分の 1 周期期間同時に電位 "H" となる。

40

【0132】

ここで、各行の表示素子は、走査線駆動回路が選択行のシフトを 2 回行う期間、連続して選択されることになる。表示画像のデータを、当該行における表示素子が選択されている期間の内、後半の期間に入力すれば表示画像を更新できる。

【0133】

ここで、第 2 画面領域に相当する表示素子の第 1 行から第 512 行までの表示画像を更新する期間を除く期間については、表示素子制御回路を非動作とする。すなわち、第 1 画面領域に相当する表示素子の第 513 行から第 1024 行までは表示画像の更新を行わず、表示素子制御回路を非動作としている。

【0134】

50

表示素子制御回路を非動作とするには、図14に示したように、クロック信号を停止（”L”のままとする）することで実現できる。また、同時に、電源電圧の供給を停止することも有効である。

【0135】

また、第2画面領域に相当する表示素子が選択されていない期間、すなわち、表示画像の更新を行わない期間は、ソース側の駆動回路も同様にクロック信号とスタートパルス信号を停止させてもよい。こうすることでさらなる電力の節約ができる。

【0136】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

10

【0137】

（実施の形態5）

本実施の形態では、カラーフィルタを設け、フルカラー表示が可能な液晶表示モジュールとする一例を示す。

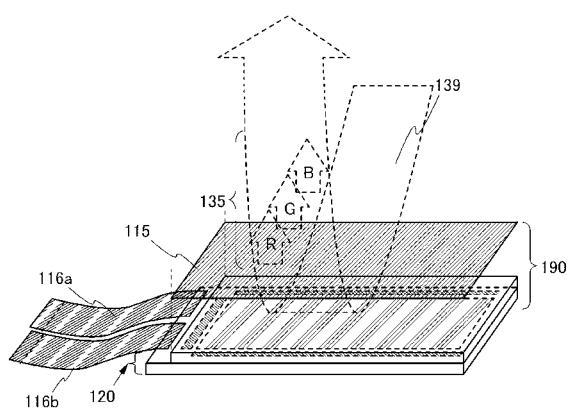

【0138】

図15に液晶表示モジュール190の構成を示す。液晶表示モジュール190は液晶素子がマトリクス状に設けられた表示パネル120と、表示パネル120と重なる偏光板及びカラーフィルタ115を有する。また、外部入力端子となるFPC（フレキシブルプリントサーキット）116a、116bは表示パネル120に設けた端子部と電気的に接続されている。表示パネル120は、実施の形態1の表示パネル100と同様の構成を有する。ただし、フルカラー表示とする場合であるため、表示パネル120は、赤色表示素子、緑色表示素子、青色表示素子の3つの表示素子を用い、それぞれに異なる映像信号を供給する回路構成とする。

20

【0139】

また、図15には、外光139が表示パネル120上の液晶素子を透過して反射電極で反射される様子を模式的に示してある。例えば、カラーフィルタの赤色領域と重なる画素においては、外光139がカラーフィルタ115を通過した後、液晶層を通過し、反射電極で反射され、再びカラーフィルタ115を通過して赤色光として取り出される。図15には、3色の光135が矢印（R、G、及びB）で模式的に示してある。液晶素子を透過する光の強度は、画像信号により変調されるため、観察者は外光139の反射光によって、映像を捉えることができる。

30

【0140】

また、表示パネル120はフォトセンサを有しており、タッチ入力機能を備えている。フォトセンサの受光領域にもカラーフィルタを重ねることによりフォトセンサを可視光センサとして機能させることもできる。また、フォトセンサの光の感度を向上させるためには、入射光を多く取り入れるため、フォトセンサの受光領域と重なる領域にはカラーフィルタに開口を設け、フォトセンサの受光領域とカラーフィルタが重ならない構成としてもよい。

【0141】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

40

【0142】

（実施の形態6）

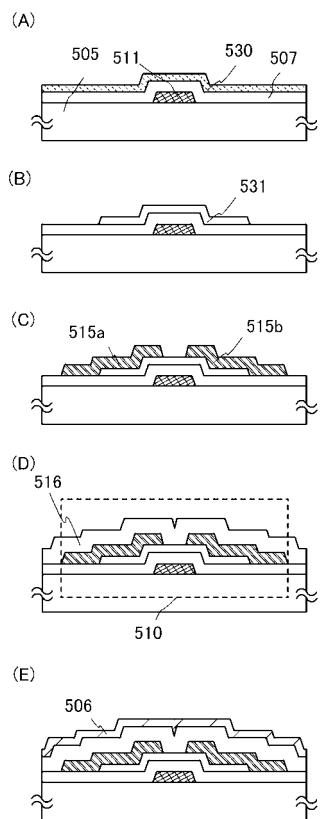

本実施の形態は、実施の形態1乃至3で説明した液晶表示装置に用いる酸化物半導体層を含むトランジスタ、及び作製方法の一例を、図18を用いて詳細に説明する。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

【0143】

図18（A）乃至（E）にトランジスタの断面構造の一例を示す。図18（A）乃至（E）に示すトランジスタ510は、図1（A）に示すトランジスタ350と同様なボトムゲ

50

ート構造の逆スタガ型トランジスタである。

【0144】

以下、図18(A)乃至(E)を用い、基板505上にトランジスタ510を作製する工程を説明する。

【0145】

まず、絶縁表面を有する基板505上に導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極層511を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0146】

本実施の形態では絶縁表面を有する基板505としてガラス基板を用いる。

【0147】

下地膜となる絶縁膜を基板505とゲート電極層511との間に設けてもよい。下地膜は、基板505からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

【0148】

また、ゲート電極層511は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

【0149】

次いで、ゲート電極層511上にゲート絶縁層507を形成する。ゲート絶縁層507は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、又は酸化ハフニウム層を単層で又は積層して形成することができる。

【0150】

本実施の形態の酸化物半導体は、不純物を除去され、I型化又は実質的にI型化された酸化物半導体を用いる。このような高純度化された酸化物半導体は界面準位、界面電荷に対して極めて敏感であるため、酸化物半導体層とゲート絶縁層との界面は重要である。そのため高純度化された酸化物半導体に接するゲート絶縁層は、高品質化が要求される。

【0151】

例えば、μ波(例えば周波数2.45GHz)を用いた高密度プラズマCVDは、緻密で絶縁耐圧の高い高品質な絶縁層を形成できるので好ましい。高純度化された酸化物半導体と高品質ゲート絶縁層とが密接することにより、界面準位を低減して界面特性を良好なものとすることができるからである。

【0152】

もちろん、ゲート絶縁層として良質な絶縁層を形成できるものであれば、スパッタリング法やプラズマCVD法など他の成膜方法を適用することができる。また、成膜後の熱処理によってゲート絶縁層の膜質、酸化物半導体との界面特性が改質される絶縁層であっても良い。いずれにしても、ゲート絶縁層としての膜質が良好であることは勿論のこと、酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

【0153】

また、ゲート絶縁層507、酸化物半導体膜530に水素、水酸基及び水分がなるべく含まれないようにするために、酸化物半導体膜530の成膜の前処理として、スパッタリング装置の予備加熱室でゲート電極層511が形成された基板505、又はゲート絶縁層507までが形成された基板505を予備加熱し、基板505に吸着した水素、水分などの不純物を脱離し排気することが好ましい。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、絶縁層516の成膜前に、ソース電極層515a及びドレイン電極層515bまで

10

20

30

40

50

形成した基板 505 にも同様に行ってよい。

【0154】

次いで、ゲート絶縁層 507 上に、膜厚 2 nm 以上 200 nm 以下、好ましくは 5 nm 以上 30 nm 以下の酸化物半導体膜 530 を形成する（図 18（A）参照。）。

【0155】

なお、酸化物半導体膜 530 をスパッタリング法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層 507 の表面に付着している粉状物質（パーティクル、ごみともいう）を除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側に RF 電源を用いて電圧を印加して基板にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気 10 に代えて窒素、ヘリウム、酸素などを用いてよい。

【0156】

酸化物半導体膜 530 に用いる酸化物半導体としては、四元系金属酸化物である In - Sn - Ga - Zn - O 系酸化物半導体や、三元系金属酸化物である In - Ga - Zn - O 系酸化物半導体、In - Sn - Zn - O 系酸化物半導体、In - Al - Zn - O 系酸化物半導体、Sn - Ga - Zn - O 系酸化物半導体、Al - Ga - Zn - O 系酸化物半導体、Sn - Al - Zn - O 系酸化物半導体や、二元系金属酸化物である In - Zn - O 系酸化物半導体、Sn - Zn - O 系酸化物半導体、Al - Zn - O 系酸化物半導体、Zn - Mg - O 系酸化物半導体、Sn - Mg - O 系酸化物半導体、In - Mg - O 系酸化物半導体、In - Ga - O 系酸化物半導体や、In - O 系酸化物半導体、Sn - O 系酸化物半導体、Zn - O 系酸化物半導体などを用いることができる。また、上記酸化物半導体に SiO<sub>2</sub> を含んでもよい。ここで、例えば、In - Ga - Zn - O 系酸化物半導体とは、インジウム（In）、ガリウム（Ga）、亜鉛（Zn）を有する酸化物膜、という意味であり、その化学量論比はとくに問わない。また、In と Ga と Zn 以外の元素を含んでもよい。本実施の形態では、酸化物半導体膜 530 として In - Ga - Zn - O 系酸化物ターゲットを用いてスパッタリング法により成膜する。この段階での断面図が図 18（A）に相当する。また、酸化物半導体膜 530 は、希ガス（代表的にはアルゴン）雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下においてスパッタ法により形成することができる。

【0157】

酸化物半導体膜 530 をスパッタリング法で作製するためのターゲットとしては、例えば、組成比として、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 1 [mol 数比] の酸化物ターゲットを用い、In - Ga - Zn - O 膜を成膜する。また、このターゲットの材料及び組成に限定されず、例えば、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 2 [mol 数比] の酸化物ターゲットを用いてよい。

【0158】

また、酸化物ターゲットの充填率は 90% 以上 100% 以下、好ましくは 95% 以上 99.9% 以下である。充填率の高い金属酸化物ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜とことができる。

【0159】

酸化物半導体膜 530 を、成膜する際に用いるスパッタガスは水素、水、水酸基又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0160】

減圧状態に保持された成膜室内に基板を保持し、基板温度を 100 以上 600 以下好ましくは 200 以上 400 以下とする。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。そして、成膜室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて基板 505 上に酸化物半導体膜 530 を成膜する。成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであつ

10

20

20

30

40

50

てもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水（H<sub>2</sub>O）など水素原子を含む化合物（より好ましくは炭素原子を含む化合物も）等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

#### 【0161】

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流（DC）電源0.5kW、酸素（酸素流量比率100%）雰囲気下の条件が適用される。なお、パルス直流電源を用いると、成膜時に発生する粉状物質（パーティクル、ごみともいう）が軽減でき、膜厚分布も均一となるために好ましい。

#### 【0162】

次いで、酸化物半導体膜530を第2のフォトリソグラフィ工程により島状の酸化物半導体層に加工する。また、島状の酸化物半導体層を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

#### 【0163】

また、ゲート絶縁層507にコンタクトホールを形成する場合、その工程は酸化物半導体膜530の加工時に同時に行うことができる。

#### 【0164】

なお、ここで酸化物半導体膜530のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。例えば、酸化物半導体膜530のウェットエッチングに用いるエッチング液としては、磷酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO07N（関東化学社製）を用いてもよい。

#### 【0165】

次いで、酸化物半導体層に第1の加熱処理を行う。この第1の加熱処理によって酸化物半導体層の脱水化または脱水素化を行うことができる。第1の加熱処理の温度は、400以上750以下、または400以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層531を得る（図18（B）参照。）。

#### 【0166】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を用いてもよい。例えば、GRTA（Gas Rapid Thermal Anneal）装置、LRTA（Lamp Rapid Thermal Anneal）装置等のRTA（Rapid Thermal Anneal）装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光（電磁波）の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。高温のガスには、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

#### 【0167】

例えば、第1の加熱処理として、650～700の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すGRTAを行ってもよい。

#### 【0168】

なお、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N（99.9999%）以上好ましくは7N（99.99999%）以上（即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下）とすることが好ましい。

#### 【0169】

10

20

30

40

50

また、第1の加熱処理で酸化物半導体層を加熱した後、同じ炉に高純度の酸素ガス、高純度のN<sub>2</sub>Oガス、又は超乾燥エア（露点が-40以下、好ましくは-60以下）を導入してもよい。酸素ガスまたはN<sub>2</sub>Oガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する酸素ガスまたはN<sub>2</sub>Oガスの純度を、6N以上好ましくは7N以上（即ち、酸素ガスまたはN<sub>2</sub>Oガス中の不純物濃度を1ppm以下、好ましくは0.1ppm以下）とすることが好ましい。酸素ガス又はN<sub>2</sub>Oガスの作用により、脱水化または脱水素化処理による不純物の排除工程によって同時に減少してしまった酸化物半導体を構成する主成分材料である酸素を供給することによって、酸化物半導体層を高純度化及び電気的にI型（真性）化する。

## 【0170】

10

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜530に行うことでもできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

## 【0171】

なお、第1の加熱処理は、上記以外にも、酸化物半導体層成膜後であれば、酸化物半導体層上にソース電極層及びドレイン電極層を積層させた後、あるいは、ソース電極層及びドレイン電極層上に絶縁層を形成した後、のいずれで行ってもよい。

## 【0172】

20

また、ゲート絶縁層507にコンタクトホールを形成する場合、その工程は酸化物半導体膜530に第1の加熱処理を行う前でも行った後に行ってもよい。

## 【0173】

30

また、酸化物半導体層を2回に分けて成膜し、2回に分けて加熱処理を行うことで、下地部材の材料が、酸化物、窒化物、金属など材料を問わず、膜厚の厚い結晶領域（単結晶領域）、即ち、膜表面に垂直にc軸配向した結晶領域を有する酸化物半導体層を形成してもよい。例えば、3nm以上15nm以下の第1の酸化物半導体膜を成膜し、窒素、酸素、希ガス、または乾燥空気の雰囲気下で450以上850以下、好ましくは550以上750以下の第1の加熱処理を行い、表面を含む領域に結晶領域（板状結晶を含む）を有する第1の酸化物半導体膜を形成する。そして、第1の酸化物半導体膜よりも厚い第2の酸化物半導体膜を形成し、450以上850以下、好ましくは600以上700以下の第2の加熱処理を行い、第1の酸化物半導体膜を結晶成長の種として、上方に結晶成長させ、第2の酸化物半導体膜の全体を結晶化させ、結果として膜厚の厚い結晶領域を有する酸化物半導体層を形成してもよい。

40

## 【0174】

次いで、ゲート絶縁層507、及び酸化物半導体層531上に、ソース電極層及びドレイン電極層（これと同じ層で形成される配線を含む）となる導電膜を形成する。ソース電極層、及びドレイン電極層に用いる導電膜としては、例えば、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素を含む金属膜、または上述した元素を成分とする金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タンゲステン膜）等を用いることができる。また、Al、Cuなどの金属膜の下側又は上側の一方または双方にTi、Mo、Wなどの高融点金属膜またはそれらの金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タンゲステン膜）を積層させた構成としてもよい。

## 【0175】

第3のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層515a、ドレイン電極層515bを形成した後、レジストマスクを除去する（図18（C）参照。）。

## 【0176】

50

第3のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いるとよい。酸化物半導体層531上で隣り合うソース電極層の下端部とドレイン電極層の下端部との間隔幅によって後に形成されるトランジスタのチャネル長Lが決定される。なお、チャネル長L=25nm未満の露光を行う場合には、

数 nm ~ 数 10 nm と極めて波長が短い超紫外線 (Extreme Ultraviolet) を用いて第3のフォトリソグラフィ工程でのレジストマスク形成時の露光を行うとよい。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長 L を 10 nm 以上 1000 nm 以下とすることも可能であり、回路の動作速度を高速化できる。

【0177】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

10

【0178】

なお、導電膜のエッチングの際に、酸化物半導体層 531 がエッチングされ、分断することのないようエッチング条件を最適化することが望まれる。しかしながら、導電膜のみをエッチングし、酸化物半導体層 531 を全くエッチングしないという条件を得ることは難しく、導電膜のエッチングの際に酸化物半導体層 531 は一部のみがエッチングされ、溝部（凹部）を有する酸化物半導体層 531 となることもある。

20

【0179】

本実施の形態では、導電膜として Ti 膜を用い、酸化物半導体層 531 には In-Ga-Zn-O 系酸化物半導体を用いたので、導電膜のエッチャントとしてアンモニア過水（アンモニア、水、過酸化水素水の混合液）を用いる。

20

【0180】

次いで、N<sub>2</sub>O、N<sub>2</sub>、または Ar などのガスを用いたプラズマ処理を行い、露出している酸化物半導体層の表面に付着した吸着水などを除去してもよい。プラズマ処理を行った場合、大気に触れることなく、酸化物半導体層の一部に接する保護絶縁膜となる絶縁層 516 を形成する。

30

【0181】

絶縁層 516 は、少なくとも 1 nm 以上の膜厚とし、スパッタ法など、絶縁層 516 に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。絶縁層 516 に水素が含まれると、その水素の酸化物半導体層への侵入、又は水素による酸化物半導体層中の酸素の引き抜き、が生じ酸化物半導体層のバックチャネルが低抵抗化（N型化）してしまい、寄生チャネルが形成されるおそれがある。よって、絶縁層 516 はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。

【0182】

本実施の形態では、絶縁層 516 として膜厚 200 nm の酸化シリコン膜を、スパッタリング法を用いて成膜する。成膜時の基板温度は、室温以上 300 以下とすればよく、本実施の形態では 100 とする。酸化シリコン膜のスパッタ法による成膜は、希ガス（代表的にはアルゴン）雰囲気下、酸素雰囲気下、または希ガスと酸素の混合雰囲気下において行うことができる。また、ターゲットとして酸化シリコンターゲットまたはシリコンターゲットを用いることができる。例えば、シリコンターゲットを用いて、酸素を含む雰囲気下でスパッタ法により酸化シリコンを形成することができる。酸化物半導体層に接して形成する絶縁層 516 は、水分や、水素イオンや、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをロックする無機絶縁膜を用い、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用いる。

40

【0183】

酸化物半導体膜 530 の成膜時と同様に、絶縁層 516 の成膜室内の残留水分を除去する

50

ためには、吸着型の真空ポンプ（クライオポンプなど）を用いることが好ましい。クライオポンプを用いて排気した成膜室で成膜した絶縁層516に含まれる不純物の濃度を低減できる。また、絶縁層516の成膜室内の残留水分を除去するための排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。

【0184】

絶縁層516を成膜する際に用いるスパッタガスは、水素、水、水酸基又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0185】

次いで、不活性ガス雰囲気下、または酸素ガス雰囲気下で第2の加熱処理（好ましくは200以上400以下、例えば250以上350以下）を行う。例えば、窒素雰囲気下で250、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層の一部（チャネル形成領域）が絶縁層516と接した状態で加熱される。

10

【0186】

以上の工程を経ることによって、酸化物半導体膜に対して第1の加熱処理を行って水素、水分、水酸基又は水素化物（水素化合物ともいう）などの不純物を酸化物半導体層より意図的に排除し、かつ不純物の排除工程によって同時に減少してしまう酸化物半導体を構成する主成分材料の一つである酸素を供給することができる。よって、酸化物半導体層は高純度化及び電気的にI型（真性）化する。

【0187】

以上の工程でトランジスタ510が形成される（図18（D）参照。）。

20

【0188】

また、絶縁層516に欠陥を多く含む酸化シリコン層を用いると、酸化シリコン層形成後の加熱処理によって酸化物半導体層中に含まれる水素、水分、水酸基又は水素化物などの不純物を酸化物絶縁層に拡散させ、酸化物半導体層中に含まれる該不純物をより低減させる効果を奏する。

【0189】

絶縁層516上にさらに保護絶縁層506を形成してもよい。保護絶縁層506としては、例えば、RFスパッタ法を用いて窒化シリコン膜を形成する。RFスパッタ法は、量産性がよいため、保護絶縁層の成膜方法として好ましい。保護絶縁層は、水分などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、窒化シリコン膜、窒化アルミニウム膜などを用いる。本実施の形態では、保護絶縁層として窒化シリコン膜を用いて保護絶縁層506を形成する（図18（E）参照。）。

30

【0190】

本実施の形態では、保護絶縁層506として、絶縁層516まで形成された基板505を100～400の温度に加熱し、水素及び水分が除去された高純度窒素を含むスパッタガスを導入しシリコン半導体のターゲットを用いて窒化シリコン膜を成膜する。この場合においても、絶縁層516と同様に、処理室内の残留水分を除去しつつ保護絶縁層506を成膜することが好ましい。

【0191】

保護絶縁層の形成後、さらに大気中、100以上200以下、1時間以上30時間以下での加熱処理を行ってもよい。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100以上200以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。

40

【0192】

このように、本実施の形態で例示したトランジスタは、高い電界効果移動度が得られるため、高速駆動が可能である。よって、液晶表示装置の画素部に高純度化された酸化物半導体層を含むトランジスタを用いることで、色分離を抑制することができ、高画質な画像を提供することができる。また、高純度化された酸化物半導体層を含むトランジスタによって、同一基板上に駆動回路部または画素部を作り分けて作製することができるため、液晶表示装置の部品点数を削減することができる。

50

## 【0193】

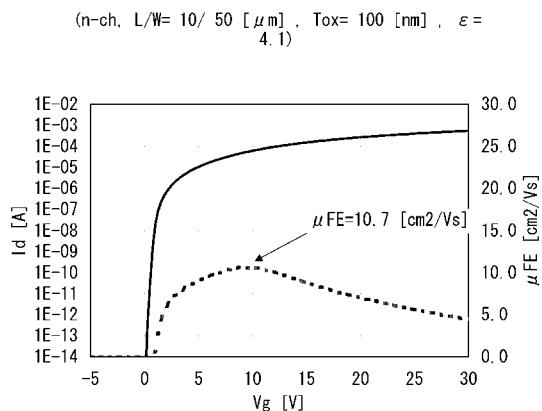

高純度化された酸化物半導体を用いたトランジスタの電界効果移動度を求めた結果について説明する。

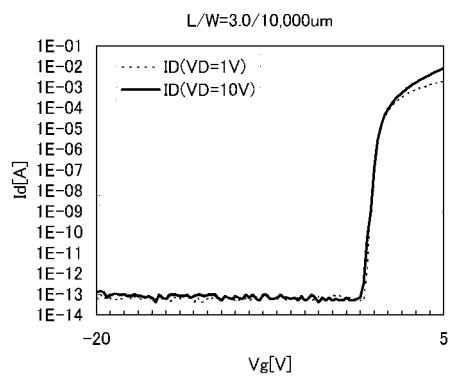

## 【0194】

上述した本実施の形態の作製方法に従って、高純度化された酸化物半導体（膜厚50nmのIn-Ga-Zn-O系酸化物半導体膜）を用いてトランジスタ（L/W=10μm/50μm）を作製し、基板温度を室温とし、ソース-ドレイン間電圧（以下、ドレイン電圧またはVdという）を10Vとし、ソース-ゲート間電圧（以下、ゲート電圧またはVgという）を-30V～+30Vまで変化させたときのソース-ドレイン電流（以下、ドレイン電流またはIdという）の変化特性、すなわちVg-Id特性を測定した。なお、図19では、Vgを-5V～+30Vまでの範囲で示している。図19に示すように高純度化された酸化物半導体層を含むトランジスタの電界移動度μFEの最大値は、10.7cm<sup>2</sup>/Vssecであることが確認できる。

10

## 【0195】

また、高純度化された酸化物半導体層を含むトランジスタを用いることにより、オフ状態における電流値（オフ電流値）をより低くすることができる。よって、画像信号等の電気信号の保持時間を長くすることができ、書き込み間隔も長く設定できる。よって、リフレッシュ動作の頻度をより少なくすることができるため、消費電力を抑制する効果を高くできる。

20

## 【0196】

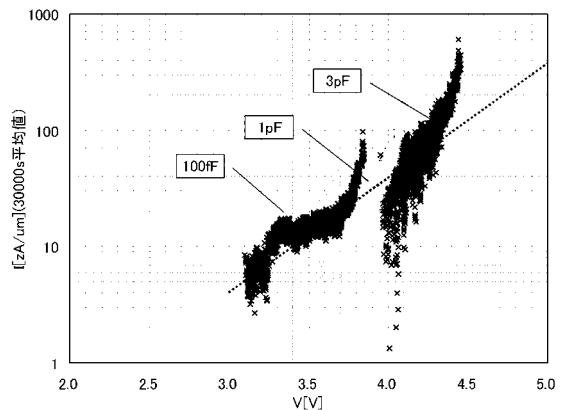

また、高純度化された酸化物半導体を用いたトランジスタのオフ電流を求めた結果について説明する。

## 【0197】

上述した本実施の形態の作製方法に従って、高純度化された酸化物半導体を用いてトランジスタを作製した。まず、高純度化された酸化物半導体を用いたトランジスタのオフ電流が十分に小さいことを考慮して、チャネル幅Wが1cmと十分に大きいトランジスタを用意してオフ電流の測定を行った。チャネル幅Wが1cmのトランジスタのオフ電流を測定した結果を図20に示す。図20において、横軸はゲート電圧VG、縦軸はドレイン電流Idである。ドレイン電圧Vdが+1Vまたは+10Vの場合、ゲート電圧VGが-5Vから-20Vの範囲では、トランジスタのオフ電流は、検出限界である $1 \times 10^{-13} A$ 以下であることがわかった。また、トランジスタのオフ電流（ここでは、単位チャネル幅（1μm）あたりの値）は $10 aA/\mu m$  ( $1 \times 10^{-17} A/\mu m$ )以下となることがわかった。

30

## 【0198】

次に、高純度化された酸化物半導体を用いたトランジスタのオフ電流をさらに正確に求めた結果について説明する。上述したように、高純度化された酸化物半導体を用いたトランジスタのオフ電流は、測定器の検出限界である $1 \times 10^{-13} A$ 以下であることがわかった。そこで、特性評価用素子を作製し、より正確なオフ電流の値（上記測定における測定器の検出限界以下の値）を求めた結果について説明する。

40

## 【0199】

電流測定方法に用いた特性評価用素子について、以下に説明する。

## 【0200】

特性評価用素子は、3つ並列に接続された測定系を用いる。それぞれの測定系は、容量素子、第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、及び第4のトランジスタを有する。第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、及び第4のトランジスタは、本実施の形態に従って作製し、図18(D)に示したトランジスタ510と同じ構造のものを使用した。

## 【0201】

一つの測定系は、第1のトランジスタのソース端子およびドレイン端子の一方と、容量素子の端子の一方と、第2のトランジスタのソース端子およびドレイン端子の一方は、電源

50

(V2を与える電源)に接続する。また、第1のトランジスタのソース端子およびドレイン端子の他方と、第3のトランジスタのソース端子およびドレイン端子の一方と、容量素子の端子の他方と、第2のトランジスタのゲート端子とは、接続する。また、第3のトランジスタのソース端子およびドレイン端子の他方と、第4のトランジスタのソース端子およびドレイン端子の一方と、第4のトランジスタのゲート端子は、電源(V1を与える電源)に接続する。また、第2のトランジスタのソース端子およびドレイン端子の他方と、第4のトランジスタのソース端子およびドレイン端子の他方とを接続し、出力端子Voutとする。

#### 【0202】

なお、第1のトランジスタのゲート端子には、第1のトランジスタのオン状態と、オフ状態を制御する電位Vext\_b2が供給され、第3のトランジスタのゲート端子には、第3のトランジスタのオン状態と、オフ状態を制御する電位Vext\_b1が供給される。また、出力端子からは電位Voutが出力される。

10

#### 【0203】

次に、上記の測定系を用いてオフ電流の測定を行う。

#### 【0204】

オフ電流を測定するために初期期間において電位差を付与し、測定期間が開始されると、時間の経過と共に第2のトランジスタのゲート端子の電位が変動する。従って、時間の経過と共に、出力端子の出力電位Voutの電位も変化することとなる。こうして得られた出力電位Voutから、オフ電流を算出することができる。

20

#### 【0205】

第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、及び第4のトランジスタは、それぞれチャネル長L=10μm、チャネル幅W=50μmの、高純度化した酸化物半導体を用いたトランジスタである。また、並列された3つ測定系において、第1の測定系の容量素子の容量値を100fFとし、第2の測定系の容量素子の容量値を1pFとし、第3の測定系の容量素子の容量値を3pFとした。

#### 【0206】

なお、オフ電流の測定では、VDD=5V、VSS=0Vとした。また、測定期間においては、電位V1を原則としてVSSとし、10~300secごとに、100msecの期間だけVDDとしてVoutを測定した。また、素子に流れる電流Iの算出に用いられるtは、約30000secとした。

30

#### 【0207】

図21には、上記電流測定によって算出されたオフ電流を示す。なお、図21は、ソース-ドレイン電圧Vと、オフ電流Iとの関係を表すものである。図21から、ソース-ドレイン電圧が4Vの条件において、オフ電流は約40zA/μmであることが分かった。また、ソース-ドレイン電圧が3.1Vの条件において、オフ電流は10zA/μm以下であることが分かった。なお、1zAは10^-21Aを表す。

#### 【0208】

以上、本実施の形態により、高純度化された酸化物半導体を用いたトランジスタでは、オフ電流が十分に小さくなることが確認された。

40

#### 【0209】

(実施の形態7)

本実施の形態においては、上記実施の形態で説明した液晶表示装置を具備する電子機器の例について説明する。

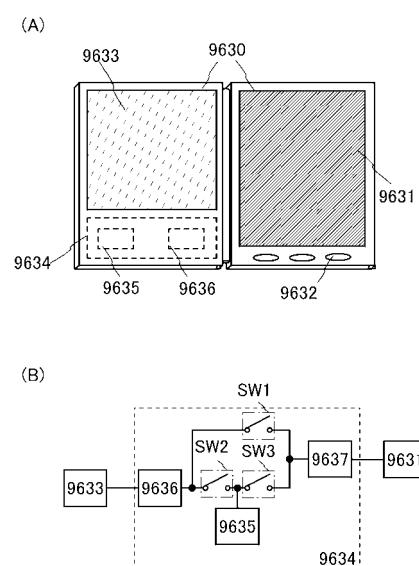

#### 【0210】

図16(A)は電子書籍(E-bookともいう)であり、筐体9630、表示部9631、操作キー9632、太陽電池9633、充放電制御回路9634を有することができる。太陽電池9633と、表示パネルとを開閉自在に装着しており、太陽電池からの電力を表示パネル、または映像信号処理部に供給する電子書籍である。図16(A)に示した電子書籍は、様々な情報(静止画、動画、テキスト画像など)を表示する機能、カレンダ

50

一、日付又は時刻などを表示部に表示する機能、表示部に表示した情報をタッチ入力操作又は編集するタッチ入力機能、様々なソフトウェア（プログラム）によって処理を制御する機能、等を有することができる。なお、図16（A）では充放電制御回路9634の一例としてバッテリー9635、DCDCコンバータ（以下、コンバータ9636と略記）を有する構成について示している。

【0211】

表示部9631としては、フォトセンサを利用したタッチ入力機能を備えた反射型の液晶表示装置を用いる場合、比較的明るい状況下での使用が予想され、太陽電池9633による発電、及びバッテリー9635での充電を効率よく行うことができ、好適である。なお太陽電池9633は、筐体9630の表面及び裏面に効率的なバッテリー9635の充電を行う構成とすることができますため好適である。なおバッテリー9635としては、リチウムイオン電池を用いると、小型化を図れる等の利点がある。

10

【0212】

また図16（A）に示す充放電制御回路9634の構成、及び動作について図16（B）にブロック図を示し説明する。図16（B）には、太陽電池9633、バッテリー9635、コンバータ9636、コンバータ9637、スイッチSW1乃至SW3、表示部9631について示しており、バッテリー9635、コンバータ9636、コンバータ9637、スイッチSW1乃至SW3が充放電制御回路9634に対応する箇所となる。

20

【0213】

まず外光により太陽電池9633により発電がされる場合の動作の例について説明する。太陽電池で発電した電力は、バッテリー9635を充電するための電圧となるようコンバータ9636で昇圧または降圧がなされる。そして、表示部9631の動作に太陽電池9633からの電力が用いられる際にはスイッチSW1をオンにし、コンバータ9637で表示部9631に必要な電圧に昇圧または降圧をすることとなる。また、表示部9631での表示を行わない際には、SW1をオフにし、SW2をオンにしてバッテリー9635の充電を行う構成とすればよい。

30

【0214】

なお太陽電池9633については、充電手段の一例として示したが、他の手段によるバッテリー9635の充電を行う構成であってもよい。また他の充電手段を組み合わせて行う構成としてもよい。

【0215】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

30

【符号の説明】

【0216】

|       |                      |    |

|-------|----------------------|----|

| 100   | 表示パネル                | 40 |

| 101   | 画素回路                 |    |

| 103   | 画素                   |    |

| 104   | 画素                   |    |

| 105   | 表示素子                 |    |

| 106   | フォトセンサ               |    |

| 107   | 表示素子駆動回路             |    |

| 108   | 表示素子駆動回路             |    |

| 109   | 回路                   |    |

| 110   | フォトセンサ駆動回路           |    |

| 115   | カラーフィルタ              |    |

| 116 a | FPC（フレキシブルプリントサーキット） |    |

| 120   | 表示パネル                |    |

| 125   | 表示素子                 |    |

| 135   | 光                    | 50 |

|         |                 |    |

|---------|-----------------|----|

| 1 3 9   | 外光              |    |

| 1 9 0   | 液晶表示モジュール       |    |

| 2 0 1   | トランジスタ          |    |

| 2 0 2   | 保持容量            |    |

| 2 0 3   | 液晶素子            |    |

| 2 0 4   | フォトダイオード        |    |

| 2 0 5   | トランジスタ          |    |

| 2 0 6   | トランジスタ          |    |

| 2 0 7   | ゲート信号線          |    |

| 2 0 8   | フォトダイオードリセット信号線 | 10 |

| 2 0 9   | 信号線             |    |

| 2 1 0   | ビデオデータ信号線       |    |

| 2 1 1   | フォトセンサ出力信号線     |    |

| 2 1 2   | フォトセンサ基準信号線     |    |

| 2 1 3   | ゲート信号線          |    |

| 2 1 4   | 容量配線            |    |

| 2 2 1   | トランジスタ          |    |

| 2 2 2   | 保持容量            |    |

| 2 2 3   | 液晶素子            |    |

| 2 2 4   | 容量配線            | 20 |

| 2 2 7   | ゲート信号線          |    |

| 2 3 0   | 基板              |    |

| 2 3 1   | 絶縁層             |    |

| 2 3 2   | ゲート絶縁層          |    |

| 2 3 3   | 酸化物半導体層         |    |

| 2 3 4   | 電極層             |    |

| 2 3 5   | 電極層             |    |

| 2 3 7   | 絶縁層             |    |

| 2 3 8   | p層              |    |

| 2 3 9   | i層              | 30 |

| 2 4 0   | n層              |    |

| 2 4 1   | 絶縁層             |    |

| 2 4 2   | 反射電極層           |    |

| 2 4 3   | 接続電極層           |    |

| 2 4 4   | 配向膜             |    |

| 2 4 5   | 凹部              |    |

| 2 5 1   | 電極層             |    |

| 2 5 2   | 電極層             |    |

| 2 5 3   | 酸化物半導体層         |    |

| 2 5 4   | 電極層             | 40 |

| 2 5 5   | 酸化物半導体層         |    |

| 2 5 6   | 酸化物半導体層         |    |

| 2 5 7   | 電極層             |    |

| 2 5 8   | 電極層             |    |

| 2 5 9   | 電極層             |    |

| 3 0 0   | 基板              |    |

| 3 0 7   | 絶縁層             |    |

| 3 0 8   | 絶縁層             |    |

| 3 4 0   | レジストマスク         |    |

| 3 4 0 a | レジストマスク         | 50 |

|         |          |    |

|---------|----------|----|

| 3 4 0 b | レジストマスク  |    |

| 3 5 0   | トランジスタ   |    |

| 3 5 0 B | トランジスタ   |    |

| 3 5 0 G | トランジスタ   |    |

| 3 5 0 R | トランジスタ   |    |

| 3 7 0   | 絶縁層      |    |

| 4 0 3   | 対向電極     |    |

| 4 0 4   | 配向膜      |    |

| 4 0 5   | 液晶層      |    |

| 4 0 8   | 対向基板     | 10 |

| 4 1 1   | 画素電極     |    |

| 4 1 1 a | 画素電極     |    |

| 4 1 1 b | 画素電極     |    |

| 4 1 2   | 画素電極     |    |

| 4 1 3   | 画素電極     |    |

| 4 1 4   | 配向膜      |    |

| 4 2 1   | 絶縁層      |    |

| 4 2 2   | 絶縁層      |    |

| 4 3 1   | 絶縁層      |    |

| 4 4 1   | スペーサ     | 20 |

| 4 5 0   | 液晶表示装置   |    |

| 4 5 1   | 画素       |    |

| 4 5 2   | 画素       |    |

| 4 5 3   | 画素       |    |

| 4 6 0   | 液晶表示装置   |    |

| 4 6 1   | 画素       |    |

| 4 6 2   | 画素       |    |

| 4 7 0   | 液晶表示装置   |    |

| 4 7 1   | 画素       |    |

| 4 7 2   | 画素       | 30 |

| 4 8 0   | 液晶表示装置   |    |

| 4 9 0   | 液晶表示装置   |    |

| 5 0 5   | 基板       |    |

| 5 0 6   | 保護絶縁層    |    |

| 5 0 7   | ゲート絶縁層   |    |

| 5 1 0   | トランジスタ   |    |

| 5 1 1   | ゲート電極層   |    |

| 5 1 2   | ゲート信号線 G |    |

| 5 1 5 a | ソース電極層   |    |

| 5 1 5 b | ドレイン電極層  | 40 |

| 5 1 6   | 絶縁層      |    |

| 5 3 0   | 酸化物半導体膜  |    |

| 5 3 1   | 酸化物半導体層  |    |

| 1 0 3 2 | 表示部      |    |

| 9 6 3 0 | 筐体       |    |

| 9 6 3 1 | 表示部      |    |

| 9 6 3 2 | 操作キー     |    |

| 9 6 3 3 | 太陽電池     |    |

| 9 6 3 4 | 充放電制御回路  |    |

| 9 6 3 5 | バッテリー    | 50 |

9 6 3 6 コンバータ

9 6 3 7 コンバータ

【図 1】

【図 2】

【図3】

(A)

(B)

【図4】

【図5】

【図6】

(A)

(B)

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

【図17】

【図18】

【図19】

【図21】

【図20】