(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2009-545133

(P2009-545133A)

(43) 公表日 平成21年12月17日(2009.12.17)

(51) Int.Cl.

H01L 27/148 (2006.01)

H04N 5/335 (2006.01)

F 1

H01L 27/14

H04N 5/335

テーマコード(参考)

4M118

5C024

審査請求 未請求 予備審査請求 未請求 (全 27 頁)

(21) 出願番号 特願2009-520753 (P2009-520753)

(86) (22) 出願日 平成19年7月9日 (2007.7.9)

(85) 翻訳文提出日 平成21年1月19日 (2009.1.19)

(86) 國際出願番号 PCT/US2007/015641

(87) 國際公開番号 WO2008/010924

(87) 國際公開日 平成20年1月24日 (2008.1.24)

(31) 優先権主張番号 11/490,383

(32) 優先日 平成18年7月20日 (2006.7.20)

(33) 優先権主張国 米国(US)

(71) 出願人 590000846

イーストマン コダック カンパニー

アメリカ合衆国 ニューヨーク州 ロチェスター ステート ストリート 343

(74) 代理人 100070150

弁理士 伊東 忠彦

(74) 代理人 100091214

弁理士 大貫 進介

(74) 代理人 100107766

弁理士 伊東 忠重

(72) 発明者 パークス, クリストファー

アメリカ合衆国 ニューヨーク州 146

12 ロチェスター ケンタッキー・クロッシング 113

最終頁に続く

(54) 【発明の名称】複数出力の電荷結合素子

## (57) 【要約】

画像センサは、一方向で一画素おきに同じ色を有する少なくとも2つの色の色フィルタ・パターンでオーバレイされた複数の画素と、1つおきの画素色フィルタ繰り返しパターンに平行に配向された3つ以上の電荷結合素子であって、それぞれの電荷結合素子が第1のゲート及び第2のゲートを有する電荷結合素子と、電荷結合素子のうちの少なくとも2つの出力における電荷検出増幅器と、CCD対CCD転送ゲートの一方側に第1のゲートがあり、CCD対CCD転送ゲートの反対側に第2のゲートがある、隣接した電荷結合素子を接続するCCD対CCD転送ゲートとを含み、CCD対CCD転送ゲートは全て、電気接続されており、第1のゲートは全て、電気接続されている。

## 【特許請求の範囲】

## 【請求項 1】

画像センサであって、

一方向で一画素おきに同じ色を有する少なくとも 2 つの色の色フィルタ・パターンでオーバレイされた複数の画素と、

1 つおきの画素色フィルタ繰り返しパターンに平行に配向された 3 つ以上の電荷結合素子であって、それぞれの電荷結合素子が第 1 のゲート及び第 2 のゲートを有する電荷結合素子と、

前記電荷結合素子のうちの少なくとも 2 つの出力における電荷検出增幅器と、

C C D 対 C C D 転送ゲートの一方側に第 1 のゲートがあり、C C D 対 C C D 転送ゲートの反対側に第 2 のゲートがある、隣接した電荷結合素子を接続する C C D 対 C C D 転送ゲートとを含み、C C D 対 C C D 転送ゲートは全て、電気接続されており、第 1 のゲートは全て、電気接続されており、第 2 のゲートは全て、電気接続されている画像センサ。10

## 【請求項 2】

請求項 1 記載の画像センサであって、前記複数の画素から最も遠い電荷結合素子への C C D 転送ゲートにドレインによって接続された電荷ドレインを更に備える画像センサ。

## 【請求項 3】

請求項 1 記載の画像センサであって、前記色フィルタ・パターンは、2 つの緑色画素、1 つの赤色画素、及び 1 つの青色画素を有する 2 × 2 画素のベイヤー色フィルタ・パターンである画像センサ。20

## 【請求項 4】

画像センサであって、

一方向で一画素おきに同じ色を有する少なくとも 2 つの色の色フィルタ・パターンでオーバレイされた複数の画素と、

1 つおきの画素色フィルタ繰り返しパターンに平行に配向された 3 つ以上の電荷結合素子であって、それぞれの電荷結合素子が第 1 のゲート、第 2 のゲート、第 3 のゲート及び第 4 のゲートをその順に有する電荷結合素子と、

前記電荷結合素子のうちの少なくとも 2 つの出力における電荷検出增幅器と、

C C D 対 C C D 転送ゲートの一方側に前記第 1 のゲート又は前記第 3 のゲートがあり、C C D 対 C C D 転送ゲートの反対側に前記第 2 のゲート又は前記第 4 のゲートがある、隣接した電荷結合素子を接続する C C D 対 C C D 転送ゲートとを含み、30

C C D 対 C C D 転送ゲートは全て、電気接続されており、第 1 のゲートは全て、電気接続されており、第 2 のゲートは全て、電気接続されており、第 3 のゲートは全て、電気接続されており、第 4 のゲートは全て、電気接続されている画像センサ。

## 【請求項 5】

請求項 3 記載の画像センサであって、前記複数の画素から最も遠い電荷結合素子への C C D 転送ゲートにドレインによって接続された電荷ドレインを更に備え、前記 C C D 転送ゲートへのドレインが前記 C C D 対 C C D 転送ゲートに電気接続されている画像センサ。

## 【請求項 6】

請求項 4 記載の画像センサであって、前記色フィルタ・パターンは、2 つの緑色画素、1 つの赤色画素、及び 1 つの青色画素を有する 2 × 2 画素のベイヤー色フィルタ・パターンである画像センサ。40

## 【請求項 7】

画像センサを動作させる方法であって、

一方向で一画素おきに同じ色を有する少なくとも 2 つの色の色フィルタ・パターンでオーバレイされた複数の画素を提供する工程と、

1 つおきの画素色フィルタ繰り返しパターンに平行に配向された 3 つ以上の電荷結合素子を提供する工程であって、それぞれの電荷結合素子が第 1 のゲート、第 2 のゲート、第 3 のゲート、及び第 4 のゲートを順に有する工程と、

前記電荷結合素子のうちの少なくとも 2 つの出力における電荷検出增幅器を提供する工50

程と、

C C D 対 C C D 転送ゲートの一方側に前記第1のゲート又は前記第3のゲートがあり、C C D 対 C C D 転送ゲートの反対側に前記第2のゲート又は前記第4のゲートそれぞれがある、隣接した電荷結合素子を接続するC C D 対 C C D 転送ゲートを提供する工程とを含み、

C C D 対 C C D 転送ゲートは全て、電気接続されており、第1のゲートは全て、電気接続されており、第2のゲートは全て、電気接続されており、第3のゲートは全て、電気接続されており、第4のゲートは全て、電気接続されており、C C D 対 C C D 転送ゲートは第1のモードで動作され、前記第1のモードでは、前記複数の画素は全て、画素を加算することなく、前記電荷結合素子のうちの少なくとも2つから読み出され、前記電荷結合素子のうちの2つは、各電荷行を保持することが必要であり、C C D 対 C C D 転送ゲートは第2のモードで動作され、前記第2のモードでは、同じ色の連続した2つの色は、一電荷結合素子のみが前記複数の画素からの各電荷行を保持する必要があるように前記電荷結合素子のうちの1つ又は複数内で加算される方法。

10

#### 【請求項8】

画像センサであって、

一方向で一画素おきに同じ色を有する少なくとも2つの色の色フィルタ・パターンでオーバレイされた複数の画素と、

1つおきの画素色フィルタ繰り返しパターンに平行に配向された3つ以上の電荷結合素子であって、それぞれの電荷結合素子が、2n個おきのゲートが第3のゲートで置き換える以外は、交番する第1のゲート及び第2のゲートを有する電荷結合素子と、

20

前記電荷結合素子のうちの少なくとも2つの出力における電荷検出増幅器と、

C C D 対 C C D 転送ゲートの一方側に前記第1のゲートがあり、C C D 対 C C D 転送ゲートの他方側に前記第2のゲート又は前記第3のゲートがある、隣接した電荷結合素子を接続するC C D 対 C C D 転送ゲートとを備え、

C C D 対 C C D 転送ゲートは全て、電気接続されており、第1のゲートは全て、電気接続されており、第2のゲートは全て、電気接続されており、第3のゲートは全て、電気接続されており、nは1を超える整数である画像センサ。

#### 【請求項9】

画像センサを動作させる方法であって、

30

一方向で一画素おきに同じ色を有する少なくとも2つの色の色フィルタ・パターンでオーバレイされた複数の画素を提供する工程と、

1つおきの画素色フィルタ繰り返しパターンに平行に配向された3つ以上の電荷結合素子であって、それぞれの電荷結合素子が、2n個のゲートおきのゲートが第3のゲートで置き換える以外は、交番する第1のゲート及び第2のゲートを有する電荷結合素子を提供する工程と、

前記電荷結合素子のうちの少なくとも2つの出力における電荷検出増幅器を提供する工程と、

C C D 対 C C D 転送ゲートの一方側に前記第1のゲートがあり、C C D 対 C C D 転送ゲートの反対側に前記第2のゲート又は前記第3のゲートがある、隣接した電荷結合素子を接続するC C D 対 C C D 転送ゲートを提供する工程と、

40

C C D 対 C C D 転送ゲート全てを電気接続する工程と、

第1のゲート全てを電気接続する工程と、

第2のゲート全てを電気接続する工程と、

第3のゲート全てを電気接続する工程とを含み、

第1のモードでは、前記複数の画素全てが、画素を加算することなく、前記電荷結合素子のうちの少なくとも2つから読み出され、前記電荷結合素子のうちの2つは、各電荷行を保持することが必要であり、第2のモードでは、同じ色のn個の画素が、前記電荷結合素子のうちの1つ又は複数内で加算され、2/n個の電荷結合素子は、前記複数の画素からの一電荷行を保持することが必要であり、nは1を超える整数である方法。

50

**【請求項 10】**

n が 2 である、請求項 9 記載の方法。

**【請求項 11】**

n が 3 である、請求項 9 記載の方法。

**【請求項 12】**

n が 4 である、請求項 9 記載の方法。

**【請求項 13】**

n が 5 である、請求項 9 記載の方法。

**【請求項 14】**

請求項 10 記載の方法であって、1つおきの第3のゲートが第4のゲートで置き換えられ、第3のモードでは、前記電荷結合素子のうちの1つ又は複数内で4個の画素が加算される方法。 10

**【請求項 15】**

請求項 11 記載の方法であって、1つおきの第3のゲートが第4のゲートで置き換えられ、第3のモードでは、前記電荷結合素子のうちの1つ又は複数内で6個の画素が加算される方法。

**【請求項 16】**

カメラであって、

画像センサを備え、前記画像センサは、

一方向で一画素おきに同じ色を有する少なくとも2つの色の色フィルタ・パターンでオーバレイされた複数の画素と、 20

1つおきの画素色フィルタ繰り返しパターンに平行に配向された3つ以上の電荷結合素子であって、それぞれの電荷結合素子が第1のゲート及び第2のゲートを有する電荷結合素子と、

前記電荷結合素子のうちの少なくとも2つの出力における電荷検出増幅器と、

C C D 対 C C D 転送ゲートの一方側に前記第1のゲートがあり、C C D 対 C C D 転送ゲートの反対側に前記第2のゲートがある、隣接した電荷結合素子を接続するC C D 対 C C D 転送ゲートとを含み、

C C D 対 C C D 転送ゲートは全て、電気接続されており、第1のゲートは全て、電気接続されており、第2のゲートは全て、電気接続されているカメラ。 30

**【請求項 17】**

請求項 16 記載のカメラであって、前記複数の画素から最も遠い電荷結合素子へのC C D 転送ゲートにドレインによって接続された電荷ドレインを更に備え、前記C C D 転送ゲートへのドレインが前記C C D 対 C C D 転送ゲートに電気接続されているカメラ。

**【請求項 18】**

請求項 16 記載のカメラであって、前記色フィルタ・パターンは、2つの緑色画素、1つの赤色画素、及び1つの青色画素を有する2×2画素のベイヤー色フィルタ・パターンであるカメラ。

**【請求項 19】**

カメラであって、

画像センサを備え、前記画像センサは、

一方向で一画素おきに同じ色を有する少なくとも2つの色の色フィルタ・パターンでオーバレイされた複数の画素と、

1つおきの画素色フィルタ繰り返しパターンに平行に配向された3つ以上の電荷結合素子であって、それぞれの電荷結合素子が第1のゲート、第2のゲート、第3のゲート、及び第4のゲートをその順に有する電荷結合素子と、

前記電荷結合素子のうちの少なくとも2つの出力における電荷検出増幅器と、

C C D 対 C C D 転送ゲートの一方側に前記第1のゲート又は前記第3のゲートがあり、C C D 対 C C D 転送ゲートの反対側に前記第2のゲート又は前記第4のゲートがある、隣接した電荷結合素子を接続するC C D 対 C C D 転送ゲートとを備え、 40

50

C C D 対 C C D 転送ゲートは全て、電気接続されており、第1のゲートは全て、電気接続されており、第2のゲートは全て、電気接続されており、第3のゲートは全て、電気接続されており、第4のゲートは全て、電気接続されているカメラ。

#### 【請求項 20】

請求項19記載のカメラであって、前記複数の画素から最も遠い電荷結合素子へのC C D転送ゲートにドレインによって接続された電荷ドレインを更に備え、前記C C D転送ゲートへのドレインが前記C C D対C C D転送ゲートに電気接続されているカメラ。

#### 【請求項 21】

請求項19記載のカメラであって、前記色フィルタ・パターンは、2つの緑色画素、1つの赤色画素、及び1つの青色画素を有する $2 \times 2$ 画素のベイヤー色フィルタ・パターンであるカメラ。10

#### 【請求項 22】

カメラであって、

画像センサを備え、前記画像センサは、一方向で一画素おきに同じ色を有する少なくとも2つの色の色フィルタ・パターンでオーバレイされた複数の画素と、

1つおきの画素色フィルタ繰り返しパターンに平行に配向された3つ以上の電荷結合素子であって、それぞれの電荷結合素子が、 $2^n$ 個おきのゲートが第3のゲートで置き換える以外は、交番する第1のゲート及び第2のゲートを有する電荷結合素子と、

前記電荷結合素子のうちの少なくとも2つの出力における電荷検出増幅器と、

C C D 対 C C D 転送ゲートの一方側に前記第1のゲートがあり、C C D 対 C C D 転送ゲートの反対側に前記第2のゲート又は前記第3のゲートがある、隣接した電荷結合素子を接続するC C D 対 C C D 転送ゲートとを備え、20

C C D 対 C C D 転送ゲートは全て、電気接続されており、第1のゲートは全て、電気接続されており、第2のゲートは全て、電気接続されており、第3のゲートは全て、電気接続されており、nは1を超える整数であるカメラ。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は一般に、画素アレイを読み出す3つ以上の水平電荷結合素子の分野に関し、特に、画素加算によるビデオ・フレーム・レートでの低減された分解能画像、又はフル分解能画像を複数の水平電荷結合素子(C C D)が読み出すことを可能にする水平電荷結合素子の分野に関する。30

##### 【背景技術】

##### 【0002】

米国特許第4513313号、第5164807号、第5841554号、及び米国特許出願公開第2005/0062868号には、m列の電荷をm個のH C C D レジスタに配分する複数出力の水平電荷結合素子(H C C D)が開示されている。前述の出力構造は、ベイヤー色フィルタ・パターンからの電荷を、レジスタ每一色に分離するものでなく、ストライプ状色フィルタ配置を必要とし、これは、好適な画像品質には望ましくなく、更に、増加したフレーム・レートの場合、画素の水平加算が可能でない。40

##### 【0003】

本発明は、ベイヤー色フィルタ・パターンの使用を可能にし、H C C D内の画素の水平加算を可能にする。

##### 【0004】

米国特許第4807037号及び第5189498号には、第1のH C C Dとは異なるチャネル・ドーピング・レベルを第2のH C C Dが有することを必要とするという望ましくない構成を有する複数出力のH C C Dが開示されている。余分なドーピングには、より多くの処理工程及びマスク・レベルが必要である。

##### 【0005】

本発明は、第2のH C C Dにおいて、余分なドーピングを必要としない。50

## 【0006】

米国特許第5216489号及び第6002146号には、2つのHCCD間の転送ゲートを必要とする複数出力HCCDが開示されている。これは、より多くの構成部分を必要とする、より複雑なHCCDクロック・ドライバである。HCCD内の画素の水平加算も開示されていない。

## 【0007】

本発明は2つのクロック・レベルのみを必要とし、前述の2つのレベルは、HCCDクロック全てに使用される。

## 【0008】

米国特許第5995249号は、複数出力のHCCDを例証するが、その構成又はタイミング信号についての情報は何も提供しない。更に、より高速なフレーム・レートの場合、HCCD内の画素の水平加算も開示しない。

10

## 【0009】

米国特許第6781628号には、複数出力のHCCDが開示されているが、より高速なフレーム・レートの場合、HCCD内の画素の水平加算を開示しない。更に、偶数列及び奇数列の場合、HCCDと画素アレイとの間の別個の制御ゲートも必要である。

## 【0010】

本発明では、偶数列及び奇数列は、画素アレイとHCCDとの間の別個の制御ゲートを有することを必要としない。

20

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0011】

本発明は、上記課題の1つ又は複数を解決することに関する。

## 【課題を解決するための手段】

## 【0012】

要約すれば、本発明の一局面によれば、本発明は、一方向で一画素おきに同じ色を有する少なくとも2つの色の色フィルタ・パターンでオーバレイされた複数の画素を含む画像センサと、1つおきの画素色フィルタ繰り返しパターンに平行に配向された3つ以上の電荷結合素子であって、それぞれの電荷結合素子が第1のゲート及び第2のゲートを有する電荷結合素子と、電荷結合素子のうちの少なくとも2つの出力における電荷検出増幅器と、CCD対CCD転送ゲートの一方側に第1のゲートがあり、CCD対CCD転送ゲートの反対側に第2のゲートがある、隣接した電荷結合素子を接続するCCD対CCD転送ゲートとを提供し、CCD対CCD転送ゲートは全て、電気接続されており、第1のゲートは全て、電気接続されており、第2のゲートは全て、電気接続されている。

30

## 【図面の簡単な説明】

## 【0013】

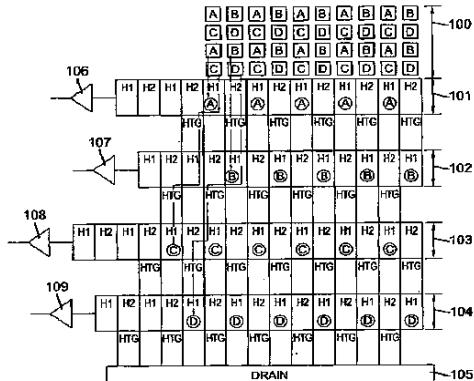

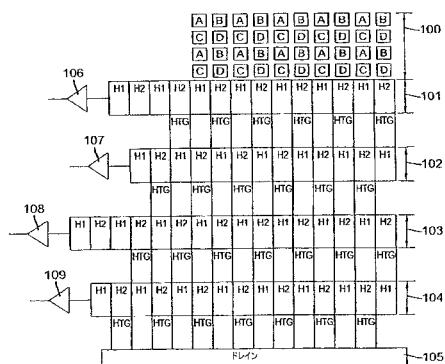

【図1a】疑似2相CCDを示す図である。

【図1b】真の2相CCDを示す図である。

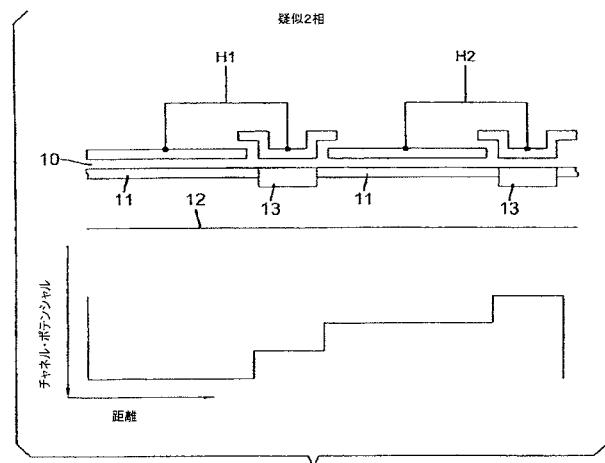

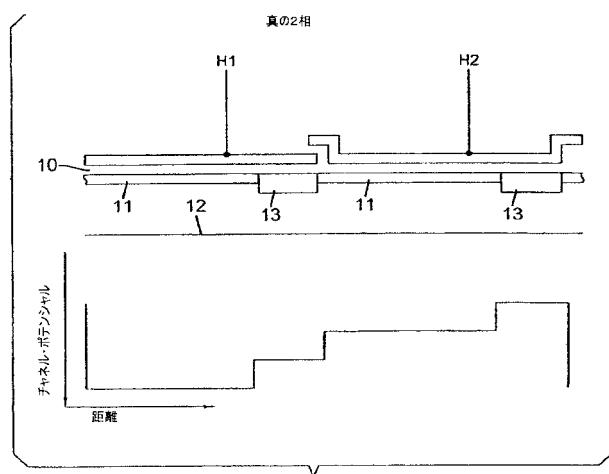

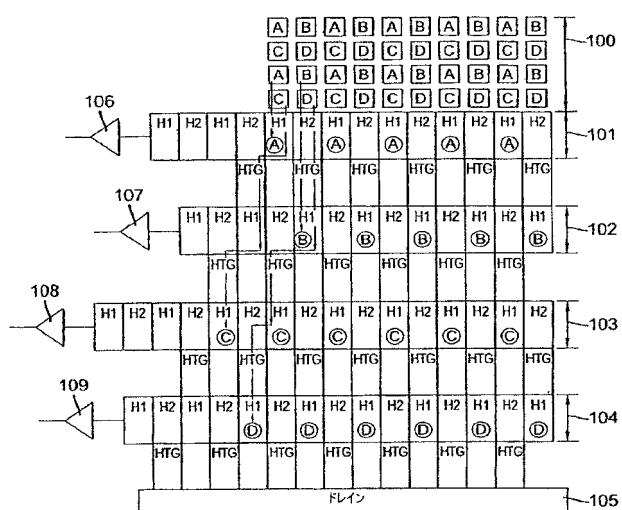

【図2】4つのCCDを有する本発明の第1の実施例の一実現形態を示すHCCDの図である。

40

【図3】画素アレイからの2行の電荷を第1の実施例のHCCDに転送するための電荷のパスを示す図である。

【図4】第1の実施例のHCCDにおける電荷の読み出しを示す図である。

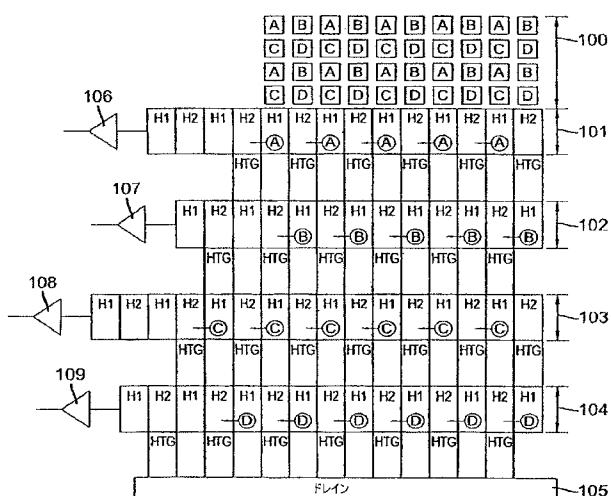

【図5】図4における電荷の転送のクロック・ドライバ・タイミングを示す図である。

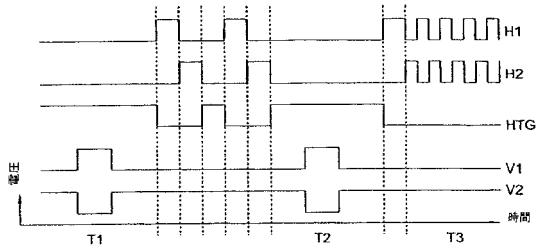

【図6】6つのCCDを有する本発明の第2の実施例の一実現形態を示すHCCDの図である。

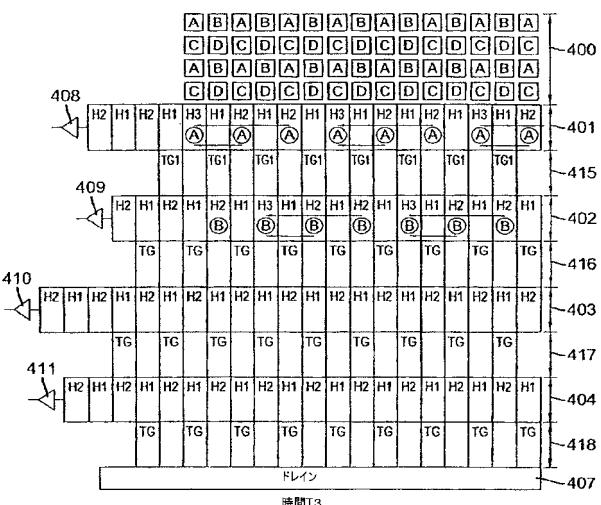

【図7】時間ステップT1における電荷パケットの場所を示す図である。

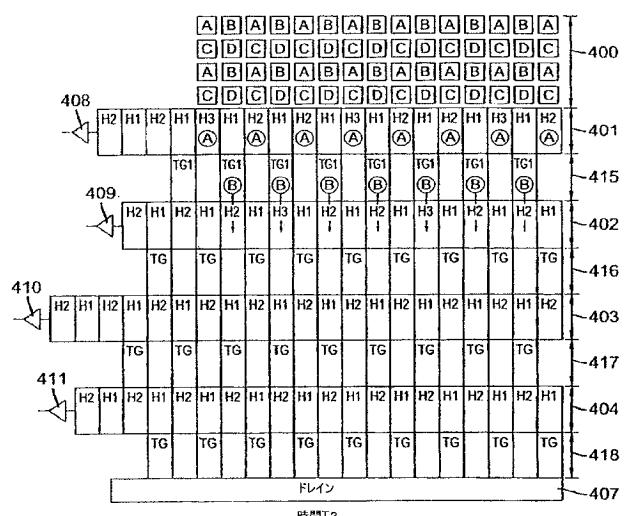

【図8】時間ステップT2における電荷パケットの場所を示す図である。

【図9】時間ステップT3における電荷パケットの場所を示す図である。

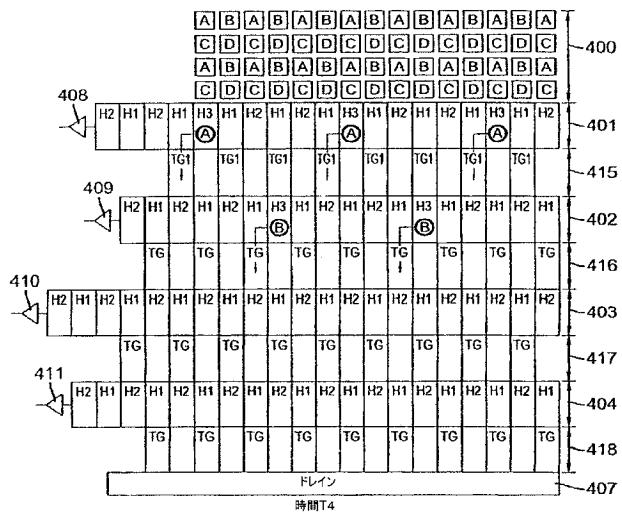

【図10】時間ステップT4における電荷パケットの場所を示す図である。

50

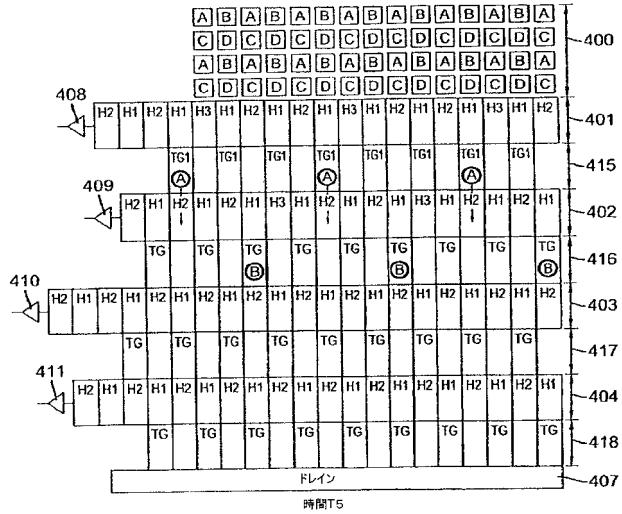

【図11】時間ステップT5における電荷パケットの場所を示す図である。

【図12】時間ステップT6における電荷パケットの場所を示す図である。

【図13】時間ステップT7における電荷パケットの場所を示す図である。

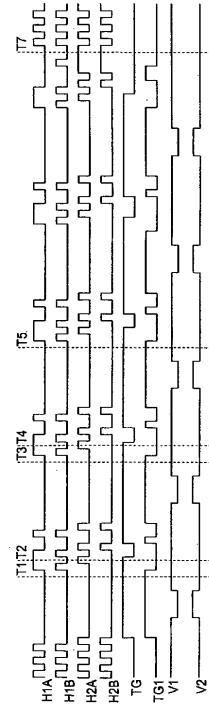

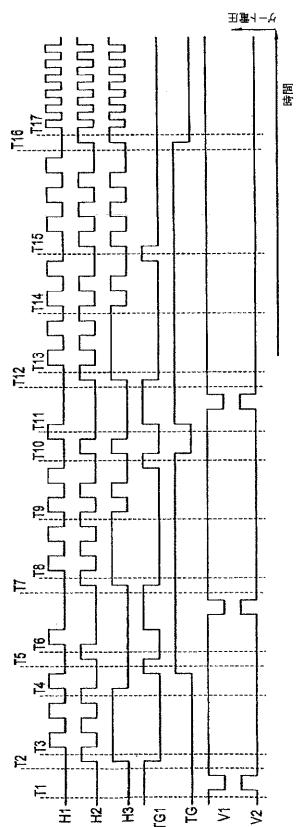

【図14】図7乃至図12における電荷の転送のクロック・ドライバ・タイミング図である。

【図15】図7乃至図13における電荷の転送のクロック・ドライバ・タイミング図である。

【図16】フル分解能読み出しの場合の第2の実施例の3つのCCDを備えたHCCDを示す図である。 10

【図17】2画素加算読み出しの第2の実施例の3つのCCDを備えたHCCDを示す図である。

【図18】本発明の第3の実施例の時間T1における電荷の場所を示す図である。

【図19】第3の実施例の時間T2における電荷の場所を示す図である。

【図20】第3の実施例の時間T3における電荷の場所を示す図である。

【図21】第3の実施例の時間T4における電荷の場所を示す図である。

【図22】第3の実施例の時間T5における電荷の場所を示す図である。

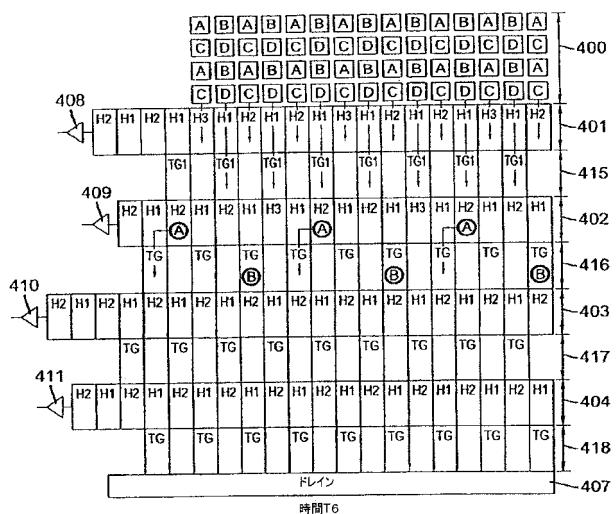

【図23】第3の実施例の時間T6における電荷の場所を示す図である。

【図24】第3の実施例の時間T7における電荷の場所を示す図である。

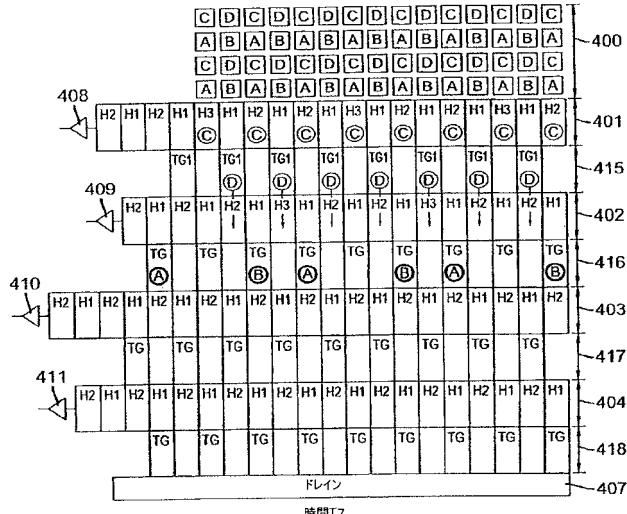

【図25】第3の実施例の時間T8における電荷の場所を示す図である。

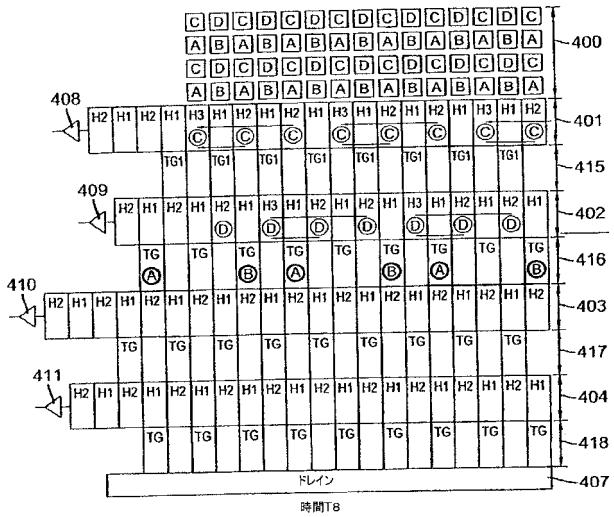

【図26】第3の実施例の時間T9における電荷の場所を示す図である。

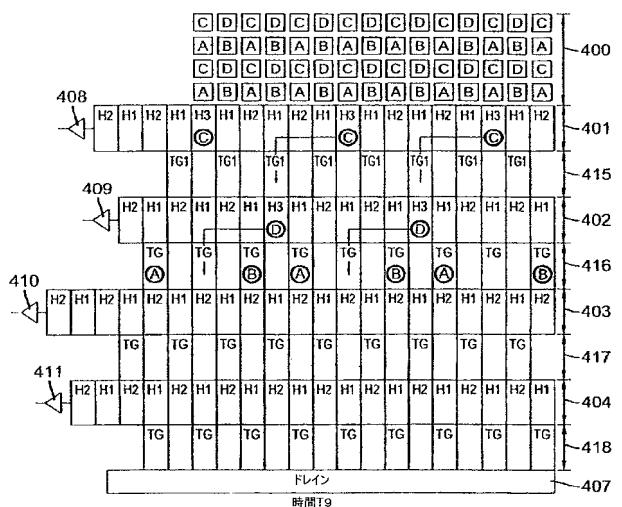

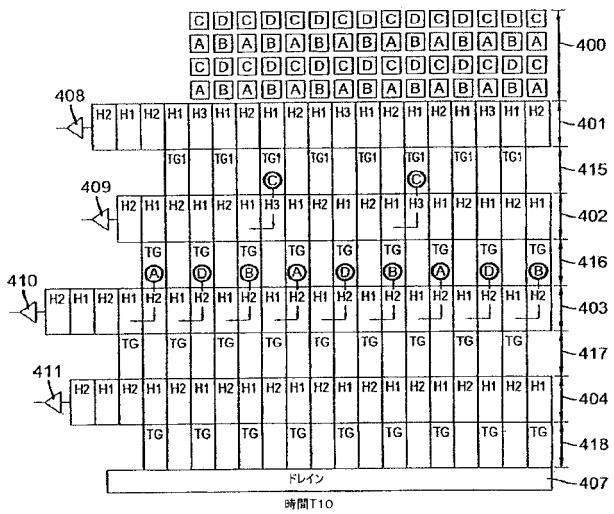

【図27】第3の実施例の時間T10における電荷の場所を示す図である。

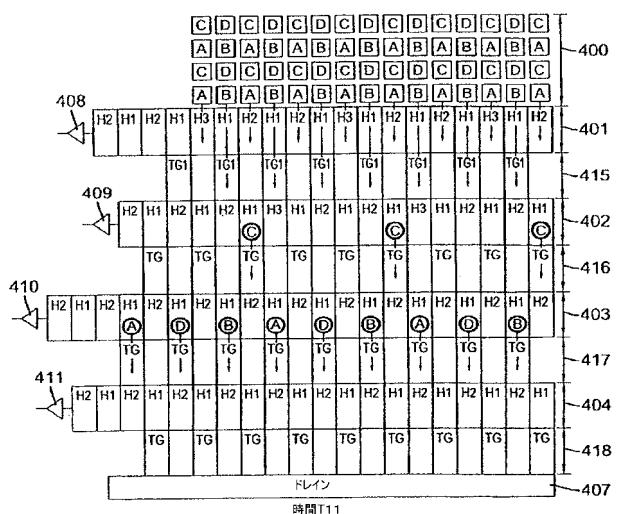

【図28】第3の実施例の時間T11における電荷の場所を示す図である。

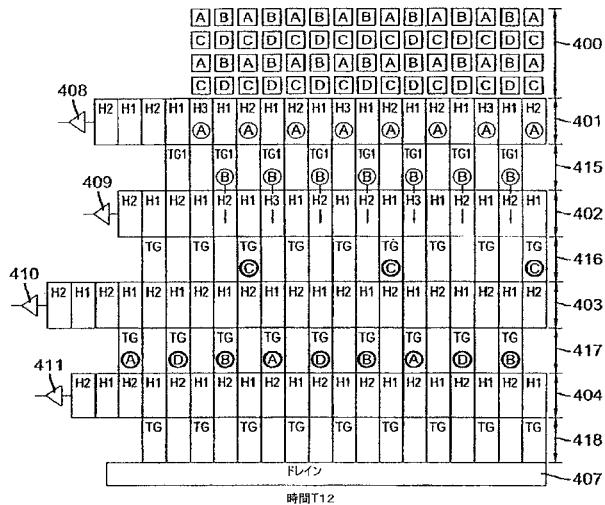

【図29】第3の実施例の時間T12における電荷の場所を示す図である。

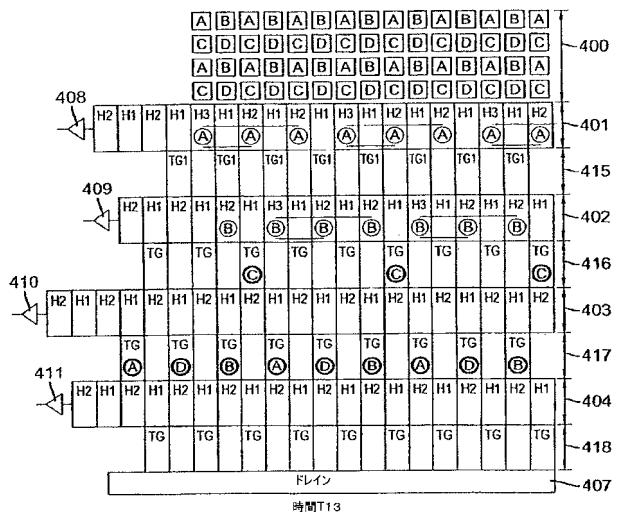

【図30】第3の実施例の時間T13における電荷の場所を示す図である。

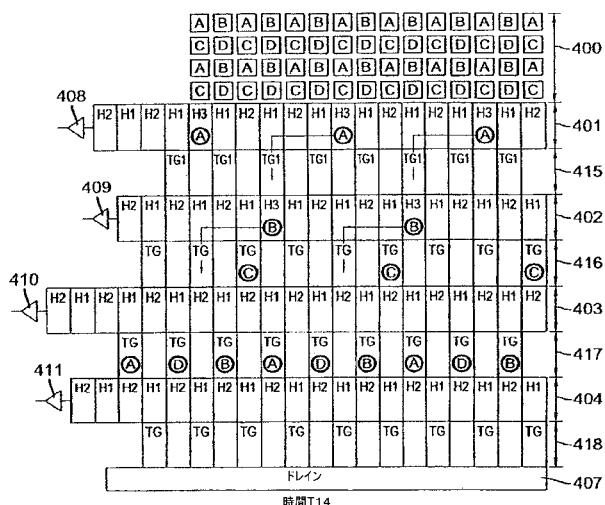

【図31】第3の実施例の時間T14における電荷の場所を示す図である。

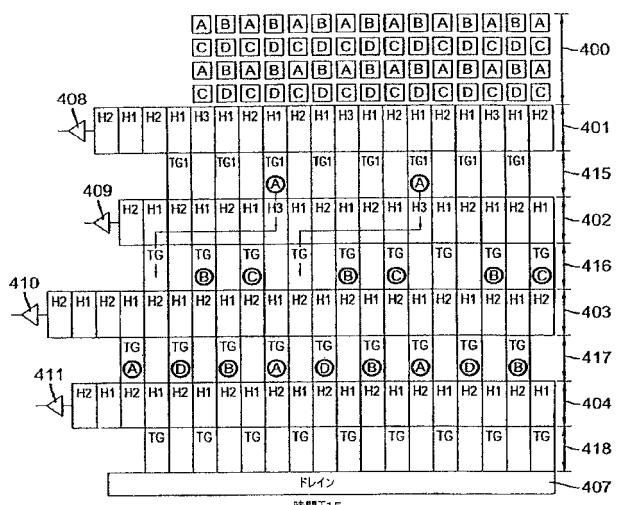

【図32】第3の実施例の時間T15における電荷の場所を示す図である。

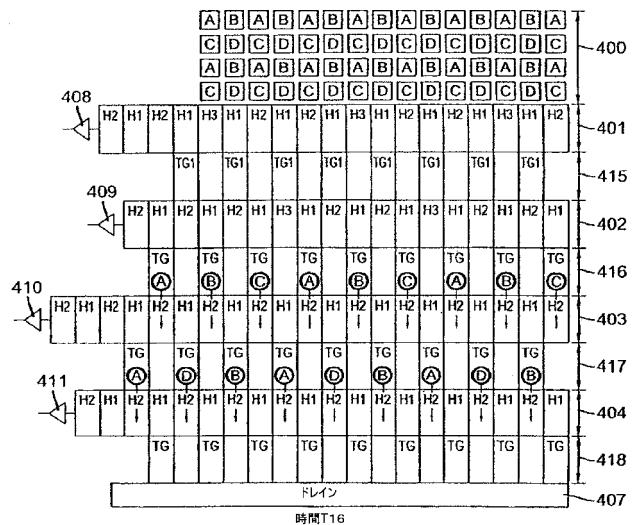

【図33】第3の実施例の時間T16における電荷の場所を示す図である。

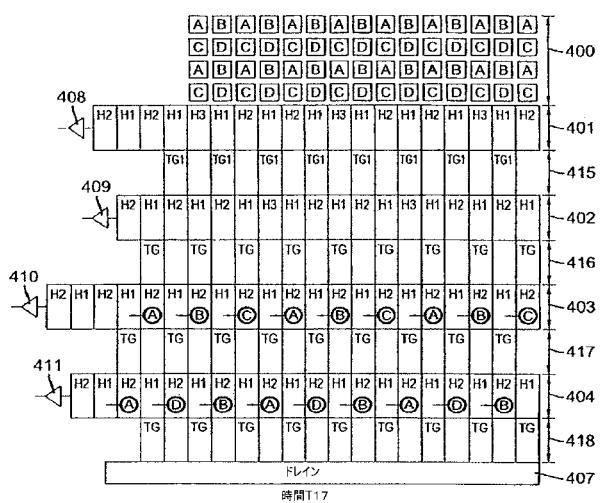

【図34】第3の実施例の時間T17における電荷の場所を示す図である。

【図35】図18乃至図34における電荷の転送のクロック・ドライバ・タイミング図である。 20

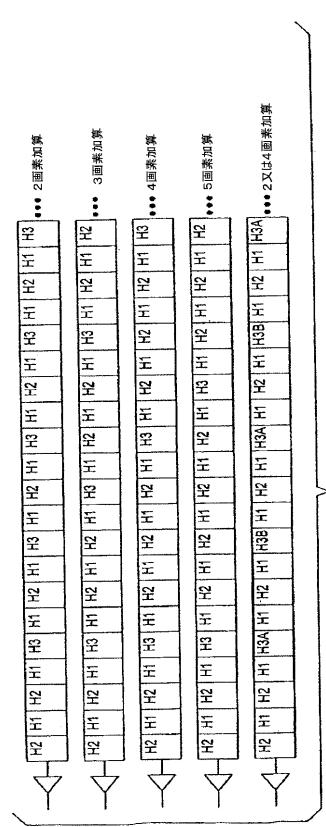

【図36】2画素加算、3画素加算、4画素加算、5画素加算、及び2又は4画素加算の場合の第3の実施例のCCD毎のゲート順序付けを示す図である。

【図37】本発明の画像センサを有するカメラを示す図である。

【発明を実施するための形態】

【0014】

本発明の前述及びその他の局面、目的、構成及び利点は、好ましい実施例、及び特許請求の範囲の以下の詳細な説明をレビューし、添付図面を参照することで、より明確に理解され、認識されよう。

【0015】

本発明は、複数の水平電荷結合素子を使用し、4つ以下の水平クロック・ドライバを使用する画素加算による低減された分解能の、より高いフレーム・レートの画像、又はフル分解能画像を読み出すという以下の利点を有する。 40

【実施例】

【0016】

本発明は好ましい実施例を参照しながら説明している。しかし、当該技術分野における当業者は、本発明の範囲から逸脱しない限り、変形及び修正を行うことが可能である。

【0017】

CCDシフト・レジスタ・ゲートは、真の2相型又は疑似2相型として規定される。図1a及び図1bは、2相CCDの2つのタイプ間の差を示す。各シフト・レジスタ・ゲートは、絶縁体10上にH1ゲート及びH2ゲートを有する。第1の導電タイプ(通常、n

50

型)のCCD埋め込みチャネル11は、第2の導電タイプ(通常、p型)のウェル又は基板12上にある。電荷の転送の方向を制御するためのチャネル・ポテンシャル障壁のインプラント13も存在している。本発明のこの詳細な説明を通して、ゲートとして識別された部分は、眞の2相タイプ、又は疑似2相タイプであり得る。

#### 【0018】

本発明の第1の実施例を図2に示す。これは、色A、B、C及びDの複数の画素100を備える画像センサである。色は通常、A及びDが緑色であり、Bが青色であり、Cが赤色であるベイヤー色フィルタ・パターンであるが、これに限定されるものでない。水平電荷結合素子(HCCD)は3つ以上存在している(101、102、103及び104)。本発明は、4つのHCCDのみに限定されず、5つ以上のものが、図2に示す例の拡張形であり、これは、当業者には明らかであろう。各HCCDは、同じ2つのクロック信号H1及びH2によって駆動される。ゲートH1及びH2は交番し、画素アレイの列毎のゲートは1つである。ゲートH1又はH2はそれぞれ、眞の2相CCDゲート又は疑似2相CCDゲートであり得る。H1ゲート及びH2ゲートが補完的にクロッキングされると、HCCD全てにおける電荷が、各HCCDの端部における電荷検出出力増幅器106、107、108及び109に向けて移動する。各HCCD間には、隣接するHCCD間で電荷が転送されることを可能にする転送ゲートHTGがある。HTGそれぞれも、眞の2相CCDゲート又は疑似2相CCDゲートである。HTGは、H2ゲートからの電荷パケット全体をHTGゲート下に保持することができるよう構成される。別の同等の設計は、H1ゲートからの電荷を受け取るためにHTGゲートを配置するというものである。

10

20

30

#### 【0019】

最後のHCCD104の下には、転送ゲートHTGにより、最後のHCCD104に結合された高速電荷ダンプ・ドレイン105がある。これは、画素アレイ100からの電荷行全体が、HCCDからクロックアウトされる代わりに、ドレインにすばやく廃棄することを可能にする。

#### 【0020】

このHCCD構造の利点は、2つの高周波クロッキング信号H1及びH2、並びに1つの低周波クロッキング信号HTGのみを必要とするという点である。図3は、4つのHCCD101、102、103及び104のうちのそれぞれに画素アレイ100から電荷パケットがどのようにして流れるかを示す。画素アレイ100からの2行の電荷が、4つのHCCD間で配分される。第1の行から、色DはHCCD104に行き、色CはHCCD103に行く。次の行から、色BはHCCD102に行き、色AはHCCD101に行く。各HCCDは、一色のみを含む。出力増幅器の電気回路の利得を色毎に違ったふうに調節することが可能であるので、HCCDそれぞれが一色を含むことが効果的である。更に、H1及びH2のクロック・サイクル毎に、 $2 \times 2$ の一画素カーネル全体が、出力増幅器106、107、108及び109で同時にサンプリングされる。

40

#### 【0021】

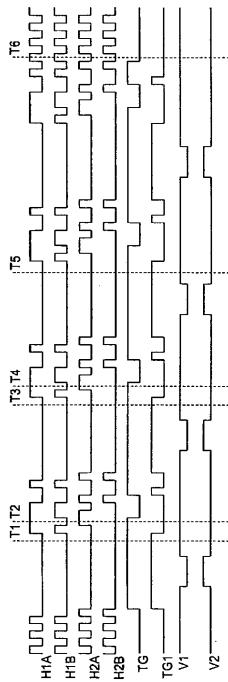

2行の電荷がそれらそれぞれのHCCDに転送されると、H1クロック及びH2クロックは次いで、補完的に高周波でクロッキングして、図4に示すように、出力増幅器106、107、108及び109に向けて電荷を移動させる。電荷移動のタイミング図を図5に示す。V1クロック線及びV2クロック線は、2相画素アレイ垂直CCDタイミングの場合である。本発明は、2相VCCDに限定されない。3つ以上の相のVCCDを使用することができる。インタレース読み出し又は電荷加算を使用するVCCDも使用することができる。

#### 【0022】

図5における時間T1では、第1の行の電荷が画素アレイ100からHCCD101及び102に転送される。T1とT2との間の時間は図3に対応する。図3では、第1の電荷行が、HCCD101及び102からHCCD103及び104に移動される。時間T2では、第2の電荷行が、画素アレイ100からHCCD101及び102に転送される。ここで、4つのHCCDは、電荷で満ちた状態であり、時間T3では、HCCDは、図

50

4に対応する出力増幅器に向けて電荷をクロッキングし始める。

【0023】

本発明の第2の実施例は、より速い読み出しモードでHCCDを動作させることに関する。ディジタル・カメラはこの場合、高分解能のシングル・ショット写真、及び、より低い分解能の毎秒30フレームのビデオを撮影することが必要である。この第2の実施例は、HCCD内の2つの画素を水平方向に加算して各HCCDの読み出しレートを倍にするよう第1の実施例を修正することができるやり方を示す。

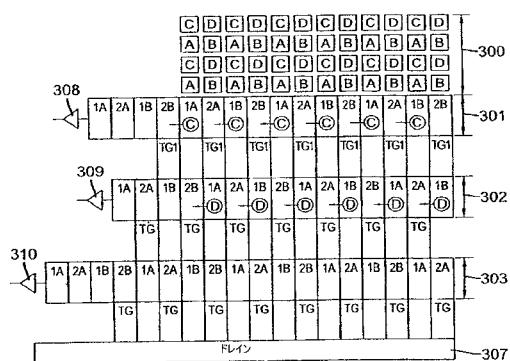

【0024】

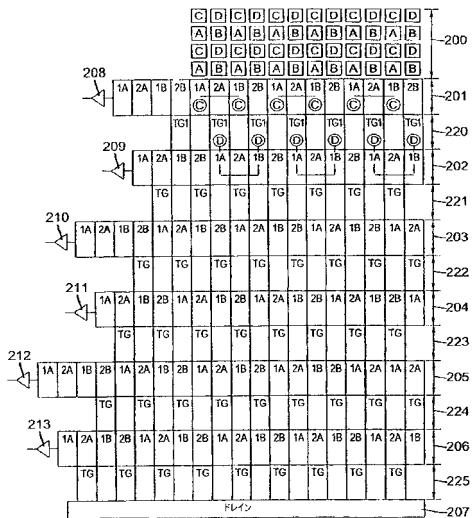

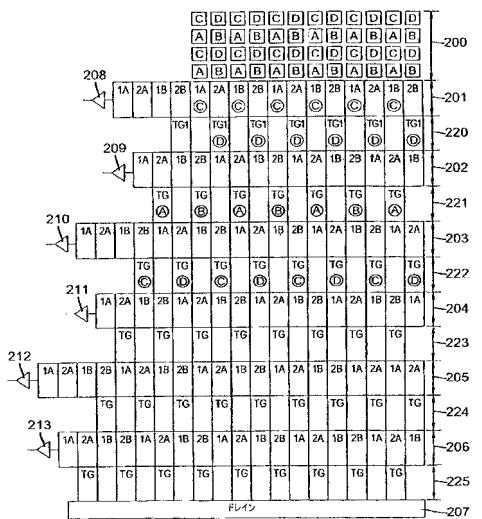

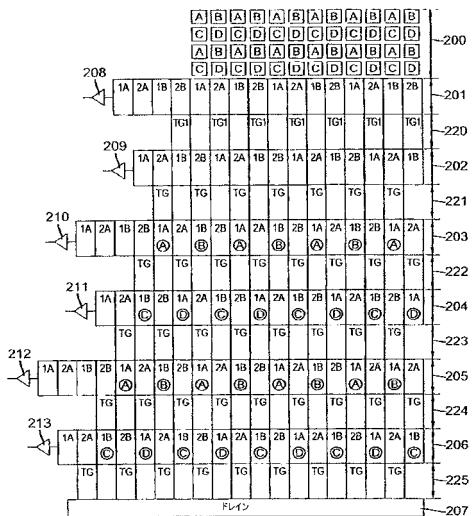

図6は、本発明の第2の実施例を示す。各HCCD201、202、203、204、

205及び206は、各HCCDに沿って、電荷検出出力増幅器208、209、210

、211、212及び213に向けて電荷を移動させるための4つの制御ゲート1A、2

A、1B及び2Bを有する。示されているHCCDは6つであり、転送ゲートTG及びT

G1が、HCCD間の電荷の転送を制御する。TG1転送ゲートは、領域220内のHC

CD201及び202の間にのみある。残りのTG転送ゲートは全て、電気接続され、領域

221、222、223及び224内にある。高速電荷ダンプ・ドレイン207に電荷

を転送するために、領域225内のTGに電気接続されたゲートも存在している。本発明

の第2の実施例は、図6のゲート1A及び1Bが互いに接続され、ゲート2A及び2B、

並びにゲートTG1及びTGが接続されている場合、図2の第1の実施例の6出力バージ

ョンに機能的に同等である。よって、フル分解能のシングル・ショット写真モードでは、

HCCDはなお、2つの高周波クロック信号及び1つの低周波転送ゲート・クロック信号

を必要とするに過ぎない。

10

20

20

【0025】

次に、第2の実施例の半分解能倍速ビデオ読み出しモードを説明する。処理は図6から始まる。図6では、第1の行は画素アレイ200から最上位の2つのHCCDに転送される。色CはHCCD201の1Aゲート及び1Bゲートに入り、色Dは、HCCD201

の2A及び2Bのゲートを通って、TG1ゲートに進む。

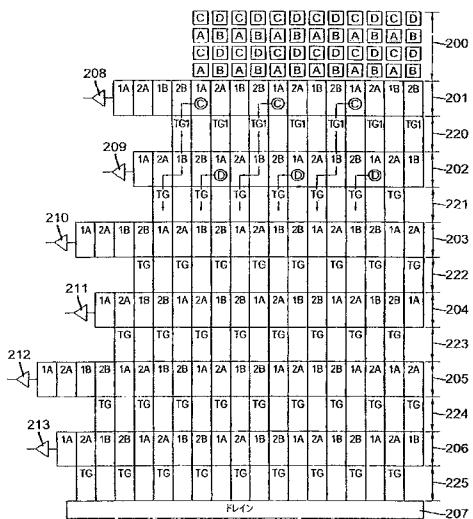

【0026】

次の工程は図7に示す。HCCD201内の1Bゲート下の色電荷パケットCは2ゲー

ト、先に進む一方、1Aゲート下の色電荷パケットCは静止状態のままである。これにより、2つの色電荷パケットCが加算される。色Dの電荷パケットがTG1ゲートからHC

CD202に転送された後、同様の処理がHCCD202において行われる。図6は、電

荷加算の結果を示す。電荷パケットC及びDの周りの2重の円は、2つの電荷パケットの

和であることを示している。

30

40

【0027】

次に、色Dの電荷パケットが、領域221内のTGゲート下に転送され、色Cの電荷パ

ケットがTG1ゲート及びHCCD202を介して転送されている間、そこに保持される

。色Dの電荷パケットは加算されているので、領域221には、空きのTGゲートが存在

している。前述の空きのTGゲートは、図9に示すように、加算された色Cの電荷パケ

ットで満たされる。同時に、画素アレイ200からの次の画素行がHCCD201及びTG

1220に転送される。

【0028】

次に、2つの色A及びBの電荷パケットがHCCD201及び202において加算され

る一方、既に加算された色C及びDの電荷パケットは、図10に示すように、次のTG領域

222に向けて転送される。

【0029】

図11では、加算された色A、B、C及びDの電荷パケットがTGゲート221及び2

22下に保持されている間、別の行の色C及びDが画素アレイ200からHCCD201

及びTG1 220に転送される。

【0030】

同じ色の2つの電荷パケットを加算する前述の処理は、最下位の4つのHCCD203

50

、204、205及び206に電荷が満たされるまで繰り返される。この場合、HCCDは、画素アレイ200からの4電荷行全体を含む。HCCD201及び202は空きである。HCCDが読み出された場合、増幅器208及び209は、電力を節減するようオフにすることが可能である。この加算処理では、フル分解能読み出しモードのような3行及び6出力の代わりに、4行及び4出力が読み出される。

#### 【0031】

図14は、4電荷行をHCCDに転送するためのタイミング・シーケンスを示す。図7は時間T1において電荷パケットがある場所を示し、図8は時間T2において電荷パケットがある場所を示し、図9は時間T3において電荷パケットがある場所を示し、図10は時間T4において電荷パケットがある場所を示し、図11は時間T5において電荷パケットがある場所を示し、図12は時間T6において電荷パケットがある場所を示す。図14のV1クロック信号及びV2クロック信号は、新たな行の電荷パケットが画素アレイ200から転送される時間を示すためにのみ示す。V1及びV2は、使用することができる多くのタイプのVCCDクロッキングの一例としてのみ、2相CCDクロッキングとして示す。3相VCCDクロッキング、4相VCCDクロッキング、又は5相以上のVCCDクロッキングを使用することができる。VCCDは又、マルチフィールドのインタレース読み出しであり得、又は、垂直画素加算機能を有し得る。

10

#### 【0032】

本発明の第2の実施例は、同時読み出しの4行のみに限定されない。図13は、第5の電荷行をHCCD202に入れるための画素加算の更に1つの工程を示す。この場合、HCCD201のみが空きである。フル分解能で読み出すために3電荷行を要する時間と同じ時間で5電荷行をHCCDから1/2分解能で読み出すことが可能である。図15は、1/2分解能で5電荷行を読み出すタイミング図を示す。時間ステップT7は図13に対応する。

20

#### 【0033】

異なる数のHCCDレジスタを備えた、第2の実施例の多くの同等の変形が存在している。例えば、一変形は、図16に示す3つのHCCDシフト・レジスタを有するというものである。高速電荷ダンプ・ドレイン307は、サブウインドウ・モードの場合、又はVCCDの余分な電荷を流す場合に、電荷行全体をすばやく空けるために使用される。フル電荷読み出しの場合、第1の2つのHCCD301及び302を使用して、画素アレイ300から、一度に一行、読み出す。増幅器308及び309のみが、フル分解能読み出しのために電力供給される。半分解能倍速読み出しモードでは、2重加算された電荷パケットが、図17に示すようにHCCD302及び303から読み出される。増幅器309及び310のみが、半分解能倍速モードで電力供給される。HCCDレジスタ302及び303は、HCCD毎の電荷読み出しの量を倍にするために2電荷行を含む。

30

#### 【0034】

図16で、レジスタ301及び302における電荷パケットがレジスタ302及び303にシフトダウンされ、次いで、増幅器309及び310から読み出される場合、画像センサから増幅器308全体を省略することができる。3つのHCCDレジスタを使用した前述の例は、本発明のHCCD構造が、偶数のHCCDレジスタにのみ限定されないことを示す。

40

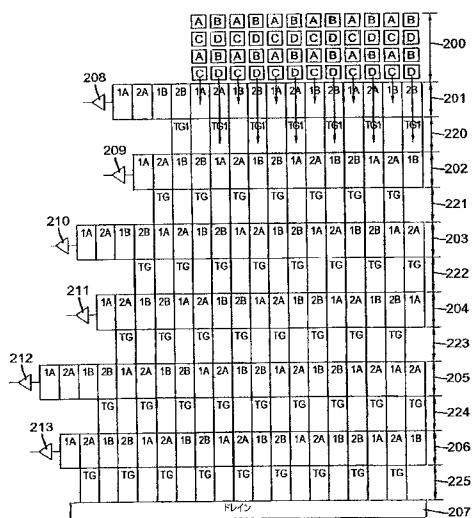

#### 【0035】

本発明の第3の実施例は、同じ色の3つの水平画素をHCCD内で加算することができるやり方を示す。これにより、ビデオ・フレーム・レートでの1/3分解能画像読み出しが行われる。

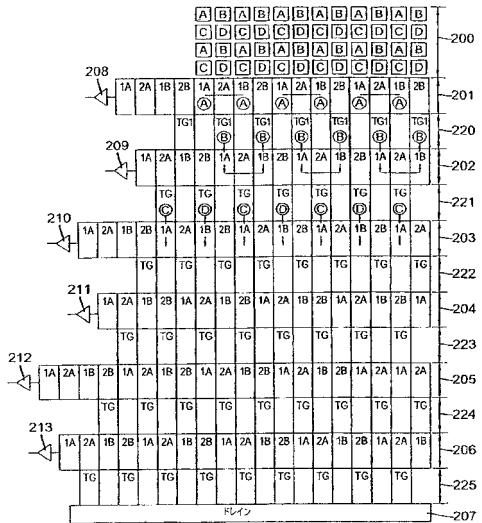

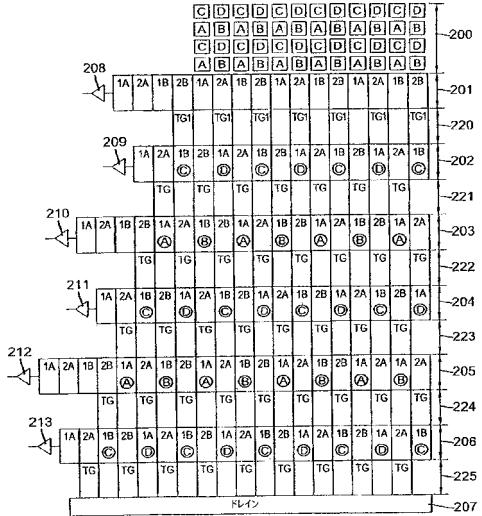

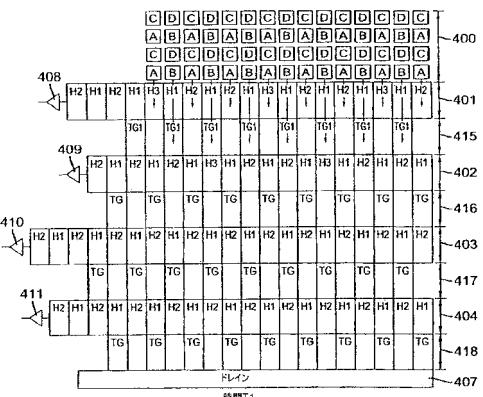

#### 【0036】

図18は第3の実施例を示す。これは、色A、B、C及びDの複数の画素400を備える画像センサである。色は通常、A及びDが緑色であり、Bが青色であり、Cが赤色であるベイヤー色フィルタ・パターンであるが、これに限定されるものでない。A、B、C及びDが全て同色であるか、又は無色（パンクロ）である単一の色装置であってもよい。電

50

荷検出出力増幅器 408、409、410 及び 411 を備えた 4 つの HCCD シフト・レジスタ 401、402、403 及び 404 が存在している。第 1 の 2 つの HCCD シフト・レジスタ 401 及び 402 は 3 つのゲート H1、H2 及び H3 を有する。H1 ゲート及び H2 ゲートは交番し、6 つおきのゲートが H3 ゲートになる。H1 とラベリングされたゲートは全て、互いに接続される。H2 とラベリングされたゲートは全て、互いに接続される。H3 とラベリングされたゲートは全て、互いに接続される。この例では、他の 2 つの HCCD シフト・レジスタ 403 及び 404 は、H1 ゲート及び H2 ゲートのみを有する。同様な変形には、HCCD シフト・レジスタ 403 及び 404 の 6 つおきのゲートが HCCD 401 及び 402 のような H3 ゲートである場合がある。

## 【0037】

10

HCCD 401 及び HCCD 402 間には、HCCD 401 から HCCD 402 に電荷を転送するために領域 415 内に転送ゲート TG1 がある。TG1 ゲートは、H1 ゲート、H2 ゲート、及び H3 ゲートと同じ量の電荷を保持することができる。領域 416、417 及び 418 内の TG ゲートは、残りの HCCD シフト・レジスタと、高速電荷ダンプ・ドレイン 407 との間の電荷の転送を制御する。

## 【0038】

20

次に、電荷加算処理を説明する。図 18 乃至 図 34 の図それぞれは、図 35 上の時間ラベルに対応する T1 乃至 T17 のタイムスタンプを有する。図 18 の時間 T1 では、第 1 の行の色 A 及び色 B が HCCD 401 及び 転送ゲート TG1 領域 415 に転送される。図 19 では、色 B の電荷が TG1 領域 415 から HCCD 402 に転送される一方、色 A の電荷は HCCD 401 に留まる。次に、図 20 では、H1 ゲート及び H2 ゲートはクロッキングされる一方、H3 ゲートは高電荷保持状態に維持される。これは、2 つの電荷パケットに、H3 ゲート下で保持された電荷パケットに追随させ、上記電荷パケットと加算させるという効果を有する。結果は図 21 に示す。3 つの電荷パケットの和を表すための 3 重同心円はこの場合、各電荷パケットの場所を示す。次いで、加算された電荷パケットが、図 22 に示すように、TG 転送ゲート及び TG1 転送ゲートに転送される。次に、TG1 転送ゲート下の電荷のみが HCCD 402 に転送される一方、TG 転送ゲート内の電荷は移動しない。これは、色 A の電荷パケットが、図 23 における色 B の電荷パケットに追随することを可能にする。次いで、図 24 では、色 C 及び色 D を含む第 2 の電荷行が HCCD 401 及び TG1 領域 415 に転送される一方、先行して加算された電荷行は、転送ゲート TG 領域 416 下に保持される。H3 ゲート下に一電荷パケットを保持することにより、次の 2 つの電荷パケットが第 1 の電荷パケットに加算されることを可能にすることにより、第 2 の電荷行が加算される。図 25 では、H1 ゲート及び H2 ゲートのクロックは、H3 ゲート下で電荷を静止状態に維持する一方で、順方向に電力供給される。図 26 では、加算された色 D の電荷パケットが、空きの TG 領域 416 に転送され、色 C の電荷パケットは TG1 領域 415 に転送される。図 27 及び図 28 では、電荷パケットは、TG 領域 416 及び 417 の次の行に転送される。加算された電荷パケットの次のフル・セットが TG 領域 416 に蓄積されている間、TG 領域 417 における加算された電荷パケットのフル・セットは、そこで待つ。図 29 では、第 3 の電荷の色 A 及び色 B の行が、HCCD 401 及び TG1 領域 415 に転送されている。H1 ゲート及び H2 ゲートをクロッキングして、同じ色の 3 つの電荷パケットの和を累積している間、H3 ゲート下に一電荷パケットを保持することにより、図 30 で加算される。図 31 では、加算された色 B の電荷パケットが TG 領域 416 に転送され、加算された色 A の電荷パケットが TG1 領域 415 に転送される。図 32 では、加算された色 A の電荷パケットを HCCD 402 を介して TG 領域 416 まで転送して、加算電荷パケットの完全な群を構成する。図 33 では、加算電荷パケットは全て、HCCD 403 及び HCCD 404 に転送される。

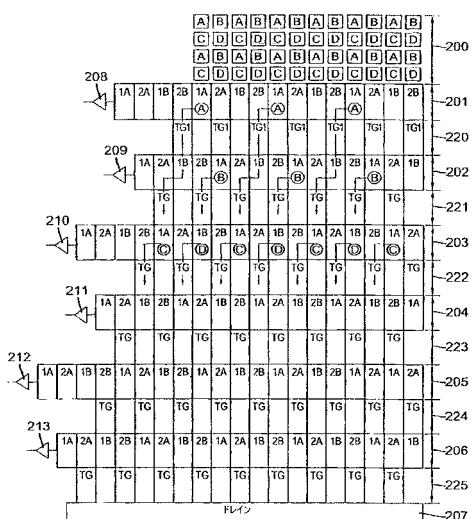

30

## 【0039】

40

最後に、図 34 では、HCCD 403 及び HCCD 404 は、2 つの HCCD シフト・レジスタにのみ、3 行の加算された電荷を含む。前述の電荷加算ビデオ・モード中に、増幅器 408 及び 409 をオフにして電力を節減する。HCCD における前述の 3 画素加算

50

処理が、垂直 C C D シフト・レジスタ内の 3 画素行の加算と組み合わせると、ちょうど 1 / 9 の分解能の高品質ビデオ画像が得られる。

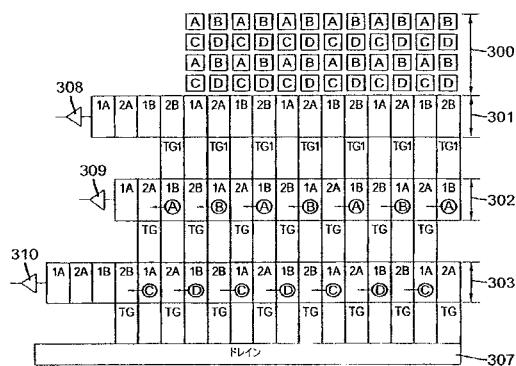

#### 【 0 0 4 0 】

これまで、第 3 の実施例について、3 つの画素を合計する場合について説明している。これは、2 つの画素から、何れの任意の数の画素加算にも容易に拡張することが可能である。例えば、n 個の画素を加算することが望ましいとする。H C C D シフト・レジスタは、交番する H 1 ゲート及び H 2 ゲートを有し、2 n 個のゲート毎のゲートが H 3 ゲートで置き換えられる。2 つの画素を加算することが望ましい場合、4 つのゲート毎のゲートが H 3 ゲートになる。図 18 に示す H C C D では、3 つの画素を加算するよう設定され、よって、 $2 \times 3$  個、すなわち 6 個のゲート毎のゲートが H 3 ゲートになる。5 つの画素を加算するためには、10 個のゲート毎のゲートが H 3 ゲートになる。画素加算の組合せも可能である。2 画素又は 4 画素を加算することが可能な H C C D レジスタの組を構成するためには、4 つのゲート及び 8 つのゲート毎に、別個に制御可能な H 3 ゲートが存在することになる。

10

#### 【 0 0 4 1 】

第 1 の H C C D 4 0 1 における H 1 ゲート、H 2 ゲート及び H 3 ゲートの順序付けは、2 画素加算、3 画素加算、4 画素加算、5 画素加算、又は 2 若しくは 4 画素加算について図 36 に示す。

#### 【 0 0 4 2 】

図 37 は、本発明の実施例のうちの 1 つを使用する画像センサ 6 0 0 を使用したカメラ 6 1 0 を示す。前述のカメラにより、1 つの出力のみを備えた画像センサと比較して増加させた写真撮影レートについて表した複数出力 H C C D シフト・レジスタを使用したフル分解能写真が撮影される。更に、動画像の記録の場合、少なくとも 30 フレーム / 秒のフレーム・レートで、より低い分解能にモードを変えることもできる。より低い分解能モードは、画像プレビュー、自動露出、及び自動フォーカスにも使用することが可能である。本発明は、フル分解能及び 30 フレーム / 秒での数百万個の画素（5 百万個の画素をゆうに超える）を備えた画像センサを読み出すのに十分な H C C D シフト・レジスタを供給する方法を提供する。

20

#### 【 0 0 4 3 】

本発明は、ベイヤー色フィルタ・パターンなどの  $2 \times 2$  色画素パターンの場合において説明している。これは、 $2 \times 2$  色パターンのみに限定されるものでない。本発明は、各側部上に 3 つ以上の画素の単位セルを備えた色パターンにも提供することができる。

30

（構成部分のリスト）

1 0 絶縁体

1 1 C C D 埋め込みチャネル

1 2 基板

1 3 チャネル・ポテンシャル障壁インプラント

1 0 0 複数の画素又は画素アレイ

1 0 1 水平電荷結合素子（H C C D）/シフト・レジスタ

40

1 0 2 水平電荷結合素子（H C C D）/シフト・レジスタ

1 0 3 水平電荷結合素子（H C C D）/シフト・レジスタ

1 0 4 水平電荷結合素子（H C C D）/シフト・レジスタ

1 0 5 高速電荷ダンプ・ドレイン

1 0 6 電荷検出出力増幅器

1 0 7 電荷検出出力増幅器

1 0 8 電荷検出出力増幅器

1 0 9 電荷検出出力増幅器

2 0 0 画素アレイ

2 0 1 水平電荷結合素子（H C C D）/シフト・レジスタ

50

2 0 2 水平電荷結合素子（H C C D）/シフト・レジスタ

|       |                                |    |

|-------|--------------------------------|----|

| 2 0 3 | 水平電荷結合素子( H C C D ) / シフト・レジスタ |    |

| 2 0 4 | 水平電荷結合素子( H C C D ) / シフト・レジスタ |    |

| 2 0 5 | 水平電荷結合素子( H C C D ) / シフト・レジスタ |    |

| 2 0 6 | 水平電荷結合素子( H C C D ) / シフト・レジスタ |    |

| 2 0 7 | 高速電荷ダンプ・ドレイン                   |    |

| 2 0 8 | 電荷検出出力増幅器                      |    |

| 2 0 9 | 電荷検出出力増幅器                      |    |

| 2 1 0 | 電荷検出出力増幅器                      |    |

| 2 1 1 | 電荷検出出力増幅器                      |    |

| 2 1 2 | 電荷検出出力増幅器                      | 10 |

| 2 1 3 | 電荷検出出力増幅器                      |    |

| 2 2 0 | 領域                             |    |

| 2 2 1 | 領域                             |    |

| 2 2 2 | 領域                             |    |

| 2 2 3 | 領域                             |    |

| 2 2 4 | 領域                             |    |

| 2 2 5 | 領域                             |    |

| 3 0 0 | 画素アレイ                          |    |

| 3 0 1 | 水平電荷結合素子( H C C D ) / シフト・レジスタ |    |

| 3 0 2 | 水平電荷結合素子( H C C D ) / シフト・レジスタ | 20 |

| 3 0 3 | 水平電荷結合素子( H C C D ) / シフト・レジスタ |    |

| 3 0 7 | 高速電荷ダンプ・ドレイン                   |    |

| 3 0 8 | 増幅器                            |    |

| 3 0 9 | 増幅器                            |    |

| 3 1 0 | 増幅器                            |    |

| 4 0 0 | 複数の画素 / 画素アレイ                  |    |

| 4 0 1 | 水平電荷結合素子( H C C D ) / シフト・レジスタ |    |

| 4 0 2 | 水平電荷結合素子( H C C D ) / シフト・レジスタ |    |

| 4 0 3 | 水平電荷結合素子( H C C D ) / シフト・レジスタ |    |

| 4 0 4 | 水平電荷結合素子( H C C D ) / シフト・レジスタ | 30 |

| 4 0 7 | 高速電荷ダンプ・ドレイン                   |    |

| 4 0 8 | 電荷検出出力増幅器                      |    |

| 4 0 9 | 電荷検出出力増幅器                      |    |

| 4 1 0 | 電荷検出出力増幅器                      |    |

| 4 1 1 | 電荷検出出力増幅器                      |    |

| 4 1 5 | 領域                             |    |

| 4 1 6 | 領域                             |    |

| 4 1 7 | 領域                             |    |

| 4 1 8 | 領域                             |    |

| 6 0 0 | 画像センサ                          | 40 |

| 6 1 0 | カメラ                            |    |

【図 1 a】

【図 1 b】

【図 2】

【図 3】

【図4】

【 図 5 】

【 図 6 】

【 図 7 】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

FIG. 14

【図15】

FIG. 15

【図16】

【図18】

【図17】

【図20】

【図19】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図 37】

FIG. 37

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2007/015641

A. CLASSIFICATION OF SUBJECT MATTER

INV. H01L27/146 H01L27/148 H01L29/768 H04N3/15 H04N9/04

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H01L H04N

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                       | Relevant to claim No. |

|-----------|----------------------------------------------------------------------------------------------------------|-----------------------|

| Y         | US 2006/125943 A1 (PARKS CHRISTOPHER [US])<br>15 June 2006 (2006-06-15)<br>abstract; figures 2,17-29     | 1-22                  |

| Y         | US 4 879 601 A (BUCK ARNOLD L [US] ET AL)<br>7 November 1989 (1989-11-07)<br>abstract; figure 1          | 1-22                  |

| A         | US 6 462 779 B1 (PHILBRICK ROBERT H [US])<br>8 October 2002 (2002-10-08)<br>abstract; figure 2           | 8-10                  |

| Y         | US 2004/150733 A1 (NAGAYOSHI RYOICHI [JP]<br>ET AL) 5 August 2004 (2004-08-05)<br>abstract; figures 1,22 | 1-3,<br>16-18         |

|           |                                                                                                          | -/-                   |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

- \*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- \*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- \*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- \*&\* document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the International search report

20 December 2007

03/01/2008

Name and mailing address of the ISA/

Authorized officer

European Patent Office, P.B. 5618 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 851 epo nl,

Fax: (+31-70) 340-3016

Heising, Stephan

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2007/015641 |

|---------------------------------------------------|

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                             | Relevant to claim No. |

|-----------|----------------------------------------------------------------------------------------------------------------|-----------------------|

| Y         | US 5 528 643 A (HYNECEK JAROSLAV [US])<br>18 June 1996 (1996-06-18)<br>abstract; figure 3                      | 1-3                   |

| Y         | EP 0 795 909 A (SONY CORP [JP])<br>17 September 1997 (1997-09-17)<br>abstract; figures 1,12,16                 | 1-3,<br>16-18         |

| Y         | US 4 500 915 A (KOIKE NORIO [JP] ET AL)<br>19 February 1985 (1985-02-19)<br>abstract; figures 2,12<br>column 7 | 1,3                   |

| A         | US 5 194 944 A (UCHIYAMA MASAYUKI [US] ET<br>AL) 16 March 1993 (1993-03-16)<br>abstract; figures 1,3,4,11      | 1,3,6,<br>18,21       |

| A         | JP 56 158577 A (VICTOR COMPANY OF JAPAN)<br>7 December 1981 (1981-12-07)<br>abstract; figure 2                 | 1                     |

| P,A       | US 2007/139545 A1 (PARKS CHRISTOPHER [US])<br>21 June 2007 (2007-06-21)<br>the whole document                  | 1-22                  |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2007/015641 |

|---------------------------------------------------|

| Patent document cited in search report |    | Publication date |                      | Patent family member(s)                                   |                                                      | Publication date |

|----------------------------------------|----|------------------|----------------------|-----------------------------------------------------------|------------------------------------------------------|------------------|

| US 2006125943                          | A1 | 15-06-2006       | NONE                 |                                                           |                                                      |                  |

| US 4879601                             | A  | 07-11-1989       | CA<br>DE<br>EP<br>JP | 2002448 A1<br>369227 T1<br>0369227 A2<br>2158763 A        | 14-05-1990<br>27-09-1990<br>23-05-1990<br>19-06-1990 |                  |

| US 6462779                             | B1 | 08-10-2002       | NONE                 |                                                           |                                                      |                  |

| US 2004150733                          | A1 | 05-08-2004       | EP<br>WO<br>JP<br>JP | 1562370 A1<br>2004045205 A1<br>3848650 B2<br>2004180284 A | 10-08-2005<br>27-05-2004<br>22-11-2006<br>24-06-2004 |                  |

| US 5528643                             | A  | 18-06-1996       | NONE                 |                                                           |                                                      |                  |

| EP 0795909                             | A  | 17-09-1997       | CA<br>JP<br>US       | 2199897 A1<br>9246519 A<br>6002146 A                      | 14-09-1997<br>19-09-1997<br>14-12-1999               |                  |

| US 4500915                             | A  | 19-02-1985       | CA<br>DE<br>EP<br>JP | 1188789 A1<br>3278655 D1<br>0077003 A2<br>58056458 U      | 11-06-1985<br>14-07-1988<br>20-04-1983<br>16-04-1983 |                  |

| US 5194944                             | A  | 16-03-1993       | JP<br>JP             | 2873046 B2<br>4013395 A                                   | 24-03-1999<br>17-01-1992                             |                  |

| JP 56158577                            | A  | 07-12-1981       | NONE                 |                                                           |                                                      |                  |

| US 2007139545                          | A1 | 21-06-2007       | WO                   | 2007078760 A2                                             |                                                      | 12-07-2007       |

---

## フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IS,IT,LT,LU,LV,MC,MT,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BH,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IS,JP,KE,KG,KM,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RS,RU,SC,SD,SE,SG,SK,SL,SM,SV,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,ZA,ZM,ZW

F ターム(参考) 4M118 AB01 BA13 DA18 DA23 DB06 DB09 FA14 FA17 FA44 GC07

GC14

5C024 AX01 CY47 DX01 EX52 GY01 GZ41 HX12 HX17