【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第4区分

【発行日】平成21年1月8日(2009.1.8)

【公開番号】特開2007-257813(P2007-257813A)

【公開日】平成19年10月4日(2007.10.4)

【年通号数】公開・登録公報2007-038

【出願番号】特願2006-304985(P2006-304985)

【国際特許分類】

|         |       |           |

|---------|-------|-----------|

| G 1 1 C | 19/28 | (2006.01) |

| G 1 1 C | 19/00 | (2006.01) |

| G 0 9 G | 3/36  | (2006.01) |

| G 0 9 G | 3/20  | (2006.01) |

| G 0 2 F | 1/133 | (2006.01) |

【F I】

|         |       |         |

|---------|-------|---------|

| G 1 1 C | 19/28 | D       |

| G 1 1 C | 19/00 | J       |

| G 0 9 G | 3/36  |         |

| G 0 9 G | 3/20  | 6 2 2 E |

| G 0 9 G | 3/20  | 6 2 1 F |

| G 0 9 G | 3/20  | 6 2 1 L |

| G 1 1 C | 19/00 | K       |

| G 0 2 F | 1/133 | 5 5 0   |

【手続補正書】

【提出日】平成20年11月14日(2008.11.14)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

第1および第2入力端子、出力端子並びにクロック端子と、

前記クロック端子に入力される第1クロック信号を前記出力端子に供給する第1トランジスタと、

前記出力端子を放電する第2トランジスタと、

前記第1トランジスタの制御電極が接続する第1ノードに第1電源端子の電位を供給する第3トランジスタと、

前記第1入力端子に入力される信号に基づいて、前記第3トランジスタの制御電極が接続する第2ノードを充電する第1充電回路と、

前記第2入力端子に入力される信号に基づいて、充電された前記第2ノードを昇圧する第1昇圧回路とを備える

ことを特徴とするシフトレジスタ回路。

【請求項2】

請求項1記載のシフトレジスタ回路であって、

前記第1充電回路は、

前記第2ノードと前記第1電源端子との間に接続し、前記第1入力端子に接続した制御電極を有する第4トランジスタであり、

前記第1昇圧回路は、

前記第2ノードと前記第2入力端子との間に接続する第1容量素子であることを特徴とするシフトレジスタ回路。

【請求項3】

請求項1記載のシフトレジスタ回路であって、

前記第1充電回路は、

前記第2ノードと前記第1入力端子との間に接続し、当該第1入力端子に接続した制御電極を有する第4トランジスタであり、

前記第1昇圧回路は、

前記第2ノードと前記第2入力端子との間に接続する第1容量素子であることを特徴とするシフトレジスタ回路。

【請求項4】

請求項2または請求項3記載のシフトレジスタ回路であって、

前記第1容量素子は、MOS(Metal Oxide Semiconductor)容量素子であることを特徴とするシフトレジスタ回路。

【請求項5】

請求項1記載のシフトレジスタ回路であって、

前記第1充電回路は、

前記第2ノードと前記第1電源端子との間に接続する第4トランジスタと、

前記第1入力端子に入力される信号に基づいて、前記第4トランジスタの制御電極が接続する第3ノードを充電する第2充電回路と、

所定の第3入力端子に入力される信号に基づいて、充電された前記第3ノードを昇圧する第2昇圧回路とを含み、

前記第1昇圧回路は、

前記第2ノードと前記第2入力端子との間に接続する第1容量素子であることを特徴とするシフトレジスタ回路。

【請求項6】

請求項5記載のシフトレジスタ回路であって、

前記第1容量素子は、MOS容量素子であることを特徴とするシフトレジスタ回路。

【請求項7】

請求項5または請求項6記載のシフトレジスタ回路であって、

前記第2充電回路は、

前記第3ノードと前記第1電源端子との間に接続し、前記第1入力端子に接続した制御電極を有する第5トランジスタであり、

前記第2昇圧回路は、

前記第3ノードと前記第3入力端子との間に接続する第2容量素子であることを特徴とするシフトレジスタ回路。

【請求項8】

請求項5または請求項6記載のシフトレジスタ回路であって、

前記第2充電回路は、

前記第3ノードと前記第1入力端子との間に接続し、当該第1入力端子に接続した制御電極を有する第5トランジスタであり、

前記第2昇圧回路は、

前記第3ノードと前記第3入力端子との間に接続する第2容量素子であることを特徴とするシフトレジスタ回路。

【請求項9】

請求項7または請求項8記載のシフトレジスタ回路であって、

前記第2容量素子は、MOS容量素子であることを特徴とするシフトレジスタ回路。

【請求項10】

請求項 1 から請求項 9 のいずれか記載のシフトレジスタ回路であって、前記出力端子と前記第 1 ノードとの間に接続する第 3 容量素子をさらに備えることを特徴とするシフトレジスタ回路。

【請求項 1 1】

請求項 1 から請求項 10 のいずれか記載のシフトレジスタ回路であって、前記第 1 電源端子には、前記第 1 クロック信号の振幅よりも大きな電圧が供給されていることを特徴とするシフトレジスタ回路。

【請求項 1 2】

複数のシフトレジスタ回路が縦続接続して成る多段のシフトレジスタ回路であって、前記多段の各段が、請求項 1 から請求項 11 のいずれか記載のシフトレジスタ回路であり、前記各段のシフトレジスタの前記第 1 電源端子に、前記第 1 クロック信号の振幅よりも大きな電圧を供給する電圧発生回路をさらに備えることを特徴とするシフトレジスタ回路。

【請求項 1 3】

請求項 1 2 記載のシフトレジスタ回路であって、前記電圧発生回路は、所定の電位が供給される第 2 電源端子と前記シフトレジスタ回路の前記第 1 電源端子との間に直列接続した第 1 および第 2 の整流素子と、前記第 1 および第 2 の整流素子の間の接続ノードと所定の第 2 クロック信号が入力されるクロック入力端子との間に接続した第 4 容量素子とを含んでいることを特徴とするシフトレジスタ回路。

【請求項 1 4】

請求項 1 3 記載のシフトレジスタ回路であって、前記第 2 クロック信号は、前記各段のシフトレジスタ回路の前記クロック端子に供給される多相クロック信号のうちの一相であることを特徴とするシフトレジスタ回路。

【請求項 1 5】

請求項 1 2 から請求項 1 4 のいずれか記載のシフトレジスタ回路であって、前記電圧発生回路は、前記各段のシフトレジスタ回路が形成された基板内に形成されていることを特徴とするシフトレジスタ回路。

【請求項 1 6】

請求項 1 2 から請求項 1 4 のいずれか記載のシフトレジスタ回路であって、前記電圧発生回路は、前記各段のシフトレジスタ回路が形成された基板に外付けされていることを特徴とするシフトレジスタ回路。

【請求項 1 7】

請求項 1 3 または請求項 1 4 記載のシフトレジスタ回路であって、前記電圧発生回路において、前記第 1 および第 2 の整流素子は、前記各段のシフトレジスタ回路が形成された基板内に形成され、前記第 4 容量素子は、前記基板に外付けされていることを特徴とするシフトレジスタ回路。

【請求項 1 8】

請求項 1 3 または請求項 1 4 記載のシフトレジスタ回路であって、前記電圧発生回路において、前記第 4 容量素子は、前記各段のシフトレジスタ回路が形成された基板内に形成され、

前記第1および第2の整流素子は、前記基板に外付けされていることを特徴とするシフトレジスタ回路。

**【請求項19】**

請求項12から請求項18のいずれか記載のシフトレジスタ回路であって、前記電圧発生回路を複数個有し、当該電圧発生回路は、互いに並列に接続されていることを特徴とするシフトレジスタ回路。

**【請求項20】**

第1および第2入力端子、出力端子並びにクロック端子と、前記クロック端子に入力されるクロック信号を前記出力端子に供給する第1トランジスタと、前記出力端子を放電する第2トランジスタと、前記第1入力端子に入力される信号に基づいて、前記第1トランジスタの制御電極が接続する第1ノードを充電する充電回路と、前記第2入力端子に入力される信号に基づいて、充電された前記第1ノードを昇圧する昇圧回路とを備えることを特徴とするシフトレジスタ回路。

**【請求項21】**

請求項20記載のシフトレジスタ回路であって、前記充電回路は、前記第1ノードと第1電源端子との間に接続し、前記第1入力端子に接続した制御電極を有する第3トランジスタであり、前記昇圧回路は、前記第1ノードと所定の第2ノードとの間に接続し当該第2ノードから前記第1ノードへの向きを導通方向とする一方向性のスイッチング素子と、前記第2ノードと前記第2入力端子との間に接続する第1容量素子と、前記第2ノードと前記第1電源端子との間に接続し、前記第1入力端子に接続した制御電極を有する第4トランジスタを含むことを特徴とするシフトレジスタ回路。

**【請求項22】**

請求項20記載のシフトレジスタ回路であって、前記充電回路は、前記第1ノードと第1電源端子との間に接続し、前記第1入力端子に接続した制御電極を有する第3トランジスタであり、前記昇圧回路は、前記第1ノードと所定の第2ノードとの間に接続し当該第2ノードから前記第1ノードへの向きを導通方向とする一方向性のスイッチング素子と、前記第2ノードと前記第2入力端子との間に接続する第1容量素子と、前記第2ノードと前記第1入力端子との間に接続し、当該第1入力端子に接続した制御電極を有する第4トランジスタを含むことを特徴とするシフトレジスタ回路。

**【請求項23】**

請求項21または請求項22記載のシフトレジスタ回路であって、前記第1容量素子は、MOS容量素子であることを特徴とするシフトレジスタ回路。

**【手続補正2】**

**【補正対象書類名】**明細書

**【補正対象項目名】**発明の名称

**【補正方法】**変更

**【補正の内容】**

【発明の名称】シフトレジスタ回路

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0039

【補正方法】変更

【補正の内容】

【0039】

また第2段目の単位シフトレジスタ回路SR2においては、第1入力端子IN1に上記の第2スタートパルスSP2が入力され、第2入力端子IN2は第1段目の単位シフトレジスタ回路SR1の出力端子OUTに接続する。第3段目以降の単位シフトレジスタ回路SRにおいては、第1入力端子IN1はその2段前(前々段)の単位シフトレジスタ回路SRの出力端子OUTに接続し、第2入力端子IN2はその前段の単位シフトレジスタ回路SRの出力端子OUTに接続する。そして各単位シフトレジスタ回路SRの出力端子OUTに出力される出力信号は、水平(又は垂直)走査パルスとしてそれぞれ対応するゲート線GLへと出力される。

【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0042

【補正方法】変更

【補正の内容】

【0042】

図3の如く、当該単位シフトレジスタ回路SRは、図2にも示した第1および第2入力端子IN1, IN2、クロック端子CK、リセット端子RSTおよび出力端子OUTの他に、低電位側電源電位VSSが供給される第1電源端子s1、高電位側電源電位VDD1, VDD2がそれぞれ供給される第2電源端子s2および第3電源端子s3を有している。高電位側電源電位VDD1, VDD2は、互いに同一レベルであってもよい。また、以下の説明では低電位側電源電位VSSが回路の基準電位となるが、実使用では画素に書き込まれるデータの電圧を基準にして基準電位が設定され、例えば高電位側電源電位VDD1, VDD2は17V、低電位側電源電位VSSは-12Vなどと設定される。

【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0051

【補正方法】変更

【補正の内容】

【0051】

その状態から、時刻t1で2段前の出力信号G<sub>n-2</sub>(第1段目の単位シフトレジスタ回路SR1の場合には第1スタートパルスSP1)がHレベルになると、それが当該単位シフトレジスタ回路SRの第1入力端子IN1に入力されトランジスタQ8がオンになる。このときノードN2はHレベルなのでトランジスタQ9もオンしているが、トランジスタQ8はトランジスタQ9よりも駆動能力が十分大きく設定されており、トランジスタQ8のオン抵抗はトランジスタQ9のオン抵抗に比べ十分低いため、ノードN3はトランジスタQ8を介して供給される電荷により充電され、そのレベルが上昇する。つまりトランジスタQ8は、第1入力端子IN1に入力される信号に基づいて、トランジスタQ3のゲートが接続するノードN3を充電する充電回路として機能する。

【手続補正6】

【補正対象書類名】明細書

【補正対象項目名】0066

【補正方法】変更

【補正の内容】

【0066】

以上の動作をまとめると、本実施の形態に係る単位シフトレジスタ回路S Rにおいては、第1入力端子I N 1および第2入力端子I N 2に信号が入力されない間はノードN 1がLレベル(V S S)、ノードN 2がHレベル(V D D 2 - V t h)のリセット状態にあり、その間はトランジスタQ 1がオフ、トランジスタQ 2がオンしているので、出力端子O U Tは低インピーダンスのLレベル(V S S)に維持される。そして第1入力端子I N 1および第2入力端子I N 2の順にパルス信号が入力されると、ノードN 2がLレベル(V S S)、ノードN 1がHレベル(V D D 1)のセット状態になる。セット状態ではトランジスタQ 1がオン、トランジスタQ 2がオフであるので、クロック端子C Kの信号(クロック信号C L K 1)がHレベルである間、ゲート線用出力端子O U TがHレベルになってゲート線を活性化する。その後、リセット端子R S Tの信号(次段のゲート線駆動信号G<sub>n+1</sub>)が入力されると、ノードN 1およびノードN 3がLレベル、ノードN 2がHレベルのリセット状態に戻る。

#### 【手続補正7】

【補正対象書類名】明細書

【補正対象項目名】0 0 8 1

【補正方法】変更

【補正の内容】

#### 【0 0 8 1】

図7は、実施の形態3に係る単位シフトレジスタ回路の構成を示す回路図である。本実施の形態においても、単位シフトレジスタ回路S Rは、第1入力端子I N 1に入力される信号に基づいてノードN 3を充電する充電回路(第1充電回路)と、第2入力端子I N 2に入力される信号に基づいて、充電されたノードN 3を昇圧する昇圧回路(第1昇圧回路)を備えている。本実施の形態において、第1充電回路は、ノードN 3と第2電源端子s 2との間に接続するトランジスタQ 8に加え、当該トランジスタQ 8のゲートが接続するノードN 4と第2電源端子s 2との間に接続するトランジスタQ 1 1、およびノードN 4と第3入力端子I N 3との間に接続した容量素子C 3とを備えている。一方、第1昇圧回路は、実施の形態1と同様に容量素子C 2により構成されている。

#### 【手続補正8】

【補正対象書類名】明細書

【補正対象項目名】0 0 8 2

【補正方法】変更

【補正の内容】

#### 【0 0 8 2】

ノードN 4と第1電源端子s 1との間には、ノードN 2に接続したゲートを有するトランジスタQ 1 2が接続している。本実施の形態では、トランジスタQ 6およびトランジスタQ 7から成るインバータ(プルダウン駆動回路)は、ノードN 4を入力端とし、ノードN 2を出力端としている。

#### 【手続補正9】

【補正対象書類名】明細書

【補正対象項目名】0 0 8 7

【補正方法】変更

【補正の内容】

#### 【0 0 8 7】

それに対し、本実施の形態に係る図7の単位シフトレジスタ回路S Rでは、第1入力端子I N 1に入力される3段前の出力信号G<sub>n-3</sub>によってノードN 4(トランジスタQ 8のゲート)がV D D - V t hのレベルに充電される。それによりトランジスタQ 8がオンするが、このときノードN 3のレベルはV D D - 2 × V t hまでしか上昇しない。しかしその後、第3入力端子I N 3に入力される2段前の出力信号G<sub>n-2</sub>によって、ノードN 4はさらに2 × V D D - V t hのレベルにまで昇圧される。それによりトランジスタQ 8は非飽和動作し、ノードN 3のレベルは高速にV D D 1 (= V D D)のレベルまで充電される

。従って、第2入力端子IN2に入力される前段の出力信号G<sub>n-1</sub>がHレベル(VDD)になると、容量素子C2を介するよう容量結合によりノードN3のレベルは2×VDDのレベルにまで上昇し、ノードN1はトランジスタQ3を通じて高速にVDD1のレベルにまで充電(プリチャージ)される。

【手続補正10】

【補正対象書類名】明細書

【補正対象項目名】0092

【補正方法】変更

【補正の内容】

【0092】

その場合には、第3入力端子IN3には2段前の単位シフトレジスタ回路SRに入力されるクロック信号が入力され、第2入力端子IN2には前段の単位シフトレジスタ回路SRに入力されるクロック信号が入力されるよう構成してもよい。即ち、例えば当該単位シフトレジスタ回路SRのクロック端子CKにクロック信号CLK1が入力されるのであれば、その第3入力端子IN3にはクロック信号CLK3を入力し、第2入力端子IN2にはクロック信号CLK4を入力すればよい。先に述べたように、通常、クロック信号の立上がり速度は単位シフトレジスタ回路SRの出力信号の立上がり速度よりも高速であるので、クロック信号を用いることによってノードN3およびノードN4の昇圧速度が速くなり、結果としてノードN1の充電(プリチャージ)がさらに高速化される。加えて、各単位シフトレジスタ回路SRの出力端子OUTにかかる負荷が低減され、出力信号G<sub>n</sub>の信号遅延が抑制される。従って、出力信号の高速化にさらに寄与できる。

【手続補正11】

【補正対象書類名】明細書

【補正対象項目名】0097

【補正方法】変更

【補正の内容】

【0097】

図10は実施の形態5に係る単位シフトレジスタ回路SRの構成を示す回路図である。実施の形態1ではトランジスタQ1のゲート・ソース間にノードN1の昇圧用の容量素子C1(昇圧容量)を設けていたが、本実施の形態ではそれをトランジスタQ1のゲート容量に置き換えている。その場合、図10の回路図の如く容量素子C1は不要になる。

【手続補正12】

【補正対象書類名】明細書

【補正対象項目名】0109

【補正方法】変更

【補正の内容】

【0109】

また、第1段目(第1ステージ)の単位シフトレジスタ回路SR1においては、第1および第2入力端子IN1, IN2に、それぞれ第1および第2スタートパルスSP1, SP2が入力信号として入力される。第2段目の単位シフトレジスタ回路SR2においては、第1入力端子IN1には上記の第2スタートパルスSP2が入力され、第2入力端子IN2は第1段目の単位シフトレジスタ回路SR1の出力端子OUTに接続する。第3段目以降の単位シフトレジスタ回路SRにおいては、第1入力端子IN1はその2段前(前々段)の単位シフトレジスタ回路SRの出力端子OUTに接続し、第2入力端子IN2はその前段の単位シフトレジスタ回路SRの出力端子OUTに接続する。そして各単位シフトレジスタ回路SRの出力端子OUTに出力される出力信号は、水平(又は垂直)走査パルスとしてゲート線GLへと出力される。

【手続補正13】

【補正対象書類名】明細書

【補正対象項目名】0112

【補正方法】変更

【補正の内容】

【0 1 1 2】

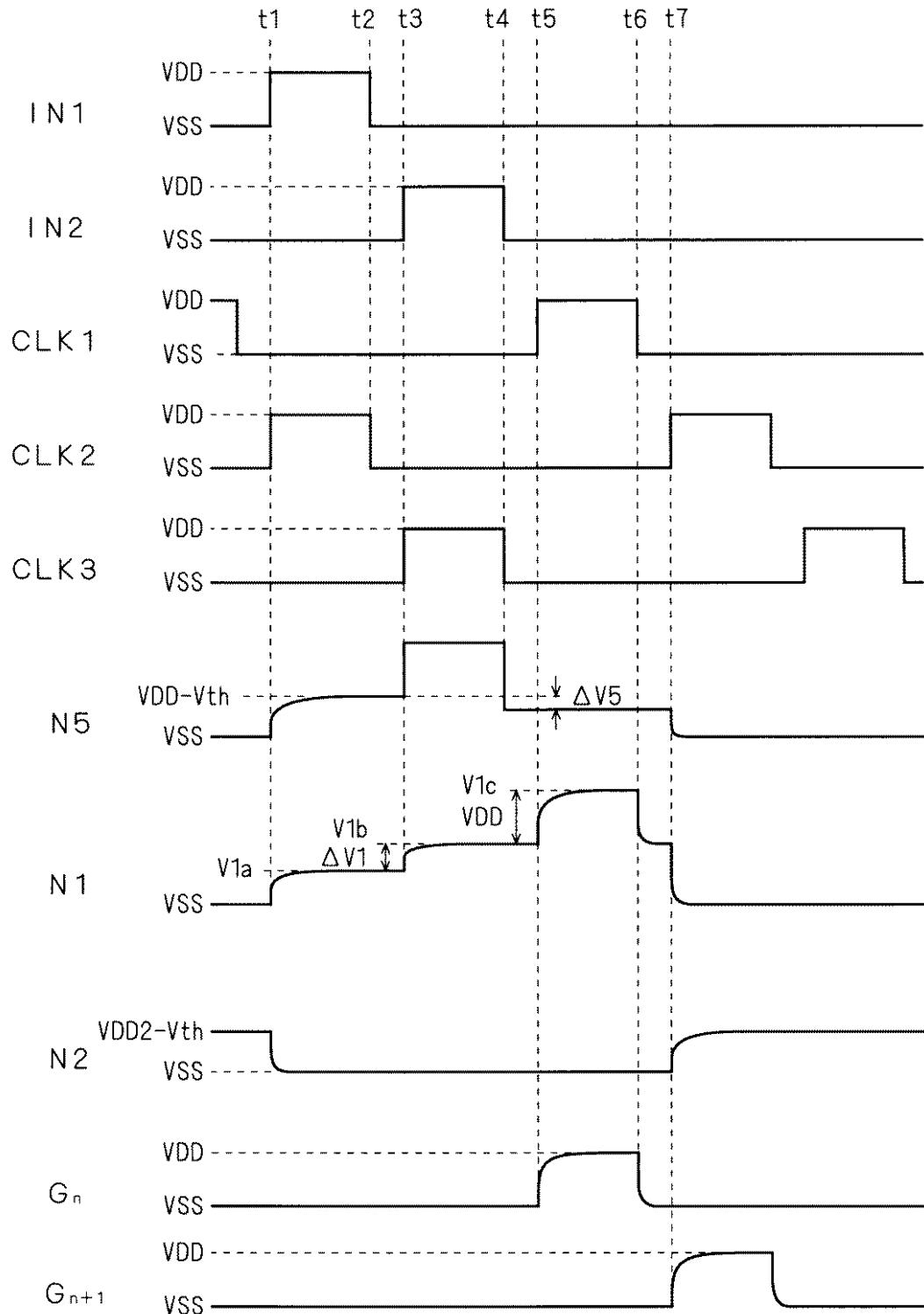

まず初期状態として、ノードN1およびノードN5がL(Low)レベル(VSS)、ノードN2がH(High)レベル(VDD2-Vth(Vth:トランジスタのしきい値電圧))であるリセット状態を想定する。また、クロック端子CK(クロック信号CLK1)、リセット端子RST(次段の出力信号Gn+1)、第1入力端子IN1(2段前の出力信号Gn-2)、第2入力端子IN2(前段の出力信号Gn-1)は何れもLレベルであるとする。リセット状態では、この単位シフトレジスタ回路SRが接続するゲート線は非選択状態にある。

【手続補正14】

【補正対象書類名】明細書

【補正対象項目名】0 1 1 3

【補正方法】変更

【補正の内容】

【0 1 1 3】

その状態から、時刻t1で2段前の出力信号Gn-2(第1段目の単位シフトレジスタ回路SR1の場合には第1スタートパルスSP1)がHレベルになると、それが当該単位シフトレジスタ回路SRの第1入力端子IN1に入力されトランジスタQ3並びにトランジスタQ14がオンになる。このときノードN2はHレベルなのでトランジスタQ4, Q15もオンしているが、トランジスタQ3, Q14はそれぞれトランジスタQ4, Q15よりも駆動能力が十分大きく設定されており、トランジスタQ3, Q14のオン抵抗はそれぞれトランジスタQ4, Q15のオン抵抗に比べ十分低い。そのため、ノードN1, N5はそれぞれトランジスタQ3, Q14を介して充電され、当該ノードN1, N5のレベルが上昇する。つまりトランジスタQ3は、第1入力端子IN1に入力される信号に基づいて、トランジスタQ1のゲートが接続するノードN1を充電する充電回路として機能する。

【手続補正15】

【補正対象書類名】明細書

【補正対象項目名】0 1 2 0

【補正方法】変更

【補正の内容】

【0 1 2 0】

具体的には、ノードN5の電荷がトランジスタQ1のゲート容量、容量素子C1、C4に分配されるようになるので、ノードN1のレベル上昇量V1は、

$$V1 = VDD \cdot C4 / (C4 + C1 + CQ1) - Vth \quad \dots (3)$$

となる。式(3)におけるC4は容量素子C4の容量値、C1は容量素子C1の容量値、CQ1はトランジスタQ1のゲート容量値、VthはトランジスタQ13のしきい値電圧である。このように、トランジスタQ13, Q14, 容量素子C4は一種のチャージポンプ回路を構成しており、トランジスタQ3による充電後のノードN1を、チャージポンプ動作によって昇圧する昇圧回路として機能している。

【手続補正16】

【補正対象書類名】明細書

【補正対象項目名】0 1 2 4

【補正方法】変更

【補正の内容】

【0 1 2 4】

その後時刻t4で前段の出力信号Gn-1がHレベルからLレベルに変化すると、第2入力端子IN2がLレベルになる。するとノードN5のレベルはそれに追随して下降するが、トランジスタQ13がダイオードとして働くため、ノードN1のレベルは変化しない(

セット状態も維持される）。そのためノードN5のレベルは、上記のチャージポンプ動作によりノードN5からノードN1に流れた電荷量に相当する電圧V5だけ低下する（図12参照）。

【手続補正17】

【補正対象書類名】明細書

【補正対象項目名】0130

【補正方法】変更

【補正の内容】

【0130】

以上の動作をまとめると、本実施の形態に係る単位シフトレジスタ回路SRにおいては、第1入力端子IN1および第2入力端子IN2に信号が入力されない間はノードN1がLレベル(VSS)、ノードN2がHレベル(VDD2-Vth)のリセット状態にあり、その間はトランジスタQ1がオフ、トランジスタQ2がオンしているので、出力端子OUTは低インピーダンスのLレベル(VSS)に維持される。そして第1入力端子IN1および第2入力端子IN2の順にパルス信号が入力されると、ノードN2がLレベル(VSS)、ノードN1が高電位側電源電位VDD1よりもさらに高いHレベルのセット状態になる。セット状態ではトランジスタQ1がオン、トランジスタQ2がオフであるので、クロック端子CKの信号（クロック信号CLK1）がHレベルである間、ゲート線用出力端子OUTがHレベルになってゲート線を活性化する。その後リセット端子RSTに信号（次段のゲート線駆動信号G<sub>n+1</sub>）が入力されると、ノードN1およびノードN5がLレベル、ノードN2がHレベルのリセット状態に戻る。

【手続補正18】

【補正対象書類名】明細書

【補正対象項目名】0134

【補正方法】変更

【補正の内容】

【0134】

本実施の形態に係る単位シフトレジスタ回路SRによれば、その回路構成は実施の形態6の容量素子C4をMOS容量素子（トランジスタQ17のゲート容量）に置き換えていけるだけなので、実施の形態6の単位シフトレジスタ回路SRと同様に動作する。よって実施の形態6と同様の効果が得られる。

【手続補正19】

【補正対象書類名】明細書

【補正対象項目名】0140

【補正方法】変更

【補正の内容】

【0140】

<実施の形態8>

実施の形態6,7においても、高電位側電源電位VDD1, VDD2は互いに同一レベルであってもよい。そこで本実施の形態においては、実施の形態4と同様に高電位側電源電位VDD1が供給される第2電源端子s2と、高電位側電源電位VDD2が供給される第3電源端子s3とを同一の端子で構成する。

【手続補正20】

【補正対象書類名】明細書

【補正対象項目名】0143

【補正方法】変更

【補正の内容】

【0143】

<実施の形態9>

図15は実施の形態9に係る単位シフトレジスタ回路SRの構成を示す回路図である。

実施の形態 6 ではトランジスタ Q 1 のゲート・ソース間にノード N 1 の昇圧用の容量素子 C 1 (昇圧容量) を設けていたが、本実施の形態ではそれをトランジスタ Q 1 のゲート容量に置き換えている。その場合、図 15 の回路図の如く容量素子 C 1 は不要になる。

【手続補正 2 1】

【補正対象書類名】明細書

【補正対象項目名】0 1 7 1

【補正方法】変更

【補正の内容】

【0 1 7 1】

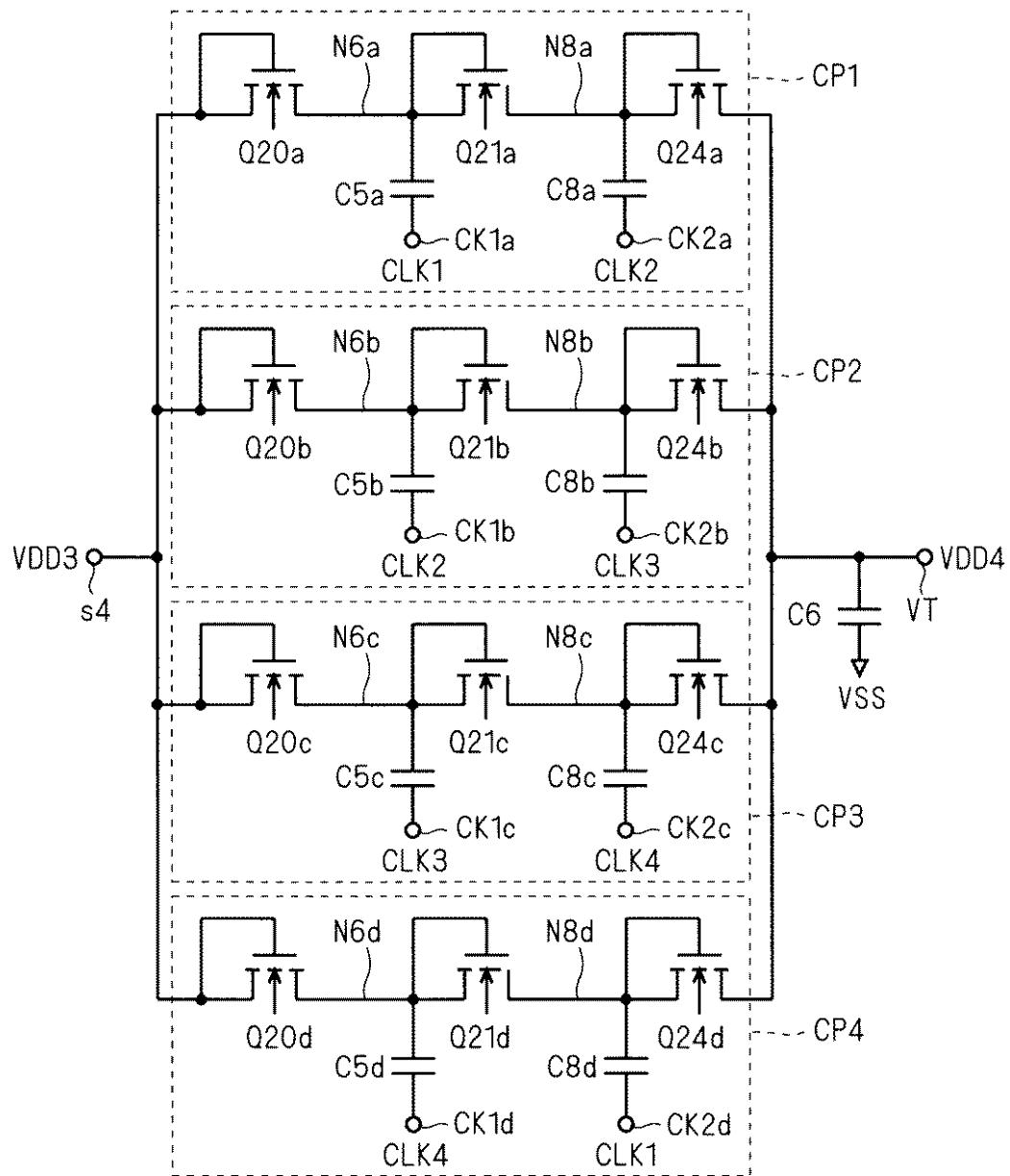

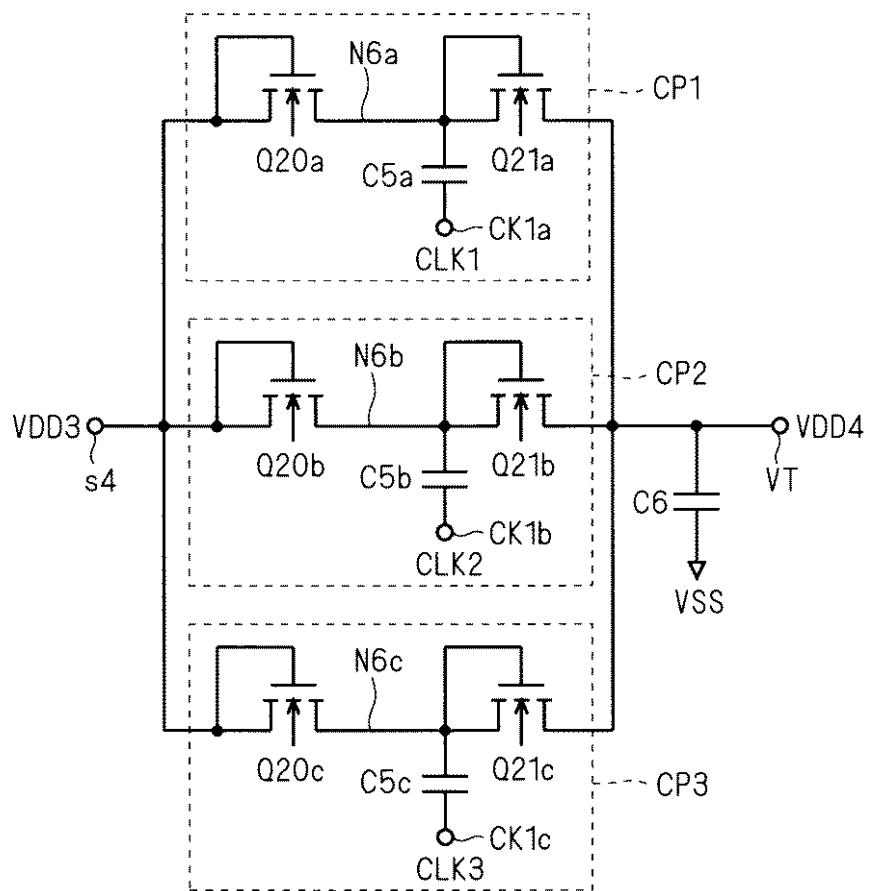

チャージポンプ回路 C P 1 は、ダイオード接続されたトランジスタ (ダイオード素子) Q 2 0 a , Q 2 1 a および、その間のノード N 6 a とクロック入力端子 C K 1 aとの間に接続したチャージポンプ容量 C 5 a から成っている。同様に、チャージポンプ回路 C P 2 は、ダイオード素子 Q 2 0 b , Q 2 1 b および、その間のノード N 6 b とクロック入力端子 C K 1 b との間に接続したチャージポンプ容量 C 5 b から成る。チャージポンプ回路 C P 3 は、ダイオード素子 Q 2 0 c , Q 2 1 c および、その間のノード N 6 c とクロック入力端子 C K 1 c との間に接続したチャージポンプ容量 C 5 c から成る。即ち、図 18 のチャージポンプ回路 C P 1 ~ C P 3 のそれぞれは、図 17 に示したチャージポンプ回路 C P と同じ構造のものである。

【手続補正 2 2】

【補正対象書類名】明細書

【補正対象項目名】0 1 7 4

【補正方法】変更

【補正の内容】

【0 1 7 4】

本実施の形態では 3 つのチャージポンプ回路を用いて電圧発生回路 3 2 を構成したが、電圧出力端子 V T のレベル低下がある程度許容される場合には、電圧発生回路 3 2 が備えるチャージポンプ回路は 1 つ (即ち実施の形態 1 0 と同じ) あるいは 2 つであってもよい。例えばチャージポンプ回路は 2 つ用いた場合であっても、実施の形態 1 0 と比較すると電圧出力端子 V T に電荷が供給される頻度は倍になるので、電圧出力端子 V T の電位低下は抑制される。

【手続補正 2 3】

【補正対象書類名】明細書

【補正対象項目名】0 1 8 3

【補正方法】変更

【補正の内容】

【0 1 8 3】

なおノード N 6 の昇圧時には、トランジスタ Q 2 3 が非飽和動作するので、ノード N 7 は第 4 電源端子 s 4 と同じ V D D 3 に充電される。このときノード N 6 が昇圧されているため、電位関係からトランジスタ Q 2 2 は、第 4 電源端子 s 4 側がソース、ノード N 6 側がドレインとなるが、そのゲート (ノード N 7 ) とソース (第 4 電源端子 s 4 ) の電位が等しいのでノード N 6 から第 4 電源端子 s 4 への電流は流れない。つまり、トランジスタ Q 2 2 は、第 4 電源端子 s 4 からノード N 6 への充電を行うが、その逆方向の電流は阻止する整流素子として機能している。

【手続補正 2 4】

【補正対象書類名】明細書

【補正対象項目名】0 1 9 7

【補正方法】変更

【補正の内容】

【0 1 9 7】

図 2 2 は本実施の形態に係る電圧発生回路 3 2 の具体的な回路構成の一例を示している

。この電圧発生回路32も、図17と同様にチャージポンプ回路CPおよび安定化容量C6により構成されているが、チャージポンプ回路CPの構成が図17とは異なっている。即ち本実施の形態では、図17のチャージポンプ回路CPに対し、ダイオード素子Q21と電圧出力端子VTとの間にさらにダイオード接続させたトランジスタQ24(ダイオード素子)を介在させると共に、ダイオード素子Q21, Q24間のノードN8とクロック入力端子CK2との間に接続した容量素子C8(チャージポンプ容量)を設けている。

【手続補正25】

【補正対象書類名】明細書

【補正対象項目名】0201

【補正方法】変更

【補正の内容】

【0201】

実施の形態10, 14から分かるように本発明によれば、図16のように3相クロック信号を用いたシフトレジスタ回路では、図17の如く2つのダイオード素子と1つのチャージポンプ容量で構成される1段のチャージポンプ回路により電圧発生回路32を構成し、トランジスタQ1のゲート・ソース間の電圧を従来技術の2倍にできる。また、図21のように4相クロック信号を用いたシフトレジスタ回路では、図22の如く3つのダイオード素子と2つのチャージポンプ容量で構成される2段のチャージポンプ回路により電圧発生回路32を構成して、トランジスタQ1のゲート・ソース間電圧を従来技術の3倍にできる。つまりn相クロック信号を用いたシフトレジスタ回路では、直列接続したn-1個のダイオード素子とそれらの間のn-2個の接続ノードの各々に接続するn-2個のチャージポンプ容量とで構成されるn-2段のチャージポンプ回路により電圧発生回路32を構成して、トランジスタQ1のゲート・ソース間電圧を従来技術のn-1倍にできる。ただし、各トランジスタの耐圧限界の範囲内で電圧を設定する必要がある。

【手続補正26】

【補正対象書類名】明細書

【補正対象項目名】0204

【補正方法】変更

【補正の内容】

【0204】

それらチャージポンプ回路CP1～CP4それぞれのクロック入力端子CK2a～CK2d(図22のクロック入力端子CK2に対応)には、シフトレジスタ回路(ゲート線駆動回路30)を駆動しているクロック信号CLK1～CLK4の何れかが入力される。即ち図23のように、チャージポンプ回路CP1のクロック入力端子CK2aにはクロック信号CLK2、チャージポンプ回路CP2のクロック入力端子CK2bにはクロック信号CLK3、チャージポンプ回路CP3のクロック入力端子CK2cにはクロック信号CLK4、チャージポンプ回路CP4のクロック入力端子CK2dにはクロック信号CLK1が、それぞれ入力される。

【手続補正27】

【補正対象書類名】明細書

【補正対象項目名】0205

【補正方法】変更

【補正の内容】

【0205】

そして、チャージポンプ回路CP1のクロック入力端子CK1aには、クロック入力端子CK2aのクロック信号CLK2とは位相の異なるクロック信号CLK1が入力される。チャージポンプ回路CP2のクロック入力端子CK1bには、クロック入力端子CK2bのクロック信号CLK3とは位相の異なるクロック信号CLK2が入力される。チャージポンプ回路CP3のクロック入力端子CK1cには、クロック入力端子CK2cのクロック信号CLK4とは位相の異なるクロック信号CLK3が入力される。チャージポンプ

回路 C P 4 のクロック入力端子 C K 1 d には、クロック入力端子 C K 2 d のクロック信号 C L K 1 とは位相の異なるクロック信号 C L K 4 が入力される。

【手続補正 2 8】

【補正対象書類名】明細書

【補正対象項目名】0 2 0 8

【補正方法】変更

【補正の内容】

【0 2 0 8】

図 2 4 は実施の形態 1 6 に係る電圧発生回路 3 2 の構成を示す回路図である。当該電圧発生回路 3 2 も、実施の形態 1 5 と同様に互いに並列に接続された 4 つのチャージポンプ回路 C P 1 ~ C P 4 が設けられている。本実施の形態では、チャージポンプ回路 C P 1 ~ C P 4 のそれぞれは、図 1 9 に示したチャージポンプ回路 C P と同じ構造のものである。

【手続補正 2 9】

【補正対象書類名】明細書

【補正対象項目名】0 2 0 9

【補正方法】変更

【補正の内容】

【0 2 0 9】

それらチャージポンプ回路 C P 1 ~ C P 4 それぞれのクロック入力端子 C K 1 a ~ C K 1 d (図 1 9 のクロック入力端子 C K 1 に対応) には、シフトレジスタ回路 (ゲート線駆動回路 3 0 ) を駆動しているクロック信号 C L K 1 ~ C L K 4 のいずれかが入力される。即ち図 2 4 のように、チャージポンプ回路 C P 1 のクロック入力端子 C K 1 a にはクロック信号 C L K 1 、チャージポンプ回路 C P 2 のクロック入力端子 C K 1 b にはクロック信号 C L K 2 、チャージポンプ回路 C P 3 のクロック入力端子 C K 1 c にはクロック信号 C L K 3 、チャージポンプ回路 C P 4 のクロック入力端子 C K 1 d にはクロック信号 C L K 4 が、それぞれ入力される。

【手続補正 3 0】

【補正対象書類名】明細書

【補正対象項目名】0 2 1 0

【補正方法】変更

【補正の内容】

【0 2 1 0】

そして、チャージポンプ回路 C P 1 のクロック入力端子 C K 2 a には、クロック入力端子 C K 1 a のクロック信号 C L K 1 とは位相の異なるクロック信号 C L K 4 が入力される。チャージポンプ回路 C P 2 のクロック入力端子 C K 2 b には、クロック入力端子 C K 1 b のクロック信号 C L K 2 とは位相の異なるクロック信号 C L K 3 が入力される。チャージポンプ回路 C P 3 のクロック入力端子 C K 2 c には、クロック入力端子 C K 1 c のクロック信号 C L K 3 とは位相の異なるクロック信号 C L K 2 が入力される。チャージポンプ回路 C P 4 のクロック入力端子 C K 2 d には、クロック入力端子 C K 1 d のクロック信号 C L K 4 とは位相の異なるクロック信号 C L K 1 が入力される。

【手続補正 3 1】

【補正対象書類名】明細書

【補正対象項目名】0 2 1 1

【補正方法】変更

【補正の内容】

【0 2 1 1】

従って、図 2 4 の電圧発生回路 3 2 では電圧出力端子 V T に、クロック信号 C L K 1 の立ち上がり時にチャージポンプ回路 C P 1 から電荷が供給され、クロック信号 C L K 2 の立ち上がり時にチャージポンプ回路 C P 2 から電荷が供給され、クロック信号 C L K 3 の立ち上がり時にチャージポンプ回路 C P 3 から電荷が供給され、クロック信号 C L K 4 の

立ち上がり時にチャージポンプ回路C P 4から電荷が供給される。つまり電圧出力端子V Tには、クロック信号C L K 1 ~ C L K 4によって順次、電荷が供給されることとなり、電圧出力端子V Tの電位低下の問題は解決される。

【手続補正32】

【補正対象書類名】明細書

【補正対象項目名】0212

【補正方法】変更

【補正の内容】

【0212】

なお、以上の実施の形態10~16においては、実施の形態1, 3の単位シフトレジスタ回路S R(図3, 図7)に対して電圧発生回路32を接続させた構成(図16, 図21)を示したが、当該電圧発生回路32の適用はそれに限られるものではない。充電後のトランジスタQ3のゲート(ノードN3)を昇圧する昇圧回路を備える実施の形態2, 4, 5の単位シフトレジスタ回路S R(図6, 図9, 図10)に対しても適用可能である。その場合にも実施の形態10~16と同様に、トランジスタQ1のゲート(ノードN1)を高い電位に充電することができるという効果が得られる。

【手続補正33】

【補正対象書類名】図面

【補正対象項目名】図12

【補正方法】変更

【補正の内容】

【図 1 2】

【手続補正 3 4】

【補正対象書類名】図面

【補正対象項目名】図 1 8

【補正方法】変更

【補正の内容】

【図 18】

【手続補正 3 5】

【補正対象書類名】図面

【補正対象項目名】図 2 3

【補正方法】変更

【補正の内容】

【図 2 3】