(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4843821号

(P4843821)

(45) 発行日 平成23年12月21日(2011.12.21)

(24) 登録日 平成23年10月21日(2011.10.21)

(51) Int.Cl.

G06F 12/06 (2006.01)

F 1

G06F 12/06 550B

請求項の数 42 (全 22 頁)

(21) 出願番号 特願2007-557019 (P2007-557019)

(86) (22) 出願日 平成18年1月11日 (2006.1.11)

(65) 公表番号 特表2008-532140 (P2008-532140A)

(43) 公表日 平成20年8月14日 (2008.8.14)

(86) 國際出願番号 PCT/US2006/001153

(87) 國際公開番号 WO2006/091283

(87) 國際公開日 平成18年8月31日 (2006.8.31)

審査請求日 平成19年10月18日 (2007.10.18)

(31) 優先権主張番号 11/064,543

(32) 優先日 平成17年2月23日 (2005.2.23)

(33) 優先権主張国 米国(US)

(73) 特許権者 510127664

ラウンド ロック リサーチ、エルエルシ

ー

アメリカ合衆国、ニューヨーク州 105

49、マウント キスコ、ディア クリー

ク レーン 26

(74) 代理人 100106851

弁理士 野村 泰久

(74) 代理人 100074099

弁理士 大菅 義之

(72) 発明者 ジェデロー, ジョセフ, エム.

アメリカ合衆国, ミネソタ州 55126

, ショアヴュー, レイランド レーン 4

302

最終頁に続く

(54) 【発明の名称】複数内部データバス及びメモリバンクインターリービングを有するメモリデバイス及び方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の出力端子及び複数の入力端子を有するメモリコントローラと、

複数の出力端子及び複数の入力端子を有する少なくとも一つのメモリデバイスと、

前記メモリコントローラの前記出力端子を前記メモリデバイスの前記入力端子へと接続

する下流バスであって、前記メモリコントローラの前記入力端子及び前記メモリデバイス

の前記出力端子から絶縁されている下流バスと、

前記メモリデバイスの前記出力端子を前記メモリコントローラの前記入力端子へと接続

する上流バスであって、前記メモリコントローラの前記出力端子及び前記メモリデバイス

の前記入力端子から絶縁されている上流バスと、

を有するメモリシステムであって、

少なくとも一つの前記メモリデバイスは、

書き込みコマンドに応じて書き込みデータを格納し、読み出しコマンドに応じて読み出

しデータを出力するよう動作可能な複数のメモリセルのバンクと、

それぞれが前記メモリデバイスの前記入力端子を、メモリセルの前記バンクのそれぞれ

へと接続する少なくとも一対の内部書き込みデータバスと、

それぞれが前記メモリデバイスの前記出力端子を、メモリセルの前記バンクのそれぞれ

へと接続する少なくとも一対の内部読み出しデータバスであって、前記内部書き込みデータ

バスから絶縁されている内部読み出しデータバスと、

前記内部書き込みデータバス及びそれぞれの前記バンクに接続されている書き込みデータ

バスと、

10

20

タ選択回路であって、それぞれの前記内部書き込みデータバスを前記バンクのいずれかに選択的に接続するよう動作可能である書き込みデータ選択回路と、

前記内部読み出しデータバス及びそれぞれの前記バンクに接続されている読み出しデータ選択回路であって、前記バンクのいずれかをそれぞれの前記内部読み出しデータバスに選択的に接続するよう動作可能である読み出しデータ選択回路と、

前記バンクのうちの一つを読みだし或いは書き込みメモリアクセスのために選択し、前記選択されたバンクのメモリセルのロウ及びカラムを選択するように動作可能であるアドレスング回路と、

メモリコマンドを受け取ってデコードし、前記メモリコマンドに対応する制御信号を発生するよう動作可能なコマンドデコーダであって、少なくとも幾つかの前記制御信号は、前記書き込みデータ選択回路を制御して、前記内部書き込みデータバスのどちらかを介して、前記メモリデバイスの前記入力端子から、選択されたバンクへと書き込みデータを接続し、少なくとも幾つかの前記制御信号は、前記読み出しデータ選択回路を制御して、前記内部読み出しデータバスのどちらかを介して、選択されたバンクから前記メモリデバイスの前記出力端子へと読み出しデータを接続する、コマンドデコーダと、

前記メモリデバイスの前記入力端子に接続された書き込みバッファであって、前記書き込みバッファは、少なくとも一つの書き込み要求からの書き込みデータを格納し、前記書き込みデータを前記書き込みバッファから、前記バンクのうちの一つへ格納するための前記内部書き込みデータバスのどちらかへと接続するように動作可能である、書き込みバッファと、

を備えていることを特徴とするメモリシステム。

#### 【請求項 2】

前記書き込みバッファは、読み出しデータが前記バンクのうちの一つから前記内部読み出しデータバスのうちの一つへ接続されるのと同時に、前記内部書き込みデータバスのどちらかを介して、前記書き込みデータを前記書き込みバッファから前記バンクのうちの他の一つへ接続するよう動作可能である、ことを特徴とする請求項1に記載のメモリシステム。

#### 【請求項 3】

前記コマンドデコーダによって生成された前記制御信号は、前記内部読み出しデータバスのどちらかを介して、読み出しデータを、選択されたバンクから前記メモリデバイスの前記出力端子へ接続するのと同時に、前記内部書き込みデータバスのどちらかを介して、書き込みデータを、前記メモリデバイスの前記入力端子から、選択されたバンクへ接続するよう動作可能である、ことを特徴とする請求項1に記載のメモリシステム。

#### 【請求項 4】

前記コマンドデコーダによって生成された前記制御信号は、書き込みデータを前記内部書き込みデータバスのうちの一つから、選択されたバンクへと接続するのと同時に、書き込みデータを前記内部書き込みデータバスのうちの他の一つから、異なる選択されたバンクに接続するよう動作可能である、ことを特徴とする請求項1に記載のメモリシステム。

#### 【請求項 5】

前記コマンドデコーダによって生成された前記制御信号は、読み出しデータを、選択されたバンクから前記内部読み出しデータバスのうちの一つへ接続するのと同時に、読み出しデータを、異なる選択されたバンクから前記内部読み出しデータバスのうちの他の一つへと接続するよう動作可能である、ことを特徴とする請求項1に記載のメモリシステム。

#### 【請求項 6】

前記メモリデバイスは、前記メモリデバイスの前記入力端子に接続されたコマンド／アドレスレジスタを更に有し、前記コマンド／アドレスレジスタは、前記下流バスを介して前記メモリデバイスへと接続された前記メモリコマンド及び前記ロウ及びカラムアドレスを格納するよう動作可能である、ことを特徴とする請求項1に記載のメモリシステム。

#### 【請求項 7】

メモリセルの前記バンクはダイナミックランダムアクセスメモリセルのバンクを含む、

10

20

30

40

50

ことを特徴とする請求項 1 に記載のメモリシステム。

【請求項 8】

前記メモリコントローラが、更にクロック信号を出力するように動作可能であり、前記メモリデバイスは、シンクロナスダイナミックランダムアクセスメモリデバイスを有し、かつ、クロック入力端子を含み、前記メモリシステムは、前記クロック信号を前記メモリコントローラから前記メモリデバイスの前記クロック入力端子へと接続するクロック信号ラインを更に有する、ことを特徴とする請求項 6 に記載のメモリシステム。

【請求項 9】

前記書き込みデータ選択回路は、前記バンクのそれぞれのための書き込みマルチプレクサを有し、前記書き込みマルチプレクサのそれぞれは、それぞれの前記内部書き込みデータバスへ接続されている複数の入力、及び、それぞれの前記バンクへ接続されている出力を有する、ことを特徴とする請求項 1 に記載のメモリシステム。

10

【請求項 10】

前記読み出しデータ選択回路は、前記内部読み出しデータバスのそれぞれのための読み出しマルチプレクサを有し、前記読み出しマルチプレクサのそれぞれは、それぞれの前記バンクへ接続されている複数の入力、及び、それぞれの前記内部読み出しデータバスへ接続されている出力を有する、ことを特徴とする請求項 1 に記載のメモリシステム。

【請求項 11】

複数の出力端子及び複数の入力端子を有するメモリデバイスであって、前記メモリデバイスは、

20

書き込みコマンドに応じて書き込みデータを格納し、読み出しコマンドに応じて読み出しデータを出力するよう動作可能な複数のメモリセルのバンクと、

それが複数のメモリデバイス入力端子をメモリセルの前記バンクのそれぞれへと接続する少なくとも一対の内部書き込みデータバスと、

それが複数のメモリデバイス出力端子をメモリセルの前記バンクのそれぞれへと接続する少なくとも一対の内部読み出しデータバスであって、前記内部書き込みデータバスから絶縁されている内部読み出しデータバスと、

前記内部書き込みデータバス及びそれぞれの前記バンクに接続されている書き込みデータ選択回路であって、それぞれの前記内部書き込みデータバスを前記バンクのいずれかに選択的に接続するよう動作可能である書き込みデータ選択回路と、

30

前記内部読み出しデータバス及びそれぞれの前記バンクに接続されている読み出しデータ選択回路であって、前記バンクのいずれかをそれぞれの前記内部読み出しデータバスに選択的に接続するよう動作可能である読み出しデータ選択回路と、

前記バンクのうちの一つを読みだし或いは書き込みメモリアクセスのために選択し、前記選択されたバンクのメモリセルのロウ及びカラムを選択するよう動作可能であるアドレスング回路と、

メモリコマンドを受け取ってデコードし、前記メモリコマンドに対応する制御信号を発生するよう動作可能なコマンドデコーダであって、少なくとも幾つかの前記制御信号は、前記書き込みデータ選択回路を制御して、前記内部書き込みデータバスのどちらかを介して、前記メモリデバイスの前記入力端子から、選択されたバンクへと書き込みデータを接続し、少なくとも幾つかの前記制御信号は、前記読み出しデータ選択回路を制御して、前記内部読み出しデータバスのどちらかを介して、選択されたバンクから前記メモリデバイスの前記出力端子へと読み出しデータを接続する、コマンドデコーダと、

40

前記メモリデバイスの前記入力端子に接続された書き込みバッファであって、前記書き込みバッファは、少なくとも一つの書き込み要求からの書き込みデータを格納し、前記書き込みデータを前記書き込みバッファから、前記バンクのうちの一つへ格納するための前記内部書き込みデータバスのどちらかへと接続するよう動作可能である、書き込みバッファと、

を備えることを特徴とするメモリデバイス。

【請求項 12】

50

前記書き込みバッファは、読み出しデータが前記バンクのうちの一つから前記内部読み出しデータバスのうちの一つへ接続されるのと同時に、前記内部書き込みデータバスのどちらかを介して、前記書き込みデータを前記書き込みバッファから前記バンクのうちの他の一つへ接続するよう動作可能である、ことを特徴とする請求項1\_1に記載のメモリデバイス。

【請求項1\_3】

前記コマンドデコーダによって生成された前記制御信号は、前記内部読み出しデータバスのどちらかを介して、読み出しデータを選択されたバンクから前記メモリデバイスの前記出力端子へ接続するのと同時に、前記内部書き込みデータバスのどちらかを介して、書き込みデータを、前記メモリデバイスの前記入力端子から、選択されたバンクへ接続するよう動作可能である、ことを特徴とする請求項1\_1に記載のメモリデバイス。

10

【請求項1\_4】

前記コマンドデコーダによって生成された前記制御信号は、書き込みデータを前記内部書き込みデータバスのうちの一つから、選択されたバンクへと接続するのと同時に、書き込みデータを前記内部書き込みデータバスのうちの他の一つから、異なる選択されたバンクに接続するよう動作可能である、ことを特徴とする請求項1\_1に記載のメモリデバイス。

【請求項1\_5】

前記コマンドデコーダによって生成された前記制御信号は、読み出しデータを異なる選択されたバンクから前記内部読み出しデータバスのうちの一つへ接続するのと同時に、読み出しデータを、異なる選択されたバンクから前記内部読み出しデータバスのうちの他の一つへと接続するよう動作可能である、ことを特徴とする請求項1\_1に記載のメモリデバイス。

20

【請求項1\_6】

前記メモリデバイスは、前記メモリデバイス入力端子に接続されたコマンド／アドレスレジスタを更に有し、前記コマンド／アドレスレジスタは、前記メモリデバイス入力端子へと接続された前記メモリコマンド及び前記ロウ及びカラムアドレスを格納するよう動作可能である、ことを特徴とする請求項1\_1に記載のメモリデバイス。

【請求項1\_7】

メモリセルの前記バンクはダイナミックランダムアクセスメモリセルのバンクを有する、ことを特徴とする請求項1\_1に記載のメモリデバイス。

30

【請求項1\_8】

前記メモリデバイスは、シンクロナスダイナミックランダムアクセスメモリデバイスを有する、ことを特徴とする請求項1\_7に記載のメモリデバイス。

【請求項1\_9】

前記書き込みデータ選択回路は、前記バンクのそれぞれのための書き込みマルチプレクサを有し、前記書き込みマルチプレクサのそれぞれは、それぞれの前記内部書き込みデータバスへ接続されている複数の入力、及び、それぞれの前記バンクへ接続されている出力を有する、ことを特徴とする、請求項1\_1に記載のメモリデバイス。

【請求項2\_0】

40

前記読み出しデータ選択回路は、前記内部読み出しデータバスのそれぞれのための読み出しマルチプレクサを有し、前記読み出しマルチプレクサのそれぞれは、それぞれの前記バンクへ接続されている複数の入力、及び、それぞれの前記内部読み出しデータバスへ接続されている出力を有する、ことを特徴とする請求項1\_1に記載のメモリデバイス。

【請求項2\_1】

プロセッサベースのコンピュータシステムであって、

プロセッサバスを有するプロセッサと、

前記プロセッサバスを介して前記プロセッサに接続され、データを前記コンピュータシステムへ入力することを可能にする入力デバイスと、

前記プロセッサバスを介して前記プロセッサに接続され、データを前記コンピュータシ

50

システムから出力することを可能にする出力デバイスと、

前記プロセッサバスを介して前記プロセッサに接続された大規模データ格納デバイスであって、前記大規模格納デバイスからデータが読み出されることを可能にする大規模データ格納デバイスと、

前記プロセッサバスを介して前記プロセッサに接続されるメモリコントローラであって、複数の出力端子及び複数の入力端子を有しているメモリコントローラと、

複数の出力端子及び複数の入力端子を有する少なくとも一つのメモリデバイスと、

前記メモリコントローラの前記出力端子を前記メモリデバイスの前記入力端子へと接続する下流バスであって、前記メモリコントローラの前記入力端子及び前記メモリデバイスの前記出力端子から絶縁されている下流バスと、

前記メモリデバイスの前記出力端子を前記メモリコントローラの前記入力端子へと接続する上流バスであって、前記メモリコントローラの前記出力端子及び前記メモリデバイスの前記入力端子から絶縁されている上流バスと、

を備え、

少なくとも一つの前記メモリデバイスは、

書き込みコマンドに応じて書き込みデータを格納し、読み出しコマンドに応じて読み出しデータを出力するよう動作可能な複数のメモリセルのバンクと、

それぞれが前記メモリデバイスの前記入力端子を、メモリセルの前記バンクのそれぞれへと接続する少なくとも一対の内部書き込みデータバスと、

それぞれが前記メモリデバイスの前記出力端子を、メモリセルの前記バンクのそれぞれへと接続する少なくとも一対の内部読み出しデータバスであって、前記内部書き込みデータバスから絶縁されている内部読み出しデータバスと、

前記内部書き込みデータバス及びそれぞれの前記バンクに接続されている書き込みデータ選択回路であって、それぞれの前記内部書き込みデータバスを前記バンクのいずれかに選択的に接続するよう動作可能である書き込みデータ選択回路と、

前記内部読み出しデータバス及びそれぞれの前記バンクに接続されている読み出しデータ選択回路であって、前記バンクのいずれかをそれぞれの前記内部読み出しデータバスに選択的に接続するよう動作可能である読み出しデータ選択回路と、

前記バンクのうちの一つを読みだし或いは書き込みメモリアクセスのために選択し、前記選択されたバンクのメモリセルのロウ及びカラムを選択するように動作可能であるアドレスング回路と、

メモリコマンドを受け取ってデコードし、前記メモリコマンドに対応する制御信号を発生するよう動作可能なコマンドデコーダであって、少なくとも幾つかの前記制御信号は、書き込みデータ選択回路を制御して、前記内部書き込みデータバスのどちらかを介して、前記メモリデバイスの前記入力端子から選択されたバンクへと書き込みデータを接続し、少なくとも幾つかの前記制御信号は、前記読み出しデータ選択回路を制御して、前記内部読み出しデータバスのどちらかを介して、選択されたバンクから前記メモリデバイスの前記出力端子へと読み出しデータを接続する、コマンドデコーダと、

前記メモリデバイスの前記入力端子に接続された書き込みバッファであって、前記書き込みバッファは、少なくとも一つの書き込み要求からの書き込みデータを格納し、前記書き込みデータを前記書き込みバッファから、前記バンクのうちの一つへ格納するための前記内部書き込みデータバスのどちらかへと接続するように動作可能である、書き込みバッファと、

を備えることを特徴とするプロセッサベースのコンピュータシステム。

**【請求項 22】**

前記書き込みバッファは、読み出しデータが前記バンクのうちの一つから前記内部読み出しデータバスのうちの一つへ接続されるのと同時に、前記内部書き込みデータバスのどちらかを介して、前記書き込みデータを前記書き込みバッファから前記バンクのうちの他の一つへ接続するよう動作可能である、ことを特徴とする請求項21に記載のプロセッサベースのコンピュータシステム。

## 【請求項 2 3】

前記コマンドデコーダによって生成された前記制御信号は、前記内部読み出しデータバスのどちらかを介して、読み出しデータを、選択されたバンクから前記メモリデバイスの前記出力端子へ接続するのと同時に、前記内部書き込みデータバスのどちらかを介して、書き込みデータを、前記メモリデバイスの前記入力端子から、選択されたバンクへ接続するよう動作可能である、ことを特徴とする請求項2\_1に記載のプロセッサベースのコンピュータシステム。

## 【請求項 2 4】

前記コマンドデコーダによって生成された前記制御信号は、書き込みデータを前記内部書き込みデータバスのうちの一つから、選択されたバンクへと接続するのと同時に、書き込みデータを前記内部書き込みデータバスのうちの他の一つから、異なる選択されたバンクに接続するよう動作可能である、ことを特徴とする請求項2\_1に記載のプロセッサベースのコンピュータシステム。

10

## 【請求項 2 5】

前記コマンドデコーダによって生成された前記制御信号は、読み出しデータを、選択されたバンクから前記内部読み出しデータバスのうちの一つへ接続するのと同時に、読み出しデータを、異なる選択されたバンクから前記内部読み出しデータバスのうちの他の一つへと接続するよう動作可能である、ことを特徴とする請求項2\_1に記載のプロセッサベースのコンピュータシステム。

## 【請求項 2 6】

20

前記メモリデバイスは、前記メモリデバイスの前記入力端子に接続されたコマンド／アドレスレジスタを更に有し、前記コマンド／アドレスレジスタは、前記下流バスを介して前記メモリデバイスへと接続された前記メモリコマンド及び前記ロウ及びカラムアドレスを格納するよう動作可能である、ことを特徴とする請求項2\_1に記載のプロセッサベースのコンピュータシステム。

## 【請求項 2 7】

メモリセルの前記バンクはダイナミックランダムアクセスメモリセルのバンクを有する、ことを特徴とする請求項2\_1に記載のプロセッサベースのコンピュータシステム。

## 【請求項 2 8】

30

前記メモリコントローラが、更にクロック信号を出力するよう動作可能であり、前記メモリデバイスは、シンクロナスダイナミックランダムアクセスメモリデバイスを有し、クロック入力端子を含み、前記メモリシステムは、前記クロック信号を前記メモリコントローラから前記メモリデバイスの前記クロック入力端子へと接続するクロック信号ラインを更に有する、ことを特徴とする請求項2\_7に記載のプロセッサベースのコンピュータシステム。

## 【請求項 2 9】

前記書き込みデータ選択回路は、前記バンクのそれぞれのための書き込みマルチプレクサを有し、前記書き込みマルチプレクサのそれぞれは、それぞれの前記内部書き込みデータバスへ接続されている複数の入力、及び、それぞれの前記バンクへ接続されている出力を有する、ことを特徴とする請求項2\_1に記載のプロセッサベースのコンピュータシステム。

40

## 【請求項 3 0】

前記読み出しデータ選択回路は、前記内部読み出しデータバスのそれぞれのための読み出しマルチプレクサを有し、前記読み出しマルチプレクサのそれぞれは、それぞれの前記バンクへ接続されている複数の入力、及び、それぞれの前記内部読み出しデータバスへ接続されている出力を有する、ことを特徴とする請求項2\_1に記載のプロセッサベースのコンピュータシステム。

## 【請求項 3 1】

複数のメモリセルのバンクを有するメモリデバイスへ、及び該メモリデバイスから、データを接続する方法であって、

50

複数の書き込みデータバス端子を介して書き込みデータを前記メモリデバイスへと接続することと、

複数の読み出しデータバス端子を介して読み出しデータを前記メモリデバイスから接続することと、

前記書き込みデータを前記書き込みデータバス端子から前記バンクのうちの第一のバンクへと接続し、同時に、前記書き込みデータを前記書き込みデータバス端子から前記バンクのうちの第二のバンクへ接続することと、

前記書き込みデータを前記書き込みデータバス端子から前記バンクのうちの第一のバンクへ接続し、同時に、前記読み出しデータを前記バンクのうちの第三のバンクから前記読み出しデータバス端子へ接続することと、

複数の書き込み要求のための前記書き込みデータを、該書き込みデータの受け取り時に該書き込みデータをメモリセルの前記バンクのうちの一つへ接続せずに、前記メモリデバイス内の書き込みバッファに保持することと、

前記書き込み要求のうちの一つのための前記保持された書き込みデータを前記バンクのうちの一つへ接続し、同時に、前記書き込み要求のうちの他の一つのための前記保持された書き込みデータを前記バンクのうちの他の一つへ接続することと、

を含むことを特徴とする方法。

【請求項 3 2】

前記書き込みデータを前記書き込みデータバス端子から前記バンクのうちの第一のバンクへ接続し、同時に、前記読み出しデータを前記バンクのうちの第三のバンクから前記読み出しデータバス端子へ接続する前記動作が、内部書き込みデータバスを介して前記書き込みデータバス端子から前記バンクのうちの前記第一のバンクへ前記書き込みデータを接続することと、内部読み出しデータバスを介して前記バンクのうちの前記第三のバンクから前記読み出しデータバス端子へ前記読み出しデータを接続することとを含む、ことを特徴とする請求項 3 1 に記載の方法。

【請求項 3 3】

前記書き込みデータを前記書き込みデータバス端子から前記バンクのうちの第一のバンクへ接続し、同時に、前記書き込みデータを前記書き込みデータバス端子から前記バンクのうちの第二のバンクへ接続する前記動作は、第一の内部書き込みデータバスを介して前記書き込みデータバス端子から前記バンクのうちの前記第一のバンクへ前記書き込みデータを接続することと、第二の内部書き込みデータバスを介して前記書き込みデータバス端子から前記バンクのうちの前記第二のバンクへ前記書き込みデータを接続することとを含む、ことを特徴とする請求項 3 1 に記載の方法。

【請求項 3 4】

前記バンクのうちの第四のバンクから前記読み出しデータバス端子へ読み出しデータを接続し、同時に、前記バンクのうちの前記第三のバンクから前記読み出しデータバス端子へ読み出しデータを接続することを更に含む、ことを特徴とする請求項 3 1 に記載の方法。

【請求項 3 5】

前記バンクのうちの第四のバンクから前記読み出しデータバス端子へ読み出しデータを接続し、同時に、前記バンクのうちの前記第三のバンクから前記読み出しデータバス端子へ読み出しデータを接続する前記動作は、第一の内部読み出しデータバスを介して前記バンクのうちの前記第三のバンクから前記読み出しデータバス端子へ前記読み出しデータを接続することと、第二の内部読み出しデータバスを介して前記バンクのうちの前記第四のバンクから前記読み出しデータバス端子へ前記読み出しデータを接続することと、を含む、ことを特徴とする請求項 3 4 に記載の方法。

【請求項 3 6】

前記メモリデバイスは、ダイナミックランダムアクセスメモリデバイスを含む、ことを特徴とする請求項 3 1 に記載の方法。

【請求項 3 7】

10

20

30

40

50

複数のメモリセルのバンクを有するメモリデバイスへ書き込みデータを接続する方法であって、

複数のそれぞれの書き込み要求のための前記書き込みデータを、複数の書き込みデータバス端子を介して前記メモリデバイスへ接続することと、

前記書き込み要求のうちの一つのための前記書き込みデータを前記バンクのうちの一つへ接続し、同時に、前記書き込み要求のうちの他の一つのための前記書き込みデータを前記バンクのうちの他の一つへ接続することと、

を含み、

前記書き込み要求のうちの一つのための前記書き込みデータを前記バンクのうちの一つへ接続し、同時に、前記書き込み要求のうちの他の一つのための前記書き込みデータを前記バンクのうちの他の一つへ接続することと、

前記書き込み要求のうちの一つのための前記書き込みデータ、及び、前記書き込み要求のうちの他の一つのための前記書き込みデータを、該書き込みデータの受け取り時に該書き込みデータをメモリセルの前記バンクへ接続せずに、前記メモリデバイス内の書き込みバッファに保持することと、

前記書き込み要求のうちの一つのための前記保持された書き込みデータを前記バンクのうちの一つへ接続し、同時に、前記書き込み要求のうちの他の一つのための前記保持された書き込みデータを前記バンクのうちの他の一つへ接続することと、

を含むことを特徴とする方法。

**【請求項 3 8】**

前記バンクのうちの一つへ前記書き込みデータを接続し、同時に、前記バンクのうちの他の一つへ書き込みデータを接続する前記動作は、第一の内部書き込みデータバスを介して前記バンクのうちの一つへ前記書き込みデータを接続することと、第二の内部書き込みデータバスを介して前記バンクのうちの他の一つへ前記書き込みデータを接続することと、を含む、ことを特徴とする請求項 3 7 に記載の方法。

**【請求項 3 9】**

読み出しデータを前記バンクのうちの他の一つから接続し、同時に、前記バンクのうちの一つ又は他の一つへ前記書き込みデータを接続することを更に含む、ことを特徴とする請求項 3 8 に記載の方法。

**【請求項 4 0】**

読み出しデータを前記バンクのうちの他の一つから接続し、同時に、前記バンクのうちの一つ又は他の一つへ前記書き込みデータを接続する前記動作は、前記第一及び第二の内部書き込みデータバスから絶縁されている内部読み出しデータバスを介して前記バンクのうちの前記他の一つから前記読み出しデータを接続することを含む、ことを特徴とする請求項 3 9 に記載の方法。

**【請求項 4 1】**

前記バンクのうちの他の一つから読み出しデータを接続し、同時に、前記バンクのうちの一つ又は他の一つへ書き込みデータを接続することを更に含む、ことを特徴とする請求項 3 7 に記載の方法。

**【請求項 4 2】**

前記メモリデバイスはダイナミックランダムアクセスメモリデバイスを含む、ことを特徴とする請求項 3 7 に記載の方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

**〔関連する出願への相互参照〕**

本出願は、ここで参照されている 2005 年 2 月 23 日に提出された「MEMORY DEVICE AND METHOD HAVING MULTIPLE INTERNAL DATA BUSES AND MEMORY BANK INTERLEAVING」という表題の U.S. Patent Application No. 11/064543 の提出日の利益を主張する。

**【0 0 0 2】**

10

20

30

40

50

**【技術分野】**

本発明は、メモリシステムに関し、より詳細には、メモリコントローラ及び一つ以上のメモリデバイスとの間のコマンド、アドレス、データ信号を接続するためのシステム及び方法に関する。

**【背景技術】****【0003】**

コンピュータシステムは、プロセッサによってアクセスされるデータを格納するため、ダイナミックランダムアクセスメモリ（DRAM）デバイスのようなメモリデバイスを使用する。このDRAMデバイスは、通常コンピュータシステムの中でシステムメモリとして使用される。典型的なコンピュータシステムでは、プロセッサバス及びメモリコントローラを介して、プロセッサはシステムメモリと通信する。システムメモリは典型的に、それぞれが複数のメモリデバイスを有するメモリモジュールとして備えられ、メモリモジュールはメモリバスを介してメモリコントローラへ接続される。プロセッサは、読み出しコマンドのようなメモリコマンドを含むメモリ要求を発し、また、データまたは指示が読み出されるべき、或いはデータまたは指示が書き込まれるべき位置を示すアドレスを発する。メモリコントローラは、ロウ及びカラムアドレスと同様に適切なコマンド信号を発生するために、コマンド及びアドレスを使用し、それらはメモリバスを介してシステムメモリへと適用される。コマンド及びアドレスに応じて、データはシステムメモリ及びプロセッサの間を伝送される。メモリコントローラは、たいていシステムコントローラの一部であり、プロセッサバスを、PCIバスのような拡張バスに接続するためのバスブリッジ回路を含んでいる。

10

**【0004】**

データのバンド幅が高いことは、メモリシステムの望ましい特性である。一般的には、バンド幅の限界はメモリコントローラには関係がない。なぜなら、メモリコントローラはメモリデバイスの許す限りできるだけ早く、システムメモリから、及びシステムメモリへ一連のデータを制御するからである。バンド幅を増加させる一つの方法は、メモリコントローラをメモリデバイスへ接続するメモリデータバスの速度を増加させることである。しかしながら、メモリデバイスはメモリコントローラ及びメモリデータバスのデータバンド幅の増加についていくことができない。特に、メモリコントローラはメモリデバイスがコマンドに対応できるような方法で、メモリデバイスへの全てのメモリコマンドを計画しなければならない。このハードウェアの限界がメモリデバイスの設計を通してある程度低減できても、ハードウェアの限界を低減することは一般的にはコスト、労力、及び／またはメモリデバイスのサイズを増加させることになるため、これらは全て望ましくない選択肢であり、妥協がされなければならない。メモリデバイスは、いかに増加した速度においても、たとえばメモリデバイスの同一ページに対する連続した通信のような、規則正しいアクセスをすばやく処理することができる一方、メモリデバイスにとって、メモリデバイスの異なるページに対するアクセスのような規則正しくない通信を解決するのは大変困難である。結果として、メモリデータバスのバンド幅の増加は対応するメモリシステムのバンド幅の増加という結果にならない。

20

**【0005】**

メモリシステムのバンド幅を増加する一つの方法は、バンクインターリービングを使用することである。バンクインターリービングでは、一つのバンクへデータが書き込まれている、或いは一つのバンクからデータが読み込まれている間に、他のメモリバンクのデータにアクセスするための準備がなされるように、二つ以上のメモリバンクが同時にアクセスされる。メモリシステムのバンド幅は、この方法を使用することで増加しうる。なぜなら、データがメモリデバイスへ、またはメモリデバイスから接続される前に、プレチャージが完了するようなメモリアクセスの準備を待つ必要がないためである。しかしながら、メモリの複数のバンクから同時に読み出す、或いは複数のバンクへ同時に書き込むことができないために、バンクインターリービングによってなされるメモリのバンド幅の改良は制限される。一つのバンクからデータを読み出している或いは一つのバンクへデータを書

30

40

50

き込んでいる際に、他のバンクからデータを読み出す或いは他のバンクへデータを書き込むための準備がなされるとき、一つのバンクへのアクセスが完了するまでは、他のバンクからの読み出しデータ或いは他のバンクへの書き込みデータを接続することは実際には不可能である。

【0006】

バンクインターリービングと類似点のあるメモリのバンド幅を増加させる方法は、メモリデバイスのインターリービングである。メモリデバイスのインターリービングでは、異なるメモリデバイスが同時にアクセスされる。結果として、データが一つのメモリデバイスから読み出されている、或いは一つのメモリデバイスに書き込まれているときに、他のメモリデバイスにアクセスするための準備をすることができる。バンクインターリービングがメモリのバンド幅を増加させるのと類似した方法で、メモリデバイスのインターリービングがメモリのバンド幅を増加させると、本質的には同じ制限を受ける。特に、一つのメモリデバイスから、或いは一つのメモリデバイスへのデータの伝送が完了するまで、実際には他のメモリデバイスへの書き込みデータ、及び他のメモリデバイスからの読み出しデータを接続することができない。

【0007】

メモリデバイスのバンド幅の制限に加えて、コンピュータシステムの性能は、メモリデバイスからデータを読み出すために必要な時間を増加させるレイテンシー問題によっても制限される。具体的には、メモリデバイスの読み出しコマンドが、シンクロナスDRAM (SDRAM) のようなシステムメモリデバイスに接続されるとき、読み出しデータは数クロックの遅延が生じるまで SDRAM デバイスから出力されることができない。SDRAM デバイスは高いデータレートでバーストデータを同時に出力することができるが、初めにデータを供給する際の遅延は、SDRAM のようなデバイスを使用するコンピュータシステムの動作速度を著しく遅らせる。これらのレイテンシー問題は一般的には、単にメモリのデータバス幅を増加させることによってでは、意味のある程度に緩和することはできない。

【0008】

メモリのレイテンシー問題は、読み出し / 書き込みターンアラウンドとして知られている、読み出しアクセスと書き込みアクセスとが交互に起こることによって非常に悪化する。メモリコントローラがメモリデバイスへの読み出しコマンドを発するとき、メモリデバイスは、メモリアレイからの読み出しデータをメモリデバイスの外部データバス端子へと接続させなければならない。そのとき、読み出しデータはメモリバスのデータバス部分を介して、メモリデバイスからメモリコントローラへ接続されなければならない。メモリコントローラが、書き込みメモリアクセスを始めるために、データバスを介して書き込みデータをメモリデバイスに接続できるのはこのときだけである。

【0009】

ページを開くことは、メモリコントローラからメモリデバイスへ、メモリコマンド、ロウアドレス及びカラムアドレスを接続する必要がある。読み出しアドレスに応じて、メモリデバイスは、そのロウのアクセストランジスタをオンにして、対応するロウを均衡に保たなければならず、また、それぞれのメモリセルがセンスアンプへ接続する電圧を、それぞれのカラムのセンスアンプがセンスすることを許容する。この全ては、かなりの時間を必要としうる。この理由のため、閉じられたページからの読み出し動作や読み出し / 書き込みターンアラウンドは、メモリデバイスが、高速メモリコントローラ及びメモリバスによって可能となるデータバンド幅を達成しようとするふうを妨げうる。

【0010】

ゆえに、より高いデータバンド幅を達成することを許容するメモリデバイス及びメモリシステムが必要となる。

【発明の開示】

【0011】

メモリシステムは、メモリコントローラを一つ以上のメモリデバイスへ接続する二つの

10

20

30

40

50

個別のデータバスの使用を介して、高いバンド幅及び低いレイテンシーを達成することができる。下流バス（下りバス）は、書き込みデータをメモリコントローラからそれぞれのメモリデバイスへと接続し、上流バス（上りバス）は読み出しデータをそれぞれのメモリデバイスからメモリコントローラへ接続する。結果として、書き込みデータがメモリコントローラからそれぞれのメモリデバイスへ接続されうるのと同時に、読み出しデータは、それぞれのメモリデバイスからメモリコントローラへ接続されうる。下流メモリバスは、書き込みデータとともに、メモリコマンド及びメモリアドレスをそれぞれのメモリデバイスへ接続するために使用される。それぞれのメモリデバイスは、書き込みデータを異なるメモリバンクへ同時に移動させる二つの内部書き込みデータバスを含んでいる。それに加えて、或いはそれに代えて、それぞれのメモリデバイスは、読み出しデータを異なるメモリバンクから同時に移動させる二つの内部読み出しデータバスを含んでいる。更に、読み出しデータが異なるバンクから読み出しデータバスへ移動させられるのと同時に、書き込みデータバスは書き込みデータを異なるバンクへと移動させてもよい。

【発明を実施するための最良の形態】

【0012】

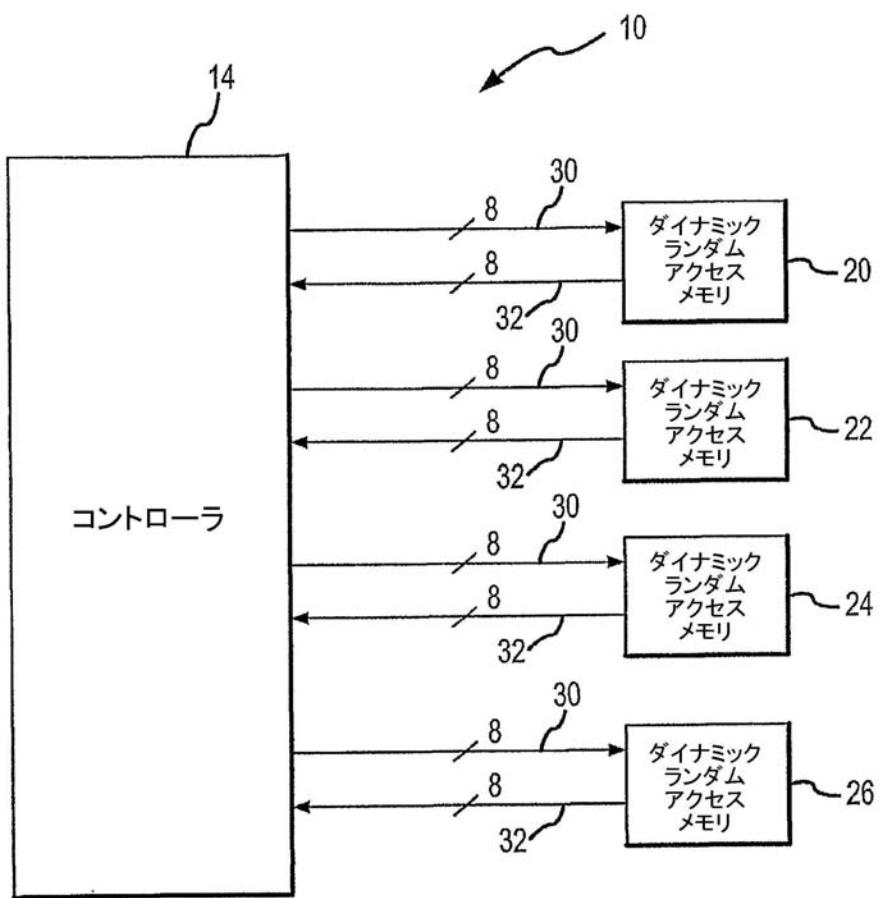

本発明の一例に係るメモリシステム10は、図1に示されている。メモリシステム10は、4つのダイナミックランダムアクセスメモリ（DRAM）デバイス20、22、24、26に接続されているメモリコントローラ14を含んでいる。メモリコントローラ14は、それぞれのDRAMデバイス20-26に、8ビット書き込みデータバス30、及び8ビット読み出しデータバス32によって接続されている。メモリコントローラ14は、メモリコマンド及びメモリアドレスを、書き込みデータバス30か、個別のコマンド／アドレスバス（示されていない）か、或いは個別のコマンド及びアドレスバス（示されていない）のいずれかを介して、DRAMデバイス20-26へと「下流方向（下り方向）」に接続する。メモリコマンド及びメモリアドレスが下流バスを介して接続される場合、これらのコマンド及びアドレスは、書き込みコマンドのためならば書き込みデータをも含むようなパケットの形でもよい。

【0013】

動作の際、メモリコントローラ14は、書き込みデータバス30を介して、書き込みデータをDRAMデバイス20-26へと「下流方向（下り方向）」に接続し、DRAMデバイス20-26は、読み出しデータバス32を介して、読み出しデータをメモリコントローラ14へと「上流方向（上り方向）」に接続する。書き込みデータバス30のバンド幅は読み出しデータバス32のバンド幅と同じでもよい。或いは、書き込みデータバス30及び読み出しデータバス32は、これらのバス30、32を介して異なるデータレートを収めるために、異なるバンド幅を有してもよい。個別の書き込み及び読み出しデータバス30、32をそれぞれ使用することによって、メモリデバイス20-26がメモリコントローラ14へ読み出しデータを接続するのと同時に、メモリコントローラ14がDRAMデバイス20-26へ書き込みデータを接続することが可能である。

【0014】

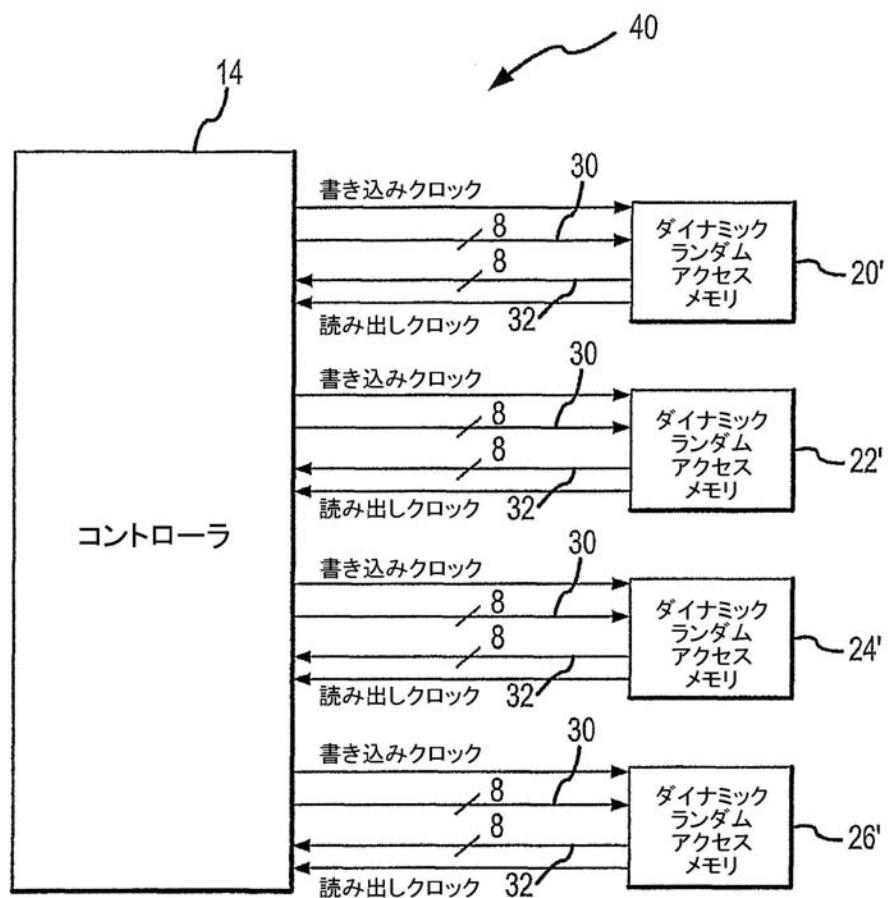

本発明の別の例に係るメモリシステム40は、図2に示されている。図2のメモリシステム40は、図1のメモリシステム10とほぼ同一である。ゆえに、簡潔のため、両方のメモリシステム10、40に共通の構成要素には、同一の参照番号が与えられ、それらの構造及び動作の説明は繰り返さない。メモリシステム40は、クロック信号に同期して動作する、シンクロナスDRAM（SDRAM）デバイス20'-26'を使用することが、図1のメモリシステム10とは異なっている。図2のメモリシステム40では、メモリコントローラ14はそれぞれの書き込みデータとともに、SDRAMデバイス20'-26'のそれぞれに書き込みクロック（WCLK）信号を接続する。WCLK信号は、書き込みメモリアクセスが向けられているSDRAMデバイス20'-26'において、書き込みデータを収集するために使用される。図2のメモリシステム40では、WCLK信号は、対応する書き込みデータが有効である期間のほぼ中間で起こる遷移を有する。SDRAMデバイス20'-26'は、書き込みデータがWCLK信号の立ち上がり端、及び立

10

20

30

40

50

ち下がり端の両方に反応してラッチされる、ダブルデータレート(DDR)デバイスでもよい。しかしながら、WCK信号の位相及び遷移回数と書き込みデータの間の他の関係が使用されてもよい。

#### 【0015】

同様の方法で、それぞれのSDRAMデバイス20' - 26'は、読み出しデータがSDRAMデバイス20' - 26'からメモリコントローラ14へ接続されるとき、読み出しクロック(RCLK)信号をメモリコントローラ14へ接続する。RCLK信号はメモリコントローラ14によって読み出しデータを収集するために使用される。図2のメモリシステム40では、RCLK信号は、対応する読み出しデータが有効である期間のほぼ開始及び端で起こる遷移を有する。SDRAMデバイス20' - 26'は、ダブルデータレート(DDR)デバイスであるため、読み出しデータは、RCLK信号の立ち上がり端及び立下り端の両方に反応してメモリコントローラ14にラッチされる。更に、RCLK信号は読み出しデータの遷移回数及び位相との他の関係を有してもよい。

10

#### 【0016】

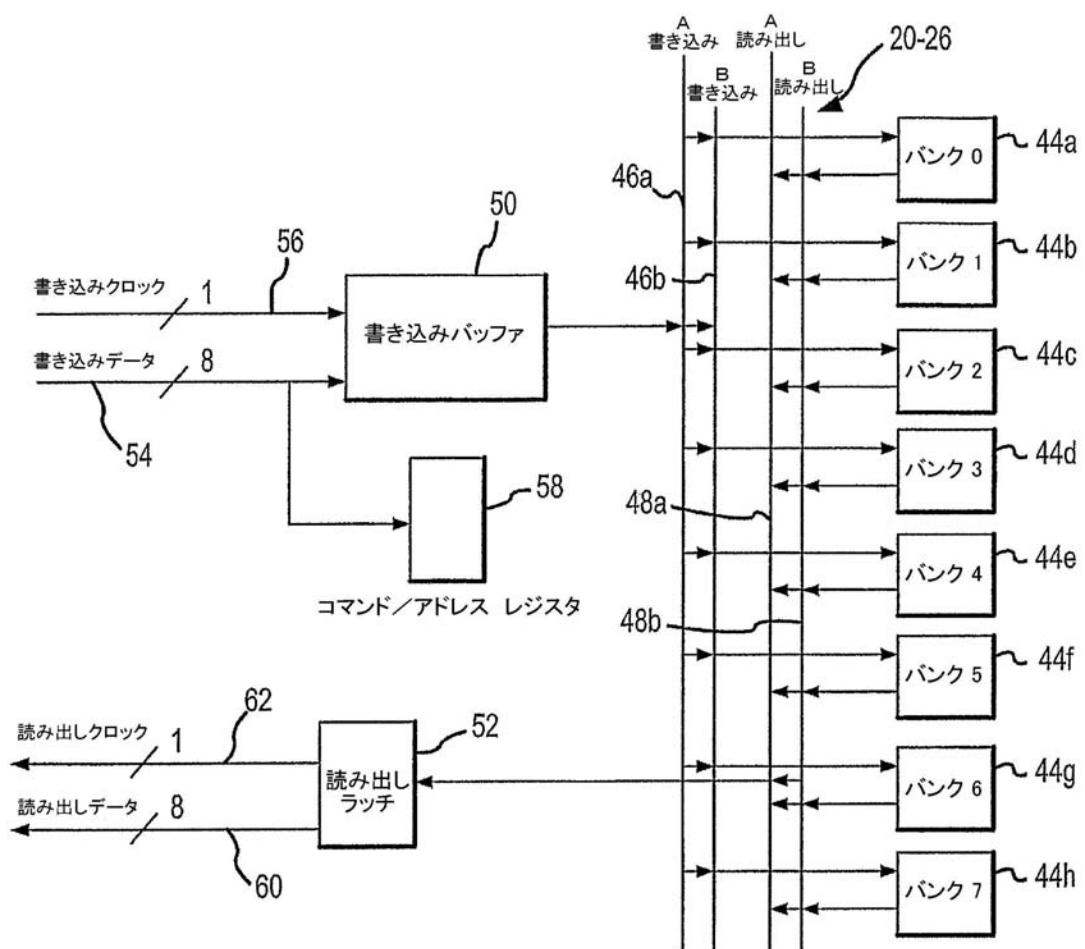

SDRAMデバイス20' - 26'の一部分が図3により詳細に示されている。それぞれのDRAMデバイス20' - 26'は、それぞれが一対の内部書き込みデータバス46a、b及び内部読み出しデータバス48a、bに接続されている8つのメモリバンク44a - hを含んでいる。書き込みデータバス46a、bは書き込みバッファ50から書き込みデータを受け取り、読み出しデータバス48a、bは読み出しラッチ52へと読み出しデータを接続する。書き込みデータは書き込みデータバス54を介して書き込みバッファ50へ接続され、ライン56を介して接続されるクロック信号によってバッファ50へラッチされる。メモリコマンド及びアドレスもまた、書き込みデータバス54を介して接続され、それらはコマンド/アドレスレジスタ58に格納される。

20

#### 【0017】

読み出しラッチ52は、ライン62に読み出しラッチ52からもまた接続されているクロック信号に同期して、8ビット読み出しデータバス60へと読み出しデータを出力する。メモリデバイス20' - 26'は、多くの他の従来のメモリデバイスの構成要素を含んでいるが、これらは簡潔性及び明快性のために図3では省略されている。

#### 【0018】

動作の際、メモリアドレスと同様に、書き込みコマンド及び読み出しコマンドのようなメモリコマンドは、書き込みデータバス54を介して接続される。メモリコマンド及びアドレスは、コマンド/アドレスレジスタ58に格納される。書き込みデータもまた、書き込みデータバス54を介して接続されて書き込みバッファ50に格納される。コマンド/アドレスレジスタ58に接続された読み出しコマンドに応じて、メモリデバイス20' - 26'は、読み出しラッチ52に接続されている読み出しデータを出力する。読み出しラッチ52は、読み出しデータバス60及びメモリコントローラ14(図1)が読み出しデータを受け取ることが可能になるまで、読み出しデータを格納する。続いて読み出しデータは、読み出しデータバス60を介して、読み出しラッチ52から一定間隔で出力される。書き込みデータが書き込みバッファ48に収められている間に多くの書き込みコマンド及び関連するアドレスがコマンド/アドレスレジスタ58に格納されるように、読み出しメモリアクセスは望ましくは書き込みメモリアクセスよりも優先的である。十分な数の書き込みアクセスが蓄積したとき、それらは読み出しアクセスを妨げることなく連続して処理されうる。結果として、読み出し/書き込みターンアラウンドに固有のレイテンシーペナルティは避けられる。

30

#### 【0019】

二つの書き込みデータバス46a、bの使用によって、書き込みデータをバンク44a - hのうちの一つに接続させるのと同時に、書き込みデータをバンク44a - hのうちの他の一つに接続することが可能となる。同様に、二つの読み出しデータバス48a、bの使用によって、読み出しデータをバンク44a - hのうちの一つから接続させるのと同時に、読み出しデータをバンク44a - hのうちの他の一つから接続することが可能となる

40

50

。更に、読み出しデータをバンク 44a - h のうちの一つから接続するのと同時に、書き込みデータをバンク 44a - h のうちの他の一つに接続することが可能となる。更に、読み出しデータが 44a - h のうちの二つの異なるバンクから同時に接続されるのと同時に、書き込みデータを 44a - h のうちの二つのバンクに同時に接続することが可能となる。データ接続の他の組み合わせも、この技術に熟練した者にとって明白であろう。結果として、以下に詳細に説明するように、バンクインターリービングがメモリデバイス 20 - 26において同時に実現されてもよい。読み出しコマンドが書き込みバス 54 を介して接続され、コマンド／アドレスレジスタ 58 に格納されることを許容することによって、読み出しコマンドは、書き込み或いは読み出し動作の間、メモリデバイス 20 - 26 へ接続されうる。結果として、読み出し動作のレイテンシーは最小化される。もしそうでなければ、読み出しコマンドが送られる前に書き込み動作が完了するのを待つ必要が生じるであろう。10

#### 【0020】

WCLK 信号がライン 56 を介して書き込みバッファ 50 へ接続されず、RCLK 信号がライン 62 を介して読み出しラッチ 52 から接続されないことを除いて、DRAM デバイス 20 - 26 のそれぞれは、図 3 に示された SDRAM デバイス 20' - 26' と実質的には同一である。

#### 【0021】

本発明の一つの具体例においては、メモリコントローラ 14 (図 1) は、メモリデバイス 20 - 26 及び 20' - 26' へと読み出し及び書き込みメモリコマンド及びアドレスを単に発する。メモリデバイス 20 - 26 及び 20' - 26' がそれらを処理できるまで、メモリコマンドは、コマンド／アドレスレジスタ 58 に格納される。コマンドは続いてメモリデバイス 20 - 26 及び 20' - 26' のそれぞれによって処理される。メモリデバイス 20 - 26 及び 20' - 26' は、読み出しデータバス 60 を介してメモリコントローラ 14 へと読み出し応答或いは書き込み応答をもまた、接続する。読み出し応答及び書き込み応答は、対応するメモリ要求の処理が完了したことをメモリコントローラ 14 に示す。メモリコントローラ 14 がメモリ要求の足跡を保持する必要がないように、また、メモリ要求は順序 通に 処理されなくてもいいように、その応答は、それに対応するメモリ要求を一意に識別 する。読み出し応答の場合には、この 読み出し応答もまた、対応する読み出し要求の結果となる読み出しデータを含んでも良い。20

#### 【0022】

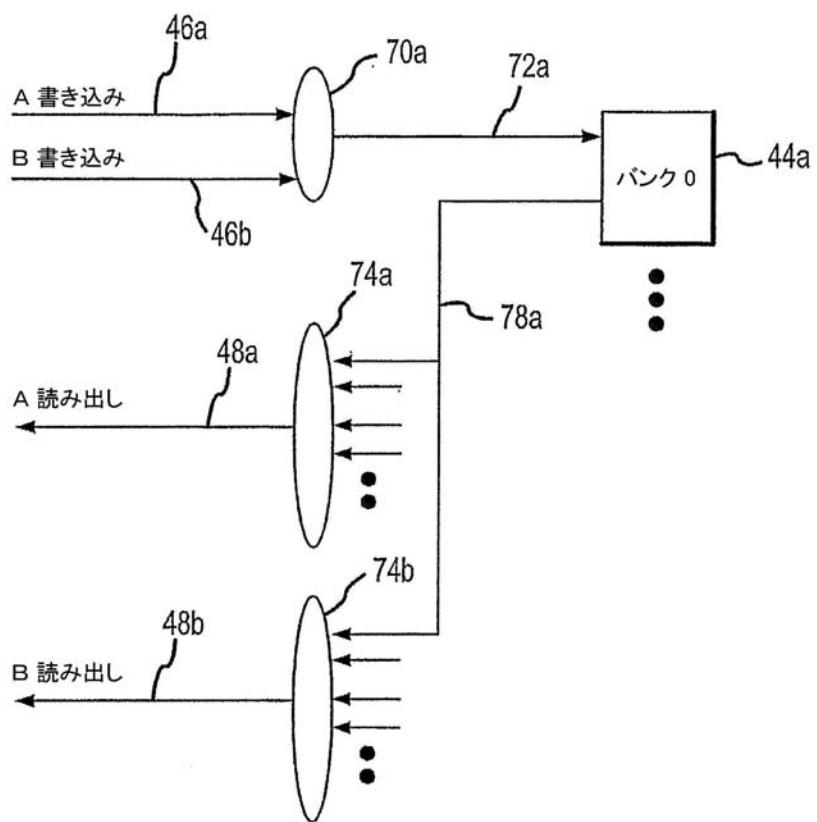

バンク 44a - h を内部書き込みデータバス 46a、b 及び内部読み出しデータバス 48a、b へと接続するための回路の一例が図 4 に示されている。内部書き込みデータバス 46a、b はマルチプレクサ 70a のそれぞれの入力に接続される。図 4 には示されていないが、70a - h のうちのそれぞれのマルチプレクサは、バンク 44a - h のそれぞれに与えられて、70a - h の全てのマルチプレクサは、内部書き込みデータバス 46a、b の両方に接続される入力を有する。70a - h のマルチプレクサのそれぞれは、単一のそれぞれのバンク書き込みバス 72a - h を介して、それぞれのバンク 44a - h へと接続された出力を有する。内部書き込みデータバス 46a、b のどちらかがバンク 44a - h のいずれかに接続されうるよう、70a - h のマルチプレクサは、制御信号 (図 4 には示されていない) によって操作される。30

#### 【0023】

書き込みデータバス 46a、b がバンク 44a - h へと接続されるのとは多少異なる方法で、内部読み出しデータバス 48a、b はバンク 44a - h へと接続される。二つのマルチプレクサ 74a、b のそれぞれは、内部読み出しデータバス 48a、b のうちの一つにそれぞれ接続された出力を有する。マルチプレクサ 74a、b の対応する入力は、お互いに、及び、単一のバンク読み出しバス 78a - h によってバンク 44a - h の一つにそれぞれ接続される。このように、マルチプレクサ 74a - b のそれぞれへの入力は、バンク 44a - h のそれぞれに供給される。どのバンク 44a - h が内部読み出しデータバス 48a、b のいずれに接続されてもよいように、マルチプレクサ 74a - b は制御信号 (図 4 には示されていない) によって操作される。40

図4には示されていない)によって操作される。

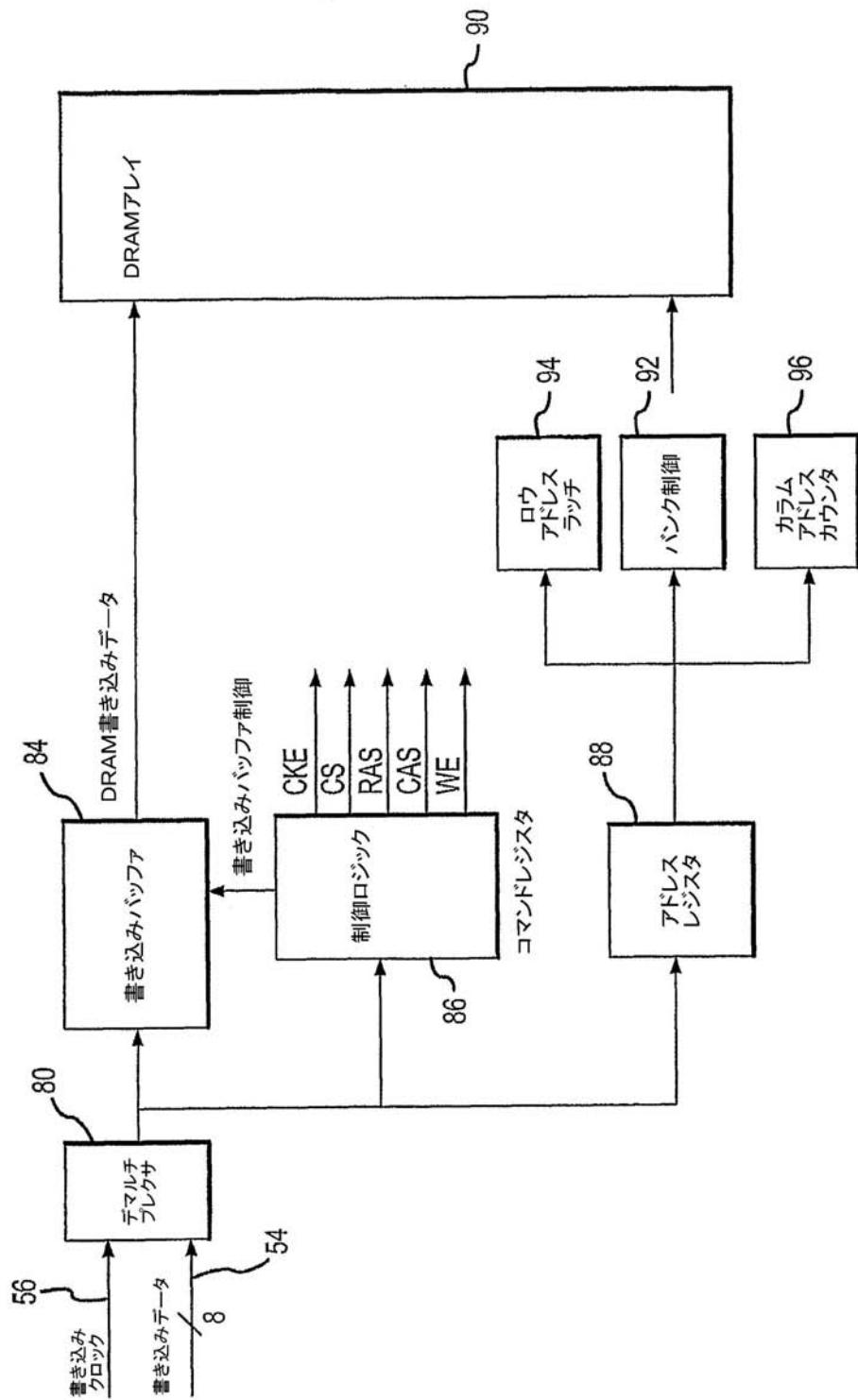

【0024】

図3に示されたSDRAMデバイス20' - 26'の回路の一部分は図5に詳細に示される。書き込みデータバス54及びクロックライン56はデマルチプレクサ80のそれぞれの入力に接続され、このデマルチプレクサ80は、書き込みデータを書き込みバッファ84へと伝送し、メモリコマンドをコマンドレジスタ86に伝送し、メモリアドレスをアドレスレジスタ88に伝送する。コマンドレジスタ86は、メモリコマンドをデコードし、かつ、それに対応する制御信号を出力する制御ロジックを含み、それら制御信号のいくつかは図5に示されている。書き込みバッファ84は、一回以上の書き込みメモリアクセスのために書き込みデータを格納し、続いてコマンドレジスタ86の制御ロジックから出力される制御信号によって決定される適切な時間に、書き込みデータをDRAMアレイ90へと接続する。DRAMアレイ90は、図3に示されている、二つの内部書き込みデータバス46a、b、二つの内部読み出しデータバス48a、b及びバンク44a - hを含んでいる。DRAMアレイ90は、図4に示されているマルチプレクサ70a - h及び74a、bもまた含んでいる。このように、書き込みバッファ84からの書き込みデータは、バンク44a - hへと接続される。連続した書き込みアクセスのための書き込みデータは、望ましくは、両方の書き込みアクセスからの書き込みデータが同時に格納されうるように、異なるバンク44a - hへと接続される。

【0025】

アドレスレジスタ88は、メモリコマンド及び(書き込み要求の場合には)書き込みデータと共に書き込みデータバス54を介して接続されるメモリアドレスを格納する。アドレスレジスタ88は、バンクアドレスに対応するアドレスビットをバンク制御回路92へ、ロウアドレスに対応するアドレスビットをロウアドレスラッチ94へ、カラムアドレスに対応するアドレスビットをカラムアドレスカウンタ96へと接続する。バンク制御回路92は、書き込みデータ或いは読み出しデータがバンク44a - hのうちの選択された一つへ、或いはそのうちの一つから接続されるようにし、ラッチ94に格納されたロウアドレスは、上記選択されたバンク44a - hにおける対応するロウを開放する。カウンタ96に与えられたカラムアドレスは、内部カウンタの最初のカウントを設定し、続いてこの最初のカウントは選択されたバンク44a - hへと出力される。

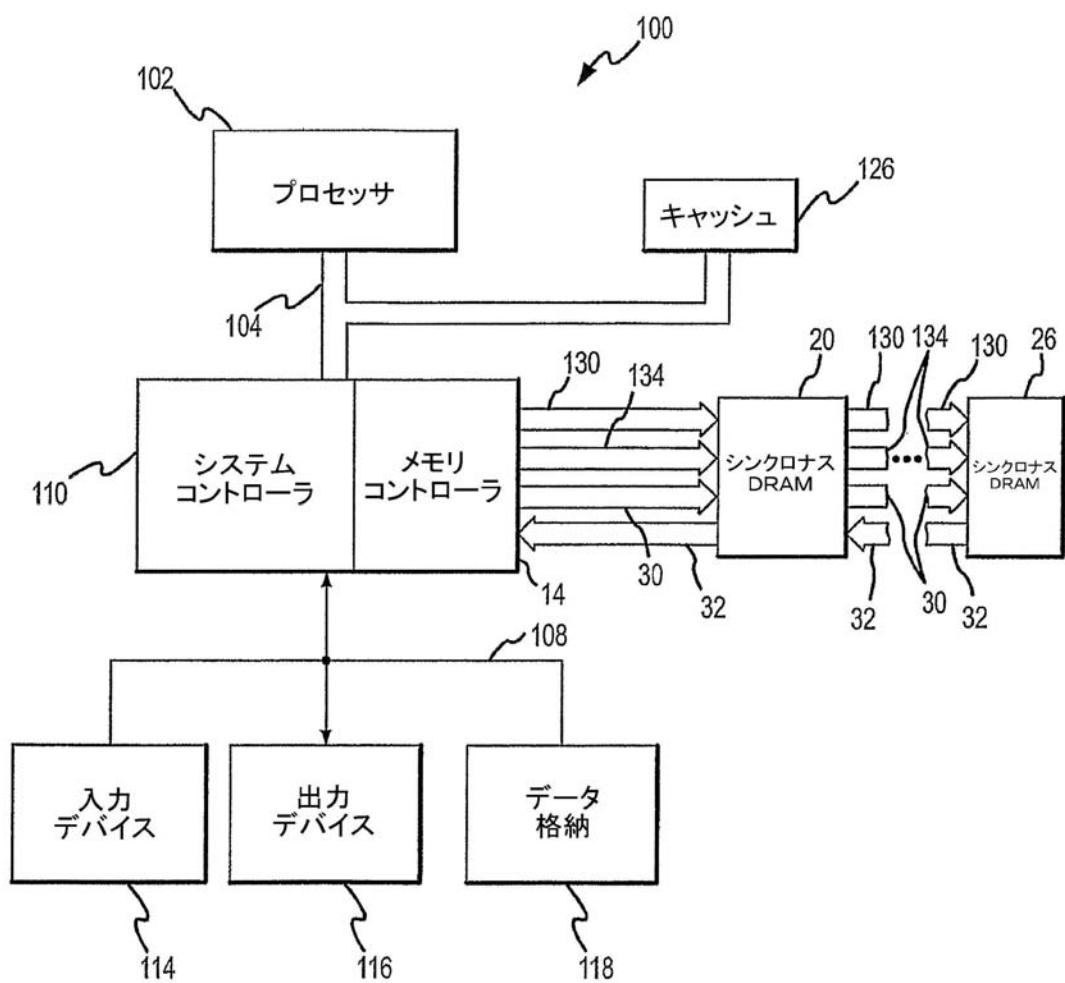

【0026】

図1のメモリシステム10、図2のメモリシステム40、或いは本発明の他の例に係るメモリシステムを使用したコンピュータシステム100は図6に示されている。コンピュータシステム100は、特定の計算或いはタスクを行うための特定のソフトウェアを実行するような、様々なコンピュータ機能を実行するためのプロセッサ102を含んでいる。プロセッサ102は、通常アドレスバス、制御バス、及びデータバスを含んでいるプロセッサバス104を含んでいる。プロセッサバスは、システムコントローラ110を介して、周辺装置要素相互連結(PCCI)バスのような拡張バス108に接続される。コンピュータシステム100は、オペレータがコンピュータシステム100とインターフェイスできるように、拡張バス108、システムコントローラ110、及びプロセッサバス104を介してプロセッサ102に接続された、キーボード或いはマウスのような一つ以上の入力デバイス114を含んでいる。典型的には、コンピュータシステム100は、拡張バス108に接続されている一つ以上の出力デバイス116も含み、典型的には出力デバイスはプリンタやビデオ端子である。外部記憶媒体(示されていない)からのデータを格納或いは取り出すために、一つ以上の大規模データ格納デバイス118もまた典型的には拡張バス108に接続される。典型的な大規模データ格納デバイス118の例は、ハード及びフロッピーディスク、テープカセット、及びコンパクトディスクドライブオンリーメモリ(CD-ROM)を含む。典型的には、プロセッサ102は、通常、スタティックランダムアクセスメモリ(SRAM)であるキャッシュメモリ126にもまた、接続されている。上述したように、コンピュータシステム100は、メモリシステム10或いは40のようなメモリシステムもまた含んでいる。より具体的には、システムコントローラ110は

10

20

30

40

50

メモリコントローラ 14 を含んでいる。メモリコントローラ 14 は、図 1 及び図 2 を参照して上記で説明したように、いくつかの D R A M デバイス 20 - 26 或いは 20' - 26' に接続されている。メモリコントローラ 14 は、コマンドバス 130 及びアドレスバス 134、並びに書き込みデータバス 30 及び読み出しデータバス 32を介して、それぞれの D R A M デバイス 20 - 26 或いは 20' - 26' に接続されている。

#### 【0027】

本発明は、開示された具体例を参照して説明されたが、当業者であれば、本発明の趣旨及び範囲から外れることなく、形状や細部において変形がなされてもよいことを認めるであろう。このような変更は、十分に当業者の技術の範囲内である。更に、本発明は添付された請求項以外では制限されることはない。

10

#### 【図面の簡単な説明】

#### 【0028】

【図 1】図 1 は、本発明の一例に係るメモリシステムのブロック図である。

【図 2】図 2 は、本発明の別の例に係るメモリシステムのブロック図である。

【図 3】図 3 は、図 1 及び図 2 のメモリシステムで使用されるダイナミックランダムアクセスメモリデバイスの一部のブロック図である。

【図 4】図 4 は、図 3 のメモリデバイスのメモリバンクと二つの書き込み及び読み出しデータバスの間の接続の一例を示す概要図である。

【図 5】図 5 は、図 3 のメモリデバイスに接続された書き込みデータバスからのコマンド及びアドレス信号を獲得するための一例を示すブロック図である。

20

【図 6】図 6 は、図 1 或いは図 2 或いは本発明の他の例のメモリシステムを使用するコンピュータシステムのブロック図である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

審査官 野田 佳邦

(56)参考文献 特開2000-215659 (JP, A)

特開2002-063791 (JP, A)

特開2004-362760 (JP, A)

特開2003-007062 (JP, A)

特開平06-060650 (JP, A)

特開平07-134895 (JP, A)

特開2003-297085 (JP, A)

特開平02-025958 (JP, A)

特表2003-514314 (JP, A)

特開平05-217365 (JP, A)

特開2002-117679 (JP, A)

特開2004-348916 (JP, A)

特開昭61-260349 (JP, A)

特表2008-511904 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 12/00-12/06

G06F 13/16-13/18

G11C 11/401