(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5941983号

(P5941983)

(45) 発行日 平成28年6月29日(2016.6.29)

(24) 登録日 平成28年5月27日(2016.5.27)

(51) Int.Cl.

**H01L 21/3205 (2006.01)**

**H01L 21/768 (2006.01)**

**H01L 23/522 (2006.01)**

**H01L 25/065 (2006.01)**

**H01L 25/07 (2006.01)**

F 1

H01L 21/88

H01L 25/08

J

C

請求項の数 13 (全 23 頁) 最終頁に続く

(21) 出願番号 特願2014-514618 (P2014-514618)

(86) (22) 出願日 平成24年6月7日(2012.6.7)

(65) 公表番号 特表2014-517537 (P2014-517537A)

(43) 公表日 平成26年7月17日(2014.7.17)

(86) 國際出願番号 PCT/US2012/041247

(87) 國際公開番号 WO2012/170625

(87) 國際公開日 平成24年12月13日(2012.12.13)

審査請求日 平成27年6月5日(2015.6.5)

(31) 優先権主張番号 13/156,609

(32) 優先日 平成23年6月9日(2011.6.9)

(33) 優先権主張国 米国(US)

(73) 特許権者 504142411

テッセラ、インコーポレイテッド

アメリカ合衆国 カリフォルニア州 95

134, サン・ノゼ、オーチャード・

パークウェイ 3025

(74) 代理人 100099623

弁理士 奥山 尚一

(74) 代理人 100096769

弁理士 有原 幸一

(74) 代理人 100107319

弁理士 松島 鉄男

(74) 代理人 100114591

弁理士 河村 英文

(74) 代理人 100125380

弁理士 中村 純子

最終頁に続く

(54) 【発明の名称】導電性粒子を用いた低応力なシリコン貫通ビアのデザイン

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の面と、該第1の面から離れた第2の面とを有し、熱膨張係数が10 ppm / よりも小さい基板と、

前記第1の面と前記第2の面とを結ぶ方向に延在する開口部と、

前記開口部内に延在している導電性ビアであって、それぞれが、第1の金属とは異なる第2の金属の層で略被覆され、前記第1の金属でできた第1の金属領域を有する複数の基材粒子を含んでおり、前記基材粒子同士は冶金接合されており、前記粒子の前記第2の金属の層は、前記第1の金属領域内に少なくとも部分的に拡散し、該導電性ビアは前記接合された基材粒子同士の間に散在する間隙領域を有し、該間隙領域は、該導電性ビアの体積の10%以上を占める、導電性ビアと

を含んでなり、

それぞれの前記基材粒子は、前記第1の金属領域と前記第2の金属の層との間のバリア層を含む、コンポーネント。

## 【請求項 2】

前記接合された基材粒子同士の間に散在し、前記導電性ビアの体積の10%以上を占める前記間隙領域は、空気で充填されている、請求項1に記載のコンポーネント。

## 【請求項 3】

前記接合された基材粒子同士の間に散在し前記開口部内で前記第1の面及び前記第2の面のうちの少なくとも一方から少なくとも貫入深さまで延在するポリマー媒体を更に含む

10

20

、請求項 1 に記載のコンポーネント。

**【請求項 4】**

前記接合された基材粒子同士の間に散在し前記開口部内で前記第 1 の面及び前記第 2 の面のうちの少なくとも一方から少なくとも貫入深さまで延在するはんだを更に含む、請求項 1 に記載のコンポーネント。

**【請求項 5】**

前記導電性ビアは、導電性パッドと電気的に接続された前記基板内の第 2 の導電性ビアに接続しており、前記第 2 のビアは不純物をドープされた半導体材料を含む、請求項 1 に記載のコンポーネント。

**【請求項 6】**

前記第 2 の金属の層のうちの少なくともいくつかの部分は、溶融温度が前記第 1 の金属領域よりも低い、請求項 1 に記載のコンポーネント。

**【請求項 7】**

前記導電性ビアのヤング率は、最大で前記ビアに含まれる前記第 1 の金属及び前記第 2 の金属のヤング率の 50 % である、請求項 1 に記載のコンポーネント。

**【請求項 8】**

前記基材粒子のうちの少なくともいくつかは、前記第 1 の金属領域に囲まれた非金属の核領域を更に有する、請求項 1 に記載のコンポーネント。

**【請求項 9】**

それぞれの前記基材粒子の前記第 1 の金属領域は、厚さが前記基材粒子の前記第 2 の金属の層の厚さよりも厚い、請求項 8 に記載のコンポーネント。

**【請求項 10】**

コンポーネントを製造する方法であって、

第 1 の面と、該第 1 の面から離れた第 2 の面とを有する基板を準備するステップであつて、該基板は熱膨張係数が 10 ppm / よりも小さく、該基板は前記第 1 の面から前記第 2 の面に向かって延在する開口部を有する、準備するステップと、

前記開口部内に複数の基材粒子を堆積させるステップであって、それぞれの基材粒子は、第 1 の金属領域と、該第 1 の金属領域を被覆する第 2 の金属層とを含み、該第 2 の金属層は融点が 400 よりも低く、前記第 1 の金属領域は融点が 500 以上である、堆積させるステップと、

それぞれの前記第 2 の金属層が前記基材粒子を溶融して互いと一体にして前記開口部内に延在する連続的な導電性ビアを形成するように、前記基材粒子を加熱するステップであつて、前記導電性ビアは、前記接合された基材粒子同士の間に散在する間隙領域を有し、該間隙領域は前記導電性ビアの体積の 10 % 以上を占める、加熱するステップと

を含んでなり、

それぞれの前記基材粒子は、前記第 1 の金属領域と前記第 2 の金属層との間のバリア層を含む、コンポーネントを製造する方法。

**【請求項 11】**

前記接合された基材粒子同士の間に散在し、前記導電性ビアの体積の 10 % 以上を占める前記間隙領域は、空気で充填されている、請求項 10 に記載の方法。

**【請求項 12】**

前記基材粒子は液体キャリア材料内に設けられており、前記液体キャリア材料は流動性的成分を含む、請求項 10 に記載の方法。

**【請求項 13】**

コンポーネントを製造する方法であって、

第 1 の面と、該第 1 の面から離れた第 2 の面とを有する基板を準備するステップであつて、該基板は熱膨張係数が 10 ppm / よりも小さく、該基板は前記第 1 の面から前記第 2 の面に向かって延在する開口部を有する、準備するステップと、

前記開口部内に複数の基材粒子を堆積させるステップであって、それぞれの基材粒子は、第 1 の金属領域と、該第 1 の金属領域を被覆する第 2 の金属層とを含み、該第 2 の金属

10

20

30

40

50

層は融点が 400 よりも低く、前記第 1 の金属領域は融点が 500 以上である、堆積させるステップと、

それぞれの前記第 2 の金属層が前記基材粒子を溶融して互いと一体にして前記開口部内に延在する連続的な導電性ビアを形成するように、前記基材粒子を加熱するステップであつて、前記導電性ビアは、前記接合された基材粒子同士の間に散在する間隙領域を有し、該間隙領域は前記導電性ビアの体積の 10 % 以上を占める、加熱するステップと

を含んでなり、

前記第 2 の金属層は前記第 1 の金属領域を被覆するバイメタル層であり、前記加熱するステップは、前記基材粒子を転移液相反応温度まで加熱し、それぞれの前記バイメタル層は前記第 1 の金属領域の回りで低融点共晶を形成する、コンポーネントを製造する方法。 10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、超小型電子デバイスのパッケージング、特に半導体デバイスのパッケージングに関する。

【0002】

【関連出願の相互参照】

本出願は、2011年6月9日に出願された米国特許出願第 13 / 156,609 号の継続出願であり、その米国特許出願の開示は本明細書に引用することにより本明細書の一部をなすものとする。 20

【背景技術】

【0003】

超小型電子素子は、一般にダイ又は半導体チップと呼ばれる、シリコン又はガリウムヒ素等の半導体材料の薄いスラブを一般的に備えている。半導体チップは、一般的に、個々の予めパッケージされたユニットとして提供される。いくつかのユニット設計では、半導体チップは基板又はチップキャリアに実装され、その基板又はチップキャリアは更にプリント回路基板（以下、「PCB」（Printed Circuit Board）とよぶ）等の回路パネル上に実装される。

【0004】

半導体チップの第 1 の面（例えば表面）には能動回路が作製される。能動回路との電気的接続を容易にするように、チップは同じ面上にボンドパッドを設けられる。ボンドパッドは通常、ダイのエッジの周囲に、又は多くのメモリデバイスの場合にはダイの中央に、規則的なアレイに配置される。ボンドパッドは一般的に、約 0.5 μm 厚の銅又はアルミニウム等の導電性金属から形成される。ボンドパッドは、単一層又は複数層の金属を含みうる。ボンドパッドのサイズはデバイスタイプによって異なるが、通常は一辺が数十ミクロンから数百ミクロンである。 30

【0005】

シリコン貫通ビア（以下、「TSV」（Through-Silicon Via）とよぶ）を用いて、ボンドパッドが半導体チップの第 1 の面とは反対側の第 2 の面（例えば裏面）に接続される。従来のビアは、半導体チップを貫通するホールと、第 1 の面から第 2 の面までホールを通って延在する導電性材料とを有している。ボンドパッドをビアに電気的に接続することにより、ボンドパッドと半導体チップの第 2 の面の導電性素子との連通を可能にすることができます。 40

【0006】

従来の TSV ホールは、能動回路を含むように使用することができる第 1 の面の部分を低減する可能性がある。このように、能動回路に使用することができる第 1 の面の利用可能な空間が低減することにより、各半導体チップを製造するのに必要なシリコンの量が増大する可能性があり、それにより、各チップのコストが増大する可能性がある。

【0007】

従来のビアには、ビアの内側の非最適な応力分布と、例えば半導体チップとチップが結

10

20

30

40

50

合される構造体との間の熱膨張係数（以下、「C T E」（Coefficient of Thermal Expansion）とよぶ）の不整合とのために、信頼性の問題がある可能性がある。例えば、半導体チップ内の導電性ピアが、比較的薄くかつ堅い誘電材料によって絶縁されている場合、ピア内に著しい応力が存在する可能性がある。さらに、半導体チップがポリマー基板の導電性素子に結合されている場合、チップと基板のC T Eがより高い構造との間の電気的接続が、C T E不整合のために応力を受けることになる。

#### 【0008】

チップのいかなる物理的構成においても、サイズは重要な考慮事項である。チップのより小型の物理的構成に対する要求は、携帯型電子デバイスの急速な発展により、更に強くなっている。単に例として、一般に「スマートフォン」と呼ばれるデバイスは、携帯電話の機能を、強力なデータプロセッサ、メモリ、並びに全地球測位システム受信機、電子カメラ及びローカルエリアネットワーク接続等の補助デバイスを、高解像度ディスプレイ及び関連する画像処理チップと一体化している。このようなデバイスは、完全なインターネット接続、最大解像度の映像を含むエンターテイメント、ナビゲーション、電子銀行等の機能を、全てポケットサイズのデバイスで提供することができる。複雑な携帯型デバイスでは、多数のチップを小さい空間に詰め込む必要がある。さらに、チップのうちのいくつかは、一般に「I / O」と呼ばれる多くの入出力接続を有している。これらのI / Oを、他のチップのI / Oと相互接続しなければならない。相互接続は、短くあるべきであり、信号伝播遅延を最小限にするように低インピーダンスであるべきである。相互接続を形成するコンポーネントは、アセンブリのサイズを大幅に増大させるべきではない。同様の必要性は、例えばインターネット検索エンジンで使用されるもの等のデータサーバにおける用途等の、他の用途でも発生する。例えば、複雑なチップ間に多数の短い低インピーダンス相互接続を提供する構造により、検索エンジンの帯域幅を増大させ、その電力消費量を低減することができる。10 20

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0009】

半導体ピアの形成及び相互接続において上記のような進歩があったが、電気的相互接続の信頼性を向上させつつ半導体チップのサイズを最小にするためには、依然として改善が必要である。本発明のこれらの特徴は、以下に説明する超小型電子パッケージの構造によつて達成することができる。30

#### 【課題を解決するための手段】

#### 【0010】

本発明の一態様によれば、コンポーネントは、第1の面と第1の面から離れた第2の面とを有する基板と、前記第1の面と前記第2の面とを結ぶ方向に延在する開口部と、該開口部内に延在する導電性ピアとを含みうる。前記基板は、C T Eが10 ppm/°よりも小さいものとすることができます。前記導電性ピアは、それぞれが、第1の金属とは異なる第2の金属の層で略被覆された、前記第1の金属でできた第1の領域を有する、複数の基材粒子を含みうる。前記基材粒子同士は冶金接合されることができ、前記粒子の前記第2の金属層は、前記第1の領域内に少なくとも部分的に拡散することができる。前記導電性ピアは、前記接合された基材粒子同士の間に散在する空隙を有することができる。該空隙は前記導電性ピアの体積の10%以上を占めることができる。40

#### 【0011】

特定の実施形態において、上記コンポーネントは、前記接合された基材粒子同士の間に散在し前記開口部内で前記第1の面及び第2の面のうちの少なくとも一方から少なくとも貫入深さまで延在するポリマー媒体も含みうる。一実施形態において、上記コンポーネントは、前記接合された基材粒子同士の間に散在し前記開口部内で前記第1の面及び第2の面のうちの少なくとも一方から少なくとも貫入深さまで延在するポリマー媒体も含みうる。50

#### 【0012】

本発明の他の態様によれば、コンポーネントは、第1の面と第1の面から離れた第2の面とを有する基板と、前記第1の面と前記第2の面とを結ぶ方向に延在する開口部と、該開口部内に延在する導電性ビアとを含みうる。前記基板は、CTEが10 ppm/未満でありうる。前記導電性ビアは、それぞれが、第1の金属とは異なる第2の金属の層で略被覆された、前記第1の金属でできた第1の領域を有する、複数の基材粒子を含みうる。前記基材粒子同士は冶金接合されることができ、前記粒子の前記第2の金属層は、前記第1の領域内に少なくとも部分的に拡散することができる。前記導電性ビアは、前記接合された基材粒子同士の間に散在し前記開口部内で前記第1の面及び第2の面のうちの少なくとも一方から少なくとも貫入深さまで延在する、はんだを含みうる。

## 【0013】

10

例示的な一実施形態において、前記貫入深さは前記導電性ビアの高さと等しいものでありうる。特定の実施形態において、前記導電性ビアは、前記接合された基材粒子同士の間に散在する空隙も有することがある。該空隙は前記導電性ビアの体積の10%以上を占めることができる。一実施形態において、前記基板は、前記第2の面に隣接する複数の能動半導体デバイスを実装することができ、前記導電性ビアは、前記第2の面における複数の導電性素子のうちの少なくとも1つと電気的に接続することができる。例示的な一実施形態において、前記導電性ビアは、前記導電性パッドと電気的に接続された前記基板内の第2の導電性ビアに接続することができる。特定の実施形態において、前記第2のビアは不純物をドープした半導体材料を含みうる。一実施形態において、前記開口部は、前記基板の前記第1の面と前記第2の面との間に延在することができる。

## 【0014】

20

特定の実施形態において、前記基板は、半導体材料、セラミックス、及びガラスからなる群から選択される材料でありうる。例示的な一実施形態において、それぞれの前記第1の金属領域は、銅及び銅を含む合金からなる群から選択された金属でありうる。一実施形態において、それぞれの前記第2の金属層は、銀、銅、インジウム、亜鉛、及びビスマスからなる群から選択された金属を含む錫合金でありうる。特定の実施形態において、前記第2の金属層のうちの少なくともいくつかの部分は、溶融温度が前記第1の金属領域よりも低いものとすることができる。例示的な一実施形態において、前記導電性ビアのヤング率は、最大で前記ビアに含まれる前記金属のヤング率の50%とすることができる。一実施形態において、前記基材粒子の平均長さは、最大で前記導電性ビアの平均直径の半分とすることができる。特定の実施形態において、それぞれの前記基材粒子の前記第2の金属層は、厚さが前記基材粒子の厚さの2%から25%の間とすることができる。

## 【0015】

30

一実施形態において、前記開口部は前記第1の面から前記第2の面に向かって延在する内面を画定することができる。コンポーネントは、該内面をコーティングする絶縁誘電体層も含みうる。該誘電体層は少なくとも前記開口部内において前記導電性ビアを前記基板から分離し絶縁することができる。例示的な一実施形態において、コンポーネントは、前記誘電体層の上にある第3の金属層も含みうる。特定の実施形態において、前記基材粒子のうちの少なくともいくつかは、前記第2の金属層によって前記第3の金属層に冶金接合することができる。

## 【0016】

40

特定の実施形態において、前記基材粒子のうちの少なくともいくつかは、前記第1の金属領域に囲まれた非金属の核領域も有することがある。例示的な一実施形態において、それぞれの前記非金属の核領域は、シリカ、セラミックス、グラファイト、及びポリマーからなる群から選択される材料でありうる。特定の実施形態において、それぞれの前記基材粒子の前記第1の金属領域は、厚さが前記基材粒子の前記第2の金属層の厚さよりも厚いものとすることができる。一実施形態において、前記非金属の核領域は固体の無機誘電材料とすることができる。前記導電性ビアのヤング率は、最大で、前記ビア内に含まれる前記金属及び前記固体の無機誘電材料のヤング率の50%とすることができる。

## 【0017】

50

本発明の更に他の態様によれば、コンポーネントは、第1の面と第1の面から離れた第2の面とを有する基板と、前記第1の面と前記第2の面とを結ぶ方向に延在する開口部と、該開口部内に延在する導電性ビアとを含みうる。前記基板は、C T E が 10 ppm / 未満である。前記導電性ビアは、それぞれが、第1の金属とは異なる第2の金属の層で略被覆された、前記第1の金属でできた第1の領域を有する、複数の基材粒子を含みうる。前記基材粒子同士は冶金接合することができる。前記粒子の前記第2の金属層は、前記第1の領域内に少なくとも部分的に拡散することができる。前記導電性ビアは、該導電性ビアの体積の少なくとも 10 % である体積を占める間隙粒子を含みうる。

#### 【 0 0 1 8 】

例示的な一実施形態において、前記間隙粒子は C T E が 10 ppm / よりも小さいものとすることができます。一実施形態において、前記導電性ビアのヤング率は、最大で、前記ビア内に含まれる前記間隙粒子の前記金属及び前記材料のヤング率の 50 % とすることができます。特定の実施形態において、前記間隙粒子のうちの少なくともいくつかは第3の金属粒子でありうる。例示的な一実施形態において、前記間隙粒子のうちの少なくともいくつかは非金属の核領域を有することができる。該非金属は、シリカ、セラミックス、グラファイト、及びポリマーからなる群から選択することができる。一実施形態において、それぞれの前記非金属の核領域は、第3の金属層に囲まれていることがある。

#### 【 0 0 1 9 】

本発明の更なる態様は、本発明の上述した態様による超小型電子構造体、本発明の上述した態様による複合チップ、又はその両方を、他の電子デバイスとともに組み込んだシステムを提供する。例えば、本システムを単一のハウジング内に配置することができる。このハウジングは携帯型ハウジングとすることができる。本発明のこの態様の好ましい実施形態によるシステムは、同等の従来システムよりも小型にすることができる。

#### 【 0 0 2 0 】

本発明のまた別の態様によれば、コンポーネントを製造する方法が、第1の面と、第1の面から離れた第2の面とを有する基板を準備するステップであって、該基板は C T E が 10 ppm / よりも小さく、該基板は前記第1の面から前記第2の面に向かって延在する開口部を有する、準備するステップを含みうる。本方法は、前記開口部内に複数の基材粒子を堆積させるステップであって、それぞれの該基材粒子は、第1の金属領域と、該第1の金属領域を被覆する第2の金属層とを含み、該第2の金属層は融点が 400 よりも低く、前記第1の金属領域は融点が 500 以上である、堆積させるステップも含みうる。本方法は、それぞれの前記第2の金属層が前記基材粒子を溶融して互いと一体にして前記開口部内に延在する連続的な導電性ビアを形成するように、前記基材粒子を加熱するステップであって、該導電性ビアは、前記接合された基材粒子同士の間に散在する空隙を有し、該空隙は前記導電性ビアの体積の 10 % 以上を占める、加熱するステップを更に含みうる。

#### 【 0 0 2 1 】

一実施形態において、前記基板は、前記第2の面に隣接する複数の能動半導体デバイスを実装することができる。前記導電性ビアは、前記第2の面における複数の導電性素子のうちの少なくとも 1つと電気的に接続することができる。例示的な一実施形態において、本方法は、前記基材粒子を加熱するステップの後に、前記第1の面を平坦化するステップも含みうる。特定の実施形態において、本方法は、前記接合された基材粒子同士の間に散在する前記空隙のうちの少なくともいくつかの中にポリマー媒体を堆積させるステップも含みうる。該ポリマー媒体は、前記開口部内で前記第1の面及び第2の面のうちの少なくとも一方から少なくとも貫入深さまで延在することができる。一実施形態において、本方法は、前記接合された基材粒子同士の間に散在する前記空隙のうちの少なくともいくつかの中にはんだを堆積させるステップも含みうる。該はんだは、前記開口部内で前記第1の面及び第2の面のうちの少なくとも一方から少なくとも貫入深さまで延在することができる。

#### 【 0 0 2 2 】

10

20

30

40

50

特定の実施形態において、それぞれの前記第1の金属領域は、銅、ニッケル、アルミニウム、及びタンゲステン、並びに銅を含む合金からなる群から選択された金属でありうる。例示的な一実施形態において、それぞれの前記第2の金属層は、錫、ビスマス、インジウム、カドミウム、セレン、亜鉛、及びその合金からなる群から選択された金属でありうる。一実施形態において、それぞれの前記基材粒子は、前記第1の金属領域と前記第2の金属層との間のバリア層を含みうる。特定の実施形態において、前記基材粒子は液体キャリア材料内に設けることができる。例示的な一実施形態において、前記開口部内に前記基材粒子を堆積させる前記ステップは、吐出、インクジェット印刷、レーザ印刷、スクリーン印刷、又はステンシルによって行うことができる。一実施形態において、前記液体キャリア材料は前記加熱ステップの結果蒸発することができる。特定の実施形態において、前記液体キャリア材料は流動性の成分を含みうる。例示的な一実施形態において、本方法は、前記加熱ステップの間又は後に、前記流動性の成分を除去するように真空処理を行うステップも含みうる。

#### 【0023】

例示的な一実施形態において、前記第2の金属層は前記第1の金属領域を被覆するバイメタル層とすることができる。前記加熱するステップは、前記基材粒子を転移液相反応温度まで加熱することができる。それぞれの前記第2のバイメタル層は前記第1の金属領域の回りで低融点共晶を形成することができる。一実施形態において、前記基材粒子のうちの隣接するもの同士の少なくともいくつかの前記低融点共晶は、前記互いに隣接する基材粒子の前記第1の金属領域内へと拡散することができる。特定の実施形態において、それぞれの前記第2のバイメタル層は、錫の層と、銀、銅、インジウム、亜鉛、及びビスマスからなる群から選択された金属を含む合金の層とを含みうる。例示的な一実施形態において、前記開口部は前記第1の面から前記第2の面向かって延在する内面を画定することができる。本方法は、前記導電性ビアを形成する前記ステップの前に、前記内面をコーティングする絶縁誘電体層を堆積させるステップも含みうる。

#### 【0024】

一実施形態において、本方法は、前記導電性ビアを形成する前記ステップの前に、前記誘電体層の上にあり前記開口部の内側を覆う第3の金属層を形成するステップも含みうる。特定の実施形態において、前記導電性ビアを形成する前記ステップは、前記基材粒子のうちの少なくともいくつかを前記第3の金属層に冶金接合することができる。例示的な一実施形態において、前記開口部内に前記基材粒子を堆積させる前記ステップは、前記基材粒子と間隙粒子との混合物を前記開口部内に堆積させるステップを含みうる。前記間隙粒子は前記導電性ビアの構造体に組み込むことができる。

#### 【0025】

特定の実施形態において、前記間隙粒子のうちの少なくともいくつかは第3の金属粒子でありうる。一実施形態において、前記間隙粒子は、銀、金、タンゲステン、モリブデン、及びニッケルからなる群から選択された少なくとも1つの金属を含む。例示的な一実施形態において、前記間隙粒子のうちの少なくともいくつかは非金属の核領域を有することがある。該非金属は、シリカ、セラミックス、グラファイト、及びポリマーからなる群から選択することができる。特定の実施形態において、前記基材粒子のうちの少なくともいくつかは、前記第1の金属領域に囲まれた非金属の核領域を有することがある。一実施形態において、それぞれの前記非金属の核領域は、シリカ、セラミックス、グラファイト、及びポリマーからなる群から選択される材料でありうる。

#### 【図面の簡単な説明】

#### 【0026】

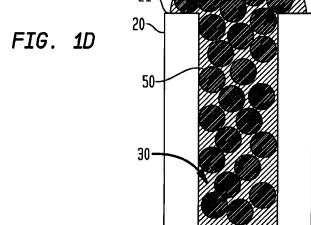

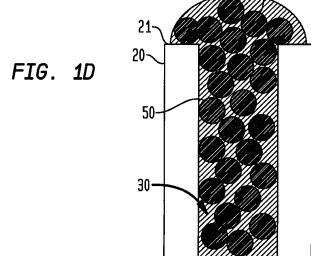

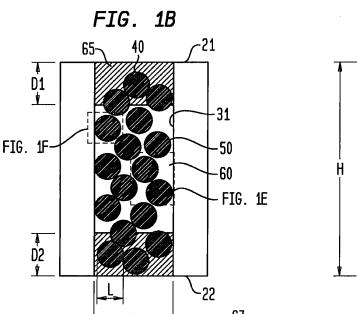

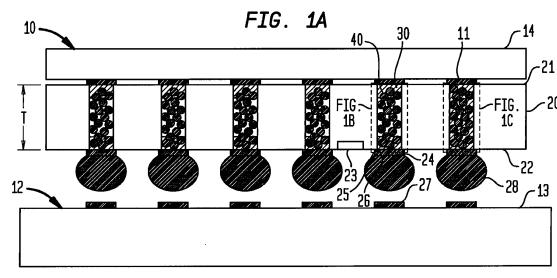

【図1A - 1D】図1Aは、本発明の一実施形態による積層型超小型電子アセンブリの概略断面図である。図1Bは、本発明による導電性ビアを示す、図1Aの一部の拡大部分断面図である。図1Cは、本発明による導電性ビアを示す、図1Aの一部の拡大部分断面図である。図1Dは、図1Cの代替的な実施形態の拡大部分断面図である。

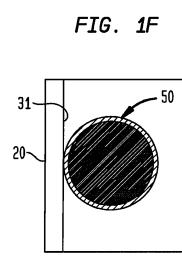

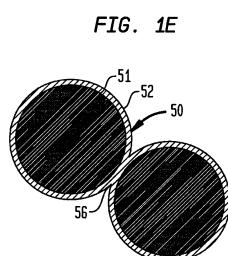

【図1E . 1F】図1Eは、隣接する基材粒子同士の間の電気的接続を示す、図1Bの一

10

20

30

40

50

部の拡大部分断面図である。図1Fは、基材粒子と開口部内面との接触を示す、図1Bの一部の拡大部分断面図である。

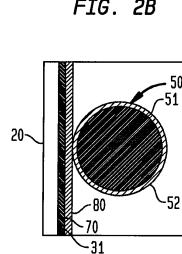

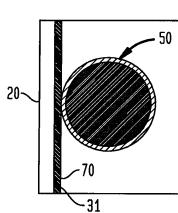

【図2】図2Aおよび図2Bは、図1Fの代替的な実施形態の拡大部分断面図である。

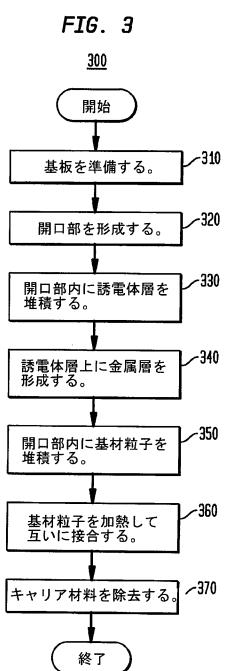

【図3】図1Aのコンポーネントを製造する方法の例示的な一方法における各プロセスを示すフローチャートである。

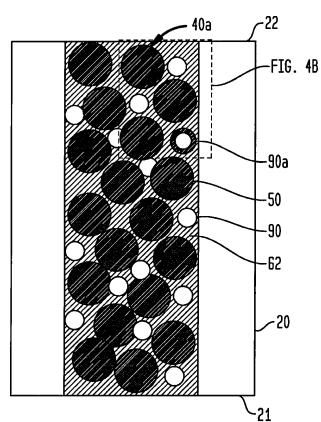

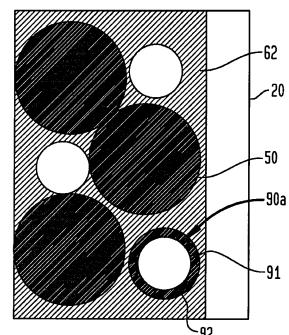

【図4】図4Aは、図1Bの代替的な実施形態の拡大部分断面図である。図4Bは、金属層でコーティングした間隙粒子を示す、図4Aの一部の拡大部分断面図である。

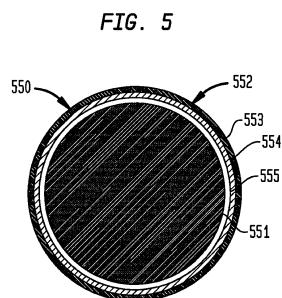

【図5】図1Aの基材粒子の代替的な実施形態の拡大部分断面図である。

【図6】図1Aの基材粒子の別の代替的な実施形態の拡大部分断面図である。

【図7】本発明の一実施形態によるシステムの概略図である。

10

#### 【発明を実施するための形態】

##### 【0027】

図1A及び図1Bに示すように、コンポーネント10は、裏面すなわち第1の面21と第1の面から離れた表面すなわち第2の面22とを有するシリコン基板20と、第1の面と第2の面との間のそれぞれの開口部30内でシリコン基板20を貫いて延在する複数の導電性ピアすなわちシリコン貫通ピア40とを含みうる。コンポーネント10は、超小型電子素子の導電性素子11を通じて基板20に電気的に接続された、第1の面21に隣接する超小型電子素子14も含みうる。コンポーネント10は、第2の面22に隣接するパッケージ基板すなわちPCB12と電気的に接続することができる。

##### 【0028】

いくつかの実施形態において、基板20は、半導体チップ、ウエハ等とすることができます。基板20は、好ましくは熱膨張係数(「CTE」)が $10 \times 10^{-6}$ / $\text{ppm}$ 未満である。特定の実施形態において、基板20はCTEが $7 \text{ ppm}$ /未満でありうる。基板20は、本質的にシリコン等の無機材料からなることがある。基板20がシリコン等の半導体からできている実施形態では、基板内の、第1の面21又は第2の面22に隣接して位置するその能動半導体領域23において、複数の能動半導体デバイス(例えば、トランジスタ、ダイオード等)を実装する(embodyed)ことができる。基板20の、第2の面22と第1の面21との間の厚さは、通常 $200 \mu\text{m}$ 未満であり、それよりも非常に小さく、例えば $130 \mu\text{m}$ 、 $70 \mu\text{m}$ 、又は更に小さくすることができる。特定の実施形態において、基板20は、半導体材料、セラミックス、及びガラスからなる群から選択される材料で作製することができる。

20

##### 【0029】

図1Aにおいて第1の面21に平行な方向を、本明細書においては「水平」又は「横」方向と称するのに対し、第1の面に垂直な方向を、本明細書においては上向きの又は下向きの方向と称し、本明細書においてはまた「鉛直」方向とも称する。本明細書において称する方向は、言及する構造体の基準系におけるものである。したがって、これらの方向は、標準基準系すなわち重力基準系に対していかなる向きであってもよい。1つの特徴部が「或る面の上方」で別の特徴部より高く配置されている、という表現は、その1つの特徴部が他方の特徴部よりも、その面から同じ垂直方向に、より大きな距離だけ離れている、ということを意味する。逆に、1つの特徴部が「或る面の上方」で別の特徴部より低く配置されている、という表現は、その1つの特徴部が他方の特徴部よりも、その面から同じ垂直方向に、より小さな距離だけ離れている、ということを意味する。

30

##### 【0030】

基板20は、第2の面22において露出している、導電性パッド24等の複数の導電性素子も含みうる。図1A及び図1Bには具体的に示していないが、能動半導体領域23における能動半導体デバイスは、存在している場合には通常、導電性パッド24に導電接続されている。したがって能動半導体デバイスは、基板20の1つ又は複数の誘電体層の中又は上方に延在している、組み込まれた配線を通じて導電的にアクセス可能である。いくつかの実施形態(図示せず)においては、導電性パッド24を基板20の第2の面22において直接露出させなくてもよい。その代わりに、導電性パッド24を、基板20の第2

40

50

の面 2 2 において露出している端子まで延在するトレースに電気的に接続することができる。導電性パッド 2 4 及び本明細書において開示するいかなる他の導電性構造体も、例えば、銅、アルミニウム、又は金を含む、任意の導電性金属で作製することができる。導電性パッド 2 4 及び本明細書において開示するいかなる導電性パッドも、円形、橢円形、三角形、正方形、長方形、又は任意の他の形状を含む、任意の上面から見た形状を有することがある。

#### 【 0 0 3 1 】

本開示において用いられる、導電性素子が基板の面「において露出している」という表現は、基板のその面に垂直な方向に、基板の外側から基板のその面に向かって動いている理論上の点に、その導電性素子が接触することができる、ということを示している。したがって、基板の面において露出している端子又は他の導電性素子は、そのような面から突出していてもよく、そのような面と同一平面上にあってもよく、そのような面に関して引っ込んでいて基板の孔又は窪みを通して露出していてもよい。10

#### 【 0 0 3 2 】

基板 2 0 は、第 2 の面 2 2 と導電性パッド 2 4との間に位置する誘電体層（図示せず）を更に含みうる。このような誘電体層は、導電性パッド 2 4 をシリコン基板 2 0 から電気的に絶縁することができる。この誘電体層を、基板 2 0 の「パッシベーション層」と呼ぶことができる。誘電体層は、無機若しくは有機の誘電材料又はその両方を含みうる。誘電体層は、電着コンフォーマルコーティング又は他の誘電材料、例えば光画像形成可能（phot oimageable）ポリマー材料、例えばはんだマスク材料を含みうる。基板 2 0 は、第 1 の面 2 1 の上にある別の誘電体層（図示せず）を更に含みうる。一例において、このような誘電体層は、存在している場合には、導電性素子を基板 2 0 の第 1 の面 2 1 から電気的に絶縁することができる。20

#### 【 0 0 3 3 】

本明細書において説明する実施形態において、第 1 の面 2 1 又は第 2 の面 2 2 の上にある誘電体層は、厚さを基板 2 0 の厚さよりも実質的に薄くすることができ、誘電体層の C T E が基板材料の C T E よりも実質的に高い場合であっても、基板の実効 C T E が基板材料の C T E と略等しくなることができるようになっている。一例において、基板 2 0 は実効 C T E が 1 0 p p m / 未満とすることができます。

#### 【 0 0 3 4 】

基板 2 0 は、第 1 の面 2 1 から基板の厚さ T を部分的に又は完全に貫いて第 2 の面 2 2 に向かって延在する、複数の開口部 3 0 を含みうる。図示の実施形態において、それぞれの開口部 3 0 は、第 1 の面 2 1 から導電性パッド 2 4 のうちの対応する 1 つまで延在している。開口部 3 0 は、例えば m 個 × n 個のアレイを含む、任意の上面から見た幾何学的形状を有することができる。m と n とはそれぞれ 1 よりも大きい。30

#### 【 0 0 3 5 】

それぞれの開口部 3 0 は、第 1 の面 2 1 から第 2 の面 2 2 に向かって延在する内面 3 1 を有する。内面 3 1 は、導電性パッド 2 4 から基板 2 0 を通って、第 2 の面 2 2 によって規定される水平面に対して 0 度から 90 度の間の角度で延在することができる。内面 3 1 は、一定の傾斜又は変化する傾斜を有することができる。例えば、第 2 の面 2 2 によって規定される水平面に対する内面 3 1 の角度すなわち傾斜は、内面が第 1 の面 2 1 に向かって貫入するにしたがって小さくなる（すなわち、正方向の大きさが小さくなる又は負方向の大きさが小さくなる）ことができる。特定の実施形態において、それぞれの開口部 3 0 は、対応する導電性パッド 2 4 から第 1 の面 2 1 に向かう方向に先細りになっていることができる。いくつかの例において、それぞれの開口部 3 0 は、例えば、とりわけ円錐台形、円柱、立方体、又は角柱を含む、任意の三次元形状を有することができる。40

#### 【 0 0 3 6 】

複数の開口部 3 0 は、開口部 3 0 のそれぞれの中に延在する複数の導電性ビア 4 0 を含みうる。それぞれの導電性ビアは、それぞれの導電性パッド 2 4 と、超小型電子素子 1 4 等の別の素子と相互接続を行う、第 1 の面 2 1 において露出している導電性コンタクト（50

図示せず)との間に延在している。特定の実施形態において、第1の導電性ビア及び第2の導電性ビア40は、それぞれ第1の電位及び第2の電位に接続可能とすることができます。一例において、導電性ビア40のうちの少なくともいくつかは、それぞれがそれぞれの導電性パッド24と電気的に接続された基板20内の第2の導電性ビア(図示せず)と電気的に接続することができる。そのような第2の導電性ビアは、不純物をドープした半導体材料を含みうる。

#### 【0037】

導電性ビア40(又は本明細書において説明する任意の他の導電性素子)のそれぞれと、基板20の外部のコンポーネントとの間の接続は、導電性塊28等の導電性塊すなわち導電性接合材料を通してのものとすることができます。図1Aに示すように、それぞれのはんだボール28は、基板20の導電性パッド24を、パッケージ基板12の対応する導電性パッド27に電気的に接続することができる。そのような導電性塊は、溶融温度が比較的低い可融金属、例えば、はんだ、錫、又は複数の金属を含む共融混合物を含みうる。代替的には、そのような導電性塊は、濡れ性金属、例えば、銅、又ははんだ若しくは別の可融金属よりも溶融温度が高い他の貴金属若しくは非貴金属を含みうる。そのような濡れ性金属は、対応する特徴部、例えば相互接続素子の可融金属でできた特徴部と接合することができる。特定の実施形態において、そのような導電性塊は、媒体内に散在する導電性材料、例えば導電性ペースト、例えば金属充填ペースト、はんだ充填ペースト、又は等方性の導電性接着剤若しくは異方性の導電性接着剤を含みうる。

#### 【0038】

それぞれの導電性ビア40は、第2の面22において単一の共通の導電性パッド24に、第1の面21において導電性コンタクトに電気的に接続することができる、複数の接合された基材粒子50を含みうる。代替的には、それぞれの導電性ビア40は、超小型電子素子14及びパッケージ基板12等、他の素子と電気的相互接続される基板20の第1の面21及び第2の面22のうちの少なくとも一方において露出している接触部を有することができる。一実施形態において、それぞれの導電性ビア40は、対応する導電性パッド24を通してその底面25から面26まで延在することができる。特定の実施形態において、それぞれの導電性ビア40は、第2の面22において複数の導電性パッド24のうちの少なくとも1つと電気的に接続することができる。一例において、基材粒子50は、平均長さLが最大で導電性ビア40の平均直径Dの半分とすることができる。

#### 【0039】

それぞれの導電性ビア40は、接合された基材粒子50同士の間に散在する空隙60も有することがある。このような空隙60(及び本明細書において説明する他の空隙の全て)は、空気で充填することができる。一例において、空隙は導電性ビア40の体積の10%以上を占めることができる。

#### 【0040】

例示的な実施形態において、このような空隙60は、基板20内での、及び/又は第2の面22において導電性パッド24に対する、若しくは第1の面21において導電性コンタクトに対する応力を、空隙が存在しない場合ほど発生させることなく膨張する更なる余地を導電性ビア40の基材粒子50に提供することができる。特に基板20の材料のCTEと導電性ビア40の材料のCTEとが比較的大きくずれている場合、このような空隙によって、このような実施形態における超小型電子ユニット10の性能を改善することができる。

#### 【0041】

それぞれの導電性ビア40は、第1の面21及び第2の面22のうちの少なくとも一方に隣接して位置する境界領域65を有することができる。それぞれの境界領域65は、例えば、開口部30内で接合された基材粒子50同士の間に散在し第1の面21又は第2の面22のそれぞれから貫入深さD1又はD2まで延在する、はんだ又はポリマーの媒体を含みうる。

#### 【0042】

10

20

30

40

50

基板 20 が、第 2 の面 22 に隣接して位置するその能動半導体領域 23 において内部に実装された複数の能動半導体デバイスを含む、特定の実施形態において、コンポーネント 10 は図 1A の代替の構成を有することができる。そのようなコンポーネント 10 の代替の構成において、基板 20 の第 2 の面 22 は超小型電子素子 14 に隣接して配置することができ、基板の導電性素子（例えば導電性パッド 24）は、例えばはんだ等の導電性塊を用いて、超小型電子素子の導電性素子 11 と接合することができる。そのような実施形態において、基板 20 の第 1 の面 21 はパッケージ基板 12 に隣接して配置することができ、基板 20 の第 1 の面 21 における導電性素子は、はんだボール 28 等の導電性塊を通してパッケージ基板 12 の導電性素子 27 に接合することができる。

## 【0043】

10

図 1C に示す代替的な導電性ピアの実施形態において、それぞれの導電性ピア 40' ははんだ領域 66 を含むことができ、はんだ領域 66 において、はんだは接合された基材粒子 50 同士の間に散在し貫入深さを貫いて延在する。貫入深さは、導電性ピアの高さ H と等しいものとすることができます。

## 【0044】

図 1D に示す別の代替的な導電性ピアの実施形態において、それぞれの導電性ピア 40' は、基板 20 の第 1 の面 21 の上方に延在する基材粒子 50 を含みうる。一例において、基材粒子 50 は基板 20 の第 1 の面 21 の上にあることができる。導電性ピア 40' ははんだ領域 67 を含むことができ、はんだ領域 67 において、はんだは、基板 20 の開口部 30 の中及び第 1 の面 21 の上方において、接合された粒子 50 同士の間に散在する。特定の実施形態において、基材粒子 50 は最初に、基板 20 の第 1 の面 21 の上方に延在するよう開口部 30 内に堆積させることができ、基材粒子同士が接合される前に導電性ピア 40' を第 1 の面に合わせて平坦化し、それによって図 1C に示す導電性ピア 40' を結果として得ることができます。一例（図示せず）において、それぞれの導電性ピアは、基板 20 の第 1 の面 21 及び第 2 の面 22 のうちの一方又は両方の下方に引っ込んだ位置に延在する基材粒子 50 を含みうる。

20

## 【0045】

図 1E に示すように、それぞれの基材粒子 50 は、第 2 の金属層 52 で略被覆された、第 1 の金属でできた第 1 の領域 51 を含みうる。それぞれの基材粒子 50 は、第 2 の金属層のうちの少なくともいくつかの部分は第 1 の金属領域よりも溶融温度が低くなるよう、それぞれの第 2 の金属層 52 を構成する金属とは異なる金属でできた第 1 の金属領域 51 を含みうる。隣接する基材粒子 50 同士は、自身の第 2 の金属層 52 によって冶金接合することができる。隣接する接合された粒子 50 同士の第 2 の金属層 52 は、接合された粒子の第 1 の領域 51 内に少なくとも部分的に拡散することができる。特定の例において、それぞれの基材粒子 50 の第 2 の金属層 52 は、厚さが基材粒子の厚さの 2 % から 25 % の間とすることができます。

30

## 【0046】

例示的な実施形態において、それぞれの第 1 の金属領域 51 は、銅及び銅を含む合金からなる群から選択された金属とすることができる。一例において、それぞれの第 2 の金属層は、銀、銅、インジウム、亜鉛、及びビスマスからなる群から選択された金属を含む錫合金とすることができる。一例において、それぞれの第 2 の金属層 52 は、融点が 400

40

よりも低いものとすることができます、それぞれの第 1 の金属領域 51 は、融点が 500 以上とすることができます。一例において、導電性ピア 40 のヤング率は、最大で導電性ピアに含まれる金属（例えば、基材粒子 50 及び金属層 80）のヤング率の 50 % とすることができます。

## 【0047】

一実施形態において、図 1F に示すように、特定の開口部 30 の内面 31 は露出していて、導電性ピア 40 の、導電性ピア 40 を貫いて延在する粒子 50 と接触することができる。

## 【0048】

50

別の例において、図 2 A に示すように、特定の開口部 3 0 の内面 3 1 は、対応する導電性ビア 4 0 が絶縁誘電体層内に延在するように、第 1 の面 2 1 と第 2 の面 2 2 との間に延在する絶縁誘電材料 7 0 でコーティングすることができる。そのような絶縁誘電体層 7 0 によって、少なくとも開口部内において、導電性ビア 4 0 を基板 2 0 の材料から分離し電気的に絶縁することができる。一例において、そのような絶縁誘電体層 7 0 は、開口部 3 0 内で露出している内面 3 1 をコンフォーマルコーティングすることができる。絶縁誘電材料 7 0 は、無機若しくは有機の誘電材料又はその両方を含みうる。特定の実施形態において、絶縁誘電材料 7 0 はコンプライアントな (compliant) 誘電材料を含んでおり、その係数と厚さとの積がコンプライアンシ (compliancy) を提供するように絶縁誘電材料の弹性係数を十分低くするとともに厚さを十分にすることができる。

10

#### 【 0 0 4 9 】

更に他の例において、図 2 B に示すように、絶縁誘電体層 7 0 と特定の開口部 3 0 の内面 3 1 との上に金属層 8 0 が存在することがある。そのような金属層 8 0 は、開口部 3 0 内で第 1 の面 2 1 と第 2 の面 2 2 との間で延在することができる。一例において、金属層 8 0 は、開口部 3 0 内で露出している絶縁誘電体層 7 0 をコンフォーマルコーティングすることができる。特定の実施形態において、金属層 8 0 は、銅、銀、金、タンゲステン、モリブデン、ニッケル、銅とタンゲステンとの合金、及びチタンとタンゲステンとの合金からなる群から選択された少なくとも 1 つの金属を含みうる。基材粒子 5 0 のうちの少なくともいくつかは、それぞれの第 2 の金属層 5 2 によって金属層 8 0 に冶金接合することができる。特定の実施形態において、金属層 8 0 は、基材粒子 5 0 の金属が基板 2 0 内に拡散するのを防止するのに役立つことができるバリア (barrier) 材料とすることができる。

20

#### 【 0 0 5 0 】

また別の例において、金属層 8 0 は、誘電体層 7 0 に隣接するバリア又は接着層を含む、金属の多数の層、及びそのようなバリア又は接着層の上にあって基材粒子 5 0 を接合することができる、別の金属層とすることができる。

#### 【 0 0 5 1 】

特定の例において、基板 2 0 が本質的に誘電材料からなる場合には、絶縁誘電体層 7 0 は省くことができ、基板 2 0 の開口部 3 0 の内面 3 1 に金属層 8 0 が直接接触することができる。

30

#### 【 0 0 5 2 】

次に、図 3 に示すフローチャート 3 0 0 を参照して超小型電子ユニット 1 0 ( 図 1 A 及び図 1 B ) を製造する方法を説明する。フローチャート 3 0 0 のステップ 3 1 0 において、基板 2 0 を準備することができる。フローチャート 3 0 0 のステップ 3 2 0 において、第 1 の面 2 1 から第 2 の面 2 2 に向かって延在する複数の開口部 3 0 を形成するように、基板 2 0 の第 1 の面から材料を除去することができる。

#### 【 0 0 5 3 】

開口部 3 0 は例えば、第 1 の面 2 1 が残る部分を保護することが所望される箇所にマスク層を形成した後、基板 2 0 を選択的にエッチングすることによって、形成することができる。例えば、光画像形成可能層、例えばフォトトレジスト層を堆積し、第 1 の面 2 1 の一部のみを被覆するようパターニングすることができ、その後決められた時間エッチングプロセスを行って開口部 3 0 を形成することができる。

40

#### 【 0 0 5 4 】

第 1 の面 2 1 から第 2 の面 2 2 に向かって下向きに延在する、それぞれの開口部 3 0 の内面 3 1 は傾斜していることができる、すなわち、第 1 の面に対して垂直な角度 (直角) 以外の角度をなして延在していることができる。ウェットエッチングプロセス、例えば特に等方性エッチングプロセスとテーパ刃を使用する鋸引きとを用いて、内面 3 1 が傾斜した開口部 3 0 を形成することができる。特に、レーザダイシング、機械的フライス加工を用いて、内面 3 1 が傾斜した開口部 3 0 を形成することもできる。

#### 【 0 0 5 5 】

50

代替的には、それぞれの開口部 30 の内面 31 は、傾斜する代わりに、第 1 の面 21 から下向きに、(図 1 A に示すように) 第 1 の面に対して略直角をなす鉛直又は略鉛直方向に延在することができる。特に、異方性エッティングプロセス、レーザダイシング、レーザドリル加工、機械的除去プロセス、例えば、鋸引き、フライス加工、超音波加工を用いて、内面 31 が略鉛直の開口部 30 を形成することができる。

#### 【0056】

一例(図示せず)において、そのようなエッティングプロセスを基板の第 2 の面 22 の上方から基板 20 に適用して、開口部 30 を形成することができる。エッティングプロセスを導電性パッド 24 の上方から行うと、開口部 30 が導電性パッドを貫いて延在してしまう可能性がある。

10

#### 【0057】

開口部 30 の形成中に、基板 20 の第 1 の面 21 及び / 又は第 2 の面 22 の上にあるパッシベーション層の一部分もまた除去することができ、基板 20 のエッティング中に、又は別個のエッティングステップとして、そのような部分を貫いてエッティングすることができる。エッティング、レーザドリル加工、機械的フライス加工、又は他の適切な技法を使用して、そのようなパッシベーション層の一部分を除去することができる。

#### 【0058】

フローチャート 300 のステップ 330 において、(図 2 A に示す) 特定の実施形態において、開口部 30 の形成後、開口部 30 の内面 31 の上に絶縁誘電体層 70 を堆積して、導電性ビア 40 が、開口部内に堆積されるときに絶縁誘電体層内で延在するようにすることができる。一例において、それぞれの内面 31 をコーティングする絶縁誘電体層 70 を堆積することができる。

20

#### 【0059】

開口部 30 の内面 31 の上に絶縁誘電体層を有する一実施形態において、基板の第 1 の面 21 の、そのような誘電体層を形成することが所望されない開口部を有する部分に、マスクを施すことができる。開口部 30 のうちの、そのようなコーティングを施していないものは、基板 20 の材料に直接接触する部分を有する(図 1 F に示す)導電性ビア 40 で後に満たすことができる。そのような導電性ビア 40 は、例えば、導電性パッド 24 の接地パッドまで延在する特定の開口部 30 に含まれうる。

#### 【0060】

30

様々な方法を用いて開口部 30 の内面 31 の上にそのような絶縁誘電体層 70 を形成することができ、そのような方法を、図 2 A を参照して以下に説明する。特定の例において、化学蒸着(CVD: Chemical Vapor Deposition)、プラズマ蒸着、原子層堆積(ALD: Atomic Layer Deposition)等の蒸着プロセスを用いて、開口部 30 の内面 31 の上に薄い絶縁誘電体層を堆積することができる。一例において、そのような絶縁誘電体層を堆積する低温プロセス中にテトラエチルオルトシリケート(TEOS)を用いることができる。例示的な実施形態において、開口部 30 の内面 31 の上に、二酸化ケイ素、ホウリケイ酸ガラス(BPSG)、ホウケイ酸ガラス(BSG)、又はリンケイ酸ガラス(PSG)の層を堆積することができ、そのようなガラスは不純物をドープしてもしなくてもよい。

40

#### 【0061】

一例において、流動性の誘電材料を基板 20 の第 1 の面 21 に施すことができ、そして、その流動性の材料は「スピンドルコーティング」操作中に開口部 30 の内面 31 にわたってより均一に分散でき、その次に、加熱を含みうる乾燥サイクルが続く。別の例において、誘電材料でできた熱可塑性フィルムを第 1 の面 21 に施すことができ、その後アセンブリは加熱されるか、又は真空環境で、すなわち、周囲圧力よりも低圧の環境に配置されて加熱される。

#### 【0062】

また別の例において、基板 20 を含むアセンブリを誘電体堆積浴に浸漬して、コンフォーマル誘電体コーティングすなわち絶縁誘電材料 70 を形成することができる。本明細書

50

において用いるとき、「コンフォーマルコーティング」とは、絶縁性の誘電材料70が開口部30の内面31の輪郭に沿う場合等、コーティングされている面の輪郭に沿う特定の材料でできたコーティングのことである。例えば、電気泳動堆積法又は電解堆積法を含む電気化学堆積法を用いて、コンフォーマル誘電材料70を形成することができる。

#### 【0063】

一例において、電気泳動堆積法を用いてコンフォーマル誘電体コーティングを形成し、コンフォーマル誘電体コーティングがアセンブリの露出している導電性及び半導電性の面上にのみ堆積するようにすることができる。堆積中、半導体デバイスウェハは所望の電位に保持され、それとは異なる所望の電位に浴を保持するように浴に電極が入れられる。そしてアセンブリは、開口部30の内面31沿いを含むがそれに限定されない導電性又は半導電性の基板の露出面に電着したコンフォーマル誘電材料70を形成するのに十分な時間、適切な条件下でこの浴内に保持される。電気泳動堆積は、それによってコーティングされる面と浴との間に十分強力な電場が維持されている限り起こる。電気泳動によって堆積したコーティングは、その堆積の、例えば電圧、濃度等のパラメータによって決まる或る特定の厚さに達すると堆積が停止するという点で、自己制御的である。

#### 【0064】

電気泳動堆積によって、基板20の導電性及び/又は半導電性の面上に、連続的で厚さが均一のコンフォーマルコーティングが形成される。加えて、電気泳動コーティングは、その誘電(非導電)特性のために、基板20の第1の面21の上にある残存するパッシベーション層の上に形成されないよう堆積することができる。言い換えれば、電気泳動堆積の特性の1つは、誘電材料の層上には通常形成されず、導体の上にある誘電体層上には、その誘電材料の層の厚さが十分である場合にはその層が誘電性なので、形成されない、ということである。電気泳動堆積は通常、厚さが約10ミクロンを超える数ミクロンまでである誘電体層上では起こらない。コンフォーマル誘電材料70は、陰極エポキシ堆積前駆体から形成することができる。代替的には、ポリウレタン又はアクリルの堆積前駆体を使用することができます。以下の表1に、電気泳動コーティング前駆体のさまざまな組成と供給業者を列挙する。

#### 【0065】

10

20

【表 1】

| 電気泳動コーティング名                | POWERCRON 645    | POWERCRON 648    | CATHOGUARD 325 |

|----------------------------|------------------|------------------|----------------|

| <b>製造業者</b>                |                  |                  |                |

| MFG                        | PPG              | PPG              | BASF           |

| タイプ                        | 陰極               | 陰極               | 陰極             |

| ポリマー基材                     | エポキシ             | エポキシ             | エポキシ           |

| 所在地                        | ペンシルバニア州ピッツバーグ   | ペンシルバニア州ピッツバーグ   | ミシガン州 サウスフィールド |

| <b>塗布データ</b>               |                  |                  |                |

| Pb/Pf フリー                  | Pb フリー           | Pb 又は Pf フリー     | Pb フリー         |

| 有害大気汚染物質(HAPs), g/L        |                  | 60-84            | 適合             |

| 揮発性有機化合物(VOC), g/L (マイナス水) |                  | 60-84            | <95            |

| 硬化                         | 20 分/175°C       | 20 分/175°C       |                |

| <b>フィルム特性</b>              |                  |                  |                |

| 色                          | 黒                | 黒                | 黒              |

| 厚さ、μm                      | 10-35            | 10-38            | 13-36          |

| ベンシル硬度                     |                  | 2H+              | 4H             |

| <b>浴特性</b>                 |                  |                  |                |

| 固体、%wt.                    | 20(18-22)        | 20(19-21)        | 17.0-21.0      |

| pH(25°C)                   | 5.9(5.8-6.2)     | 5.8(5.6-5.9)     | 5.4-6.0        |

| 導電率(25°C)μS                | 1000-1500        | 1200-1500        | 1000-1700      |

| P/B 比                      | 0.12-0.14        | 0.12-0.16        | 0.15-0.20      |

| 動作温度、°C                    | 30-34            | 34               | 29-35          |

| 時間、秒                       | 120-180          | 60-180           | 120+           |

| 陽極                         | SS316            | SS316            | SS316          |

| 電圧                         |                  | 200-400          | >100           |

| 電気泳動コーティング名                | ELECTROLAC       | LECTRASEAL DV494 | LECTROBASE 101 |

| <b>製造業者</b>                |                  |                  |                |

| MFG                        | MACDERMID        | LVH COATINGS     | LVH COATINGS   |

| タイプ                        | 陰極               | 陽極               | 陰極             |

| ポリマー基材                     | ポリウレタン           | ウレタン             | ウレタン           |

| 所在地                        | コネチカット州ウォーター・ベリー | 英國バーミンガム         | 英國バーミンガム       |

| <b>塗布データ</b>               |                  |                  |                |

| Pb/Pf フリー                  |                  | Pb フリー           | Pb フリー         |

| 有害大気汚染物質(HAPs), g/L        |                  |                  |                |

| 揮発性有機化合物(VOC), g/L (マイナス水) |                  |                  |                |

| 硬化                         | 20 分/149°C       | 20 分/175°C       | 20 分/175°C     |

| <b>フィルム特性</b>              |                  |                  |                |

| 色                          | 透明(+染色)          | 黒                | 黒              |

| 厚さ、μm                      |                  | 10-35            | 10-35          |

| ベンシル硬度                     | 4H               |                  |                |

| <b>浴特性</b>                 |                  |                  |                |

| 固体、%wt.                    | 7.0(6.5-8.0)     | 10-12            | 9-11           |

| pH(25°C)                   | 5.5-5.9          | 7-9              | 4.3            |

| 導電率(25°C)μS                | 450-600          | 500-800          | 400-800        |

| P/B 比                      |                  |                  |                |

| 動作温度、°C                    | 27-32            | 23-28            | 23-28          |

| 時間、秒                       |                  |                  | 60-120         |

| 陽極                         | SS316            | 316SS            | 316SS          |

| 電圧                         | 40、最大            |                  | 50-150         |

## 【0066】

別の例において、誘電材料 70 は電解によって形成することができる。このプロセスは、堆積した層の厚さが、それが形成される導電性又は半導電性の面に近接していることによって制限されない、という点を除き、電気泳動堆積に類似している。このように、電解堆積誘電体層を、要件に基づいて選択される厚さまで形成することができ、処理時間は達

10

20

30

40

50

成される厚さの一要因である。

**【0067】**

フローチャート300のステップ340では、特定の実施形態(図2Bに示す)において、絶縁誘電体層70の堆積後、絶縁誘電体層とそれぞれの開口部30の内面31との上に金属層80を形成することができる。一例において、それぞれの開口部30の内側を覆う(lining)金属層80を形成することができる。

**【0068】**

金属層80を形成するのに、例示的な一方は、絶縁誘電体層70の露出している面上への主要金属層のスパッタリングによる形成、めっき、化学蒸着、プラズマ蒸着、又は機械的堆積のうちの1つ以上のものにより金属層を堆積させることを含む。機械的堆積は、コーティングされる面上に加熱された金属粒子の流れを高速で向けることを含みうる。このステップは、例えばプランケット堆積により絶縁誘電体層70上に行うことができる。

10

**【0069】**

導電性素子を形成するのに使用できる本質的に任意の技法を用いて、金属層80又は第1の面21及び第2の面22の上に他の金属素子を形成することができるが、本明細書に引用することにより本明細書の一部をなす、本願と同一の所有者によって所有される2010年7月23日に出願された米国特許出願第12/842,669号においてより詳細に説明されている特定の技法を用いることができる。このような技法は、例えば、面を、導電性素子がその面の他の部分とは異なるように形成される経路に沿って面のそういった部分を処理するように、レーザで、又はフライス加工若しくはサンドブラスト等の機械的プロセスで選択的に処理することを含みうる。例えば、その面から、特定の経路に沿ってのみ、レーザ又は機械的プロセスを用いて犠牲層等の材料をアブレーション又は除去し、そのようにしてその経路に沿って延在する溝を形成することができる。その後その溝内に触媒等の材料を堆積させることができ、溝内に1つ以上の金属層を堆積させることができる。

20

**【0070】**

フローチャート300のステップ350において、開口部30の形成後(そして所望であれば、誘電体層70及び金属層80の形成後)、開口部内に基材粒子を堆積させることができます。特定の実施形態において、後にフローチャート300のステップ360又はステップ370で除去することができる液体キャリア材料内に基材粒子50を入れることができる。開口部30内への基材粒子50の堆積は、例えば、吐出、インクジェット印刷、レーザ印刷、スクリーン印刷、又はステンシル(stenciling)によって行うことができる。一実施形態において、液体キャリア材料は流動性の成分を含みうる。そのような堆積ステップは、真空チャンバ内で堆積を行って開口部30内への基材粒子50の堆積を助けることによって向上させることができる。代替的には、最初の堆積の間又は後に基板20の反対側から真空を与えて、基材粒子を開口部30内に引き込むのを助けることができる。

30

**【0071】**

例示的な実施形態において、基材粒子50がその中にある状態で開口部30内に送達される液体キャリア材料は、導電性マトリクス材料を含みうる。その後の焼結プロセスにおいて、基板20は焼結温度まで加熱することができる。その加熱中に導電性マトリクス材料は変化を受け、それによってその後、基材粒子50同士を電気的かつ機械的に、永久に接合する。

40

**【0072】**

堆積時、すなわち焼結前、導電性マトリクス材料は、銅や銀等の高融点材料の粒子や薄片と、錫、ビスマス、若しくは錫とビスマスとの組み合わせ等の低融点材料の粒子又は薄片とを含みうる。粒子によっては、金属又は非金属の核、例えばポリマー、シリカ又はグラファイトの核と、その上の、低融点金属等のそれとは異なる金属とを含む構造を有することができる。

**【0073】**

いくつかの例において、導電性マトリクス材料は「反応性」すなわち未硬化のポリマー

50

を含みうる。堆積後、次にその構造体を導電性マトリクス材料の焼結温度まで加熱することができる。この焼結プロセス中、高融点金属と低融点金属とが融解して一緒になり、通常は両者の間に金属間化合物を形成し、オープンセルの泡状の外観を有することができる金属の固体マトリクスを形成する。堆積された導電性マトリクス材料は、焼結プロセス中に蒸発等によってその金属成分から出て行き、導電性マトリクス材料内部に空隙ができるようになる媒体を含みうる。代替的には、導電性マトリクス材料は、反応性ポリマー成分を含みうる。ポリマー成分は通常、焼結プロセスの結果、架橋し硬化する。焼結プロセスの結果、ポリマー成分は金属マトリクスの全体にわたって散在状態になることができ、ポリマー材料は通常その金属マトリクスのオープンセル内でつながって一緒にになっている。そして、金属マトリクスと全体にわたって散在するポリマーとが、固体の導電性構造体を形成することができる。

#### 【0074】

或る特定の条件下では、焼結後、導電性マトリクス材料は固体構造体を形成することができ、この固体構造体は焼結プロセスを行う温度よりも実質的に高温でなければ再溶融( reflowed)できない。特に、導電性材料、例えば、銅でできた少なくとももう1つの他の金属成分との金属間化合物の形成において、低融点金属、例えば錫又はビスマスが実質的に使い果たされる場合に、焼結によってこのような結果を得ることができる。

#### 【0075】

用途によっては、導電性マトリクス材料の焼結温度を、はんだでできた代替的な接続を形成するのに必要な再溶融温度よりも実質的に低い温度にすることができる。銅又は銀等の金属をはんだに加えて、はんだの機械的弾性を向上させ溶融温度を上げることができる。したがって、導電性マトリクス材料で形成した導電性ビア40の構造体は、対応するはんだ接続よりも低い接合温度で、機械的により強固なシステムを提供することができる。

#### 【0076】

そのような場合、そのような導電性マトリクス材料の使用は、より高温の接合プロセスに伴う諸問題を回避するのに役立つことができる。例えば、導電性マトリクス材料を用いて達成されるより低温の接合プロセスは、ガラス転移温度が比較的低い有機材料を含む基板内での望ましくない変化を回避するのに役立つことができる。より低温の接合プロセスはまた、超小型電子素子14と比べて基板20の熱膨張に差があるということに関する、そのような接合プロセス中の諸問題に対処することができる。この場合、より低温の接合プロセスであればパッケージの信頼性の改善につなげることができる。接合プロセス中の熱エクスカーション(thermal excursion: 熱変動)が減ると、組み立てた超小型電子ユニット10内に閉じ込められる応力低減につなげることができるからである。

#### 【0077】

特定の例において、導電性マトリクス材料は堆積される流動性の成分を含みうる。この流動性の成分は、焼結プロセス中の酸化の副生成物を除去するのに役立つことができる。一実施形態において、流動性の成分のない導電性マトリクス材料を用いて接合プロセスを行うことができる。そのような場合、低圧の、例えば部分真空の環境、又は、酸素を取り除いたか若しくは別の気体で置換した環境で、接合プロセスを行うことができる。

#### 【0078】

フローチャート300のステップ360において、開口部30内に基材粒子50を堆積させた後、それぞれの第2の金属層52によって基材粒子同士が互いに溶融して、開口部内に延在する連続的な導電性ビア40を形成するように、基材粒子を加熱することができる。特定の例において、加熱ステップ360の後、導電性ビア40は、接合された基材粒子50同士の間に散在する空隙60を有することができる。そのような空隙60は、導電性ビア40の体積の10%以上を占めることができる。

#### 【0079】

一例において、400と500との間の温度まで基材粒子を加熱することによって基材粒子50同士を冶金接合することができるよう、それぞれの第2の金属層52の融点は400よりも低いものとすることができ、それぞれの第1の金属領域51の融点は

10

20

30

40

50

500 以上とすることができます。一実施形態において、開口部 30 のうちの少なくともいくつかにおける基材粒子 50 のうちの少なくともいくつかは、それぞれの導電性パッド 24 の底面 25 にも冶金接合することができる。特定の実施形態において、フローチャート 300 の加熱ステップ 360 は、基材粒子 50 のうちの少なくともいくつかを金属層 80 に冶金接合することができる。一例において、加熱ステップ 360 の後に、第 1 の面 21 を平坦化するステップを行うことができる。

#### 【0080】

フローチャート 300 のステップ 370において、開口部 30 内からキャリア材料を除去することができる。一実施形態において、基材粒子 50 を加熱した結果、液体キャリア材料は蒸発することができる。特定の実施形態において、加熱ステップ中又はその後に真空処理を行って開口部 30 から流動性の成分を除去することができる。10

#### 【0081】

その後、それぞれの開口部 30 内で延在する境界領域 65 を形成することができる。境界領域 65 がポリマーである実施形態において、絶縁誘電体層 70 に関する上述した方法と同様の方法を用いて境界領域を形成することができる。一例において、境界領域 65 はフローチャート 300 の加熱ステップ 360 及び / 又はキャリア除去ステップ 370 の後で導電性ビア 40 内に残っている空隙 60 のうちの少なくともいくつかの中に堆積されるポリマー媒体とすることができます。そのようなポリマー媒体は、開口部 30 内で第 1 の面 21 及び第 2 の面 22 のうちの少なくとも一方から少なくとも貫入深さ D1 及び / 又は D2 まで延在することができる。20

#### 【0082】

境界領域 65 がはんだである実施形態において、導電性塊 28 に関する上述した方法と同様の方法を用いて境界領域を形成することができる。特定の例において、境界領域 65 はフローチャート 300 の加熱ステップ 360 及び / 又はキャリア除去ステップ 370 の後で導電性ビア 40 内に残っている空隙 60 のうちの少なくともいくつかの中に堆積されるはんだでありうる。そのようなはんだは、開口部 30 内で第 1 の面 21 及び第 2 の面 22 のうちの少なくとも一方から少なくとも貫入深さ D1 及び / 又は D2 まで延在することができます。

#### 【0083】

図 4A 及び図 4B は、代替の構成を有する図 1A 及び図 1B の導電性ビア 40 の変形例を示す。導電性ビア 40a は、間隙粒子 90 及び 90a を含むということを除き、上述の導電性ビア 40 と同じである。特定の実施形態において、例示的な間隙粒子 90 及び 90a のうちの一方又は両方は、導電性ビア 40a の接合された基材粒子 50 同士の間に散在することができる。一例において、間隙粒子 90 及び / 又は 90a は、導電性ビア 40a の構造体に組み込むことができる。一実施形態において、間隙粒子 90 及び / 又は 90a は、導電性ビア 40a の体積の少なくとも 10 % の体積を占めることができる。30

#### 【0084】

1 つ以上の間隙粒子 90 は、図 4A に示すように単一の材料領域を有することができる。そのような材料が単一の間隙粒子 90 は、金属、シリカ、セラミックス、グラファイト、又はポリマー等の材料を含みうる。代替的には、図 4B において見てとれるように、1 つ以上の間隙粒子 90a は、非金属の核領域 91 を有することがある。非金属の各領域 91 は例えば、シリカ、セラミックス、グラファイト、又はポリマー等の材料を含みうる。そのような非金属の核領域 91 は、銅やアルミニウム等の金属でできた第 3 の金属層 92 に囲まれることがある。40

#### 【0085】

特定の実施形態において、それぞれの間隙粒子 90 及び / 又は 90a は、C T E が 10 ppm / よりも小さいものとすることができる。一例において、導電性ビア 40 のヤング率は、最大でビアに含まれる金属（例えば、基材粒子 50 及び金属層 80）及びビアに含まれる間隙粒子の材料（例えば、間隙粒子 90 及び / 又は 90a の材料）のヤング率の 50 % とすることができます。50

## 【0086】

それぞれの導電性ビア40aは、接合された基材粒子50と間隙粒子90及び/又は90aとの間に延在する間隙領域62を含みうる。間隙領域62は、例えばはんだ又はポリマー媒体を含みうる。図4Aに示すように、間隙領域62は導電性ビア40aの高さと等しいものとすることができる貫入深さを貫いて延在することができる(図1Cに示すはんだ領域66と同様)、又は代替的には、間隙領域は、第1の面21及び第2の面22のうちの少なくとも一方に隣接して位置することができ、開口部30内で第1の面21又は第2の面22それから貫入深さD1又はD2まで延在することができる(図1Bに示す境界領域65と同様)。

## 【0087】

導電性ビア40aは、基材粒子50を開口部30内に堆積させるステップ350が基材粒子と間隙粒子90及び/又は90aとの混合物を開口部内に堆積させることを含みうるということを除き、図3に示すフローチャート300を参照して上述したのと同じ方法を用いて形成することができる。加熱ステップ360において、基材粒子50と間隙粒子90及び/又は90aとと一緒に導電性ビア40aの構造体に組み込むことができる。

## 【0088】

図5は、図3のフローチャート300に示す加熱ステップ360の前の図1Eの基材粒子50の実施形態を示す。図5に示す基材粒子550は、外層553と内層554とを有する第2のバイメタル層552を含むということを除き、上述の基材粒子50と同じである。一例において、外層553及び内層554のうちの一方は錫の層とすることができます、外層及び内層のうちの他方は、銀、銅、インジウム、亜鉛、及びビスマスからなる群から選択された金属を含む合金の層とすることができます。

## 【0089】

基材粒子550は、第1の金属領域551と第2のバイメタル層552との間に延在するバリア層555も含む。そのようなバリア層555は、タンゲステン等のバリア金属を含むことができ、バリア金属は、フローチャート300の加熱ステップ360中に第2のバイメタル層552の金属が第1の金属領域551内に拡散する速度を下げることができる。

## 【0090】

導電性ビア40、40'、40''、及び40aは、加熱ステップ360において、それぞれの第1の金属領域551の回りでそれぞれの第2のバイメタル層552が低融点共晶を形成することができるよう、基材粒子を転移液相反応温度まで加熱することができることを除き、図3に示すフローチャート300を参照して上述した方法と同じ方法を用いて、基材粒子550を使って形成することができる。一実施形態において、基材粒子550のうちの隣接するもの同士のうちの少なくともいくつかでできた低融点共晶は、互いに隣接する基材粒子の第1の金属領域551内へと拡散することができる。フローチャート300の加熱ステップ360中に基材粒子550を加熱した後、基材粒子550は図1Eに示す基材粒子50に変わることができる。そのような基材粒子50はそれぞれ、隣接する基材粒子同士を接合して一緒にする第2の金属層52を有することができ、第2の金属層は、内層553及び外層554の金属を含む。

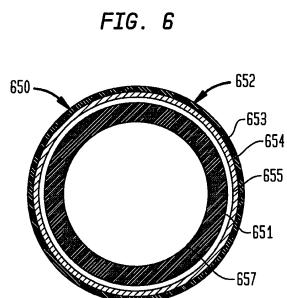

## 【0091】

図6は、図3のフローチャート300に示す加熱ステップ360の前の、図5の基材粒子550の代替のタイプを示す。図6に示す基材粒子650は、第1の金属領域651に囲まれた非金属の核領域657を含むということを除き、上述の基材粒子650と同じである。それぞれの非金属の核領域657は、シリカ、セラミックス、グラファイト、及びポリマーからなる群から選択された1つ又は複数の材料で作製することができる。

## 【0092】

一実施形態において、それぞれの基材粒子650の第1の金属領域651は、厚さが基材粒子の第2の金属層652の厚さよりも厚いものとすることができます。特定の例において、非金属の核領域657は固体の無機誘電材料とすることができます、そのような基材粒子

650を含む導電性ビア40、40'、40''、又は40aのヤング率は、最大で、導電性ビア内に含まれる金属及び固体の無機誘電材料のヤング率の50%とすることができる。

#### 【0093】

一例において、特定の導電性ビア40、40'、40''、又は40aは、基材粒子50、550、及び650のうちのいずれか又は全ての混合物を用いて形成することができる。別の例において、特定の導電性ビア40、40'、40''、又は40aは、間隙粒子90又は90aと基材粒子50、550、及び650のうちのいずれか又は全てとの混合物を用いて形成することができる。

#### 【0094】

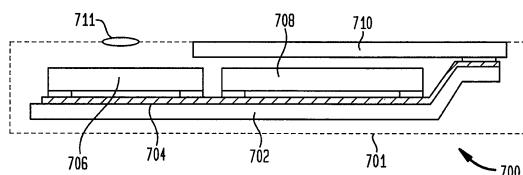

図7に示すように、上述した超小型電子ユニットを、多様な電子システムの構成で利用することができる。例えば、本発明の更なる実施形態によるシステム700は、他の電子コンポーネント708及び710とともに上述したような超小型電子アセンブリ706を含む。説明した例では、コンポーネント708は半導体チップであり、コンポーネント710が表示画面であるが、他の任意のコンポーネントを使用することができる。当然ながら、例示を明確にするように図7には2つの追加のコンポーネントのみを示すが、本システムは、任意の数のこののようなコンポーネントを含みうる。上述した超小型電子アセンブリ706を、上述したような超小型電子ユニットのうちのいずれかとすることができます。更なる変形形態では、任意の数のこののような超小型電子アセンブリ706を使用することができる。

10

#### 【0095】

構造体706並びにコンポーネント708及び710は、破線で概略的に示す共通ハウジング701内に取り付けることができ、必要に応じて互いに電気的に相互接続されて所望の回路を形成することができる。図示する例示的なシステムでは、システムは、可撓性プリント回路基板等の回路パネル702を含むことができ、回路パネルは、コンポーネントを互いに相互接続する多数の導体704を含むことができ、それらのうちの1つのみを図7に示す。しかしながら、これは単に例示的なものであり、電気接続をもたらす任意の適切な構造を使用することができる。

20

#### 【0096】

ハウジング701は、例えば携帯電話又は携帯情報端末における使用可能なタイプの携帯型ハウジングとして示されており、画面710は、ハウジングの表面において露出していることができる。電子アセンブリ706が、撮像チップ等の感光素子を含む場合、光を構造体に誘導するように、レンズ711又は他の光学デバイスも提供することができる。この場合もまた、図7に示す簡略化システムは単に例示的なものであり、上述した構造体を用いて、例えばデスクトップコンピュータ、ルータ等、一般に固定構造体とみなされるシステムを含む他のシステムを作製することができる。

30

#### 【0097】

本明細書に開示されているキャビティ、孔及び導電性素子は、2010年7月23日に出願された、同時係属の本願と同一の譲受人に譲渡された米国特許出願第12/842,587号、同第12/842,612号、同第12/842,651号、同第12/842,669号、同第12/842,692号及び同第12/842,717号に、かつ公開されている米国特許出願公開第2008/0246136号により詳細に開示されているもの等のプロセスによって形成することができ、それらの開示内容は、引用することにより本明細書の一部をなす。

40

#### 【0098】

本発明は特定の実施形態を参照しながら本明細書において説明されてきたが、これらの実施形態は本発明の原理及び応用形態を例示するにすぎないことを理解されたい。それゆえ、添付の特許請求の範囲によって規定されるような本発明の趣旨及び範囲から逸脱することなく、例示的な実施形態に数多くの変更を加えることができること、及び他の構成を案出できることを理解されたい。

50

## 【0099】

特許請求の範囲において記述される種々の従属請求項及び特徴は、初期の請求項において提示されるのとは異なる方法において組み合わせることができるこことを理解されるであろう。また、個々の実施形態との関連で説明された特徴は、記述される実施形態のうちの他の実施形態と共に用できることも理解されるであろう。

## 【産業上の利用可能性】

## 【0100】

本発明は、限定はしないが、電子コンポーネント及び電子コンポーネントを製造する方法を含む、広範な産業上の利用可能性を有する。

【図1A - 1D】

【図1E . 1F】

【図2】

【図3】

【図4】

FIG. 4A

FIG. 4B

【図5】

【図7】

FIG. 7

【図6】

## フロントページの続き

(51)Int.Cl. F I

**H 0 1 L 25/18 (2006.01)**

(74)代理人 100142996

弁理士 森本 聰二

(74)代理人 100154298

弁理士 角田 恭子

(74)代理人 100166268

弁理士 田中 祐

(74)代理人 100170379

弁理士 徳本 浩一

(74)代理人 100161001

弁理士 渡辺 篤司

(74)代理人 100179154

弁理士 児玉 真衣

(74)代理人 100180231

弁理士 水島 亜希子

(74)代理人 100184424

弁理士 増屋 徹

(72)発明者 ウォイチック, チャールズ・ジー

アメリカ合衆国カリフォルニア州95134, サン・ノゼ, オーチャード・パークウェイ 302

5, テッセラ, インコーポレイテッド気付

(72)発明者 デサイ, キショール

アメリカ合衆国カリフォルニア州94539, フリーモント, キャメロン・ヒルズ・コート 18

28

(72)発明者 モハメド, イリヤス

アメリカ合衆国カリフォルニア州95050, サンタ・クララ, ボハノン・ドライブ 2377

(72)発明者 キャスキー, テレンス

アメリカ合衆国カリフォルニア州95134, サン・ノゼ, オーチャード・パークウェイ 302

5, テッセラ, インコーポレイテッド内

審査官 長谷川 直也

(56)参考文献 特開2011-249408 (JP, A)

米国特許出願公開第2005/0121768 (US, A1)

米国特許出願公開第2003/0006066 (US, A1)

特開2007-266183 (JP, A)

特表2009-515354 (JP, A)

特開2005-197733 (JP, A)

特開2000-223836 (JP, A)

## (58)調査した分野(Int.Cl., DB名)

H 0 1 L 21/3205-21/3213、21/768、

23/12-23/15、23/52-23/522、

25/00-25/18、

H 0 5 K 1/11、3/40-3/42