(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4301462号

(P4301462)

(45) 発行日 平成21年7月22日(2009.7.22)

(24) 登録日 平成21年5月1日(2009.5.1)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/78  | (2006.01) | HO1L 29/78 | 301X |

| HO1L 21/768 | (2006.01) | HO1L 29/78 | 301G |

| HO1L 23/522 | (2006.01) | HO1L 21/90 | B    |

| HO1L 29/423 | (2006.01) | HO1L 29/58 | G    |

| HO1L 29/49  | (2006.01) |            |      |

請求項の数 1 (全 15 頁)

(21) 出願番号

特願平9-264141

(22) 出願日

平成9年9月29日(1997.9.29)

(65) 公開番号

特開平11-103054

(43) 公開日

平成11年4月13日(1999.4.13)

審査請求日

平成16年9月28日(2004.9.28)

(73) 特許権者 501285133

川崎マイクロエレクトロニクス株式会社

千葉県千葉市美浜区中瀬一丁目3番地

(74) 代理人 100080458

弁理士 高矢 諭

(74) 代理人 100076129

弁理士 松山 圭佑

(74) 代理人 100089015

弁理士 牧野 剛博

(72) 発明者 木下 英太

東京都千代田区内幸町二丁目2番3号 川崎製鉄株式会社 東京本社内

(72) 発明者 木村 吉孝

東京都千代田区内幸町二丁目2番3号 川崎製鉄株式会社 東京本社内

最終頁に続く

(54) 【発明の名称】電界効果トランジスタ

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板表面の一部に形成された矩形の第1の部分を有するアクティブ領域と、前記アクティブ領域とアクティブでない非アクティブ領域にまたがって形成されたゲート電極とを有する電界効果トランジスタにおいて、

前記非アクティブ領域上に形成された前記ゲート電極の第1のコンタクトと、前記ゲート電極で分割された前記アクティブ領域の一方に設置されたソースのコンタクト及び前記分割されたアクティブ領域の他方に配置されたドレインのコンタクトと、前記非アクティブ領域上に形成された前記ゲート電極の第2のコンタクト又は前記ゲート電極とは異なる他のゲート電極の第3のコンタクトとが、縦横に配置されており、

前記ゲート電極は、前記ソースのコンタクト及びドレインのコンタクトの間に通した直線部分、前記ゲート電極の第1のコンタクトに対応する部分、及び、前記ゲート電極の第1のコンタクトに対応する部分と前記直線部分とを斜めに結ぶ屈曲部分とを有し、

前記ゲート電極の屈曲部分は、前記ゲート電極の第1のコンタクト及び前記ゲート電極の第2又は前記他のゲート電極の第3のコンタクトと前記ソースのコンタクト及び前記ドレインのコンタクトとの間を通る前記アクティブ領域の矩形の第1の部分の1辺を構成する直線状の1辺と鈍角をなして交わり、

前記アクティブ領域は、更に、前記第1の部分の直線状の1辺から前記ゲート電極の第1のコンタクトと前記ゲート電極の第2又は前記他のゲート電極の第3のコンタクトとの間に突き出した、斜辺を有する先細りの凸部である、前記ゲート電極の屈曲部分に隣接し

10

20

て配置されたドレン領域またはソース領域となる第2の部分を有することを特徴とする電界効果トランジスタ。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、拡散層領域をソースからドレンに流れる電流を、該拡散層領域に対して電気的に絶縁させながら該拡散層領域の上方に設けた、ゲート電極に印加する電圧により制御するようにした電界効果トランジスタに係り、特に、集積回路パターン設計の能率低下を抑えながら、限られた集積回路面積の範囲で電界効果トランジスタのアクティブ領域を拡大することで、集積度の低下を抑えながら駆動電流を増大することができる電界効果トランジスタに関する。 10

【0002】

【従来の技術】

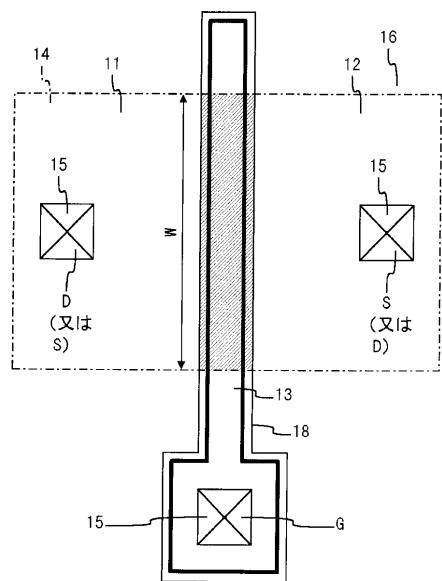

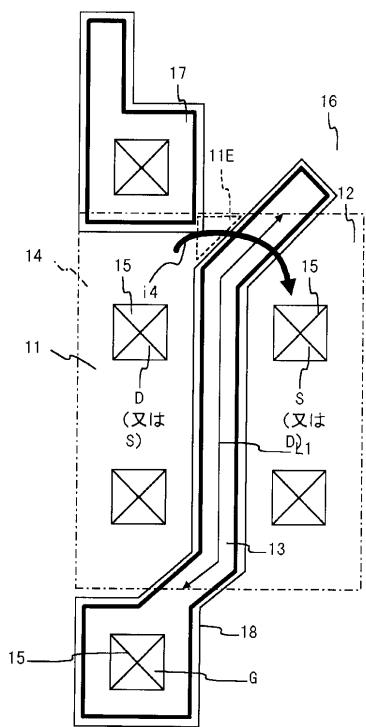

図1は、従来の電界効果トランジスタの構成例を示す。

【0003】

図中、Gはゲート、Dはドレン、Sはソース、11はドレン領域、12はソース領域、13はゲート電極、13の斜線部分はゲート領域である。なおWはいわゆるゲート幅であり、チャネル幅である。又14は拡散層領域であり、前記ドレン領域及び前記ソース領域の境界を形成するアクティブ領域である。16は素子分離領域、又、17は隣接して形成される電界効果トランジスタのゲート電極である。×印の付された正方形の15はコンタクトホールであり、この図1では合計3つある。なお以降、図中の太線はゲート電極を示し、一点鎖線は拡散層領域を示す。 20

【0004】

本従来例では、ゲート領域13の外側にゲート側壁18を設けてドレン電界を緩和するような構造となっている。これは、近年の微細化された電界効果トランジスタにおいて、その長期動作の保証を目的として、いわゆるホットキャリアの発生を抑制し電界効果トランジスタの劣化が進行しにくくするためである。

【0005】

【発明が解決しようとする課題】

前述した電界効果トランジスタは基本的な構成のものであり、半導体集積回路では極めて多数作り込まれている。半導体集積回路のパターン設計では、これら電界効果トランジスタのパターンを如何に能率良く設計していくかが、その設計のほとんどがコンピュータを利用するようになった今日でも極めて重要である。このための様々な技術が開示されているものの、更なる改善が求められている。 30

【0006】

ここで近年の微細化された電界効果トランジスタにおいて、この電界効果トランジスタの駆動電流は、電流経路に直列に挿まったドレン及びソースの寄生抵抗の大小によって大きく変化する。電界効果トランジスタの駆動電流は、前述の図1のゲート幅Wに依存し、該ゲート幅Wを広くする程向上することができる。したがって、限られた回路面積の中で如何にこのゲート幅Wを拡大できるかが、トランジスタを設計する上で大きな課題となり、半導体装置や半導体集積回路のパターン設計の課題となっている。 40

【0007】

本発明は、前記従来の問題点を解決するべくなされたもので、集積回路パターン設計の能率低下を抑えながら、限られた集積回路面積の範囲で電界効果トランジスタのアクティブ領域を拡大することで、集積度の低下を抑えながら該電界効果トランジスタの駆動電流を増大することを目的とする。

【0008】

【課題を解決するための手段】

本発明は、半導体基板表面の一部に形成された矩形の第1の部分を有するアクティブ領域と、前記アクティブ領域とアクティブでない非アクティブ領域にまたがって形成された

ゲート電極とを有する電界効果トランジスタにおいて、前記非アクティブ領域上に形成された前記ゲート電極の第1のコンタクトと、前記ゲート電極で分割された前記アクティブ領域の一方に設置されたソースのコンタクト及び前記分割されたアクティブ領域の他方に配置されたドレインのコンタクトと、前記非アクティブ領域上に形成された前記ゲート電極の第2のコンタクト又は前記ゲート電極とは異なる他のゲート電極の第3のコンタクトとが、縦横に配置されており、前記ゲート電極は、前記ソースのコンタクト及びドレインのコンタクトの間に通した直線部分、前記ゲート電極の第1のコンタクトに対応する部分、及び、前記ゲート電極の第1のコンタクトに対応する部分と前記直線部分とを斜めに結ぶ屈曲部分とを有し、前記ゲート電極の屈曲部分は、前記ゲート電極の第1のコンタクト及び前記ゲート電極の第2又は前記他のゲート電極の第3のコンタクトと前記ソースのコンタクト及び前記ドレインのコンタクトとの間を通る前記アクティブ領域の矩形の第1の部分の1辺を構成する直線状の1辺と鈍角をなして交わり、前記アクティブ領域は、更に、前記第1の部分の直線状の1辺から前記ゲート電極の第1のコンタクトと前記ゲート電極の第2又は前記他のゲート電極の第3のコンタクトとの間に突き出した、斜辺を有する先細りの凸部である、前記ゲート電極の屈曲部分に隣接して配置されたドレイン領域またはソース領域となる第2の部分を有することにより、前記課題を解決したものである。

#### 【0009】

ここで上記の電界効果トランジスタとは、一般的な電界効果トランジスタを示し、例えば前述の図1に示したものと同様に機能する電界効果トランジスタを示すものとする。又上述のように縦横に配置するコンタクト配置予定箇所について本発明は、該コンタクト配置予定箇所の縦の配置間隔と横の配置間隔が同一であることに限定するものではない。更に上述の、拡散層領域には接続されないコンタクトには、単に拡散層領域に未接続のものに限定されるものではなく、該コンタクト自体が存在しないような前述のコンタクト配置予定箇所も含まれる。

#### 【0012】

以下、本発明の作用について簡単に説明する。

#### 【0013】

駆動電流を増加させ集積回路動作速度を高めるためには、電界効果トランジスタの実効的なゲート幅をより広く形成すると共に、このドレイン抵抗またはソース抵抗を如何に減らすかが、トランジスタ設計する上で大きな課題となっている。このようなトランジスタの性能上の課題に加え、本発明では集積回路パターン設計の能率についても考慮している。

#### 【0014】

また本発明ではソース及びドレイン及びゲート電極に対する接続に用いるコンタクトを、縦横に等間隔のコンタクト配置予定箇所に配置するようにしている。このためこれらコンタクトの配置位置の決定は、どのコンタクト配置予定箇所に配置するかの選択的決定となる。このような選択的決定は、配置位置を2次元座標として決定するより容易であり、集積回路パターン設計の能率を改善することができる。

#### 【0015】

又このようにコンタクトをコンタクト配置予定箇所に配置するようにすると、ソース及びドレイン及びゲート電極に対する接続に用いるコンタクトの配置位置の決定に制限が生じる。このため、電界効果トランジスタのゲート幅が短縮されて、該電界効果トランジスタの駆動電流が低下してしまう恐れがある。あるいはゲート幅を拡張すると、集積度が低下してしまう恐れがある。

#### 【0016】

このため本発明では、ソースのコンタクト及びドレインのコンタクトの間に通したゲート電極を、斜めに引き伸ばすようにしている。この斜め引き伸ばしは、後述する実施形態においては、アクティブ領域の第1の部分の直線状の一辺と鈍角で交わる、ゲート電極の第1の部分である。例えば、ゲート電極を、斜めに該ゲート電極用のコンタクトに接続して、電界効果トランジスタを構成してもよい。このようにゲート電極を引き伸ばすように

10

20

30

40

50

して、限られた集積回路面積を効果的に利用して、電界効果トランジスタのゲート幅を拡張することができる。

#### 【0017】

更に本発明では、電界効果トランジスタの拡散層領域を拡張するようにしている。この拡散層領域の拡張は、実施形態において後述する、アクティブ領域の第2の部分である。例えば拡散領域を、その電界効果トランジスタのものをも含めその他の拡散層領域には接続されないコンタクトの間の部分の方向に拡張するようしている。このことによっても、限られた集積回路面積を効果的に利用して、電界効果トランジスタのゲート幅を拡張することができる。

#### 【0018】

10

このように本発明によれば、集積回路パターン設計の能率低下を抑えながら、限られた集積回路面積の範囲で電界効果トランジスタのゲート幅を拡大することで、集積度の低下を抑えながら該電界効果トランジスタの駆動電流を増大することができる。

#### 【0019】

ゲート領域のうち素子分離領域に突き出した部分に隣接するドレイン領域であっても、ドレイン長を長く確保することが可能で、このドレイン領域を流れるドレイン - ソース間電流の経路に直列に挟まるドレイン抵抗を小さく抑制することが可能となる。したがって、この経路を流れるドレイン - ソース間電流を大きくすることができ、これにより電界効果トランジスタ全体の駆動電流を増加させることができるとなる。さらにこの際、ゲート領域の長手方向に突き出した、ソースまたはドレイン領域の凸部を、近接して形成される電界効果トランジスタ等の素子領域に影響を及ぼさない程度に、小さく配置すれば、従来と同一の面積を確保することができ、これにより、集積回路は従来と同一の面積を確保したまま、動作速度の高速化を図ることが可能となる。

#### 【0020】

又、ドレイン電界を緩和しホットキャリア発生を抑制するために、ゲート領域の周囲にゲート側が形成される構成を有する電界効果トランジスタにおいては、ゲート側壁直下のシート抵抗は、ドレイン領域ソース領域に比較してはるかに高くなっているので、上記のドレイン - ソース間電流増加の効果は更に大きくなり、集積回路は一層の動作速度の高速化を図ることができる。

#### 【0021】

##### 【発明の実施の形態】

以下、図を用いて本発明の実施の形態を詳細に説明する。

#### 【0022】

前述の従来例及び以下の比較例や実施形態ではいずれも、同符号は同一のものを表わし、太線はゲート電極を表わす。又以下の比較例や実施形態では、電界効果トランジスタはNチャネル型のトランジスタを用いている。ソース及びドレイン及びゲート電極に対する接続に用いるコンタクトは、縦横に等間隔のコンタクト配置予定箇所に配置するようになされている。斜線部分はいずれも、本発明に係る拡散層領域の拡張部分である。但しゲート電極13の延長に伴って拡張されている拡散層領域は、特に斜線は付されていない。

#### 【0023】

40

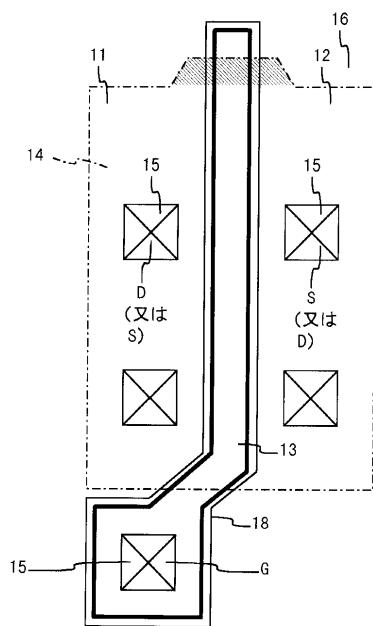

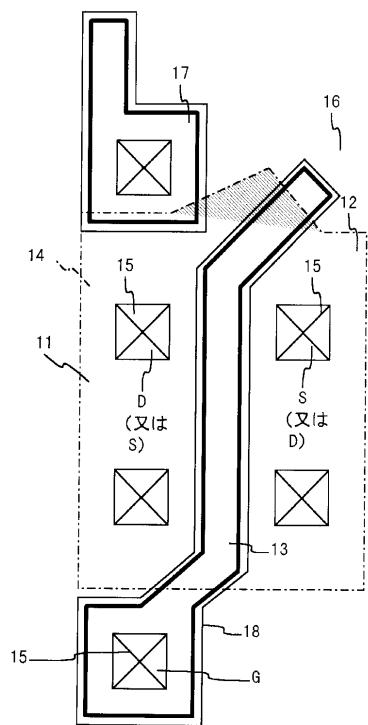

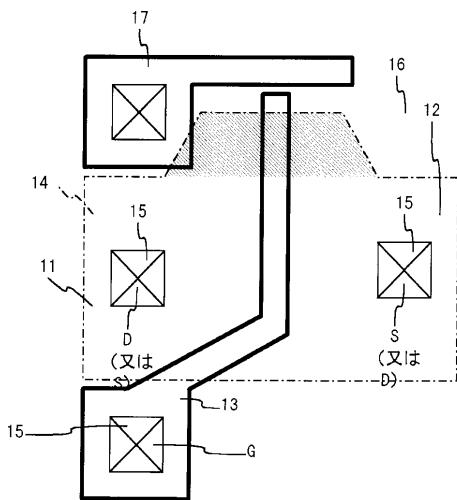

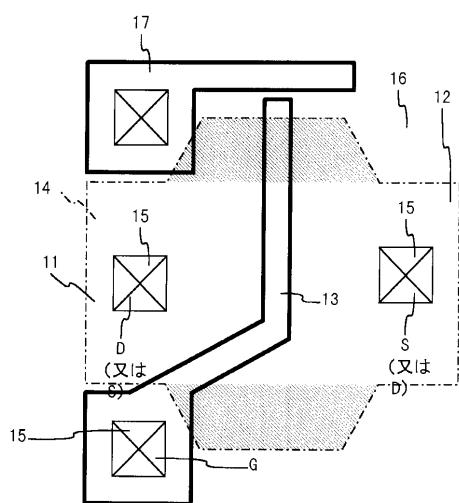

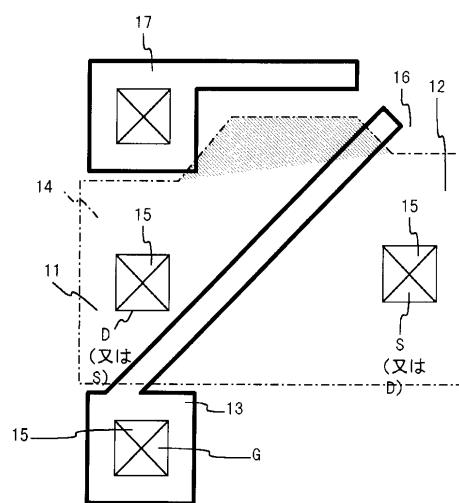

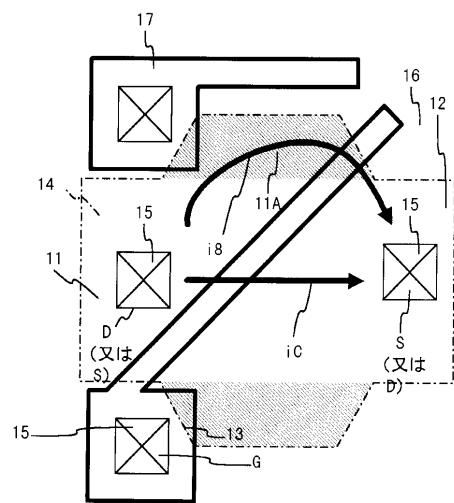

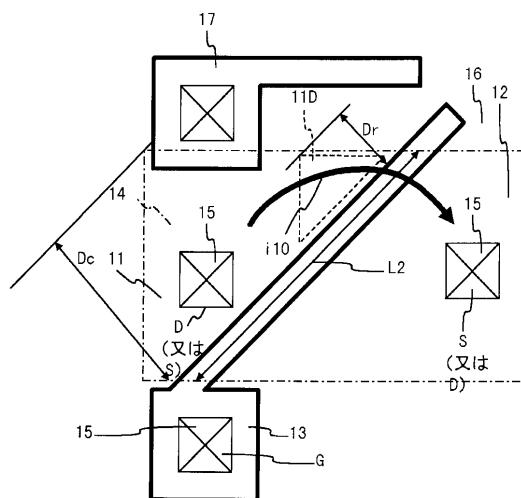

図2～図5はそれぞれ、第1～第4比較例の集積回路レイアウト図である。

#### 【0024】

これら比較例では、ドレインの接続に用いる2つのコンタクトと、ソースの接続に用いる2つのコンタクトとの間に、これら図2～図5において上下方向にゲート電極13が通されている。又該ゲート電極13は左斜め下にというように、斜めに図中最左下のコンタクト15に接続されている。なお17は隣接して形成される電界効果トランジスタのゲート電極である。

#### 【0025】

次にまず第1比較例では斜線で示されるように、上方に拡散層領域の少なくとも一部が拡張されている。この図2の電界効果トランジスタに対して、その上方にはコンタクト1

5が設けられていない、コンタクト配置予定箇所がある。このように本比較例では、図示される電界効果トランジスタのものをも含めその他の拡散層領域には接続されないコンタクトの間の部分の方向に拡張されている。

#### 【0026】

次に第2～第4比較例では、ドレインの接続に用いる2つのコンタクトと、ソースの接続に用いる2つのコンタクトとの間にあるゲート電極13が、図中右上に延長されている。即ち、コンタクトが配置されていない前記コンタクト配置予定箇所の方に斜めに引き伸ばし、延長されている。又、該延長に伴って拡散層領域を拡張する。

#### 【0027】

又第2比較例では図3の斜線で示されるように、上方に拡散層領域の少なくとも一部が拡張されている。あるいは、第3比較例では図4の斜線で示されるように、上方及び下方に都合2箇所、拡散層領域の少なくとも一部が拡張されている。10

#### 【0028】

図3や図4の電界効果トランジスタに対して、図中最左上のコンタクト15は、該電界効果トランジスタに未使用であり、又該コンタクト15の右方には、コンタクト15が設けられていない、コンタクト配置予定箇所がある。このようにこれら比較例では、図示される電界効果トランジスタのものをも含めその他の拡散層領域には接続されないコンタクトの間の部分の方向に拡張されている。

#### 【0029】

又図4では、図中にある電界効果トランジスタに対して、図中最左下のコンタクト15は、その電界効果トランジスタのものをも含めその他の拡散層領域には接続されない。又該コンタクト15の右方には、コンタクト15が設けられていない、コンタクト配置予定箇所がある。これらコンタクトの間にもこのように第3実施形態では、拡散層領域が拡張されている。20

#### 【0030】

このように拡散層領域を拡張することで、集積回路レイアウトで未使用の領域を効果的に活用し前記拡散層領域を拡張し、これにより限られた集積回路面積の範囲で電界効果トランジスタのゲート幅を拡大することができる。

#### 【0031】

図6～図10はそれぞれ、第5～第9比較例の集積回路レイアウト図である。30

#### 【0032】

前述の第1～第4比較例では、コンタクト配置予定箇所の横方向で最小間隔の間に、ゲート電極13が通されていた。これらに対してここで考える第5～第9比較例では、コンタクト配置予定箇所の横方向で最小間隔が2つ分の間に、ゲート電極13が通されている。なお第5～第9比較例では、ドレインの接続に用いる1つのコンタクトと、ソースの接続に用いる1つのコンタクトとの間に、これらの図6～図10において上下方向にゲート電極13が通されている。

#### 【0033】

特に第5及び第6比較例では、上下に図中垂直に通されるゲート電極13が、該垂直部の下端で左斜め下にというように、斜めに図中最左下のコンタクト15に接続されている。これら第5及び第6比較例のゲート電極13はこのような形状であり、前述の第1比較例のゲート電極13の形状に類似している。40

#### 【0034】

一方、第7～第9比較例ではゲート電極13は、ドレインのコンタクトと、ソースの接続のコンタクトとの間の部分から直接、斜めに図中最左下のコンタクト15に接続されている。このような図中でゲート電極13の垂直部分がない第7～第9比較例についても、前述のようにソース及びドレイン及びゲート電極に対する接続に用いるコンタクトをコンタクト配置予定箇所に配置するようにし、集積回路パターン設計の能率低下を抑えながら、限られた集積回路面積の範囲で電界効果トランジスタのゲート幅を拡大することができる。50

## 【0035】

又第5及び第7比較例では図6や図8の斜線で示されるように、上方に拡散層領域の少なくとも一部が拡張されている。あるいは、第6及び第8比較例では図7や図9の斜線で示されるように、上方及び下方に、拡散層領域の少なくとも一部が拡張されている。

## 【0036】

図6や図8の電界効果トランジスタに対して、図中最左上のコンタクト15は、該電界効果トランジスタに未使用であり、又該コンタクト15の右方には、コンタクト15が設けられていない、コンタクト配置予定箇所がある。このようにこれら比較例では、図示される電界効果トランジスタのものをも含めその他の拡散層領域には接続されないコンタクトの間の部分の方向に拡張されている。

10

## 【0037】

又図7や図9では、図中にある電界効果トランジスタに対して、図中最左下のコンタクト15は、その電界効果トランジスタのものをも含めその他の拡散層領域には接続されない。又該コンタクト15の右方には、コンタクト15が設けられていない、コンタクト配置予定箇所がある。これらコンタクトの間にこのように第6及び第8比較例では拡散層領域が拡張されている。

## 【0038】

このように拡散層領域を拡張することで、集積回路レイアウトで未使用の領域を効果的に活用し前記拡散層領域を拡張し、これにより限られた集積回路面積の範囲で電界効果トランジスタのゲート幅を拡大することができる。

20

## 【0039】

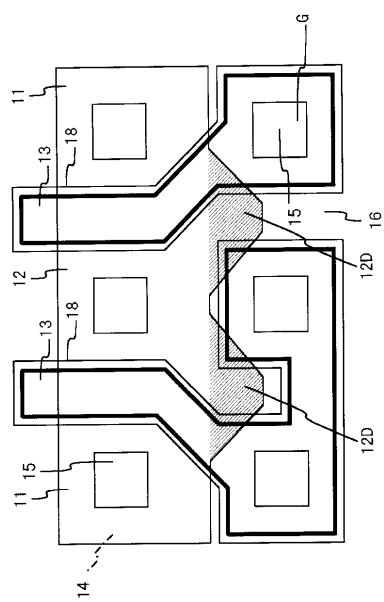

次に図11は、本発明が適用された実施形態の集積回路レイアウト図である。

## 【0040】

本実施形態では2つのゲート電極13がいずれも、ドレインの接続に用いる1つのコンタクトと、ソースの接続に用いる1つのコンタクトとの間に通されている。

## 【0041】

又上下に図中垂直に通される2つのゲート電極13がそれぞれ、左のものは該垂直部の下端で左斜め下に、右のものは該垂直部の下端で右斜め下に、というように、斜めに図中最左下あるいは最右下のコンタクト15に接続されている。これらゲート電極13はこのような形状であり、前述の第1比較例のゲート電極13の形状に類似している。

30

## 【0042】

又本実施形態では図11の斜線で示されるように、下方に拡散層領域の少なくとも一部が拡張されている。図11の電界効果トランジスタに対して、図中下段3個のコンタクト15は、拡散層領域の接続に未使用である。このようにこれら実施形態では、図示の電界効果トランジスタのものをも含めその他の拡散層領域には接続されないコンタクトの間の部分の方向に拡散層領域の少なくとも一部が拡張されている。

## 【0043】

このように拡散層領域を拡張することで、集積回路レイアウトで未使用の領域を効果的に活用し前記拡散層領域を拡張し、これにより限られた集積回路面積の範囲で電界効果トランジスタのゲート幅を拡大することができる。

40

## 【0044】

本実施形態では、2つの電界効果トランジスタが隣接して配置されており、それぞれのゲート領域13の屈曲部位に隣接して、斜線を付したソース領域の凸部12Dが配置されている。本実施形態における駆動電流増加のメカニズムは、前述の比較例の場合と同様である。

## 【0045】

ここで前述の第8比較例を第9比較例と比較し、又前述の第3比較例を第4比較例と比較し、斜線で示した拡散層領域の拡張について考える。

## 【0046】

第9比較例のゲート領域13を前述のように斜めに配置する。これは、近接して形成さ

50

れる電界効果トランジスタ等の素子領域に影響を及ぼすことなく、図10中でL2で示した電界効果トランジスタの実効的なチャネル幅を長さのように、アクティブ領域14の幅よりも長く形成し、電界効果トランジスタの駆動電流を増加させて、半導体集積回路をより高速に動作させるためである。

#### 【0047】

又第4比較例の図5に示した電界効果トランジスタにおいては、ゲート領域13は直線状ではなく2箇所で屈曲している。これは、ゲート領域13をこのように屈曲させることで、近接して形成される電界効果トランジスタ等の素子領域に影響を及ぼすことなく、ゲート領域を単に直線状に配置した場合よりも、図5中L1で示す、電界効果トランジスタの実効的なゲート幅を長く形成し、電界効果トランジスタの駆動電流を増加させて、半導体集積回路をより高速に動作させるためである。10

#### 【0048】

近年の微細化された電界効果トランジスタにおいては、電流経路に直列に挟まつたドレイン及びソースの寄生抵抗の大小によって、電界効果トランジスタの駆動電流が大きく変化する。したがって、駆動電流を増加させ集積回路動作速度を高めるためには、上記で述べたように電界効果トランジスタの実効的なチャネル幅をより長く形成すると共に、このドレイン抵抗またはソース抵抗を如何に減らすかが、トランジスタ設計する上の大きな課題となっている。

#### 【0049】

まず第8比較例を第9比較例と比較し、斜線で示した拡散層領域の拡張について考える。20

#### 【0050】

図10に示した第9比較例においては、ゲート領域13のうちの素子分離領域16に突き出した部分に近接する、破線で示すドレイン領域11Dでは、ゲート領域13とドレイン領域端53との距離であるドレイン長D<sub>p</sub>が、電界効果トランジスタ中央部のD<sub>c</sub>よりもはるかに短くなっている。このため、このドレイン領域11Dを流れるドレイン-ソース間電流の経路i10には、狭いドレイン長D<sub>p</sub>に対応した高抵抗のドレイン抵抗が、寄生抵抗として直列に挟まることになる。したがって、経路i10を流れる電流は小さく、このドレイン領域11Dは、電界効果トランジスタの駆動電流増加に、それほど大きな寄与をしない。30

#### 【0051】

これに対して第8比較例の電界効果トランジスタでは、ゲート領域13のうち素子分離領域16に突き出した部分に隣接してドレイン領域に、斜線部の凸部11Aが設けられており、この部位ではドレイン長が極端に短くなることがない。このため、この凸部を含むドレイン領域を流れるドレイン-ソース間電流の経路i8においては、直列に挟まるドレイン寄生抵抗は、この比較的広いドレイン長に対応した比較的低い抵抗となる。したがって、経路i8を流れる電流は、ゲート領域中央部を流れる電流iCとほぼ同様の電流密度とすることができます。よって、従来の場合と同一の面積でありながら、より駆動電流の大きな電界効果トランジスタとなる。

#### 【0052】

なお、第8比較例の説明から容易に類推されるように、ゲート領域の長手方向に突き出した、凸部というのは、ドレイン領域側だけではなく、ソース領域側に設置されたものでも、上記同様の直列抵抗低減による駆動能力向上の効果を有する。しかもソース側抵抗が小さくなることにより電界効果トランジスタの基板バイアス効果が弱まり、ドレイン領域側に凸部を配置した場合よりも、駆動電流増加の割合は大きくなる。40

#### 【0053】

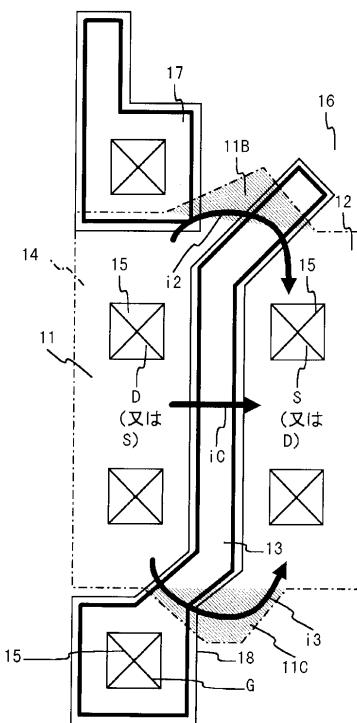

ここで前述の第3比較例を第4比較例と比較し、斜線で示した拡散層領域の拡張について考える。

#### 【0054】

図5の第4比較例のような、ゲート領域13が屈曲し、ゲート側壁18を有する構造の50

電界効果トランジスタにおいては、ゲート領域 13 のうちの素子分離領域 16 に突き出した部分に隣接する、破線で示すドレイン領域 11E は、ゲート側壁を有さない電界効果トランジスタの場合よりも、更に狭くなっている。ゲート側壁直下のシート抵抗は、ドレイン領域ソース領域に比較してはるかに高いので、ドレイン - ソース間電流の経路 i4 に直列に挟まつたドレイン寄生抵抗は大幅に増加する。このため、この電流経路 i4 は電界効果トランジスタの駆動電流にほとんど寄与しないという結果になる。

#### 【0055】

これに対して図 4 の第 3 比較例では、ゲート領域 13 の 2箇所の屈曲部位に隣接するよう、斜線を付したドレイン領域の凸部 11B 及びソース領域の凸部 11C が配置されている。本比較例では、ゲート領域 13 を囲むように、ゲート側壁 18 が形成されているが、図から容易にわかるように、ドレイン領域凸部 11B 及びソース領域凸部 11C があることにより、図 8 の場合よりも更に効果的に、十分なドレイン長及びソース長を確保することが可能となっている。このため、ドレイン凸部 11B を含むドレイン領域を流れるドレイン - ソース間電流の経路 i2 においては、直列に挟まるドレイン寄生抵抗は、この比較的広いドレイン長に対応した比較的低い抵抗となり、又ソース凸部 11C を含むソース領域を流れるドレイン - ソース間電流の経路 i3 においても、直列に挟まるソース寄生抵抗は、この比較的広いソース長に対応した比較的低い抵抗となる。したがって、経路 i2 及び i3 を流れる電流は、ゲート領域中央部を流れる電流 iC とほぼ同様の電流密度とすることができ、従来の場合と同一の面積でありながら、より駆動電流の大きな電界効果トランジスタとなる。

10

20

#### 【0056】

ここで前述の第 3 比較例、第 8 比較例及び本発明の実施形態の電界効果トランジスタにおいてそれぞれ、ドレイン領域凸部及びソース領域凸部の有無による駆動電流増加の効果の相違は以下の表 1 のとおりである。

#### 【0057】

##### 【表 1】

|             | 凸部の有   | 凸部の無   | 駆動電流増加 |

|-------------|--------|--------|--------|

| 第 3 比較例     | 2.01mA | 1.84mA | +9.5%  |

| 第 8 比較例     | 1.68mA | 1.62mA | +3.8%  |

| 本発明<br>実施形態 | 0.85mA | 0.79mA | +7.4%  |

30

40

#### 【0058】

なお上記の測定条件は、下記のとおりである。

#### 【0059】

##### 【表 2】

|                       | 第3比較例          | 第8比較例  | 本発明<br>実施形態 |    |

|-----------------------|----------------|--------|-------------|----|

| ゲート長<br>(チャネル長)       | 0.35 μm        | 0.4 μm | 0.35 μm     |    |

| ゲート側壁幅                | 150nm          | (なし)   | 150nm       | 10 |

| ソースドレイン<br>領域シート抵抗    | 70Ω/□          | 70Ω/□  | 70Ω/□       |    |

| ゲート側壁直下<br>(LDD)シート抵抗 | 5kΩ/□          | (なし)   | 5kΩ/□       |    |

| ゲート直線部長さ              | 2.8 μm         | 2.6 μm | 2.6 μm      | 20 |

| ゲート屈曲部長さ              | 1.5 μm(両<br>側) | (なし)   | 0.7 μm      |    |

| ゲート屈曲角度               | 45度            | 45度    | 45度         |    |

| ゲート突き出し部<br>長さ        | 0.6 μm         | 0.6 μm | 0.4 μm      | 30 |

## 【0060】

なお上記の測定条件において、ゲート部長さとは、ゲート電極中心線に沿った長さを測ったものである。ゲート直線部長さとは、ゲート電極中央部の直線部分についての長さである。ゲート屈曲部長さとは、屈曲部分について、屈曲部分からアクティブ端までの距離である。ゲート突き出し部長さとは、ゲートがアクティブ端の外側(素子分離領域)に突き出した部分の長さである。

## 【0061】

又上記においてソース・ドレイン  $I_{ds}$  の測定の、ゲート・ソース電圧  $V_{gs}$  及びドレイン・ソース電圧  $V_{ds}$  の条件は下記のとおりである。

## 【0062】

$$V_{gs} = 3.3 \text{ V} \quad \dots (1)$$

$$V_{ds} = 3.3 \text{ V} \quad \dots (2)$$

## 【0063】

上記からわかるように、本発明による、電界効果トランジスタの駆動電流増加の効果は明らかである。

## 【0064】

なお、以上説明してきたドレイン領域及びソース領域の凸部形状は、本実施例で示した台形に限る必要はなく、ドレインまたはソースの寄生抵抗低減の効果を有する配置がなされ

るならば、三角形でも、四角形でもよいのはいうまでもない。

【0065】

ここで、アクティブ領域の第1の部分を、例えば図1の従来例での矩形の拡散層領域14とする。又アクティブ領域の第2の部分を、前述した実施形態における拡散層領域14の斜線部分とし、付加される凸部とする。

【0066】

すると半導体基板表面に形成されたアクティブ領域と、前記アクティブ領域上に形成されたゲート電極とを有し、前記ゲート電極のコンタクトと、前記ゲート電極で分割された前記アクティブ領域の片側に設置されるコンタクトとが概略直線状に設置された電界効果トランジスタを考えることができる。又このような電界効果トランジスタであって、前記アクティブ領域は、直線状の1辺を有する第1の部分を含み、前記ゲート電極の少なくとも1辺は、前記アクティブ領域の第1の部分の直線状の1辺と鈍角で交わる第1の部分を有し、前記アクティブ領域が、更に、前記ゲート電極の第1の部分と交わる部分において、前記第1の部分の直線状の1辺に接続され、外側に広がる第2の部分を含むことを特徴とする電界効果トランジスタは、本発明の1つとなる。これはアクティブ領域という表現を用いて表わした本発明の1つの電界効果トランジスタ例である。

10

【0067】

又該電界効果トランジスタ例において、前記アクティブ領域の第2の部分の1辺が、前記ゲート電極の第1の部分と概略直交することを特徴とする電界効果トランジスタは1つの変形例である。

20

【0068】

前記電界効果トランジスタ例において、前記アクティブ領域の第2の部分が、前記ゲート電極の第1の部分から、ゲート電極の幅以上の距離にまで広がっていることを特徴とする電界効果トランジスタは1つの変形例である。

【0069】

前記電界効果トランジスタ例において、前記アクティブ領域の第1の部分が、概略方形であることを特徴とする電界効果トランジスタは1つの変形例である。

【0070】

前記電界効果トランジスタ例において、前記アクティブ領域の第2の部分は、前記第1の部分の直線状の1辺の一部にのみ接続されていることを特徴とする電界効果トランジスタは1つの変形例である。

30

【0071】

前記電界効果トランジスタ例において、前記アクティブ領域が、前記ゲート電極下のチャネル領域と、前記チャネル領域に隣接した一定幅の第1の拡散領域と、その外側の前記第1の拡散領域に比較して抵抗が低い、第2の拡散領域とを含むことを特徴とする電界効果トランジスタは1つの変形例である。

【0072】

又本発明を利用した半導体装置を製造するためのマスクパターンの設計方法を考える。即ち、半導体基板表面に形成されたアクティブ領域と、前記アクティブ領域上に形成されたゲート電極とを有し、前記ゲート電極のコンタクトと、前記ゲート電極で分割された前記アクティブ領域の片側に設置されるコンタクトとが概略直線状に設置された半導体素子、を製造するためのマスクパターンの設計方法を考える。このマスクパターンの設計方法の1つとして、直線状の1辺を有する第1の部分を含む、前記アクティブ領域形成用マスクパターンを配置する手順と、少なくとも1辺が、前記アクティブ領域の第1の部分と鈍角で交わる第1の部分を有する、前記ゲート電極形成用マスクパターンを配置する手順と、前記アクティブ領域形成用マスクパターンの、前記ゲート電極形成用マスクパターンの第1の部分と交わる部分に、前記第1の部分の直線状の1辺に接続して、外側に広がる第2の部分を追加する手順とを含むことを特徴とする半導体装置のマスクパターンの設計方法によって、本発明を利用した半導体装置を製造することができる。

40

【0073】

50

### 【発明の効果】

以上、詳細に説明したように、本発明によれば、集積回路パターン設計の能率低下を抑えながら、限られた集積回路面積の範囲で電界効果トランジスタのゲート幅を拡大することで、集積度の低下を抑えながら該電界効果トランジスタの駆動電流を増大することができる。

### 【0074】

又以下のような効果を得ることができる。

### 【0075】

ゲート領域のうち素子分離領域に突き出した部分に隣接するドレイン領域であっても、ドレイン長を長く確保することが可能で、このドレイン領域を流れるドレイン-ソース間電流の経路に直列に挿まるドレイン抵抗を小さく抑制することが可能となる。したがって、この経路を流れるドレイン-ソース間電流を大きくすることができ、これにより電界効果トランジスタ全体の駆動電流を増加させることができるとなる。さらにこの際、ゲート領域の長手方向に突き出した、ソースまたはドレイン領域の凸部を、近接して形成される電界効果トランジスタ等の素子領域に影響を及ぼさない程度に、小さく配置すれば、従来と同一の面積を確保することができ、これにより、集積回路は従来と同一の面積を確保したまま、動作速度の高速化を図ることが可能となる。

10

### 【0076】

又、ドレイン電界を緩和しホットキャリア発生を抑制するために、ゲート領域の周囲にゲート側が形成される構成を有する電界効果トランジスタにおいては、ゲート側壁直下のシート抵抗は、ドレイン領域ソース領域に比較してはるかに高くなっているので、上記のドレイン-ソース間電流増加の効果は更に大きくなり、集積回路は一層の動作速度の高速化を図ることができる。

20

### 【図面の簡単な説明】

【図1】従来からの一般的な電界効果トランジスタの集積回路レイアウト図

【図2】第1比較例の電界効果トランジスタの集積回路レイアウト図

【図3】第2比較例の電界効果トランジスタの集積回路レイアウト図

【図4】第3比較例の電界効果トランジスタの集積回路レイアウト図

【図5】第4比較例の電界効果トランジスタの集積回路レイアウト図

30

【図6】第5比較例の電界効果トランジスタの集積回路レイアウト図

【図7】第6比較例の電界効果トランジスタの集積回路レイアウト図

【図8】第7比較例の電界効果トランジスタの集積回路レイアウト図

【図9】第8比較例の電界効果トランジスタの集積回路レイアウト図

【図10】第9比較例の電界効果トランジスタの集積回路レイアウト図

【図11】本発明が適用された実施形態の電界効果トランジスタの集積回路レイアウト図

### 【符号の説明】

G ... ゲート

D ... ドレイン

S ... ソース

1 1 ... ドレイン領域

40

1 2 ... ソース領域

1 3 ... ゲート電極

1 4 ... 拡散層領域

1 5 ... コンタクト

1 6 ... 素子分離領域

1 7 ... 隣接する電界効果トランジスタのゲート電極

1 8 ... ゲート側壁

W ... ゲート幅

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

---

フロントページの続き

(72)発明者 飯田 重雄

東京都千代田区内幸町二丁目2番3号 川崎製鉄株式会社 東京本社内

審査官 松嶋 秀忠

(56)参考文献 特開平03-089555(JP,A)

特開平02-170437(JP,A)

特開平04-164371(JP,A)

特開平04-370966(JP,A)

特開平09-134967(JP,A)

特開平05-190817(JP,A)

米国特許第5539246(US,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/768

H01L 23/522

H01L 29/423

H01L 29/49

H01L 29/78

H01L 21/336