(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization International Bureau

(43) International Publication Date

22 April 2004 (22.04.2004)

PCT

(10) International Publication Number

**WO 2004/034422 A2**

(51) International Patent Classification<sup>7</sup>:

**H01L**

KLOSOWIAK, Tomasz; 308 Greenfield Drive, Glenview, IL 60025 (US).

(21) International Application Number:

PCT/US2003/027964

(74) Agents: NICHOLS, Daniel K. et al.; MOTOROLA, INC., Intellectual Property Department, 1303 East Algonquin Road, Schaumburg, IL 60196 (US).

(22) International Filing Date:

5 September 2003 (05.09.2003)

(81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VC, VN, YU, ZA, ZM, ZW.

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

10/241,265 11 September 2002 (11.09.2002) US

(71) Applicant: MOTOROLA, INC., A CORPORATION OF THE STATE OF DELAWARE [US/US]; 1303 East Algonquin Road, Schaumburg, IL 60196 (US).

(72) Inventors: QI, Jing; 1120 E. Algonquin Road #10, Schaumburg, IL 60173 (US). DANVIR, Janice; 1317 N. Harvard, Arlington Heights, IL 60004 (US).

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PT, RO, SE, SI, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

*[Continued on next page]*

(54) Title: WAFER COATING AND SINGULATION METHOD

WO 2004/034422 A2

(57) **Abstract:** A wafer is first diced (22) on the active surface side to form channels (38) that will ultimately define the edges (39) of individual integrated circuit chip, the dicing being of such a depth that it only cuts part-way through the wafer. The front side (36) of the wafer is then coated (24) with an underfill material (40). The back side of the wafer is then lapped, ground, polished or otherwise treated (26) so as to remove material down to the level of the previously diced channels. The wafer is then singulated (28) by cutting the underfill material (92) that was deposited in the channels during the coating step, so that the integrated circuit chip (12) is released from the wafer.

**Published:**

- without international search report and to be republished upon receipt of that report

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

WAFER COATING AND SINGULATION METHODFIELD OF THE INVENTION

5 This invention relates generally to a wafer-level method of providing an underfill material on flip chip integrated circuits. More particularly, the present invention relates to a method in which a bumped wafer is partially diced prior to the application of a polymeric underfill material.

10 BACKGROUND OF THE INVENTION

There are a number of conventional processes for packaging integrated circuits. One approach which is commonly referred to as "flip chip" packaging generally contemplates forming solder bumps (or other suitable contacts) directly on the contact pads formed on an integrated circuit die. The die is then typically attached to a substrate such as a printed circuit board so that the die contacts directly connect to corresponding contacts on the substrate. The solder bumps are then reflowed to electrically connect the die to the substrate. When a flip chip is attached to the substrate, an air gap typically remains between flip chip and substrate. This gap is commonly filled with material that is flowed into the gap in liquid form and then solidified. This material is typically a mixture of a resin and small silica spheres and is generally referred to as underfill, as it fills the gap under the chip. The underfill material is applied in liquid form from a dispenser at one edge of the flip chip. The underfill material then flows into the air gap and spreads across the flip chip until finally the entire area of the gap between flip chip and substrate is filled.

25 There are problems associated with underfill. For example, the application of underfill must be repeated for each flip chip, and repeating this operation many times adds to the cost of manufacture. Also, as the underfill material flows past solder bumps to fill the gap, separation of glass from resin may occur. This segregation of silica and resin alters the mechanical properties of the filled region and thereby negates the mechanical function of the underfill.

30 Recently, advances have been made which improve and streamline the underfill process. One method that has shown some commercial interest involves

dispensing underfill before assembling the flip chip to the board. While simplifying the flip chip process, it still requires extra steps and cannot be run on a standard surface mount assembly line. Another approach to solving these problems appears in U.S. Patent 6,323,062 where a method for applying an underfill and edge coating to a flip chip is described. The method includes the steps of adhering a bumped wafer to an expandable carrier substrate, sawing the wafer to form individual chips, stretching the carrier substrate in a bidirectional manner to form channels between each of the individual chips, applying an underfill material to the bumped surfaces of the chips and around the edges of the chips, cutting the underfill material in the channels between the chips and removing the individual, underfill coated chips from the carrier. Unfortunately, this method suffers from the need to precisely control the bidirectional stretching of the carrier film, which is difficult to implement, and introduces new issues such as out of plane die.

In spite of the numerous advantages provided by flip chip technology, a need still exists for a lower cost underfill application process for flip chips which simplifies the application of the critical underfill, and reduces the number of process steps required.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The features of the invention believed to be novel are set forth with particularity in the appended claims. The invention itself however, both as to organization and method of operation, together with objects and advantages thereof, may be best understood by reference to the following detailed description of the invention, which describes certain exemplary embodiments of the invention, taken in conjunction with the accompanying drawings in which:

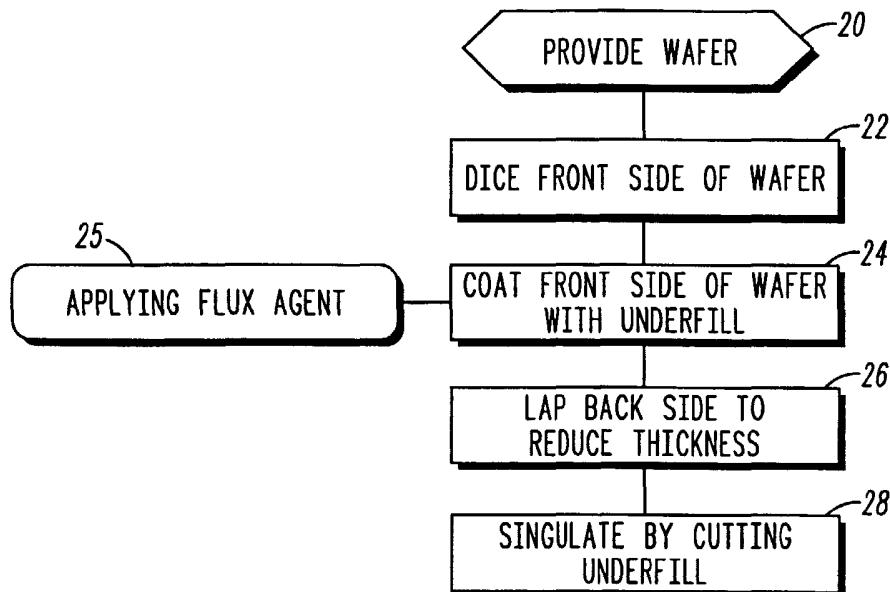

FIG. 1 is a plan view of a wafer containing one or more integrated circuit flip chips in accordance with the present invention.

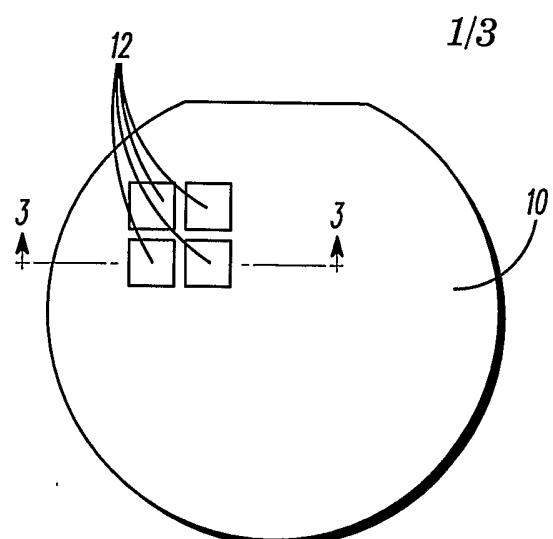

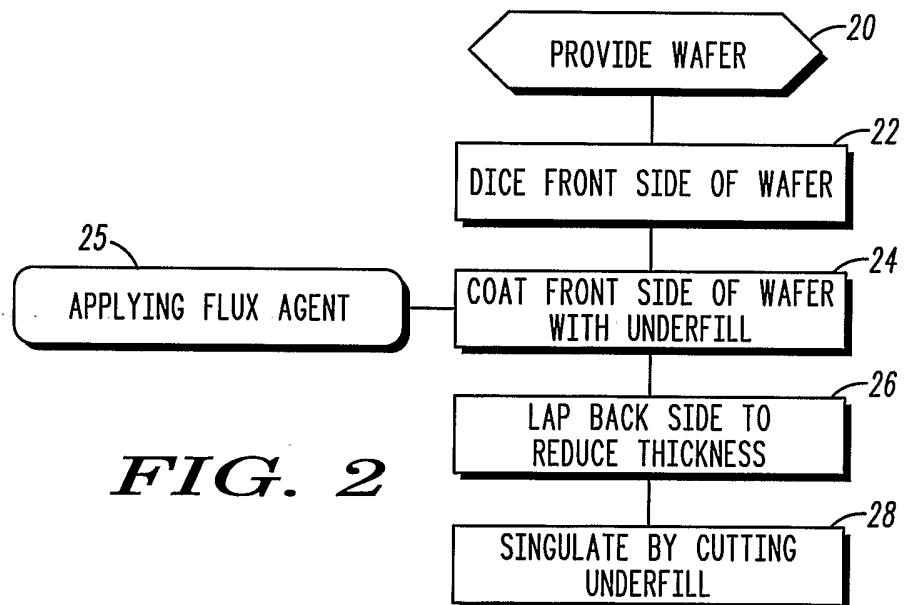

FIG. 2 is a flowchart detailing the process for providing an underfill material on an integrated circuit chip in accordance with certain embodiments of the present invention.

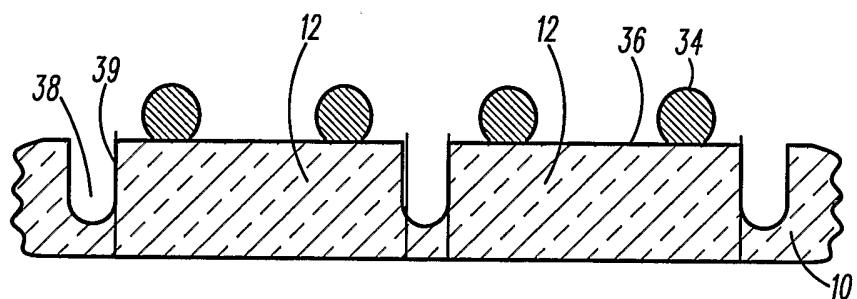

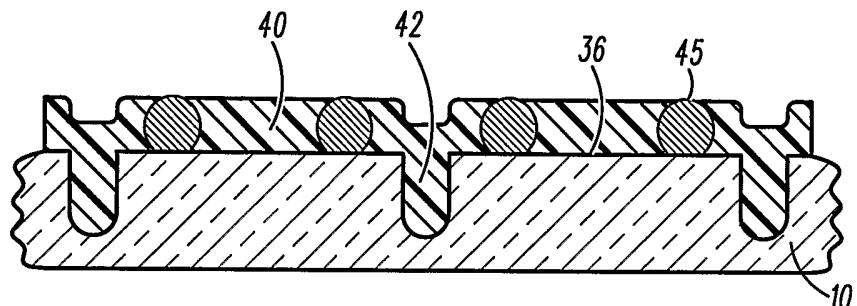

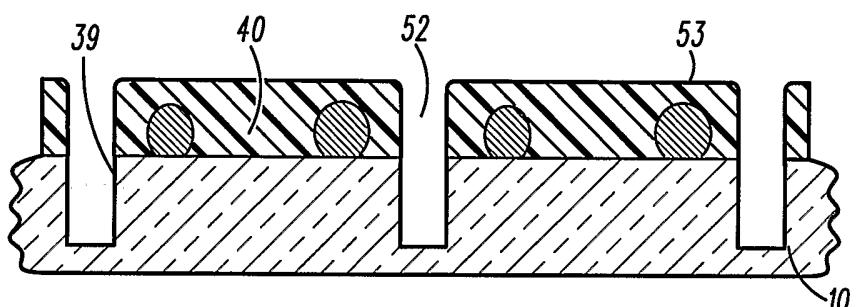

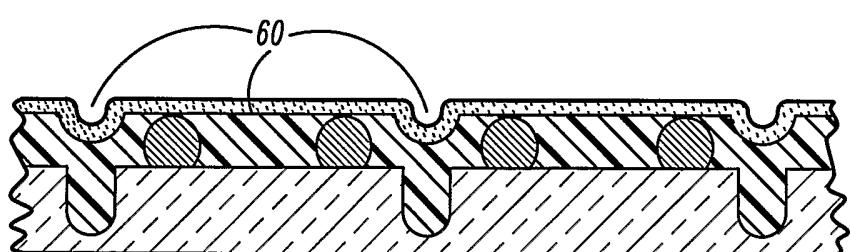

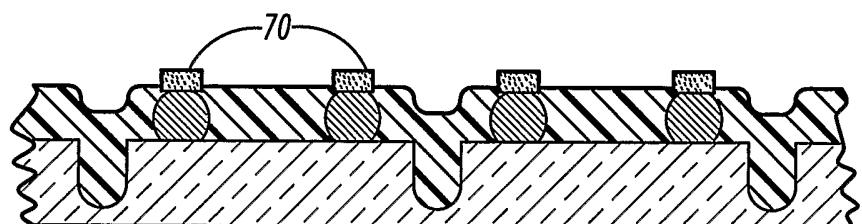

FIG. 3-11 are cross-sectional views of a portion of the wafer depicted in FIG. 1, in accordance with the present invention.

#### DETAILED DESCRIPTION OF THE INVENTION

5 While this invention is susceptible of embodiment in many different forms, there is shown in the drawings and will herein be described in detail specific embodiments, with the understanding that the present disclosure is to be considered as an example of the principles of the invention and not intended to limit the invention to the specific embodiments shown and described. In the description below, 10 like reference numerals are used to describe the same, similar or corresponding elements in the several views of the drawings. The terms a or an, as used herein, are defined as one or more than one. The term plurality, as used herein, is defined as two or more than two. The term another, as used herein, is defined as at least a second or more. The terms including and/or having, as used herein, are defined as comprising 15 (i.e., open language).

A novel method is described for providing an underfill material on an integrated circuit chip at the wafer level. The wafer typically contains one or more integrated circuit chips, and each integrated circuit chip typically has a plurality of solder bumps on its active surface. The wafer is first diced on the active surface side 20 to form channels that will ultimately define the edges of each individual integrated circuit chip, the dicing being of such a depth that it only cuts part-way through the wafer. The front side of the wafer is then coated with an underfill material. Generally, a portion of each solder bump remains uncoated, but in certain cases the bumps can be completely covered. The back side of the wafer is then lapped, ground, polished or 25 otherwise treated so as to remove material down to the level of the previously diced channels. This reduction in the thickness of the wafer causes the original diced channels to now extend completely from the front side to the back side of the thinned wafer. The wafer is then singulated by cutting the underfill material that was deposited in the channels during the coating step, so that the integrated circuit chip is 30 released from the wafer, and the underfill material that was coated on the active side

remains affixed to the active surface of each individual integrated circuit chip.

Referring now to FIGS. 1-11, a wafer 10 contains one or more integrated circuit (IC) chips 12 patterned on a front or active side 36 thereof. The wafer is typically a silicon wafer, but can also consist of other materials used to make ICs, such as gallium arsenide. As in the conventional art, the IC chips are patterned in an array, typically orthogonal, and each of the ICs is pre-bumped. That is, a bump 34, typically a solder ball, has been applied to at least some of the contact pads on the IC. The process and nomenclature of bumping wafers is well known to those of ordinary skill in the art of flip chip packaging, and will not be further elaborated upon here for sake of brevity. In the flowchart of FIG. 2, the first step 20 is that of providing the wafer just described. In the next step, 22, the wafer is diced or sawn on the front or active side, as depicted in FIG. 3. However, unlike the prior art, the wafer is not cut completely through, and the step of sawing 22 is performed so that the depth of the channels or grooves 38 formed in the wafer is such that they only extend part-way through the thickness of the wafer. Since the cuts formed by the dicing step do not extend completely through the thickness of the wafer, this leaves the wafer intact and in one piece, with the channels 38 defining what will ultimately become the edges or sides 39 of each individual flip chip 12. Referring now to FIG. 4, an underfill material 40 is applied to the active surface 36 of each IC on the wafer in step 24. The application of underfill can be provided in a myriad of ways that are common to the art of coating and semiconductor processing. For example, one can dip, spray, flood coat, spin coat, or curtain coat a liquid solution of the underfill material onto the wafer, or the underfill material can be selectively applied by stenciling or printing. After applying a liquid solution of underfill, it obviously must be treated in such a way as to render it at least semi-solid, for example, by heating to remove residual solvents, or if it is a high solids material, by partially curing it to convert it from a liquid to a solid. Some underfill materials that we find useful are epoxies, polyimides, and silicone-polyimide copolymers. If the underfill material is mass coated onto the surface of the wafer, as in dipping, spraying, flood coating, spin coating, or curtain coating liquid solutions, then it will at least partially fill 42 the channels that were cut

in the wafer surface. The coating 42 in the channels serves to also coat all the edges of each IC.

5        Optionally, the underfill material 40 can be applied as a solid film, laminated onto the active surface of the wafer. Normally, the underfill material is applied such that at least a portion 45 of the surface of the bumps are left uncoated so that when the flip chip is ultimately assembled onto a printed circuit board, it will solder more easily. However, we also contemplate in FIG. 5 that our invention can be used in a manner where the bumps are completely covered 53 with the underfill material and the bumps ‘solder through’ the underfill during the flip chip assembly step. For 10      example, an underfill material containing a fluxing agent that is useful in this embodiment is described in United States Patent No. 5,128,746 “Adhesive and Encapsulant Material With Fluxing Properties”. In another embodiment shown in FIG. 5, if the underfill material 40 is selectively applied by stenciling or printing or laminating, then there would be little, if any, underfill material 52 in the channels, and 15      thus there would be no underfill material on the edges 39 of the ICs.

20        An optional step 25, depicted in FIGS. 6 and 7, can be employed wherein a fluxing agent 60 is applied on top of the underfill material and the exposed portion of the solder bumps to aid in the soldering process during assembly to the printed circuit board. The fluxing agent can be applied over the entire surface 60, or it can be selectively applied 70 only on the exposed portion of the solder bumps. There are many well known fluxing agents in the electronics industry, as well as methods of 25      application.

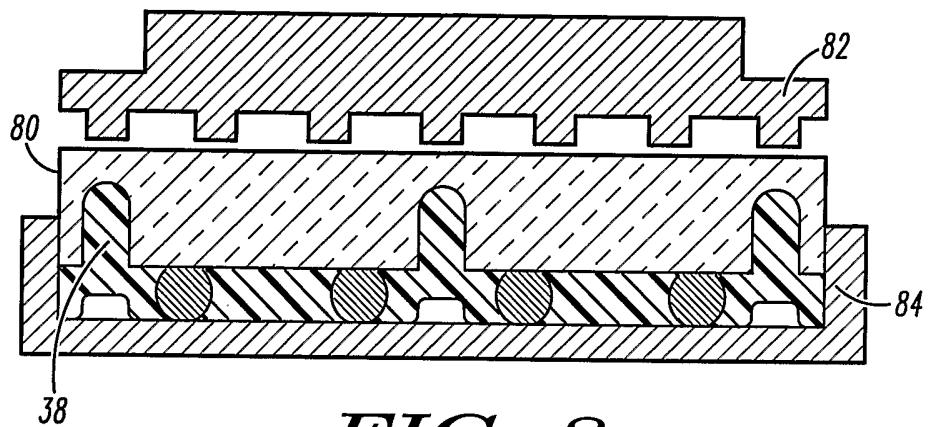

25        Continuing on, in the next step 26 depicted in FIG. 8, the wafer is placed active side down in a proper holding fixture 84 and the back side 80 (i.e. the side opposite the active side or the bumped side) is then lapped. Lapping is a well known process of removal of some of the semiconductor wafer material to reduce the thickness of the wafer by a carefully controlled amount by moving the wafer across a flat plate 82 on which a liquid abrasive has been poured. Back lapping is well known in the semiconductor industry. Other methods of material removal such as grinding or 30      polishing are also contemplated as equivalents. The lapping process continues until

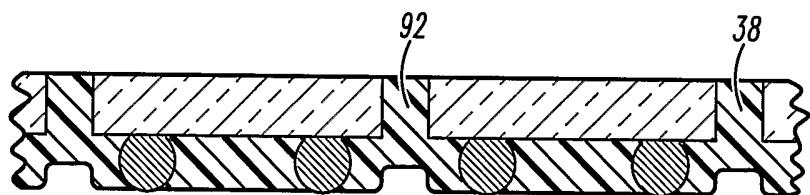

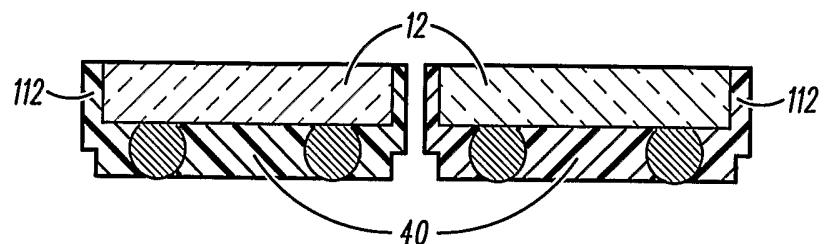

sufficient material has been removed from the back side of the wafer so that the channels 38 that were originally cut so as to only partially extend into the wafer, now traverse completely through the wafer from the front side to the back side as shown in FIG. 9. If one has followed the process embodiment depicted in FIG. 5 where underfill material is not deposited in the channels 38, then when the thickness of the wafer is reduced sufficiently so that the channels extend completely from front to back, the individual IC chips have been singulated by the act of lapping, as shown in FIG. 10, and no further processing is necessary. However, if underfill material has been deposited in the channels, then a step of singulating 28 is performed by cutting through the underfill material 92 remaining in the channels. This can be performed from the active side or from the back side of the IC, and is typically accomplished by use of a laser (excimer, UV, CO<sub>2</sub> or other type) or by mechanically cutting or sawing. Referring now to FIG. 11, after the material 92 in the channels has been cut, the individual IC chips 12 are free, and each chip has underfill material 112 on the edges that were defined during the step of dicing 22, since this secondary cut is typically narrower than the original dicing cut. In both embodiments, the underfill material 40 deposited on the active surface during step 24 remains on the active surface of the flip chip IC 112 after it has been singulated from the wafer.

In summary, our invention, as described in embodiments herein, is implemented by dicing a wafer on the active surface to form channels that ultimately define the edges of each individual integrated circuit chip, the dicing being of such a depth that it only cuts part-way through the wafer. The front side of the wafer is then coated with an underfill material. Generally, a portion of each solder bump remains uncoated, but in certain cases the bumps can be completely covered. The back side of the wafer is then lapped, ground, polished or otherwise treated so as to remove material down to the level of the previously diced channels. This reduction in the thickness of the wafer causes the original diced channels to now extend completely from the front side to the back side of the wafer. The wafer is then singulated by cutting any underfill material that was deposited in the channels during the coating step, so that the integrated circuit chip is released from the wafer, and the underfill

material that was coated on the active side remains affixed to the active surface of each individual integrated circuit chip. However, those skilled in the art will appreciate that the processes described above can be implemented in any number of variations without departing from the present invention.

5 In the illustrations above, multiple embodiments have been elucidated. Other combinations and permutations of these embodiments will occur to those skilled in the art upon consideration of the teachings herein. Those skilled in the art will also appreciate that other coating, dicing, cutting, fluxing, lapping and singulating process can be employed without departing from the present invention. Such alternative methodologies should be considered equivalents. While the invention has been described in conjunction with specific embodiments, it is evident that many alternatives, modifications, permutations and variations will become apparent to those of ordinary skill in the art in light of the foregoing description. Accordingly, it is intended that the present invention embrace all such alternatives, modifications and 10 variations as fall within the scope of the appended claims.

15

What is claimed is:

1. A method for providing an underfill material on an integrated circuit chip and for singulating the chip from a wafer, comprising the following steps in the order named:

- a. providing a wafer having a front side and a back side, the wafer containing at least one integrated circuit chip, the integrated circuit chip having a plurality of solder bumps on said front side of the wafer;

- 5 b. cutting said front side of the wafer to form channels that define edges on said at least one integrated circuit chip, the cutting being of a depth which does not cut completely through the wafer;

- c. coating said front side of the wafer with an underfill material;

- 10 d. lapping the back side of the wafer to reduce the thickness of the wafer sufficient to cause the channels to extend from the front side to the back side; and

- e. wherein the underfill material coated on the front side remains affixed 15 to the integrated circuit chip.

2. The method as recited in claim 1, further comprising, after step (c), a step of providing a coating of a fluxing agent on the plurality of solder bumps.

3. The method as recited in claim 2, wherein the step of providing a coating of flux occurs immediately after step (c) and prior to step (d).

- 20 4. The method as recited in claim 1, wherein the underfill material is deposited into the channels and onto said edges of the integrated circuit chip during the step of coating.

5. The method as recited in claim 1, wherein the step of lapping comprises grinding, polishing or lapping the back side of the wafer.

- 25 6. The method as recited in claim 1, wherein the step of coating comprises coating by dipping, spraying, or printing a liquid material, or laminating a film.

7. The method as recited in claim 1, wherein the integrated circuit is a flip chip integrated circuit.

8. The method as recited in claim 1, wherein the underfill material is selected from 30 the group consisting of epoxies, polyimides, and silicone-polyimide copolymers.

9. The method as recited in claim 1, wherein the (c) step of coating further comprises coating each of said solder bumps.

10. The method as recited in claim 1, wherein the (c) step of coating comprises leaving a portion of each of said solder bumps uncoated.

- 5 11. A method for providing an underfill material on an integrated circuit chip, comprising the following steps in the order named:

- a. providing a wafer having a front side and a back side, the wafer containing at least one integrated circuit chip, the integrated circuit chip having a plurality of solder bumps on said front side of the wafer;

- 10 b. cutting said front side of the wafer to form channels that define edges on said at least one integrated circuit chip, the cutting being of a depth which does not cut completely through the wafer;

- c. coating said front side of the wafer with an underfill material so as to leave a portion of each of said solder bumps uncoated;

- 15 d. removing material from the back side of the wafer to reduce the thickness of the wafer sufficiently to cause the channels to extend from the front side to the back side;

- e. singulating the wafer by cutting underfill material in the channels sufficient to singulate the integrated circuit chip from the wafer; and

- 20 f. wherein the underfill material coated on the front side remains affixed to the singulated integrated circuit chip.

12. The method as recited in claim 11, further comprising, after step (c), a step of providing a coating of flux on said uncoated portion of the solder bumps.

13. The method as recited in claim 12, wherein the step of providing a coating of flux further comprises providing a coating of flux on the underfill material.

- 25 14. The method as recited in claim 12, wherein the step of providing a coating of flux occurs immediately after step (c) and prior to step (d).

15. The method as recited in claim 11, wherein the underfill material is deposited into the channels and onto said edges of the integrated circuit chip during the step of coating.

16. The method as recited in claim 15, wherein underfill material remains coated on said edges of the integrated circuit chip after the step of singulating.

17. The method as recited in claim 11, wherein the step of singulating comprises cutting the underfill material with a laser or slicing or sawing the underfill material.

18. The method as recited in claim 11, wherein the step of removing material from the back side of the wafer comprises grinding, polishing or lapping the back side of the wafer.

19. The method as recited in claim 11, wherein the step of coating comprises coating by dipping, spraying or printing a liquid material, or laminating a film.

20. The method as recited in claim 11, wherein the integrated circuit is a flip chip integrated circuit.

21. The method as recited in claim 11, wherein the underfill material is selected from the group consisting of epoxies, polyimides, and silicone-polyimide copolymers.

22. The method as recited in claim 11, wherein the step of cutting comprises sawing.

23. A wafer level method for providing a layer of underfill adhesive on an integrated circuit having an active surface that includes solder balls on electrically conductive pads, comprising:

- providing a silicon wafer containing one or more of the integrated circuits;

- cutting the active surface of the wafer to form channels that define edges on the integrated circuit, the cutting being of a depth which does not penetrate completely through the wafer;

- forming a layer of underfill adhesive on the active surface of the integrated circuit and in the channels, wherein at least some portion of most of the solder balls remain uncovered;

- partially curing the underfill adhesive;

- removing silicon from the back side of the wafer sufficient to cause the channels to penetrate completely through the wafer; and

cutting the underfill adhesive contained in the channels to singulate at least one integrated circuit chip having an underfill material on its active surface and edges.

24. The method as recited in claim 23, further comprising a step of providing a coating of flux on said uncoated portion of the solder bumps.

5

25. The method as recited in claim 23, wherein the step of providing a coating of flux further comprises providing a coating of flux on the underfill material.

26. The method as recited in claim 23, wherein the step of removing silicon from the back side of the wafer comprises grinding, polishing or lapping the back side of the wafer.

10

27. A method of providing a layer of underfill adhesive on a wafer having an array of bumped integrated circuits, each circuit having an active surface that includes solder balls on electrically conductive pads, comprising:

15

dicing the wafer on the bumped side to form grooves having a predetermined depth that is less than the thickness of the wafer;

coating the wafer with an underfill material so as to cover the active surface and fill the grooves with the underfill material;

polishing the side of the wafer opposite the active surface until the diced grooves extend completely through the wafer; and

20

cutting through the underfill material in the grooves to singulate the array of bumped integrated circuits.

**FIG. 1****FIG. 2****FIG. 3**

2/3

**FIG. 4****FIG. 5****FIG. 6****FIG. 7**

3/3

**FIG. 8****FIG. 9****FIG. 10****FIG. 11**