## (12) 特許協力条約に基づいて公開された国際出願

(19) 世界知的所有権機関

国際事務局

(43) 国際公開日

2016年11月3日 (03.11.2016)

W I P O | P C T

(10) 国際公開番号

WO 2016/174744 A1

- (51) 国際特許分類 :

G06F 12/02 (2006.01) G11C 13/00 (2006.01)

G06F 12/00 (2006.01)

- (21) 国際出願番号 : PCT/JP2015/062853

- (22) 国際出願日 : 2015年4月28日 (28.04.2015)

- (25) 国際出願の言語 : 日本語

- (26) 国際公開の言語 : 日本語

- (71) 出願人 : 株式会社日立製作所 (HITACHI, LTD.)

[JP/JP]; 〒1008280 東京都千代田区丸の内一丁目

6番6号 Tokyo (JP).

- (72) 発明者 : 三浦 譲士 (MIURA Seiji); 〒1008280 東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内 Tokyo (JP).

- (74) 代理人 : 青稜特許業務法人 (SEIRYO I.P.C.); 〒1040032 東京都中央区八丁堀二丁目24番2号 Tokyo (JP).

(81) 指定国(表示のない限り、全ての種類の国内保護が可能): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, ML, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) 指定国(表示のない限り、全ての種類の広域保護が可能): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), ユーラシア (AM, AZ, BY, KG, KZ, RU, TJ, TM), ヨーロッパ (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

[続葉有]

(54) Title: NONVOLATILE MEMORY CONTROL METHOD, CONTROL DEVICE, AND SEMICONDUCTOR STORAGE DEVICE

(54) 発明の名称 : 不揮発性メモリの制御方法、制御装置、および半導体記憶装置

- Step0: Initiate measurement of validity period TC

Step1: Perform various calculations when access by host occurs

Step2: Has validity period TC(T1) elapsed?

Step3: Stop measurement of validity period TC, and analyze access characteristics

Step4: Determine block sizes for selected logical addresses DLAD

Step5: Create block size table BLKTBL, address conversion tables DLPTTBL and LPTTBL, erase count table ERSTBL, and address map ADMAP

Step6: Has product life of memory module NVMD been reached?

Step7: Resume measurement of validity period TC

- AA SATRT

BB END

C Yes

DD No

(57) Abstract: Disclosed is a nonvolatile memory control method for controlling a nonvolatile memory having an erase unit and a write unit that differ in size fixim each other, said nonvolatile memory control method being characterized by mapping physical addresses of the nonvolatile memory to a predetermined range of logical addresses, and controlling the size of the erase unit including the physical addresses mapped to the predetermined range of logical addresses, in accordance with the state of write access to the predetermined range of logical addresses.

(57) 要約: 消去単位と書き込み単位が異なる不揮発性メモリの制御方法であつて、所定単位の論理アドレスに対して不揮発性メモリの物理アドレスを割り当て、所定単位の論理アドレスに対するライトアクセスの状況に応じて、論理アドレスに割り当てられる物理アドレスが含まれる消去単位の大きさを制御することを特徴とする、不揮発性メモリの制御方法が開示される。

添付公開書類：

- 國際調査報告 (条約第21条(3))

## 明 細 書

### 発明の名称 :

不揮発性メモリの制御方法、制御装置、および半導体記憶装置

### 技術分野

[0001] 本発明は、半導体装置に関し、特に不揮発性メモリ装置を備えた半導体装置に関する。

### 背景技術

[0002] 近年、不揮発性メモリ装置として、記録材料にカルコゲナイト材料を用いた相変化メモリが盛んに研究されている。相変化メモリとは、電極間の記録材料が異なる抵抗状態を持つことを利用し、情報を記憶する抵抗変化型メモリの一種である。

[0003] 相変化メモリにおいては、 $\text{Ge}_2\text{Sb}_2\text{Te}_5$ などの相変化材料の抵抗値がアモルファス状態と結晶状態とで異なることを利用して情報を記憶する。アモルファス状態では抵抗が高く(高抵抗状態)、結晶状態では抵抗が低い(低抵抗状態)。従って、相変化メモリからの情報読み出しあは、素子の両端に電位差を与え、素子に流れる電流を測定し、素子の高抵抗状態/低抵抗状態を判別することにより実現する。

[0004] 相変化メモリにおいては、電流により発生するジュール熱によって、相変化材料により構成されたところの相変化膜の電気抵抗を異なる状態に変化させることによりデータを書き換える。

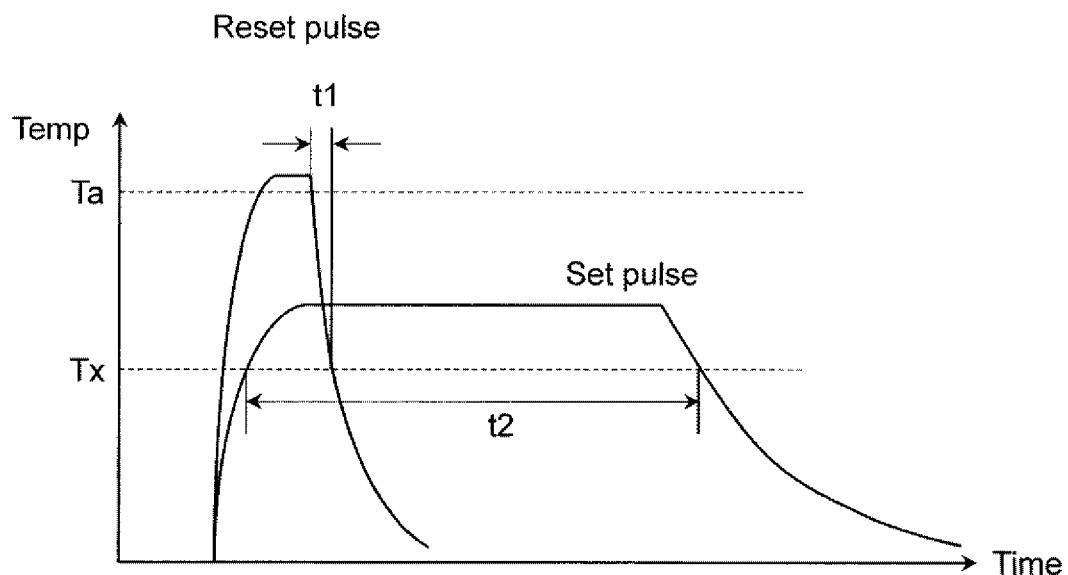

[0005] 図19は、相変化材料を用いた抵抗性記憶素子の相変化に必要なパルス幅と温度との関係を示す図である。同図において、縦軸は温度を表し、横軸は時間を表す。この記憶素子に記憶情報 "0" を書き込む場合には、図19に示す様に、大電流を流して記憶素子をカルコゲナイト材料の融点 $T_a$ 以上に熱してから急冷する様なリセットパルスを印加する。この場合、冷却時間 $t_1$ を短くすることにより(例えば約1nsに設定することにより)、カルコゲナイト材料は高抵抗のアモルファス(非晶質)状態となる。逆に、記憶情

報 "1" を書き込む場合には、記憶素子を融点  $T_a$  よりも低いが、結晶化温度  $T_x$  (ガラス転移点と同じかそれよりも高い) よりも高い温度領域に保つ様な十分な電流を流すようにセットパルスを長時間印加する。これにより、カルコゲナイト材料は低抵抗の多結晶状態となる。

[0006] この相変化メモリは抵抗素子構造を小さくすると、相変化膜の状態変化に必要な電流が小さくなる。このため、相変化メモリは、原理上、微細化に向けており、研究が盛んに行われている。特許文献 1、特許文献 2 および特許文献 3 には、3 次元構造の不揮発性メモリが開示されている。

[0007] 特許文献 1 および 3 には、可変抵抗素子とこれに並列接続されるトランジスタと備えたメモリセルを積層方向に向けて直列に接続した構成が示されている。また、特許文献 2 には、可変抵抗素子とこれに直列接続されるダイオードと備えたメモリセルを積層方向に向けて導電線を挟んで直列に接続した構成が示されている。当該構成では、例えば 2 個のメモリセルの間の導電線と、2 個のメモリセルの外側の 2 本の導電線との間に電位差を与えることで、当該 2 個のメモリセルに対して一括して書き込み動作が行われる。

[0008] また、特許文献 3 には、 $N \times M$  個の 3 次元構造のメモリセルアレイ内のデータを一括で消去する方法が示されている。さらに、消去動作時のジュール熱が、消去対象のメモリセルアレイへ隣接する周辺のメモリセルの結晶状態に大きな影響を及ぼさないように熱緩衝領域を設けることが示されている。また、特許文献 4 には、不揮発性メモリに関し、コントローラがワーカロード指標に応じて、メモリユニットのうちの 1 つを選択することが開示されている。

## 先行技術文献

### 特許文献

[0009] 特許文献 1 : 国際公開第 2011/074545 号

特許文献 2 : 特開 2011-142186 号公報

特許文献 3 : 国際公開第 2014/188484 号

特許文献 4 : 特開 2014-179086 号公報

## 発明の概要

### 発明が解決しようとする課題

[001 0] 本発明者らは、本願に先立ち、SSD (Solid State Drive) やメモリカードなどのストレージへ利用されているNAND型フラッシュメモリの制御方法について検討した。さらに、抵抗変化型メモリを利用した制御方法について検討した。

[001 1] [NAND型フラッシュメモリの制御方法に対する検討]

NAND型フラッシュメモリに代表される不揮発性メモリは、あるメモリ領域へデータを書き込むためには、予め、そのメモリ領域のデータを消去する必要がある。この消去時の最小データ単位は例えば1Mバイト等（例えば1ロックという）であり、書き込み時の最小データ単位は例えば8Kバイト等（例えば1ページという）である。不揮発性メモリでは、1ロックのメモリ領域に、論理アドレスに対応した物理アドレスを持つページに書き込みを行う。このとき、同じ論理アドレスで新しいデータを書き込む場合には、古いページを無効化し、新しいページにデータを書き込む。1ロックが有効なページと無効なページで満たされると、それ以上は書き込みができないくなる。つまり、8Kバイトのデータを書くために、1Mバイトの消去済メモリ領域を確保する必要がある。この1Mバイトの消去済メモリ領域を確保するために、SSD内部ではガーベージコレクションと呼ばれる動作が必要となる。このガーベージコレクション動作は、空き領域（消去済ロック数）が所定以下になった場合に、開始する。このガーベージコレクション動作によって、消去済ロック数を1つ増やしたい場合は、最低、2個のロック（以下のメモリ領域A、B）を選択する必要がある。SSDは、先ず、既に書き込み済の1Mバイトの不揮発性メモリ領域AおよびBから、現時点でも有効なデータ（ページ）を読み出し、これらのデータを集めて、RAMへ書き込む。次に、不揮発性メモリ領域AおよびBを消去する。最後に、RAMへ書き込まれたデータをまとめて不揮発性メモリ領域Aへ書き込む。このガーベージコレクション動作によって、1Mバイトの不揮発性メモリ領域B

が消去済メモリ領域となり、この不揮発性メモリ領域Bへ新たにデータを書き込むことができる。このようなガーベージコレクションは、消去単位と書き込み単位の大きさが異なり、上書きができないメモリにおいては、従来から行われている。

- [001 2] しかしながら、このガーベージコレクション動作によって、SSD内部では、ある不揮発メモリ領域から他の不揮発性メモリ領域へのデータの移動が発生し、ここのデータ移動期間中は、ホストコントローラからSSDへ要求されたライト及びリードリクエストが実行できず、SSDの性能が劣化してしまう。

- [001 3] さらに、ガーベージコレクション動作に伴うデータ移動により、ホストコントローラからSSDへ要求されたライトデータサイズよりも、大きなデータサイズの書き込みが行われる。このため、SSDの信頼性や寿命が低下する。

- [0014] 本願発明は、上記のような課題に鑑みてなされたものである。本願発明の目的は、高性能化、高信頼化を実現する半導体装置を提供することにある。

- [001 5] 本願発明の前記並びにその他の目的と新規な特徴は、本明細書の記述及び添付図面から明らかになるであろう。

### 課題を解決するための手段

- [001 6] 本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

- [001 7] 本発明の一側面は、消去単位と書き込み単位が異なる不揮発性メモリの制御方法である。この方法では、所定単位の論理アドレスに対して不揮発性メモリの物理アドレスを割り当て、所定単位の論理アドレスに対するライトアクセスの状況に応じて、論理アドレスに割り当てられる物理アドレスが含まれる消去単位の大きさを制御する。

- [001 8] 消去単位の具体的な定義としては、「消去回数を管理するための、一つのまとまった領域」であり、「1つの消去コマンドで消去される領域」あるいは、「1つの消去コマンドで消去される領域」の整数倍の領域となる。本明

細書ではこれをプロックと称することがある。プロック毎の消去回数は、消去回数テーブル等で管理される。

- [0019] ライトアクセスの状況の評価方法は種々考えられるが、一例としては、所定単位の論理アドレスの平均ライトデータ量および所定単位の論理アドレスのライトアクセス回数の少なくとも一つによって評価できる。

- [0020] また、ライトアクセスの状況は、全ての論理アドレスの平均ライトデータ量および全ての論理アドレスのライトアクセス回数の少なくとも一つを用いて正規化することもできる。

- [0021] さらに、所定単位の論理アドレスに対するリードアクセスの状況を考慮して、消去単位の大きさを制御することもできる。

- [0022] さらに、所定単位の論理アドレスに対するライトアクセスの状況に応じて、割り当てられる物理アドレスに含まれるプロジェクトナル領域の量を制御することもできる。

- [0023] 本発明の他の側面は、種々の不揮発メモリに対して、上記の方法で制御を行う不揮発性メモリの制御装置である。不揮発性メモリの制御装置の一例としては、論理アドレスに対して不揮発性メモリの物理アドレスを割り当て、物理アドレスにアクセスを行う制御回路であって、この制御回路は、論理アドレスに対するアクセス状況に基づいて、論理アドレスに対応する物理アドレスを含む消去単位プロックの大きさを動的に変化させる。

- [0024] 本発明の他の側面は、不揮発性メモリと、入力される論理アドレスに対して物理アドレスを割り当て、不揮発性メモリの前記物理アドレスにアクセスを行う制御回路と、を有する半導体記憶装置である。制御回路は、不揮発性メモリの物理アドレスを含むプロックのプロックサイズを動的に変化させ、書き込みを行うことを特徴とする。

- [0025] 好ましい態様では、制御回路は、論理アドレス毎に、制御回路へ入力するライトリクエストの第1特徴量を計算し、第1特徴量に基づいて、不揮発性メモリの前記物理アドレスを含む前記プロックのプロックサイズを決定する。具体的な例としては、第1特徴量は、例えばアクセス頻度の高い論理アド

レスを示す特徴量であり、例えば、後述するロックサイズファクタが典型例である。

- [0026] 本発明の他の側面は、不揮発性メモリと、入力される論理アドレスに対して物理アドレスを割り当て、不揮発性メモリの前記物理アドレスにアクセスを行う制御回路と、を有する半導体記憶装置である。制御回路は、不揮発性メモリの論理アドレスの容量に対する物理アドレスの容量を動的に変化させ、書き込みを行うことを特徴とする。

- [0027] 好ましい態様では、制御回路は、論理アドレス毎に、制御回路へ入力するライトリクエストの第2特徴量を計算し、第2特徴量に基づいて、論理アドレスを複数個分含む論理アドレス領域の容量に対する、物理アドレスを複数個分含む物理アドレス領域の容量を決定する。具体的な例としては、第2特徴量は、例えば論理アドレスのデータがどれほどの割合ライトされているかを示す特徴量であり、後述するプロビジョナル容量ファクタが典型例である。物理アドレス領域の容量を決定する具体的手法では、後述するプロビジョナル容量を変化させる例が挙げられる。

- [0028] 本発明の他の側面では、半導体装置は、不揮発性メモリと、不揮発性メモリをアクセスする制御回路と、を具備している。制御回路は、一定期間以内で外部から入力されるライトリクエストの論理アドレスに対するアクセスの頻度を計算し、このアクセス頻度を基に、不揮発性メモリのロックサイズを変更し、書き込みを行う。これにより、アクセス頻度の高い論理アドレスに対応する物理アドレスを含むロックのロックサイズが小さくなり、ロック内の有効データ量が少なくなる。これによつて、ガーベージコレクション時のデータコピー量が小さくなり、コピー時間が短縮されるため制御回路は、外部から入力されるライトおよびリードリクエストを待たせる時間が短くなり半導体装置のデータ転送速度が向上する。ここにおいてロックとは、ガーベージコレクションが行われる際の、消去単位と把握することができる。

## 発明の効果

[0029] 本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

[0030] すなわち、高性能で、信頼性が高く且つコストが低い不揮発性メモリを備えた半導体装置を提供することができる。

### 図面の簡単な説明

[0031] [図1]本発明の一実施の形態による半導体装置において、それを適用した情報処理システムの概略構成例を示すプロック図である。

[図2]図1における制御回路の構成例を示すプロック図である。

[図3]図1におけるメモリモジュール内の制御回路の構成を示すプロック図である。

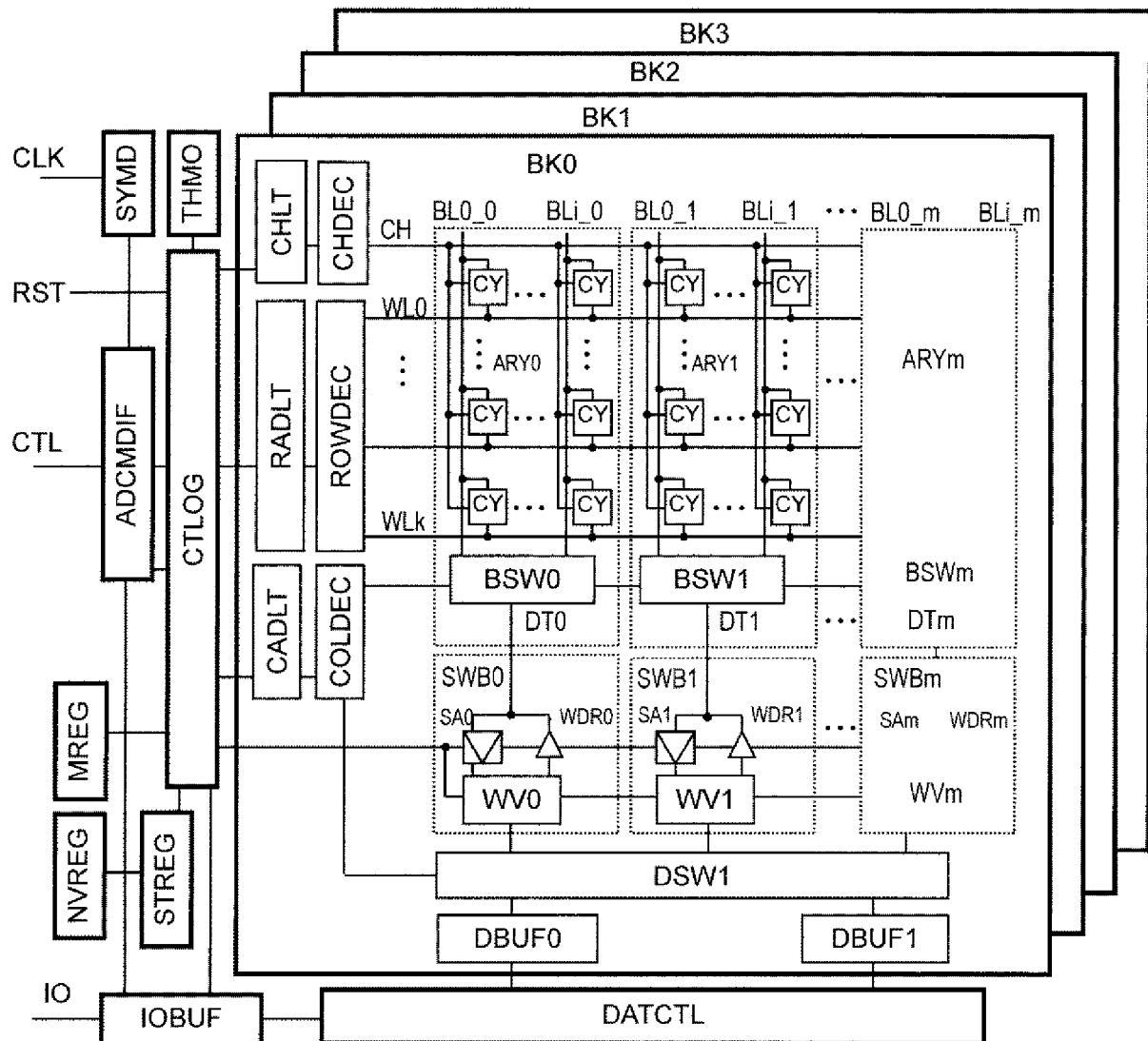

[図4]図1における不揮発性メモリ装置NMOV～31の構成例を示すプロック図である。

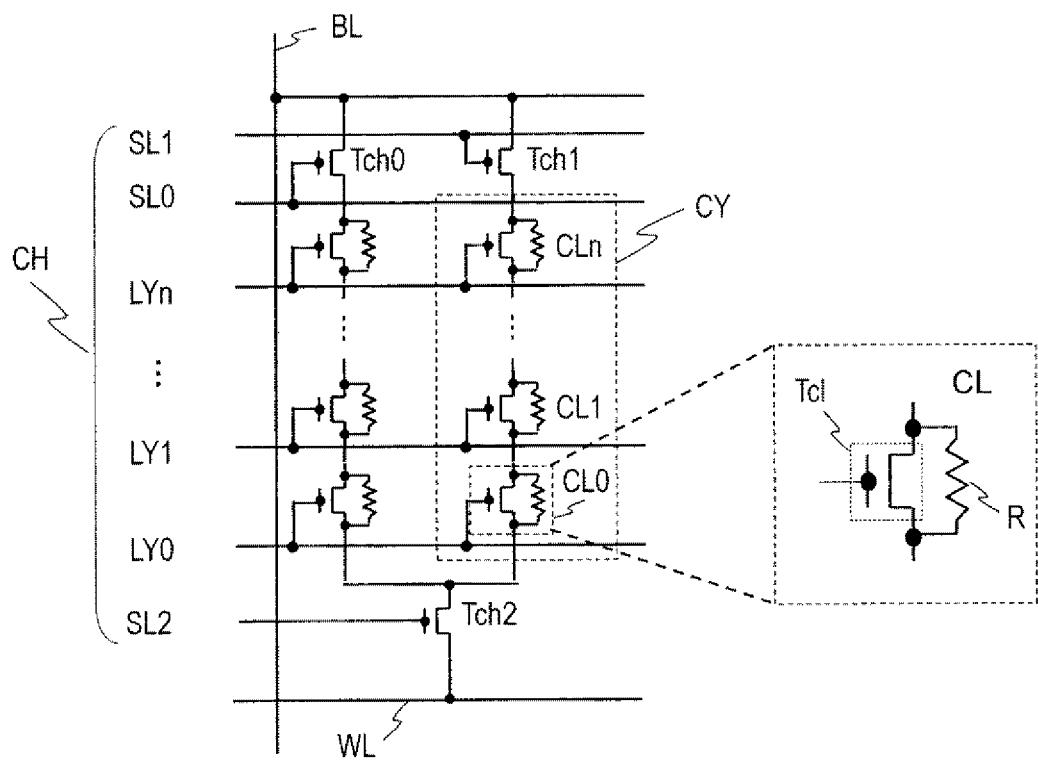

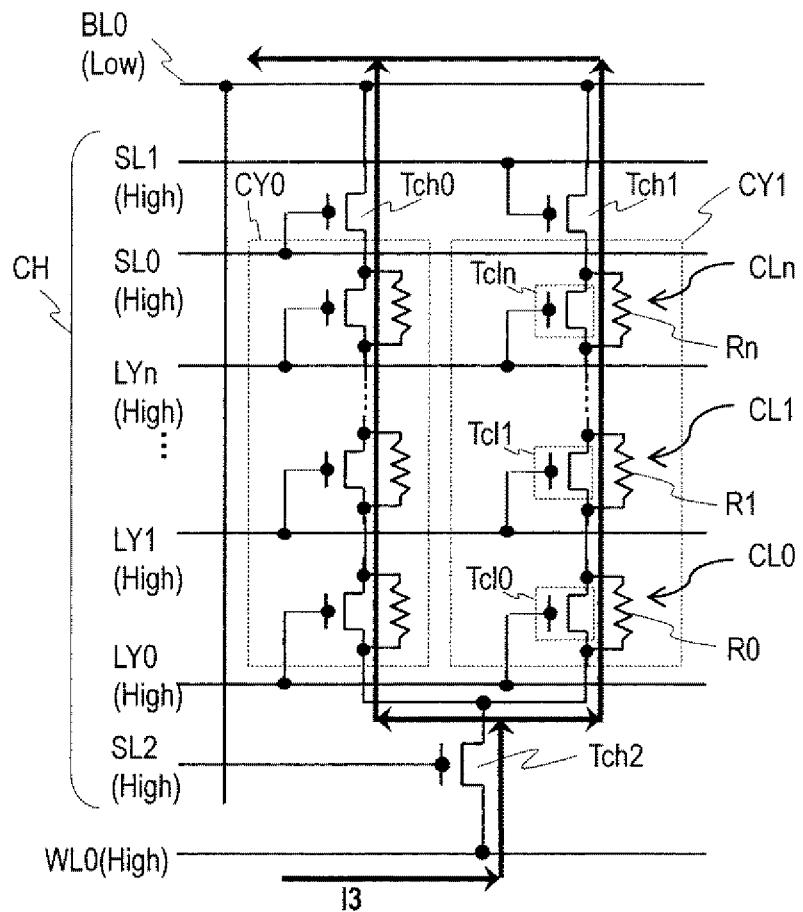

[図5]図4におけるチェインメモリアレイの構成例を示す回路図である。

[図6]図5のチェインメモリアレイの動作例を示す回路図である。

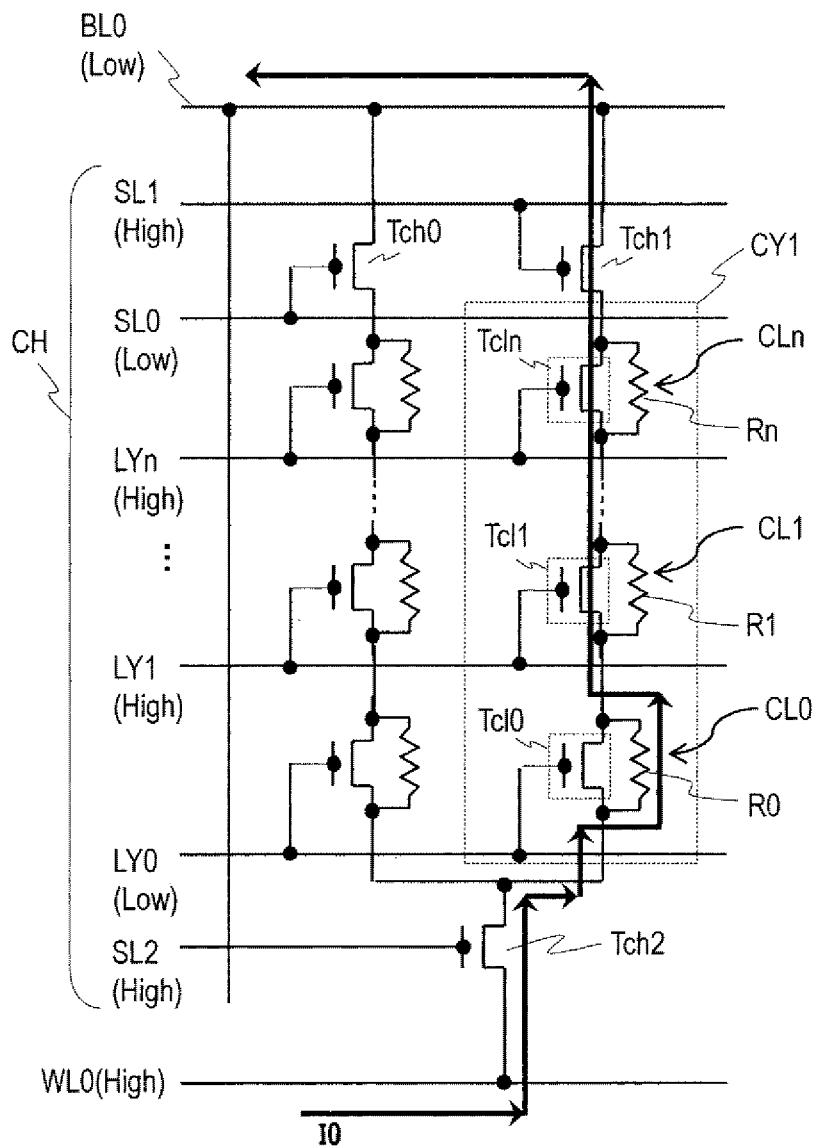

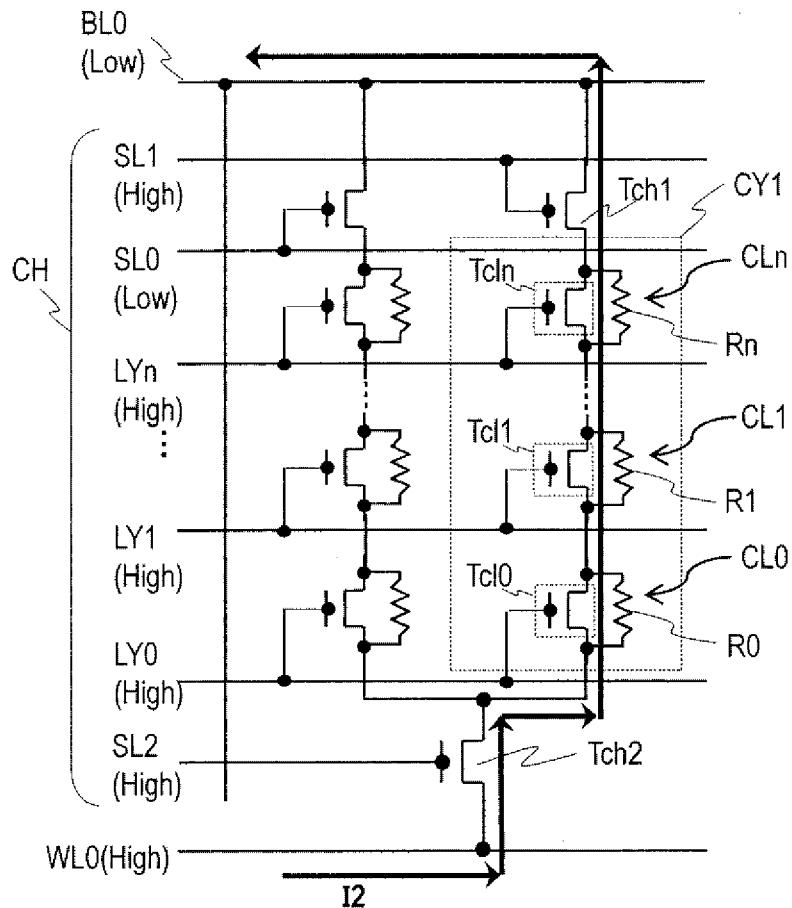

[図7]図5のチェインメモリアレイの別の動作例を示す回路図である。

[図8]図5のチェインメモリアレイの別の動作例を示す回路図である。

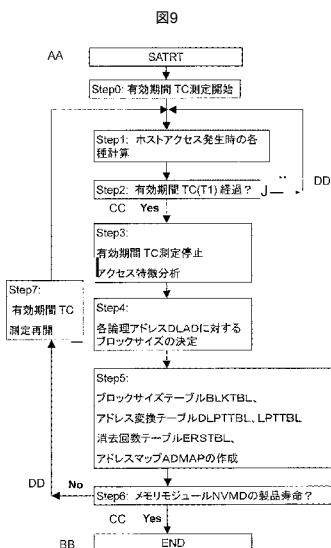

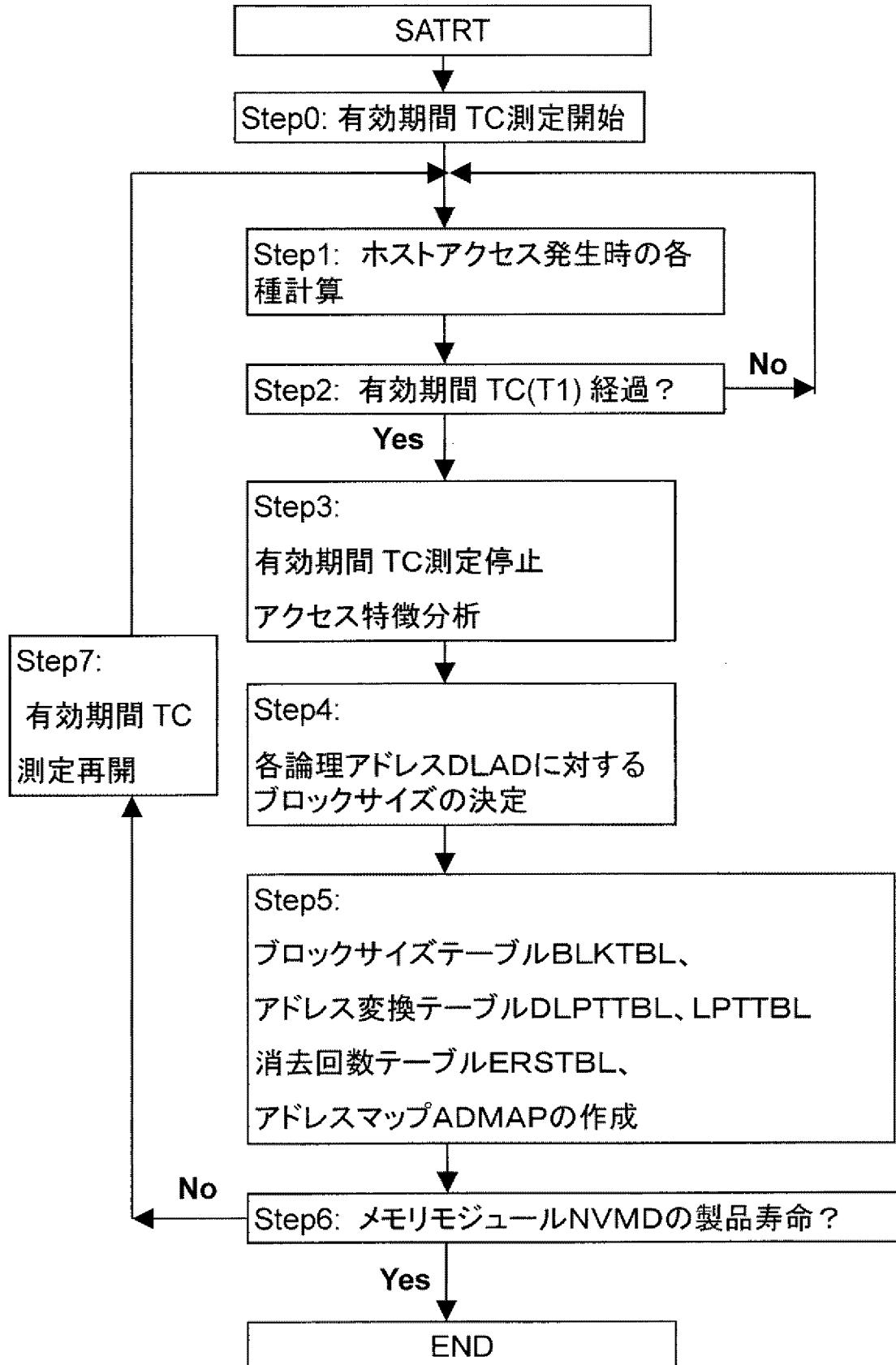

[図9]動的プロックサイズ変更の動作の全体フローを示すフロー図である。

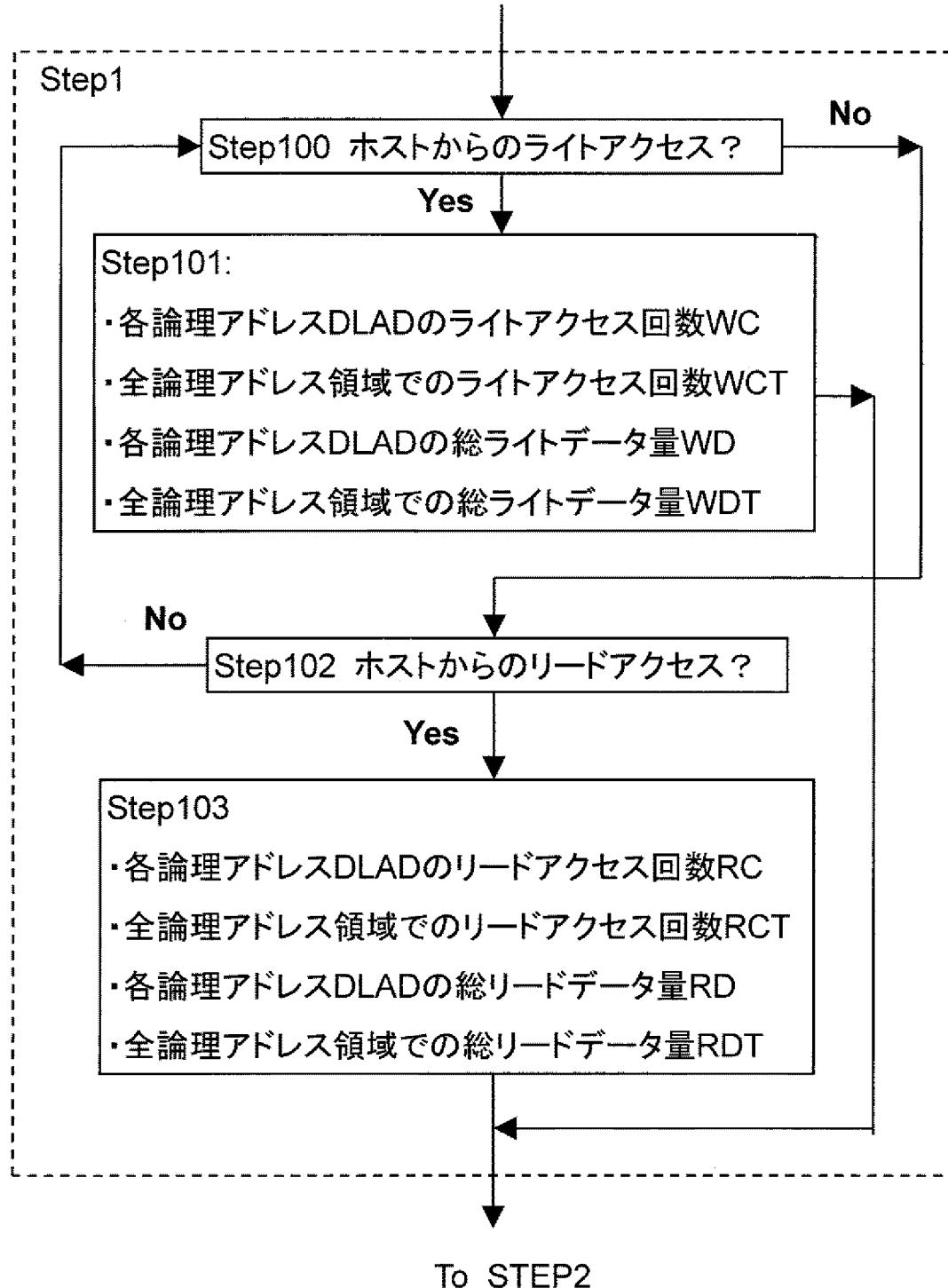

[図10]図9のStep1の詳細動作を示すフロー図である。

[図11]図9のStep3の詳細動作を示すフロー図である。

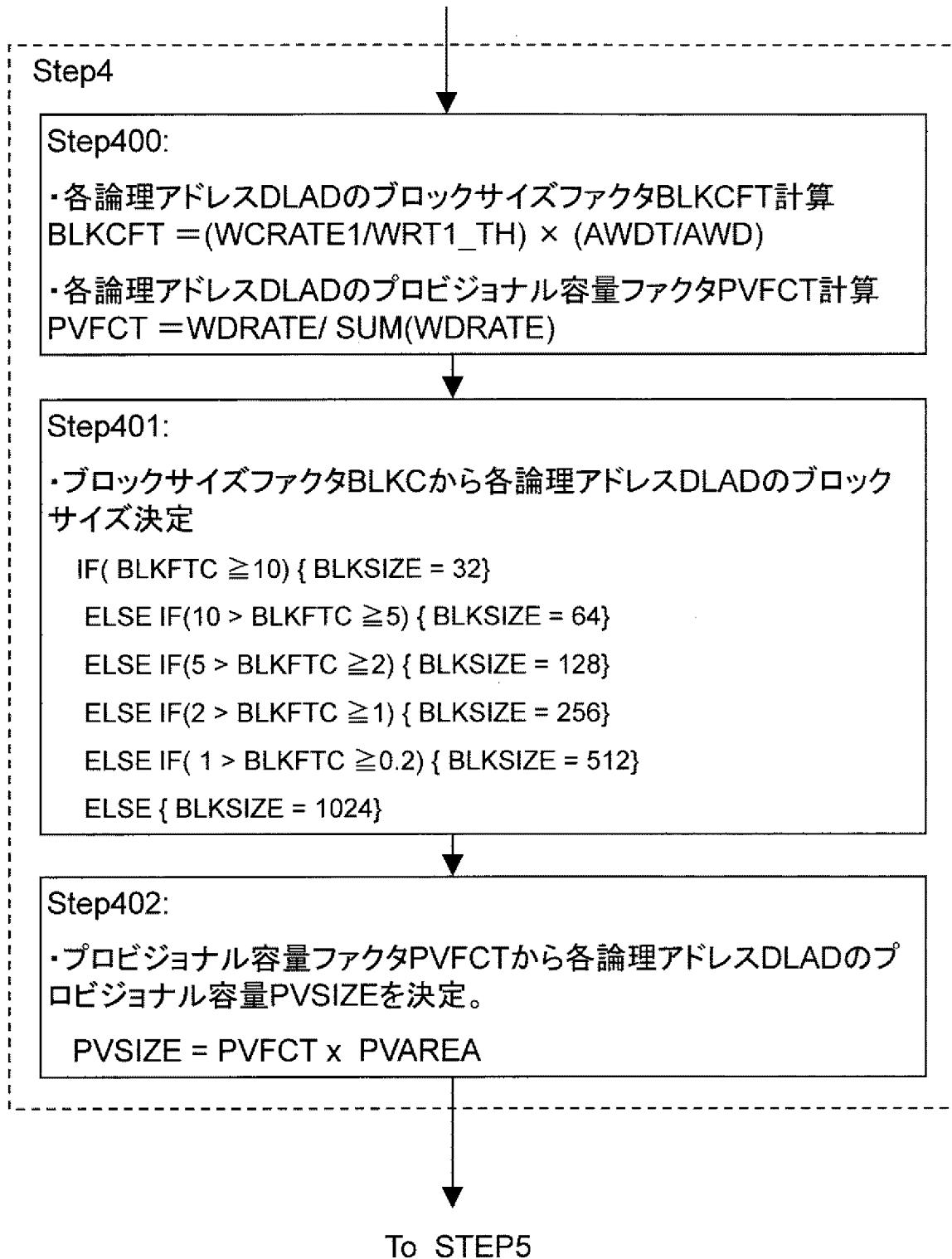

[図12]図9のStep4の詳細動作を示すフロー図である。

[図13]プロックサイズテーブルBLKTBLとアドレス変換テーブルDLPTBLを示す表図である。

[図14]プロックサイズテーブルBLKTBLとアドレス変換テーブルDLPTBLを示す表図である。

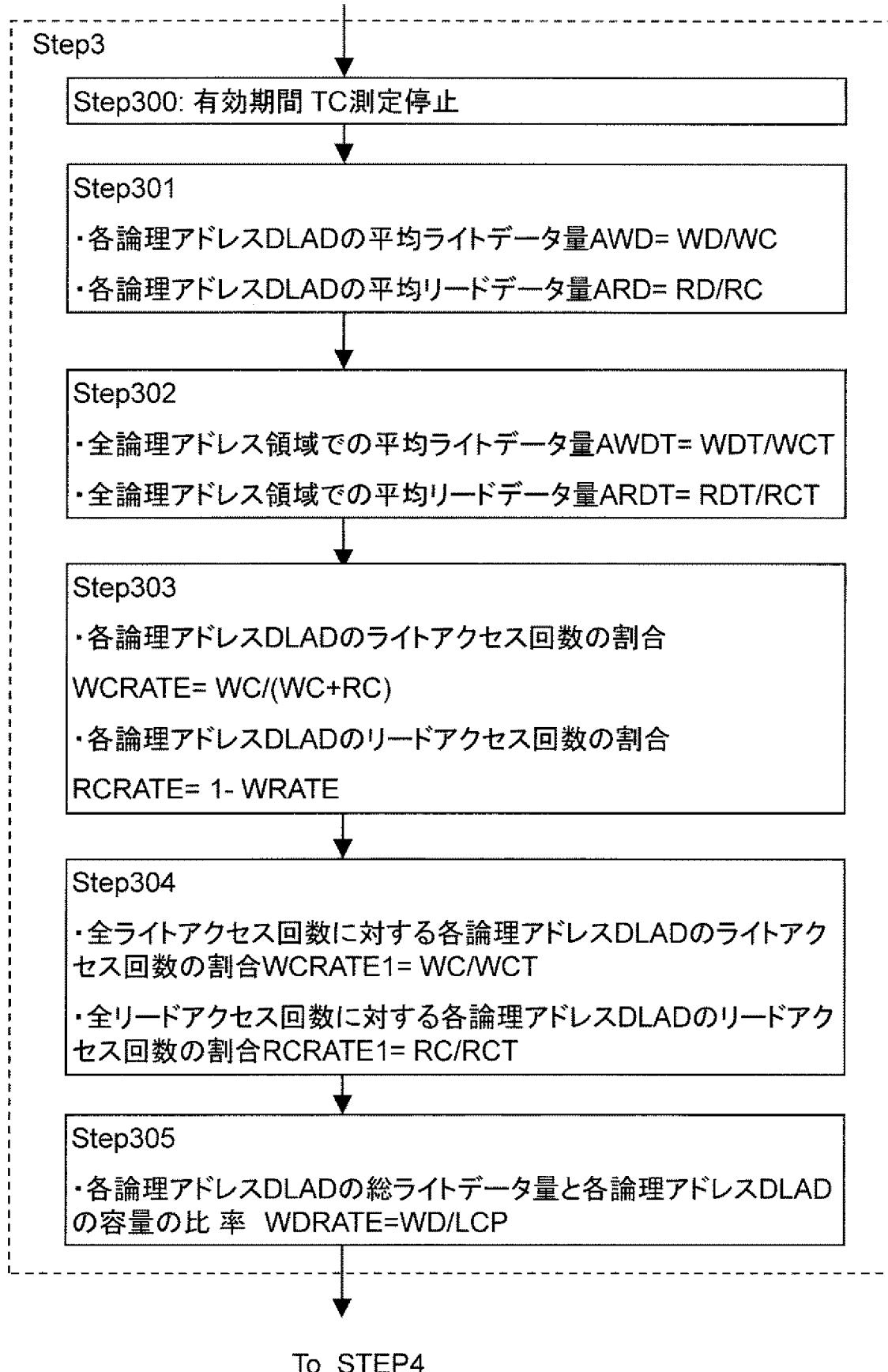

[図15]不揮発性メモリのメモリアレイのプロック構成の一例を示す上面図である。

[図16]不揮発性メモリのメモリアレイのプロック構成の一例を示す上面図である。

[図17] 不揮発性メモリのメモリアレイのプロック構成の一例を示す上面図である。

[図18] 不揮発性メモリのメモリアレイのプロック構成の一例を示す上面図である。

[図19] 相変化材料を用いた抵抗性記憶素子の相変化に必要なパルス幅と温度との関係を示すグラフ図である。

## 発明を実施するための形態

[0032] 以下の実施の形態においては、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明する。特に明示した場合を除き、それらは互いに無関係ではなく、一方は他方の一部または全部の変形例、応用例、詳細説明、補足説明等の関係にある。また、以下の実施の形態において、要素の数等（個数、数値、量、範囲等を含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

[0033] さらに、以下の実施の形態において、その構成要素（要素ステップ等も含む）は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数等（個数、数値、量、範囲等を含む）についても同様である。

[0034] 以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一または関連する符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

[0035] 実施の形態において各プロックを構成する回路素子は特に制限されないが、公知のCMOS（相補型MOSトランジスタ）等の集積回路技術によって

、単結晶シリコンのような1個の半導体基板上に形成される。また、実施の形態で述べるメモリセルとしては、相変化メモリ、R e R A M (Resistive Random Access Memory) のような抵抗性記憶素子を用いるものとする。

[0036] <情報処理システムの概要>

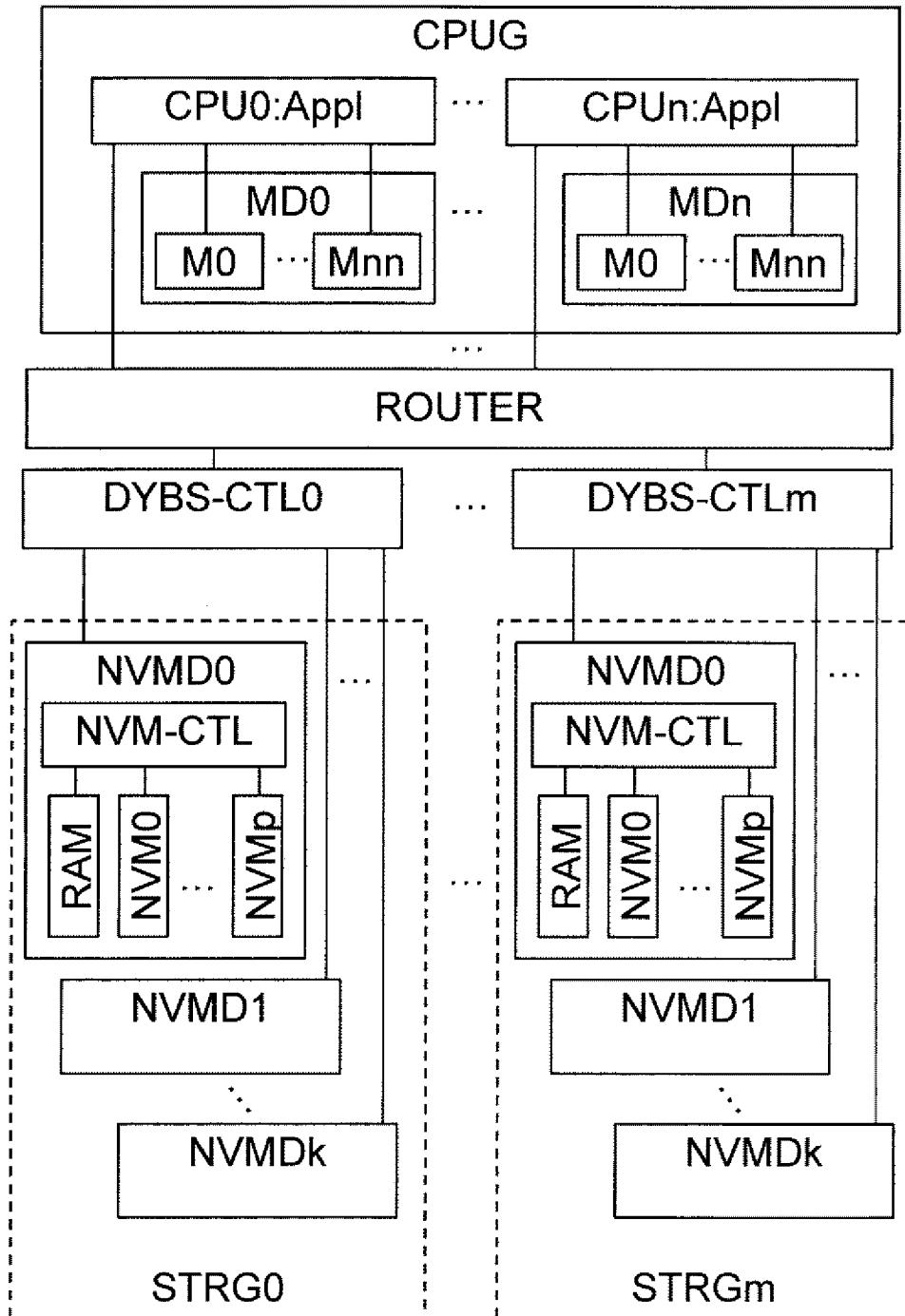

図1は、本発明の一実施の形態による半導体装置において、それを適用した情報処理システムの概略構成例を示すプロック図である。図1に示す情報処理システムは、情報処理装置C P U Gと、ルーター装置ROUTERと、制御装置D Y B 3 \_ ○丁1 0 ~ mと、ストレージ装置S T R G 0 ~ mとを備える。

[0037] 情報処理装置C P U Gは、特に限定しないが、情報処理回路C P U 0 ~ nと、C P U メモリモジュールM D 0 ~ nとを備える。C P U メモリモジュールM D 0 ~ nの各々は、メモリ装置M 0 ~ n nを備える。

[0038] ストレージ装置S T R G 0 ~ mの各々には、不揮発メモリモジュールN V M D 0 ~ kを備えている。

[0039] 不揮発メモリモジュールN V M D 0 ~ kの各々は、不揮発性メモリ装置N V M 0 ~ pと、ランダムアクセスメモリRAMと、これら不揮発性メモリ装置およびランダムアクセスメモリを制御する制御回路N V M — C T Lを備える。不揮発性メモリ装置N V M 0 ~ N V M pは、例えば同じ構成および性能を備えている。

[0040] 不揮発メモリモジュールN V M D 0 ~ kの各々の不揮発性メモリ装置N V M 0 ~ pには、情報処理回路C P U 0 ~ nにて動作するオペレーティングシステム、アプリケーションプログラム、データが格納される。

[0041] 不揮発性メモリ装置N V M 0 ~ pには、また、制御装置D Y B S — C T L 0 ~ mにて管理するメモリモジュールN V M D 0 ~ kの物理アドレス領域D P A Dに対する管理プロックサイズの対応を示した2次プロックサイズテーブルB L K T B L 2と、論理アドレスD L A Dに対応したメモリモジュールN V M D 0 ~ 3 1の物理アドレスD P A Dの2次アドレス変換テーブルD L

P T B L 2 が格納される。なお、ロックサイズテーブルとアドレス変換テーブルは、制御装置 D Y B S \_ C T L もコピーを持つ。便宜上、制御装置 D Y B S \_ C T L が持つテーブルを 1 次テーブル、不揮発メモリモジュール N V M D 0 ~ k が持つテーブルを 2 次テーブルとする。

- [0042] 不揮発性メモリ装置 N V M O ~ p には、また、制御回路 N V M — C T L にて管理される情報処理装置 C P U G からの論理アドレス L A D と、メモリモジュール N V M D 0 ~ k 内の不揮発性メモリ装置 N V M 0 ~ p の物理アドレス P A D との対応を行う 2 次アドレス変換テーブル D L P T B L 2 と、ロック毎の消去回数テーブル E R S T B L と、アドレスマップ A D M A P が格納される。もっとも、2 次ロックサイズテーブル、アドレス変換テーブル、消去回数テーブル、アドレスマップ等は、制御回路や制御装置に別途設けられた専用のメモリに格納してもよい。

- [0043] 以上で、n、n n、m、p、k は、其々自然数を表すものとする。

- [0044] 不揮発メモリモジュール N V M D 0 ~ p は、特に限定しないが、例えば S D (S o l i d S t a t e D r i v e) 等に該当するものである。

- [0045] 情報処理装置 C P U G の情報処理回路 C P U 0 ~ n のいずれかが、ルーターアクセス装置 R O U T E R および制御装置 D Y B S \_ C T L 0 ~ m を通じてストレージ装置 S T R G 0 ~ m の不揮発性メモリ装置 N V M 0 ~ p へ格納されているオペレーティングシステム、アプリケーションプログラム、データを読み出し、C T L メモリモジュール M D 0 ~ n へ転送、保存する。

その後、情報処理回路 C P U 0 ~ n が、メモリモジュール M D 0 ~ n へ保存したデータを利用し、オペレーティングシステムやアプリケーションプログラムを実行する。

- [0046] 情報処理回路 C P U 0 ~ n が、アプリケーションプログラムの実行結果をストレージ装置 S T R G 0 ~ m へ格納する場合、ルーター装置 R O U T E R および制御装置 D Y B 3 \_ ○丁<sub>1</sub> 0 ~ m を通じて、ストレージ装置 S T R G 0 ~ m 内の不揮発性メモリ装置 N V M 0 ~ N V M p へ格納する。

- [0047] 情報処理装置 C P U G は、ストレージ装置 S T R G 0 ~ m へ保存されてい

るデータを最小 512 バイト単位の論理アドレス (L A D) にて管理している。

[0048] ルーター装置 ROUTER は、情報処理装置 C PUG からの読み出し命令、書込み命令やデータを制御装置 DYB3\_〇丁<sub>1</sub>0～m へ転送し、また、御装置 DYBS\_CTL 0～m からのデータを情報処理装置 C PUG へ転送する装置である。

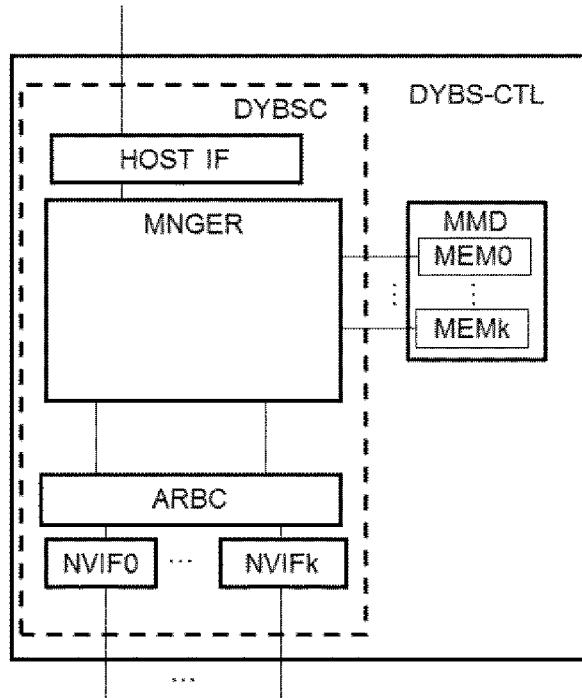

[0049] 図 2 には制御装置 DYBS-CTL の構成を示している。

[0050] 制御装置 DYBS\_CTL 0～m は、ストレージ装置 STRG 0～m の不揮発性メモリ装置 NVM 0～NVM p へ格納されている 2 次ロックサイズテーブル BLK\_TBL 2 を読み出し、制御装置 DYBS\_CTL 0～m 内のメモリ装置 MMD へ転送する。この結果、メモリ装置 MMD は 2 次ロックサイズテーブルのコピーである、1 次ロックサイズテーブル BLK\_TBL 1 を持つ。

[0051] また、制御装置 DYBS\_CTL 0～m は、ストレージ装置 STRG 0～m へ保存されているデータを、最小 512 バイト単位 (セクタ単位) の論理アドレス (L A D) にて管理するコントローラである。

[0052] また、制御装置 DYBS\_CTL 0～m は、ルーター装置 ROUTER を通じて、情報処理装置 C PUG からの読み出しおよび書込み命令に従い、インターフェース信号 HDH\_IF を通じ、これらメモリモジュール NVM 0～k に対してデータの読み出しあり書込みを行う。

[0053] この際、制御装置 DYBS\_CTL 0～m は、ルーター装置 ROUTER を通じて、入力した情報処理装置 C PUG からの論理アドレス LAD に対するメモリモジュール NVM 0～k の物理アドレス D PAD を決定し、メモリモジュール NVM 0～k に対してデータの読み出しあり書込みを行う。

[0054] さらに、制御装置 DYBS\_CTL 0～m は、情報処理装置 C PUG からの読み出しおよび書込みアクセスの特徴を分析し、メモリモジュール NVM 0～k の物理アドレス領域 D PAD に対する管理ロックサイズを動的に最適に変更し、メモリ装置 MMD 内の 1 次ロックサイズテーブル BLK

B L 1 を更新する。これによつて、情報処理システムの性能および信頼性が向上する。

- [0055] メモリモジュール N V M D O ~ k 内の制御回路 N V M — C T L は、不揮発性メモリ装置 N V M O ~ p へ格納されている 2 次アドレス変換テーブル D L P T B L 2 、ロック毎の消去回数テーブル E R S T B L と、アドレスマップ ADDMAP を読み出し、2 次アドレス変換テーブル D L P T B L 2 とロック毎の消去回数テーブル E R S T B L をメモリモジュール N V M D O ~ k 内のメモリ装置 RAM へ転送し、アドレスマップ ADDMAP を読み出し、マップレジスタ M A P R E G へ転送する。

- [0056] メモリ制御回路 N V M — C T L が、データを不揮発性メモリ装置 N V M O ~ P へ書込む場合、不揮発性メモリ装置 N V M O ~ p の物理ページアドレス P A D は、不揮発性メモリ装置 N V M O ~ p を管理するロック毎の書き込み回数が平準化するように、物理ページアドレス P A D を決定し、2 次アドレス変換テーブル D L P T B L 2 を更新する。

- [0057] また、メモリ制御回路 N V M — C T L が、データを不揮発性メモリ装置 N V M O ~ p から読み出す場合、メモリ制御回路 N V M — C T L は、2 次アドレス変換テーブル D L P T B L 2 を参照し、論理アドレス L A D に対する物理アドレス P A D を決定し、物理アドレス P A D に格納されたデータを読み出す。

- [0058] さらに、制御装置 D Y B S \_ C T L 0 ~ m が 1 次ロックサイズテーブル B L K T B L 1 を更新した後に、制御装置 D Y B 3 \_ ○丁 1 0 ~ m の指示によって、2 次ロックサイズテーブル B L K T B L 2 の情報を基に、メモリ制御回路 N V M — C T L は 2 次アドレス変換テーブル D L P T B L 2 と、ロック毎の消去回数テーブル E R S T B L と、アドレスマップ ADDMAP を再構築する。これによつて、メモリモジュール N V M D O ~ k の性能および信頼性が向上する。

- [0059] 図 2 は、図 1 における制御装置 D Y B S \_ C T L 0 ~ m の構成例を示すプロック図である。図 2 に示す制御装置 D Y B S — C T L には、制御ロック

D Y B S C とメモリモジュール M M D が含まれている。

- [0060] 制御プロック D Y B S C は、インターフェース回路 H O S T I F と、情報処理回路 M N G E R と、調停回路 A R B C と、メモリモジュール N V M D 0 ~ k とのインターフェース回路 N V I F 0 ~ k から構成される。メモリモジュール M M D には、メモリ装置 M E M 0 ~ M E M k が含まれている。

- [0061] メモリモジュール M M D には、論理アドレス D L A D 每のロックサイズを示す 1 次ロックサイズテーブル B L K T B L 1 と、論理アドレス D L A D に対応したメモリモジュール N V M D 0 ~ k の物理アドレス D P A D の 1 次アドレス変換テーブル D L P T B L 1 が保存される。

- [0062] また、分割論理アドレス D L A D は、複数の論理アドレス L A D を含む論理アドレス領域を示し、物理アドレス D P A D は、複数の物理アドレス P A D を含む物理アドレス領域を示す。

- [0063] 制御装置 D Y B S — C T L の読み出し動作について説明する。ルーター装置 R O U T E R を通じて、情報処理装置 C P U G からのリードリクエスト (R Q) が入力される。リードリクエスト (R Q) には論理アドレス (L A D) 、データ読み出し命令 (R D) 、セクタカウント (S E C) などが含まれる。

- [0064] 制御装置 D Y B S — C T L はメモリ装置 M M D へ格納されている 1 次アドレス変換テーブル D L P T B L 1 を参照し、論理アドレス L A D を含む分割論理アドレス D L A D に対応した物理アドレス D P A D 0 を読み出し、この物理アドレス D P A D 0 によって論理アドレス L A D のデータを格納したメモリモジュール N V M D 0 を選択し、リードリクエスト (R Q) を転送する。

- [0065] メモリモジュール N V M D 0 では、2 次アドレス変換テーブル D L P T B L 2 を参照し、論理アドレス L A D に対応した物理ページアドレス P A D に格納されているデータの中で、セクタカウント分だけのデータ D T A T 0 を読み出す。

- [0066] 読み出されたデータ D A T A 0 は、制御装置 D Y B S — C T L へ転送され

、さらに、ルーター装置ROUTERを通じて、情報処理装置CPUGへ転送される。

[0067] 制御装置DYS-CTLの書き込み動作について説明する。ルーター装置ROUTERを通じて、情報処理装置CPUGからライトリクエスト(WQ)が入力される。ライトリクエスト(WQ)には論理アドレス(LAD)、データ書き込み命令(WT)、セクタカウント(SEC)などが含まれる。

[0068] 制御装置DYS-CTLはメモリ装置MMDへ格納されている1次アドレス変換テーブルDLPTBL1を参照し、論理アドレスLADが含まれる論理アドレスDLADに対応した物理アドレスDPAD1を読み出し、この物理アドレスDPAD1によって論理アドレスLADのデータを格納したメモリモジュールNVM1を選択し、ライトリクエスト(WQ)を転送する。

[0069] メモリモジュールNVM1では、ロックの書き込み回数を平準化するよう物理アドレスPADを決定し、この物理アドレスPADへセクタカウントだけのデータDAT1を書き込む。その後、2次アドレス変換テーブルDLPTBL2を更新し、論理アドレスLADと最新の物理アドレスPADを対応付けする。

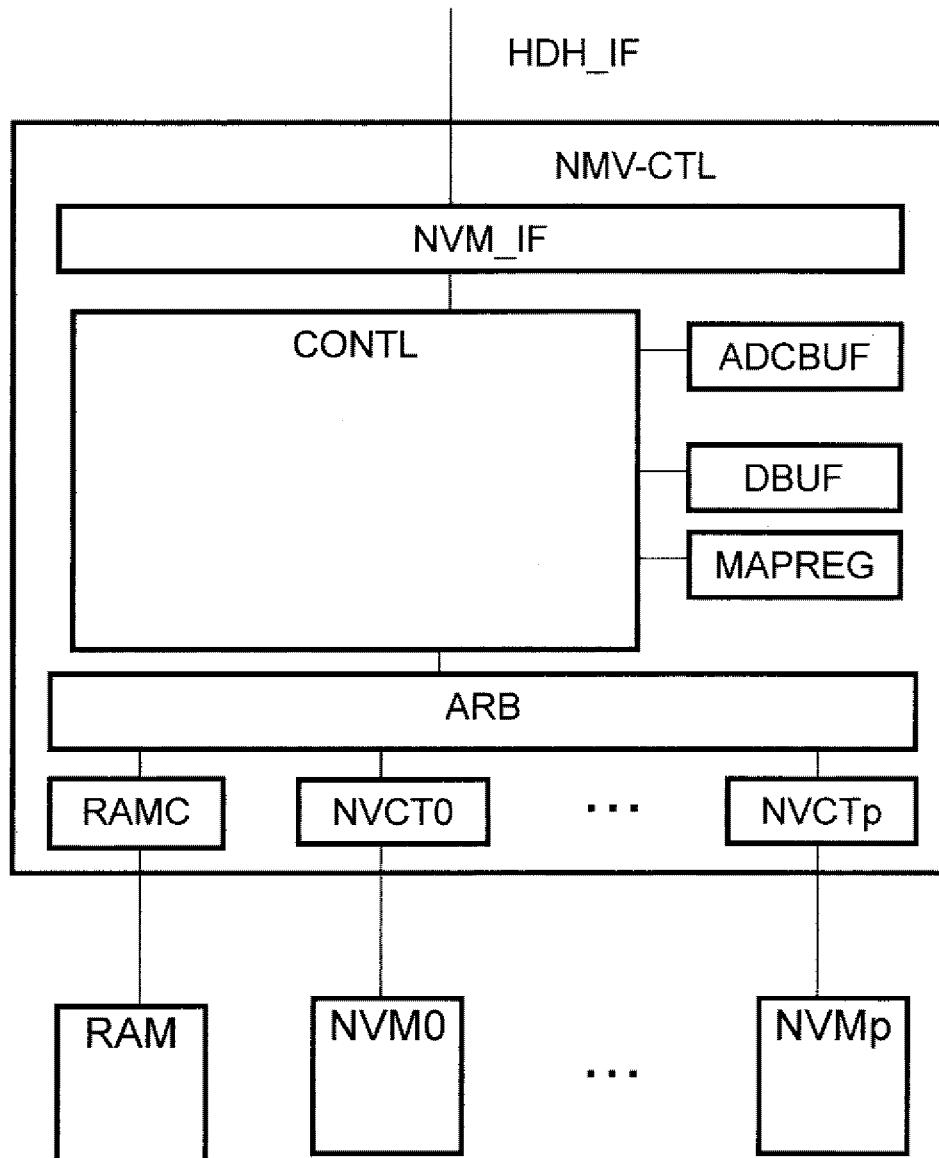

[0070] 図3は、図1におけるメモリモジュールNVM0-kのメモリ制御回路NVM\_CTLのプロック図である。

[0071] メモリ制御回路NVM-CTLは、インターフェース回路NVM\_IFと、アドレス/コマンドバッファADCBUFと、データバッファDBUFと、マップレジスタMAPREGと、調停回路ARBと、情報処理回路CONTLと、RAMのメモリ制御回路RAMC、不揮発性メモリ装置NVM0-pのメモリ制御回路NVCTOpと、を備える。メモリ制御回路RAMCは、図1のランダムアクセスメモリRAMを直接制御し、NVCT0-pは、図1の不揮発性メモリ装置NVM0-pをそれぞれ直接制御する。

[0072] データバッファDBUFは、不揮発性メモリ装置NVM0-pの書き込みデータや読み出しはデータを一時的に蓄える。

- [0073] アドレス/コマンドバッファADCBUFは、制御装置DYBS\_CTLからメモリ制御回路NVM-CTLへ入力した論理アドレスLADと、データ読み出し命令(RD)と、データ書き込み命令(WT)を一時的に蓄える。

- [0074] メモリ装置RAMには、2次アドレス変換テーブルDLPTBL2と、ロック毎の消去回数テーブルERSTBLが保存される。

- [0075] マップレジスタMAPREGには、アドレスマップADDMAPが格納され、1ロックサイズ毎の不揮発性メモリ装置NVM0～p内部のXアドレス、YアドレスおよびZアドレスの対応が示されている。

- [0076] 制御装置DYB3\_〇丁<sub>1</sub>0～mの指示によって、2次ロックサイズテーブルBLKTB<sub>L</sub>2の情報を基に、メモリ制御回路NVM-CTLは2次アドレス変換テーブルDLPTBL2と、ロック毎の消去回数テーブルERSTBLと、アドレスマップADDMAPを再構築する。これによつて、メモリモジュールNVM<sub>D</sub>0～kの性能および信頼性が向上する。

- [0077] 図4は、図1における不揮発性メモリ装置NVM<sub>O～p</sub>の構成例を示すプロック図であり、図5は、図4におけるチェインメモリアレイの構成例を示す回路図である。

- [0078] 図4に示す不揮発性メモリ装置は、図1の不揮発性メモリ装置NVM<sub>O～p</sub>のそれぞれに該当するものであり、ここでは、一例として相変化型の不揮発性メモリ(相変化メモリ)が用いられているが、フラッシュメモリや他の抵抗変化型メモリであつてもよい。不揮発性メモリ装置は、クロック生成回路SYMD、ステータスレジスタSTREG、イレースサイズ指定レジスタNVREG、アドレス・コマンドインターフェース回路ADCMDIF、IOバッファI/OBUF、制御回路CTL<sub>OG</sub>、温度センサTHM<sub>O</sub>、データ制御回路DATCTL、メモリバンクBK<sub>0～BK3</sub>を備える。

- [0079] 各メモリバンクBK<sub>0～BK3</sub>は、メモリアレイARY<sub>x</sub>(x=0～m)と、各メモリアレイにそれぞれ対応して設けられる読み書き制御ロックSWB<sub>x</sub>(x=0～m)と、これらを制御する各種周辺回路を備える。各種周

迂回路の中には、ロウアドレスラッチR A D L T、カラムアドレスラッチC A D L T、ロウデコーダR ○W D E C、カラムデコーダC ○L D E C、チェイン選択アドレスラッチC H L T、チェインデコーダC H D E C、データ選択回路D S W 1、データバッファD B U F 0, D B U F 1が含まれる。

[0080] 各メモリアレイA R Y x (x = 0 ~ m) は、複数のワード線W L 0 ~ W L k と複数のビット線B L 0\_x ~ B L i\_x の交点に配置される複数のチェインメモリアレイC Y と、複数のビット線B L 0\_x ~ B L i\_x (x = 0 ~ m) のいずれかを選択してデータ線D T x に接続するビット線選択回路B S W x を備える。各読み書き制御ロックS W B x (x = 0 ~ m) は、データ線D T x (x = 0 ~ m) に接続されるセンスアンプS A x (x = 0 ~ m) およびライトドライバW D R x (x = 0 ~ m) と、書き込み動作時に、これらを用いてデータの検証を行う書き込みデータ検証回路W V x (x = 0 ~ m) を備える。また、図4に示した不揮発性メモリ装置を動作させるインターフェースはN A N D型フラッシュメモリインターフェースやD R A Mインターフェースなどのメモリインターフェースを採用すると、従来システムとのインターフェースの互換性を保つことができ、利便性が良い不揮発性メモリ装置を提供できる。

[0081] さらに、図4に示した不揮発性メモリ装置は、1つのコマンドで消去できるロックサイズが物理的に固定しておらず、メモリ制御回路N V M \_ C T L にて、制御上の管理単位として容易に変更可能である。このため、情報処理装置C P U GのメモリモジュールN V M Dへのアクセスの特徴を分析し、不揮発性メモリ装置のロックサイズ動的に最適化することで、情報処理システムの性能や信頼性の向上が図れる。

[0082] 図5に示すように、各チェインメモリアレイC Y は、複数の相変化メモリセルC L 0 ~ C L n が直列に接続された構成を備え、その一端はチェイン選択トランジスタT c h 2 を介してワード線W L に接続され、他端はチェイン選択トランジスタT c h 0 およびT c h 1 を介してビット線B L に接続される。複数の相変化メモリセルC L 0 ~ C L n は、図示は省略するが、半導体

基板に対して高さ方向に順に積層配置され、互いに直列接続される。また、各相変化メモリセルCLは、可変抵抗型の記憶素子Rと、それに並列接続されるメモリセル選択トランジスタTch1を備える。記憶素子Rは、例えばカルコゲナイト材料で形成される。

[0083] 図5の例では、2個のチェインメモリアレイCYがチェイン選択トランジスタTch2を共有しており、チェインメモリアレイ選択線SLO, SL1, SL2によって各チェインメモリアレイ内のチェイン選択トランジスタTch0, 1, 2がそれぞれ制御され、これによつていずれか一方のチェインメモリアレイが選択される。また、メモリセル選択線LY(LYO~LYn)は、対応する相変化メモリセルのゲート電極に接続され、メモリセル選択線LYによって、相変化メモリセルCL0~CLn内のメモリセル選択トランジスタTch1がそれぞれ制御され、これによつて各相変化メモリセルが適宜選択される。なお、チェインメモリアレイ選択線SLO, SL1, SL2およびメモリセル選択線LYO~LYnは、チェイン制御線CHとして、図4のチェイン選択アドレスラッチCHLTおよびチェインデコーダCHDECを介して適宜駆動される。

[0084] 次に、図4の不揮発性メモリ装置の動作について簡単に説明する。図4において、まず、制御回路CTL0Gは、アドレス・コマンドインターフェース回路ADCMDIFを介して制御信号CTLを受ける。制御信号CTLは、特に限定しないが、例えば、コマンド・ラッティネーブル信号(CLE)、チップイネーブル信号(CEB)、アドレス・ラッチ信号(ALE)、ライトイネーブル信号(WEB)、リードイネーブル信号(REB)、レディビジー信号(RBB)を含み、これらの組み合わせによつて、書込み命令又は読み出し命令が発行される。また、制御回路CTL0Gは、制御信号CTLと共に、I/OバッファI/OBUFを介して入出力信号I/Oを受ける。入出力信号I/Oには、アドレス信号が含まれており、制御回路CTL0Gは、当該アドレス信号からロウアドレスおよびカラムアドレスを抽出する。制御回路CTL0Gは、当該ロウアドレス、カラムアドレス、ならびに予め定めら

れる書込み・読み出し単位等に基づいて、適宜内部アドレスを生成し、ロウアドレスラッチR A D L T、カラムアドレスラッチC A D L Tならびにチェイン選択アドレスラッチC H L Tにそれぞれ伝送する。

[0085] ロウデコーダR O W D E Cは、ロウアドレスラッチR A D L Tの出力を受けてワート線W L 0～W L kの選択を行い、カラムデコーダC O L D E Cは、カラムアドレスラッチC A D L Tの出力を受けてビット線B L 0\_x～B L i\_x(x=0～m)の選択を行う。また、チェインデコーダC H D E Cは、チェイン選択アドレスラッチC H L Tの出力を受けて、チェイン制御線C Hの選択を行う。制御信号C T Lによって読み出し命令が入力された際、前述したワート線、ビット線およびチェイン制御線の組み合わせによって選択されたチェインメモリアレイC Yからビット線選択回路B S W 0～B S W mを介してデータが読み出される。当該読み出されたデータは、センスアンプS A 0～S A mで増幅され、データ選択回路D S W 1を介してデータバッファD B U F 0(又はD B U F 1)に伝送される。そして、データバッファD B U F 0(又はD B U F 1)上のデータは、データ制御回路D A T C T LおよびI/OバッファI/O B U Fを介して入出力信号I/Oに順次伝送される。

[0086] 一方、制御信号C T Lによって書込み命令が入力された際、入出力信号I/Oには、前述したアドレス信号に続いてデータ信号が伝送され、データ信号は、データ制御回路D A T C T Lを介してデータバッファD B U F 0(又はD B U F 1)に入力される。データバッファD B U F 0(又はD B U F 1)上のデータ信号は、データ選択回路D S W 1、ライトドライバW D R 0～W D R mおよびビット線選択回路B S W 0～B S W mを介して、前述したワート線、ビット線およびチェイン制御線の組み合わせによって選択されたチェインメモリアレイC Yに書き込まれる。また、この際に、書込みデータ検証回路W V 0～W V mは、書込みを行ったデータをセンスアンプS A 0～S A mを介して適宜読み出しながら書込みレベルが十分なレベルに達したかを検証し、十分なレベルに達するまでライトドライバW D R 0～W D R mを用いて再度の書込み動作を行う。

[0087] 図6は、図5のチェインメモリアレイの動作例を示す説明図である。この図6を用いて、例えば、チェインメモリアレイCY1内の相変化メモリセルCL0における可変抵抗型記憶素子R0を高抵抗や低抵抗にする際の動作について説明する。チェインデコーダCHDECによって、チェインメモリアレイ選択線SL1のみが活性化(SLO=Low, SL1=High, SL2=High)され、チェイン選択トランジスタTch1およびTch2が導通状態となる。続いて、メモリセル選択線LY0のみが非活性化(LYO=Low, LY1～LYn=High)され、相変化メモリセルCL0のメモリセルCL1～CLnのメモリセル選択トランジスタTc10はカットオフ状態となり、残りのメモリセルCL1～CLnのメモリセル選択トランジスタTc11～Tc1nは導通状態となる。

[0088] 次に、ワード線WL0がHighとなり、続いてビット線BL0がLowになると、電流I0がワード線WL0から、チェイン選択トランジスタTch2、可変抵抗型記憶素子R0、メモリセル選択トランジスタTc11～Tc1nおよびチェイン選択トランジスタTch1を経由してビット線BL0へ流れる。この電流I0が図14に示したReset電流パルスの形に制御されることで、可変抵抗型記憶素子R0は高抵抗となる。また、この電流I0が図14に示したSet電流パルスの形に制御されることで、可変抵抗型記憶素子R0は低抵抗となる。可変抵抗型記憶素子R0～Rnの抵抗値の違いによってデータ"1"と"0"が区別される。

[0089] また、図4で示すように複数のビット線BL0\_0、BL0\_1～BL0\_mへ電流I0を流すことで、書き込み速度を向上することができる。

[0090] 特に限定しないが、可変抵抗型記憶素子が低抵抗になった場合に、データ"1"が記録され、高抵抗になった場合にデータ"0"が記録されるものとする。

[0091] なお、可変抵抗型記憶素子R0に記録されたデータを読み出す場合は、可変抵抗型記憶素子R0の抵抗値が変化しない程度に、データ書き込みと同様の経路で電流が印加される。この場合、可変抵抗型記憶素子R0の抵抗値に応

じた電圧値がセンスアンプ（この例では図4のS A 0）で検出され、データ "0" および "1" が判定される。

[0092] また、図4で示すように複数のビット線B L 0\_0、B L 0\_1～B L 0\_mを通じて可変抵抗型記憶素子R 0の抵抗値が変化しない程度に、データ書き込みと同様の経路で電流が印加することで、複数のセンスアンプ（この例では図4のS A 0～S A m）にてデータ "0" および "1" が判定され、読み出し速度を向上することができる。

[0093] 図7および図8は、図5のチェインメモリアレイの別の動作例を示す説明図である。

[0094] 図7を用いて、1チェインメモリアレイC Y 1内の全可変抵抗型記憶素子R 0～R nを一括で低抵抗にする際の動作を説明する。チェインデコーダC H D E Cによって、チェインメモリアレイ選択線S L 1のみが活性化（S L 0 = L o w、S L 1 = H i g h、S L 2 = H i g h）され、チェイン選択トランジスタT c h 1およびT c h 2が導通状態となる。続いて、メモリセル選択線L Y 0～L Y nが活性化（L Y 0～L Y n = H i g h）され、メモリセルC L 0～C L nのメモリセル選択トランジスタT c l 0～T c l nは導通状態となる。次に、ワード線W L 0がH i g hとなり、続いてビット線B L 0がL o wになると、電流I 2がワード線W L 0から、チェイン選択トランジスタT c h 2、メモリセル選択トランジスタT c l 0～T c l nおよびチェイン選択トランジスタT c h 1を経由してビット線B L 0へ流れる。この電流I 2によるジュール熱が、可変抵抗型記憶素子R 0～R nへ伝導し、可変抵抗型記憶素子R 0～R nは一括して低抵抗となる。この電流I 2は、可変抵抗型記憶素子R 0～R nが一括して低抵抗にできる様な値に制御される。

[0095] 図8を用いて、チェインメモリアレイC Y 0およびC Y 1内の全可変抵抗型記憶素子R 0～R nを一括で低抵抗にする際の動作を説明する。チェインデコーダC H D E Cによって、チェインメモリアレイ選択線S L 0および1が活性化（S L 0、S L 1 = H i g h、S L 2 = H i g h）され、チェイン

メモリアレイCY0およびCY1双方のチェイン選択トランジスタTch0、Tch1およびTch2が導通状態となる。続いて、メモリセル選択線LY0～LYnが活性化(LY0～LYn=High)され、チェインメモリアレイCY0およびCY1双方のメモリセルCL0～CLnのメモリセル選択トランジスタTc10～Tc1nは導通状態となる。次に、ワード線WL0がHighとなり、続いてビット線BL0がLowになると、電流I3がワード線WLOから、チェイン選択トランジスタTch2、チェインメモリアレイCY0およびCY1双方のメモリセル選択トランジスタTc10～Tc1nおよびチェイン選択トランジスタTch0およびTch1を経由してビット線BL0へ流れる。この電流I3によるジュール熱が、チェインメモリアレイCY0およびCY1双方の可変抵抗型記憶素子R0～Rnへ伝導し、可変抵抗型記憶素子R0～Rnは一括して低抵抗となる。電流I3の値は、チェインメモリアレイCY0およびCY1双方の可変抵抗型記憶素子R0～Rnを一括して低抵抗にするような値に制御される。

[0096] 以上説明したように、必要に応じて、同時に複数のチェインメモリアレイ内のメモリセルを低抵抗にすることができ、消去データレートを向上することができる。

[0097] 図9～図12を用いて制御装置DYS-CTLおよびメモリ制御回路NVM-CTLが行う動的ロックサイズ変更の動作を説明する。

[0098] 図9は動的ロックサイズ変更の動作の全体フローを示す。また、図10、図11および図12では、図9のStep1およびStep3およびStep4の詳細動作を示す。図13および図14では、1次ロックサイズテーブルBLKTLおよび1次アドレス変換テーブルDLPTBLを示す。

[0099] 図9のフローにおいて、先ず、Step0で有効期間TCの測定を開始する。有効期間は、アクセスの特徴を分析するためのサンプリング期間である。

[0100] 次に、情報処理装置CPUGからルーター装置ROUTERを通じて、制御装置DYS-CTLへリードリクエスト(RQ)やライトリクエスト(

W Q ) が入力した際に、Step 1を実行する。Step 1では、Step 100～103を行う。

[01 01] 図 10 のフローにおいて、Step 100では、ホストからのアクセスがライトアクセスかどうかを判定する。ライトアクセスであれば、Step 101を行い、ライトアクセスでなければStep 102を行う。Step 101では、以下を計算する。

- ・各論理アドレスDLADのライトアクセス回数WC

- ・全論理アドレス領域でのライトアクセス回数WCT

- ・各論理アドレスDLADの総ライトデータ量WD

- ・全論理アドレス領域での総ライトデータ量WDT

Step 101が終了するとStep 102を行う。

[01 02] Step 102では、ホストからのアクセスがリードアクセスかどうかを判定する。リードアクセスであれば、Step 103を行い、リードアクセスでなければStep 100を行う。Step 103では、以下を計算する。

- ・各論理アドレスDLADのリードアクセス回数RC

- ・全論理アドレス領域でのリードアクセス回数RCT

- ・各論理アドレスDLADの総リードデータ量RD

- ・全論理アドレス領域での総リードデータ量RDT

Step 103が終了するとStep 2を行う。

[01 03] 図 9 に戻り、Step 2では、Step 3で行うアクセス特徴分析のための、Step 101およびStep 103で実行する各種計算の有効期間TCが期間T1を経過したかどうかをチェックする。

[01 04] 有効期間T1を経過した場合、Step 3を行い、有効期間T1を経過していない場合、Step 1を行う。

[01 05] Step 3では、有効期間TCの測定を停止し、Step 1での各種計算結果を利用し、アクセスの特徴を分析する。Step 3では、Step 300～305を行う。

[0106] 図 1 1において、先ず Step 300 では、有効期間 T C の測定を一旦停止する。次の Step 301 では以下を計算する。

- 各論理アドレス D L A D の 1 回のライトアクセス当たりの平均ライトデータ量 A W D :  $A W D = \text{論理アドレス D L A D の総ライトデータ量 W D} / \text{論理アドレス D L A D の総ライトアクセス数 W C}$

- 各論理アドレス D L A D の 1 回のリードアクセス当たりの平均リードデータ量 A R D :  $A R D = \text{論理アドレス D L A D の総リードデータ量 R D} / \text{論理アドレス D L A D の総リードアクセス数 R C}$

次の Step 302 では以下を計算する。

- 全論理アドレス領域での 1 回のライトアクセス当たりの平均ライトデータ量 A W D T :  $A W D T = \text{全論理アドレス領域での総ライトデータ量 W D T} / \text{全論理アドレス領域での総ライトアクセス数 W C T}$

全論理アドレス領域での 1 回のリードアクセス当たりの平均リードデータ量 A R D T :  $A R D T = \text{全論理アドレス領域での総リードデータ量 R D T} / \text{全論理アドレス領域での総リードアクセス数 R C T}$

次の Step 303 では以下を計算する。

- 各論理アドレス D L A D のライトアクセス回数の割合 W C R A T E :  $W C R A T E = W C / (W C + R C)$

- 各論理アドレス D L A D のリードアクセス回数の割合 R C R A T E :  $R C R A T E = R C / (W C + R C) = 1 - W C R A T E$

次の Step 304 では以下を計算する。

- 全論理アドレス領域での総ライトアクセス回数 W C T に対する論理アドレス D L A D の総ライトアクセス回数 W C の割合 W R A T E 1 :  $W R A T E 1 = W C / W C T$

- 全論理アドレス領域での総リードアクセス回数 R C T に対する論理アドレス D L A D の総リードアクセス回数 R C の割合 R R A T E 1 :  $R R A T E 1 = R C / R C T$

次の Step 305 では以下を計算する。

・各論理アドレス D L A D の総ライドデータ量 W D と各論理アドレス D L A D の容量 L C P の比率 W D R A T E = W D / L C P

図 11 のフローではライトとリードの両方の特性を検討している。ライトの特性は、上述のように小さなロックに集中してアクセスさせたほうが、ガーベージコレクションのコピー量が減る。一方、リードのアクセスは不揮発性メモリに分散してデータが配置されたほうが、リード性能は向上する。よって性能/ランансを取るために、両者を考慮することがより望ましい。

[01 07] 図 9 に戻って説明を続ける。Step 3 の終了後 Step 4 を行う。Step 4 では、Step 3 での分析結果を利用して、各論理アドレス D L A D に対するロックサイズを決定する。Step 4 では、Step 4 00 ~ 402 を行う。

[01 08] 図 12において Step 4 00 では、

・各論理アドレス D L A D のロックサイズファクタ (Lock Size Factor) B L K F C T と、プロビジョナル容量ファクタ (Provisional Area Factor) P V F C T を計算する。

[01 09] ロックサイズファクタ B L K F C T は、

$$B L K F C T = (W C R A T E 1 / W R T 1 A V G) \times (A W D T / A W D)$$

で表す。

[01 10] W R T 1 A V G は、全論理アドレス領域の容量に対する各論理アドレス D L A D の容量の割合である。つまり、情報処理装置 C P U G からのライトアクセスが平均的に各論理アドレス D L A D へ生じた場合の、各論理アドレス D L A D のライトアクセス回数の割合である。W C R A T E 1 は各論理アドレス D L A D のライトアクセス回数の割合であるから、(W C R A T E 1 / W R T 1 A V G) が大きいということは、当該論理アドレスには平均以上にアクセス回数が集中していること、すなわちホットエリアであることを示す。

[01 11] A W D T は全論理アドレス領域での 1 回のライトアクセス当たりの平均ライドデータ量、A W D は各論理アドレス D L A D の 1 回のライトアクセス当たりの平均ライドデータ量である。よって、(A W D T / A W D) が大きい

ということは、当該論理アドレスに書き込まれる1回あたりのデータが、平均より小さいということを示す。以上の説明より明らかのように、ロックサイズファクタBLKFCFは、1回のライトアクセス当たりのライトデータサイズが小さなライトアクセスが高頻度で、当該論理アドレスDLADへ発生している場合大きな値をとる指標である。後に詳述するように、本実施例では、BLKFCFが大きい場合、その論理アドレスに対応する物理アドレス（消去ロック）の大きさを小さくする制御を行う。

[01 12] 一方、1回当たりのサイズが大きなサイズのライトアクセスが、高頻度で、大量に発生する論理アドレスの場合は、消去回数が増えるのと、実効メモリ量を減少させないために、大きなサイズのロックのままにしておいたほうがよい。

[01 13] また、プロビジョナル容量ファクタPVFCFは、 $PVFCF = WDRAE / SUM(WDRAE)$ で表す。通常、論理アドレスの容量に対して、物理アドレスの容量は少し大きくなっている。この余裕分（例えば20%程度等）をプロビジョナル領域という。プロビジョナル領域を確保することにより、データの再書き込みを行った場合でも、使用可能な領域を枯渇しにくくすることができる。このプロビジョナル領域を変化させることにより、物理アドレス（消去ロック）中の無効データの割合を調節することができる。なぜなら、物理アドレスの有効データは、論理アドレス容量以上にはならないから、通常、物理アドレスは最大でプロビジョナル領域分の無効データを持つことができるからである。

[01 14] WDRAEは各論理アドレスDLADの総ライトデータ量WDと各論理アドレスDLADの容量LCPの比率であり、 $SUM(WDRAE)$ はそれらの合計である。よって、プロビジョナル容量ファクタPVFCFは、当該論理アドレスのデータがどれほどの割合ライトされているかを示している。後に詳述するように、本実施例では、PVFCFが大きい場合、その論理アドレスに対応する物理アドレス（消去ロック）のプロビジョナル領域を大きくする制御を行う。

- [01 15] プロビジョナル領域を大きくすることにより、消去ロックに含まれる無効データの割合を大きくすることができる。一方、プロビジョナル領域が大きくするということは、物理アドレスを余計に消費することになるから、プロビジョナル領域を大きくする物理アドレスは、ライトされる割合の大きな（すなわち、無効データの量が多くなる可能性のある）領域に限ることが望ましい。

- [01 16] 次のStep 401では各論理アドレスDLADのロックサイズファクタBLKFACTを利用し、各論理アドレスDLADのロックサイズBLKSIZEを決定する。

- [01 17] ロックサイズファクタBLKFACTが大きな値をもつ論理アドレスDLADほど、1回のライトアクセス当たりのライトデータサイズが小さなライトアクセスが、高頻度で、大量に、その当該論理アドレスDLADへ発生していることを示す。したがって、ロックサイズファクタBLKFACTが大きな値をもつ論理アドレスDLADほど、小さなロックサイズを割り当てるにより、ロック内の有効となる物理ページの数が少くなり、メモリモジュールNVM内部で行うガーベージコレクション動作に伴うデータコピー量が小さくなる。このため、データコピー時間が短くなるため、制御装置DYBS-CTLからのリードリクエストRQやライトリクエストWQの待ち時間が短くなり性能が向上する。

- [01 18] ライトアクセスが非常に高頻度で、大量に、特定の領域に集中している場合、極端な例では、その領域に有効な物理ページがなくなる場合もある。このような場合には、データコピー自体不要であり、当該領域を消去するだけになる。ロックサイズを適切に選ぶと、このようにデータコピー自体不要になる場合が増え、性能が向上することが期待できる。

- [01 19] なお、アクセス頻度が高い論理アドレス領域のことをHOTエリアといい、ここに書き込まれるデータをHOTデータともいう。また、アクセス頻度が低い論理アドレス領域のことをCOLDエリアといい、ここに書き込まれるデータをCOLDデータともいう。

- [0120] プロックサイズファクタ $B_LK_{FACT}$  値の判定数値は一例であってとくに限定しないが、以下に例を示す判定によってプロックサイズ $B_LK_{SIZE}$ を決定する。

- [0121] プロックサイズファクタ $B_LK_{FACT} \geq 10$  の場合、プロックサイズ $B_LK_{SIZE} = 32KB$

- 10 > プロックサイズファクタ $B_LK_{FACT} \geq 5$  の場合、プロックサイズ $B_LK_{SIZE} = 64KB$ 、

- 5 > プロックサイズファクタ $B_LK_{FACT} \geq 2$  の場合、プロックサイズ $B_LK_{SIZE} = 128KB$ 、

- 2 > プロックサイズファクタ $B_LK_{FACT} \geq 1$  の場合、プロックサイズ $B_LK_{SIZE} = 256KB$ 、

- 1 > プロックサイズファクタ $B_LK_{FACT} \geq 0.2$  の場合、プロックサイズ $B_LK_{SIZE} = 512KB$ 、

- 0.2 > プロックサイズファクタ $B_LK_{FACT}$  の場合、プロックサイズ $B_LK_{SIZE} = 1024KB$

- 次の Step 402 では各論理アドレス $D_LAD$  のプロビジョナル容量ファクタ $PVFCT$  を利用し、各論理アドレス $D_LAD$  のプロビジョナル容量 $PVSIZE$  を決定する。

- [0122] プロビジョナル容量ファクタ $PVFCT$  が大きな値をもつ論理アドレス $D_LAD$ ほど、ライトデータ量が多いことを示す。したがって、論理アドレス $D_LAD$ へ、書き換え回数に上限のある不揮発性メモリの物理アドレス $D_PAD$ を割り当てる場合、メモリモジュール $NVMD$  の寿命が情報処理システムの寿命を決定するため、メモリモジュール $NVMD$  を寿命が長くするよう、プロビジョナル容量ファクタ $PVFCT$  が大きな値をもつ論理アドレス $D_LAD$ ほど、プロビジョナル領域全容量 $PVAREA$  の中で、その論理アドレス $D_LAD$ へ割り当てる容量が大きくする必要がある。

- [0123] そこで、プロビジョナル容量 $PVSIZE$  は、 $PVSIZE = PVFCT \times$  プロビジョナル領域全容量 $PVAREA$  と表すことができる。

- [01 24] 図 9において、次の Step 5 では、制御装置 DYBS\_CTL は Step 4 で求めたロックサイズ BLKSIZE とプロビジョナル容量 PVSIZE を利用し、ロックサイズを示す 1 次ロックサイズテーブル BLKTBL\_1 と 1 次アドレス変換テーブル DLPTBL\_1 を作成する。

- [01 25] さらに、制御装置 DYB3\_〇丁<sub>1</sub>0～m が 1 次ロックサイズテーブル BLKTBL\_1 と、1 次アドレス変換テーブル DLPTBL\_1 を作成した後に、

制御装置 DYBS\_CTL は、メモリ制御回路 NVM\_CTL へ、1 次プロックサイズテーブル BLKTBL\_1 と、1 次アドレス変換テーブル DLPTBL\_1 を転送し、2 次アドレス変換テーブル DLPTBL\_2 と、プロック毎の消去回数テーブル ERSTBL と、アドレスマップ ADMAP を新規に作成するよう指示する。

メモリ制御回路 NVM\_CTL は制御装置 DYBS\_CTL の指示に従つて、

1 次プロックサイズテーブル BLKTBL\_1 および 1 次アドレス変換テーブル DLPTBL\_1 の情報を基に、2 次アドレス変換テーブル DLPTBL\_2 と、プロック毎の消去回数テーブル ERSTBL と、アドレスマップ ADMAP を作成する。

- [01 26] 次の Step 6 では、制御装置 DYBS\_CTL は、メモリモジュール NVMD が製品寿命に到達したかをチェックする。

- [01 27] メモリモジュール NVMD が製品寿命に到達しなかった場合、Step 7 を行う。メモリモジュール NVMD が製品寿命に到達した場合、メモリ制御回路 NVM\_CTL は動的ロックサイズ変更の動作を終了する。

Step 7 では、有効期間 TC の測定を再開する。

- [01 28] 図 13(A) および (B) には、制御装置 DYBS\_CTL が最初に (すなわち、図 9 で、1 回目の有効期間 TC (T1) の測定と分析が終わった後) 作成した、64 個の論理アドレス DLAD 每に対応した 1 次ロックサイズテーブル BLKTBL\_1 と 1 次アドレス変換テーブル DLPTBL\_1 を示す。

- [01 29] 図 14 (A) および (B) には、制御装置 D Y B S — C T L が 2 回目 (すなわち、図 9 で、2 回目の有効期間 T C (T 2) の測定と分析が終わった後) に作成した、64 個の論理アドレス D L A D 每に対応した 1 次ロックサイズテーブル B L K T B L 1 と 1 次アドレス変換テーブル D L P T B L 1 を示す。

- [01 30] ロックサイズテーブルは、各論理アドレスに対してアクセス特性と、アクセス特性に基づいた物理ロック仕様を表している。ロックサイズテーブルにおいては、既述のように、D L A D は論理アドレス、W C R A T E 1 はライトアクセス回数の割合、A W D は論理アドレスの 1 回のライトアクセス当たりの平均ライトデータ量、W D R A T E は各論理アドレス D L A D の総ライトデータ量 W D と各論理アドレス D L A D の容量 L C P の比率である。

- [01 31] B L K F C T はロックサイズファクタで、これが大きな値をもつ論理アドレス D L A D ほど、1 回のライトアクセス当たりのライトデータサイズが小さなライトアクセスが高頻度で、当該論理アドレス D L A D へ発生していることを示す。B L K S I Z E は論理アドレス D L A D のロックサイズ、P V F C T はプロビジョナル容量ファクタで、これが大きな値をもつ論理アドレス D L A D ほど、ライトデータ量が多いことを示す。P V S I Z E はプロビジョナル容量である。

- [01 32] W R T 1 A V G は全論理アドレス領域の容量に対する各論理アドレス D L A D の容量の割合、A W D T は全論理アドレス領域での 1 回のライトアクセス当たりの平均ライトデータ量、P V A R E A はプロビジョナル領域全容量である。

- [01 33] アドレス変換テーブルは、ロックサイズテーブルに基づいて、論理アドレスに対する物理アドレスの割り当てを表す。アドレス変換テーブルにおいては、D P A D は論理アドレス D L A D に対応したメモリモジュールの物理アドレス、D P A D S I Z E は物理アドレスの容量、P R A R E A はプロビジョナル領域に割り当てられた物理アドレスである。図 13 (A) のプロッ

クサイズテーブル B L K T B L をみると、

論理アドレス D L A D 0 ~ 6 3 へは、1回のライトアクセス当たりのライトデータサイズが小さなライトアクセスが、高頻度で、大量に、発生しているため、ロックサイズファクタ B L K F C T の値が、8 . 2 8 と高い値になっている。

そのため、論理アドレス D L A D 0 ~ 6 3 のロックサイズ B L K S I Z E は比較的小さな 6 4 K B となる。

[0134] 一方、論理アドレス D 1 八 D 4 4 8 ~ 5 1 1 へは、1回のライトアクセス当たりのライトデータサイズが大きなライトアクセスが、低頻度で、少量発生しているためロックサイズファクタ B L K F C T の値が、0 . 0 3 と低いあたいたくなっている。そのため、論理アドレス D L A D 4 4 8 ~ 5 1 1 のロックサイズ B L K S I Z E は比較的大きな 1 0 2 4 K B となる。

[0135] また、論理アドレス D L A D 0 ~ 6 3 へのライトとデータ量が多いため、プロビジョナル容量ファクタ P V F C T の値が 0 . 2 5 と最も高い値を示している。そのため、論理アドレス D L A D 0 ~ 6 3 のプロビジョナル容量 P V S I Z E は 3 2 と最も高い値となる。

[0136] 一方、論理アドレス D 1 八 D 4 4 8 ~ 5 1 1 への、ライトとデータ量が少ないため、プロビジョナル容量ファクタ P V F C T の値が 0 . 0 5 5 と最も低い値を示している。そのため、論理アドレス D L A D 4 4 8 ~ 5 1 1 のプロビジョナル容量 P V S I Z E は 7 と最も低い値となる。

[0137] 図 13 (B) のアドレス変換テーブル D L P T B L をみると、論理アドレス D L A D 0 ~ 6 3 へ割り当てられている物理アドレス D P A D は D P D A O ~ 6 3 、 D P A D 5 1 2 ~ 5 4 3 である。

[0138] つまり、論理アドレス D L A D 0 ~ 6 3 へ割り当てられている物理アドレス D P A D の容量 D P A D S I Z E は最も大きな値 9 6 となっている。これは、論理アドレス D L A D 0 ~ 6 3 のプロビジョナル容量 P V S I Z E の値 3 2 が論理アドレス D L A D 0 ~ 6 4 までの容量値 6 4 へ加算されているためである。

[0139] 一方、論理アドレス D<sub>1</sub> 八D448～511へ割り当てられている物理アドレス D P A D は D P D A 448～511、D P A D 631～639である。

つまり、論理アドレス D<sub>1</sub> 六D448～511へ割り当てられている物理アドレス D P A D の容量 D P A D S I Z E は最も小さな値 71 となっている。これは、論理アドレス D<sub>1</sub> 八D448～511のプロビジョナル容量 P V S I Z E の値 7 が論理アドレス D L A D 448～511までの容量値 64 へ加算されているためである。

[0140] 図 14 (A) のロックサイズテーブル B L K T B L をみると、論理アドレス D L A D 0～63 のロックサイズファクタ B L K F C T の値が、11.04 と高い値になっている。そのため、論理アドレス D L A D 0～63 のロックサイズ B L K S I Z E は 32KB となる。

[0141] つまり、このロックサイズファクタ B L K F C T の値は、制御装置 D Y B S—C T L が 1 回目に作成したロックサイズテーブル B L K T B L での論理アドレス D L A D 0～63 のロックサイズファクタ B L K F C T よりも高い値となっている。これは論理アドレス D L A D 0～63 へ 1 回のライトアクセス当たりのライトデータサイズが小さなライトアクセスが、さらに、高頻度で、大量に、発生していることを示す。

[0142] 制御装置 D Y B S—C T L は、論理アドレス D L A D 每のライトアクセスの特徴を抽出し、論理アドレス D L A D 0～63 のロックサイズ B L K S I Z E を 64KB から 32KB へ変更している。

[0143] また、論理アドレス D L A D 192～255 のロックサイズファクタ B L K F C T の値が、0.58 と低い値になっている。そのため、論理アドレス D L A D 192～255 のロックサイズ B<sub>1</sub> に 31Z E は 512KB となる。

つまり、このロックサイズファクタ B L K F C T の値は、制御装置 D Y B S—C T L が 1 回目に作成したロックサイズテーブル B L K T B L での論理アドレス D L A D 192～255 のロックサイズファクタ B L K F C T

よりも低い値となっている。これは論理アドレス D L A D 1 9 2 ~ 2 5 5 へ 1 回のライトアクセス当たりのライトデータサイズが大きなライトアクセスが、さらに、低頻度で、発生していることを示す。

- [0144] 制御装置 D Y B S — C T L は、論理アドレス D L A D 每のライトアクセスの特徴を抽出し、論理アドレス D L A D 1 9 2 ~ 2 5 5 のプロックサイズ B L K S I Z E を 2 5 6 K B から 5 1 2 K B へ変更している。

- [0145] 図 14 (B) のアドレス変換テーブル D L P T B L をみると、論理アドレス D L A D 0 ~ 6 3 へ割り当てられている物理アドレス D P A D は D P D A 0 ~ 6 3 、 D P A D 5 1 2 ~ 5 6 4 である。

- [0146] つまり、論理アドレス D L A D 0 ~ 6 3 へ割り当てられている物理アドレス D P A D の容量 D P A D S I Z E は 1 1 7 となっている。

- [0147] これは、制御装置 D Y B S — C T L が 1 回目に作成したアドレス変換テーブル D L P T B L での論理アドレス D L A D 0 ~ 6 3 のプロビジョナル容量 P V S I Z E よりも高い値である 5 3 となっているためである。

- [0148] この様に、制御装置 D Y B S — C T L は、論理アドレス D L A D 每のライトデータ量を計算し、論理アドレス D L A D 0 ~ 6 3 へ割り当てる物理アドレス D P A D の容量 D P A D S I Z E を 9 6 から 1 1 7 へ増加している。

- [0149] また、論理アドレス D L A D 1 9 2 ~ 2 5 5 へ割り当てられている物理アドレス D P A D は D P D A 1 9 2 ~ 2 5 5 、 D P A D 6 1 1 ~ 6 2 1 である。

つまり、論理アドレス D L A D 1 9 2 ~ 2 5 5 へ割り当てられている物理アドレス D P A D の容量 D P A D S I Z E は 7 5 となっている。

- [0150] これは、制御装置 D Y B S — C T L が 1 回目に作成したアドレス変換テーブル D L P T B L での論理アドレス D L A D 1 9 2 ~ 2 5 5 のプロビジョナル容量 P V S I Z E よりも低い値である 1 1 となるためである。

- [0151] この様に、制御装置 D Y B S — C T L は、論理アドレス D L A D 每のライトデータ量を計算し、論理アドレス D L A D 1 9 2 ~ 2 5 5 へ割り当てる物理アドレス D P A D の容量 D P A D S I Z E を 1 8 から 1 1 へ減少している

。

[01 52] 以上述べたように制御装置 D Y B S — C T L は、プロックサイズテーブルやアドレス変換テーブルに基づいた制御を行い、メモリアレイの消去プロックの大きさや、プロビジョナル領域の設定が行われる。特許文献 3 に示されている 3 次元構造の不揮発性メモリでは、N × M 個の 3 次元構造のメモリセルアレイ内のデータを一括で消去する方法が示されている。この N と M の値は、どのメモリセルアレイを選択するかによって決めることができる。また、消去動作時のジュール熱が、消去対象のメモリセルアレイへ隣接する周辺のメモリセルの結晶状態に大きな影響を及ぼさないように熱緩衝領域を設けることが示されている。しかし、この熱緩衝領域にはデータを書き込まないため消去データ単位を小さくするほど、熱緩衝領域の割合が増え、実効メモリ容量が減少してしまう。すなわち、プロックのプロックサイズを均等に小さくすれば、プロック内の有効データ量が少なくなるという効果はあるが、プロックの境界部分に熱緩衝領域が配置されている場合、その割合が増え、実効的なデータ容量が減少する。このように、従来の不揮発性メモリ装置では、SSD の性能と実効メモリ容量はトレードオフの関係にあった。よつて、必要に応じてプロックサイズを変化させる本実施例の構成に利点がある。

。

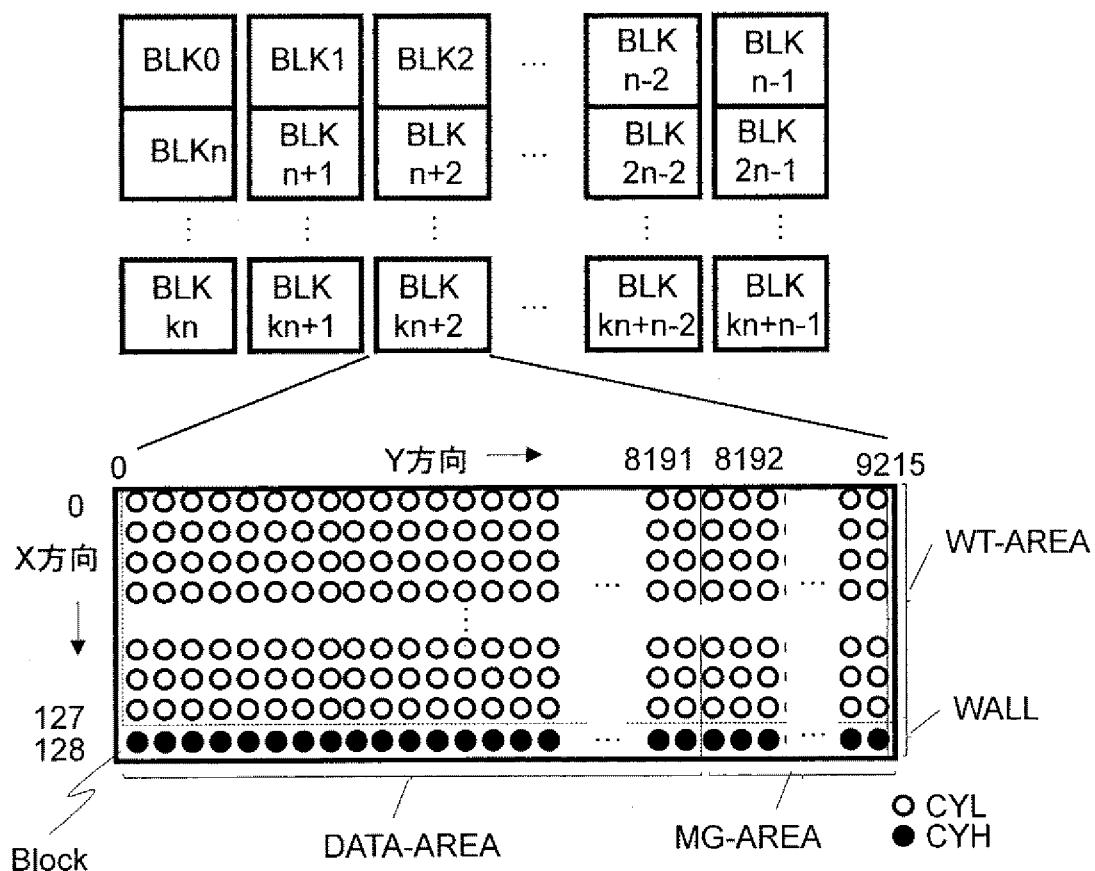

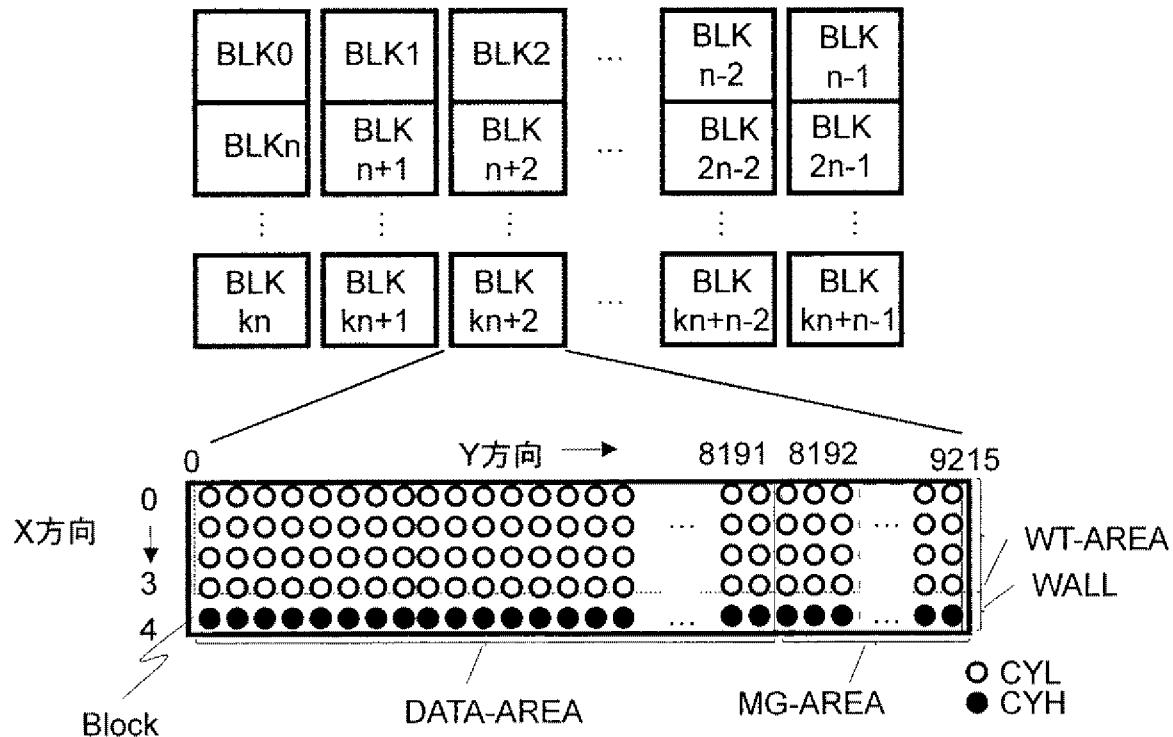

[01 53] 図 15 は、制御装置 D Y B S — C T L がメモリ制御回路 N V M — C T L へ転送したプロックサイズテーブル B L K T B L 情報を基に、メモリ制御回路 N V M — C T L が作成したアドレスマップ A D M A P 情報を利用し、構築する不揮発性メモリ装置 N M V のメモリアレイのプロック構成の一例であり、プロックサイズが 1024 KB の場合のプロック構成の一例である。

[01 54] 一つのプロックは、129 (X 方向 : X \_ B L K) × 9216 (Y 方向 : Y — B L K) × 8 (Z 方向 : Z — B L K) のチェインメモリアレイにて構成され、そのサイズは 11888864 バイト (= 129 (X 方向) × 9216 (Y 方向) × 8 (Z 方向)) であることを示す。

[01 55] また、消去データ単位は、8 (X 方向 : X E R S) × 72 (Y 方向 : Y E

R S ) X 8 (Z 方向 : Z E R S ) のメモリアレイが一括で低抵抗になり、その消去データサイズは 576 バイト (= 9 (X 方向) X 72 (Y 方向) X 8 (Z 方向) ) である。

[01 56] また、X 方向に一行分だけのメモリアレイ、つまり 1 (X 方向 : X W A L ) X 9216 (Y 方向) X 8 (Z 方向) のメモリアレイが熱緩衝領域 W A L L として設定され、そのサイズは 9216 バイト (= 1 (X 方向) X 9216 (Y 方向) X 8 (Z 方向) ) であることを示す。

[01 57] 不揮発性メモリ装置は、プロック B L K 0 ~ B L K kn+n-1 で構成されており、それぞれのプロック内のメモリアレイ A R Y のチェインメモリアレイ C Y L と、チェインメモリアレイ C Y H の配置の一例が示されている。これらの図において、チェインメモリアレイ C Y L は、白い丸印で示され、熱緩衝領域を構成するチェインメモリアレイ C Y H は、黒い丸印で示されている。以下の図面においても、チェインメモリアレイ C Y L とチェインメモリアレイ C Y H は同様な表示方法をする。

[01 58] 図 15において、一つのプロックは、129 (X 方向) X 9216 (Y 方向) のチェインメモリアレイにて構成され、そのサイズは 11888864 バイト (= 129 (X 方向) X 9216 (Y 方向) X 8 (Z 方向) ) である。このプロックが多数個配置され、図 4 に示す不揮発性メモリのメモリアレイを構成する。

[01 59] 一つのプロック内の書き込み領域 W T - A R E A は、消去領域と同一で、複数のチェインメモリアレイ C Y L が物理的に集まって形成されている領域である。

[01 60] 書込み領域 W T - A R E A のサイズは 1179648 バイト (= 128 (X 方向) X 9216 (Y 方向) X 8 (Z 方向) ) である。

[01 61] 書込み領域 W T - A R E A 内のデータ領域 D A T A - A R E A のサイズは 1048576 バイト (= 128 (X 方向) X 8192 (Y 方向) X 8 (Z 方向) ) で、書き込み領域 W T - A R E A 内の管理領域 M G - A R E A のサイズは 131072 バイト (= 128 (X 方向) X 1024 (Y 方向) X 8 (Z 方向) ) である。

z 方向 ) ) である。

[01 62] 一つの論理アドレス L A D のデータサイズは、8 1 9 2 バイトであり、情報処理回路 C O N T L は、このデータ D A T A に対する E C C コードを生成し、不揮発性メモリのメモリアレイのロック内の書き込み領域 W T \_ A R E A へ、データ D A T A と E C C コードを書き込む。

[01 63] また、一つの物理アドレスには、一つの論理アドレス L A D のデータ D A T A を書き込む 8 1 9 2 バイトのデータ領域 D A T A — A R E A と、データ D A T A に対する E C C コードなどを書き込む 1 0 2 4 バイトの管理領域 M G \_ A R E A が割り当てられるため、

1 0 4 8 5 7 6 バイトの書き込み領域 W T \_ A R E A には、128つの論理アドレス L A D に対する物理アドレスのデータが格納される。

[01 64] また、熱緩衝領域 WALL は、書き込み領域 W T \_ A R E A の外側に配置される複数のチェインメモリアレイ C Y H が物理的に集まって形成されている領域である。

[01 65] 図 15において、熱緩衝領域 WALL のサイズは 9 2 1 6 バイト (= 1 (X 方向) X 9 2 1 6 (Y 方向) X 8 (Z 方向)) である。

[01 66] また、先ず、書き込み領域 W T — A R E A (= 消去領域) 内の全チェインメモリアレイ C Y L に含まれる全メモリセルのデータは、"1" (S e t 状態 : 低抵抗状態) となる。すなわち、一括消去され、次に、物理アドレス P A D 毎に、"0" のデータのみが (R e s e t 状態 : 高抵抗状態) が書き込まれる。たとえば、書き込み領域 W T — A R E A サイズが 1 1 7 9 6 4 8 バイトで、一回の消去動作による一括消去データサイズが 5 7 6 バイトである場合、2 0 4 8 回の消去動作が Y 方向と平行な方向に、順に行われ、書き込み領域 W T — A R E A の全メモリセルのデータは、"1" (S e t 状態 : 低抵抗状態) となる。

[01 67] 热緩衝領域 WALL に対しては消去動作が行われないため、書き込み領域へ消去動作を行つた際の热ディスクタップによる信頼性低下の影響が、隣接するロックへ及ぼされることはない。さらに、熱緩衝領域 WALL に対しては、"0"

のデータ（Reset状態：高抵抗状態）も書き込まれることは無い。熱緩衝領域となるメモリアレイCYHは構造的には通常のメモリセルであるが、制御装置により、書き込みや消去が行われないように制御される。

[01 68] この様に、チエインメモリアレイCYHを熱緩衝領域WALLとして書き込み領域（＝消去領域）の周辺に配置することで、熱ディィスターブによる信頼性低下を防ぐことができる。

[01 69] なお、図15ではX方向には熱緩衝領域WALLが形成されていない。この実施例ではデバイス構造として、各ロックBLKの間にはY方向に物理的に間隔が設けられているため、X方向には熱緩衝領域WALLが必要ないため形成されていないが、必要に応じてX方向にも熱緩衝領域を設けてよい。

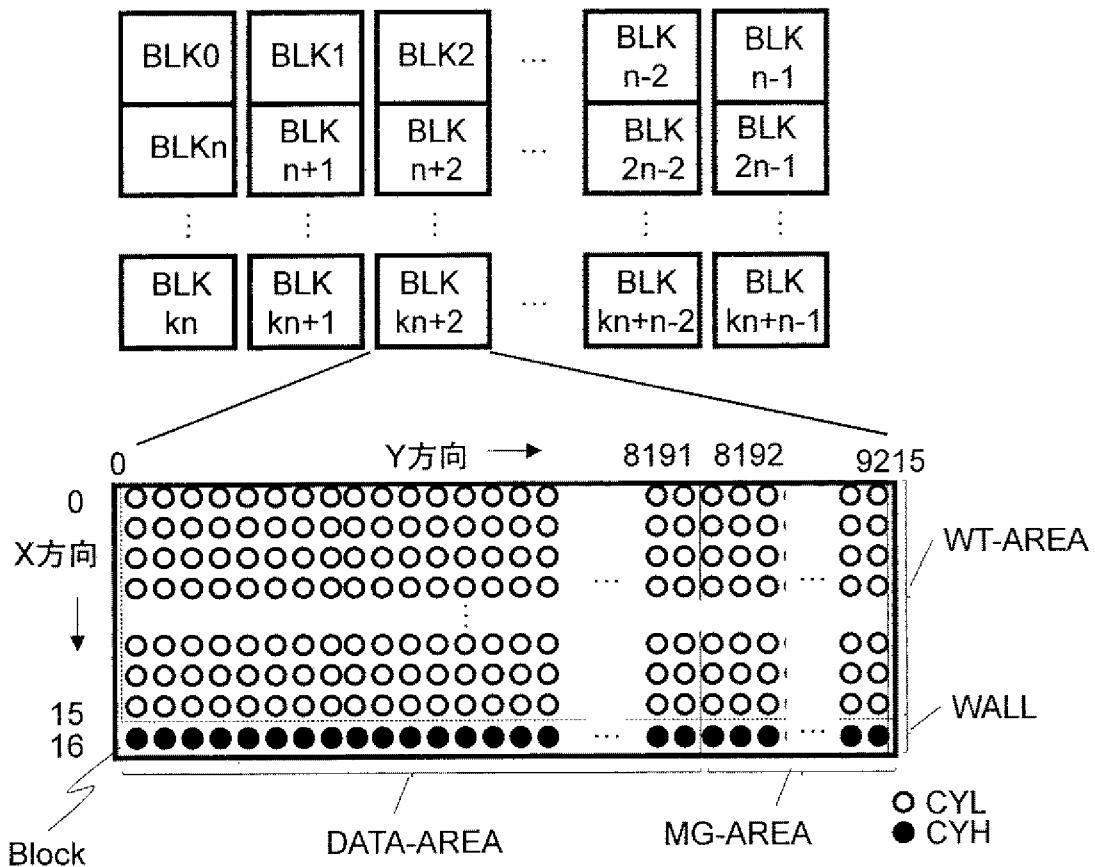

[01 70] 図16は、制御装置DYS-CCTLがメモリ制御回路NVM-CCTLへ転送したロックサイズテーブルBLKTBL情報を基に、メモリ制御回路NVM-CCTLが作成したアドレスマップADMAP情報を利用し、構築する不揮発性メモリ装置NMVのメモリアレイのロック構成の一例であり、ロックサイズが128KBの場合のロック構成の一例である。

[01 71] 一つのロックは、17（X方向：X-BLK）×9216（Y方向：Y-BLK）×8（Z方向：Z-BLK）のチエインメモリアレイにて構成され、そのサイズは156672バイト（＝17（X方向）×9216（Y方向）×8（Z方向））である。

[01 72] また、消去データ単位および熱緩衝領域WALLは、図15と同様である。チエインメモリアレイCYLとチエインメモリアレイCYHの表示方法は図15と同様である。

[01 73] 図16において、一つのロックは、17（X方向）×9216（Y方向）のチエインメモリアレイにて構成され、そのサイズは156672バイト（＝17（X方向）×9216（Y方向）×8（Z方向））である。このロックが多数個配置され、図4に示す不揮発性メモリのメモリアレイを構成する。

[01 74] 一つのロック内の書き込み領域WT-AREAは、消去領域と同一で、複

数のチェインメモリアレイCYLが物理的に集まって形成されている領域である。

- [0175] 書込み領域WT AREAのサイズは147456バイト(=16(X方向)X9216(Y方向)X8(Z方向))である。

- [0176] 書込み領域WT AREA内のデータ領域DATA-AREAのサイズは131072バイト(=16(X方向)X8192(Y方向)X8(Z方向))で、書込み領域WT AREA内の管理領域MG-AREAのサイズは16384バイト(=16(X方向)X1024(Y方向)X8(Z方向))である。

- [0177] 情報処理回路CONTLによる不揮発性メモリのメモリアレイへの書き込み方法および消去方法は、図15と同様である。

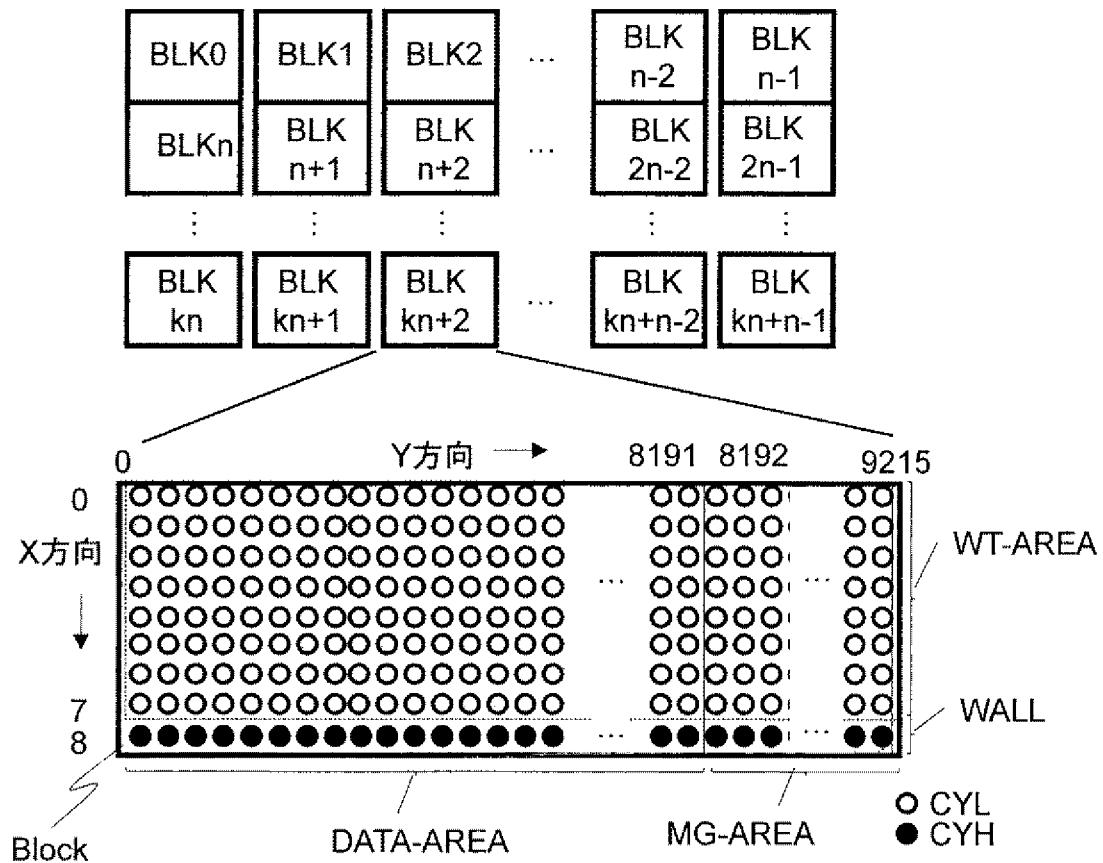

- [0178] 図17は、制御装置DYBS-CTLがメモリ制御回路NVM-CTLへ転送したロックサイズテーブルBLKCTL情報を基に、メモリ制御回路NVM-CTLが作成したアドレスマップADMAP情報を利用し、構築する不揮発性メモリ装置NMVのメモリアレイのロック構成の一例であり、ロックサイズが64KBの場合のロック構成の一例である。

- [0179] 一つのロックは、9(X方向:X-BLK)X9216(Y方向:Y-BLK)X8(Z方向:Z-BLK)のチェインメモリアレイにて構成され、そのサイズは82944バイト(=9(X方向)X9216(Y方向)X8(Z方向))である。

- [0180] また、消去データ単位および熱緩衝領域WALLは、図15と同様である。チェインメモリアレイCYLとチェインメモリアレイCYHの表示方法は図15と同様である。

- [0181] 図17において、一つのロックは、9(X方向)X9216(Y方向)のチェインメモリアレイにて構成され、そのサイズは82944バイト(=9(X方向)X9216(Y方向)X8(Z方向))である。このロックが多数個配置され、図4に示す不揮発性メモリのメモリアレイを構成する。

- [0182] 一つのロック内の書き込み領域WT-AREAは、消去領域と同一で、複

数のチェインメモリアレイCYLが物理的に集まって形成されている領域である。

[0183] 書込み領域WT AREAのサイズは73728バイト(=8(X方向)X9216(Y方向)X8(Z方向))である。

[0184] 書込み領域WT AREA内のデータ領域DATA-AREAのサイズは65536バイト(=8(X方向)X8192(Y方向)X8(Z方向))で、書込み領域WT AREA内の管理領域MG AREAのサイズは8192バイト(=8(X方向)X1024(Y方向)X8(Z方向))である。

[0185] 情報処理回路CONTLによる不揮発性メモリのメモリアレイへの書き込み方法および消去方法は、図15と同様である。

[0186] 図18は、制御装置DYBS-CTLがメモリ制御回路NVM-CTLへ転送したロックサイズテーブルBLKCTL情報を基に、メモリ制御回路NVM-CTLが作成したアドレスマップADMAP情報を利用し、構築する不揮発性メモリ装置NMVのメモリアレイのロック構成の一例であり、ロックサイズが32KBの場合のロック構成の一例である。

[0187] 一つのロックは、5(X方向:X-BLK)X9216(Y方向:Y-BLK)X8(Z方向:Z-BLK)のチェインメモリアレイにて構成され、そのサイズは46080バイト(=5(X方向)X9216(Y方向)X8(Z方向))である。

[0188] また、消去データ単位および熱緩衝領域WALLは、図15と同様である。チェインメモリアレイCYLとチェインメモリアレイCYHの表示方法は図15と同様である。

[0189] 図18において、一つのロックは、5(X方向)X9216(Y方向)のチェインメモリアレイにて構成され、そのサイズは46080バイト(=9(X方向)X9216(Y方向)X8(Z方向))である。このロックが多数個配置され、図4に示す不揮発性メモリのメモリアレイを構成する。

[0190] 一つのロック内の書き込み領域WT-AREAは、消去領域と同一で、複

数のチェインメモリアレイCYLが物理的に集まって形成されている領域である。

- [0191] 書込み領域WT\_AREAのサイズは36864バイト(=4(X方向)X9216(Y方向)X8(Z方向))である。

- [0192] 書込み領域WT\_AREA内のデータ領域DATA-AREAのサイズは32768バイト(=8(X方向)X8192(Y方向)X8(Z方向))で、書込み領域WT\_AREA内の管理領域MG\_AREAのサイズは8192バイト(=8(X方向)X1024(Y方向)X8(Z方向))である。

- [0193] 情報処理回路CONTLによる不揮発性メモリのメモリアレイへの書き込み方法および消去方法は、図15と同様である。

- [0194] 図15～図18で説明した様に、ロックサイズテーブルBLKTBLL情報を基に、メモリ制御回路NVM-CTLが、図4に示す不揮発性メモリのメモリアレイのロックサイズを最適に構成でき、不揮発性メモリ容量に対する熱緩衝領域の割合を抑え、メモリモジュールMDの低コスト化と高性能化を実現できる。

- [0195] 図15～図18では、ロックサイズを変更するに際して、Y方向の幅を変えずにX方向の幅を変更しているが、サイズの変更方法としてはこれに限るものではなく、Y方向の幅を変更してもよい。ただし、図15～図18の手法では、X方向に並ぶロックの境界を変更するために、Y方向に並ぶメモリアレイCYHの位置を変更するだけでよいので制御が簡単である。また、Y方向に並ぶロックの境界は、デバイス構造による物理的な間隔を利用しているので、熱緩衝領域の設定が必要ないという利点もある。なお、熱緩衝の影響を無視できるデバイス構造であれば、熱緩衝領域は設けなくてもよい。

- [0196] (まとめ)

以上に説明した各実施の形態によって得られる主な効果は以下の通りである。

- [01 97] 第 1 に、論理アドレス毎に生じるライトおよびリードリクエストの特徴量を抽出することにより、論理アドレスのロックサイズ最適に変更でき、半導体装置のデータ転送性能を向上できる。

- [01 98] 第 2 に、論理アドレス毎に生じるライトリクエストの特徴量を抽出することにより、各論理アドレス領域に対する物理アドレス領域の容量を最適化でき、半導体装置の信頼性を向上できる。

- [01 99] 第 3 に、論理アドレス毎に生じるライトおよびリードリクエストの特徴量を抽出することにより、論理アドレスのロックサイズ最適に変更でき、不揮発性メモリ容量に対する熱緩衝領域の割合を抑え、半導体装置の低コスト化を実現できる。

- [0200] 以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。例えば、上記した実施の形態は、本発明を分かり易く説明するために詳細に説明したものであり、必ずしも説明した全ての構成を備えるものに限定されるものではない。また、ある実施の形態の構成の一部を他の実施の形態の構成に置き換えることが可能であり、また、ある実施の形態の構成に他の実施の形態の構成を加えることも可能である。また、各実施の形態の構成の一部について、他の構成の追加・削除・置換をすることが可能である。また、実施の形態においては、主に相変化メモリを代表として説明を行ったが、R e R A M 等を含めた抵抗変化型のメモリであれば、同様に適用して同様の効果が得られる。

- [0201] また、実施例において、複数のメモリセルが半導体基板に対して高さ方向に順に積層して配置される 3 次元構造のメモリを代表として説明を行ったが、半導体基板に対して高さ方向に 1 つのメモリセルが配置される 2 次元構造のメモリにおいても同様に適用して同様の効果が得られる。

### 産業上の利用可能性

- [0202] 不揮発性メモリを利用した、記憶装置の技術分野に利用することができる。

## 符号の説明

[0203] A D C M D I F …アドレス・コマンドインターフェース回路、A R B …調停回路、A R Y …メモリアレイ、B K …メモリバンク、B L …ビット線、B S W …ビット線選択回路、B U F …バッファ、C A D L T …カラムアドレスラッ奇、C H …チェイン制御線、C H D E C …チェインデコーダ、C H L T …チェイン選択アドレスラッ奇、C L …相変化メモリセル、C O L D E C …カラムデコーダ、P A D …物理アドレス、C P A D …物理アドレス、C P U G …情報処理装置、C T L O G …制御回路、C Y …チェインメモリアレイ、D A T C T L …データ制御回路、D B U F …データバッファ、D S W …データ選択回路、D T …データ線、E N U M …エントリー番号、H D H \_ I F …インターフェース信号、H O S T \_ I F …インターフェース回路、I O B U F …I Oバッファ、L A D …論理アドレス、L R N G …論理アドレス領域、D L P T B L …アドレス変換テーブル、L Y …メモリセル選択線、L Y C …レイヤ番号、L Y N …データ書き込みレイヤ情報、M A P R E G …マップレジスタ、M D L C T …制御回路、M N E R C …最小消去回数、M N G E R …情報処理回路、M N I P A D …無効物理オフセットアドレス、M N V P A D …有効物理オフセットアドレス、M X E R C …最大消去回数、M X I P A D …無効物理オフセットアドレス、M X V P A D …有効物理オフセットアドレス、N V C T …メモリ制御回路、N V M …不揮発性メモリ装置、N V M M D …メモリモジュール、P A D …物理アドレス、P A D T B L …物理アドレステーブル、P E R C …消去回数、P P A D …物理オフセットアドレス、P R N G …物理アドレス領域、P V L D …有効フラグ、R …記憶素子、R A D L T …ロウアアドレスラッ奇、R A M …ランダムアクセスメモリ、R A M C …メモリ制御回路、R E F \_ C L K …基準クロック信号、R E G …レジスタ、R O W D E C …ロウデコーダ、R S T S I G …リセット信号、S A …センスアンプ、S G A D …物理セグメントアドレス、S L …チェインメモリアレイ選択線、S T R E G …ステータスレジスタ、S W B …読み書き制御ブロック、S Y M D …クロック生成回路、T c h …チェイン選択トランジスタ、T c \_ T …

メモリセル選択トランジスタ、THMO…温度センサ、TNIPA…無効物理アドレス総数、TNVPA…有効物理アドレス総数、WDR…ライトドライバ、WL…ワード線、WV…書き込みデータ検証回路、CPUG…情報処理装置、ROUTER…ルーター装置、DYBS\_CTL0～31…制御装置、STRG0～31…ストレージ装置、CPU0～31…情報処理回路、MDO～31～CPUメモリモジュール、M0～7…メモリ装置を備える。NVMDO～31…メモリモジュール、NVM0～NVM31…不揮発性メモリ装置、RAM0…ランダムアクセスメモリNVM—CTL…メモリ制御回路、BLKTBL…ロックサイズテーブル、DLPTBL…アドレス変換テーブル、DLAD…論理アドレス、DPAD…物理アドレス、ERSTB\_L…消去回数テーブル、ADMAPP…アドレスマップ

## 請求の範囲

[請求項 1] 消去単位と書き込み単位が異なる不揮発性メモリの制御方法であつて、

所定単位の論理アドレスに対して前記不揮発性メモリの物理アドレスを割り当て、

前記所定単位の論理アドレスに対するライトアクセスの状況に応じて、当該論理アドレスに割り当てられる物理アドレスが含まれる前記消去単位の大きさを制御することを特徴とする、不揮発性メモリの制御方法。

[請求項 2] 前記ライトアクセスの状況は、前記所定単位の論理アドレスの平均ライトデータ量および前記所定単位の論理アドレスのライトアクセス回数の少なくとも一つを含むことを特徴とする、請求項 1 記載の不揮発性メモリの制御方法。

[請求項 3] 前記ライトアクセスの状況は、全ての論理アドレスの平均ライトデータ量および全ての論理アドレスのライトアクセス回数の少なくとも一つを含むことを特徴とする、請求項 2 記載の不揮発性メモリの制御方法。

[請求項 4] さらに、前記所定単位の論理アドレスに対するリードアクセスの状況に応じて、前記消去単位の大きさを制御することを特徴とする、請求項 1 記載の不揮発性メモリの制御方法。

[請求項 5] 前記所定単位の論理アドレスに対するライトアクセスの状況に応じて、前記割り当てられる物理アドレスに含まれるプロビジョナル領域の量を制御することを特徴とする請求項 1 記載の不揮発性メモリの制御方法。

[請求項 6] 不揮発性メモリの制御装置であつて、

論理アドレスに対して前記不揮発性メモリの物理アドレスを割り当て、前記物理アドレスにアクセスを行う制御回路を有し、

前記制御回路は、前記論理アドレスに対するアクセス状況に基づい

て、当該論理アドレスに対応する前記物理アドレスを含む消去単位プロックの大きさを動的に変化させることを特徴とする不揮発性メモリの制御装置。

[請求項7]

不揮発性メモリと、

入力される論理アドレスに対して物理アドレスを割り当て、前記不揮発性メモリの前記物理アドレスにアクセスを行う制御回路と、を有し、

前記制御回路は、前記不揮発性メモリの前記物理アドレスを含むプロックのプロックサイズを動的に変化させ、書き込みを行うことを特徴とする半導体記憶装置。

[請求項8]

請求項7に記載の半導体記憶装置において、

前記制御回路は、前記論理アドレス毎に、前記制御回路へ入力するライトリクエストの第1特徴量を計算し、前記第1特徴量に基づいて、前記不揮発性メモリの前記物理アドレスを含む前記プロックのプロックサイズを決定することを特徴とする半導体記憶装置。

[請求項9]

請求項7に記載の半導体記憶装置において、

前記制御回路は、前記論理アドレス毎に、前記制御回路へ入力するライトリクエストの第2特徴量を計算し、前記第2特徴量に基づいて、前記論理アドレスを複数個分含む論理アドレス領域の容量に対する、前記物理アドレスを複数個分含む物理アドレス領域の容量を決定することを特徴とする半導体記憶装置。

[請求項10]

請求項8に記載の半導体記憶装置において、

前記制御回路は、前記論理アドレスに対する前記プロックサイズを示すプロックサイズテーブルを作成することを特徴とする半導体記憶装置。

[請求項11]

請求項9に記載の半導体記憶装置において、

前記制御回路は、前記論理アドレスに領域に対する前記物理アドレス領域を示すアドレス変換テーブルを作成することを特徴とする半導体

記憶装置。

[請求項12] 請求項8に記載の半導体記憶装置において、

前記制御回路は、前記第1特徴量が大きいほど、より小さな前記プロックサイズを前記論理アドレスへ割り当てる特徴とする半導体記憶装置。

[請求項13] 請求項9に記載の半導体記憶装置において、

前記制御回路は、前記第2特徴量が大きいほど、より大きな前記物理アドレス領域の容量を、前記論理アドレス領域へ割り当てる特徴とする半導体記憶装置。

[請求項14] 請求項8に記載の半導体記憶装置において、

前記制御回路は、期間T内で、前記制御回路へ入力したライトリクエストに対して、前記第1特徴量を計算し、前記第1特徴量に基づいて、前記不揮発性メモリの前記物理アドレスを含む前記プロックのプロックサイズを決定する特徴とする半導体記憶装置。

[請求項15] 請求項9に記載の半導体記憶装置において、

前記制御回路は、期間T内で、前記論理アドレス毎に、前記制御回路へ入力するライトリクエストの第2特徴量を計算し、前記第2特徴量に基づいて、前記論理アドレスを複数個分含む論理アドレス領域の容量に対する、前記物理アドレスを複数個分含む物理アドレス領域の容量を決定する特徴とする半導体記憶装置。

[図1]

図1

[図2]

図2

[図3]

図3

[図4]

図4

[図5]

図5

[図6]

図6

[図7]

図7

[図8]

図8

[図9]

図9

[図10]

図10

[図11]

図11

[図12]

図12

[図13]

## 図13

(A)

| DLAD    | WCRATE1 | AWD | WDRATE | BLKFCT | BLKSIZE | PVFCT | PV SIZE |

|---------|---------|-----|--------|--------|---------|-------|---------|

| 0~63    | 0.36    | 8   | 1.8    | 8.28   | 64      | 0.25  | 32      |

| 64~127  | 0.3     | 8   | 1.5    | 6.9    | 64      | 0.20  | 26      |

| 128~191 | 0.1     | 8   | 0.5    | 2.3    | 128     | 0.068 | 9       |

| 192~255 | 0.1     | 16  | 1      | 1.15   | 256     | 0.137 | 18      |

| 256~319 | 0.05    | 16  | 0.5    | 0.58   | 512     | 0.068 | 9       |

| 320~383 | 0.05    | 32  | 1      | 0.29   | 512     | 0.137 | 18      |

| 384~447 | 0.03    | 32  | 0.6    | 0.17   | 1024    | 0.082 | 11      |

| 448~511 | 0.01    | 64  | 0.4    | 0.03   | 1024    | 0.055 | 7       |

| WRT1AVG | AWDT | LCP | PVARA |

|---------|------|-----|-------|

| 0.125   | 23   | 64  | 128   |

(B)

| DLAD    | BLKSIZE | DPAD             | DPAD SIZE   |

|---------|---------|------------------|-------------|

| 0~63    | 64      | 0~63, 512~543    | 96 = 64+32  |

| 64~127  | 64      | 64~127, 544~569  | 90 = 64+26  |

| 128~191 | 128     | 128~191, 570~578 | 73 = 64+9   |

| 192~255 | 256     | 192~255, 579~595 | 82 = 64+18  |

| 256~319 | 512     | 256~319, 594~604 | 73 = 64 + 9 |

| 320~383 | 512     | 320~383, 603~621 | 82 = 64+18  |

| 384~447 | 1024    | 384~447, 622~632 | 75 = 64 +11 |

| 448~511 | 1024    | 448~511, 631~639 | 71 = 64 + 7 |

| PRAREA  |

|---------|

| 512~639 |

[図14]

## 図14

(A)

| DLAD    | WCRATE1 | AWD | WDRATE | BLKFCT | BLKSIZE | PVFCT | PV SIZE |

|---------|---------|-----|--------|--------|---------|-------|---------|

| 0~63    | 0.48    | 8   | 1.8    | 11.04  | 32      | 0.41  | 53      |

| 64~127  | 0.32    | 8   | 1.5    | 7.3    | 64      | 0.275 | 35      |

| 128~191 | 0.105   | 8   | 0.5    | 2.4    | 128     | 0.09  | 12      |

| 192~255 | 0.05    | 16  | 1      | 0.58   | 512     | 0.086 | 11      |

| 256~319 | 0.02    | 16  | 0.5    | 0.23   | 512     | 0.034 | 4       |

| 320~383 | 0.01    | 32  | 1      | 0.06   | 512     | 0.034 | 4       |

| 384~447 | 0.01    | 32  | 0.6    | 0.06   | 1024    | 0.034 | 4       |

| 448~511 | 0.005   | 64  | 0.4    | 0.01   | 1024    | 0.034 | 4       |

| WRT1AVG | AWDT | LCP | PVAREA |

|---------|------|-----|--------|

| 0.125   | 23   | 64  | 128    |

(B)

| DLAD    | BLKSIZE | DPAD             | DPAD SIZE   |

|---------|---------|------------------|-------------|

| 0~63    | 32      | 0~63, 512~564    | 117 = 64+53 |

| 64~127  | 64      | 64~127, 565~599  | 99 = 64+35  |

| 128~191 | 128     | 128~191, 600~610 | 76 = 64+12  |

| 192~255 | 512     | 192~255, 611~621 | 75 = 64+11  |

| 256~319 | 512     | 256~319, 622~626 | 68 = 64+4   |

| 320~383 | 512     | 320~383, 627~630 | 68 = 64+4   |

| 384~447 | 1024    | 384~447, 631~635 | 68 = 64+4   |

| 448~511 | 1024    | 448~511, 636~649 | 68 = 64+4   |

|         |

|---------|

| PRAREA  |

| 512~639 |

[図15]

図15

[図16]

16

[図17]

図17

[図18]

図18

[図19]

図19

## INTERNATIONAL SEARCH REPORT

International application No.

PCT / JP2 015 / 062853

## A. CLASSIFICATION OF SUBJECT MATTER

G 06F1 2/02 (2006.01)i, G 06F12 / 00 (2006.01)i, G 11C13 / 00 (2006.01)i

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

G 06F12 / 00-G06F12 / 06, G 11C16 / 02-G11C17 / 18, G 11C13 / 00

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

|         |         |        |           |           |        |         |        |           |           |

|---------|---------|--------|-----------|-----------|--------|---------|--------|-----------|-----------|

| Jitsuyo | Shinan  | Koho   | 1922-1996 | Jitsuyo   | Shinan | Toroku  | Koho   | 1996-2015 |           |

| Kokai   | Jitsuyo | Shinan | Koho      | 1971-2015 | Toroku | Jitsuyo | Shinan | Koho      | 1994-2015 |

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                | Relevant to claim No. |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X<br>A    | J P 2013 - 250982 A (Samsung Electronics Co., Ltd .),<br>12 December 2013 (12.12.2013),<br>paragraphs [0021] to [0031], [0037], [0067]<br>& U S 2013 / 0326119 A1 | 7<br>1-6, 8-15        |

| A         | J P 2002 - 133877 A (Toshiba Corp .),<br>10 May 2002 (10.05.2002),<br>paragraphs [0037] to [0039], [0042]<br>(Family : none )                                     | 1 - 15                |

Further documents are listed in the continuation of Box C. See patent family annex.

\* Special categories of cited documents:

'A' document defining the general state of the art which is not considered to be of particular relevance

'E' earlier application or patent but published on or after the international filing date

'L' document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

'O' document referring to an oral disclosure, use, exhibition or other means

'P' document published prior to the international filing date but later than the priority date claimed

'T' later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

'X' document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

'Y' document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

'&amp;' document member of the same patent family

Date of the actual completion of the international search

16 June 2015 (16.06.15)Date of mailing of the international search report

30 June 2015 (30.06.15)Name and mailing address of the ISA/

Japan Patent Office

3-4-3, Kasumigaseki, Chiyoda-ku,

Tokyo 100-8915, JapanAuthorized officer

Telephone No.

## A. 発明の属する分野の分類 (国際特許分類 (IPC))

Int.Cl. G06F12/02 (2006. 01) i, G06F12/00 (2006. 01) i, G11C13/00 (2006. 01) i

## B. 調査を行った分野

## 調査を行った最小限資料 (国際特許分類 (IPC))

Int.Cl. G06F12/00- G06F12/06, G11C16/02-G1 1C17/18, G11C13/00

## 最小限資料以外の資料で調査を行った分野に含まれるもの

|             |            |

|-------------|------------|

| 日本国実用新案公報   | 1922—1996年 |

| 日本国公開実用新案公報 | 1971—2015年 |

| 日本国実用新案登録公報 | 1996—2015年 |

| 日本国登録実用新案公報 | 1994—2015年 |

## 国際調査で使用した電子データベース (データベースの名称、調査に使用した用語)

## C. 関連すると認められる文献

| 引用文献の<br>カテゴリー水 | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                           | 関連する<br>請求項の番号 |

|-----------------|-----------------------------------------------------------------------------|----------------|

| X               | JP 2013-250982 A (三星電子株式会社) 2013.12.12 ,                                    | 7              |

| A               | 段落 [0021] - [0031] , [0037], [0067] & U.S. 2013/0326119 A 1                 | 1-6, 8-15      |

| A               | JP 2002-133877 A (株式会社東芝) 2002.05.10 ,<br>段落 [0037]-[0039] [0042] (ファミリーなし) | 1-15           |

C 欄の続きにも文献が列挙されている。 パテントファミリーに関する別紙を参照。

## \* 引用文献のカテゴリー

- 「」特に関連のある文献ではなく、一般的技術水準を示すもの

- 「」国際出願日前の出願または特許であるが、国際出願日以後に公表されたもの

- 「」優先権主張に疑義を提起する文献又は他の文献の発行日若しくは他の特別な理由を確立するために引用する文献（理由を付す）

- 「」口頭による開示、使用、展示等に言及する文献

- 「」国際出願日前で、かつ優先権の主張の基礎となる出願

## の日の後に公表された文献

- 「」国際出願日又は優先日後に公表された文献であって出願と矛盾するものではなく、発明の原理又は理論の理解のために引用するもの

- 「」特に関連のある文献であって、当該文献のみで発明の新規性又は進歩性がないと考えられるもの

- 「」特に関連のある文献であって、当該文献と他の1以上の文献との、当業者にとって自明である組合せによって進歩性がないと考えられるもの

- 「」同一パテントファミリー文献

## 国際調査を完了した日

16. 06. 2015

## 国際調査報告の発送日

30. 06. 2015

## 国際調査機関の名称及びあて先

日本国特許庁 (ISA/JP)

郵便番号 100-8915

東京都千代田区霞が関三丁目4番3号

## 特許庁審査官 権限のある職員 )

5U 5089

塩澤 如正

電話番号 03-3581-1101 内線 3565